半導体回路パターンの形成方法

【課題】スループットを短縮し、所望の回路パターンを形成することが可能な半導体回路パターンの形成方法を提供する。

【解決手段】半導体基板上に被エッチング膜を形成し、この被エッチング膜上に現像液溶解性膜を形成する。次に、現像液溶解性膜上にフォトレジスト膜を形成し、フォトマスクを介してフォトレジスト膜を露光する。さらに、現像液を用いてフォトレジスト膜を現像する。この工程では、フォトレジストパターンの下側の現像液溶解性膜を、アンダーカット状の残存部分を残すように溶解させる。次に、フォトレジスト膜を覆うように耐エッチング膜を形成したのち、フォトレジスト膜を除去することにより、被エッチング膜上に、フォトレジスト膜の開口部に対応する耐エッチング膜のパターンを形成するリフトオフ工程を行う。その後、現像液溶解性膜と耐エッチング膜とをマスクとして、被エッチング膜をエッチングする。

【解決手段】半導体基板上に被エッチング膜を形成し、この被エッチング膜上に現像液溶解性膜を形成する。次に、現像液溶解性膜上にフォトレジスト膜を形成し、フォトマスクを介してフォトレジスト膜を露光する。さらに、現像液を用いてフォトレジスト膜を現像する。この工程では、フォトレジストパターンの下側の現像液溶解性膜を、アンダーカット状の残存部分を残すように溶解させる。次に、フォトレジスト膜を覆うように耐エッチング膜を形成したのち、フォトレジスト膜を除去することにより、被エッチング膜上に、フォトレジスト膜の開口部に対応する耐エッチング膜のパターンを形成するリフトオフ工程を行う。その後、現像液溶解性膜と耐エッチング膜とをマスクとして、被エッチング膜をエッチングする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体回路パターンの形成方法に関する。

【背景技術】

【0002】

一般に、半導体回路パターンは、以下のようなフォトリソグラフィ工程により形成される。まず、半導体基板上にシリコン酸化膜や金属膜などの被エッチング膜を堆積し、その表面にフォトレジストを塗布する。次に、フォトマスクを用いてフォトレジストを露光して回路パターンの潜像を形成し、現像液を用いてフォトレジストを現像する。ポジ型フォトレジストの場合には、フォトレジストの露光部分(潜像以外の部分)が現像液により除去される。その後、被エッチング膜のフォトレジストで被覆されていない部分をエッチングにより除去し、これにより半導体基板上に回路パターンが形成される。

【0003】

また、開口部を形成したフォトレジスト上に金属膜を堆積し、溶剤等を用いてフォトレジストを(その上の金属膜と共に)除去するリフトオフ工程により、微細な金属膜パターンを形成することも提案されている(例えば、特許文献1,2参照)。

【0004】

近年、回路パターンの更なる微細化に伴い、2回のフォトリソグラフィ工程を行うダブルパターニング法が提案されている。このダブルパターニング法では、第1のフォトマスクと第2のフォトマスクを用いて2回の露光を行う。第1および第2のフォトマスクは、形成する回路パターンのピッチ(W)の2倍のピッチ(2×W)のラインパターンを、互いに半ピッチ(W)だけずらして形成したものである。

【0005】

1回目のフォトリソグラフィ工程では、半導体基板上に被エッチング膜を堆積し、さらに金属等のハードマスク(耐エッチング膜)を堆積したのち、その表面にフォトレジストを塗布する。次に、第1のフォトマスクを介してフォトレジストを露光し、現像およびエッチングを行う。これにより、被エッチング膜上に、ハードマスクのパターンが形成される。

【0006】

さらに、2回目のフォトリソグラフィ工程では、ハードマスクのパターンが形成された被エッチング膜上に、フォトレジストをさらに塗布する。次に、第2のフォトマスクを用いてフォトレジストを露光し、現像およびエッチングを行う。これにより、被エッチング膜上に、第1および第2のフォトマスクのパターンを合成した、ピッチWのハードマスクパターンが形成される。このハードマスクを介して被エッチング膜をエッチングすることにより、ピッチWの微細な回路パターンが形成される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2004−335775号公報(図1参照)

【特許文献2】特開2003−289165号公報(図2参照)

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、このようなダブルパターニング法では、2回のフォトリソグラフィ工程を実施する必要があるため、処理時間が長く、スループットが低下する上、製造コストが高くなる。また、第1のフォトマスクと第2のフォトマスクとの重ね合わせ精度によっては、回路パターンのピッチにずれが生じ、あるいは回路パターンが重なり合って線幅が太くなるなど、所望の回路パターンを形成できない可能性がある。

【0009】

本発明は、上記の課題を解決するためになされたものであり、スループットを短縮し、所望の回路パターンを形成することが可能な半導体回路パターンの形成方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明に係る半導体回路パターンの形成方法は、半導体基板上に被エッチング膜を形成する工程と、被エッチング膜上に現像液溶解性膜を形成する工程と、現像液溶解性膜上にフォトレジスト膜を形成する工程と、フォトマスクを介してフォトレジスト膜を露光する工程と、現像液を用いてフォトレジスト膜を現像する工程であって、フォトレジスト膜の下側の現像液溶解性膜をアンダーカット状の残存部分を残して溶解させる工程と、フォトレジスト膜を覆うように耐エッチング膜を形成したのち、フォトレジスト膜を除去することにより、被エッチング膜上に、フォトレジスト膜の開口部に対応する耐エッチング膜のパターンを形成するリフトオフ工程と、現像液溶解性膜と耐エッチング膜とをマスクとして被エッチング膜をエッチングする工程とを有する。

【発明の効果】

【0011】

本発明では、リフトオフ工程により形成された耐エッチング膜と、アンダーカット状に残った現像液溶解性膜とをマスクとして、被エッチング膜をエッチングすることにより、1回のフォトリソグラフィ工程で微細な回路パターンを形成することができる。そのため、ダブルパターニング法と比較してスループットを短縮することができ、製造コストを低減することができる。また、複数のフォトマスクを重ね合わせる必要がないため、フォトマスクの位置ずれ等に起因する精度の低下がなく、所望の回路パターンを形成することができる。

【図面の簡単な説明】

【0012】

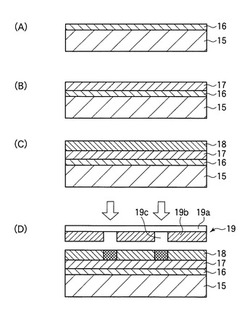

【図1】本発明の実施の形態における半導体回路パターンの形成方法を示す図である。

【図2】本発明の実施の形態における半導体回路パターンの形成方法を示す図である。

【図3】本発明の実施の形態における半導体回路パターンの形成方法で用いるフォトマスクを説明するための図である。

【図4】比較例における半導体回路パターンの形成方法を示す図である。

【図5】比較例における半導体回路パターンの形成方法において用いられるフォトマスクを説明するための図である。

【図6】比較例における半導体回路パターンの形成方法を示す図である。

【図7】比較例における半導体回路パターンの形成方法を示す図である。

【発明を実施するための形態】

【0013】

以下では、本発明の実施の形態について、図面を参照して説明する。

図1(A)〜(D)および図2(A)〜(D)は、本発明の実施の形態における半導体回路パターンの形成方法を示す工程毎の断面図である。本実施の形態における半導体回路パターンの形成方法は、現像液溶解性の膜を用いることにより、短いスループットでの、微細な回路パターンの形成を可能にしたものである。

【0014】

まず、図1(A)に示すように、半導体基板(ウエハ)15上に、被エッチング膜16を堆積する。この被エッチング膜16は、例えば、ポリシリコンまたはAl−Cuである。被エッチング膜16の厚さは、ポリシリコンの場合には約0.15μm〜0.30μmであり、Al−Cuの場合には約0.25μm〜0.40μmである。

【0015】

この被エッチング膜16上に、図1(B)に示すように、現像液溶解性の樹脂を塗布し、現像液溶解性膜17を形成する。この現像液溶解性膜17は、例えば、ポリアミック酸であり、厚さは約0.40μmである。現像液溶解性膜17は、後述する現像液に溶解するものであり、また、耐エッチング性を有するものである。

【0016】

次に、図1(C)に示すように、現像液溶解性膜17上にフォトレジストを塗布し、フォトレジスト膜18を形成する。このフォトレジスト膜18は、例えば、ポリヒドロキシスチレンをベースとした樹脂を含むKrfエキシマ用レジストであり、厚さは約0.4μm〜0.60μmである。

【0017】

次に、図1(D)に示すように、フォトマスク19を用いて、フォトレジスト膜18を露光する。フォトマスク19は、ポジ型、ネガ型のいずれであってもよいが、ここではポジ型であるものとして説明する。

【0018】

このフォトマスク19は、図3(B)に模式的に示すように、例えば石英ガラス等の基板19a上に、銅(Cu)等の遮光膜19bを形成し、ラインパターン19c(フォトレジストがポジ型の場合は光透過部)を形成したものである。ラインパターン19cのピッチは、形成する回路パターンL(図3(A))のピッチWの2倍(2×W)である。

【0019】

次に、図2(A)に示すように、現像液を用いて、フォトレジスト膜18を現像する。現像液としては、例えば、2.38質量%テトラメチルアンモニウムヒドロキシド“NMD−3”(東京応化工業株式会社製)を用いる。フォトレジスト18の露光部分は除去されて開口部となり、フォトレジストパターン18aが形成される。

【0020】

この現像工程では、フォトレジスト18の下側の現像液溶解性膜17も溶解して除去される。現像液溶解性膜17の溶解は、フォトレジストパターン18aの開口部(露光部分)の直下から進行し、パターン部分(非露光部分)の直下に一定幅のアンダーカット状の残存部分が残る。この現像液溶解性膜17のアンダーカット形状は、例えば、現像液濃度(2.38%)、現像時間、現像後のベーク温度・ベーク時間等により制御することができる。

【0021】

次に、図2(B)に示すように、フォトレジストパターン18aを覆うように、例えば蒸着により、耐エッチング膜20を堆積する。このとき、被エッチング膜16の、フォトレジストパターン18aの開口部を介して露出する部分も、耐エッチング膜20により被覆される。耐エッチング膜20は、例えば、窒化膜であり、厚さは約0.10〜0.20μmである。

【0022】

次に、図2(C)に示すように、フォトレジストパターン18aを、例えば剥離液に浸すことによって除去する。これにより、被エッチング膜16上には、上述したアンダーカット状の現像液溶解性膜17と共に、リフトオフ工程により形成された耐エッチング膜20が残る。

【0023】

その後、図2(D)に示すように、現像液溶解性膜17と耐エッチング膜20とをハードマスクとして、被エッチング膜16をエッチングする。ここでは、例えばドライエッチングを行う。これにより、被エッチング膜16の、現像液溶解性膜17および耐エッチング膜20で被覆されていない部分が除去され、回路パターンが形成される。

【0024】

最後に、現像液溶解性膜17を、例えばUVアッシングにより除去し、耐エッチング膜20を、例えばフロロカーボン(CF)系ガスを用いたドライエッチングにより除去する。これにより、半導体回路パターンの形成が完了する。

【0025】

上記の図2(D)に示した工程において、耐エッチング膜20は、フォトレジストパターン18aの開口部に形成されたものであるため、(フォトマスク19のラインパターンに対応して)ピッチは2×Wである。一方、現像液溶解性膜17は、フォトレジストパターン18aのパターン部分の直下にアンダーカット状に残った部分であるため、ピッチは2×Wであるが、耐エッチング膜20のパターンに対して半ピッチ(W)だけずれている。従って、耐エッチング膜20と現像液溶解性膜17とで形成される合成パターンのピッチは、Wとなる。

【0026】

そのため、耐エッチング膜20と現像液溶解性膜17とをハードマスクとしてエッチングを行うことにより、フォトマスク19のラインパターンのピッチ(2×W)の半分のピッチ(W)の回路パターンを半導体基板15上に形成することができる。

【0027】

以上説明したように、本実施の形態における半導体回路パターンの形成方法によれば、リフトオフ工程により形成した耐エッチング膜20と、アンダーカット状に残った現像液溶解性膜17とをハードマスクとして、被エッチング膜16をエッチングすることにより、フォトマスク19のラインパターンのピッチ(2×W)の半分のピッチ(W)で回路パターンを形成することができる。このように、1回のフォトリソグラフィ工程で微細な回路パターンを形成することができるため、ダブルパターニング法と比較して、成膜工程やエッチング工程を削減することができ、スループットを短縮することができる。

【0028】

また、ダブルパターニング法のように複数のフォトマスクを重ね合わせる必要がないため、フォトマスクの重ね合わせ位置ずれ等による精度の低下がなく、所望の回路パターンを形成することができる。また、フォトマスクも1つで済むため、製造コストを低減することができる。

【0029】

なお、図1〜図2の各工程において説明した材料、膜厚、エッチング法などの具体例は、あくまでも好ましい一例であり、本発明は、これらの例に限定されるものではない。

【0030】

次に、本発明の実施の形態に対する比較例について、図4〜図7を参照して説明する。

【0031】

図4(A)〜(D)は、一般的な半導体回路パターンの形成方法を示す図である。

まず、図4(A)に示すように、半導体基板1上に、シリコン酸化膜や金属膜などの被エッチング膜2を堆積する。次に、この被エッチング膜2上に、図4(B)に示すように、フォトレジスト膜3を形成する。

【0032】

次に、図4(C)に示すように、フォトレジスト膜3を、フォトマスク4を介して露光し、フォトレジスト膜3に回路パターンの潜像を形成する。フォトマスク4は、形成する回路パターンのピッチと同一ピッチのラインパターンを形成したものである。

【0033】

その後、図4(D)に示すように、現像液を用いてフォトレジスト3を現像する。被エッチング膜2のフォトレジスト膜3で被覆されていない部分は、エッチングにより除去され、半導体基板1上に回路パターンが形成される。

【0034】

この方法では、半導体基板1上に形成される回路パターンのピッチを狭くするためには、フォトマスク4のラインパターンのピッチを狭くする必要がある。そのため、回路パターンの微細化への対応には限界がある。

【0035】

次に、ダブルパターニング法について説明する。

図5は、ダブルパターニング法で用いるフォトマスクを示す図である。ダブルパターニング法では、ピッチWで配列された回路パターンL(図5(A))を、2×Wのピッチで配列されたラインパターンaと、同じく2×Wのピッチで配置されたラインパターンbとに分割し、ラインパターンaのみを形成した第1のフォトマスク8(図5(B))と、ラインパターンbのみを形成した第2のフォトマスク9(図5(C))とを用いる。

【0036】

図6(A)〜(F)および図7(A)〜(E)は、ダブルパターニング法を示す図である。1回目のフォトリソグラフィ工程では、まず、図6(A)に示すように、半導体基板10上に被エッチング膜11を堆積する。

【0037】

次に、図6(B)に示すように、被エッチング膜11上に、金属等のハードマスク(耐エッチング膜)12を堆積する。このハードマスク12の表面に、図6(C)に示すように、フォトレジスト膜13を形成する。

【0038】

次に、図6(D)に示すように、第1のフォトマスク8を用いてフォトレジスト膜13を露光する。その後、図6(E)に示すように、フォトレジスト膜13を現像することにより、フォトレジストパターン13aを形成する。

【0039】

次に、図6(F)に示すように、ハードマスク12のフォトレジストパターン13aで被覆されていない部分をエッチングにより除去することにより、被エッチング膜11上に、第1のフォトマスク8に対応するハードマスクパターン12aを形成する。その後、フォトレジストパターン13aを除去する。

【0040】

2回目のフォトリソグラフィ工程では、まず、図7(A)に示すように、被エッチング膜11上に、(被エッチング膜11上のハードマスク12aのパターンを覆うように)フォトレジストを塗布し、フォトレジスト膜14を形成する。

【0041】

次に、図7(B)に示すように、第2のフォトマスク9を用いてフォトレジス膜14を露光する。その後、図7(C)に示すように、フォトレジスト膜14を現像することにより、フォトレジストパターン14aを形成する。

【0042】

次に、図7(D)に示すように、ハードマスク12のフォトレジストパターン14aに被覆されていない部分をエッチングにより除去する。これにより、被エッチング膜11上には、1回目の露光・現像・エッチング(図6(D)〜(F))により形成されたハードマスクパターン12aと、2回目の露光・現像・エッチング(図7(B)〜(D))により形成されたハードマスクパターン12bとが形成される。

【0043】

その後、図7(E)に示すように、ハードマスクパターン12a,12bを用いて被エッチング膜11をエッチングすることにより、回路パターンを形成する。

【0044】

このダブルパターニング法では、微細な回路パターンを形成することはできるが、2回のフォトリソグラフィ工程を実施する必要があるため、処理に要する時間が長く、スループットが低下する上、製造コストが高くなる。また、第1のフォトマスク8と第2のフォトマスク9との重ね合わせ精度が低いと、回路パターンのピッチにずれが生じ、あるいは回路パターンが重なり合って線幅が太くなるなど、所望の回路パターンを形成できない可能性がある。

【0045】

これに対し、上述した本発明の実施形態による半導体回路パターンの形成方法(図1〜図3)によれば、現像工程においてアンダーカット状に形成した現像液溶解性膜17と、リフトオフ工程により形成した耐エッチング膜20とをマスクとして、被エッチング膜16をエッチングするため、1回のフォトリソグラフィ工程で微細な回路パターンを高い精度で形成することができ、スループットを短縮することができる上、製造コストを低減することができる。さらに、ダブルパターニング法のように複数のフォトマスクを重ね合わせる必要がないため、フォトマスクの重ね合わせ位置ずれ等による精度の低下がなく、所望の回路パターンを形成することができる。

【符号の説明】

【0046】

15 半導体基板、 16 被エッチング膜、 17 現像液溶解性膜、 18 フォトレジスト膜、 18a フォトレジストパターン、 19 フォトマスク、 19a 基板、 19b ラインパターン、 20 耐エッチング膜、 L ラインパターン、 W 回路パターンのピッチ。

【技術分野】

【0001】

本発明は、半導体回路パターンの形成方法に関する。

【背景技術】

【0002】

一般に、半導体回路パターンは、以下のようなフォトリソグラフィ工程により形成される。まず、半導体基板上にシリコン酸化膜や金属膜などの被エッチング膜を堆積し、その表面にフォトレジストを塗布する。次に、フォトマスクを用いてフォトレジストを露光して回路パターンの潜像を形成し、現像液を用いてフォトレジストを現像する。ポジ型フォトレジストの場合には、フォトレジストの露光部分(潜像以外の部分)が現像液により除去される。その後、被エッチング膜のフォトレジストで被覆されていない部分をエッチングにより除去し、これにより半導体基板上に回路パターンが形成される。

【0003】

また、開口部を形成したフォトレジスト上に金属膜を堆積し、溶剤等を用いてフォトレジストを(その上の金属膜と共に)除去するリフトオフ工程により、微細な金属膜パターンを形成することも提案されている(例えば、特許文献1,2参照)。

【0004】

近年、回路パターンの更なる微細化に伴い、2回のフォトリソグラフィ工程を行うダブルパターニング法が提案されている。このダブルパターニング法では、第1のフォトマスクと第2のフォトマスクを用いて2回の露光を行う。第1および第2のフォトマスクは、形成する回路パターンのピッチ(W)の2倍のピッチ(2×W)のラインパターンを、互いに半ピッチ(W)だけずらして形成したものである。

【0005】

1回目のフォトリソグラフィ工程では、半導体基板上に被エッチング膜を堆積し、さらに金属等のハードマスク(耐エッチング膜)を堆積したのち、その表面にフォトレジストを塗布する。次に、第1のフォトマスクを介してフォトレジストを露光し、現像およびエッチングを行う。これにより、被エッチング膜上に、ハードマスクのパターンが形成される。

【0006】

さらに、2回目のフォトリソグラフィ工程では、ハードマスクのパターンが形成された被エッチング膜上に、フォトレジストをさらに塗布する。次に、第2のフォトマスクを用いてフォトレジストを露光し、現像およびエッチングを行う。これにより、被エッチング膜上に、第1および第2のフォトマスクのパターンを合成した、ピッチWのハードマスクパターンが形成される。このハードマスクを介して被エッチング膜をエッチングすることにより、ピッチWの微細な回路パターンが形成される。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2004−335775号公報(図1参照)

【特許文献2】特開2003−289165号公報(図2参照)

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、このようなダブルパターニング法では、2回のフォトリソグラフィ工程を実施する必要があるため、処理時間が長く、スループットが低下する上、製造コストが高くなる。また、第1のフォトマスクと第2のフォトマスクとの重ね合わせ精度によっては、回路パターンのピッチにずれが生じ、あるいは回路パターンが重なり合って線幅が太くなるなど、所望の回路パターンを形成できない可能性がある。

【0009】

本発明は、上記の課題を解決するためになされたものであり、スループットを短縮し、所望の回路パターンを形成することが可能な半導体回路パターンの形成方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明に係る半導体回路パターンの形成方法は、半導体基板上に被エッチング膜を形成する工程と、被エッチング膜上に現像液溶解性膜を形成する工程と、現像液溶解性膜上にフォトレジスト膜を形成する工程と、フォトマスクを介してフォトレジスト膜を露光する工程と、現像液を用いてフォトレジスト膜を現像する工程であって、フォトレジスト膜の下側の現像液溶解性膜をアンダーカット状の残存部分を残して溶解させる工程と、フォトレジスト膜を覆うように耐エッチング膜を形成したのち、フォトレジスト膜を除去することにより、被エッチング膜上に、フォトレジスト膜の開口部に対応する耐エッチング膜のパターンを形成するリフトオフ工程と、現像液溶解性膜と耐エッチング膜とをマスクとして被エッチング膜をエッチングする工程とを有する。

【発明の効果】

【0011】

本発明では、リフトオフ工程により形成された耐エッチング膜と、アンダーカット状に残った現像液溶解性膜とをマスクとして、被エッチング膜をエッチングすることにより、1回のフォトリソグラフィ工程で微細な回路パターンを形成することができる。そのため、ダブルパターニング法と比較してスループットを短縮することができ、製造コストを低減することができる。また、複数のフォトマスクを重ね合わせる必要がないため、フォトマスクの位置ずれ等に起因する精度の低下がなく、所望の回路パターンを形成することができる。

【図面の簡単な説明】

【0012】

【図1】本発明の実施の形態における半導体回路パターンの形成方法を示す図である。

【図2】本発明の実施の形態における半導体回路パターンの形成方法を示す図である。

【図3】本発明の実施の形態における半導体回路パターンの形成方法で用いるフォトマスクを説明するための図である。

【図4】比較例における半導体回路パターンの形成方法を示す図である。

【図5】比較例における半導体回路パターンの形成方法において用いられるフォトマスクを説明するための図である。

【図6】比較例における半導体回路パターンの形成方法を示す図である。

【図7】比較例における半導体回路パターンの形成方法を示す図である。

【発明を実施するための形態】

【0013】

以下では、本発明の実施の形態について、図面を参照して説明する。

図1(A)〜(D)および図2(A)〜(D)は、本発明の実施の形態における半導体回路パターンの形成方法を示す工程毎の断面図である。本実施の形態における半導体回路パターンの形成方法は、現像液溶解性の膜を用いることにより、短いスループットでの、微細な回路パターンの形成を可能にしたものである。

【0014】

まず、図1(A)に示すように、半導体基板(ウエハ)15上に、被エッチング膜16を堆積する。この被エッチング膜16は、例えば、ポリシリコンまたはAl−Cuである。被エッチング膜16の厚さは、ポリシリコンの場合には約0.15μm〜0.30μmであり、Al−Cuの場合には約0.25μm〜0.40μmである。

【0015】

この被エッチング膜16上に、図1(B)に示すように、現像液溶解性の樹脂を塗布し、現像液溶解性膜17を形成する。この現像液溶解性膜17は、例えば、ポリアミック酸であり、厚さは約0.40μmである。現像液溶解性膜17は、後述する現像液に溶解するものであり、また、耐エッチング性を有するものである。

【0016】

次に、図1(C)に示すように、現像液溶解性膜17上にフォトレジストを塗布し、フォトレジスト膜18を形成する。このフォトレジスト膜18は、例えば、ポリヒドロキシスチレンをベースとした樹脂を含むKrfエキシマ用レジストであり、厚さは約0.4μm〜0.60μmである。

【0017】

次に、図1(D)に示すように、フォトマスク19を用いて、フォトレジスト膜18を露光する。フォトマスク19は、ポジ型、ネガ型のいずれであってもよいが、ここではポジ型であるものとして説明する。

【0018】

このフォトマスク19は、図3(B)に模式的に示すように、例えば石英ガラス等の基板19a上に、銅(Cu)等の遮光膜19bを形成し、ラインパターン19c(フォトレジストがポジ型の場合は光透過部)を形成したものである。ラインパターン19cのピッチは、形成する回路パターンL(図3(A))のピッチWの2倍(2×W)である。

【0019】

次に、図2(A)に示すように、現像液を用いて、フォトレジスト膜18を現像する。現像液としては、例えば、2.38質量%テトラメチルアンモニウムヒドロキシド“NMD−3”(東京応化工業株式会社製)を用いる。フォトレジスト18の露光部分は除去されて開口部となり、フォトレジストパターン18aが形成される。

【0020】

この現像工程では、フォトレジスト18の下側の現像液溶解性膜17も溶解して除去される。現像液溶解性膜17の溶解は、フォトレジストパターン18aの開口部(露光部分)の直下から進行し、パターン部分(非露光部分)の直下に一定幅のアンダーカット状の残存部分が残る。この現像液溶解性膜17のアンダーカット形状は、例えば、現像液濃度(2.38%)、現像時間、現像後のベーク温度・ベーク時間等により制御することができる。

【0021】

次に、図2(B)に示すように、フォトレジストパターン18aを覆うように、例えば蒸着により、耐エッチング膜20を堆積する。このとき、被エッチング膜16の、フォトレジストパターン18aの開口部を介して露出する部分も、耐エッチング膜20により被覆される。耐エッチング膜20は、例えば、窒化膜であり、厚さは約0.10〜0.20μmである。

【0022】

次に、図2(C)に示すように、フォトレジストパターン18aを、例えば剥離液に浸すことによって除去する。これにより、被エッチング膜16上には、上述したアンダーカット状の現像液溶解性膜17と共に、リフトオフ工程により形成された耐エッチング膜20が残る。

【0023】

その後、図2(D)に示すように、現像液溶解性膜17と耐エッチング膜20とをハードマスクとして、被エッチング膜16をエッチングする。ここでは、例えばドライエッチングを行う。これにより、被エッチング膜16の、現像液溶解性膜17および耐エッチング膜20で被覆されていない部分が除去され、回路パターンが形成される。

【0024】

最後に、現像液溶解性膜17を、例えばUVアッシングにより除去し、耐エッチング膜20を、例えばフロロカーボン(CF)系ガスを用いたドライエッチングにより除去する。これにより、半導体回路パターンの形成が完了する。

【0025】

上記の図2(D)に示した工程において、耐エッチング膜20は、フォトレジストパターン18aの開口部に形成されたものであるため、(フォトマスク19のラインパターンに対応して)ピッチは2×Wである。一方、現像液溶解性膜17は、フォトレジストパターン18aのパターン部分の直下にアンダーカット状に残った部分であるため、ピッチは2×Wであるが、耐エッチング膜20のパターンに対して半ピッチ(W)だけずれている。従って、耐エッチング膜20と現像液溶解性膜17とで形成される合成パターンのピッチは、Wとなる。

【0026】

そのため、耐エッチング膜20と現像液溶解性膜17とをハードマスクとしてエッチングを行うことにより、フォトマスク19のラインパターンのピッチ(2×W)の半分のピッチ(W)の回路パターンを半導体基板15上に形成することができる。

【0027】

以上説明したように、本実施の形態における半導体回路パターンの形成方法によれば、リフトオフ工程により形成した耐エッチング膜20と、アンダーカット状に残った現像液溶解性膜17とをハードマスクとして、被エッチング膜16をエッチングすることにより、フォトマスク19のラインパターンのピッチ(2×W)の半分のピッチ(W)で回路パターンを形成することができる。このように、1回のフォトリソグラフィ工程で微細な回路パターンを形成することができるため、ダブルパターニング法と比較して、成膜工程やエッチング工程を削減することができ、スループットを短縮することができる。

【0028】

また、ダブルパターニング法のように複数のフォトマスクを重ね合わせる必要がないため、フォトマスクの重ね合わせ位置ずれ等による精度の低下がなく、所望の回路パターンを形成することができる。また、フォトマスクも1つで済むため、製造コストを低減することができる。

【0029】

なお、図1〜図2の各工程において説明した材料、膜厚、エッチング法などの具体例は、あくまでも好ましい一例であり、本発明は、これらの例に限定されるものではない。

【0030】

次に、本発明の実施の形態に対する比較例について、図4〜図7を参照して説明する。

【0031】

図4(A)〜(D)は、一般的な半導体回路パターンの形成方法を示す図である。

まず、図4(A)に示すように、半導体基板1上に、シリコン酸化膜や金属膜などの被エッチング膜2を堆積する。次に、この被エッチング膜2上に、図4(B)に示すように、フォトレジスト膜3を形成する。

【0032】

次に、図4(C)に示すように、フォトレジスト膜3を、フォトマスク4を介して露光し、フォトレジスト膜3に回路パターンの潜像を形成する。フォトマスク4は、形成する回路パターンのピッチと同一ピッチのラインパターンを形成したものである。

【0033】

その後、図4(D)に示すように、現像液を用いてフォトレジスト3を現像する。被エッチング膜2のフォトレジスト膜3で被覆されていない部分は、エッチングにより除去され、半導体基板1上に回路パターンが形成される。

【0034】

この方法では、半導体基板1上に形成される回路パターンのピッチを狭くするためには、フォトマスク4のラインパターンのピッチを狭くする必要がある。そのため、回路パターンの微細化への対応には限界がある。

【0035】

次に、ダブルパターニング法について説明する。

図5は、ダブルパターニング法で用いるフォトマスクを示す図である。ダブルパターニング法では、ピッチWで配列された回路パターンL(図5(A))を、2×Wのピッチで配列されたラインパターンaと、同じく2×Wのピッチで配置されたラインパターンbとに分割し、ラインパターンaのみを形成した第1のフォトマスク8(図5(B))と、ラインパターンbのみを形成した第2のフォトマスク9(図5(C))とを用いる。

【0036】

図6(A)〜(F)および図7(A)〜(E)は、ダブルパターニング法を示す図である。1回目のフォトリソグラフィ工程では、まず、図6(A)に示すように、半導体基板10上に被エッチング膜11を堆積する。

【0037】

次に、図6(B)に示すように、被エッチング膜11上に、金属等のハードマスク(耐エッチング膜)12を堆積する。このハードマスク12の表面に、図6(C)に示すように、フォトレジスト膜13を形成する。

【0038】

次に、図6(D)に示すように、第1のフォトマスク8を用いてフォトレジスト膜13を露光する。その後、図6(E)に示すように、フォトレジスト膜13を現像することにより、フォトレジストパターン13aを形成する。

【0039】

次に、図6(F)に示すように、ハードマスク12のフォトレジストパターン13aで被覆されていない部分をエッチングにより除去することにより、被エッチング膜11上に、第1のフォトマスク8に対応するハードマスクパターン12aを形成する。その後、フォトレジストパターン13aを除去する。

【0040】

2回目のフォトリソグラフィ工程では、まず、図7(A)に示すように、被エッチング膜11上に、(被エッチング膜11上のハードマスク12aのパターンを覆うように)フォトレジストを塗布し、フォトレジスト膜14を形成する。

【0041】

次に、図7(B)に示すように、第2のフォトマスク9を用いてフォトレジス膜14を露光する。その後、図7(C)に示すように、フォトレジスト膜14を現像することにより、フォトレジストパターン14aを形成する。

【0042】

次に、図7(D)に示すように、ハードマスク12のフォトレジストパターン14aに被覆されていない部分をエッチングにより除去する。これにより、被エッチング膜11上には、1回目の露光・現像・エッチング(図6(D)〜(F))により形成されたハードマスクパターン12aと、2回目の露光・現像・エッチング(図7(B)〜(D))により形成されたハードマスクパターン12bとが形成される。

【0043】

その後、図7(E)に示すように、ハードマスクパターン12a,12bを用いて被エッチング膜11をエッチングすることにより、回路パターンを形成する。

【0044】

このダブルパターニング法では、微細な回路パターンを形成することはできるが、2回のフォトリソグラフィ工程を実施する必要があるため、処理に要する時間が長く、スループットが低下する上、製造コストが高くなる。また、第1のフォトマスク8と第2のフォトマスク9との重ね合わせ精度が低いと、回路パターンのピッチにずれが生じ、あるいは回路パターンが重なり合って線幅が太くなるなど、所望の回路パターンを形成できない可能性がある。

【0045】

これに対し、上述した本発明の実施形態による半導体回路パターンの形成方法(図1〜図3)によれば、現像工程においてアンダーカット状に形成した現像液溶解性膜17と、リフトオフ工程により形成した耐エッチング膜20とをマスクとして、被エッチング膜16をエッチングするため、1回のフォトリソグラフィ工程で微細な回路パターンを高い精度で形成することができ、スループットを短縮することができる上、製造コストを低減することができる。さらに、ダブルパターニング法のように複数のフォトマスクを重ね合わせる必要がないため、フォトマスクの重ね合わせ位置ずれ等による精度の低下がなく、所望の回路パターンを形成することができる。

【符号の説明】

【0046】

15 半導体基板、 16 被エッチング膜、 17 現像液溶解性膜、 18 フォトレジスト膜、 18a フォトレジストパターン、 19 フォトマスク、 19a 基板、 19b ラインパターン、 20 耐エッチング膜、 L ラインパターン、 W 回路パターンのピッチ。

【特許請求の範囲】

【請求項1】

半導体基板上に被エッチング膜を形成する工程と、

前記被エッチング膜上に現像液溶解性膜を形成する工程と、

前記現像液溶解性膜上にフォトレジスト膜を形成する工程と、

フォトマスクを介して前記フォトレジスト膜を露光する工程と、

現像液を用いて前記フォトレジスト膜を現像する工程であって、前記フォトレジスト膜の下側の前記現像液溶解性膜をアンダーカット状の残存部分を残すように溶解させる工程と、

前記フォトレジスト膜を覆うように耐エッチング膜を形成したのち、前記フォトレジスト膜を除去することにより、前記被エッチング膜上に、前記フォトレジスト膜の開口部に対応する前記耐エッチング膜のパターンを形成するリフトオフ工程と、

前記現像液溶解性膜と前記耐エッチング膜とをマスクとして、被エッチング膜をエッチングする工程と

を有することを特徴とする半導体回路パターンの形成方法。

【請求項2】

前記フォトマスクとして、半導体回路パターンの2倍のピッチでパターンが形成されたフォトマスクを用いることを特徴とする請求項1に記載の半導体回路パターンの形成方法。

【請求項3】

前記現像液溶解性膜は、ポリアミック酸を含むことを特徴とする請求項1または2に記載の半導体回路パターンの形成方法。

【請求項1】

半導体基板上に被エッチング膜を形成する工程と、

前記被エッチング膜上に現像液溶解性膜を形成する工程と、

前記現像液溶解性膜上にフォトレジスト膜を形成する工程と、

フォトマスクを介して前記フォトレジスト膜を露光する工程と、

現像液を用いて前記フォトレジスト膜を現像する工程であって、前記フォトレジスト膜の下側の前記現像液溶解性膜をアンダーカット状の残存部分を残すように溶解させる工程と、

前記フォトレジスト膜を覆うように耐エッチング膜を形成したのち、前記フォトレジスト膜を除去することにより、前記被エッチング膜上に、前記フォトレジスト膜の開口部に対応する前記耐エッチング膜のパターンを形成するリフトオフ工程と、

前記現像液溶解性膜と前記耐エッチング膜とをマスクとして、被エッチング膜をエッチングする工程と

を有することを特徴とする半導体回路パターンの形成方法。

【請求項2】

前記フォトマスクとして、半導体回路パターンの2倍のピッチでパターンが形成されたフォトマスクを用いることを特徴とする請求項1に記載の半導体回路パターンの形成方法。

【請求項3】

前記現像液溶解性膜は、ポリアミック酸を含むことを特徴とする請求項1または2に記載の半導体回路パターンの形成方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−176042(P2011−176042A)

【公開日】平成23年9月8日(2011.9.8)

【国際特許分類】

【出願番号】特願2010−37731(P2010−37731)

【出願日】平成22年2月23日(2010.2.23)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【Fターム(参考)】

【公開日】平成23年9月8日(2011.9.8)

【国際特許分類】

【出願日】平成22年2月23日(2010.2.23)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【Fターム(参考)】

[ Back to top ]