半導体回路及びテスト方法

【課題】スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供する。

【解決手段】複数の被試験回路と、試験回路に対応して設けられた複数の第1のラッチ回路と、第2のラッチ回路と、パターンアドレスに対応して入力信号が規定されたテストパターンのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する総合判定回路と、複数の第1のラッチ回路と第2のラッチ回路とを、第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

【解決手段】複数の被試験回路と、試験回路に対応して設けられた複数の第1のラッチ回路と、第2のラッチ回路と、パターンアドレスに対応して入力信号が規定されたテストパターンのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する総合判定回路と、複数の第1のラッチ回路と第2のラッチ回路とを、第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体回路、及びテスト方法に関する。

【背景技術】

【0002】

近年のLSI(Large Scale Integration)の高集積化に伴い、ハイエンドのCPUチップには数十個のCPU機能ブロックが搭載される。また、CPU(Central Processing Unit)チップに搭載された各CPU機能ブロックは、それぞれ独立して動作する。このようなCPUチップを使用するシステムでは、一部のCPU機能ブロックを使用しないことにより、システムランクに差異をつける。そこで、全ての機能ブロックが正常に動作する完全良否のCPUチップに加えて、不良のCPU機能ブロックを一部有する部分良否のCPUチップも利用される。

【0003】

CPU機能ブロックの試験は、Logicテスター(ATE:Automated Test Equipment)によって実施される。試験の結果、例えば、4つのCPU機能ブロックを備えるCPUチップについて、1つのCPU機能ブロックが正常に動作しなかった場合、当該CPUチップは3つのCPU機能ブロックのみを有する3Core品とランク判定される。

【0004】

各CPU機能ブロックは、それぞれBIST(built-in self test)回路を有する。そして、Logicテスターは、パターンアドレスに対応して入力信号が規定されたテストパターンに基づいて、CPUチップから各CPU機能ブロックの動作試験の結果を示す良否判定値を出力させる。具体的に、テストパターンに基づいて、BIST回路にCPU機能ブロックの動作試験が指示されると共に、その試験結果を示す良否判定値がスキャンラッチに出力され、スキャンラッチに保持された良否判定値がスキャンチェーンによって順次出力される。

【0005】

続いて、Logicテスターは、例えば、スキャンチェーンから出力された良否判定値と良判定を示す期待値とを順次比較し、全て一致する場合は試験結果をPass、一致しない良否判定値(不良判定)がある場合は試験結果をFailとする。また、Failの場合、Logicテスターは、不良判定を示す良否判定値が出力されたタイミングに対応するパターンアドレスを、不良パターンアドレスとして出力する。そして、Logicテスターは、不良パターンアドレスに基づいて、正常に動作しないCPU機能ブロックを特定する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−122009号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、テストパターンによって、試験の内容が異なる。そのため、各CPU機能ブロックの良否判定値が出力されるタイミングのパターンアドレス(不良パターンアドレス)もテストパターンによって異なる。これにより、Logicテスターは、不良パターンアドレスだけでは、不良判定を示す良否判定値が試験結果として出力されたCPU機能ブロックを特定することができない。

【0008】

そこで、本発明では、スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供することにある。

【課題を解決するための手段】

【0009】

第1の側面は、複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、パターンアドレスに対応して入力信号が規定されたテストパターンの前記パターンアドレス順に入力される前記入力信号に基づいて、前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

【発明の効果】

【0010】

第1の側面によれば、スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する。

【図面の簡単な説明】

【0011】

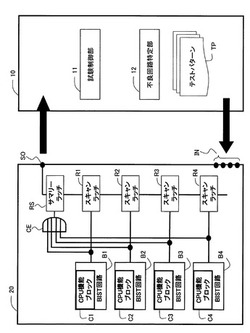

【図1】CPUチップとLogicテスターを表す例図である。

【図2】テストパターンの一例を表す図である。

【図3】Logicテスターの試験処理の流れを表すフローチャート図である。

【図4】CPUチップからの出力値例とテスター情報の一例を表す図である。

【図5】パターンアドレスと、当該パターンアドレスのタイミングに出力される良否判定値に対応するCPU機能ブロックとの関係を表す対応表の一例である。

【図6】本実施の形態例におけるCPUチップとLogicテスターを表す例図である。

【図7】本実施の形態例のCPUチップからの出力値例とテスター情報を表す例図である。

【図8】アドレス差分値と差分値に対応するCPU機能ブロックとの関係を表す図である。

【発明を実施するための形態】

【0012】

以下、図面にしたがって本発明の実施の形態について説明する。ただし、本発明の技術的範囲はこれらの実施の形態に限定されず、特許請求の範囲に記載された事項とその均等物まで及ぶものである。

【0013】

図1は、CPUチップ20とLogicテスター10の一例を表す図である。同図のCPUチップ20は、被試験回路である4つのCPU機能ブロックC1〜C4を搭載し、正常に動作するCPU機能ブロックC1〜C4の数に基づいてその製品ランクが判定される。各CPU機能ブロックC1〜C4にはそれぞれBIST回路B1〜B4が備えられる。また、CPUチップ20は、CPU機能ブロックC1〜C4に対応するスキャンラッチR1〜R4を有する。

【0014】

BIST回路B1〜B4は、例えば、入力信号に基づいて、試験動作用の信号をCPU機能ブロックC1〜C4に入力すると共に、CPU機能ブロックC1〜C4から動作結果の信号を取得して試験の動作結果を示す良否判定値をスキャンラッチR1〜R4に出力する。各スキャンラッチR1〜R4はスキャンチェーンを構成し、各スキャンラッチR1〜R4に保持された良否判定値はスキャンチェーンによって出力端子SOから順番に出力される。

【0015】

図1のCPUチップ20では、出力端子SOに近い順に、CPU機能ブロックC1に対応するスキャンラッチR1から、CPU機能ブロックC4に対応するスキャンラッチR4まで順番に配置されている。そのため、スキャンチェーンは、スキャンラッチR1、R2、R3、R4の順番に、保持する良否判定値をシフトレジスタ動作によって出力する。

【0016】

このように、図1のCPUチップ20では、各BIST回路B1〜B4からの出力された良否判定値を保持させたスキャンラッチR1〜R4でスキャンチェーンを構成し、各良否判定値をひとつの出力端子SOから出力させる。これにより、CPUチップ20はBIST回路B1〜B4毎に出力端子を備える必要がなく、試験用の出力端子の数を最小限に抑えることができる。

【0017】

続いて、図1のLogicテスター10は、試験制御部11と不良回路特定部12とを有する。Logicテスター10は、テストパターンTPに基づいてCPUチップ20の試験を行う。テストパターンTPには、パターンアドレス順に、各パターンアドレスに対応して入力信号が規定される。試験制御部11は、クロック信号に同期して、テストパターンTPのパターンアドレス順に、対応する入力信号をCPUチップ20の入力端子SIに入力する。そして、CPUチップ20において入力信号に基づいて一連の試験処理が行われる。

【0018】

CPUチップ20において、例えば、次のような処理が行われる。BIST回路B1〜B4は、リセット処理及び初期化設定処理の後、CPU機能ブロックC1〜C4の試験動作の制御を行う。具体的に、BIST回路B1〜B4は、入力信号に基づく試験動作をCPU機能ブロックC1〜C4に指示する。そして、BIST回路B1〜B4は、CPU機能ブロックC1〜C4の試験動作が終了すると、その結果情報を取得して良否判定を行い、その良否判定値を対応するスキャンラッチR1〜R4に出力する。そして、スキャンチェーンは、スキャンラッチR1〜R4に保持された良否判定値を順次出力する。

【0019】

CPUチップ20における一連の試験処理の後、続いて、試験制御部11は、CPUチップ20から出力された各CPU機能ブロックC1〜C4の試験動作結果を表す良否判定値と期待値とを比較し、CPUチップ20の試験結果(Pass/Fail)を判定する。この例において、期待値は、良判定を示す良否判定値であるものとする。このため、各良否判定値が全て良判定を示す良否判定値の場合の試験結果はPass、ひとつでも否判定を示す良否判定値の場合の試験結果はFailと判定される。試験結果がFailの場合、試験制御部11は、否判定を示す良否判定値が出力されたタイミングに対応するパターンアドレス(不良パターンアドレス)を、テスター情報として出力する。

【0020】

続いて、Logicテスター10の不良回路特定部12は、試験結果がFailの場合、テスター情報として出力された不良パターンアドレスに基づいて、当該不良パターンアドレスのタイミングに出力された良否判定値に対応するCPU機能ブロックC1〜C4を特定する。Logicテスター10における各処理の詳細については、後述する。

【0021】

図2は、テストパターンTPの一例を表す図である。テストパターンTPにおいて、入力信号に基づいて、CPUチップ10の一連の試験動作が規定される。一連の試験動作とは、前述したとおり、例えば、BIST回路B1〜B4のリセット処理T1及び初期化処理T2、BIST回路B1〜B4によるCPU機能ブロックC1〜C4の試験動作の制御処理T3、スキャンラッチへの各良否判定値の出力処理T4、スキャンチェーンによる各良否判定値の出力処理T5である。

【0022】

また、テストパターンTPには、パターンアドレスに対応して1〜n個の入力信号が規定される。入力信号とは、例えば、BIST回路B1〜B4の試験動作の内容を指示する信号や、試験動作で使用される信号、スキャンチェーンに保持された各良否判定値の出力を指示する信号等である。また、一般的に、試験対象の半導体回路に対して、多数のテストパターンTPが用意される。

【0023】

また、図2のテストパターンTPでは、例えば、パターンアドレスに対応して、出力値に加えて出力信号の期待値EXが規定される。同図における期待値EXとは、パターンアドレスに対応する入力信号が入力されたタイミングに、出力端子SO(図1)から出力される出力信号の期待値である。本実施の形態例では、出力信号の期待値EXとして、例えば、H値、L値、無効な出力値を示す×が規定される。H値は不良判定を示す良否判定値であり、L値は良判定を示す良否判定値である。

【0024】

具体的に、図2に例示したテストパターン1の例TP1では、パターンアドレス1000のタイミングまでは、出力値の期待値に×が規定されている。一方、パターンアドレス1001〜1004に対応する出力値の期待値には、良判定を示すL値が規定されている。これは、パターンアドレス1001〜1004のタイミングに各CPU機能ブロックC1〜C4の良否判定値が出力されることを示す。また、CPU機能ブロックC1〜C4の試験結果を示す良否判定値が全てL値である場合に試験結果がPass、いずれかの良否判定値がH値である場合に試験結果がFailとなることを示す。

【0025】

また、図1で前述したとおり、スキャンチェーンは、CPU機能ブロックC1からCPU機能ブロックC4にかけて対応する良否判定値を順に出力する。そのため、パターンアドレス1001のタイミングで出力される出力値は、出力端子SOに最も近いスキャンラッチR1に保持されるCPU機能ブロックC1の良否判定値を示す。そして、パターンアドレス1002のタイミングで出力される出力値は、次に出力端子SOに近いスキャンラッチR2に保持されるCPU機能ブロックC2の良否判定値を示す。同様に、パターンアドレス1003のタイミングで出力される出力値はCPU機能ブロックC3の良否判定値、パターンアドレス1004のタイミングで出力される出力値はCPU機能ブロックC4の良否判定値を示す。

【0026】

続いて、Logicテスター10によるCPUチップ20の試験処理の流れについて、フローチャート図に基づいて説明する。

【0027】

図3は、Logicテスター10の試験処理の流れを表すフローチャート図である。本実施の形態例では、初めに、処理対象のパターンアドレスが0に初期化される(S10)。そして、Logicテスター10は、テストパターンTPのパターンアドレス順に、パターンアドレスに対応する入力信号をCPUチップ20に入力する(S11)。そして、Logicテスター10は、テストパターンTPにおいて規定された、パターンアドレスに対応する出力信号の期待値が無効(本実施の形態例では×)であるか否かをチェックする(S12)。

【0028】

パターンアドレスに対応する出力信号の期待値が無効の場合(S12のYES)、Logicテスター10は、処理S15に遷移し、パターンアドレスがテストパターンTPにおける最後のパターンアドレスに達したか否かを判定する(S15)。最後のパターンアドレスに達していない場合(S15のNO)、Logicテスター10は、パターンアドレスをインクリメントして(S16)、引き続き、インクリメントしたパターンアドレスに対応する入力信号をCPUチップ20に入力する(S11)。一般的に、各CPU機能ブロックC1〜C4の良否判定値が各スキャンラッチR1〜R4に保持されるタイミングに対応する所定のパターンアドレスまでは、出力信号の期待値は無効(S12のYES)に設定され、パターンアドレスが順次インクリメントされCPUチップ20の試験処理が進められる。

【0029】

一方、パターンアドレスに対応する出力信号の期待値が無効ではない場合(S12のNO)、Logicテスター10は、CPUチップ20から出力された出力値とテストパターンTPに規定されたパターンアドレスに対応する期待値とが一致するか否かを判定する(S13)。一致しない場合(S13のNO)、Logicテスター10は、テスター情報として、期待値と一致しない出力値が出力されたタイミングのパターンアドレス(不良パターンアドレス)と、出力端子情報(本実施の形態例では、必ず出力端子SO)とを出力する(S14)。一方、CPUチップ20から出力された出力値とテストパターンTPに規定されたパターンアドレスに対応する期待値とが一致する場合(S13のYES)、何も出力しない。

【0030】

S13の処理の後、Logicテスター10は、パターンアドレスがテストパターンTPにおける最後のパターンアドレスに達したか否かを判定し(S15)、達していない場合(S15のNO)、パターンアドレスをインクリメントして(S16)、処理S11に戻る。

【0031】

最終的に、パターンアドレスがテストパターンTPの最後に達すると(S15のYES)、Logicテスター10は、テストパターンTPに基づくCPUチップ20の試験結果がPassであるかFailであるかを判定する(S17)。テストパターンTPに基づくCPUチップ20の試験結果がFailの場合(S17のYES)、即ち、期待値と一致しない出力値が出力された場合、続いて、Logicテスター10は、テスター情報に基づいて不良のCPU機能ブロックを特定する(S18)。

【0032】

不良のCPU機能ブロックが特定された場合(S18)、または、試験結果がPassの場合(S17のNO)、Logicテスター10は、一連の試験処理を終了する。そして、Logicテスター10は、別のテストパターンTPに基づいてCPUチップ20の試験を実施する。

【0033】

続いて、図3のフローチャート図におけるテスター情報に基づく不良のCPU機能ブロックの特定処理(S18)について具体的に説明する。

【0034】

図4は、CPUチップ20からの出力値例OT1、OT2、及び、Logicテスター10が生成するテスター情報L1の一例を表す図である。同図の上部には、2つのテストパターンTP1、TP2にそれぞれ基づく出力値例OT1、OT2が例示されている。同図の出力値例において、Lは良判定を示す出力値、Hは不良判定を示す出力値、−は無効な出力値を表す。

【0035】

図2のテストパターンTP1で前述したとおり、テストパターンTP1ではパターンアドレス1001〜1004の各タイミングに対応するCPU機能ブロックC1〜C4の良否判定値が出力される。同図の出力値例OT1によると、パターンアドレス1002のタイミングに不良を示す良否判定値が出力される。このため、テストパターンTP1に基づく試験結果はFailと判定され、図4の下図のような、出力端子情報SOと不良パターンアドレス1002を有するテスター情報L1が出力される。

【0036】

続いて、Logicテスター10の不良回路特定部12は、テスター情報L1の不良パターンアドレス1002に基づいて、不良判定を示す良否判定値が試験結果として出力されたCPU機能ブロックC1〜C4を特定する。ただし、不良回路特定部12は、不良パターンアドレスだけでは、不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックを特定することができない。この点について説明する。

【0037】

例えば、図4におけるテストパターンTP2の出力値例OT2によると、パターンアドレス1505〜1508のタイミングに、各CPU機能ブロックC1〜C4の良否判定値が出力される。具体的に、パターンアドレス1505のタイミングにCPU機能ブロックC1、パターンアドレス1506のタイミングにCPU機能ブロックC2の試験結果を表す良否判定値が出力される。パターンアドレス1507、1508についても同様である。

【0038】

なお、図4の出力値例OT2によると、パターンアドレス1505〜1508のタイミングに出力される良否判定値は全て良判定を示す。このため、テストパターンTP2に基づく試験結果はPassとなり、テスター情報は生成されない。

【0039】

このように、テストパターンTP1、TP2によって、各CPU機能ブロックC1〜C4の良否判定値が出力されるタイミングに対応するパターンアドレスは異なる。つまり、パターンアドレス1002のタイミングに良否判定値が出力されるCPU機能ブロックは、テストパターンTP1、TP2によって異なる。このため、不良回路特定部12は、不良パターンアドレスから、当該不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックを一意に特定できない。そこで、不良回路特定部12は、次に例示する対応表をテストパターン毎に参照して、不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックC1〜C4を特定する。

【0040】

図5は、パターンアドレスと、当該パターンアドレスのタイミングに出力される良否判定値に対応するCPU機能ブロックC1〜C4との対応関係を表す表TBの一例である。同図のように、対応表TBは、テストパターンTP1、TP2毎に、パターンアドレスと、当該パターンアドレスに対応するCPU機能ブロックC1〜C4との対応関係を有する。不良回路特定部12は、同図の対応表TBを参照して、テストパターンTP1の場合、不良パターンアドレス1002に基づいて、不良パターンアドレス1002のタイミングに良否判定値が出力されるCPU機能ブロック「C2」を特定する。

【0041】

しかしながら、この特定処理において、不良パターンアドレスに基づいて図5の対応表TBの参照することによって、Logicテスター10の稼働環境におけるCPU負荷が増大すると共に、CPUチップ20の試験に要する時間が長くなる。また、ユーザーは、テストパターンTP毎に、図5のような対応表TBを用意しておく必要があり、効率的ではない。

【0042】

そこで、本実施の形態例における半導体回路(CPUチップ20)は、複数の被試験回路(CPU機能ブロック)と、試験回路に対応して設けられた複数の第1のラッチ回路(スキャンラッチ)と、第2のラッチ回路(サマリーラッチ)と、接続経路と、複数の内部試験回路(BIST回路)と、総合判定回路CEとを有する。

【0043】

また、接続経路は、複数の第1のラッチ回路と第2のラッチ回路とを第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する。そして、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

【0044】

内部試験回路は、複数の被試験回路それぞれに設けられ、パターンアドレスに対応して入力信号が規定されたテストパターンTPのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する。また、内部試験回路が第1のラッチ回路に良否判定値を出力する時、総合判定回路CEは、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する。

【0045】

そして、出力値に不良判定を示す値がある場合、初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、不良判定を示す良否判定値を出力した内部試験回路が特定される。

【0046】

これにより、半導体回路の試験結果がFailの場合、各被試験回路の試験結果を表す良否判定値が出力される前に、半導体回路全体の試験結果が不良であることを表す総合良否判定値が、半導体回路から出力される。また、不良判定を示す良否判定値に対応する不良パターンアドレスに加えて、不良判定を示す総合良否判定値に対応する不良パターンアドレスが出力されることにより、両不良パターンアドレスの差分値に基づいて不良判定を示す良否判定値が出力される被試験回路が容易に特定される。

【0047】

図6は、本実施の形態例におけるCPUチップ20と、Logicテスター10の一例を表す図である。図1のCPUチップ20と同様にして、本実施の形態例におけるCPUチップ20は、被試験回路である4つのCPU機能ブロックC1〜C4を搭載すると共に、各CPU機能ブロックにはBIST回路B1〜B4がそれぞれ備えられる。そして、本実施の形態例におけるCPUチップ20は、BIST回路から出力される良否判定結果を保持するスキャンラッチR1〜R4に加えて、総合良否判定結果値を出力する総合判定回路CEと、当該総合良否判定結果値を保持するサマリーラッチRSを有する。

【0048】

総合判定回路CEは、被試験回路の良否判定値が全て良判定を示す値である場合は良判定を示す値を、ひとつでも不良判定を示す値がある場合は不良判定を示す値を総合良否判定結果値としてサマリーラッチRSに出力する。図6において、総合判定回路CEは、全てのBIST回路B1〜B4から出力された良否判定値の論理和演算結果をサマリーラッチRSに出力する。これにより、各BIST回路から出力された良否判定値が全て良判定を示すL値である場合にはL値が、ひとつでも不良判定を示すH値がある場合はH値が、サマリーラッチRSに出力される。つまり、いずれかのCPU機能ブロックC1〜C4の試験結果が不良判定を示すH値だった場合、対応するスキャンラッチR1〜R4に加えて、サマリーラッチRSにもH値が保持される。

【0049】

なお、総合判定回路CEはこの例に限定されるものではない。例えば、良判定を示す値がH値、不良判定を示す値がL値の場合、総合判定回路CEは入力信号の論理積演算値をサマリーラッチRSに出力する。これにより、入力された良否判定値が全て良判定を示すH値である場合にはH値が、ひとつでも不良判定を示すL値がある場合はL値が、サマリーラッチRSに出力される。

【0050】

また、図6の本実施の形態例のCPUチップ20において、出力端子SOに近いほうから、サマリーラッチRS、CPU機能ブロックC1に対応するスキャンラッチR1、CPU機能ブロックC2に対応するスキャンラッチR2、CPU機能ブロックC3に対応するスキャンラッチR3、CPU機能ブロックC4に対応するスキャンラッチR4の順に配置される。このため、スキャンチェーンによる各ラッチの値の出力時、サマリーラッチRSに保持された値が最初に出力される。

【0051】

本実施の形態例におけるCPUチップ20の試験の流れは、図3のフローチャート図と同様である。ただし、本実施の形態例では、テスター情報の内容と、不良パターンアドレスに基づく不良のCPU機能ブロックC1〜C4の特定処理(S18)の内容について相違する。続いて、その相違について述べる。なお、本実施の形態例において、テストパターンTPに規定された総合良否判定値(出力値)に対応する期待値は、良判定を示すL値であるものする。

【0052】

図3のフローチャート図で前述したとおり、出力信号が期待値と一致しない場合(S13のNO)、Logicテスター10は、出力端子情報と不良パターンアドレスとを出力する(S14)。本実施の形態例において、CPUチップ20からは、初めに、サマリーラッチRSに保持された総合良否判定値が出力される。そのため、本実施の形態例では、試験結果がFailの場合、総合良否判定値が出力されたタイミングのパターンアドレスと、各CPU機能ブロックに対応する良否判定値であって不良判定を示す良否判定値が出力されたタイミングのパターンアドレスとが不良パターンアドレスとして出力される。

【0053】

図7は、本実施の形態例におけるCPUチップ20からの出力値例OT11、OT12、及び、Logicテスター10が生成するテスター情報L11の一例を表す図である。同図のテストパターン1出力値例OT11のように、本実施の形態例では、パターンアドレス1000〜1004のタイミングに有効な出力値が出力されるものとする。具体的に、パターンアドレス1000のタイミングには総合良否判定値が、パターンアドレス1001〜1004のタイミングには、各CPU機能ブロックC1〜C4の試験結果を表す良否判定値が順番に出力される。

【0054】

図7の出力値例OT11では、パターンアドレス1000、1002のタイミングに不良を示す良否判定値(H値)が出力される。そこで、本実施の形態例におけるLogicテスター10は、図7の下図のように、出力端子情報SOと不良パターンアドレス1000、1002を有するテスター情報L11を出力する。ここで、初めに出力された不良パターンアドレス1000は、サマリーラッチRSに保持された総合良否判定値が出力されたタイミングのパターンアドレス(以下、サマリー不良パターンアドレス)であり、続く不良パターンアドレス1002は、スキャンラッチR1〜R4に保持され、不良判定を示す良否判定値が出力されたタイミングのパターンアドレス(以下、個別不良パターンアドレス)である。

【0055】

本実施の形態例におけるLogicテスター10の不良回路特定部12は、サマリー不良パターンアドレスと、個別不良パターンアドレスとの差分値に基づいて、個別不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックを特定する。続いて、その方法について説明する。

【0056】

前述したとおり、本実施の形態例におけるスキャンチェーン(図6)では、出力端子SOに近いほうから、サマリーラッチRS、CPU機能ブロックC1〜C4に対応するそれぞれのスキャンラッチR1〜R4が配置される。そのため、常に、サマリーラッチRS、スキャンラッチR1、スキャンラッチR2、スキャンラッチR3、スキャンラッチR4の順に、保持された値が出力される。このため、サマリーラッチRSに保持された値が出力されるタイミングのパターンアドレスと、特定のスキャンラッチR1〜R4に保持された値が出力されるタイミングのパターンアドレスとの差分値は、いずれのテストパターンにおいても同じである。

【0057】

図8は、サマリー不良パターンアドレスと個別不良パターンアドレスとの差分値と、個別不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックとの対応関係を表す図80である。このように、パターンアドレスの差分値(同図の例では、1〜4)と、個別不良パターンアドレスに対応するCPU機能ブロックとの対応関係は、テストパターンTP1、TP2共に同じである。つまり、個別不良パターンアドレスに対応するCPU機能ブロックC1〜C4は、パターンアドレスの差分値に基づいてテストパターンにかかわらず一意に特定される。

【0058】

そこで、不良回路特定部12は、サマリー不良パターンアドレスと個別不良パターンアドレスの差分値(図8の例では、1〜4)に基づいて、個別不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックC1〜C4を特定する。例えば、図7の出力値例OT11において、Logicテスター10は、サマリー不良パターンアドレス1000と個別不良パターンアドレス1002との差分値「2」に基づいて、不良のCPU機能ブロック「C2」を特定する。

【0059】

また、図7のテストパターン2の出力値例OT12では、パターンアドレス1504、1506のタイミングに不良判定を示す値が出力される。この場合についても、同様にして、Logicテスター10は、サマリー不良パターンアドレス1504と個別不良パターンアドレス1506との差分値「2」に基づいて、不良のCPU機能ブロック「C2」を特定することができる。

【0060】

このように、本実施の形態例におけるCPUチップ20の試験において、試験結果がFailの場合、個別不良パターンアドレスに加えて、サマリー不良パターンアドレスが合わせて出力される。これにより、個別不良パターンアドレスとサマリー不良パターンアドレスの差分値に基づいて、個別不良パターンアドレスに対応するCPU機能ブロックが容易に特定される。

【0061】

なお、図7では、4つのCPU機能ブロックC1〜C4のうちひとつのCPU機能ブロックについて不良判定を示す良否判定値が出力される場合を例示したが、これに限定されるものではない。複数のCPU機能ブロックC1〜C4について不良判定を示す良否判定値が出力される場合についても同様である。この場合、サマリー不良パターンアドレスと、複数の個別不良パターンアドレスとそれぞれの差分値に基づいて、不良のCPU機能ブロックが複数特定される。

【0062】

このように、本実施の形態例における半導体回路は、複数の被試験回路と、試験回路に対応して設けられた複数のスキャンラッチ(第1のラッチ回路)と、サマリーラッチ(第2のラッチ回路)と、サマリーラッチに保持された値が最初に出力されるように複数のスキャンラッチとサマリーラッチとを接続しスキャンチェーンを構成する接続経路と、複数の内部試験回路と、総合判定回路CEとを有する。

【0063】

内部試験回路は、複数の被試験回路それぞれに設けられ、テストパターンTPのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値をスキャンラッチにそれぞれ出力する。この時、総合判定回路CEは、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値をサマリーラッチに出力する。そして、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、各ラッチに保持された良否判定値を順番に出力値として出力する。

【0064】

これにより、スキャンチェーンからの出力値に期待値と異なる(不良判定を示す良否判定値)がある場合、即ち、半導体回路の試験結果がFailの場合、各被試験回路の試験結果を表す良否判定値が出力される前に、半導体回路の試験結果が不良であることを表す良否判定値が出力される。これにより、初めに出力された良否判定値に基づいて、半導体回路の試験結果が不良であることが検知される。

【0065】

また、本実施の形態例における半導体回路において、スキャンチェーンからの出力値に不良判定を示す値がある場合、初めに出力された不良判定値に対応するパターンアドレス(サマリー不良パターンアドレス)と、2つ目以降に出力された不良判定値に対応するパターンアドレス(個別不良パターンアドレス)との差分値に基づいて、不良判定を示す良否判定値を出力した内部試験回路が特定される。

【0066】

つまり、スキャンチェーンからの出力値に不良判定を示す値がある場合(試験結果がFailの場合)、サマリーラッチRSに保持された総合良否判定値が出力されるタイミングのパターンアドレス(サマリー不良パターンアドレス)に続いて、スキャンラッチR1〜R4に保持され不良判定を示す良否判定値が出力されるタイミングのパターンアドレス(個別不良パターンアドレス)が出力される。サマリー不良パターンアドレスと個別不良パターンアドレスとの差分値と、当該個別不良パターンアドレスに対応する被試験回路との対応関係は、いずれのテストパターンにおいても同じである。従って、差分値に基づいて個別不良パターンアドレスに対応する被試験回路が容易に特定される。

【0067】

また、これにより、本実施の形態例における半導体回路は、パターンアドレスと当該パターンアドレスのタイミングに出力される良否判定値に対応する被試験回路との対応関係を表す対応表(図5)を不要にする。また、差分値に基づく不良の被試験回路の特定処理では、対応表の参照が不要であることから、CPU負荷が抑えられ試験に係る時間も短縮される。このため、本実施の形態例における半導体回路は、被試験回路やテストパターンTPの数が多量である場合でも、サマリー不良パターンアドレスと個別不良パターンアドレスの差分値に基づいて不良の被試験回路が特定可能であることにより、効率的な試験を実現可能にする。

【0068】

以上の実施の形態をまとめると、次の付記のとおりである。

【0069】

(付記1)

複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、パターンアドレスに対応して入力信号が規定されたテストパターンの前記パターンアドレス順に入力される前記入力信号に基づいて、前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する半導体回路。

【0070】

(付記2)

付記1において、

前記出力値に前記不良判定を示す値がある場合、初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、前記不良判定を示す良否判定値を出力した前記内部試験回路が特定される半導体回路。

【0071】

(付記3)

付記2において、

前記第1のパターンアドレスは、前記初めに出力された不良判定値が出力されたタイミングのパターンアドレスであり、

前記第2のパターンアドレスは、前記2つ目以降に出力された不良判定値が出力されたタイミングのパターンアドレスである半導体回路。

【0072】

(付記4)

付記1において、

前記スキャン出力モードを示す前記入力信号は、所定のパターンアドレス以降のパターンアドレスに対応するタイミングに入力される半導体回路。

【0073】

(付記5)

付記4において、

前記所定のパターンアドレスは、前記テストパターンによって異なる半導体回路。

【0074】

(付記6)

複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、入力信号に基づいて前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する半導体回路のテスト方法であって、

パターンアドレスに対応して前記入力信号が規定されたテストパターンの前記パターンアドレス順に、前記入力信号を前記半導体回路に入力し、当該入力信号に基づいて前記半導体回路から出力される出力値を順番に取得し、前記出力値に前記不良判定を示す値がある場合、不良判定値が出力されたタイミングのパターンアドレスを出力する不良パターンアドレス出力工程と、

初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、前記不良判定を示す良否判定値を出力した前記内部試験回路を特定する不良回路特定工程と、を有するテスト方法。

【符号の説明】

【0075】

10:Logicテスター、20:半導体回路、C1〜C4:CPU機能ブロック、B1〜B4:BIST回路、CE:総合判定回路、R1〜R4:スキャンラッチ、RS:サマリーラッチ

【技術分野】

【0001】

本発明は、半導体回路、及びテスト方法に関する。

【背景技術】

【0002】

近年のLSI(Large Scale Integration)の高集積化に伴い、ハイエンドのCPUチップには数十個のCPU機能ブロックが搭載される。また、CPU(Central Processing Unit)チップに搭載された各CPU機能ブロックは、それぞれ独立して動作する。このようなCPUチップを使用するシステムでは、一部のCPU機能ブロックを使用しないことにより、システムランクに差異をつける。そこで、全ての機能ブロックが正常に動作する完全良否のCPUチップに加えて、不良のCPU機能ブロックを一部有する部分良否のCPUチップも利用される。

【0003】

CPU機能ブロックの試験は、Logicテスター(ATE:Automated Test Equipment)によって実施される。試験の結果、例えば、4つのCPU機能ブロックを備えるCPUチップについて、1つのCPU機能ブロックが正常に動作しなかった場合、当該CPUチップは3つのCPU機能ブロックのみを有する3Core品とランク判定される。

【0004】

各CPU機能ブロックは、それぞれBIST(built-in self test)回路を有する。そして、Logicテスターは、パターンアドレスに対応して入力信号が規定されたテストパターンに基づいて、CPUチップから各CPU機能ブロックの動作試験の結果を示す良否判定値を出力させる。具体的に、テストパターンに基づいて、BIST回路にCPU機能ブロックの動作試験が指示されると共に、その試験結果を示す良否判定値がスキャンラッチに出力され、スキャンラッチに保持された良否判定値がスキャンチェーンによって順次出力される。

【0005】

続いて、Logicテスターは、例えば、スキャンチェーンから出力された良否判定値と良判定を示す期待値とを順次比較し、全て一致する場合は試験結果をPass、一致しない良否判定値(不良判定)がある場合は試験結果をFailとする。また、Failの場合、Logicテスターは、不良判定を示す良否判定値が出力されたタイミングに対応するパターンアドレスを、不良パターンアドレスとして出力する。そして、Logicテスターは、不良パターンアドレスに基づいて、正常に動作しないCPU機能ブロックを特定する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−122009号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、テストパターンによって、試験の内容が異なる。そのため、各CPU機能ブロックの良否判定値が出力されるタイミングのパターンアドレス(不良パターンアドレス)もテストパターンによって異なる。これにより、Logicテスターは、不良パターンアドレスだけでは、不良判定を示す良否判定値が試験結果として出力されたCPU機能ブロックを特定することができない。

【0008】

そこで、本発明では、スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する半導体回路及びテスト方法を提供することにある。

【課題を解決するための手段】

【0009】

第1の側面は、複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、パターンアドレスに対応して入力信号が規定されたテストパターンの前記パターンアドレス順に入力される前記入力信号に基づいて、前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

【発明の効果】

【0010】

第1の側面によれば、スキャンチェーンから出力される複数の被試験回路の試験結果情報に基づいて、不良の被試験回路を効率的に特定する。

【図面の簡単な説明】

【0011】

【図1】CPUチップとLogicテスターを表す例図である。

【図2】テストパターンの一例を表す図である。

【図3】Logicテスターの試験処理の流れを表すフローチャート図である。

【図4】CPUチップからの出力値例とテスター情報の一例を表す図である。

【図5】パターンアドレスと、当該パターンアドレスのタイミングに出力される良否判定値に対応するCPU機能ブロックとの関係を表す対応表の一例である。

【図6】本実施の形態例におけるCPUチップとLogicテスターを表す例図である。

【図7】本実施の形態例のCPUチップからの出力値例とテスター情報を表す例図である。

【図8】アドレス差分値と差分値に対応するCPU機能ブロックとの関係を表す図である。

【発明を実施するための形態】

【0012】

以下、図面にしたがって本発明の実施の形態について説明する。ただし、本発明の技術的範囲はこれらの実施の形態に限定されず、特許請求の範囲に記載された事項とその均等物まで及ぶものである。

【0013】

図1は、CPUチップ20とLogicテスター10の一例を表す図である。同図のCPUチップ20は、被試験回路である4つのCPU機能ブロックC1〜C4を搭載し、正常に動作するCPU機能ブロックC1〜C4の数に基づいてその製品ランクが判定される。各CPU機能ブロックC1〜C4にはそれぞれBIST回路B1〜B4が備えられる。また、CPUチップ20は、CPU機能ブロックC1〜C4に対応するスキャンラッチR1〜R4を有する。

【0014】

BIST回路B1〜B4は、例えば、入力信号に基づいて、試験動作用の信号をCPU機能ブロックC1〜C4に入力すると共に、CPU機能ブロックC1〜C4から動作結果の信号を取得して試験の動作結果を示す良否判定値をスキャンラッチR1〜R4に出力する。各スキャンラッチR1〜R4はスキャンチェーンを構成し、各スキャンラッチR1〜R4に保持された良否判定値はスキャンチェーンによって出力端子SOから順番に出力される。

【0015】

図1のCPUチップ20では、出力端子SOに近い順に、CPU機能ブロックC1に対応するスキャンラッチR1から、CPU機能ブロックC4に対応するスキャンラッチR4まで順番に配置されている。そのため、スキャンチェーンは、スキャンラッチR1、R2、R3、R4の順番に、保持する良否判定値をシフトレジスタ動作によって出力する。

【0016】

このように、図1のCPUチップ20では、各BIST回路B1〜B4からの出力された良否判定値を保持させたスキャンラッチR1〜R4でスキャンチェーンを構成し、各良否判定値をひとつの出力端子SOから出力させる。これにより、CPUチップ20はBIST回路B1〜B4毎に出力端子を備える必要がなく、試験用の出力端子の数を最小限に抑えることができる。

【0017】

続いて、図1のLogicテスター10は、試験制御部11と不良回路特定部12とを有する。Logicテスター10は、テストパターンTPに基づいてCPUチップ20の試験を行う。テストパターンTPには、パターンアドレス順に、各パターンアドレスに対応して入力信号が規定される。試験制御部11は、クロック信号に同期して、テストパターンTPのパターンアドレス順に、対応する入力信号をCPUチップ20の入力端子SIに入力する。そして、CPUチップ20において入力信号に基づいて一連の試験処理が行われる。

【0018】

CPUチップ20において、例えば、次のような処理が行われる。BIST回路B1〜B4は、リセット処理及び初期化設定処理の後、CPU機能ブロックC1〜C4の試験動作の制御を行う。具体的に、BIST回路B1〜B4は、入力信号に基づく試験動作をCPU機能ブロックC1〜C4に指示する。そして、BIST回路B1〜B4は、CPU機能ブロックC1〜C4の試験動作が終了すると、その結果情報を取得して良否判定を行い、その良否判定値を対応するスキャンラッチR1〜R4に出力する。そして、スキャンチェーンは、スキャンラッチR1〜R4に保持された良否判定値を順次出力する。

【0019】

CPUチップ20における一連の試験処理の後、続いて、試験制御部11は、CPUチップ20から出力された各CPU機能ブロックC1〜C4の試験動作結果を表す良否判定値と期待値とを比較し、CPUチップ20の試験結果(Pass/Fail)を判定する。この例において、期待値は、良判定を示す良否判定値であるものとする。このため、各良否判定値が全て良判定を示す良否判定値の場合の試験結果はPass、ひとつでも否判定を示す良否判定値の場合の試験結果はFailと判定される。試験結果がFailの場合、試験制御部11は、否判定を示す良否判定値が出力されたタイミングに対応するパターンアドレス(不良パターンアドレス)を、テスター情報として出力する。

【0020】

続いて、Logicテスター10の不良回路特定部12は、試験結果がFailの場合、テスター情報として出力された不良パターンアドレスに基づいて、当該不良パターンアドレスのタイミングに出力された良否判定値に対応するCPU機能ブロックC1〜C4を特定する。Logicテスター10における各処理の詳細については、後述する。

【0021】

図2は、テストパターンTPの一例を表す図である。テストパターンTPにおいて、入力信号に基づいて、CPUチップ10の一連の試験動作が規定される。一連の試験動作とは、前述したとおり、例えば、BIST回路B1〜B4のリセット処理T1及び初期化処理T2、BIST回路B1〜B4によるCPU機能ブロックC1〜C4の試験動作の制御処理T3、スキャンラッチへの各良否判定値の出力処理T4、スキャンチェーンによる各良否判定値の出力処理T5である。

【0022】

また、テストパターンTPには、パターンアドレスに対応して1〜n個の入力信号が規定される。入力信号とは、例えば、BIST回路B1〜B4の試験動作の内容を指示する信号や、試験動作で使用される信号、スキャンチェーンに保持された各良否判定値の出力を指示する信号等である。また、一般的に、試験対象の半導体回路に対して、多数のテストパターンTPが用意される。

【0023】

また、図2のテストパターンTPでは、例えば、パターンアドレスに対応して、出力値に加えて出力信号の期待値EXが規定される。同図における期待値EXとは、パターンアドレスに対応する入力信号が入力されたタイミングに、出力端子SO(図1)から出力される出力信号の期待値である。本実施の形態例では、出力信号の期待値EXとして、例えば、H値、L値、無効な出力値を示す×が規定される。H値は不良判定を示す良否判定値であり、L値は良判定を示す良否判定値である。

【0024】

具体的に、図2に例示したテストパターン1の例TP1では、パターンアドレス1000のタイミングまでは、出力値の期待値に×が規定されている。一方、パターンアドレス1001〜1004に対応する出力値の期待値には、良判定を示すL値が規定されている。これは、パターンアドレス1001〜1004のタイミングに各CPU機能ブロックC1〜C4の良否判定値が出力されることを示す。また、CPU機能ブロックC1〜C4の試験結果を示す良否判定値が全てL値である場合に試験結果がPass、いずれかの良否判定値がH値である場合に試験結果がFailとなることを示す。

【0025】

また、図1で前述したとおり、スキャンチェーンは、CPU機能ブロックC1からCPU機能ブロックC4にかけて対応する良否判定値を順に出力する。そのため、パターンアドレス1001のタイミングで出力される出力値は、出力端子SOに最も近いスキャンラッチR1に保持されるCPU機能ブロックC1の良否判定値を示す。そして、パターンアドレス1002のタイミングで出力される出力値は、次に出力端子SOに近いスキャンラッチR2に保持されるCPU機能ブロックC2の良否判定値を示す。同様に、パターンアドレス1003のタイミングで出力される出力値はCPU機能ブロックC3の良否判定値、パターンアドレス1004のタイミングで出力される出力値はCPU機能ブロックC4の良否判定値を示す。

【0026】

続いて、Logicテスター10によるCPUチップ20の試験処理の流れについて、フローチャート図に基づいて説明する。

【0027】

図3は、Logicテスター10の試験処理の流れを表すフローチャート図である。本実施の形態例では、初めに、処理対象のパターンアドレスが0に初期化される(S10)。そして、Logicテスター10は、テストパターンTPのパターンアドレス順に、パターンアドレスに対応する入力信号をCPUチップ20に入力する(S11)。そして、Logicテスター10は、テストパターンTPにおいて規定された、パターンアドレスに対応する出力信号の期待値が無効(本実施の形態例では×)であるか否かをチェックする(S12)。

【0028】

パターンアドレスに対応する出力信号の期待値が無効の場合(S12のYES)、Logicテスター10は、処理S15に遷移し、パターンアドレスがテストパターンTPにおける最後のパターンアドレスに達したか否かを判定する(S15)。最後のパターンアドレスに達していない場合(S15のNO)、Logicテスター10は、パターンアドレスをインクリメントして(S16)、引き続き、インクリメントしたパターンアドレスに対応する入力信号をCPUチップ20に入力する(S11)。一般的に、各CPU機能ブロックC1〜C4の良否判定値が各スキャンラッチR1〜R4に保持されるタイミングに対応する所定のパターンアドレスまでは、出力信号の期待値は無効(S12のYES)に設定され、パターンアドレスが順次インクリメントされCPUチップ20の試験処理が進められる。

【0029】

一方、パターンアドレスに対応する出力信号の期待値が無効ではない場合(S12のNO)、Logicテスター10は、CPUチップ20から出力された出力値とテストパターンTPに規定されたパターンアドレスに対応する期待値とが一致するか否かを判定する(S13)。一致しない場合(S13のNO)、Logicテスター10は、テスター情報として、期待値と一致しない出力値が出力されたタイミングのパターンアドレス(不良パターンアドレス)と、出力端子情報(本実施の形態例では、必ず出力端子SO)とを出力する(S14)。一方、CPUチップ20から出力された出力値とテストパターンTPに規定されたパターンアドレスに対応する期待値とが一致する場合(S13のYES)、何も出力しない。

【0030】

S13の処理の後、Logicテスター10は、パターンアドレスがテストパターンTPにおける最後のパターンアドレスに達したか否かを判定し(S15)、達していない場合(S15のNO)、パターンアドレスをインクリメントして(S16)、処理S11に戻る。

【0031】

最終的に、パターンアドレスがテストパターンTPの最後に達すると(S15のYES)、Logicテスター10は、テストパターンTPに基づくCPUチップ20の試験結果がPassであるかFailであるかを判定する(S17)。テストパターンTPに基づくCPUチップ20の試験結果がFailの場合(S17のYES)、即ち、期待値と一致しない出力値が出力された場合、続いて、Logicテスター10は、テスター情報に基づいて不良のCPU機能ブロックを特定する(S18)。

【0032】

不良のCPU機能ブロックが特定された場合(S18)、または、試験結果がPassの場合(S17のNO)、Logicテスター10は、一連の試験処理を終了する。そして、Logicテスター10は、別のテストパターンTPに基づいてCPUチップ20の試験を実施する。

【0033】

続いて、図3のフローチャート図におけるテスター情報に基づく不良のCPU機能ブロックの特定処理(S18)について具体的に説明する。

【0034】

図4は、CPUチップ20からの出力値例OT1、OT2、及び、Logicテスター10が生成するテスター情報L1の一例を表す図である。同図の上部には、2つのテストパターンTP1、TP2にそれぞれ基づく出力値例OT1、OT2が例示されている。同図の出力値例において、Lは良判定を示す出力値、Hは不良判定を示す出力値、−は無効な出力値を表す。

【0035】

図2のテストパターンTP1で前述したとおり、テストパターンTP1ではパターンアドレス1001〜1004の各タイミングに対応するCPU機能ブロックC1〜C4の良否判定値が出力される。同図の出力値例OT1によると、パターンアドレス1002のタイミングに不良を示す良否判定値が出力される。このため、テストパターンTP1に基づく試験結果はFailと判定され、図4の下図のような、出力端子情報SOと不良パターンアドレス1002を有するテスター情報L1が出力される。

【0036】

続いて、Logicテスター10の不良回路特定部12は、テスター情報L1の不良パターンアドレス1002に基づいて、不良判定を示す良否判定値が試験結果として出力されたCPU機能ブロックC1〜C4を特定する。ただし、不良回路特定部12は、不良パターンアドレスだけでは、不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックを特定することができない。この点について説明する。

【0037】

例えば、図4におけるテストパターンTP2の出力値例OT2によると、パターンアドレス1505〜1508のタイミングに、各CPU機能ブロックC1〜C4の良否判定値が出力される。具体的に、パターンアドレス1505のタイミングにCPU機能ブロックC1、パターンアドレス1506のタイミングにCPU機能ブロックC2の試験結果を表す良否判定値が出力される。パターンアドレス1507、1508についても同様である。

【0038】

なお、図4の出力値例OT2によると、パターンアドレス1505〜1508のタイミングに出力される良否判定値は全て良判定を示す。このため、テストパターンTP2に基づく試験結果はPassとなり、テスター情報は生成されない。

【0039】

このように、テストパターンTP1、TP2によって、各CPU機能ブロックC1〜C4の良否判定値が出力されるタイミングに対応するパターンアドレスは異なる。つまり、パターンアドレス1002のタイミングに良否判定値が出力されるCPU機能ブロックは、テストパターンTP1、TP2によって異なる。このため、不良回路特定部12は、不良パターンアドレスから、当該不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックを一意に特定できない。そこで、不良回路特定部12は、次に例示する対応表をテストパターン毎に参照して、不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックC1〜C4を特定する。

【0040】

図5は、パターンアドレスと、当該パターンアドレスのタイミングに出力される良否判定値に対応するCPU機能ブロックC1〜C4との対応関係を表す表TBの一例である。同図のように、対応表TBは、テストパターンTP1、TP2毎に、パターンアドレスと、当該パターンアドレスに対応するCPU機能ブロックC1〜C4との対応関係を有する。不良回路特定部12は、同図の対応表TBを参照して、テストパターンTP1の場合、不良パターンアドレス1002に基づいて、不良パターンアドレス1002のタイミングに良否判定値が出力されるCPU機能ブロック「C2」を特定する。

【0041】

しかしながら、この特定処理において、不良パターンアドレスに基づいて図5の対応表TBの参照することによって、Logicテスター10の稼働環境におけるCPU負荷が増大すると共に、CPUチップ20の試験に要する時間が長くなる。また、ユーザーは、テストパターンTP毎に、図5のような対応表TBを用意しておく必要があり、効率的ではない。

【0042】

そこで、本実施の形態例における半導体回路(CPUチップ20)は、複数の被試験回路(CPU機能ブロック)と、試験回路に対応して設けられた複数の第1のラッチ回路(スキャンラッチ)と、第2のラッチ回路(サマリーラッチ)と、接続経路と、複数の内部試験回路(BIST回路)と、総合判定回路CEとを有する。

【0043】

また、接続経路は、複数の第1のラッチ回路と第2のラッチ回路とを第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する。そして、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する。

【0044】

内部試験回路は、複数の被試験回路それぞれに設けられ、パターンアドレスに対応して入力信号が規定されたテストパターンTPのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を第1のラッチ回路にそれぞれ出力する。また、内部試験回路が第1のラッチ回路に良否判定値を出力する時、総合判定回路CEは、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を第2のラッチ回路に出力する。

【0045】

そして、出力値に不良判定を示す値がある場合、初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、不良判定を示す良否判定値を出力した内部試験回路が特定される。

【0046】

これにより、半導体回路の試験結果がFailの場合、各被試験回路の試験結果を表す良否判定値が出力される前に、半導体回路全体の試験結果が不良であることを表す総合良否判定値が、半導体回路から出力される。また、不良判定を示す良否判定値に対応する不良パターンアドレスに加えて、不良判定を示す総合良否判定値に対応する不良パターンアドレスが出力されることにより、両不良パターンアドレスの差分値に基づいて不良判定を示す良否判定値が出力される被試験回路が容易に特定される。

【0047】

図6は、本実施の形態例におけるCPUチップ20と、Logicテスター10の一例を表す図である。図1のCPUチップ20と同様にして、本実施の形態例におけるCPUチップ20は、被試験回路である4つのCPU機能ブロックC1〜C4を搭載すると共に、各CPU機能ブロックにはBIST回路B1〜B4がそれぞれ備えられる。そして、本実施の形態例におけるCPUチップ20は、BIST回路から出力される良否判定結果を保持するスキャンラッチR1〜R4に加えて、総合良否判定結果値を出力する総合判定回路CEと、当該総合良否判定結果値を保持するサマリーラッチRSを有する。

【0048】

総合判定回路CEは、被試験回路の良否判定値が全て良判定を示す値である場合は良判定を示す値を、ひとつでも不良判定を示す値がある場合は不良判定を示す値を総合良否判定結果値としてサマリーラッチRSに出力する。図6において、総合判定回路CEは、全てのBIST回路B1〜B4から出力された良否判定値の論理和演算結果をサマリーラッチRSに出力する。これにより、各BIST回路から出力された良否判定値が全て良判定を示すL値である場合にはL値が、ひとつでも不良判定を示すH値がある場合はH値が、サマリーラッチRSに出力される。つまり、いずれかのCPU機能ブロックC1〜C4の試験結果が不良判定を示すH値だった場合、対応するスキャンラッチR1〜R4に加えて、サマリーラッチRSにもH値が保持される。

【0049】

なお、総合判定回路CEはこの例に限定されるものではない。例えば、良判定を示す値がH値、不良判定を示す値がL値の場合、総合判定回路CEは入力信号の論理積演算値をサマリーラッチRSに出力する。これにより、入力された良否判定値が全て良判定を示すH値である場合にはH値が、ひとつでも不良判定を示すL値がある場合はL値が、サマリーラッチRSに出力される。

【0050】

また、図6の本実施の形態例のCPUチップ20において、出力端子SOに近いほうから、サマリーラッチRS、CPU機能ブロックC1に対応するスキャンラッチR1、CPU機能ブロックC2に対応するスキャンラッチR2、CPU機能ブロックC3に対応するスキャンラッチR3、CPU機能ブロックC4に対応するスキャンラッチR4の順に配置される。このため、スキャンチェーンによる各ラッチの値の出力時、サマリーラッチRSに保持された値が最初に出力される。

【0051】

本実施の形態例におけるCPUチップ20の試験の流れは、図3のフローチャート図と同様である。ただし、本実施の形態例では、テスター情報の内容と、不良パターンアドレスに基づく不良のCPU機能ブロックC1〜C4の特定処理(S18)の内容について相違する。続いて、その相違について述べる。なお、本実施の形態例において、テストパターンTPに規定された総合良否判定値(出力値)に対応する期待値は、良判定を示すL値であるものする。

【0052】

図3のフローチャート図で前述したとおり、出力信号が期待値と一致しない場合(S13のNO)、Logicテスター10は、出力端子情報と不良パターンアドレスとを出力する(S14)。本実施の形態例において、CPUチップ20からは、初めに、サマリーラッチRSに保持された総合良否判定値が出力される。そのため、本実施の形態例では、試験結果がFailの場合、総合良否判定値が出力されたタイミングのパターンアドレスと、各CPU機能ブロックに対応する良否判定値であって不良判定を示す良否判定値が出力されたタイミングのパターンアドレスとが不良パターンアドレスとして出力される。

【0053】

図7は、本実施の形態例におけるCPUチップ20からの出力値例OT11、OT12、及び、Logicテスター10が生成するテスター情報L11の一例を表す図である。同図のテストパターン1出力値例OT11のように、本実施の形態例では、パターンアドレス1000〜1004のタイミングに有効な出力値が出力されるものとする。具体的に、パターンアドレス1000のタイミングには総合良否判定値が、パターンアドレス1001〜1004のタイミングには、各CPU機能ブロックC1〜C4の試験結果を表す良否判定値が順番に出力される。

【0054】

図7の出力値例OT11では、パターンアドレス1000、1002のタイミングに不良を示す良否判定値(H値)が出力される。そこで、本実施の形態例におけるLogicテスター10は、図7の下図のように、出力端子情報SOと不良パターンアドレス1000、1002を有するテスター情報L11を出力する。ここで、初めに出力された不良パターンアドレス1000は、サマリーラッチRSに保持された総合良否判定値が出力されたタイミングのパターンアドレス(以下、サマリー不良パターンアドレス)であり、続く不良パターンアドレス1002は、スキャンラッチR1〜R4に保持され、不良判定を示す良否判定値が出力されたタイミングのパターンアドレス(以下、個別不良パターンアドレス)である。

【0055】

本実施の形態例におけるLogicテスター10の不良回路特定部12は、サマリー不良パターンアドレスと、個別不良パターンアドレスとの差分値に基づいて、個別不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックを特定する。続いて、その方法について説明する。

【0056】

前述したとおり、本実施の形態例におけるスキャンチェーン(図6)では、出力端子SOに近いほうから、サマリーラッチRS、CPU機能ブロックC1〜C4に対応するそれぞれのスキャンラッチR1〜R4が配置される。そのため、常に、サマリーラッチRS、スキャンラッチR1、スキャンラッチR2、スキャンラッチR3、スキャンラッチR4の順に、保持された値が出力される。このため、サマリーラッチRSに保持された値が出力されるタイミングのパターンアドレスと、特定のスキャンラッチR1〜R4に保持された値が出力されるタイミングのパターンアドレスとの差分値は、いずれのテストパターンにおいても同じである。

【0057】

図8は、サマリー不良パターンアドレスと個別不良パターンアドレスとの差分値と、個別不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックとの対応関係を表す図80である。このように、パターンアドレスの差分値(同図の例では、1〜4)と、個別不良パターンアドレスに対応するCPU機能ブロックとの対応関係は、テストパターンTP1、TP2共に同じである。つまり、個別不良パターンアドレスに対応するCPU機能ブロックC1〜C4は、パターンアドレスの差分値に基づいてテストパターンにかかわらず一意に特定される。

【0058】

そこで、不良回路特定部12は、サマリー不良パターンアドレスと個別不良パターンアドレスの差分値(図8の例では、1〜4)に基づいて、個別不良パターンアドレスのタイミングに良否判定値が出力されるCPU機能ブロックC1〜C4を特定する。例えば、図7の出力値例OT11において、Logicテスター10は、サマリー不良パターンアドレス1000と個別不良パターンアドレス1002との差分値「2」に基づいて、不良のCPU機能ブロック「C2」を特定する。

【0059】

また、図7のテストパターン2の出力値例OT12では、パターンアドレス1504、1506のタイミングに不良判定を示す値が出力される。この場合についても、同様にして、Logicテスター10は、サマリー不良パターンアドレス1504と個別不良パターンアドレス1506との差分値「2」に基づいて、不良のCPU機能ブロック「C2」を特定することができる。

【0060】

このように、本実施の形態例におけるCPUチップ20の試験において、試験結果がFailの場合、個別不良パターンアドレスに加えて、サマリー不良パターンアドレスが合わせて出力される。これにより、個別不良パターンアドレスとサマリー不良パターンアドレスの差分値に基づいて、個別不良パターンアドレスに対応するCPU機能ブロックが容易に特定される。

【0061】

なお、図7では、4つのCPU機能ブロックC1〜C4のうちひとつのCPU機能ブロックについて不良判定を示す良否判定値が出力される場合を例示したが、これに限定されるものではない。複数のCPU機能ブロックC1〜C4について不良判定を示す良否判定値が出力される場合についても同様である。この場合、サマリー不良パターンアドレスと、複数の個別不良パターンアドレスとそれぞれの差分値に基づいて、不良のCPU機能ブロックが複数特定される。

【0062】

このように、本実施の形態例における半導体回路は、複数の被試験回路と、試験回路に対応して設けられた複数のスキャンラッチ(第1のラッチ回路)と、サマリーラッチ(第2のラッチ回路)と、サマリーラッチに保持された値が最初に出力されるように複数のスキャンラッチとサマリーラッチとを接続しスキャンチェーンを構成する接続経路と、複数の内部試験回路と、総合判定回路CEとを有する。

【0063】

内部試験回路は、複数の被試験回路それぞれに設けられ、テストパターンTPのパターンアドレス順に入力される入力信号に基づいて、被試験回路に試験動作を実行させ、動作結果に基づく良否判定値をスキャンラッチにそれぞれ出力する。この時、総合判定回路CEは、複数の良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値をサマリーラッチに出力する。そして、スキャンチェーンは、入力信号がスキャン出力モードを示す時に、各ラッチに保持された良否判定値を順番に出力値として出力する。

【0064】

これにより、スキャンチェーンからの出力値に期待値と異なる(不良判定を示す良否判定値)がある場合、即ち、半導体回路の試験結果がFailの場合、各被試験回路の試験結果を表す良否判定値が出力される前に、半導体回路の試験結果が不良であることを表す良否判定値が出力される。これにより、初めに出力された良否判定値に基づいて、半導体回路の試験結果が不良であることが検知される。

【0065】

また、本実施の形態例における半導体回路において、スキャンチェーンからの出力値に不良判定を示す値がある場合、初めに出力された不良判定値に対応するパターンアドレス(サマリー不良パターンアドレス)と、2つ目以降に出力された不良判定値に対応するパターンアドレス(個別不良パターンアドレス)との差分値に基づいて、不良判定を示す良否判定値を出力した内部試験回路が特定される。

【0066】

つまり、スキャンチェーンからの出力値に不良判定を示す値がある場合(試験結果がFailの場合)、サマリーラッチRSに保持された総合良否判定値が出力されるタイミングのパターンアドレス(サマリー不良パターンアドレス)に続いて、スキャンラッチR1〜R4に保持され不良判定を示す良否判定値が出力されるタイミングのパターンアドレス(個別不良パターンアドレス)が出力される。サマリー不良パターンアドレスと個別不良パターンアドレスとの差分値と、当該個別不良パターンアドレスに対応する被試験回路との対応関係は、いずれのテストパターンにおいても同じである。従って、差分値に基づいて個別不良パターンアドレスに対応する被試験回路が容易に特定される。

【0067】

また、これにより、本実施の形態例における半導体回路は、パターンアドレスと当該パターンアドレスのタイミングに出力される良否判定値に対応する被試験回路との対応関係を表す対応表(図5)を不要にする。また、差分値に基づく不良の被試験回路の特定処理では、対応表の参照が不要であることから、CPU負荷が抑えられ試験に係る時間も短縮される。このため、本実施の形態例における半導体回路は、被試験回路やテストパターンTPの数が多量である場合でも、サマリー不良パターンアドレスと個別不良パターンアドレスの差分値に基づいて不良の被試験回路が特定可能であることにより、効率的な試験を実現可能にする。

【0068】

以上の実施の形態をまとめると、次の付記のとおりである。

【0069】

(付記1)

複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、パターンアドレスに対応して入力信号が規定されたテストパターンの前記パターンアドレス順に入力される前記入力信号に基づいて、前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する半導体回路。

【0070】

(付記2)

付記1において、

前記出力値に前記不良判定を示す値がある場合、初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、前記不良判定を示す良否判定値を出力した前記内部試験回路が特定される半導体回路。

【0071】

(付記3)

付記2において、

前記第1のパターンアドレスは、前記初めに出力された不良判定値が出力されたタイミングのパターンアドレスであり、

前記第2のパターンアドレスは、前記2つ目以降に出力された不良判定値が出力されたタイミングのパターンアドレスである半導体回路。

【0072】

(付記4)

付記1において、

前記スキャン出力モードを示す前記入力信号は、所定のパターンアドレス以降のパターンアドレスに対応するタイミングに入力される半導体回路。

【0073】

(付記5)

付記4において、

前記所定のパターンアドレスは、前記テストパターンによって異なる半導体回路。

【0074】

(付記6)

複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、入力信号に基づいて前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する半導体回路のテスト方法であって、

パターンアドレスに対応して前記入力信号が規定されたテストパターンの前記パターンアドレス順に、前記入力信号を前記半導体回路に入力し、当該入力信号に基づいて前記半導体回路から出力される出力値を順番に取得し、前記出力値に前記不良判定を示す値がある場合、不良判定値が出力されたタイミングのパターンアドレスを出力する不良パターンアドレス出力工程と、

初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、前記不良判定を示す良否判定値を出力した前記内部試験回路を特定する不良回路特定工程と、を有するテスト方法。

【符号の説明】

【0075】

10:Logicテスター、20:半導体回路、C1〜C4:CPU機能ブロック、B1〜B4:BIST回路、CE:総合判定回路、R1〜R4:スキャンラッチ、RS:サマリーラッチ

【特許請求の範囲】

【請求項1】

複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、パターンアドレスに対応して入力信号が規定されたテストパターンの前記パターンアドレス順に入力される前記入力信号に基づいて、前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する半導体回路。

【請求項2】

請求項1において、

前記出力値に前記不良判定を示す値がある場合、初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、前記不良判定を示す良否判定値を出力した前記内部試験回路が特定される半導体回路。

【請求項3】

請求項2において、

前記第1のパターンアドレスは、前記初めに出力された不良判定値が出力されたタイミングのパターンアドレスであり、

前記第2のパターンアドレスは、前記2つ目以降に出力された不良判定値が出力されたタイミングのパターンアドレスである半導体回路。

【請求項4】

請求項1において、

前記スキャン出力モードを示す前記入力信号は、所定のパターンアドレス以降のパターンアドレスに対応するタイミングに入力される半導体回路。

【請求項5】

複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、入力信号に基づいて前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する半導体回路のテスト方法であって、

パターンアドレスに対応して前記入力信号が規定されたテストパターンの前記パターンアドレス順に、前記入力信号を前記半導体回路に入力し、当該入力信号に基づいて前記半導体回路から出力される出力値を順番に取得し、前記出力値に前記不良判定を示す値がある場合、不良判定値が出力されたタイミングのパターンアドレスを出力する不良パターンアドレス出力工程と、

初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、前記不良判定を示す良否判定値を出力した前記内部試験回路を特定する不良回路特定工程と、を有するテスト方法。

【請求項1】

複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、パターンアドレスに対応して入力信号が規定されたテストパターンの前記パターンアドレス順に入力される前記入力信号に基づいて、前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する半導体回路。

【請求項2】

請求項1において、

前記出力値に前記不良判定を示す値がある場合、初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、前記不良判定を示す良否判定値を出力した前記内部試験回路が特定される半導体回路。

【請求項3】

請求項2において、

前記第1のパターンアドレスは、前記初めに出力された不良判定値が出力されたタイミングのパターンアドレスであり、

前記第2のパターンアドレスは、前記2つ目以降に出力された不良判定値が出力されたタイミングのパターンアドレスである半導体回路。

【請求項4】

請求項1において、

前記スキャン出力モードを示す前記入力信号は、所定のパターンアドレス以降のパターンアドレスに対応するタイミングに入力される半導体回路。

【請求項5】

複数の被試験回路と、

前記試験回路に対応して設けられた複数の第1のラッチ回路と、

第2のラッチ回路と、

前記複数の被試験回路それぞれに設けられ、入力信号に基づいて前記被試験回路に試験動作を実行させ、動作結果に基づく良否判定値を前記第1のラッチ回路にそれぞれ出力する複数の内部試験回路と、

前記内部試験回路が前記第1のラッチ回路に前記良否判定値を出力する時、複数の前記良否判定値のうち不良判定を示す値がある場合に当該不良判定を示す良否判定値を前記第2のラッチ回路に出力する総合判定回路と、

前記複数の第1のラッチ回路と前記第2のラッチ回路とを、前記第2のラッチ回路に保持された値が最初に出力されるように接続しスキャンチェーンを構成する接続経路とを有し、

前記スキャンチェーンは、前記入力信号がスキャン出力モードを示す時に、前記第1、2のラッチ回路に保持された良否判定値を順番に出力値として出力する半導体回路のテスト方法であって、

パターンアドレスに対応して前記入力信号が規定されたテストパターンの前記パターンアドレス順に、前記入力信号を前記半導体回路に入力し、当該入力信号に基づいて前記半導体回路から出力される出力値を順番に取得し、前記出力値に前記不良判定を示す値がある場合、不良判定値が出力されたタイミングのパターンアドレスを出力する不良パターンアドレス出力工程と、

初めに出力された不良判定値に対応する第1のパターンアドレスと、2つ目以降に出力された不良判定値に対応する第2のパターンアドレスとの差分値に基づいて、前記不良判定を示す良否判定値を出力した前記内部試験回路を特定する不良回路特定工程と、を有するテスト方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−40899(P2013−40899A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−179713(P2011−179713)

【出願日】平成23年8月19日(2011.8.19)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月19日(2011.8.19)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]