半導体回路

【課題】温度変化や製造プロセスのばらつきに起因する出力の変動を抑制する。

【解決手段】温度が上昇するとバイアス電圧生成回路28からNMOSトランジスタ26のゲートに供給されるバイアス電圧VGSが低下することで参照電流Irefが低下し、温度上昇に伴う電圧Vcの低下幅が小さくなり、温度が低下するとバイアス電圧VGSが上昇することで参照電流Irefが増大し、温度低下に伴う電圧Vcの増加幅が小さくなる。、製造プロセスのばらつきによりトランジスタの閾値電圧Vtが設計値より低下した場合は、バイアス電圧VGSも低下することで参照電流Irefが低下し、閾値電圧Vtの低下に伴う電圧Vcの低下幅が小さくなり、製造プロセスのばらつきによりトランジスタの閾値電圧Vtが設計値より上昇している場合は、バイアス電圧VGSも上昇することで参照電流Irefが増大し、閾値電圧Vtの上昇に伴う電圧Vcの増加幅が小さくなる。

【解決手段】温度が上昇するとバイアス電圧生成回路28からNMOSトランジスタ26のゲートに供給されるバイアス電圧VGSが低下することで参照電流Irefが低下し、温度上昇に伴う電圧Vcの低下幅が小さくなり、温度が低下するとバイアス電圧VGSが上昇することで参照電流Irefが増大し、温度低下に伴う電圧Vcの増加幅が小さくなる。、製造プロセスのばらつきによりトランジスタの閾値電圧Vtが設計値より低下した場合は、バイアス電圧VGSも低下することで参照電流Irefが低下し、閾値電圧Vtの低下に伴う電圧Vcの低下幅が小さくなり、製造プロセスのばらつきによりトランジスタの閾値電圧Vtが設計値より上昇している場合は、バイアス電圧VGSも上昇することで参照電流Irefが増大し、閾値電圧Vtの上昇に伴う電圧Vcの増加幅が小さくなる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体回路に係り、特に、入力電流に応じて変化する電圧を出力する電子回路を備えた半導体回路に関する。

【背景技術】

【0002】

携帯電話やTVに設けられたLCDにおけるバックライトの輝度調整や、照明装置における輝度(照度)等の制御には、光電変換素子によって周囲光の光量を検知して輝度等の制御を行う制御回路が搭載されたLSIが用いられている。周囲光の光量は、暗い状態(低照度)から晴天の太陽光下(高照度)まで指数関数的に増減変化するので、上記の制御回路は、周囲光の受光量に応じて光電変換素子を流れる光電流に対し、オペアンプを用いて電流電圧変換を行ったり、トランジスタやバイポーラを用いて電流増幅を行う際に、同時に対数変換(対数圧縮)を施すことで、後段で処理し易いレベルに変換する構成とされている。

【0003】

光電変換素子を流れる光電流に対して電流電圧変換及び対数変換を行う変換回路の従来の構成の一例を図13(A)に示す。図13(A)に示す構成では、光電変換素子100の一端がオペアンプ102の反転入力側に接続され、オペアンプ102の非反転入力端には一定のバイアス電圧Vrefが供給される。対数変換を行う場合、オペアンプ102の帰還部、すなわち電流電圧変換部にはダイオードが用いられる。図13ではMOSトランジスタ104をダイオード接続することでダイオードとして動作させている。なお、MOSトランジスタ104は、電流電圧変換が自然対数となる領域、すなわち、MOSトランジスタ104の電流電圧特性におけるサブスレッショルド領域で動作させている。このとき、出力端子OUTからの出力電圧Voは、近似的に、

Iph=Is{exp(qVg/nKT)−1)} …(1)

上記(1)式で表される。ここでIphは光電流、Isは逆電圧飽和電流、qは電荷量、Kはボルツマン定数、Tは絶対温度、nは理想係数(プロセス製造過程に起因)である。

【0004】

また、上記の(1)式で表される出力電圧Voの温度依存性を低減するために、図13(B)に示す構成も提案されている。図13(B)に示す構成では、MOSトランジスタ104から成る対数変換用のダイオードと同じ特性のダイオードを接続する(なお図13(B)ではMOSトランジスタ106をダイオードとして動作させている)と共に、電流源108によってノードAに参照電流Irefを供給している。ここで、逆方向バイアス条件では(1)式における"1"を無視できるので、図13(B)に示す構成における出力電圧Voは、

Vo=nKT/q×ln(Iph/Iref)×A …(2)

上記(2)式で表され、温度依存性の大きい電流Isが消去される。ここでAは電圧アンプ110の増幅度である。これにより、(2)式からも明らかなように、対数変換後の出力電圧V0の温度依存性はnK/q倍に低減される。なお、特許文献1の図7にも図13(B)と類似の構成が開示されている。

【特許文献1】特開平11−38463号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、図13(B)に示す構成では、温度が上昇するとMOSトランジスタ104,106の閾値電圧Vtが低下するため、ノードAの電圧Vcは低下する。図13(B)に示す構成では、ノードAの電圧Vcが変化すると出力電圧V0も変化するので、光電流Iphが一定であっても温度変化に応じて出力電圧V0が変動するという問題がある。また、製造プロセスのばらつきの影響でMOSトランジスタ104,106の閾値電圧Vtが設計値よりも低い場合、電流が一定であればノードAの電圧Vcが低下するので、光電流Iphが一定であっても製造プロセスのばらつきに起因する閾値電圧Vtのばらつきによって出力電圧V0が変動するという問題もある。

【0006】

本発明は上記事実を考慮して成されたもので、温度変化や製造プロセスのばらつきに起因する出力の変動を抑制できる半導体回路を得ることが目的である。

【課題を解決するための手段】

【0007】

上記目的を達成するために請求項1記載の発明に係る半導体回路は、第1ノードと第2ノードの間に設けられた半導体素子を備え、入力電流に応じて出力が変化すると共に、前記第2ノードに供給される参照電流に応じて定まる前記第2ノードの電圧が変化した場合も前記出力が変化する電子回路と、供給されたバイアス電圧のレベルに応じた参照電流を前記第2ノードに供給する参照電流用トランジスタを備えた参照電流供給手段と、温度及び前記半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧を前記参照電流用トランジスタへ供給するバイアス電圧発生手段と、を含んで構成されている。

【0008】

請求項1記載の発明に係る電子回路は、第1ノードと第2ノードの間に設けられた半導体素子を備え、入力電流に応じて出力(電圧又は電流)が変化すると共に、第2ノードに供給される参照電流又は第2ノードの電圧が変化した場合も出力が変化するように構成されている。なお、この電子回路としては、例えば請求項2に記載したように、入力端に入力電流が供給されると共に出力端が第1ノードに接続されたオペアンプと、第1ノードとオペアンプの入力端の間に設けられたダイオード素子と、入力端が第2ノードに接続された増幅器を備えると共に、半導体素子もダイオード素子で構成され、入力電流の対数値に比例する電圧を出力する電流電圧変換回路が好適であるが、入力電流に応じて出力(電圧又は電流)が変化すると共に、第2ノードに供給される参照電流又は第2ノードの電圧が変化した場合も出力が変化するものであれば、他の構成であってもよい。また、上記の電子回路は、例えば請求項3に記載したように、光電変換素子が接続され、光電変換素子の受光量に応じて光電変換素子を流れる電流が入力される構成が好適であるが、入力電流は他の電流であってもよい。また本発明において、任意のノードや端子への電流の「供給」には、任意のノードや端子へマイナスの電流(逆向きの電流)を供給する(される)ことも含まれる(以下同様)。

【0009】

また、請求項1記載の発明に係る電子回路は、温度が上昇するに従い、第1ノードと第2ノードの間に設けられた半導体素子のキャリア移動度が低下し閾値電圧が低下することで第2ノードの電圧が低下すると共に、半導体素子の製造プロセスのばらつきによっても閾値電圧が変動することで第2ノードの電圧が変動するが、当該電子回路は、前述のように入力電流に応じて出力が変化すると共に、第2ノードの電圧が変化した場合も出力が変化するので、温度変化や半導体素子の製造プロセスのばらつきによって出力(電圧又は電流)が変動することになる。

【0010】

これに対して請求項1記載の発明では、供給されたバイアス電圧のレベルに応じた参照電流を第2ノードに供給する参照電流用トランジスタを備えた参照電流供給手段が設けられており、バイアス電圧発生手段は、温度変化及び半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧を参照電流用トランジスタへ供給する。これにより、温度変化が生じた場合や、半導体素子の製造プロセスのばらつきが生じていた場合は、バイアス電圧発生手段から参照電流用トランジスタへ供給されるバイアス電圧のレベルが変化し、このバイアス電圧のレベルの変化に伴い参照電流用トランジスタによって第2ノードに供給される参照電流が変化し、この参照電流の変化に伴って第2ノードの電圧の変化が抑制される。従って、請求項1記載の発明によれば、温度変化や製造プロセスのばらつきに起因する出力の変動を抑制することができる。

【0011】

なお、請求項1記載の発明において、バイアス電圧発生手段は、例えば請求項4に記載したように、半導体素子と同一プロセスで形成された複数のバイアス電圧用トランジスタを、温度が上昇するに従ってバイアス電圧のレベルが低下し、製造プロセスのばらつきに伴い複数のバイアス電圧用トランジスタの閾値電圧が低下するに従ってバイアス電圧のレベルが低下するように接続して構成することができる。上記のように、バイアス電圧発生手段を複数のバイアス電圧用トランジスタで構成することで、温度変化に対して半導体素子と同様の特性変化(キャリア移動度の変化に伴う閾値電圧の変化等)を示すと共に、複数のバイアス電圧用トランジスタを半導体素子と同一プロセスで形成することで、製造プロセスのばらつきによる特性変化(閾値電圧の変化等)についても半導体素子と同様となるので、これら複数のバイアス電圧用トランジスタを接続してバイアス電圧発生手段を構成することで、温度変化及び半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧の発生を実現することができる。

【0012】

また、請求項1記載の発明において、参照電流供給手段は、参照電流用トランジスタとして単一のトランジスタを備えた構成であってもよいが、当該参照電流用トランジスタも製造プロセスのばらつきの影響を受け、製造プロセスのばらつきの影響で参照電流用トランジスタの閾値電圧が大きく変化した場合、参照用供給用トランジスタによって第2ノードに供給される参照電流も大きく変化することで、第2ノードの電圧の変化を精度良く抑制することが困難となる。これを考慮すると、参照電流供給手段は、例えば請求項5に記載したように、供給されたバイアス電圧のレベルに応じた参照電流を第2ノードに供給する参照電流用トランジスタを複数備えると共に、参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかを個々の参照電流用トランジスタ毎に切替可能な切替手段を備え、切替手段は、個々の参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかが、第2ノードの電圧が所定値に一致するように切替されることが好ましい。

【0013】

請求項5記載の発明では、複数の参照電流用トランジスタのうち、第2ノードに接続されている個々の参照電流用トランジスタが第2ノードに供給する参照電流の総和が第2ノードに供給される参照電流となるので、参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかを個々の参照電流用トランジスタ毎に切替えることで、第2ノードに供給する参照電流の大きさ、すなわち第2ノードの電圧を小さな変化幅で変化させることが可能となり、製造プロセスのばらつきの影響で個々の参照電流用トランジスタの閾値電圧が変化していたとしても、第2ノードの電圧の変化を精度良く抑制することが可能となる。

【0014】

また、請求項5記載の発明において、個々の参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかの切替えは、製造プロセスのばらつきに起因する第2ノードの電圧の変化を抑制することが目的であり、第2ノードの電圧が所定値に一致するように、個々の参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかを一旦切替えた後は、当該切替えを変更する必要はない。これを考慮すると、例えば請求項6に記載したように、参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかを切替させる切替信号を、個々の参照電流用トランジスタ毎に切替手段に供給する切替信号供給手段を設け、切替信号供給手段から個々の参照電流用トランジスタ毎に切替手段に供給される切替信号が、第2ノードの電圧を測定した結果に基づきメタルトリミングによって設定されるようにしてもよい。

【0015】

本発明に係る半導体回路を複数製造した場合、個々の半導体回路における適正な切替信号が相違する可能性があるが、請求項6記載の発明では、第2ノードの電圧を測定した結果に基づきメタルトリミングによって切替信号が設定されるので、上記のような場合にも切替信号供給手段を一定の構成とすることができ、半導体回路の製造が容易になると共に、個々の半導体回路毎に相違する(可能性がある)切替信号を安定して切替手段に供給することができる。

【0016】

また、請求項6記載の発明において、切替手段は、例えば請求項7に記載したように、個々の参照電流用トランジスタに対応して設けられた複数のトランスファーゲートを備え、参照電流用トランジスタ毎に供給された切替信号が、対応するトランスファーゲートに各々入力される構成を採用することができる。

【発明の効果】

【0017】

以上説明したように本発明は、入力電流に応じて出力が変化すると共に第2ノードの電圧が変化した場合も出力が変化する電子回路に、供給されたバイアス電圧のレベルに応じた参照電流を第2ノードに供給する参照電流用トランジスタを備えた参照電流供給手段と、温度及び半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧を参照電流用トランジスタへ供給するバイアス電圧発生手段を設けたので、温度変化や製造プロセスのばらつきに起因する出力の変動を抑制できる、という優れた効果を有する。

【発明を実施するための最良の形態】

【0018】

以下、図面を参照して本発明の実施形態の一例を詳細に説明する。

【0019】

〔第1実施形態〕

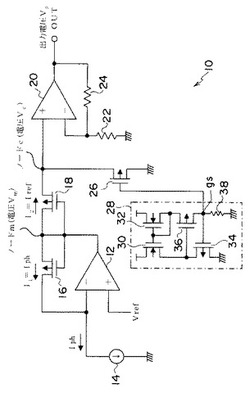

図1には本第1実施形態に係る対数変換回路10が示されている。対数変換回路10は本発明に係る半導体回路に対応している。なお、本実施形態に係る対数変換回路は、光電変換素子によって周囲光の光量を検知してLCDのバックライトの輝度等の制御を行う照明制御回路の一部を構成しており、照明制御回路の一部としてLSI等の半導体集積回路に搭載されている。対数変換回路10はオペアンプ12を備え、オペアンプ12の反転入力端には、一端が接地され受光量に応じた光電流Iphを発生させる光電変換素子14の他端が接続されている。なお、光電変換素子14は請求項3に記載の光電変換素子に対応している。また、オペアンプ12の非反転入力端は図示しない定電圧電源に接続され、一定のバイアス電圧Vrefが供給される。またオペアンプ12の出力端はノードmに接続されている。ノードmは本発明に係る第1ノードに対応している。

【0020】

また、対数変換回路10は一対のNMOSトランジスタ16,18を備えており、NMOSトランジスタ16,18のゲート及びドレインはノードmに各々接続されている。NMOSトランジスタ16,18はサブスレッショルド領域で動作するように設計されており、ゲートとドレインが短絡されていることで、互いに同じ特性のダイオードとして各々機能する。NMOSトランジスタ16のソースはオペアンプ12の反転入力端に接続されている。NMOSトランジスタ16は請求項2に記載のダイオード素子に、オペアンプ12は請求項2に記載のオペアンプに各々対応しており、NMOSトランジスタ16及びオペアンプ12は、光電変換素子14で発生された光電流Iphを、光電流Iphの対数値に比例する電圧へ変換する対数変換/電流電圧変換部として機能する。

【0021】

一方、NMOSトランジスタ18のソースはノードcを介してオペアンプ20の非反転入力端に接続されている。ノードcは本発明に係る第2ノードに対応しており、NMOSトランジスタ18は本発明に係る半導体素子(より詳しくは請求項2に記載の「ダイオード素子で構成された半導体素子」)に対応している。オペアンプ20の反転入力端は抵抗22を介して接地されており、オペアンプ20の出力端は対数変換回路10の出力端OUTに接続され、また抵抗24を介してオペアンプ20の反転入力端にも接続されている。オペアンプ20及び抵抗22,24は電圧アンプとして機能し、請求項2に記載の増幅器に対応している。

【0022】

なお、上述したオペアンプ12,20、NMOSトランジスタ16,18及び抵抗22,24は本発明に係る電子回路(詳しくは請求項2に記載の電流電圧変換回路)に対応している。また本実施形態では、製造の容易さを考慮してNMOSトランジスタ16,18をダイオード素子として用いているが、本発明はこれに限られるものではなく、NMOSトランジスタ16,18に代えてダイオードを設けてもよい。

【0023】

また、ノードcにはNMOSトランジスタ26のドレインが接続されている。NMOSトランジスタ26は本発明に係る参照電流供給手段の参照電流用トランジスタに対応しており、ソースが接地され、ゲートにはバイアス電圧生成回路28が接続されている。バイアス電圧生成回路28は本発明に係るバイアス電圧発生手段(より詳しくは請求項4に記載のバイアス電圧発生手段)に対応しており、NMOSトランジスタ16,18と同一プロセスで形成された2個のPMOSトランジスタ30,32と2個のNMOSトランジスタ34,36を備えている。なお、これらのPMOSトランジスタ30,32及びNMOSトランジスタ34,36は、請求項4に記載の複数のバイアス電圧用トランジスタに対応しており、飽和領域で動作するようにサイズ(チャンネル幅(W)とチャンネル長(L)の比であるW/Lサイズ)が調整されている。また、PMOSトランジスタ30,32はW/Lサイズが同一とされている。

【0024】

バイアス電圧生成回路28のPMOSトランジスタ30,32はドレインが図示しない電源に各々接続され、ゲートが互いに接続されている。また、PMOSトランジスタ30のソースにはNMOSトランジスタ34のドレイン及びNMOSトランジスタ36のゲートが各々接続されており、PMOSトランジスタ32はゲートとソースが短絡されており、PMOSトランジスタ32のソースにはNMOSトランジスタ36のドレインが接続されている。また、NMOSトランジスタ34はゲートがノードgsに接続され、ソースが接地されており、NMOSトランジスタ36のソースもノードgsに接続されている。更に、ノードgsは一端が接地された抵抗38の他端が接続されていると共に、NMOSトランジスタ26のゲートに接続されている。

【0025】

次に、本第1実施形態に係る対数変換回路10の作用を説明する。対数変換回路10はノードcにNMOSトランジスタ26が接続され、このNMOSトランジスタ26のゲートにはバイアス電圧生成回路28によってバイアス電圧が供給されることで、対数変換回路10のノードcには、NMOSトランジスタ26のゲートに供給されたバイアス電圧のレベルに応じた参照電流Irefが流れる。このため、対数変換回路10の出力電圧Voは先の(2)式で表される値、すなわち光電流Iphの対数値に比例する値になり(但し、(2)式におけるAはオペアンプ20、抵抗22,24から成る電圧アンプの増幅度)、(2)式からも明らかなように、出力電圧V0の温度依存性はnK/q倍に低減される。

【0026】

ところで、本第1実施形態に係る対数変換回路10では、電圧降下によりノードcの電圧Vcがノードmの電圧Vmよりも低くなり、出力電圧V0はノードcの電圧Vcに応じて変化する。またNMOSトランジスタ16,18におけるキャリア移動度は温度によって変化し、温度が上昇するに従ってキャリア移動度が低下する一方、温度が下降するに従ってキャリア移動度が増大するが、このNMOSトランジスタ16,18におけるキャリア移動度の変化に応じてNMOSトランジスタ16,18の閾値電圧Vtが変化し、これに伴ってノードmの電圧Vm及びノードcの電圧Vcが変化する。このため、図13(B)に示す構成のように、ノードcを流れる参照電流Irefが一定の場合(参照電流Irefが温度や対数変換回路10(半導体集積回路)の製造プロセスの影響を受けない場合)は、図4に示すように、温度変化に対して電圧Vm,Vcが同じ変化を示すことで、一定の光電流Iphに対応する出力電圧V0が温度変化に対して大きく変動する。

【0027】

また、NMOSトランジスタ16,18の閾値電圧Vtは、対数変換回路10(半導体集積回路)の製造プロセスのばらつき(特に、NMOSトランジスタの閾値電圧Vtを規定するP型半導体の低濃度インプラ(イオン注入)のばらつき)によっても変化し、これに伴ってノードmの電圧Vm及びノードcの電圧Vcが変化するので、図13(B)に示す構成のようにノードcを流れる参照電流Irefが一定の場合(参照電流Irefが温度や製造プロセスの影響を受けない場合)は、図6に示すように、製造プロセスのばらつきに伴うNMOSトランジスタ16,18の閾値電圧Vtの変化に対して電圧Vm,Vcが同じ変化を示すことで、一定の光電流Iphに対応する出力電圧V0が温度変化に対して大きく変動する。

【0028】

これに対して本第1実施形態に係る対数変換回路10は、バイアス電圧生成回路28のPMOSトランジスタ30,32のW/Lサイズが同一とされ、PMOSトランジスタ30,32及びNMOSトランジスタ34,36が飽和領域で各々動作するように各トランジスタのW/L等が最適化されており、PMOSトランジスタ30を流れる電流I1=PMOSトランジスタ32を流れる電流I2で、かつ、NMOSトランジスタ34を流れる電流=PMOSトランジスタ30を流れる電流I1であるので、ノードGSの電圧(NMOSトランジスタ26のゲートに供給されるバイアス電圧)VGSはVGS=I1×Rとなる(但しRは抵抗38の電気抵抗)。そして電流I1をNMOSトランジスタ34のパラメータ(キャリア移動度μ、ゲート絶縁膜容量Cox、チャンネル幅W、チャンネル長L、ゲート電圧(=NMOSトランジスタ26のゲートに供給されるバイアス電圧)VGS、閾値電圧Vt)を用いて表すと、次の(3)式のようになる。

I1=1/2・μ・Cox・W/L・(VGS−Vt)2 …(3)

なお、本第1実施形態に係る対数変換回路10において、一例として、温度が所定値かつ閾値電圧Vtが設計値(Typical)の条件での電流I1,I2=5μAとしたい場合には、例えばPMOSトランジスタ30,32のW/L=15μm/2μm、NMOSトランジスタ34,36のW/L=5μm/5μm、抵抗38の電気抵抗値R=180kΩに調整することで実現することができる。

【0029】

ここで、温度が上昇しNMOSトランジスタ34のキャリア移動度μが低下すると、上記の(3)式で表される電流I1が減少することで、図2にも示すように、NMOSトランジスタ34のゲート電圧(バイアス電圧)VGSが低下される。また、温度が低下しNMOSトランジスタ34のキャリア移動度μが増大すると、上記の(3)式で表される電流I1が増大することで、図2にも示すように、NMOSトランジスタ34のゲート電圧(バイアス電圧)VGSが上昇される。

【0030】

また、バイアス電圧生成回路28のPMOSトランジスタ30,32及びNMOSトランジスタ34,36は、NMOSトランジスタ16,18と同一プロセスで形成されているので、製造プロセスのばらつきによりNMOSトランジスタ16,18の閾値電圧Vtが設計値より低下している場合は、NMOSトランジスタ34,36の閾値電圧Vtも同様に設計値より低下していることになり、図2に"Vt:Low"と表記して示すようにバイアス電圧VGSも低下される。また、製造プロセスのばらつきによりNMOSトランジスタ16,18の閾値電圧Vtが設計値よりも上昇している場合は、NMOSトランジスタ34,36の閾値電圧Vtも同様に設計値よりも上昇していることになり、図2に"Vt:High"と表記して示すようにバイアス電圧VGSも上昇される。

【0031】

NMOSトランジスタ26のゲートには、バイアス電圧生成回路28で発生されたバイアス電圧VGS、すなわち温度変化及び製造プロセスのばらつきに伴う閾値電圧Vtの変化に対して図2に示すように変化するバイアス電圧VGSが供給される。これにより、温度が上昇した場合は、バイアス電圧VGSが低下されることでノードcを流れる参照電流IrefがNMOSトランジスタ26によって低下され、温度上昇に起因するノードcの電圧Vcの低下幅は参照電流Irefの低下分だけ小さくなる。また、温度が低下した場合は、バイアス電圧VGSが上昇されることでノードcを流れる参照電流IrefがNMOSトランジスタ26によって増大され、温度低下に起因するノードcの電圧Vcの増加幅は参照電流Irefの増大分だけ小さくなる。従って、本第1実施形態に係る対数変換回路10では、図3に示すように、温度変化に対するノードcの電圧Vcの変動が抑制され、一定の光電流Iphに対応する出力電圧V0が温度変化の影響で変動することを抑制することができる。

【0032】

また、製造プロセスのばらつきに伴ってNMOSトランジスタ16,18の閾値電圧Vtが設計値より低下していた場合は、バイアス電圧VGSが低下されることでノードcを流れる参照電流IrefがNMOSトランジスタ26によって低下され、閾値電圧Vtの低下に起因するノードcの電圧Vcの低下幅は参照電流Irefの低下分だけ小さくなる。また、製造プロセスのばらつきに伴ってNMOSトランジスタ16,18の閾値電圧Vtが設計値より上昇していた場合は、バイアス電圧VGSが上昇されることでノードcを流れる参照電流IrefがNMOSトランジスタ26によって増大され、閾値電圧Vtの低下に起因するノードcの電圧Vcの増加幅は参照電流Irefの増大分だけ小さくなる。従って、本第1実施形態に係る対数変換回路10では、図5に示すように、製造プロセスのばらつきに伴う閾値電圧Vtの変動に対するノードcの電圧Vcの変動が抑制され、一定の光電流Iphに対応する出力電圧V0が、製造プロセスのばらつきに伴う閾値電圧の変動の影響で変動することも抑制することができる。

【0033】

〔第2実施形態〕

次に本発明の第2実施形態について説明する。なお、第1実施形態と同一の部分には同一の符号を付し、説明を省略する。図7には、本第2実施形態に係る対数変換回路50が示されている。この対数変換回路50も本発明に係る半導体回路に対応している。対数変換回路50では、第1実施形態で説明した対数変換回路10に対して3個のNMOSトランジスタ52,54,56が追加されている。NMOSトランジスタ52,54,56は、ドレインが切替部58を介してノードcに各々接続され、ソースが各々接地され、ゲートがバイアス電圧生成回路28に各々接続されており、NMOSトランジスタ52,54,56のゲートには、NMOSトランジスタ26と同様にバイアス電圧生成回路28からバイアス電圧VGSが供給される。なお、NMOSトランジスタ52,54,56は請求項5に記載の複数の参照電流用トランジスタに対応している。

【0034】

切替部58は3個のトランスファーゲート60,62,64を備えており、トランスファーゲート60はNMOSトランジスタ52のドレインとノードcの間に、トランスファーゲート62はNMOSトランジスタ54のドレインとノードcの間に、トランスファーゲート64はNMOSトランジスタ56のドレインとノードcの間に各々設けられている。トランスファーゲート60のゲートtg1,tg1_b、トランスファーゲート62のゲートtg2,tg2_b、及び、トランスファーゲート64のゲートtg3,tg3_bは切替信号供給部66に各々接続されており、トランスファーゲート60,62,64は切替信号供給部66から個々のゲートに供給された切替信号に応じてオン状態(導通状態)又はオフ状態(非導通状態)に切り替わる。

【0035】

なお、本第2実施形態では、トランスファーゲート60,64として、ゲートtg1,tg3に供給される切替信号がハイレベル、ゲートtg1_b,tg3_bに供給される切替信号がローレベルのときにオン状態となり、ゲートtg1,tg3に供給される切替信号がローレベル、ゲートtg1_b,tg3_bに供給される切替信号がハイレベルのときにオフ状態となるトランスファーゲートを用いている一方、トランスファーゲート62としては、ゲートtg2に供給される切替信号がローレベル、ゲートtg2_bに供給される切替信号がハイレベルのときにオン状態となり、ゲートtg2に供給される切替信号がハイレベル、ゲートtg2_bに供給される切替信号がローレベルのときにオフ状態となるトランスファーゲートを用いている。切替部58は請求項5に記載の切替手段に対応しており、トランスファーゲート60,62,64は請求項7に記載の複数のトランスファーゲートに対応している。

【0036】

図8に示すように、切替信号供給部66は個々のトランスファーゲート60,62,64に対応する3個の切替信号生成回路68A〜68Cを備えている。個々の切替信号生成回路68は2個のNOT回路70,72を備えている。NOT回路70の入力端には、ドレインが図示しない電源に接続されゲートが接地されたPMOSトランジスタ74のソースと、抵抗76の一端が各々接続されている。抵抗76の他端は、外部に露出しておりメタルトリミングによって切断することが可能なフューズ78の一端に接続されており、フューズ78の他端は接地されている。またNOT回路70の出力端は、ゲートtgi_bに供給する切替信号tgi_b(但しi=1〜3)を出力するための信号出力端と、NOT回路72の入力端に各々接続されており、NOT回路72の出力端はゲートtgiに供給する切替信号tgi(但しi=1〜3)を出力するための信号出力端に接続されている。

【0037】

上記構成により、個々の切替信号生成回路68は、フューズ78が未切断の状態では切替信号tgiとしてローレベル、切替信号tgi_bとしてハイレベルの信号が出力され、メタルトリミングによってフューズ78が切断された状態では切替信号tgiとしてハイレベル、切替信号tgi_bとしてローレベルの信号が出力される。なお、切替信号供給部66は請求項6に記載の切替信号供給手段に対応している。

【0038】

次に本第2実施形態の作用について、第1実施形態と異なる部分のみ説明する。第1実施形態で説明した対数変換回路10は、参照電流用トランジスタとして単一のNMOSトランジスタ26が設けられているが、このNMOSトランジスタ26も製造プロセスのばらつきの影響を受けて閾値電圧Vtが変動するので、製造プロセスのばらつきの影響でNMOSトランジスタ16,18,26の閾値電圧Vtが大きく変動した場合には、バイアス電圧生成回路28によるバイアス電圧VGSの変更に拘わらず参照電流Irefが設計値に対して大きくずれることで、例として図10に矢印で示すように、ノードcの電圧Vcが設計値に対して大きくずれ、これに伴って出力電圧V0も設計値に対して大きくずれてしまうという問題が生ずる。

【0039】

これに対して本第2実施形態に係る対数変換回路50では、参照電流用トランジスタとして、NMOSトランジスタ26に加えてNMOSトランジスタ52,54,56が設けられており、NMOSトランジスタ26を流れる電流をIr0、NMOSトランジスタ52を流れる電流をIr1、NMOSトランジスタ54を流れる電流をIr2、NMOSトランジスタ56を流れる電流をIr3とすると、参照電流IrefはIref=Ir0+Ir1+Ir2+Ir3となる。また、NMOSトランジスタ52,54,56とノードcとの間には、切替信号供給部66から供給された切替信号に応じてオン状態(導通状態)又はオフ状態(非導通状態)に切り替わるトランスファーゲート60,62,64が設けられているので、トランスファーゲート60,62,64に供給する切替信号のレベルを切替えることで、NMOSトランジスタ52,54,56を流れる電流Ir1,Ir2,Ir3を互いに独立にオンオフすることができる。

【0040】

なお、本第2実施形態に係る切替信号供給部66の個々の切替信号生成回路68A〜68Cは、当初は何れもフューズ78が未切断の状態であるので、切替信号供給部66からは切替信号tgiとしてローレベル、切替信号tgi_bとしてハイレベルの信号が出力され、トランスファーゲート60,62,64のうちトランスファーゲート62のみオン状態となっている。従って、参照電流Irefは当初はIref=Ir0+Ir2となっている。

【0041】

本第2実施形態では、対数変換回路50を搭載した半導体集積回路を製造した後、製造した半導体集積回路を出荷する前に、以下の調整作業が行われる。この調整作業では、まず、温度を規定値に維持すると共に、一定光量の光を光電変換素子14に照射することで光電変換素子14で一定の光電流Iphが発生させた状態で、ノードcの電圧Vcが測定される。次に、電圧Vcの測定値と設計値との偏差に基づいて、トランスファーゲート60,62,64のオンオフの状態の切替えが必要か否かが判断される。前記偏差が許容範囲内であれば、トランスファーゲート60,62,64のオンオフの状態の切替えは不要と判断されて作業終了となるが、前記偏差が許容範囲を超えている場合は、トランスファーゲート60,62,64のオンオフの状態の切替えが必要と判断され、電圧Vcの測定値と設計値との偏差を小さくするためには何れのトランスファーゲートのオンオフの状態を切替えるべきかが判断され、オンオフの状態を切替えるトランスファーゲートに対応する切替信号生成回路68のフューズ78をメタルトリミングによって切断する作業が行われる。

【0042】

上記のように、本第2実施形態では参照電流Irefを調整することでノードcの電圧Vcを調整しているが、一般に電圧Vと電流IにはV=logIの関係があるため、トランスファーゲート60,62,64の各々のオンオフの状態の組み合わせを切替える(切替信号生成回路68A〜68Cのフューズ78の切断/非切断の組み合わせを選択する)ことで、参照電流Irefが指数関数的に変化するように、NMOSトランジスタ52,54,56のサイズ(W/Lサイズ)の組み合わせが予め設定されている。なお、次の表1には、

個々の切替信号生成回路68のフューズ78の切断/非切断を選択することで、各トランスファーゲートのオンオフの状態の組み合わせを切替えた場合の参照電流Irefの変化の一例を示す。

【0043】

【表1】

【0044】

このように、各トランスファーゲートのオンオフの状態の組み合わせの切替えに対して参照電流Irefが指数関数的に変化するように構成することで、各トランスファーゲートのオンオフの状態の組み合わせの切替えに対して電圧Vcがおよそ一定の変化幅で変化するので(図9も参照)、電圧Vcを設計値に一致、又は、設計値との偏差が非常に小さい値へ調整することを容易に実現することができる。従って、製造プロセスのばらつきの影響でNMOSトランジスタ16,18,26の閾値電圧Vtが大きく変動し、出力電圧V0が設計値に対して大きくずれてしまっていた場合にも、上記の調整作業を行うことで、例として図11にも示すように、出力電圧V0を設計値に一致、又は、設計値との偏差が非常に小さい値へ調整することができる。

【0045】

また、上記の調整作業を一旦行った後は、各トランスファーゲートのオンオフの状態を切替える必要はなく、また、温度変化に対するノードcの電圧Vcの変動は、NMOSトランジスタ26,52,54,56のゲートに各々供給されるバイアス電圧VGSが、第1実施形態で説明したバイアス電圧生成回路28によって温度変化に応じて調整されることで抑制されるので、対数変換回路50を搭載した半導体集積回路の出荷後に、ユーザが出力電圧V0等を調整する作業を行う必要もなくなる。

【0046】

なお、上記では本発明に係る半導体素子としてNMOSトランジスタ18を、請求項2に記載のダイオード素子としてNMOSトランジスタ16を、本発明に係る参照電流用トランジスタとしてNMOSトランジスタ26を各々適用した態様を説明したが、本発明はこれに限定されるものではない。例として図12には、第1実施形態で説明した対数変換回路10に対し、本発明に係る半導体素子をPMOSトランジスタ44に、請求項2に記載のダイオード素子をPMOSトランジスタ42に、本発明に係る参照電流用トランジスタをNMOSトランジスタ46に各々置き換えた構成の対数変換回路40を示す。図12に示すように、本発明に係る半導体素子、請求項2に記載のダイオード素子及び本発明に係る参照電流用トランジスタはPMOSトランジスタで構成することも可能である。また、第2実施形態で説明した対数変換回路50のNMOSトランジスタ52,54,56についても、同様にPMOSトランジスタへ置き換え可能であることは言うまでもない。

【0047】

また、上記では本発明に係る半導体回路として、光電変換素子14で発生された光電流Iphに対して対数変換及び電流電圧変換を行う対数変換回路10,40,50を例に説明したが、本発明に係る半導体回路のうちの電子回路は、入力電流に応じて出力が変化すると共に、第2ノードに供給される参照電流に応じて定まる第2ノードの電圧が変化した場合も出力が変化する構成であればよく、例えば光電流Iphに対して対数変換のみを行い光電流Iphの対数値に比例する電流を出力する構成の変換回路に本発明を適用することも可能であり、入力電流も光電流Iphに限られるものではない。

【図面の簡単な説明】

【0048】

【図1】第1実施形態に係る対数変換回路の回路図である。

【図2】温度変化及び製造プロセスのばらつきに起因する閾値電圧Vtの変化に対する、バイアス電圧生成回路によって生成されるバイアス電圧Vgsの変化を示す線図である。

【図3】本実施形態に係る対数変換回路における温度変化に対する出力電圧V0の変化を示す線図である。

【図4】従来の対数変換回路における温度変化に対する出力電圧V0の変化を示す線図である。

【図5】本実施形態に係る対数変換回路における、製造プロセスのばらつきに起因する閾値電圧Vtの変化に対する出力電圧V0の変化を示す線図である。

【図6】従来の対数変換回路における、製造プロセスのばらつきに起因する閾値電圧Vtの変化に対する出力電圧V0の変化を示す線図である。

【図7】第2実施形態に係る対数変換回路の回路図である。

【図8】第2実施形態に係る切替信号供給部の回路図である。

【図9】切替信号の変更(メタルトリミング)による電流Iref及び電圧Vcの変化を示す線図である。

【図10】製造プロセスのばらつきに起因する、設計値からの出力電圧V0のずれを示す線図である。

【図11】メタルトリミングによる出力電圧V0のずれの修正を説明するための線図である。

【図12】対数変換回路の他の構成を示す回路図である。

【図13】(A)及び(B)は電流電圧変換及び対数変換を行う変換回路の従来の構成を各々示す回路図である。

【符号の説明】

【0049】

10 対数変換回路

12 オペアンプ

14 光電変換素子

16 NMOSトランジスタ

18 NMOSトランジスタ

26 NMOSトランジスタ

28 バイアス電圧生成回路

30 PMOSトランジスタ

32 PMOSトランジスタ

34 NMOSトランジスタ

36 NMOSトランジスタ

38 抵抗

40 対数変換回路

42 PMOSトランジスタ

44 PMOSトランジスタ

46 PMOSトランジスタ

50 対数変換回路

52 NMOSトランジスタ

54 NMOSトランジスタ

56 NMOSトランジスタ

58 切替部

60 トランスファーゲート

62 トランスファーゲート

64 トランスファーゲート

66 切替信号供給部

68A〜68C 切替信号生成回路

78 フューズ

【技術分野】

【0001】

本発明は半導体回路に係り、特に、入力電流に応じて変化する電圧を出力する電子回路を備えた半導体回路に関する。

【背景技術】

【0002】

携帯電話やTVに設けられたLCDにおけるバックライトの輝度調整や、照明装置における輝度(照度)等の制御には、光電変換素子によって周囲光の光量を検知して輝度等の制御を行う制御回路が搭載されたLSIが用いられている。周囲光の光量は、暗い状態(低照度)から晴天の太陽光下(高照度)まで指数関数的に増減変化するので、上記の制御回路は、周囲光の受光量に応じて光電変換素子を流れる光電流に対し、オペアンプを用いて電流電圧変換を行ったり、トランジスタやバイポーラを用いて電流増幅を行う際に、同時に対数変換(対数圧縮)を施すことで、後段で処理し易いレベルに変換する構成とされている。

【0003】

光電変換素子を流れる光電流に対して電流電圧変換及び対数変換を行う変換回路の従来の構成の一例を図13(A)に示す。図13(A)に示す構成では、光電変換素子100の一端がオペアンプ102の反転入力側に接続され、オペアンプ102の非反転入力端には一定のバイアス電圧Vrefが供給される。対数変換を行う場合、オペアンプ102の帰還部、すなわち電流電圧変換部にはダイオードが用いられる。図13ではMOSトランジスタ104をダイオード接続することでダイオードとして動作させている。なお、MOSトランジスタ104は、電流電圧変換が自然対数となる領域、すなわち、MOSトランジスタ104の電流電圧特性におけるサブスレッショルド領域で動作させている。このとき、出力端子OUTからの出力電圧Voは、近似的に、

Iph=Is{exp(qVg/nKT)−1)} …(1)

上記(1)式で表される。ここでIphは光電流、Isは逆電圧飽和電流、qは電荷量、Kはボルツマン定数、Tは絶対温度、nは理想係数(プロセス製造過程に起因)である。

【0004】

また、上記の(1)式で表される出力電圧Voの温度依存性を低減するために、図13(B)に示す構成も提案されている。図13(B)に示す構成では、MOSトランジスタ104から成る対数変換用のダイオードと同じ特性のダイオードを接続する(なお図13(B)ではMOSトランジスタ106をダイオードとして動作させている)と共に、電流源108によってノードAに参照電流Irefを供給している。ここで、逆方向バイアス条件では(1)式における"1"を無視できるので、図13(B)に示す構成における出力電圧Voは、

Vo=nKT/q×ln(Iph/Iref)×A …(2)

上記(2)式で表され、温度依存性の大きい電流Isが消去される。ここでAは電圧アンプ110の増幅度である。これにより、(2)式からも明らかなように、対数変換後の出力電圧V0の温度依存性はnK/q倍に低減される。なお、特許文献1の図7にも図13(B)と類似の構成が開示されている。

【特許文献1】特開平11−38463号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、図13(B)に示す構成では、温度が上昇するとMOSトランジスタ104,106の閾値電圧Vtが低下するため、ノードAの電圧Vcは低下する。図13(B)に示す構成では、ノードAの電圧Vcが変化すると出力電圧V0も変化するので、光電流Iphが一定であっても温度変化に応じて出力電圧V0が変動するという問題がある。また、製造プロセスのばらつきの影響でMOSトランジスタ104,106の閾値電圧Vtが設計値よりも低い場合、電流が一定であればノードAの電圧Vcが低下するので、光電流Iphが一定であっても製造プロセスのばらつきに起因する閾値電圧Vtのばらつきによって出力電圧V0が変動するという問題もある。

【0006】

本発明は上記事実を考慮して成されたもので、温度変化や製造プロセスのばらつきに起因する出力の変動を抑制できる半導体回路を得ることが目的である。

【課題を解決するための手段】

【0007】

上記目的を達成するために請求項1記載の発明に係る半導体回路は、第1ノードと第2ノードの間に設けられた半導体素子を備え、入力電流に応じて出力が変化すると共に、前記第2ノードに供給される参照電流に応じて定まる前記第2ノードの電圧が変化した場合も前記出力が変化する電子回路と、供給されたバイアス電圧のレベルに応じた参照電流を前記第2ノードに供給する参照電流用トランジスタを備えた参照電流供給手段と、温度及び前記半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧を前記参照電流用トランジスタへ供給するバイアス電圧発生手段と、を含んで構成されている。

【0008】

請求項1記載の発明に係る電子回路は、第1ノードと第2ノードの間に設けられた半導体素子を備え、入力電流に応じて出力(電圧又は電流)が変化すると共に、第2ノードに供給される参照電流又は第2ノードの電圧が変化した場合も出力が変化するように構成されている。なお、この電子回路としては、例えば請求項2に記載したように、入力端に入力電流が供給されると共に出力端が第1ノードに接続されたオペアンプと、第1ノードとオペアンプの入力端の間に設けられたダイオード素子と、入力端が第2ノードに接続された増幅器を備えると共に、半導体素子もダイオード素子で構成され、入力電流の対数値に比例する電圧を出力する電流電圧変換回路が好適であるが、入力電流に応じて出力(電圧又は電流)が変化すると共に、第2ノードに供給される参照電流又は第2ノードの電圧が変化した場合も出力が変化するものであれば、他の構成であってもよい。また、上記の電子回路は、例えば請求項3に記載したように、光電変換素子が接続され、光電変換素子の受光量に応じて光電変換素子を流れる電流が入力される構成が好適であるが、入力電流は他の電流であってもよい。また本発明において、任意のノードや端子への電流の「供給」には、任意のノードや端子へマイナスの電流(逆向きの電流)を供給する(される)ことも含まれる(以下同様)。

【0009】

また、請求項1記載の発明に係る電子回路は、温度が上昇するに従い、第1ノードと第2ノードの間に設けられた半導体素子のキャリア移動度が低下し閾値電圧が低下することで第2ノードの電圧が低下すると共に、半導体素子の製造プロセスのばらつきによっても閾値電圧が変動することで第2ノードの電圧が変動するが、当該電子回路は、前述のように入力電流に応じて出力が変化すると共に、第2ノードの電圧が変化した場合も出力が変化するので、温度変化や半導体素子の製造プロセスのばらつきによって出力(電圧又は電流)が変動することになる。

【0010】

これに対して請求項1記載の発明では、供給されたバイアス電圧のレベルに応じた参照電流を第2ノードに供給する参照電流用トランジスタを備えた参照電流供給手段が設けられており、バイアス電圧発生手段は、温度変化及び半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧を参照電流用トランジスタへ供給する。これにより、温度変化が生じた場合や、半導体素子の製造プロセスのばらつきが生じていた場合は、バイアス電圧発生手段から参照電流用トランジスタへ供給されるバイアス電圧のレベルが変化し、このバイアス電圧のレベルの変化に伴い参照電流用トランジスタによって第2ノードに供給される参照電流が変化し、この参照電流の変化に伴って第2ノードの電圧の変化が抑制される。従って、請求項1記載の発明によれば、温度変化や製造プロセスのばらつきに起因する出力の変動を抑制することができる。

【0011】

なお、請求項1記載の発明において、バイアス電圧発生手段は、例えば請求項4に記載したように、半導体素子と同一プロセスで形成された複数のバイアス電圧用トランジスタを、温度が上昇するに従ってバイアス電圧のレベルが低下し、製造プロセスのばらつきに伴い複数のバイアス電圧用トランジスタの閾値電圧が低下するに従ってバイアス電圧のレベルが低下するように接続して構成することができる。上記のように、バイアス電圧発生手段を複数のバイアス電圧用トランジスタで構成することで、温度変化に対して半導体素子と同様の特性変化(キャリア移動度の変化に伴う閾値電圧の変化等)を示すと共に、複数のバイアス電圧用トランジスタを半導体素子と同一プロセスで形成することで、製造プロセスのばらつきによる特性変化(閾値電圧の変化等)についても半導体素子と同様となるので、これら複数のバイアス電圧用トランジスタを接続してバイアス電圧発生手段を構成することで、温度変化及び半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧の発生を実現することができる。

【0012】

また、請求項1記載の発明において、参照電流供給手段は、参照電流用トランジスタとして単一のトランジスタを備えた構成であってもよいが、当該参照電流用トランジスタも製造プロセスのばらつきの影響を受け、製造プロセスのばらつきの影響で参照電流用トランジスタの閾値電圧が大きく変化した場合、参照用供給用トランジスタによって第2ノードに供給される参照電流も大きく変化することで、第2ノードの電圧の変化を精度良く抑制することが困難となる。これを考慮すると、参照電流供給手段は、例えば請求項5に記載したように、供給されたバイアス電圧のレベルに応じた参照電流を第2ノードに供給する参照電流用トランジスタを複数備えると共に、参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかを個々の参照電流用トランジスタ毎に切替可能な切替手段を備え、切替手段は、個々の参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかが、第2ノードの電圧が所定値に一致するように切替されることが好ましい。

【0013】

請求項5記載の発明では、複数の参照電流用トランジスタのうち、第2ノードに接続されている個々の参照電流用トランジスタが第2ノードに供給する参照電流の総和が第2ノードに供給される参照電流となるので、参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかを個々の参照電流用トランジスタ毎に切替えることで、第2ノードに供給する参照電流の大きさ、すなわち第2ノードの電圧を小さな変化幅で変化させることが可能となり、製造プロセスのばらつきの影響で個々の参照電流用トランジスタの閾値電圧が変化していたとしても、第2ノードの電圧の変化を精度良く抑制することが可能となる。

【0014】

また、請求項5記載の発明において、個々の参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかの切替えは、製造プロセスのばらつきに起因する第2ノードの電圧の変化を抑制することが目的であり、第2ノードの電圧が所定値に一致するように、個々の参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかを一旦切替えた後は、当該切替えを変更する必要はない。これを考慮すると、例えば請求項6に記載したように、参照電流用トランジスタを第2ノードに接続するか第2ノードから切り離すかを切替させる切替信号を、個々の参照電流用トランジスタ毎に切替手段に供給する切替信号供給手段を設け、切替信号供給手段から個々の参照電流用トランジスタ毎に切替手段に供給される切替信号が、第2ノードの電圧を測定した結果に基づきメタルトリミングによって設定されるようにしてもよい。

【0015】

本発明に係る半導体回路を複数製造した場合、個々の半導体回路における適正な切替信号が相違する可能性があるが、請求項6記載の発明では、第2ノードの電圧を測定した結果に基づきメタルトリミングによって切替信号が設定されるので、上記のような場合にも切替信号供給手段を一定の構成とすることができ、半導体回路の製造が容易になると共に、個々の半導体回路毎に相違する(可能性がある)切替信号を安定して切替手段に供給することができる。

【0016】

また、請求項6記載の発明において、切替手段は、例えば請求項7に記載したように、個々の参照電流用トランジスタに対応して設けられた複数のトランスファーゲートを備え、参照電流用トランジスタ毎に供給された切替信号が、対応するトランスファーゲートに各々入力される構成を採用することができる。

【発明の効果】

【0017】

以上説明したように本発明は、入力電流に応じて出力が変化すると共に第2ノードの電圧が変化した場合も出力が変化する電子回路に、供給されたバイアス電圧のレベルに応じた参照電流を第2ノードに供給する参照電流用トランジスタを備えた参照電流供給手段と、温度及び半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧を参照電流用トランジスタへ供給するバイアス電圧発生手段を設けたので、温度変化や製造プロセスのばらつきに起因する出力の変動を抑制できる、という優れた効果を有する。

【発明を実施するための最良の形態】

【0018】

以下、図面を参照して本発明の実施形態の一例を詳細に説明する。

【0019】

〔第1実施形態〕

図1には本第1実施形態に係る対数変換回路10が示されている。対数変換回路10は本発明に係る半導体回路に対応している。なお、本実施形態に係る対数変換回路は、光電変換素子によって周囲光の光量を検知してLCDのバックライトの輝度等の制御を行う照明制御回路の一部を構成しており、照明制御回路の一部としてLSI等の半導体集積回路に搭載されている。対数変換回路10はオペアンプ12を備え、オペアンプ12の反転入力端には、一端が接地され受光量に応じた光電流Iphを発生させる光電変換素子14の他端が接続されている。なお、光電変換素子14は請求項3に記載の光電変換素子に対応している。また、オペアンプ12の非反転入力端は図示しない定電圧電源に接続され、一定のバイアス電圧Vrefが供給される。またオペアンプ12の出力端はノードmに接続されている。ノードmは本発明に係る第1ノードに対応している。

【0020】

また、対数変換回路10は一対のNMOSトランジスタ16,18を備えており、NMOSトランジスタ16,18のゲート及びドレインはノードmに各々接続されている。NMOSトランジスタ16,18はサブスレッショルド領域で動作するように設計されており、ゲートとドレインが短絡されていることで、互いに同じ特性のダイオードとして各々機能する。NMOSトランジスタ16のソースはオペアンプ12の反転入力端に接続されている。NMOSトランジスタ16は請求項2に記載のダイオード素子に、オペアンプ12は請求項2に記載のオペアンプに各々対応しており、NMOSトランジスタ16及びオペアンプ12は、光電変換素子14で発生された光電流Iphを、光電流Iphの対数値に比例する電圧へ変換する対数変換/電流電圧変換部として機能する。

【0021】

一方、NMOSトランジスタ18のソースはノードcを介してオペアンプ20の非反転入力端に接続されている。ノードcは本発明に係る第2ノードに対応しており、NMOSトランジスタ18は本発明に係る半導体素子(より詳しくは請求項2に記載の「ダイオード素子で構成された半導体素子」)に対応している。オペアンプ20の反転入力端は抵抗22を介して接地されており、オペアンプ20の出力端は対数変換回路10の出力端OUTに接続され、また抵抗24を介してオペアンプ20の反転入力端にも接続されている。オペアンプ20及び抵抗22,24は電圧アンプとして機能し、請求項2に記載の増幅器に対応している。

【0022】

なお、上述したオペアンプ12,20、NMOSトランジスタ16,18及び抵抗22,24は本発明に係る電子回路(詳しくは請求項2に記載の電流電圧変換回路)に対応している。また本実施形態では、製造の容易さを考慮してNMOSトランジスタ16,18をダイオード素子として用いているが、本発明はこれに限られるものではなく、NMOSトランジスタ16,18に代えてダイオードを設けてもよい。

【0023】

また、ノードcにはNMOSトランジスタ26のドレインが接続されている。NMOSトランジスタ26は本発明に係る参照電流供給手段の参照電流用トランジスタに対応しており、ソースが接地され、ゲートにはバイアス電圧生成回路28が接続されている。バイアス電圧生成回路28は本発明に係るバイアス電圧発生手段(より詳しくは請求項4に記載のバイアス電圧発生手段)に対応しており、NMOSトランジスタ16,18と同一プロセスで形成された2個のPMOSトランジスタ30,32と2個のNMOSトランジスタ34,36を備えている。なお、これらのPMOSトランジスタ30,32及びNMOSトランジスタ34,36は、請求項4に記載の複数のバイアス電圧用トランジスタに対応しており、飽和領域で動作するようにサイズ(チャンネル幅(W)とチャンネル長(L)の比であるW/Lサイズ)が調整されている。また、PMOSトランジスタ30,32はW/Lサイズが同一とされている。

【0024】

バイアス電圧生成回路28のPMOSトランジスタ30,32はドレインが図示しない電源に各々接続され、ゲートが互いに接続されている。また、PMOSトランジスタ30のソースにはNMOSトランジスタ34のドレイン及びNMOSトランジスタ36のゲートが各々接続されており、PMOSトランジスタ32はゲートとソースが短絡されており、PMOSトランジスタ32のソースにはNMOSトランジスタ36のドレインが接続されている。また、NMOSトランジスタ34はゲートがノードgsに接続され、ソースが接地されており、NMOSトランジスタ36のソースもノードgsに接続されている。更に、ノードgsは一端が接地された抵抗38の他端が接続されていると共に、NMOSトランジスタ26のゲートに接続されている。

【0025】

次に、本第1実施形態に係る対数変換回路10の作用を説明する。対数変換回路10はノードcにNMOSトランジスタ26が接続され、このNMOSトランジスタ26のゲートにはバイアス電圧生成回路28によってバイアス電圧が供給されることで、対数変換回路10のノードcには、NMOSトランジスタ26のゲートに供給されたバイアス電圧のレベルに応じた参照電流Irefが流れる。このため、対数変換回路10の出力電圧Voは先の(2)式で表される値、すなわち光電流Iphの対数値に比例する値になり(但し、(2)式におけるAはオペアンプ20、抵抗22,24から成る電圧アンプの増幅度)、(2)式からも明らかなように、出力電圧V0の温度依存性はnK/q倍に低減される。

【0026】

ところで、本第1実施形態に係る対数変換回路10では、電圧降下によりノードcの電圧Vcがノードmの電圧Vmよりも低くなり、出力電圧V0はノードcの電圧Vcに応じて変化する。またNMOSトランジスタ16,18におけるキャリア移動度は温度によって変化し、温度が上昇するに従ってキャリア移動度が低下する一方、温度が下降するに従ってキャリア移動度が増大するが、このNMOSトランジスタ16,18におけるキャリア移動度の変化に応じてNMOSトランジスタ16,18の閾値電圧Vtが変化し、これに伴ってノードmの電圧Vm及びノードcの電圧Vcが変化する。このため、図13(B)に示す構成のように、ノードcを流れる参照電流Irefが一定の場合(参照電流Irefが温度や対数変換回路10(半導体集積回路)の製造プロセスの影響を受けない場合)は、図4に示すように、温度変化に対して電圧Vm,Vcが同じ変化を示すことで、一定の光電流Iphに対応する出力電圧V0が温度変化に対して大きく変動する。

【0027】

また、NMOSトランジスタ16,18の閾値電圧Vtは、対数変換回路10(半導体集積回路)の製造プロセスのばらつき(特に、NMOSトランジスタの閾値電圧Vtを規定するP型半導体の低濃度インプラ(イオン注入)のばらつき)によっても変化し、これに伴ってノードmの電圧Vm及びノードcの電圧Vcが変化するので、図13(B)に示す構成のようにノードcを流れる参照電流Irefが一定の場合(参照電流Irefが温度や製造プロセスの影響を受けない場合)は、図6に示すように、製造プロセスのばらつきに伴うNMOSトランジスタ16,18の閾値電圧Vtの変化に対して電圧Vm,Vcが同じ変化を示すことで、一定の光電流Iphに対応する出力電圧V0が温度変化に対して大きく変動する。

【0028】

これに対して本第1実施形態に係る対数変換回路10は、バイアス電圧生成回路28のPMOSトランジスタ30,32のW/Lサイズが同一とされ、PMOSトランジスタ30,32及びNMOSトランジスタ34,36が飽和領域で各々動作するように各トランジスタのW/L等が最適化されており、PMOSトランジスタ30を流れる電流I1=PMOSトランジスタ32を流れる電流I2で、かつ、NMOSトランジスタ34を流れる電流=PMOSトランジスタ30を流れる電流I1であるので、ノードGSの電圧(NMOSトランジスタ26のゲートに供給されるバイアス電圧)VGSはVGS=I1×Rとなる(但しRは抵抗38の電気抵抗)。そして電流I1をNMOSトランジスタ34のパラメータ(キャリア移動度μ、ゲート絶縁膜容量Cox、チャンネル幅W、チャンネル長L、ゲート電圧(=NMOSトランジスタ26のゲートに供給されるバイアス電圧)VGS、閾値電圧Vt)を用いて表すと、次の(3)式のようになる。

I1=1/2・μ・Cox・W/L・(VGS−Vt)2 …(3)

なお、本第1実施形態に係る対数変換回路10において、一例として、温度が所定値かつ閾値電圧Vtが設計値(Typical)の条件での電流I1,I2=5μAとしたい場合には、例えばPMOSトランジスタ30,32のW/L=15μm/2μm、NMOSトランジスタ34,36のW/L=5μm/5μm、抵抗38の電気抵抗値R=180kΩに調整することで実現することができる。

【0029】

ここで、温度が上昇しNMOSトランジスタ34のキャリア移動度μが低下すると、上記の(3)式で表される電流I1が減少することで、図2にも示すように、NMOSトランジスタ34のゲート電圧(バイアス電圧)VGSが低下される。また、温度が低下しNMOSトランジスタ34のキャリア移動度μが増大すると、上記の(3)式で表される電流I1が増大することで、図2にも示すように、NMOSトランジスタ34のゲート電圧(バイアス電圧)VGSが上昇される。

【0030】

また、バイアス電圧生成回路28のPMOSトランジスタ30,32及びNMOSトランジスタ34,36は、NMOSトランジスタ16,18と同一プロセスで形成されているので、製造プロセスのばらつきによりNMOSトランジスタ16,18の閾値電圧Vtが設計値より低下している場合は、NMOSトランジスタ34,36の閾値電圧Vtも同様に設計値より低下していることになり、図2に"Vt:Low"と表記して示すようにバイアス電圧VGSも低下される。また、製造プロセスのばらつきによりNMOSトランジスタ16,18の閾値電圧Vtが設計値よりも上昇している場合は、NMOSトランジスタ34,36の閾値電圧Vtも同様に設計値よりも上昇していることになり、図2に"Vt:High"と表記して示すようにバイアス電圧VGSも上昇される。

【0031】

NMOSトランジスタ26のゲートには、バイアス電圧生成回路28で発生されたバイアス電圧VGS、すなわち温度変化及び製造プロセスのばらつきに伴う閾値電圧Vtの変化に対して図2に示すように変化するバイアス電圧VGSが供給される。これにより、温度が上昇した場合は、バイアス電圧VGSが低下されることでノードcを流れる参照電流IrefがNMOSトランジスタ26によって低下され、温度上昇に起因するノードcの電圧Vcの低下幅は参照電流Irefの低下分だけ小さくなる。また、温度が低下した場合は、バイアス電圧VGSが上昇されることでノードcを流れる参照電流IrefがNMOSトランジスタ26によって増大され、温度低下に起因するノードcの電圧Vcの増加幅は参照電流Irefの増大分だけ小さくなる。従って、本第1実施形態に係る対数変換回路10では、図3に示すように、温度変化に対するノードcの電圧Vcの変動が抑制され、一定の光電流Iphに対応する出力電圧V0が温度変化の影響で変動することを抑制することができる。

【0032】

また、製造プロセスのばらつきに伴ってNMOSトランジスタ16,18の閾値電圧Vtが設計値より低下していた場合は、バイアス電圧VGSが低下されることでノードcを流れる参照電流IrefがNMOSトランジスタ26によって低下され、閾値電圧Vtの低下に起因するノードcの電圧Vcの低下幅は参照電流Irefの低下分だけ小さくなる。また、製造プロセスのばらつきに伴ってNMOSトランジスタ16,18の閾値電圧Vtが設計値より上昇していた場合は、バイアス電圧VGSが上昇されることでノードcを流れる参照電流IrefがNMOSトランジスタ26によって増大され、閾値電圧Vtの低下に起因するノードcの電圧Vcの増加幅は参照電流Irefの増大分だけ小さくなる。従って、本第1実施形態に係る対数変換回路10では、図5に示すように、製造プロセスのばらつきに伴う閾値電圧Vtの変動に対するノードcの電圧Vcの変動が抑制され、一定の光電流Iphに対応する出力電圧V0が、製造プロセスのばらつきに伴う閾値電圧の変動の影響で変動することも抑制することができる。

【0033】

〔第2実施形態〕

次に本発明の第2実施形態について説明する。なお、第1実施形態と同一の部分には同一の符号を付し、説明を省略する。図7には、本第2実施形態に係る対数変換回路50が示されている。この対数変換回路50も本発明に係る半導体回路に対応している。対数変換回路50では、第1実施形態で説明した対数変換回路10に対して3個のNMOSトランジスタ52,54,56が追加されている。NMOSトランジスタ52,54,56は、ドレインが切替部58を介してノードcに各々接続され、ソースが各々接地され、ゲートがバイアス電圧生成回路28に各々接続されており、NMOSトランジスタ52,54,56のゲートには、NMOSトランジスタ26と同様にバイアス電圧生成回路28からバイアス電圧VGSが供給される。なお、NMOSトランジスタ52,54,56は請求項5に記載の複数の参照電流用トランジスタに対応している。

【0034】

切替部58は3個のトランスファーゲート60,62,64を備えており、トランスファーゲート60はNMOSトランジスタ52のドレインとノードcの間に、トランスファーゲート62はNMOSトランジスタ54のドレインとノードcの間に、トランスファーゲート64はNMOSトランジスタ56のドレインとノードcの間に各々設けられている。トランスファーゲート60のゲートtg1,tg1_b、トランスファーゲート62のゲートtg2,tg2_b、及び、トランスファーゲート64のゲートtg3,tg3_bは切替信号供給部66に各々接続されており、トランスファーゲート60,62,64は切替信号供給部66から個々のゲートに供給された切替信号に応じてオン状態(導通状態)又はオフ状態(非導通状態)に切り替わる。

【0035】

なお、本第2実施形態では、トランスファーゲート60,64として、ゲートtg1,tg3に供給される切替信号がハイレベル、ゲートtg1_b,tg3_bに供給される切替信号がローレベルのときにオン状態となり、ゲートtg1,tg3に供給される切替信号がローレベル、ゲートtg1_b,tg3_bに供給される切替信号がハイレベルのときにオフ状態となるトランスファーゲートを用いている一方、トランスファーゲート62としては、ゲートtg2に供給される切替信号がローレベル、ゲートtg2_bに供給される切替信号がハイレベルのときにオン状態となり、ゲートtg2に供給される切替信号がハイレベル、ゲートtg2_bに供給される切替信号がローレベルのときにオフ状態となるトランスファーゲートを用いている。切替部58は請求項5に記載の切替手段に対応しており、トランスファーゲート60,62,64は請求項7に記載の複数のトランスファーゲートに対応している。

【0036】

図8に示すように、切替信号供給部66は個々のトランスファーゲート60,62,64に対応する3個の切替信号生成回路68A〜68Cを備えている。個々の切替信号生成回路68は2個のNOT回路70,72を備えている。NOT回路70の入力端には、ドレインが図示しない電源に接続されゲートが接地されたPMOSトランジスタ74のソースと、抵抗76の一端が各々接続されている。抵抗76の他端は、外部に露出しておりメタルトリミングによって切断することが可能なフューズ78の一端に接続されており、フューズ78の他端は接地されている。またNOT回路70の出力端は、ゲートtgi_bに供給する切替信号tgi_b(但しi=1〜3)を出力するための信号出力端と、NOT回路72の入力端に各々接続されており、NOT回路72の出力端はゲートtgiに供給する切替信号tgi(但しi=1〜3)を出力するための信号出力端に接続されている。

【0037】

上記構成により、個々の切替信号生成回路68は、フューズ78が未切断の状態では切替信号tgiとしてローレベル、切替信号tgi_bとしてハイレベルの信号が出力され、メタルトリミングによってフューズ78が切断された状態では切替信号tgiとしてハイレベル、切替信号tgi_bとしてローレベルの信号が出力される。なお、切替信号供給部66は請求項6に記載の切替信号供給手段に対応している。

【0038】

次に本第2実施形態の作用について、第1実施形態と異なる部分のみ説明する。第1実施形態で説明した対数変換回路10は、参照電流用トランジスタとして単一のNMOSトランジスタ26が設けられているが、このNMOSトランジスタ26も製造プロセスのばらつきの影響を受けて閾値電圧Vtが変動するので、製造プロセスのばらつきの影響でNMOSトランジスタ16,18,26の閾値電圧Vtが大きく変動した場合には、バイアス電圧生成回路28によるバイアス電圧VGSの変更に拘わらず参照電流Irefが設計値に対して大きくずれることで、例として図10に矢印で示すように、ノードcの電圧Vcが設計値に対して大きくずれ、これに伴って出力電圧V0も設計値に対して大きくずれてしまうという問題が生ずる。

【0039】

これに対して本第2実施形態に係る対数変換回路50では、参照電流用トランジスタとして、NMOSトランジスタ26に加えてNMOSトランジスタ52,54,56が設けられており、NMOSトランジスタ26を流れる電流をIr0、NMOSトランジスタ52を流れる電流をIr1、NMOSトランジスタ54を流れる電流をIr2、NMOSトランジスタ56を流れる電流をIr3とすると、参照電流IrefはIref=Ir0+Ir1+Ir2+Ir3となる。また、NMOSトランジスタ52,54,56とノードcとの間には、切替信号供給部66から供給された切替信号に応じてオン状態(導通状態)又はオフ状態(非導通状態)に切り替わるトランスファーゲート60,62,64が設けられているので、トランスファーゲート60,62,64に供給する切替信号のレベルを切替えることで、NMOSトランジスタ52,54,56を流れる電流Ir1,Ir2,Ir3を互いに独立にオンオフすることができる。

【0040】

なお、本第2実施形態に係る切替信号供給部66の個々の切替信号生成回路68A〜68Cは、当初は何れもフューズ78が未切断の状態であるので、切替信号供給部66からは切替信号tgiとしてローレベル、切替信号tgi_bとしてハイレベルの信号が出力され、トランスファーゲート60,62,64のうちトランスファーゲート62のみオン状態となっている。従って、参照電流Irefは当初はIref=Ir0+Ir2となっている。

【0041】

本第2実施形態では、対数変換回路50を搭載した半導体集積回路を製造した後、製造した半導体集積回路を出荷する前に、以下の調整作業が行われる。この調整作業では、まず、温度を規定値に維持すると共に、一定光量の光を光電変換素子14に照射することで光電変換素子14で一定の光電流Iphが発生させた状態で、ノードcの電圧Vcが測定される。次に、電圧Vcの測定値と設計値との偏差に基づいて、トランスファーゲート60,62,64のオンオフの状態の切替えが必要か否かが判断される。前記偏差が許容範囲内であれば、トランスファーゲート60,62,64のオンオフの状態の切替えは不要と判断されて作業終了となるが、前記偏差が許容範囲を超えている場合は、トランスファーゲート60,62,64のオンオフの状態の切替えが必要と判断され、電圧Vcの測定値と設計値との偏差を小さくするためには何れのトランスファーゲートのオンオフの状態を切替えるべきかが判断され、オンオフの状態を切替えるトランスファーゲートに対応する切替信号生成回路68のフューズ78をメタルトリミングによって切断する作業が行われる。

【0042】

上記のように、本第2実施形態では参照電流Irefを調整することでノードcの電圧Vcを調整しているが、一般に電圧Vと電流IにはV=logIの関係があるため、トランスファーゲート60,62,64の各々のオンオフの状態の組み合わせを切替える(切替信号生成回路68A〜68Cのフューズ78の切断/非切断の組み合わせを選択する)ことで、参照電流Irefが指数関数的に変化するように、NMOSトランジスタ52,54,56のサイズ(W/Lサイズ)の組み合わせが予め設定されている。なお、次の表1には、

個々の切替信号生成回路68のフューズ78の切断/非切断を選択することで、各トランスファーゲートのオンオフの状態の組み合わせを切替えた場合の参照電流Irefの変化の一例を示す。

【0043】

【表1】

【0044】

このように、各トランスファーゲートのオンオフの状態の組み合わせの切替えに対して参照電流Irefが指数関数的に変化するように構成することで、各トランスファーゲートのオンオフの状態の組み合わせの切替えに対して電圧Vcがおよそ一定の変化幅で変化するので(図9も参照)、電圧Vcを設計値に一致、又は、設計値との偏差が非常に小さい値へ調整することを容易に実現することができる。従って、製造プロセスのばらつきの影響でNMOSトランジスタ16,18,26の閾値電圧Vtが大きく変動し、出力電圧V0が設計値に対して大きくずれてしまっていた場合にも、上記の調整作業を行うことで、例として図11にも示すように、出力電圧V0を設計値に一致、又は、設計値との偏差が非常に小さい値へ調整することができる。

【0045】

また、上記の調整作業を一旦行った後は、各トランスファーゲートのオンオフの状態を切替える必要はなく、また、温度変化に対するノードcの電圧Vcの変動は、NMOSトランジスタ26,52,54,56のゲートに各々供給されるバイアス電圧VGSが、第1実施形態で説明したバイアス電圧生成回路28によって温度変化に応じて調整されることで抑制されるので、対数変換回路50を搭載した半導体集積回路の出荷後に、ユーザが出力電圧V0等を調整する作業を行う必要もなくなる。

【0046】

なお、上記では本発明に係る半導体素子としてNMOSトランジスタ18を、請求項2に記載のダイオード素子としてNMOSトランジスタ16を、本発明に係る参照電流用トランジスタとしてNMOSトランジスタ26を各々適用した態様を説明したが、本発明はこれに限定されるものではない。例として図12には、第1実施形態で説明した対数変換回路10に対し、本発明に係る半導体素子をPMOSトランジスタ44に、請求項2に記載のダイオード素子をPMOSトランジスタ42に、本発明に係る参照電流用トランジスタをNMOSトランジスタ46に各々置き換えた構成の対数変換回路40を示す。図12に示すように、本発明に係る半導体素子、請求項2に記載のダイオード素子及び本発明に係る参照電流用トランジスタはPMOSトランジスタで構成することも可能である。また、第2実施形態で説明した対数変換回路50のNMOSトランジスタ52,54,56についても、同様にPMOSトランジスタへ置き換え可能であることは言うまでもない。

【0047】

また、上記では本発明に係る半導体回路として、光電変換素子14で発生された光電流Iphに対して対数変換及び電流電圧変換を行う対数変換回路10,40,50を例に説明したが、本発明に係る半導体回路のうちの電子回路は、入力電流に応じて出力が変化すると共に、第2ノードに供給される参照電流に応じて定まる第2ノードの電圧が変化した場合も出力が変化する構成であればよく、例えば光電流Iphに対して対数変換のみを行い光電流Iphの対数値に比例する電流を出力する構成の変換回路に本発明を適用することも可能であり、入力電流も光電流Iphに限られるものではない。

【図面の簡単な説明】

【0048】

【図1】第1実施形態に係る対数変換回路の回路図である。

【図2】温度変化及び製造プロセスのばらつきに起因する閾値電圧Vtの変化に対する、バイアス電圧生成回路によって生成されるバイアス電圧Vgsの変化を示す線図である。

【図3】本実施形態に係る対数変換回路における温度変化に対する出力電圧V0の変化を示す線図である。

【図4】従来の対数変換回路における温度変化に対する出力電圧V0の変化を示す線図である。

【図5】本実施形態に係る対数変換回路における、製造プロセスのばらつきに起因する閾値電圧Vtの変化に対する出力電圧V0の変化を示す線図である。

【図6】従来の対数変換回路における、製造プロセスのばらつきに起因する閾値電圧Vtの変化に対する出力電圧V0の変化を示す線図である。

【図7】第2実施形態に係る対数変換回路の回路図である。

【図8】第2実施形態に係る切替信号供給部の回路図である。

【図9】切替信号の変更(メタルトリミング)による電流Iref及び電圧Vcの変化を示す線図である。

【図10】製造プロセスのばらつきに起因する、設計値からの出力電圧V0のずれを示す線図である。

【図11】メタルトリミングによる出力電圧V0のずれの修正を説明するための線図である。

【図12】対数変換回路の他の構成を示す回路図である。

【図13】(A)及び(B)は電流電圧変換及び対数変換を行う変換回路の従来の構成を各々示す回路図である。

【符号の説明】

【0049】

10 対数変換回路

12 オペアンプ

14 光電変換素子

16 NMOSトランジスタ

18 NMOSトランジスタ

26 NMOSトランジスタ

28 バイアス電圧生成回路

30 PMOSトランジスタ

32 PMOSトランジスタ

34 NMOSトランジスタ

36 NMOSトランジスタ

38 抵抗

40 対数変換回路

42 PMOSトランジスタ

44 PMOSトランジスタ

46 PMOSトランジスタ

50 対数変換回路

52 NMOSトランジスタ

54 NMOSトランジスタ

56 NMOSトランジスタ

58 切替部

60 トランスファーゲート

62 トランスファーゲート

64 トランスファーゲート

66 切替信号供給部

68A〜68C 切替信号生成回路

78 フューズ

【特許請求の範囲】

【請求項1】

第1ノードと第2ノードの間に設けられた半導体素子を備え、入力電流に応じて出力が変化すると共に、前記第2ノードに供給される参照電流に応じて定まる前記第2ノードの電圧が変化した場合も前記出力が変化する電子回路と、

供給されたバイアス電圧のレベルに応じた参照電流を前記第2ノードに流す参照電流用トランジスタを備えた参照電流供給手段と、

温度変化及び前記半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧を前記参照電流用トランジスタへ供給するバイアス電圧発生手段と、

を含む半導体回路。

【請求項2】

前記電子回路は、入力端に入力電流が供給されると共に出力端が前記第1ノードに接続されたオペアンプと、前記第1ノードと前記オペアンプの前記入力端の間に設けられたダイオード素子と、入力端が前記第2ノードに接続された増幅器を備えると共に、前記半導体素子もダイオード素子で構成され、入力電流の対数値に比例する電圧を出力する電流電圧変換回路であることを特徴とする請求項1記載の半導体回路。

【請求項3】

前記電子回路には光電変換素子が接続され、前記光電変換素子の受光量に応じて前記光電変換素子を流れる電流が入力されることを特徴とする請求項1記載の半導体回路。

【請求項4】

前記バイアス電圧発生手段は、前記半導体素子と同一プロセスで形成された複数のバイアス電圧用トランジスタが、温度が上昇するに従って前記バイアス電圧のレベルが低下し、前記製造プロセスのばらつきに伴い前記複数のバイアス電圧用トランジスタの閾値電圧が低下するに従って前記バイアス電圧のレベルが低下するように接続されて構成されていることを特徴とする請求項1記載の半導体回路。

【請求項5】

前記参照電流供給手段は、供給されたバイアス電圧のレベルに応じた参照電流を前記第2ノードに供給する前記参照電流用トランジスタを複数備えると共に、前記参照電流用トランジスタを前記第2ノードに接続するか前記第2ノードから切り離すかを個々の前記参照電流用トランジスタ毎に切替可能な切替手段を備え、

前記切替手段は、個々の前記参照電流用トランジスタを前記第2ノードに接続するか前記第2ノードから切り離すかが、前記第2ノードの電圧が所定値に一致するように切替されることを特徴とする請求項1記載の半導体回路。

【請求項6】

前記参照電流用トランジスタを前記第2ノードに接続するか前記第2ノードから切り離すかを切替させる切替信号を、個々の前記参照電流用トランジスタ毎に前記切替手段に供給する切替信号供給手段を更に備え、前記切替信号供給手段から個々の前記参照電流用トランジスタ毎に前記切替手段に供給される切替信号は、前記第2ノードの電圧を測定した結果に基づきメタルトリミングによって設定されることを特徴とする請求項5記載の半導体回路。

【請求項7】

前記切替手段は、個々の前記参照電流用トランジスタに対応して設けられた複数のトランスファーゲートを備え、前記参照電流用トランジスタ毎に供給された切替信号は、対応するトランスファーゲートに各々入力されることを特徴とする請求項6記載の半導体回路。

【請求項1】

第1ノードと第2ノードの間に設けられた半導体素子を備え、入力電流に応じて出力が変化すると共に、前記第2ノードに供給される参照電流に応じて定まる前記第2ノードの電圧が変化した場合も前記出力が変化する電子回路と、

供給されたバイアス電圧のレベルに応じた参照電流を前記第2ノードに流す参照電流用トランジスタを備えた参照電流供給手段と、

温度変化及び前記半導体素子の製造プロセスのばらつきに応じてレベルが変化するバイアス電圧を前記参照電流用トランジスタへ供給するバイアス電圧発生手段と、

を含む半導体回路。

【請求項2】

前記電子回路は、入力端に入力電流が供給されると共に出力端が前記第1ノードに接続されたオペアンプと、前記第1ノードと前記オペアンプの前記入力端の間に設けられたダイオード素子と、入力端が前記第2ノードに接続された増幅器を備えると共に、前記半導体素子もダイオード素子で構成され、入力電流の対数値に比例する電圧を出力する電流電圧変換回路であることを特徴とする請求項1記載の半導体回路。

【請求項3】

前記電子回路には光電変換素子が接続され、前記光電変換素子の受光量に応じて前記光電変換素子を流れる電流が入力されることを特徴とする請求項1記載の半導体回路。

【請求項4】

前記バイアス電圧発生手段は、前記半導体素子と同一プロセスで形成された複数のバイアス電圧用トランジスタが、温度が上昇するに従って前記バイアス電圧のレベルが低下し、前記製造プロセスのばらつきに伴い前記複数のバイアス電圧用トランジスタの閾値電圧が低下するに従って前記バイアス電圧のレベルが低下するように接続されて構成されていることを特徴とする請求項1記載の半導体回路。

【請求項5】

前記参照電流供給手段は、供給されたバイアス電圧のレベルに応じた参照電流を前記第2ノードに供給する前記参照電流用トランジスタを複数備えると共に、前記参照電流用トランジスタを前記第2ノードに接続するか前記第2ノードから切り離すかを個々の前記参照電流用トランジスタ毎に切替可能な切替手段を備え、

前記切替手段は、個々の前記参照電流用トランジスタを前記第2ノードに接続するか前記第2ノードから切り離すかが、前記第2ノードの電圧が所定値に一致するように切替されることを特徴とする請求項1記載の半導体回路。

【請求項6】

前記参照電流用トランジスタを前記第2ノードに接続するか前記第2ノードから切り離すかを切替させる切替信号を、個々の前記参照電流用トランジスタ毎に前記切替手段に供給する切替信号供給手段を更に備え、前記切替信号供給手段から個々の前記参照電流用トランジスタ毎に前記切替手段に供給される切替信号は、前記第2ノードの電圧を測定した結果に基づきメタルトリミングによって設定されることを特徴とする請求項5記載の半導体回路。

【請求項7】

前記切替手段は、個々の前記参照電流用トランジスタに対応して設けられた複数のトランスファーゲートを備え、前記参照電流用トランジスタ毎に供給された切替信号は、対応するトランスファーゲートに各々入力されることを特徴とする請求項6記載の半導体回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2009−272979(P2009−272979A)

【公開日】平成21年11月19日(2009.11.19)

【国際特許分類】

【出願番号】特願2008−123001(P2008−123001)

【出願日】平成20年5月9日(2008.5.9)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【Fターム(参考)】

【公開日】平成21年11月19日(2009.11.19)

【国際特許分類】

【出願日】平成20年5月9日(2008.5.9)

【出願人】(308033711)OKIセミコンダクタ株式会社 (898)

【Fターム(参考)】

[ Back to top ]