半導体基板の表面処理方法、半導体基板、及び薄膜形成方法

【課題】半導体基板上への薄膜形成工程(例えば、エピタキシャル成長工程)直前に、簡単な前処理を行うだけで、半導体基板上に良質な半導体薄膜を形成可能な技術を提供する。

【解決手段】1又は2以上の結晶層を有する半導体基板11の最表層の表面を、当該最表層の熱分解温度より低い熱分解温度を有する材料からなる被覆膜12で被覆し、この状態でウェハ容器に収容し保管する。そして、この被覆膜12が形成された半導体基板1をウェハ容器から取り出し、被覆膜12を熱分解により当該半導体基板11表面から除去してから、薄膜形成工程13を行う。

【解決手段】1又は2以上の結晶層を有する半導体基板11の最表層の表面を、当該最表層の熱分解温度より低い熱分解温度を有する材料からなる被覆膜12で被覆し、この状態でウェハ容器に収容し保管する。そして、この被覆膜12が形成された半導体基板1をウェハ容器から取り出し、被覆膜12を熱分解により当該半導体基板11表面から除去してから、薄膜形成工程13を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体基板上に半導体薄膜を形成する際のプロセス技術に関し、特に、半導体基板の表面処理方法、表面処理された半導体基板、及び表面処理された半導体基板を用いた薄膜形成方法に関する。

【背景技術】

【0002】

従来、半導体基板上に半導体薄膜を形成する方法として、有機金属気相成長(MOCVD:Metal Organic Chemical Vapor Deposition)法、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法が知られている(例えば、特許文献1、2)。これらの方法は、半導体基板表面に必要な原料を導入し、化学的或いは物理的に薄膜を形成する方法である。

例えば、レーザ或いはトランジスタといった半導体デバイスを作製する場合、上記MOCVD法やMBE法により、半導体基板上に必要な半導体結晶薄膜を重ねて成長することが行われる(例えば、ヘテロ構造を有するエピタキシャル結晶の積層構造)。

【0003】

上述した半導体薄膜の形成に用いられる半導体基板(例えば、GaAs基板等)は、ウェハに加工された後、すぐに薄膜形成装置に投入されるわけではなく、所定の保管ケース内に収容され保管される。このとき、収容された半導体基板は、保管雰囲気や保管ケースからの影響を受け、保管期間の経過に伴って表面に不純物(例えば、Si、O、C、S等)が付着することがある。このような半導体基板表面に存在する不純物は、半導体基板上に形成される半導体薄膜の特性に影響を与えるため、できる限り少なく、かつ、安定に制御されている必要がある。

【0004】

従来は、MOCVD装置やMBE装置等の薄膜形成装置に半導体基板を投入する前に、その表面を酸などでエッチングしたり、薄膜形成装置に投入した後に水素ガス或いは真空中で熱処理を行ったりするなどして、半導体基板表面の清浄化或いは安定化が図られている。

【特許文献1】特開2001−302389号公報

【特許文献2】WO2005/006421号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、半導体基板表面に熱処理を施す方法では、薄膜形成装置の装置上の制約によっては、不純物が十分に除去できないという問題がある。また、半導体基板表面にエッチング処理を施す方法では、半導体基板上に薄膜を形成する工程の直前にエッチング工程を設けて表面をエッチングしなければならないことによる負担、エッチング条件の安定化に関する負荷、使用済み廃液の処理などの問題がある。

【0006】

本発明は、半導体基板上への薄膜形成工程(例えば、エピタキシャル成長工程)直前に、簡単な前処理を行うだけで、半導体基板上に良質な半導体薄膜を形成可能な技術を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するため、請求項1に記載の発明は、1又は2以上の結晶層を有する半導体基板の表面処理方法において、

前記半導体基板の最表層の表面を、当該最表層の熱分解温度より低い熱分解温度を有する材料からなる被覆膜で被覆することを特徴とする。

すなわち、基板表面を保護するために、半導体基板の最表層より低い温度で熱分解する材料、好ましくは、大気中、不活性ガス中若しくは真空中で安定な材料からなる被覆膜を最表層表面に予め形成するようにしている。

【0008】

ここで、1又は2以上の結晶層を有する半導体基板とは、単一の半導体材料からなる基板及びこの基板上にエピタキシャル成長等により1以上の結晶層を形成された基板を含むことを意味する。つまり、半導体基板の最表層とは、単一の半導体材料からなる基板の場合は当該基板であり、基板上に1以上の結晶層が形成されている場合は最上位の結晶層である。

また、最表層の熱分解温度とは、最表層の構成成分の1つの分圧が1×10−5Torrを超える温度とする。

【0009】

これにより、半導体基板を保管している間に、保管される環境によって最表層表面が汚染されるのを防止することができる。また、被覆膜は、半導体基板の最表層の熱分解温度より低い熱分解温度を有する材料からなるので、エピタキシャル薄膜や絶縁膜の形成プロセスで通常実施されている薄膜形成前の熱処理(サーマルエッチング:表面酸化層を除去する工程)の過程で容易に除去することができる。

したがって、半導体基板を薄膜形成装置に投入するまでの保管期間に、保管環境によって基板表面(被覆膜表面)が不純物で汚染されても、この不純物を効果的に除去できる。その結果、半導体基板上にエピタキシャル層や絶縁膜層等の薄膜を形成する工程において、半導体基板表面の不純物量を安定に制御することができる。

【0010】

請求項2に記載の発明は、請求項1に記載の半導体基板の表面処理方法において、前記被覆膜の厚みは、当該被覆膜材料の1分子層以上10分子層以下であることを特徴とする。

被覆膜の厚みは、半導体基板表面をくまなく覆うために1分子層以上を必要とする。一方、薄膜形成プロセスで通常行われる薄膜形成前の熱処理で被覆膜を除去するため、厚すぎると工程が無駄に長くなり実用的ではない。そこで、従来の熱処理時間に過度の負担を加えない範囲として10分子層以下とする。

好ましくは、1分子層以上5分子層以下、さらに好ましくは、1分子層以上3分子層以下とする。例えば、被覆する材料がInAsエピタキシャル層である場合は、1分子層は6Åであるから、6Å以上60Å以下、好ましくは6Å以上30Å以下、さらに好ましくは6Å以上18Å以下となる。

【0011】

請求項3に記載の発明は、請求項1又は2に記載の半導体基板の表面処理方法において、前記被覆膜は、前記最表層と同族系元素で構成されていることを特徴とする。

ここで、同族系元素とは、例えば、最表層がGaAs化合物半導体であればIII−V族系化合物半導体(例えば、InAs等)であり、被覆膜が熱分解されることにより発生する元素が最表層を汚染する虞のない元素であることを意味する。

これにより、薄膜形成前の熱処理により被覆膜を分解しても、半導体基板の最表層表面が再汚染される虞はないので、半導体基板表面の不純物量を安定に制御することができる。

【0012】

請求項4に記載の発明は、請求項1から3のいずれか一項に記載の半導体基板の表面処理方法において、前記最表層はGaAs単結晶層であり、前記被覆膜材料はInAsであることを特徴とする。

これにより、InAs被覆膜が分解されることにより発生する元素(In、As)によりGaAs単結晶層表面が再汚染される虞はないので、薄膜形成前に行われる熱処理で半導体基板に影響を与えることなくInAs被覆膜は除去される。

【0013】

請求項5に記載の発明は、請求項4に記載の半導体基板の表面処理方法において、前記被覆膜は、InAsからなるエピタキシャル成長層であることを特徴とする。

すなわち、InAs被覆膜は、形成方法の一例として一般的なエピタキシャル成長方法を利用でき、被覆膜を形成するにあたり特別な方法を要するわけではない。エピタキシャル成長方法を利用することにより、被覆膜の厚みを容易に制御することができる。

【0014】

請求項6に記載の発明は、請求項1から5のいずれか一項に記載の表面処理方法により表面処理されていることを特徴とする半導体基板である。

このようにして被覆膜を形成された半導体基板は、薄膜形成前の熱処理により容易に被覆膜を除去でき、最表層表面の不純物を低減できるとともに安定して制御できるので、薄膜形成用の半導体基板として好適である。

【0015】

請求項7に記載の発明は、請求項6に記載の半導体基板を用いて、上記被覆膜を熱分解により当該半導体基板表面から除去してから、薄膜形成工程を行うことを特徴とする薄膜形成方法である。

このように、被覆膜を形成された半導体基板を薄膜形成用の基板として用い、この半導体基板から被覆膜を除去した後に薄膜形成工程を行うことにより、半導体基板表面の不純物は低減されるとともに安定して制御されるので、この半導体基板上に形成される薄膜は不純物により悪影響を受けることなく、高品質なものとなる。

【発明の効果】

【0016】

本発明によれば、半導体基板(基板上にエピタキシャル層を形成された基板を含む)の最表層に被覆膜を形成するので、薄膜形成前に半導体基板を保管する間に、表面状態を保護し、安定な状態に保つことができる。したがって、本発明に係る半導体基板の表面処理方法、半導体基板、及び薄膜形成方法は、高品質な薄膜を形成するのに極めて有用である。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施の形態を図面に基づいて説明する。

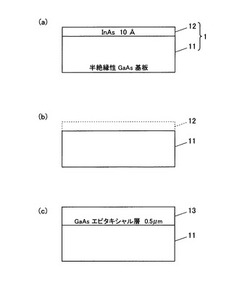

図1は、被覆膜付きの半導体基板を用いた薄膜形成プロセスにおける遷移状態を示す説明図である。本実施形態では、単一の材料からなる半絶縁性GaAs単結晶基板を用いた場合について示している。

【0018】

図1(a)に示すように、被覆膜付きの半導体基板1は、半絶縁性GaAs単結晶基板11の上に、InAs被覆膜12が形成されてなる。InAs被覆膜12の厚さは、例えば10Åである。この厚さは、InAsの1分子層の厚さは6Åなので、約1.67分子層に相当する。

このように、InAs被覆膜12の厚みを1分子層以上10分子層以下とすることで、薄膜形成プロセスで通常行われる薄膜形成前の熱処理(サーマルエッチング)によりInAs被覆膜12は容易に除去される。また、1分子層以上であれば半導体基板表面を保護する機能を発揮するので、熱処理時間に過度の負担を加えないように、1分子層以上10分子層以下、好ましくは、1分子層以上5分子層以下、さらに好ましくは、1分子層以上3分子層以下とする。

【0019】

GaAs単結晶基板を用いる場合、GaAsは熱分解温度が約700℃であるので、それより低い熱分解温度の材料が被覆膜の材料として選定される。GaAs単結晶基板が劣化することなく、被覆膜を熱分解して除去するためである。

また、被覆膜が熱分解されることにより発生する元素が最表層(ここでは、GaAs単結晶基板)を汚染する虞のない元素となるように被覆膜の材料が選定される。

そこで、本実施形態では、熱分解温度が約500℃のInAsを被覆膜12の材料としている。なお、最表層がGaAsである場合の被覆膜材料はInAsに限定されず、熱分解温度がGaAsよりも低く、同族系の元素で構成される材料であればよい。

【0020】

図1(a)に示す被覆膜付きの半導体基板1は、例えば、GaAs単結晶基板11の製造工程の最終処理(研磨、エッチングなど)終了後、GaAs単結晶基板11を直ちにMBE結晶成長装置に投入し、基板温度400℃でIn源及びAs源を同時照射して、InAsエピタキシャル膜を10Å(1分子層=6Å)成長させることにより作製される。

エピタキシャル成長方法を利用してInAs被覆膜12を形成することにより、厚さは正確に制御される。

【0021】

被覆膜付きの半導体基板1は、所定のウェハ容器に収容され、所定の期間保管される。その後、薄膜形成装置に投入され、所望の薄膜を形成するのに用いられる。例えば、半導体基板1上には、エピタキシャル層や絶縁膜層等の薄膜が形成される。

【0022】

図1(b)に示すように、薄膜形成工程では、まず、熱処理(サーマルエッチング)によりInAs被覆膜12を除去する。InAsの熱分解温度が500℃でGaAsの熱分解温度が700℃なので、例えば、熱処理温度を650℃とすれば、GaAs単結晶基板11が熱分解することなく、InAs被覆膜12だけを熱分解して除去することができる。このとき、熱分解により、InやAsが発生するが、これらはGaAsと同族系の元素なので、GaAs単結晶基板11を汚染する虞はない。

【0023】

次いで、図1(c)に示すように、GaAs単結晶基板11上に、例えば、GaAsエピタキシャル層を形成する。GaAs単結晶基板11とGaAsエピタキシャル層13との界面には残存する不純物は少なく、安定して制御されているので、GaAsエピタキシャル層13は界面に残存する不純物の影響を受けることなく高品質な結晶となる。

【0024】

(実施例)

図1(a)に示す被覆膜付き半導体基板1をウェハ容器(フロロウェア社製)に収容し、大気中で2ヶ月保管した。その後、ウェハ容器から取り出し、MBE結晶成長装置に投入し、サーマルクリーニング(基板温度650℃で10分間熱処理)を行うことにより、表面酸化層とともにInAs被覆膜12を除去した(図1(b)参照)。

そして、GaAs基板11上に、基板温度550℃でGa源及びAs源を同時に照射し、図1(c)に示すGaAsエピタキシャル層13を0.5μm成長させた。

【0025】

図2は、本実施例によりエピタキシャル層を成長させた場合のGaAs基板11とGaAsエピタキシャル層13の界面における不純物量の分析結果である。図2より、表面から0.5μm付近(界面付近)には、不純物O、C、Si、Sが残存していることがわかる。後述する比較例における分析結果(図3)と比較するとS、Cが低減されている。

(比較例)

比較例では、GaAs単結晶基板をInAs被覆膜で被覆することなく、そのままウェハ容器に収容し、大気中で2ヶ月間保管した。なお、GaAs単結晶基板は、実施例と同一ロットで製造したものである。その後、ウェハ容器から取り出し、実施例と同一バッチでMBE結晶成長装置に投入し、サーマルクリーニング(基板温度650℃で10分間熱処理)を行って、表面酸化膜を除去した。

そして、GaAs基板上に、基板温度550℃でGa源及びAs源を同時に照射し、GaAsエピタキシャル層を0.5μm成長させた。

【0026】

図3は、比較例によりエピタキシャル層を成長させた場合のGaAs基板とGaAsエピタキシャル層の界面における不純物量の分析結果である。図3より、表面から0.5μm付近(界面付近)には、不純物O、C、Si、Sが残存していることがわかる。

【0027】

【表1】

【0028】

表1は、図2、図3に示す分析結果に基づく界面(深さ0.5μm)における不純物の定量値を示している。基板界面の不純物は、一般的にシート濃度で表される。図2、3のSIMS分析結果より、界面近傍の不純物のピーク付近の領域の濃度を積分してシート濃度が求められる。具体的にはSIMSで得られた濃度に深さ範囲を掛けることで面濃度(atoms/cm2)が求められる。

表1に示すように、実施例の場合は、比較例に比べて、S、Cが大幅に低減され、O、Siはほぼ同じであった。また、比較例におけるS、Cの不純物量は、GaAs基板をウェハ容器に保管する前の不純物量とほとんど変化なかった。

これより、O、Siはサーマルクリーニングの過程で除去できるが、S、Cはサーマルクリーニングにより除去されないため、基板表面の汚染の状態を反映していると考えられる。つまり、実施例では、このサーマルクリーニングにより除去されないS、Cを効果的に除去できたことになる。

【0029】

上述したように、被覆膜付き半導体基板1によれば、半導体基板11の最表層に被覆膜12を形成するので、薄膜形成前に半導体基板を保管する間に、表面状態を保護し、安定な状態に保つことができる。また、半導体基板11上に薄膜を形成する際に、熱処理により被覆膜は容易に除去されるので、半導体基板11とその基板上に形成される薄膜層との界面に残存する不純物を低減できるとともに、表面状態の安定化を図ることができる。したがって、本発明は、高品質な薄膜を形成するのに極めて有用である。

【0030】

以上、本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明は上記実施形態に限定されるものではなく、その要旨を逸脱しない範囲で変更可能である。

例えば、上記実施形態では、単一の材料からなるGaAs単結晶基板を薄膜形成に使用する場合について説明したが、本発明は、GaAsに限らず、その他の半導体基板を薄膜形成に使用する場合にも適用できる。

【0031】

また、例えば、半導体基板上にエピタキシャル層を形成したものを一旦装置外に取り出して保管しておき、再びエピタキシャル成長する場合にも適用できる。この場合は、エピタキシャル層の表面に被覆膜を形成するようにし、被覆膜の熱分解温度はエピタキシャル層の熱分解温度以下とする。

また、本発明は、半導体基板上に薄膜を形成する場合に有用なことは上述したとおりであるが、半導体基板上に蒸着したり、スパッタリングしたりする場合にも有用である。

【0032】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0033】

【図1】図1は、被覆膜付きの半導体基板を用いた薄膜形成工程における遷移状態を示す説明図である。

【図2】実施例によりエピタキシャル層を成長させた場合のGaAs基板とGaAsエピタキシャル層の界面における不純物量の分析結果である。

【図3】比較例によりエピタキシャル層を成長させた場合のGaAs基板とGaAsエピタキシャル層の界面における不純物量の分析結果である。

【符号の説明】

【0034】

1 被覆膜付き半導体基板

11 GaAs単結晶基板

12 InAs被覆膜

13 GaAsエピタキシャル層

【技術分野】

【0001】

本発明は、半導体基板上に半導体薄膜を形成する際のプロセス技術に関し、特に、半導体基板の表面処理方法、表面処理された半導体基板、及び表面処理された半導体基板を用いた薄膜形成方法に関する。

【背景技術】

【0002】

従来、半導体基板上に半導体薄膜を形成する方法として、有機金属気相成長(MOCVD:Metal Organic Chemical Vapor Deposition)法、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法が知られている(例えば、特許文献1、2)。これらの方法は、半導体基板表面に必要な原料を導入し、化学的或いは物理的に薄膜を形成する方法である。

例えば、レーザ或いはトランジスタといった半導体デバイスを作製する場合、上記MOCVD法やMBE法により、半導体基板上に必要な半導体結晶薄膜を重ねて成長することが行われる(例えば、ヘテロ構造を有するエピタキシャル結晶の積層構造)。

【0003】

上述した半導体薄膜の形成に用いられる半導体基板(例えば、GaAs基板等)は、ウェハに加工された後、すぐに薄膜形成装置に投入されるわけではなく、所定の保管ケース内に収容され保管される。このとき、収容された半導体基板は、保管雰囲気や保管ケースからの影響を受け、保管期間の経過に伴って表面に不純物(例えば、Si、O、C、S等)が付着することがある。このような半導体基板表面に存在する不純物は、半導体基板上に形成される半導体薄膜の特性に影響を与えるため、できる限り少なく、かつ、安定に制御されている必要がある。

【0004】

従来は、MOCVD装置やMBE装置等の薄膜形成装置に半導体基板を投入する前に、その表面を酸などでエッチングしたり、薄膜形成装置に投入した後に水素ガス或いは真空中で熱処理を行ったりするなどして、半導体基板表面の清浄化或いは安定化が図られている。

【特許文献1】特開2001−302389号公報

【特許文献2】WO2005/006421号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、半導体基板表面に熱処理を施す方法では、薄膜形成装置の装置上の制約によっては、不純物が十分に除去できないという問題がある。また、半導体基板表面にエッチング処理を施す方法では、半導体基板上に薄膜を形成する工程の直前にエッチング工程を設けて表面をエッチングしなければならないことによる負担、エッチング条件の安定化に関する負荷、使用済み廃液の処理などの問題がある。

【0006】

本発明は、半導体基板上への薄膜形成工程(例えば、エピタキシャル成長工程)直前に、簡単な前処理を行うだけで、半導体基板上に良質な半導体薄膜を形成可能な技術を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するため、請求項1に記載の発明は、1又は2以上の結晶層を有する半導体基板の表面処理方法において、

前記半導体基板の最表層の表面を、当該最表層の熱分解温度より低い熱分解温度を有する材料からなる被覆膜で被覆することを特徴とする。

すなわち、基板表面を保護するために、半導体基板の最表層より低い温度で熱分解する材料、好ましくは、大気中、不活性ガス中若しくは真空中で安定な材料からなる被覆膜を最表層表面に予め形成するようにしている。

【0008】

ここで、1又は2以上の結晶層を有する半導体基板とは、単一の半導体材料からなる基板及びこの基板上にエピタキシャル成長等により1以上の結晶層を形成された基板を含むことを意味する。つまり、半導体基板の最表層とは、単一の半導体材料からなる基板の場合は当該基板であり、基板上に1以上の結晶層が形成されている場合は最上位の結晶層である。

また、最表層の熱分解温度とは、最表層の構成成分の1つの分圧が1×10−5Torrを超える温度とする。

【0009】

これにより、半導体基板を保管している間に、保管される環境によって最表層表面が汚染されるのを防止することができる。また、被覆膜は、半導体基板の最表層の熱分解温度より低い熱分解温度を有する材料からなるので、エピタキシャル薄膜や絶縁膜の形成プロセスで通常実施されている薄膜形成前の熱処理(サーマルエッチング:表面酸化層を除去する工程)の過程で容易に除去することができる。

したがって、半導体基板を薄膜形成装置に投入するまでの保管期間に、保管環境によって基板表面(被覆膜表面)が不純物で汚染されても、この不純物を効果的に除去できる。その結果、半導体基板上にエピタキシャル層や絶縁膜層等の薄膜を形成する工程において、半導体基板表面の不純物量を安定に制御することができる。

【0010】

請求項2に記載の発明は、請求項1に記載の半導体基板の表面処理方法において、前記被覆膜の厚みは、当該被覆膜材料の1分子層以上10分子層以下であることを特徴とする。

被覆膜の厚みは、半導体基板表面をくまなく覆うために1分子層以上を必要とする。一方、薄膜形成プロセスで通常行われる薄膜形成前の熱処理で被覆膜を除去するため、厚すぎると工程が無駄に長くなり実用的ではない。そこで、従来の熱処理時間に過度の負担を加えない範囲として10分子層以下とする。

好ましくは、1分子層以上5分子層以下、さらに好ましくは、1分子層以上3分子層以下とする。例えば、被覆する材料がInAsエピタキシャル層である場合は、1分子層は6Åであるから、6Å以上60Å以下、好ましくは6Å以上30Å以下、さらに好ましくは6Å以上18Å以下となる。

【0011】

請求項3に記載の発明は、請求項1又は2に記載の半導体基板の表面処理方法において、前記被覆膜は、前記最表層と同族系元素で構成されていることを特徴とする。

ここで、同族系元素とは、例えば、最表層がGaAs化合物半導体であればIII−V族系化合物半導体(例えば、InAs等)であり、被覆膜が熱分解されることにより発生する元素が最表層を汚染する虞のない元素であることを意味する。

これにより、薄膜形成前の熱処理により被覆膜を分解しても、半導体基板の最表層表面が再汚染される虞はないので、半導体基板表面の不純物量を安定に制御することができる。

【0012】

請求項4に記載の発明は、請求項1から3のいずれか一項に記載の半導体基板の表面処理方法において、前記最表層はGaAs単結晶層であり、前記被覆膜材料はInAsであることを特徴とする。

これにより、InAs被覆膜が分解されることにより発生する元素(In、As)によりGaAs単結晶層表面が再汚染される虞はないので、薄膜形成前に行われる熱処理で半導体基板に影響を与えることなくInAs被覆膜は除去される。

【0013】

請求項5に記載の発明は、請求項4に記載の半導体基板の表面処理方法において、前記被覆膜は、InAsからなるエピタキシャル成長層であることを特徴とする。

すなわち、InAs被覆膜は、形成方法の一例として一般的なエピタキシャル成長方法を利用でき、被覆膜を形成するにあたり特別な方法を要するわけではない。エピタキシャル成長方法を利用することにより、被覆膜の厚みを容易に制御することができる。

【0014】

請求項6に記載の発明は、請求項1から5のいずれか一項に記載の表面処理方法により表面処理されていることを特徴とする半導体基板である。

このようにして被覆膜を形成された半導体基板は、薄膜形成前の熱処理により容易に被覆膜を除去でき、最表層表面の不純物を低減できるとともに安定して制御できるので、薄膜形成用の半導体基板として好適である。

【0015】

請求項7に記載の発明は、請求項6に記載の半導体基板を用いて、上記被覆膜を熱分解により当該半導体基板表面から除去してから、薄膜形成工程を行うことを特徴とする薄膜形成方法である。

このように、被覆膜を形成された半導体基板を薄膜形成用の基板として用い、この半導体基板から被覆膜を除去した後に薄膜形成工程を行うことにより、半導体基板表面の不純物は低減されるとともに安定して制御されるので、この半導体基板上に形成される薄膜は不純物により悪影響を受けることなく、高品質なものとなる。

【発明の効果】

【0016】

本発明によれば、半導体基板(基板上にエピタキシャル層を形成された基板を含む)の最表層に被覆膜を形成するので、薄膜形成前に半導体基板を保管する間に、表面状態を保護し、安定な状態に保つことができる。したがって、本発明に係る半導体基板の表面処理方法、半導体基板、及び薄膜形成方法は、高品質な薄膜を形成するのに極めて有用である。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施の形態を図面に基づいて説明する。

図1は、被覆膜付きの半導体基板を用いた薄膜形成プロセスにおける遷移状態を示す説明図である。本実施形態では、単一の材料からなる半絶縁性GaAs単結晶基板を用いた場合について示している。

【0018】

図1(a)に示すように、被覆膜付きの半導体基板1は、半絶縁性GaAs単結晶基板11の上に、InAs被覆膜12が形成されてなる。InAs被覆膜12の厚さは、例えば10Åである。この厚さは、InAsの1分子層の厚さは6Åなので、約1.67分子層に相当する。

このように、InAs被覆膜12の厚みを1分子層以上10分子層以下とすることで、薄膜形成プロセスで通常行われる薄膜形成前の熱処理(サーマルエッチング)によりInAs被覆膜12は容易に除去される。また、1分子層以上であれば半導体基板表面を保護する機能を発揮するので、熱処理時間に過度の負担を加えないように、1分子層以上10分子層以下、好ましくは、1分子層以上5分子層以下、さらに好ましくは、1分子層以上3分子層以下とする。

【0019】

GaAs単結晶基板を用いる場合、GaAsは熱分解温度が約700℃であるので、それより低い熱分解温度の材料が被覆膜の材料として選定される。GaAs単結晶基板が劣化することなく、被覆膜を熱分解して除去するためである。

また、被覆膜が熱分解されることにより発生する元素が最表層(ここでは、GaAs単結晶基板)を汚染する虞のない元素となるように被覆膜の材料が選定される。

そこで、本実施形態では、熱分解温度が約500℃のInAsを被覆膜12の材料としている。なお、最表層がGaAsである場合の被覆膜材料はInAsに限定されず、熱分解温度がGaAsよりも低く、同族系の元素で構成される材料であればよい。

【0020】

図1(a)に示す被覆膜付きの半導体基板1は、例えば、GaAs単結晶基板11の製造工程の最終処理(研磨、エッチングなど)終了後、GaAs単結晶基板11を直ちにMBE結晶成長装置に投入し、基板温度400℃でIn源及びAs源を同時照射して、InAsエピタキシャル膜を10Å(1分子層=6Å)成長させることにより作製される。

エピタキシャル成長方法を利用してInAs被覆膜12を形成することにより、厚さは正確に制御される。

【0021】

被覆膜付きの半導体基板1は、所定のウェハ容器に収容され、所定の期間保管される。その後、薄膜形成装置に投入され、所望の薄膜を形成するのに用いられる。例えば、半導体基板1上には、エピタキシャル層や絶縁膜層等の薄膜が形成される。

【0022】

図1(b)に示すように、薄膜形成工程では、まず、熱処理(サーマルエッチング)によりInAs被覆膜12を除去する。InAsの熱分解温度が500℃でGaAsの熱分解温度が700℃なので、例えば、熱処理温度を650℃とすれば、GaAs単結晶基板11が熱分解することなく、InAs被覆膜12だけを熱分解して除去することができる。このとき、熱分解により、InやAsが発生するが、これらはGaAsと同族系の元素なので、GaAs単結晶基板11を汚染する虞はない。

【0023】

次いで、図1(c)に示すように、GaAs単結晶基板11上に、例えば、GaAsエピタキシャル層を形成する。GaAs単結晶基板11とGaAsエピタキシャル層13との界面には残存する不純物は少なく、安定して制御されているので、GaAsエピタキシャル層13は界面に残存する不純物の影響を受けることなく高品質な結晶となる。

【0024】

(実施例)

図1(a)に示す被覆膜付き半導体基板1をウェハ容器(フロロウェア社製)に収容し、大気中で2ヶ月保管した。その後、ウェハ容器から取り出し、MBE結晶成長装置に投入し、サーマルクリーニング(基板温度650℃で10分間熱処理)を行うことにより、表面酸化層とともにInAs被覆膜12を除去した(図1(b)参照)。

そして、GaAs基板11上に、基板温度550℃でGa源及びAs源を同時に照射し、図1(c)に示すGaAsエピタキシャル層13を0.5μm成長させた。

【0025】

図2は、本実施例によりエピタキシャル層を成長させた場合のGaAs基板11とGaAsエピタキシャル層13の界面における不純物量の分析結果である。図2より、表面から0.5μm付近(界面付近)には、不純物O、C、Si、Sが残存していることがわかる。後述する比較例における分析結果(図3)と比較するとS、Cが低減されている。

(比較例)

比較例では、GaAs単結晶基板をInAs被覆膜で被覆することなく、そのままウェハ容器に収容し、大気中で2ヶ月間保管した。なお、GaAs単結晶基板は、実施例と同一ロットで製造したものである。その後、ウェハ容器から取り出し、実施例と同一バッチでMBE結晶成長装置に投入し、サーマルクリーニング(基板温度650℃で10分間熱処理)を行って、表面酸化膜を除去した。

そして、GaAs基板上に、基板温度550℃でGa源及びAs源を同時に照射し、GaAsエピタキシャル層を0.5μm成長させた。

【0026】

図3は、比較例によりエピタキシャル層を成長させた場合のGaAs基板とGaAsエピタキシャル層の界面における不純物量の分析結果である。図3より、表面から0.5μm付近(界面付近)には、不純物O、C、Si、Sが残存していることがわかる。

【0027】

【表1】

【0028】

表1は、図2、図3に示す分析結果に基づく界面(深さ0.5μm)における不純物の定量値を示している。基板界面の不純物は、一般的にシート濃度で表される。図2、3のSIMS分析結果より、界面近傍の不純物のピーク付近の領域の濃度を積分してシート濃度が求められる。具体的にはSIMSで得られた濃度に深さ範囲を掛けることで面濃度(atoms/cm2)が求められる。

表1に示すように、実施例の場合は、比較例に比べて、S、Cが大幅に低減され、O、Siはほぼ同じであった。また、比較例におけるS、Cの不純物量は、GaAs基板をウェハ容器に保管する前の不純物量とほとんど変化なかった。

これより、O、Siはサーマルクリーニングの過程で除去できるが、S、Cはサーマルクリーニングにより除去されないため、基板表面の汚染の状態を反映していると考えられる。つまり、実施例では、このサーマルクリーニングにより除去されないS、Cを効果的に除去できたことになる。

【0029】

上述したように、被覆膜付き半導体基板1によれば、半導体基板11の最表層に被覆膜12を形成するので、薄膜形成前に半導体基板を保管する間に、表面状態を保護し、安定な状態に保つことができる。また、半導体基板11上に薄膜を形成する際に、熱処理により被覆膜は容易に除去されるので、半導体基板11とその基板上に形成される薄膜層との界面に残存する不純物を低減できるとともに、表面状態の安定化を図ることができる。したがって、本発明は、高品質な薄膜を形成するのに極めて有用である。

【0030】

以上、本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明は上記実施形態に限定されるものではなく、その要旨を逸脱しない範囲で変更可能である。

例えば、上記実施形態では、単一の材料からなるGaAs単結晶基板を薄膜形成に使用する場合について説明したが、本発明は、GaAsに限らず、その他の半導体基板を薄膜形成に使用する場合にも適用できる。

【0031】

また、例えば、半導体基板上にエピタキシャル層を形成したものを一旦装置外に取り出して保管しておき、再びエピタキシャル成長する場合にも適用できる。この場合は、エピタキシャル層の表面に被覆膜を形成するようにし、被覆膜の熱分解温度はエピタキシャル層の熱分解温度以下とする。

また、本発明は、半導体基板上に薄膜を形成する場合に有用なことは上述したとおりであるが、半導体基板上に蒸着したり、スパッタリングしたりする場合にも有用である。

【0032】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0033】

【図1】図1は、被覆膜付きの半導体基板を用いた薄膜形成工程における遷移状態を示す説明図である。

【図2】実施例によりエピタキシャル層を成長させた場合のGaAs基板とGaAsエピタキシャル層の界面における不純物量の分析結果である。

【図3】比較例によりエピタキシャル層を成長させた場合のGaAs基板とGaAsエピタキシャル層の界面における不純物量の分析結果である。

【符号の説明】

【0034】

1 被覆膜付き半導体基板

11 GaAs単結晶基板

12 InAs被覆膜

13 GaAsエピタキシャル層

【特許請求の範囲】

【請求項1】

1又は2以上の結晶層を有する半導体基板の表面処理方法において、

前記半導体基板の最表層の表面を、当該最表層の熱分解温度より低い熱分解温度を有する材料からなる被覆膜で被覆することを特徴とする半導体基板の表面処理方法。

【請求項2】

前記被覆膜の厚みは、当該被覆膜材料の1分子層以上10分子層以下であることを特徴とする請求項1に記載の半導体基板の表面処理方法。

【請求項3】

前記被覆膜は、前記最表層と同族系元素で構成されていることを特徴とする請求項1又は2に記載の半導体基板の表面処理方法。

【請求項4】

前記最表層はGaAs単結晶層であり、前記被覆膜材料はInAsであることを特徴とする請求項3に記載の半導体基板の表面処理方法。

【請求項5】

前記被覆膜は、InAsからなるエピタキシャル成長層であることを特徴とする請求項4に記載の半導体基板の表面処理方法。

【請求項6】

請求項1から5のいずれか一項に記載の表面処理方法により表面処理されていることを特徴とする半導体基板。

【請求項7】

請求項6に記載の半導体基板を用いて、

上記被覆膜を熱分解により当該半導体基板表面から除去してから、薄膜形成工程を行うことを特徴とする薄膜形成方法。

【請求項1】

1又は2以上の結晶層を有する半導体基板の表面処理方法において、

前記半導体基板の最表層の表面を、当該最表層の熱分解温度より低い熱分解温度を有する材料からなる被覆膜で被覆することを特徴とする半導体基板の表面処理方法。

【請求項2】

前記被覆膜の厚みは、当該被覆膜材料の1分子層以上10分子層以下であることを特徴とする請求項1に記載の半導体基板の表面処理方法。

【請求項3】

前記被覆膜は、前記最表層と同族系元素で構成されていることを特徴とする請求項1又は2に記載の半導体基板の表面処理方法。

【請求項4】

前記最表層はGaAs単結晶層であり、前記被覆膜材料はInAsであることを特徴とする請求項3に記載の半導体基板の表面処理方法。

【請求項5】

前記被覆膜は、InAsからなるエピタキシャル成長層であることを特徴とする請求項4に記載の半導体基板の表面処理方法。

【請求項6】

請求項1から5のいずれか一項に記載の表面処理方法により表面処理されていることを特徴とする半導体基板。

【請求項7】

請求項6に記載の半導体基板を用いて、

上記被覆膜を熱分解により当該半導体基板表面から除去してから、薄膜形成工程を行うことを特徴とする薄膜形成方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2009−182315(P2009−182315A)

【公開日】平成21年8月13日(2009.8.13)

【国際特許分類】

【出願番号】特願2008−22910(P2008−22910)

【出願日】平成20年2月1日(2008.2.1)

【出願人】(591007860)日鉱金属株式会社 (545)

【Fターム(参考)】

【公開日】平成21年8月13日(2009.8.13)

【国際特許分類】

【出願日】平成20年2月1日(2008.2.1)

【出願人】(591007860)日鉱金属株式会社 (545)

【Fターム(参考)】

[ Back to top ]