半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えば三次元実装に用いる、半導体基板の製造方法に関するものである。

【背景技術】

【0002】

現在、携帯電話機やノート型パソコン等の携帯性を有する電子機器は、小型・軽量化のため、内部に設けられる半導体チップ等の各種の電子部品の小型が図られている。さらに、これらの電子機器においては、それら各種の電子部品を実装するスペースも極めて制限されている。このため、例えば半導体チップにおいては、そのパッケージング方法が工夫され、現在ではCPS(Chip Scale Package)といわれる超小型のパッケージングが案出されている。このCPS技術を用いて製造された半導体チップは、実装面積が半導体チップの面積と同程度で良いため、高密度実装を図ることができる。

【0003】

上記の電子機器は、今後、益々小型及び多機能化が求められることが予想できており、半導体チップの実装密度をさらに高める必要が出てきている。かかる背景の下、三次元実装技術が案出されてきた。

【0004】

この三次元実装技術は、同様の機能を有する半導体チップ同士又は異なる機能を有する半導体チップ同士を積層し、各半導体チップ間を配線接続することで、半導体チップの高密度実装を図る技術である。

【0005】

この三次元実装技術で用いられる半導体チップは、その表面と裏面とに形成された外部接続用の接続端子と、半導体チップの表面と裏面とを貫通する貫通穴を有する。そして、この貫通穴に形成された導電材を介して表裏面の接続端子同士が電気的に接続された電極構造を有する。そして、このような電極構造を有する半導体チップを積層すると、ある半導体チップの裏面に形成された接続端子が、他の半導体チップの表面に形成された接続端子と接続され、各半導体チップ間で配線接続される。

【0006】

三次元実装技術で用いられる半導体チップは、多くの工程を経て製造される。三次元実装に用いられる従来の半導体基板では、工程数を極力低減して製造効率を上昇させるために、外部接続用の接続端子と貫通穴内の導電材を、以下の工程を経て形成している(例えば、特許文献1参照)。

【0007】

図5(a)〜(j)に、従来の半導体基板の製造方法を示す。

【0008】

まず、シリコンウエハ等の半導体基板51上に、ビアパターンレジスト52による貫通穴パターン形成を行い(図5(a)参照)、レジスト開口部分53をドライエッチング等で加工してビアホール54を形成する(図5(b)参照)。そして、後述する配線層(メッキCu膜60)を流れる電流が半導体基板51へ拡散することを防止するために、SiO2又はSiN等からなる絶縁膜55を形成する(図5(c)参照)。次いで、配線層となるCuが半導体基板51へ拡散することを防止するため、Ti、TiN、Ta、又は、TaN等のバリア膜56を形成する(図5(d)参照)。そして、配線層となるCu膜60を形成するために、まず、スパッタ装置等を用いてCu又はAl等のシード膜57を形成し(図5(d)参照)、配線パターン用レジスト58により半導体基板51の裏面の配線パターンを形成する(図5(e)参照)。そして、配線パターン用レジスト58のレジスト開口部59にメッキCu膜60をメッキ処理により形成し(図5(f)参照)、配線パターン用レジスト58を剥離する(図5(g)参照)。そして、メッキ処理で形成したメッキCu膜60を保護するマスクレジスト61を形成し(図5(h)参照)、エッチングによって配線パターン外のバリア膜56及びシード膜57を除去する(図5(i)参照)。最後に、メッキCu膜60を保護しているマスクレジスト61を剥離し完成となる(図5(j)参照)。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−273107号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献1に示す工程におけるウエットエッチングによるメタル膜除去は、安定化が困難である。安定化が困難な理由は、主にスパッタ装置で形成されるメタル膜の形成量又は形成される膜質が、基板面内でバラつくためである。メタル膜除去が不安定になると、ウエットエッチングでも、液温又は浴槽攪拌等の条件により面内でエッチングレートに差が生じ、結果として、サイドエッチと呼ばれる現象が発生する。

【0011】

図6にサイドエッチ発生部の図を示す。基板面内でのエッチングに差が生じた結果、シード膜57上のメッキCu膜60の下部では、サイドエッチが進行する箇所が発生する。サイドエッチが進行する箇所が発生した結果として、配線細化が生じる。シード膜57上のメッキCu膜60の下部のシード膜57が横方向にエッチングが進行する(サイドエッチが進行)と、配線層の断面形状は下部がへこんだキノコ型となる。この断面形状は、上部分(メッキCu膜60等)が重く、下部分(シード膜57やバリア膜56等)が細いため、バランスが悪い。そのため、多少の外部荷重で、図7に示すように配線層(メッキCu膜60)が倒れてしまう場合がある。また、外部荷重がなくとも、サイドエッチの進行が激しくなると配線層が自立できなくなる場合がある。

【0012】

本発明は、これらの課題を解決し、サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記目的を達成するために、本発明の半導体基板の製造方法は、半導体基板の裏面に、開口部分を有するレジストにより貫通穴を形成し、前記レジストの前記開口部分にビアホールを形成し、前記半導体基板の裏面上に絶縁膜を形成し、前記絶縁膜上に配線パターン用レジストを形成し、前記配線パターン用レジスト、及び、前記絶縁膜の前記配線パターン用レジストで覆われていない部分に、バリア膜を形成し、前記バリア膜上にシード膜を形成し、前記配線パターン用レジストを前記絶縁膜から剥離し、前記絶縁膜上にメッキマスクレジストを形成し、前記メッキマスクレジストで覆われていない部分に、メッキ処理により配線Cu膜を形成し、前記メッキマスクレジストをメッキマスクレジストから剥離することを特徴とする。

【発明の効果】

【0014】

本発明によれば、サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供することができる。

【図面の簡単な説明】

【0015】

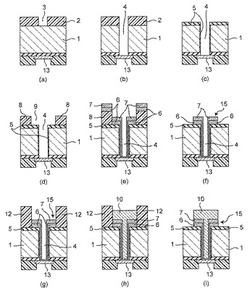

【図1】(a)〜(i)本発明の第一実施形態における三次元実装に用いる半導体基板の製造方法の工程を順に示す断面図

【図2】第一実施形態における半導体基板の製造方法を用いる場合のメッキ用電極の配置の説明図

【図3】(a)〜(c)第一実施形態の変形例におけるメッキマスクレジスト形成からメッキマスクレジスト剥離工程の拡大断面図

【図4】本第一実施形態と従来例の形成手順の違いを示した説明図

【図5】(a)〜(j)従来の半導体基板の製造方法の工程を順に示す断面図

【図6】サイドエッチ発生部を説明するための断面図

【図7】配線細化による倒壊を説明するための断面図

【発明を実施するための形態】

【0016】

以下、本発明の半導体基板の製造方法について、図面を参照しながら説明する。なお、以下の説明において、同じ構成については、同一符号を用いて詳しい説明は省略する。

【0017】

図1は、本発明の第一実施形態における三次元実装に用いる半導体基板の製造方法を示した図である。

【0018】

まず、シリコンウエハ等の半導体基板1の裏面(図1(a)の上面側)上に、ビアパターンレジスト2による貫通穴パターンの形成を行う(図1(a)参照)。ビアパターンレジスト2の貫通穴パターンは、レジスト開口部分3を有している。

【0019】

次いで、ビアパターンレジスト2のレジスト開口部分3を利用して、ドライエッチング等の加工により、ビアホール4を半導体基板1に形成する(図1(b)参照)。このとき、ビアホール4の底面に、半導体基板1の表面側(図1(b)の下面側)の電極パッド13が露出するようにする。

【0020】

次いで、配線層を流れる電流が半導体基板1へ拡散することを防止するため、SiO2又はSiN等からなる絶縁膜5を、ビアホール4の側壁及び半導体基板1の裏面上に形成する(図1(c)参照)。

【0021】

ここまでは、従来の方法と同様であるが、本発明の第一実施形態では、以後の工程において、ウエットエッチング工程を削除している。具体的には、本発明の第一実施形態では、半導体基板1の配線パターン以外の部分(配線パターンを形成しない部分)に、バリア膜6及びシード膜7の金属製の膜を付着させないことで、ウエットエッチング工程を削除している。

【0022】

ウエットエッチング工程を削除した、本発明の第一実施形態の方法について説明する。まず、半導体基板1上の絶縁膜5の裏面の所定部分(配線パターンを形成しない部分)に配線パターン用レジスト8を形成する(図1(d)参照)。配線パターン用レジスト8の配線パターンは、ビアホール4の開口部分を含む配線パターン用レジスト開口部9を有している。

【0023】

次いで、拡散防止用のバリア膜6及びシード膜7を、配線パターン用レジスト開口部9に露出した絶縁膜5上に順次形成する(図1(e)参照)。このとき、ビアホール4の側壁及び底面にもバリア膜6及びシード膜7が形成される。バリア膜6及びシード膜7は、主に、スパッタリング法を用いて形成される。スパッタリング法を用いることで、半導体基板1の絶縁膜5の表面全面及びビアホール4にスパッタ膜が飛散する。そのため、バリア膜6及びシード膜7は、配線パターン用レジスト8の表面、及び、配線パターン用レジスト開口部9の表面、及び、ビアホール4の側壁及び底面に形成される。ここで、配線パターン用レジスト開口部9の表面とは、配線として残したい部分である。また、ビアホール4の底面とは、ビアホール4の底面に露出した電極パッド13の表面である。

【0024】

次に、絶縁膜5から配線パターン用レジスト8の剥離を行うことで、配線パターン用レジスト8の上部にあるバリア膜6及びシード膜7は、配線パターン用レジスト8と共に半導体基板1上から消失する(図1(f)参照)。この方法により、まず、半導体基板1上に、バリア膜6及びシード膜7で構成される配線パターン15を形成することができる。

【0025】

次いで、配線Cu膜(配線層)の一例としてのメッキCu膜10が不必要部分に成長することを防止するため、メッキマスクレジスト12を、絶縁膜5上に形成する(図1(g)参照)。

【0026】

次いで、電気信号伝達用の電極パッド13よりメッキ電流を印加して、メッキCu膜10をビアホール4内で成長させて、ビアホール4内及びビアホール4の上方のメッキマスクレジスト12間の開口部(バリア膜6及びシード膜7が形成されている部分)にメッキCu膜10を形成する(図1(h)参照)。電気信号伝達用の電極パッド13は、半導体基板1の表面側(図1(h)の下面側)、すなわち、ビアホール4の下部に設置されている。

【0027】

次いで、絶縁膜5からメッキマスクレジスト12を剥離して完成となる(図1(i)参照)。

【0028】

メッキ工程に関しては、半導体基板1の裏面に形成された配線パターン15が独立して配置されていない場合には、半導体基板1の裏面内の任意の1箇所に電極を設置すると、全ての配線に電流が流れる。このような場合においては、メッキ用電極14を半導体基板1の裏面に設置すればよい。一方、配線パターン15が独立して配置されている場合には、メッキ用電極14は半導体基板1の裏面の複数個所に設置しなければならない。しかし、メッキ用電極14の複数箇所への設置は、電極用配線等がメッキ浴槽内でメッキ液の対流を妨害し、メッキCu膜10のメッキ成長にムラができる。そのため、メッキ用電極14の複数箇所への設置は、現実的には困難である。

【0029】

そこで、第一実施形態では、以下のように、メッキ液の対流を妨害しないように、半導体基板1の表面より各配線パターン15にメッキ電流を印加することのできるメッキ用電極14を構成している。

【0030】

第一実施形態における半導体基板の製造方法を用いる場合のメッキ用電極14の配置を図2に示す。

【0031】

三次元実装に用いる半導体基板1のため、ビアホール4の下部には電気信号伝達用の電極パッド13が設置されている。この電極パッド13にメッキ用電極14が半導体基板1の表面側(図2の下側)から接触できるよう、メッキ用電極14には、図2の示すように、電極パッド13のパターンと逆の突起14aを設ける。すなわち、電極パッド13は半導体基板1の表面側の凹部の底面に配置されているのに対して、メッキ用電極14は半導体基板1の表面側の凹部内に挿入して電極パッド13と電気的に接触可能な突起14aを有している。このメッキ用電極14を半導体基板1の表面にセットし(図2参照)、メッキ時の電流印加を半導体基板1の表面側から行う。このメッキ用電極14を用いた場合の効果は、半導体基板1の裏面側より電流印加した場合と比較して、ビアホール4の内部のメッキCu膜10のメッキ成長が確実となり、デバイスの歩留が向上することである。デバイスの歩留が向上する理由としては、メッキ成長用のシード膜7を形成するためのスパッタ粒子は直線的に飛散することで、ビアホール4の内部の側壁はスパッタ粒子の付着確率が低くなるためである。スパッタ粒子の付着確率が低くなることで、ビアホール4の側壁のメッキ成長用のシード膜7の膜厚が薄くなると共に、ビアホール4の側壁のメッキ成長用のシード膜7の膜質も、半導体基板1の裏面に形成されたメッキ成長用のシード膜7の膜質と比較して、緻密性が低下する。これにより、ビアホール4の側壁のシード膜7はメッキ電流が流れにくくなり、シード膜7にメッキ電流が流れている途中で、シード膜7の抵抗増加又は断線が発生し、半導体基板1の裏面からのメッキ電流印加では、メッキCu膜10のメッキ成長がビアホール4途中で停止し、ビアホール4の底までメッキCu膜10が形成できなくなる可能性がある。

【0032】

これに対して、本発明の第一実施形態のように、半導体基板1の表面側よりメッキ電流を印加することで、メッキCu膜10は、ビアホール4の底(電極パッド13の表面)から成長し、たとえ途中でシード膜7が断線していても、ビアホール4の底からのメッキCu膜10のボトムアップにより、ビアホール4の底の電極パッド13と、半導体基板1の裏面に形成されたシード膜7とが、メッキCu膜10で電気的に繋がる。このため、ビアホール4の内部でのメッキ未形成によるデバイス不良を防止することができる。

【0033】

メッキCu膜10が不必要な部分に成長することを防止するために、メッキマスクレジスト12の裏面側の配線パターン15の配線の寸法又は断面形状に制約を受けない場合は、必ずしもメッキマスクレジスト12の形成は必要でない。

【0034】

しかし、配線パターン15の配線の断面形状に制約がある場合は、任意の断面形状に応じたメッキマスクレジスト12を形成することで、必要な配線の断面形状を得ることができる。必要な配線の断面形状とは、例えば、左右からの荷重に耐えるために、配線下部の土台部分(基礎部分)が大きく、安定した断面形状(例えば、台形断面形状)などである。

【0035】

配線下部の土台部分(基礎部分)が大きく安定した形状を形成する工程の一例として、第一実施形態におけるメッキマスクレジスト形成工程からメッキマスクレジスト剥離工程までの拡大図を図3(a)〜(c)に示す。

【0036】

始めに、メッキマスクレジスト形成工程では、露出している絶縁膜5の表面のみならず、スパッタにより形成したシード膜7の外側を覆うように、メッキマスクレジスト12を形成する。具体的には、露出している絶縁膜5の表面及びシード膜7の一部(ビアホール4よりも遠い外側の部分)の表面にメッキマスクレジスト12を形成する(図3(a)参照)。

【0037】

次いで、メッキ工程では、メッキマスクレジスト12で覆われていない部分(シード膜7の残りの部分など)にメッキCu膜10を形成する(図3(b)参照)。

【0038】

その後、メッキマスクレジスト剥離工程では、メッキマスクレジスト12を絶縁膜5の表面及びシード膜7の一部の表面から剥離する(図3(c)参照)。

【0039】

この工程により、シード膜7の内側の部分(ビアホール4の近傍部分)を覆うと共に、下部の土台部分(基礎部分)がビアホール4の直径より外向きに突出し、ビアホール4の直径より大きな径を有するメッキCu膜10を形成することができる。また、従来の工程で発生するサイドエッチによる配線の断面形状のキノコ型(配線の断面形状の下部がへこんだ形状)を防止するため、シード膜7の幅以上にメッキCu膜10を成長させないことができる。これにより、メッキCu膜10を、シード膜7の幅と同等又はそれ以下の寸法に形成できるため、配線の断面形状の土台部分が大きくなり、安定した断面形状を有する配線を形成することができる。

【0040】

また、この方法を用いれば、メッキマスクレジスト12の形成状態次第で、様々な配線の断面形状を得ることが出来る。

【0041】

例えば、メッキCu膜10を階段状に形成させたい場合は、メッキマスクレジスト12の形成を複数回行い、メッキマスクレジスト12を階段状に形成しておけば良い。この場合、メッキCu膜10は、メッキマスクレジスト12に沿って成長するため、最終的なメッキCu膜10の仕上がりは階段状になる。これにより、メッキCu膜10の任意の断面形状を得ることができる。さらに、横方向からの荷重に対し、配線が倒れにくいよう、より安定した断面形状を得たい場合は、段数を増やすことで、配線上部を小さくすることが可能である。また、配線容量を得るために、太い配線を形成したい場合は、配線の断面形状を正方形に近い形にするために、段数を少なくするなど、用途に応じた配線の断面形状を得ることができる。

【0042】

以上が、本第一実施形態における半導体基板の製造方法である。本第一実施形態の形成手順(図1(a)〜(i)参照)と従来例の形成手順(図5(a)〜(j)参照)との違いを示した図を図4に示す。各工程において、上記本第一実施形態を用いることにより、工程順序の入れ替えが可能となり、従来例におけるウエットエッチング工程(図4左側の(i)ウエットエッチング)を削除することができる。

【0043】

なお、上記様々な変形例のうちの任意の変形例を適宜組み合わせることにより、それぞれの有する効果を奏するようにすることも可能である。

【産業上の利用可能性】

【0044】

本発明の半導体基板の製造方法は、半導体デバイスを安価で、高品質・高歩留に生産する半導体基板の製造方法に適用できる。

【符号の説明】

【0045】

1 半導体基板

2 ビアパターンレジスト

3 レジスト開口部

4 ビアホール

5 絶縁膜

6 バリア膜

7 シード膜

8 配線パターン用レジスト

9 配線パターン用レジスト開口部

10 メッキCu膜

12 メッキマスクレジスト

13 電極パッド

14 メッキ用電極

14a 突起

15 配線パターン

【技術分野】

【0001】

本発明は、例えば三次元実装に用いる、半導体基板の製造方法に関するものである。

【背景技術】

【0002】

現在、携帯電話機やノート型パソコン等の携帯性を有する電子機器は、小型・軽量化のため、内部に設けられる半導体チップ等の各種の電子部品の小型が図られている。さらに、これらの電子機器においては、それら各種の電子部品を実装するスペースも極めて制限されている。このため、例えば半導体チップにおいては、そのパッケージング方法が工夫され、現在ではCPS(Chip Scale Package)といわれる超小型のパッケージングが案出されている。このCPS技術を用いて製造された半導体チップは、実装面積が半導体チップの面積と同程度で良いため、高密度実装を図ることができる。

【0003】

上記の電子機器は、今後、益々小型及び多機能化が求められることが予想できており、半導体チップの実装密度をさらに高める必要が出てきている。かかる背景の下、三次元実装技術が案出されてきた。

【0004】

この三次元実装技術は、同様の機能を有する半導体チップ同士又は異なる機能を有する半導体チップ同士を積層し、各半導体チップ間を配線接続することで、半導体チップの高密度実装を図る技術である。

【0005】

この三次元実装技術で用いられる半導体チップは、その表面と裏面とに形成された外部接続用の接続端子と、半導体チップの表面と裏面とを貫通する貫通穴を有する。そして、この貫通穴に形成された導電材を介して表裏面の接続端子同士が電気的に接続された電極構造を有する。そして、このような電極構造を有する半導体チップを積層すると、ある半導体チップの裏面に形成された接続端子が、他の半導体チップの表面に形成された接続端子と接続され、各半導体チップ間で配線接続される。

【0006】

三次元実装技術で用いられる半導体チップは、多くの工程を経て製造される。三次元実装に用いられる従来の半導体基板では、工程数を極力低減して製造効率を上昇させるために、外部接続用の接続端子と貫通穴内の導電材を、以下の工程を経て形成している(例えば、特許文献1参照)。

【0007】

図5(a)〜(j)に、従来の半導体基板の製造方法を示す。

【0008】

まず、シリコンウエハ等の半導体基板51上に、ビアパターンレジスト52による貫通穴パターン形成を行い(図5(a)参照)、レジスト開口部分53をドライエッチング等で加工してビアホール54を形成する(図5(b)参照)。そして、後述する配線層(メッキCu膜60)を流れる電流が半導体基板51へ拡散することを防止するために、SiO2又はSiN等からなる絶縁膜55を形成する(図5(c)参照)。次いで、配線層となるCuが半導体基板51へ拡散することを防止するため、Ti、TiN、Ta、又は、TaN等のバリア膜56を形成する(図5(d)参照)。そして、配線層となるCu膜60を形成するために、まず、スパッタ装置等を用いてCu又はAl等のシード膜57を形成し(図5(d)参照)、配線パターン用レジスト58により半導体基板51の裏面の配線パターンを形成する(図5(e)参照)。そして、配線パターン用レジスト58のレジスト開口部59にメッキCu膜60をメッキ処理により形成し(図5(f)参照)、配線パターン用レジスト58を剥離する(図5(g)参照)。そして、メッキ処理で形成したメッキCu膜60を保護するマスクレジスト61を形成し(図5(h)参照)、エッチングによって配線パターン外のバリア膜56及びシード膜57を除去する(図5(i)参照)。最後に、メッキCu膜60を保護しているマスクレジスト61を剥離し完成となる(図5(j)参照)。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−273107号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、特許文献1に示す工程におけるウエットエッチングによるメタル膜除去は、安定化が困難である。安定化が困難な理由は、主にスパッタ装置で形成されるメタル膜の形成量又は形成される膜質が、基板面内でバラつくためである。メタル膜除去が不安定になると、ウエットエッチングでも、液温又は浴槽攪拌等の条件により面内でエッチングレートに差が生じ、結果として、サイドエッチと呼ばれる現象が発生する。

【0011】

図6にサイドエッチ発生部の図を示す。基板面内でのエッチングに差が生じた結果、シード膜57上のメッキCu膜60の下部では、サイドエッチが進行する箇所が発生する。サイドエッチが進行する箇所が発生した結果として、配線細化が生じる。シード膜57上のメッキCu膜60の下部のシード膜57が横方向にエッチングが進行する(サイドエッチが進行)と、配線層の断面形状は下部がへこんだキノコ型となる。この断面形状は、上部分(メッキCu膜60等)が重く、下部分(シード膜57やバリア膜56等)が細いため、バランスが悪い。そのため、多少の外部荷重で、図7に示すように配線層(メッキCu膜60)が倒れてしまう場合がある。また、外部荷重がなくとも、サイドエッチの進行が激しくなると配線層が自立できなくなる場合がある。

【0012】

本発明は、これらの課題を解決し、サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

上記目的を達成するために、本発明の半導体基板の製造方法は、半導体基板の裏面に、開口部分を有するレジストにより貫通穴を形成し、前記レジストの前記開口部分にビアホールを形成し、前記半導体基板の裏面上に絶縁膜を形成し、前記絶縁膜上に配線パターン用レジストを形成し、前記配線パターン用レジスト、及び、前記絶縁膜の前記配線パターン用レジストで覆われていない部分に、バリア膜を形成し、前記バリア膜上にシード膜を形成し、前記配線パターン用レジストを前記絶縁膜から剥離し、前記絶縁膜上にメッキマスクレジストを形成し、前記メッキマスクレジストで覆われていない部分に、メッキ処理により配線Cu膜を形成し、前記メッキマスクレジストをメッキマスクレジストから剥離することを特徴とする。

【発明の効果】

【0014】

本発明によれば、サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供することができる。

【図面の簡単な説明】

【0015】

【図1】(a)〜(i)本発明の第一実施形態における三次元実装に用いる半導体基板の製造方法の工程を順に示す断面図

【図2】第一実施形態における半導体基板の製造方法を用いる場合のメッキ用電極の配置の説明図

【図3】(a)〜(c)第一実施形態の変形例におけるメッキマスクレジスト形成からメッキマスクレジスト剥離工程の拡大断面図

【図4】本第一実施形態と従来例の形成手順の違いを示した説明図

【図5】(a)〜(j)従来の半導体基板の製造方法の工程を順に示す断面図

【図6】サイドエッチ発生部を説明するための断面図

【図7】配線細化による倒壊を説明するための断面図

【発明を実施するための形態】

【0016】

以下、本発明の半導体基板の製造方法について、図面を参照しながら説明する。なお、以下の説明において、同じ構成については、同一符号を用いて詳しい説明は省略する。

【0017】

図1は、本発明の第一実施形態における三次元実装に用いる半導体基板の製造方法を示した図である。

【0018】

まず、シリコンウエハ等の半導体基板1の裏面(図1(a)の上面側)上に、ビアパターンレジスト2による貫通穴パターンの形成を行う(図1(a)参照)。ビアパターンレジスト2の貫通穴パターンは、レジスト開口部分3を有している。

【0019】

次いで、ビアパターンレジスト2のレジスト開口部分3を利用して、ドライエッチング等の加工により、ビアホール4を半導体基板1に形成する(図1(b)参照)。このとき、ビアホール4の底面に、半導体基板1の表面側(図1(b)の下面側)の電極パッド13が露出するようにする。

【0020】

次いで、配線層を流れる電流が半導体基板1へ拡散することを防止するため、SiO2又はSiN等からなる絶縁膜5を、ビアホール4の側壁及び半導体基板1の裏面上に形成する(図1(c)参照)。

【0021】

ここまでは、従来の方法と同様であるが、本発明の第一実施形態では、以後の工程において、ウエットエッチング工程を削除している。具体的には、本発明の第一実施形態では、半導体基板1の配線パターン以外の部分(配線パターンを形成しない部分)に、バリア膜6及びシード膜7の金属製の膜を付着させないことで、ウエットエッチング工程を削除している。

【0022】

ウエットエッチング工程を削除した、本発明の第一実施形態の方法について説明する。まず、半導体基板1上の絶縁膜5の裏面の所定部分(配線パターンを形成しない部分)に配線パターン用レジスト8を形成する(図1(d)参照)。配線パターン用レジスト8の配線パターンは、ビアホール4の開口部分を含む配線パターン用レジスト開口部9を有している。

【0023】

次いで、拡散防止用のバリア膜6及びシード膜7を、配線パターン用レジスト開口部9に露出した絶縁膜5上に順次形成する(図1(e)参照)。このとき、ビアホール4の側壁及び底面にもバリア膜6及びシード膜7が形成される。バリア膜6及びシード膜7は、主に、スパッタリング法を用いて形成される。スパッタリング法を用いることで、半導体基板1の絶縁膜5の表面全面及びビアホール4にスパッタ膜が飛散する。そのため、バリア膜6及びシード膜7は、配線パターン用レジスト8の表面、及び、配線パターン用レジスト開口部9の表面、及び、ビアホール4の側壁及び底面に形成される。ここで、配線パターン用レジスト開口部9の表面とは、配線として残したい部分である。また、ビアホール4の底面とは、ビアホール4の底面に露出した電極パッド13の表面である。

【0024】

次に、絶縁膜5から配線パターン用レジスト8の剥離を行うことで、配線パターン用レジスト8の上部にあるバリア膜6及びシード膜7は、配線パターン用レジスト8と共に半導体基板1上から消失する(図1(f)参照)。この方法により、まず、半導体基板1上に、バリア膜6及びシード膜7で構成される配線パターン15を形成することができる。

【0025】

次いで、配線Cu膜(配線層)の一例としてのメッキCu膜10が不必要部分に成長することを防止するため、メッキマスクレジスト12を、絶縁膜5上に形成する(図1(g)参照)。

【0026】

次いで、電気信号伝達用の電極パッド13よりメッキ電流を印加して、メッキCu膜10をビアホール4内で成長させて、ビアホール4内及びビアホール4の上方のメッキマスクレジスト12間の開口部(バリア膜6及びシード膜7が形成されている部分)にメッキCu膜10を形成する(図1(h)参照)。電気信号伝達用の電極パッド13は、半導体基板1の表面側(図1(h)の下面側)、すなわち、ビアホール4の下部に設置されている。

【0027】

次いで、絶縁膜5からメッキマスクレジスト12を剥離して完成となる(図1(i)参照)。

【0028】

メッキ工程に関しては、半導体基板1の裏面に形成された配線パターン15が独立して配置されていない場合には、半導体基板1の裏面内の任意の1箇所に電極を設置すると、全ての配線に電流が流れる。このような場合においては、メッキ用電極14を半導体基板1の裏面に設置すればよい。一方、配線パターン15が独立して配置されている場合には、メッキ用電極14は半導体基板1の裏面の複数個所に設置しなければならない。しかし、メッキ用電極14の複数箇所への設置は、電極用配線等がメッキ浴槽内でメッキ液の対流を妨害し、メッキCu膜10のメッキ成長にムラができる。そのため、メッキ用電極14の複数箇所への設置は、現実的には困難である。

【0029】

そこで、第一実施形態では、以下のように、メッキ液の対流を妨害しないように、半導体基板1の表面より各配線パターン15にメッキ電流を印加することのできるメッキ用電極14を構成している。

【0030】

第一実施形態における半導体基板の製造方法を用いる場合のメッキ用電極14の配置を図2に示す。

【0031】

三次元実装に用いる半導体基板1のため、ビアホール4の下部には電気信号伝達用の電極パッド13が設置されている。この電極パッド13にメッキ用電極14が半導体基板1の表面側(図2の下側)から接触できるよう、メッキ用電極14には、図2の示すように、電極パッド13のパターンと逆の突起14aを設ける。すなわち、電極パッド13は半導体基板1の表面側の凹部の底面に配置されているのに対して、メッキ用電極14は半導体基板1の表面側の凹部内に挿入して電極パッド13と電気的に接触可能な突起14aを有している。このメッキ用電極14を半導体基板1の表面にセットし(図2参照)、メッキ時の電流印加を半導体基板1の表面側から行う。このメッキ用電極14を用いた場合の効果は、半導体基板1の裏面側より電流印加した場合と比較して、ビアホール4の内部のメッキCu膜10のメッキ成長が確実となり、デバイスの歩留が向上することである。デバイスの歩留が向上する理由としては、メッキ成長用のシード膜7を形成するためのスパッタ粒子は直線的に飛散することで、ビアホール4の内部の側壁はスパッタ粒子の付着確率が低くなるためである。スパッタ粒子の付着確率が低くなることで、ビアホール4の側壁のメッキ成長用のシード膜7の膜厚が薄くなると共に、ビアホール4の側壁のメッキ成長用のシード膜7の膜質も、半導体基板1の裏面に形成されたメッキ成長用のシード膜7の膜質と比較して、緻密性が低下する。これにより、ビアホール4の側壁のシード膜7はメッキ電流が流れにくくなり、シード膜7にメッキ電流が流れている途中で、シード膜7の抵抗増加又は断線が発生し、半導体基板1の裏面からのメッキ電流印加では、メッキCu膜10のメッキ成長がビアホール4途中で停止し、ビアホール4の底までメッキCu膜10が形成できなくなる可能性がある。

【0032】

これに対して、本発明の第一実施形態のように、半導体基板1の表面側よりメッキ電流を印加することで、メッキCu膜10は、ビアホール4の底(電極パッド13の表面)から成長し、たとえ途中でシード膜7が断線していても、ビアホール4の底からのメッキCu膜10のボトムアップにより、ビアホール4の底の電極パッド13と、半導体基板1の裏面に形成されたシード膜7とが、メッキCu膜10で電気的に繋がる。このため、ビアホール4の内部でのメッキ未形成によるデバイス不良を防止することができる。

【0033】

メッキCu膜10が不必要な部分に成長することを防止するために、メッキマスクレジスト12の裏面側の配線パターン15の配線の寸法又は断面形状に制約を受けない場合は、必ずしもメッキマスクレジスト12の形成は必要でない。

【0034】

しかし、配線パターン15の配線の断面形状に制約がある場合は、任意の断面形状に応じたメッキマスクレジスト12を形成することで、必要な配線の断面形状を得ることができる。必要な配線の断面形状とは、例えば、左右からの荷重に耐えるために、配線下部の土台部分(基礎部分)が大きく、安定した断面形状(例えば、台形断面形状)などである。

【0035】

配線下部の土台部分(基礎部分)が大きく安定した形状を形成する工程の一例として、第一実施形態におけるメッキマスクレジスト形成工程からメッキマスクレジスト剥離工程までの拡大図を図3(a)〜(c)に示す。

【0036】

始めに、メッキマスクレジスト形成工程では、露出している絶縁膜5の表面のみならず、スパッタにより形成したシード膜7の外側を覆うように、メッキマスクレジスト12を形成する。具体的には、露出している絶縁膜5の表面及びシード膜7の一部(ビアホール4よりも遠い外側の部分)の表面にメッキマスクレジスト12を形成する(図3(a)参照)。

【0037】

次いで、メッキ工程では、メッキマスクレジスト12で覆われていない部分(シード膜7の残りの部分など)にメッキCu膜10を形成する(図3(b)参照)。

【0038】

その後、メッキマスクレジスト剥離工程では、メッキマスクレジスト12を絶縁膜5の表面及びシード膜7の一部の表面から剥離する(図3(c)参照)。

【0039】

この工程により、シード膜7の内側の部分(ビアホール4の近傍部分)を覆うと共に、下部の土台部分(基礎部分)がビアホール4の直径より外向きに突出し、ビアホール4の直径より大きな径を有するメッキCu膜10を形成することができる。また、従来の工程で発生するサイドエッチによる配線の断面形状のキノコ型(配線の断面形状の下部がへこんだ形状)を防止するため、シード膜7の幅以上にメッキCu膜10を成長させないことができる。これにより、メッキCu膜10を、シード膜7の幅と同等又はそれ以下の寸法に形成できるため、配線の断面形状の土台部分が大きくなり、安定した断面形状を有する配線を形成することができる。

【0040】

また、この方法を用いれば、メッキマスクレジスト12の形成状態次第で、様々な配線の断面形状を得ることが出来る。

【0041】

例えば、メッキCu膜10を階段状に形成させたい場合は、メッキマスクレジスト12の形成を複数回行い、メッキマスクレジスト12を階段状に形成しておけば良い。この場合、メッキCu膜10は、メッキマスクレジスト12に沿って成長するため、最終的なメッキCu膜10の仕上がりは階段状になる。これにより、メッキCu膜10の任意の断面形状を得ることができる。さらに、横方向からの荷重に対し、配線が倒れにくいよう、より安定した断面形状を得たい場合は、段数を増やすことで、配線上部を小さくすることが可能である。また、配線容量を得るために、太い配線を形成したい場合は、配線の断面形状を正方形に近い形にするために、段数を少なくするなど、用途に応じた配線の断面形状を得ることができる。

【0042】

以上が、本第一実施形態における半導体基板の製造方法である。本第一実施形態の形成手順(図1(a)〜(i)参照)と従来例の形成手順(図5(a)〜(j)参照)との違いを示した図を図4に示す。各工程において、上記本第一実施形態を用いることにより、工程順序の入れ替えが可能となり、従来例におけるウエットエッチング工程(図4左側の(i)ウエットエッチング)を削除することができる。

【0043】

なお、上記様々な変形例のうちの任意の変形例を適宜組み合わせることにより、それぞれの有する効果を奏するようにすることも可能である。

【産業上の利用可能性】

【0044】

本発明の半導体基板の製造方法は、半導体デバイスを安価で、高品質・高歩留に生産する半導体基板の製造方法に適用できる。

【符号の説明】

【0045】

1 半導体基板

2 ビアパターンレジスト

3 レジスト開口部

4 ビアホール

5 絶縁膜

6 バリア膜

7 シード膜

8 配線パターン用レジスト

9 配線パターン用レジスト開口部

10 メッキCu膜

12 メッキマスクレジスト

13 電極パッド

14 メッキ用電極

14a 突起

15 配線パターン

【特許請求の範囲】

【請求項1】

半導体基板の裏面に、開口部分を有するレジストにより貫通穴を形成し、

前記レジストの前記開口部分にビアホールを形成し、

前記半導体基板の裏面上に絶縁膜を形成し、

前記絶縁膜上に配線パターン用レジストを形成し、

前記配線パターン用レジスト、及び、前記絶縁膜の前記配線パターン用レジストで覆われていない部分に、バリア膜を形成し、

前記バリア膜上にシード膜を形成し、

前記配線パターン用レジストを前記絶縁膜から剥離し、

前記絶縁膜上にメッキマスクレジストを形成し、

前記メッキマスクレジストで覆われていない部分に、メッキ処理により配線Cu膜を形成し、

前記メッキマスクレジストをメッキマスクレジストから剥離する、

半導体基板の製造方法。

【請求項2】

前記半導体基板はシリコンウエハであり、

前記ビアホールの形成にはドライエッチングを使用し、

前記絶縁膜としてSiO2又はSiNを使用し、

前記バリア膜としてTi、TiN、Ta、又は、TaNを使用し、

前記シード膜としてCu又はAlを使用する、

請求項1に記載の半導体基板の製造方法。

【請求項3】

前記半導体基板の配線パターンが形成されていない表面側からメッキ電流を印加して、前記配線Cu膜を形成する、

請求項1又は2に記載の半導体基板の製造方法。

【請求項4】

前記半導体基板上に形成する前記配線Cu配線の断面形状に応じて、前記メッキマスクレジストの形成を複数回行う、

請求項1〜3のいずれか1つに記載の半導体基板の製造方法。

【請求項1】

半導体基板の裏面に、開口部分を有するレジストにより貫通穴を形成し、

前記レジストの前記開口部分にビアホールを形成し、

前記半導体基板の裏面上に絶縁膜を形成し、

前記絶縁膜上に配線パターン用レジストを形成し、

前記配線パターン用レジスト、及び、前記絶縁膜の前記配線パターン用レジストで覆われていない部分に、バリア膜を形成し、

前記バリア膜上にシード膜を形成し、

前記配線パターン用レジストを前記絶縁膜から剥離し、

前記絶縁膜上にメッキマスクレジストを形成し、

前記メッキマスクレジストで覆われていない部分に、メッキ処理により配線Cu膜を形成し、

前記メッキマスクレジストをメッキマスクレジストから剥離する、

半導体基板の製造方法。

【請求項2】

前記半導体基板はシリコンウエハであり、

前記ビアホールの形成にはドライエッチングを使用し、

前記絶縁膜としてSiO2又はSiNを使用し、

前記バリア膜としてTi、TiN、Ta、又は、TaNを使用し、

前記シード膜としてCu又はAlを使用する、

請求項1に記載の半導体基板の製造方法。

【請求項3】

前記半導体基板の配線パターンが形成されていない表面側からメッキ電流を印加して、前記配線Cu膜を形成する、

請求項1又は2に記載の半導体基板の製造方法。

【請求項4】

前記半導体基板上に形成する前記配線Cu配線の断面形状に応じて、前記メッキマスクレジストの形成を複数回行う、

請求項1〜3のいずれか1つに記載の半導体基板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−248671(P2012−248671A)

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願番号】特願2011−119094(P2011−119094)

【出願日】平成23年5月27日(2011.5.27)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願日】平成23年5月27日(2011.5.27)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]