半導体基板の解析方法

【課題】表面にDZを有する半導体基板において、該DZの有無を判定することを目的の一とする。

【解決手段】表面にDZ、内部にIG層を有する半導体基板において、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、一次モードのライフタイムτ11および下記数式を用いて、IG層のバルクライフタイムτIGを求め、第1のサンプルに対して、表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGを比較し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGの差が0となったとき、DZが消失したと判定することができる。

【解決手段】表面にDZ、内部にIG層を有する半導体基板において、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、一次モードのライフタイムτ11および下記数式を用いて、IG層のバルクライフタイムτIGを求め、第1のサンプルに対して、表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGを比較し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGの差が0となったとき、DZが消失したと判定することができる。

【発明の詳細な説明】

【技術分野】

【0001】

技術分野は、半導体基板の解析方法に関する。また、SOI基板の作製方法に関する。

【背景技術】

【0002】

単層構造のシリコン基板の解析方法として、μ−PCD(Microwave−Photo Conductive Decay)法により得られた過剰キャリア密度の時間変化(減衰曲線)から、シリコン基板中の少数キャリアのライフタイム(バルクライフタイムτbともいう)を測定する手法が知られている(特許文献1参照)。

【0003】

バルクライフタイムは、半導体のエネルギーギャップ中の欠陥や不純物に起因する準位(これらをまとめて欠陥準位と呼ぶ)の大小を示す指標の一つである。特にエネルギーギャップ中の深い位置に存在する欠陥準位は、キャリアの生成再結合中心としての性質が濃い。バルクライフタイムはキャリアが生成されてからそれらの準位を介して再結合によって消滅するまでの時間(寿命)の目安である。欠陥準位が多いほど再結合の頻度が増加するため、バルクライフタイムは減少する。

【0004】

また、例えば、単結晶シリコン基板においてその表面は結晶の周期性が断絶する箇所であり、表面ダングリングボンド等に伴う欠陥準位が存在する。表面再結合速度は表面における欠陥準位の大小を示す指標の一つである。

【0005】

また、μ−PCD法は、半導体基板等の試料を非破壊かつ非接触で測定することができるため、バルクライフタイム測定法として有効な手法である。以下にその原理を説明する。

【0006】

試料の表面にレーザとマイクロ波(μ波ともいう)を同時に照射する。レーザ照射によって試料中に過剰キャリアが生成される。そして、レーザ照射を止めるとエネルギーギャップ中の欠陥準位を介した再結合により、一定時間後に熱平衡状態のキャリア密度に戻る。ここで、キャリア密度とμ波の反射率との相関を利用し、反射マイクロ波を検波することで、減衰中のキャリア密度の時間変化を追うことができる。レーザ照射を止めてから十分な時間が経つと、キャリア密度の減衰は最も時定数の長いモードのみが残り、減衰曲線は指数関数1つで表されるようになる。その最も長い時定数を一次モードのライフタイムτ1と呼ぶ。

【0007】

ここで、μ−PCD法から得られた一次モードのライフタイムτ1は一般に試料のバルクライフタイムτbよりも短くなる。一次モードのライフタイムτ1は表面再結合速度の寄与(表面でのキャリア消滅)とバルクライフタイムの寄与(バルク内でのキャリア消滅)の両方を含むためである。

【0008】

μ−PCD法を用いてバルクライフタイムを測定するには、表面再結合速度を可能な限り0に近付けることで表面の影響を排除し、一次モードのライフタイムτ1をバルクライフタイムτbと近似するS−loweringという手法が知られている。この手法においては、例えば、熱酸化膜形成やケミカルパッシベーションといった表面処理が採用される。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開昭59−55013号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

シリコン基板にアルゴン等の不活性ガス雰囲気でアニールを施し、形成されたDZ(Denuded Zone)の一部をガラス基板、シリコン基板、サファイア基板等へ転載する場合、これを繰り返すうちに上記基板側のDZは薄膜化され、やがて消失してしまう。

【0011】

一方で、μ−PCD法を用いた複数層構造(多層構造ともいう)を有する半導体基板の解析の試みは少なかった。表面近傍にDZを有し、内部にIG(Intrinsic Gettering)層を有する半導体基板について、DZの厚さの測定法は提案されていない。

【0012】

そこで、本発明の一態様は、表面にDZを有する半導体基板において、該DZの残存有無を判定することを目的の一とする。

【課題を解決するための手段】

【0013】

本発明の一態様は、表面近傍にDZを有し、内部にIG層を有する半導体基板に対して、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、一次モードのライフタイムτ11および下記数式を用いて、IG層のバルクライフタイムτIGを求め、第1のサンプルの表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGを比較し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGの差が0となったとき、DZが消失したと判定する半導体基板の解析方法である。

【0014】

【数1】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【0015】

本発明の他の一態様は、表面近傍にDZを有し、内部にIG層を有する半導体基板に対して、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、一次モードのライフタイムτ11および下記数式を用いて、IG層のバルクライフタイムτIGを求め、第1のサンプルの表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGを比較し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGの差がIG層のバルクライフタイムτIGに対して、設定した割合以下となった時にDZが僅少であると判定する半導体基板の解析方法である。

【0016】

【数2】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【0017】

ここで、τIGとτ12の大小関係はτIG<τ12となる。第2のサンプルの一次モードライフタイムτ12はτIGに加え、それよりも圧倒的に大きいDZのバルクライフタイムτDZが寄与するためである。また、第2のサンプルにおける表面の寄与は、それが無視できるほどの表面再結合速度に制御されている。

【0018】

ここで、転載工程の繰り返しに伴うDZ幅の減少によるτIGおよびτ12の推移について数値シミュレーション結果を用いて説明する。図3はIG層の外側にDZがある層構造を想定した多層モデル計算の例である。ここでは、τIG=1μsec、τDZ=1msecとした。白丸は表面再結合速度S=1×105cm/secとしてμ−PCDシミュレーションから得られたτ11を数式1に代入して近似的に見積もったτIGである。黒丸は表面再結合速度S=10cm/secとしてμ−PCDシミュレーションから得られたτ12である。DZの薄膜化が進むにつれて、τIGがτ12に近づくことが確認できる。

【0019】

図3に示すようにDZの薄膜化によってτ12は減少してτIGへ近付き、DZが完全に消失するとτ12はτIGにほぼ一致する。

【0020】

転載工程毎に上記の解析を用いてτIGとτ12を取得し、その差(τ12−τIG)が0となったとき、DZが消失したと判定することができる。なお、本明細書では、「τ12とτIGの差が0」という表現は、τ12とτIGの差がほぼ0という意味も含むものとする。

【0021】

また、DZが消失していた場合、そのまま次の転載工程を行うと別基板へ転載される半導体層は結晶欠陥を多く含むIG層を含んでしまう可能性があるため、(τ12−τIG)がτIGに対して、設定した割合以下(例えば、実施の形態1では0.05以下)となった時にDZが僅少であると判定するとより好ましい。

【0022】

また、本発明の他の一態様は、半導体基板のDZは、半導体基板を不活性雰囲気中または水素雰囲気中でアニールすることにより形成してもよい。

【0023】

また、本発明の他の一態様は、半導体基板にシリコン基板を用いてもよい。

【0024】

また、本発明の他の一態様は、一次モードのライフタイムτ11および一次モードのライフタイムτ12は、μ−PCD法を用いて測定してもよい。

【発明の効果】

【0025】

本発明の一態様は、上記方法で解析することにより、DZの残存有無を判定することができる。

【0026】

また、本発明の他の一態様は、上記方法で解析することにより、DZが僅少であると判定することができる。

【図面の簡単な説明】

【0027】

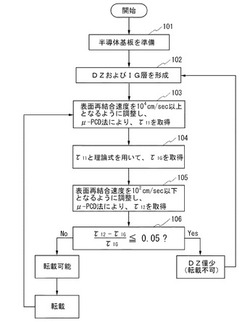

【図1】半導体装置の解析方法の一例を説明する図。

【図2】SOI基板の作製方法を示す図。

【図3】転載工程によるDZの薄膜化を示す図。

【発明を実施するための形態】

【0028】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなく、その形態および詳細を様々に変更しうることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

【0029】

(実施の形態1)

本実施の形態では、表面にDZを有する半導体基板において、DZの残存有無を判定する解析方法および残存するDZが僅少であると判定する解析方法について説明する。本実施の形態の図1では、残存するDZが僅少であると判定する解析方法について示されている。解析は、次の工程A乃至工程Gによって行われる。

【0030】

<工程A:半導体基板の準備(図1のステップ101に対応)>

解析に用いる半導体基板を準備する。半導体基板としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウムまたは炭化シリコンなどの第14族元素を含む結晶半導体基板を用いればよい。

【0031】

本実施の形態に用いる半導体基板の厚さは、薄すぎると基板処理時や測定時のハンドリングが困難になるため、0.5mm以上であることが望ましい。

【0032】

<工程B:DZ、IG層の形成(図1のステップ102に対応)>

次に、半導体基板に対してアルゴン、ヘリウム、窒素等の不活性雰囲気中、または水素雰囲気中でアニールを施すことによりDZが形成される。当該アニールを施すことで、半導体基板の表面近傍の酸素等が外方拡散し、該表面近傍に結晶欠陥が少ない層(DZ)を形成することができる。DZの形成方法は、これに限定されない。

【0033】

そして、表面近傍より内側(DZより内側)には、DZに比べて圧倒的に結晶欠陥の多い層(IG層)となる。すなわち、半導体基板は、表面近傍にDZを有し、内部にIG層を有する。

【0034】

なお、本実施の形態に用いた半導体基板は、シリコン基板であり、DZの膜厚(一般的に10μm以上100μm以下)は、シリコン基板の膜厚(一般的に500μm以上1mm以下)に比較して十分薄い。

【0035】

<工程C:半導体基板における一次モードのライフタイムτ11の取得(図1のステップ103に対応)>

次に、半導体基板表面の表面再結合速度を1×104cm/sec以上に調整する。これを第1のサンプルとする。調整する方法としては、例えば、半導体基板表面に自然酸化膜を形成すればよい。自然酸化膜は一般的に数万程度の非常に大きい表面再結合速度を有している。そして、μ−PCD法によって、一次モードのライフタイムτ11を測定する。

【0036】

半導体基板表面に形成する自然酸化膜は、半導体基板を準備した段階で形成されている自然酸化膜を用いてもよいし、当該自然酸化膜をフッ化水素酸などにより除去して純水によって洗浄した後に、再度、自然酸化膜を形成してもよい。なお、形成する自然酸化膜の厚さは特に限定されない。

【0037】

<工程D:半導体基板におけるIG層のバルクライフタイムτIGの取得(図1のステップ104に対応)>

次に半導体基板におけるIG層のバルクライフタイムτIGを求める。

【0038】

ここで、工程Cにおいて、半導体基板表面の表面再結合速度が1×104cm/sec以上の場合、一次モードのライフタイムτ11は、以下のような数式で近似できる。

【0039】

【数3】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【0040】

得られた一次モードのライフタイムτ11および上記数式を用いて、IG層のバルクライフタイムτIGを算出する。

【0041】

IG層のバルクライフタイムτIGを算出後、表面再結合速度が1×104cm/sec以上である半導体基板表面の膜を除去する。自然酸化膜は、例えば、フッ化水素酸などにより除去すればよい。

【0042】

<工程E:半導体基板の一次モードのライフタイムτ12の測定(図1のステップ105に対応)>

次に、第1のサンプルの半導体基板表面の表面再結合速度を1×102cm/sec以下に調整する。これを第2のサンプルとする。調整する方法としては、例えば、半導体基板表面に熱酸化膜やケミカルパッシベーション膜を形成すればよい。

【0043】

特にケミカルパッシベーション膜は半導体基板の表面再結合速度を小さくすることが可能である。具体的には、表面再結合速度を1cm/sec以上10cm/sec以下にすることが可能である。

【0044】

また、半導体基板表面の表面再結合速度を1×102cm/sec以下に調整する方法として、化学気相蒸着法(CVD法ともいう。)を用いて形成した、窒化シリコンを主成分とする膜、酸化アルミニウムを主成分とする膜またはアモルファスシリコンを主成分とする膜などを用いることができる。例えば、アモルファスシリコンを主成分とする膜であれば、SiH4とH2を用いたRFプラズマCVDにより200℃程度の温度で作製することができる。

【0045】

次に一次モードのライフタイムτ12を測定する。本実施の形態では、μ−PCD法によって、一次モードのライフタイムτ12を測定する。

【0046】

<工程F:判定(図1のステップ106に対応)>

次に、工程Dにおいて取得したIG層のバルクライフタイムτIGと工程Eで測定した一次モードのライフタイムτ12とを比較する。

【0047】

IG層のバルクライフタイムτIGと一次モードのライフタイムτ12とを比較した結果、その差(τ12−τIG)がτIGに対して、設定した割合以下(本実施の形態では、0.05以下)であると残存するDZが僅少であると判定する。そのまま次の転載工程を行うと別基板へ転載される半導体層は結晶欠陥を多く含むIG層を含んでしまう可能性があるため、再度、DZを形成する必要がある。

【0048】

上記の判定法によって残存するDZが僅少であると判定された場合、ステップ102へ戻り、アルゴン等の不活性ガス雰囲気でアニールを施し再びDZを形成する。

【0049】

上記の判定法によってDZがまだ十分あり、転載可能と判定された場合、転載工程を行った後、ステップ103へ戻り、再び同様の解析を行う。

【0050】

また、図1には示していないがIG層のバルクライフタイムτIGと一次モードのライフタイムτ12とを比較した結果、その差(τ12−τIG)が0であるとDZが消失したと判定することができる。

【0051】

以上の工程を行うことにより、算出したバルクライフタイムτIGおよび測定した一次モードのライフタイムτ12のみにより、半導体基板表面のDZの残存有無を非常に簡便に判定することができ、結晶欠陥の多いIG層の別基板への転載を防ぐことができるため、歩留まりの向上が期待できる。

【0052】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0053】

(実施の形態2)

本実施の形態では、実施の形態1の方法により解析した半導体基板を用い、SOI(Silicon On Insulator)基板を作製する方法を示す。

【0054】

まず、半導体基板201を準備する(図2(A)参照)。半導体基板201は、実施の形態1の方法で解析され、DZがまだ十分あると確認されたものを用いる。

【0055】

次いで、半導体基板201にイオン203照射をし、所定の深さに損傷領域205を形成する(図2(B)参照)。

【0056】

損傷領域205は、電界で加速されたイオン(イオンビーム)203を半導体基板201に照射し、半導体基板201の表面から所定の深さにイオン203を導入することで、形成することができる。

【0057】

イオン203の照射は、水素、不活性元素(例えばヘリウム)またはハロゲン(例えばフッ素)等のイオンを用い、イオンドーピング法またはイオン注入法により行うことができる。

【0058】

なお、上記の「イオンドーピング法」とは、原料ガスから生成されるイオン化したガスを質量分離せず、そのまま電界で加速して対象物に照射し、イオン化したガスの元素を対象物に含ませる方式を指す。また、上記の「イオン注入法」とは、原料ガスをプラズマ化し、このプラズマに含まれるイオン種を引き出し、質量分離をして、所定の質量を有するイオン種を加速して、イオンビームとして、対象物に注入する方法である。

【0059】

次に、支持基板207を準備する(図2(C)参照)。

【0060】

支持基板207は、ガラス、プラスチック、セラミック、石英、サファイアなどの絶縁体でなる基板、シリコンなどの半導体でなる基板、金属やステンレスなどの導電体でなる基板を用いることができる。

【0061】

次いで、半導体基板201と支持基板207とを、絶縁層209を介して貼り合わせる(図2(D)参照)。貼り合わせは、半導体基板201の損傷領域205を形成した際にイオン203が導入された側を貼り合わせ面(接合面ともいう)として行う。

【0062】

絶縁層209は、2つの基板を貼り合わせるための接合層として機能するものであり、半導体基板201上に形成してもよく、支持基板207上に形成してもよい。半導体基板201上に絶縁層209を形成する場合、上記イオン203の照射の前に絶縁層209を形成してもよい。

【0063】

絶縁層209は、熱酸化膜やCVD法により、酸化物または窒化物等を、単層または積層させて形成すればよい。具体的な材料としては、酸化シリコン、窒化シリコン、酸化窒化シリコン、または窒化酸化シリコン等が挙げられる。

【0064】

なお、本明細書中において、酸化窒化シリコンなどの「酸化窒化物」とは、その組成として、窒素よりも酸素の含有量が多いものを示す。

【0065】

なお、本明細書中において、窒化酸化シリコンなどの「窒化酸化物」とは、その組成として、酸素よりも窒素の含有量が多いものを示す。

【0066】

ここで、含有量の比較は、ラザフォード後方散乱法および水素前方散乱法の測定結果に基づいて行うこととする。

【0067】

また、貼り合わせを行う前に、2つの基板の貼り合わせ面に洗浄やプラズマ処理などの表面処理を行ってもよい。表面処理を行うことで、親水性または清浄性が向上し、貼り合わせの際の接合強度を向上させることができる。なお、表面処理は、2つの基板の少なくとも一方に行えばよい。また、絶縁層209が形成されている基板に表面処理を行う場合は、絶縁層209の表面に対して行う。

【0068】

次に、加熱処理を行い、損傷領域205において半導体基板201を分離(分断ともいう)する(図2(E)参照)。該分離により、支持基板207上に、絶縁層209と、半導体基板201の一部からなる半導体層211とを順に設けることができる。すなわち、支持基板207上に、半導体基板201の一部からなる半導体層211を転載することができる。

【0069】

なお、加熱処理は、300℃以上、かつ、支持基板207の歪み点未満の温度で行えばよい。

【0070】

このようにして、SOI基板213を作製することができる。

【0071】

実施の形態1の解析方法を用いることで、予め半導体基板のDZの有無を判定することができる。そして、DZの内部に損傷領域を形成し、DZの一部を転載することで、結晶欠陥が少ない半導体層を得ることができる。

【0072】

なお、SOI基板とは、支持基板上に絶縁層を介して半導体層が設けられたものの総称であり、シリコン層を有する基板に限定されない。

【0073】

そして、このSOI基板を用いて、トランジスタまたはダイオード等の半導体装置を作製することができる。

【0074】

また、上記半導体素子を用いて、様々な電子機器を作製することができる。電子機器の一例としては、テレビ、パーソナルコンピュータ、ビデオカメラ、デジタルカメラ、ナビゲーションシステムまたは携帯情報端末(携帯電話、電子書籍または携帯型ゲーム機等)などの表示装置が挙げられる。これら表示装置の表示部または周辺部に、上記半導体素子を用いた回路を設けることができる。

【0075】

また、電子機器の他の一例としては、表示部を必須としないものでもよく、例えば、無線タグ、認証装置、照明装置または空調機などの様々な装置が挙げられる。これらの装置に上記半導体素子を用いた回路を設けることができる。

【0076】

上記回路としては、画素回路、駆動回路、演算回路、センサ回路、電源回路またはメモリ回路など、上記半導体素子を用いることが可能な回路が挙げられる。

【0077】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

【0078】

101 ステップ

102 ステップ

103 ステップ

104 ステップ

105 ステップ

106 ステップ

201 半導体基板

203 イオン

205 損傷領域

207 支持基板

209 絶縁層

211 半導体層

213 SOI基板

【技術分野】

【0001】

技術分野は、半導体基板の解析方法に関する。また、SOI基板の作製方法に関する。

【背景技術】

【0002】

単層構造のシリコン基板の解析方法として、μ−PCD(Microwave−Photo Conductive Decay)法により得られた過剰キャリア密度の時間変化(減衰曲線)から、シリコン基板中の少数キャリアのライフタイム(バルクライフタイムτbともいう)を測定する手法が知られている(特許文献1参照)。

【0003】

バルクライフタイムは、半導体のエネルギーギャップ中の欠陥や不純物に起因する準位(これらをまとめて欠陥準位と呼ぶ)の大小を示す指標の一つである。特にエネルギーギャップ中の深い位置に存在する欠陥準位は、キャリアの生成再結合中心としての性質が濃い。バルクライフタイムはキャリアが生成されてからそれらの準位を介して再結合によって消滅するまでの時間(寿命)の目安である。欠陥準位が多いほど再結合の頻度が増加するため、バルクライフタイムは減少する。

【0004】

また、例えば、単結晶シリコン基板においてその表面は結晶の周期性が断絶する箇所であり、表面ダングリングボンド等に伴う欠陥準位が存在する。表面再結合速度は表面における欠陥準位の大小を示す指標の一つである。

【0005】

また、μ−PCD法は、半導体基板等の試料を非破壊かつ非接触で測定することができるため、バルクライフタイム測定法として有効な手法である。以下にその原理を説明する。

【0006】

試料の表面にレーザとマイクロ波(μ波ともいう)を同時に照射する。レーザ照射によって試料中に過剰キャリアが生成される。そして、レーザ照射を止めるとエネルギーギャップ中の欠陥準位を介した再結合により、一定時間後に熱平衡状態のキャリア密度に戻る。ここで、キャリア密度とμ波の反射率との相関を利用し、反射マイクロ波を検波することで、減衰中のキャリア密度の時間変化を追うことができる。レーザ照射を止めてから十分な時間が経つと、キャリア密度の減衰は最も時定数の長いモードのみが残り、減衰曲線は指数関数1つで表されるようになる。その最も長い時定数を一次モードのライフタイムτ1と呼ぶ。

【0007】

ここで、μ−PCD法から得られた一次モードのライフタイムτ1は一般に試料のバルクライフタイムτbよりも短くなる。一次モードのライフタイムτ1は表面再結合速度の寄与(表面でのキャリア消滅)とバルクライフタイムの寄与(バルク内でのキャリア消滅)の両方を含むためである。

【0008】

μ−PCD法を用いてバルクライフタイムを測定するには、表面再結合速度を可能な限り0に近付けることで表面の影響を排除し、一次モードのライフタイムτ1をバルクライフタイムτbと近似するS−loweringという手法が知られている。この手法においては、例えば、熱酸化膜形成やケミカルパッシベーションといった表面処理が採用される。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開昭59−55013号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

シリコン基板にアルゴン等の不活性ガス雰囲気でアニールを施し、形成されたDZ(Denuded Zone)の一部をガラス基板、シリコン基板、サファイア基板等へ転載する場合、これを繰り返すうちに上記基板側のDZは薄膜化され、やがて消失してしまう。

【0011】

一方で、μ−PCD法を用いた複数層構造(多層構造ともいう)を有する半導体基板の解析の試みは少なかった。表面近傍にDZを有し、内部にIG(Intrinsic Gettering)層を有する半導体基板について、DZの厚さの測定法は提案されていない。

【0012】

そこで、本発明の一態様は、表面にDZを有する半導体基板において、該DZの残存有無を判定することを目的の一とする。

【課題を解決するための手段】

【0013】

本発明の一態様は、表面近傍にDZを有し、内部にIG層を有する半導体基板に対して、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、一次モードのライフタイムτ11および下記数式を用いて、IG層のバルクライフタイムτIGを求め、第1のサンプルの表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGを比較し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGの差が0となったとき、DZが消失したと判定する半導体基板の解析方法である。

【0014】

【数1】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【0015】

本発明の他の一態様は、表面近傍にDZを有し、内部にIG層を有する半導体基板に対して、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、一次モードのライフタイムτ11および下記数式を用いて、IG層のバルクライフタイムτIGを求め、第1のサンプルの表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGを比較し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGの差がIG層のバルクライフタイムτIGに対して、設定した割合以下となった時にDZが僅少であると判定する半導体基板の解析方法である。

【0016】

【数2】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【0017】

ここで、τIGとτ12の大小関係はτIG<τ12となる。第2のサンプルの一次モードライフタイムτ12はτIGに加え、それよりも圧倒的に大きいDZのバルクライフタイムτDZが寄与するためである。また、第2のサンプルにおける表面の寄与は、それが無視できるほどの表面再結合速度に制御されている。

【0018】

ここで、転載工程の繰り返しに伴うDZ幅の減少によるτIGおよびτ12の推移について数値シミュレーション結果を用いて説明する。図3はIG層の外側にDZがある層構造を想定した多層モデル計算の例である。ここでは、τIG=1μsec、τDZ=1msecとした。白丸は表面再結合速度S=1×105cm/secとしてμ−PCDシミュレーションから得られたτ11を数式1に代入して近似的に見積もったτIGである。黒丸は表面再結合速度S=10cm/secとしてμ−PCDシミュレーションから得られたτ12である。DZの薄膜化が進むにつれて、τIGがτ12に近づくことが確認できる。

【0019】

図3に示すようにDZの薄膜化によってτ12は減少してτIGへ近付き、DZが完全に消失するとτ12はτIGにほぼ一致する。

【0020】

転載工程毎に上記の解析を用いてτIGとτ12を取得し、その差(τ12−τIG)が0となったとき、DZが消失したと判定することができる。なお、本明細書では、「τ12とτIGの差が0」という表現は、τ12とτIGの差がほぼ0という意味も含むものとする。

【0021】

また、DZが消失していた場合、そのまま次の転載工程を行うと別基板へ転載される半導体層は結晶欠陥を多く含むIG層を含んでしまう可能性があるため、(τ12−τIG)がτIGに対して、設定した割合以下(例えば、実施の形態1では0.05以下)となった時にDZが僅少であると判定するとより好ましい。

【0022】

また、本発明の他の一態様は、半導体基板のDZは、半導体基板を不活性雰囲気中または水素雰囲気中でアニールすることにより形成してもよい。

【0023】

また、本発明の他の一態様は、半導体基板にシリコン基板を用いてもよい。

【0024】

また、本発明の他の一態様は、一次モードのライフタイムτ11および一次モードのライフタイムτ12は、μ−PCD法を用いて測定してもよい。

【発明の効果】

【0025】

本発明の一態様は、上記方法で解析することにより、DZの残存有無を判定することができる。

【0026】

また、本発明の他の一態様は、上記方法で解析することにより、DZが僅少であると判定することができる。

【図面の簡単な説明】

【0027】

【図1】半導体装置の解析方法の一例を説明する図。

【図2】SOI基板の作製方法を示す図。

【図3】転載工程によるDZの薄膜化を示す図。

【発明を実施するための形態】

【0028】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなく、その形態および詳細を様々に変更しうることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

【0029】

(実施の形態1)

本実施の形態では、表面にDZを有する半導体基板において、DZの残存有無を判定する解析方法および残存するDZが僅少であると判定する解析方法について説明する。本実施の形態の図1では、残存するDZが僅少であると判定する解析方法について示されている。解析は、次の工程A乃至工程Gによって行われる。

【0030】

<工程A:半導体基板の準備(図1のステップ101に対応)>

解析に用いる半導体基板を準備する。半導体基板としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウムまたは炭化シリコンなどの第14族元素を含む結晶半導体基板を用いればよい。

【0031】

本実施の形態に用いる半導体基板の厚さは、薄すぎると基板処理時や測定時のハンドリングが困難になるため、0.5mm以上であることが望ましい。

【0032】

<工程B:DZ、IG層の形成(図1のステップ102に対応)>

次に、半導体基板に対してアルゴン、ヘリウム、窒素等の不活性雰囲気中、または水素雰囲気中でアニールを施すことによりDZが形成される。当該アニールを施すことで、半導体基板の表面近傍の酸素等が外方拡散し、該表面近傍に結晶欠陥が少ない層(DZ)を形成することができる。DZの形成方法は、これに限定されない。

【0033】

そして、表面近傍より内側(DZより内側)には、DZに比べて圧倒的に結晶欠陥の多い層(IG層)となる。すなわち、半導体基板は、表面近傍にDZを有し、内部にIG層を有する。

【0034】

なお、本実施の形態に用いた半導体基板は、シリコン基板であり、DZの膜厚(一般的に10μm以上100μm以下)は、シリコン基板の膜厚(一般的に500μm以上1mm以下)に比較して十分薄い。

【0035】

<工程C:半導体基板における一次モードのライフタイムτ11の取得(図1のステップ103に対応)>

次に、半導体基板表面の表面再結合速度を1×104cm/sec以上に調整する。これを第1のサンプルとする。調整する方法としては、例えば、半導体基板表面に自然酸化膜を形成すればよい。自然酸化膜は一般的に数万程度の非常に大きい表面再結合速度を有している。そして、μ−PCD法によって、一次モードのライフタイムτ11を測定する。

【0036】

半導体基板表面に形成する自然酸化膜は、半導体基板を準備した段階で形成されている自然酸化膜を用いてもよいし、当該自然酸化膜をフッ化水素酸などにより除去して純水によって洗浄した後に、再度、自然酸化膜を形成してもよい。なお、形成する自然酸化膜の厚さは特に限定されない。

【0037】

<工程D:半導体基板におけるIG層のバルクライフタイムτIGの取得(図1のステップ104に対応)>

次に半導体基板におけるIG層のバルクライフタイムτIGを求める。

【0038】

ここで、工程Cにおいて、半導体基板表面の表面再結合速度が1×104cm/sec以上の場合、一次モードのライフタイムτ11は、以下のような数式で近似できる。

【0039】

【数3】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【0040】

得られた一次モードのライフタイムτ11および上記数式を用いて、IG層のバルクライフタイムτIGを算出する。

【0041】

IG層のバルクライフタイムτIGを算出後、表面再結合速度が1×104cm/sec以上である半導体基板表面の膜を除去する。自然酸化膜は、例えば、フッ化水素酸などにより除去すればよい。

【0042】

<工程E:半導体基板の一次モードのライフタイムτ12の測定(図1のステップ105に対応)>

次に、第1のサンプルの半導体基板表面の表面再結合速度を1×102cm/sec以下に調整する。これを第2のサンプルとする。調整する方法としては、例えば、半導体基板表面に熱酸化膜やケミカルパッシベーション膜を形成すればよい。

【0043】

特にケミカルパッシベーション膜は半導体基板の表面再結合速度を小さくすることが可能である。具体的には、表面再結合速度を1cm/sec以上10cm/sec以下にすることが可能である。

【0044】

また、半導体基板表面の表面再結合速度を1×102cm/sec以下に調整する方法として、化学気相蒸着法(CVD法ともいう。)を用いて形成した、窒化シリコンを主成分とする膜、酸化アルミニウムを主成分とする膜またはアモルファスシリコンを主成分とする膜などを用いることができる。例えば、アモルファスシリコンを主成分とする膜であれば、SiH4とH2を用いたRFプラズマCVDにより200℃程度の温度で作製することができる。

【0045】

次に一次モードのライフタイムτ12を測定する。本実施の形態では、μ−PCD法によって、一次モードのライフタイムτ12を測定する。

【0046】

<工程F:判定(図1のステップ106に対応)>

次に、工程Dにおいて取得したIG層のバルクライフタイムτIGと工程Eで測定した一次モードのライフタイムτ12とを比較する。

【0047】

IG層のバルクライフタイムτIGと一次モードのライフタイムτ12とを比較した結果、その差(τ12−τIG)がτIGに対して、設定した割合以下(本実施の形態では、0.05以下)であると残存するDZが僅少であると判定する。そのまま次の転載工程を行うと別基板へ転載される半導体層は結晶欠陥を多く含むIG層を含んでしまう可能性があるため、再度、DZを形成する必要がある。

【0048】

上記の判定法によって残存するDZが僅少であると判定された場合、ステップ102へ戻り、アルゴン等の不活性ガス雰囲気でアニールを施し再びDZを形成する。

【0049】

上記の判定法によってDZがまだ十分あり、転載可能と判定された場合、転載工程を行った後、ステップ103へ戻り、再び同様の解析を行う。

【0050】

また、図1には示していないがIG層のバルクライフタイムτIGと一次モードのライフタイムτ12とを比較した結果、その差(τ12−τIG)が0であるとDZが消失したと判定することができる。

【0051】

以上の工程を行うことにより、算出したバルクライフタイムτIGおよび測定した一次モードのライフタイムτ12のみにより、半導体基板表面のDZの残存有無を非常に簡便に判定することができ、結晶欠陥の多いIG層の別基板への転載を防ぐことができるため、歩留まりの向上が期待できる。

【0052】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0053】

(実施の形態2)

本実施の形態では、実施の形態1の方法により解析した半導体基板を用い、SOI(Silicon On Insulator)基板を作製する方法を示す。

【0054】

まず、半導体基板201を準備する(図2(A)参照)。半導体基板201は、実施の形態1の方法で解析され、DZがまだ十分あると確認されたものを用いる。

【0055】

次いで、半導体基板201にイオン203照射をし、所定の深さに損傷領域205を形成する(図2(B)参照)。

【0056】

損傷領域205は、電界で加速されたイオン(イオンビーム)203を半導体基板201に照射し、半導体基板201の表面から所定の深さにイオン203を導入することで、形成することができる。

【0057】

イオン203の照射は、水素、不活性元素(例えばヘリウム)またはハロゲン(例えばフッ素)等のイオンを用い、イオンドーピング法またはイオン注入法により行うことができる。

【0058】

なお、上記の「イオンドーピング法」とは、原料ガスから生成されるイオン化したガスを質量分離せず、そのまま電界で加速して対象物に照射し、イオン化したガスの元素を対象物に含ませる方式を指す。また、上記の「イオン注入法」とは、原料ガスをプラズマ化し、このプラズマに含まれるイオン種を引き出し、質量分離をして、所定の質量を有するイオン種を加速して、イオンビームとして、対象物に注入する方法である。

【0059】

次に、支持基板207を準備する(図2(C)参照)。

【0060】

支持基板207は、ガラス、プラスチック、セラミック、石英、サファイアなどの絶縁体でなる基板、シリコンなどの半導体でなる基板、金属やステンレスなどの導電体でなる基板を用いることができる。

【0061】

次いで、半導体基板201と支持基板207とを、絶縁層209を介して貼り合わせる(図2(D)参照)。貼り合わせは、半導体基板201の損傷領域205を形成した際にイオン203が導入された側を貼り合わせ面(接合面ともいう)として行う。

【0062】

絶縁層209は、2つの基板を貼り合わせるための接合層として機能するものであり、半導体基板201上に形成してもよく、支持基板207上に形成してもよい。半導体基板201上に絶縁層209を形成する場合、上記イオン203の照射の前に絶縁層209を形成してもよい。

【0063】

絶縁層209は、熱酸化膜やCVD法により、酸化物または窒化物等を、単層または積層させて形成すればよい。具体的な材料としては、酸化シリコン、窒化シリコン、酸化窒化シリコン、または窒化酸化シリコン等が挙げられる。

【0064】

なお、本明細書中において、酸化窒化シリコンなどの「酸化窒化物」とは、その組成として、窒素よりも酸素の含有量が多いものを示す。

【0065】

なお、本明細書中において、窒化酸化シリコンなどの「窒化酸化物」とは、その組成として、酸素よりも窒素の含有量が多いものを示す。

【0066】

ここで、含有量の比較は、ラザフォード後方散乱法および水素前方散乱法の測定結果に基づいて行うこととする。

【0067】

また、貼り合わせを行う前に、2つの基板の貼り合わせ面に洗浄やプラズマ処理などの表面処理を行ってもよい。表面処理を行うことで、親水性または清浄性が向上し、貼り合わせの際の接合強度を向上させることができる。なお、表面処理は、2つの基板の少なくとも一方に行えばよい。また、絶縁層209が形成されている基板に表面処理を行う場合は、絶縁層209の表面に対して行う。

【0068】

次に、加熱処理を行い、損傷領域205において半導体基板201を分離(分断ともいう)する(図2(E)参照)。該分離により、支持基板207上に、絶縁層209と、半導体基板201の一部からなる半導体層211とを順に設けることができる。すなわち、支持基板207上に、半導体基板201の一部からなる半導体層211を転載することができる。

【0069】

なお、加熱処理は、300℃以上、かつ、支持基板207の歪み点未満の温度で行えばよい。

【0070】

このようにして、SOI基板213を作製することができる。

【0071】

実施の形態1の解析方法を用いることで、予め半導体基板のDZの有無を判定することができる。そして、DZの内部に損傷領域を形成し、DZの一部を転載することで、結晶欠陥が少ない半導体層を得ることができる。

【0072】

なお、SOI基板とは、支持基板上に絶縁層を介して半導体層が設けられたものの総称であり、シリコン層を有する基板に限定されない。

【0073】

そして、このSOI基板を用いて、トランジスタまたはダイオード等の半導体装置を作製することができる。

【0074】

また、上記半導体素子を用いて、様々な電子機器を作製することができる。電子機器の一例としては、テレビ、パーソナルコンピュータ、ビデオカメラ、デジタルカメラ、ナビゲーションシステムまたは携帯情報端末(携帯電話、電子書籍または携帯型ゲーム機等)などの表示装置が挙げられる。これら表示装置の表示部または周辺部に、上記半導体素子を用いた回路を設けることができる。

【0075】

また、電子機器の他の一例としては、表示部を必須としないものでもよく、例えば、無線タグ、認証装置、照明装置または空調機などの様々な装置が挙げられる。これらの装置に上記半導体素子を用いた回路を設けることができる。

【0076】

上記回路としては、画素回路、駆動回路、演算回路、センサ回路、電源回路またはメモリ回路など、上記半導体素子を用いることが可能な回路が挙げられる。

【0077】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

【0078】

101 ステップ

102 ステップ

103 ステップ

104 ステップ

105 ステップ

106 ステップ

201 半導体基板

203 イオン

205 損傷領域

207 支持基板

209 絶縁層

211 半導体層

213 SOI基板

【特許請求の範囲】

【請求項1】

表面近傍にDZを有し、内部にIG層を有する半導体基板に対して、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、

前記一次モードのライフタイムτ11および下記数式を用いて、前記IG層のバルクライフタイムτIGを求め、

前記第1のサンプルの表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、

前記一次モードのライフタイムτ12と前記IG層のバルクライフタイムτIGを比較し、

前記一次モードのライフタイムτ12と前記IG層のバルクライフタイムτIGの差が0となったとき、DZが消失したと判定する半導体基板の解析方法。

【数1】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【請求項2】

表面近傍にDZを有し、内部にIG層を有する半導体基板に対して、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、

前記一次モードのライフタイムτ11および下記数式を用いて、前記IG層のバルクライフタイムτIGを求め、

前記第1のサンプルの表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、

前記一次モードのライフタイムτ12と前記IG層のバルクライフタイムτIGを比較し、

前記一次モードのライフタイムτ12と前記IG層のバルクライフタイムτIGの差が前記IG層のバルクライフタイムτIGに対して、設定した割合以下となった時にDZが僅少であると判定する半導体基板の解析方法。

【数2】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【請求項3】

前記DZは、半導体基板を不活性雰囲気中または水素雰囲気中でアニールすることにより形成する請求項1または請求項2に記載の半導体基板の解析方法。

【請求項4】

前記半導体基板は、シリコン基板である請求項1乃至請求項3に記載の半導体基板の解析方法。

【請求項5】

前記一次モードのライフタイムτ11および前記一次モードのライフタイムτ12は、μ−PCD法を用いて測定する請求項1乃至請求項4に記載の半導体基板の解析方法。

【請求項1】

表面近傍にDZを有し、内部にIG層を有する半導体基板に対して、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、

前記一次モードのライフタイムτ11および下記数式を用いて、前記IG層のバルクライフタイムτIGを求め、

前記第1のサンプルの表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、

前記一次モードのライフタイムτ12と前記IG層のバルクライフタイムτIGを比較し、

前記一次モードのライフタイムτ12と前記IG層のバルクライフタイムτIGの差が0となったとき、DZが消失したと判定する半導体基板の解析方法。

【数1】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【請求項2】

表面近傍にDZを有し、内部にIG層を有する半導体基板に対して、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、

前記一次モードのライフタイムτ11および下記数式を用いて、前記IG層のバルクライフタイムτIGを求め、

前記第1のサンプルの表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、

前記一次モードのライフタイムτ12と前記IG層のバルクライフタイムτIGを比較し、

前記一次モードのライフタイムτ12と前記IG層のバルクライフタイムτIGの差が前記IG層のバルクライフタイムτIGに対して、設定した割合以下となった時にDZが僅少であると判定する半導体基板の解析方法。

【数2】

(ただし、数式中、Dは少数キャリア拡散定数、τ11は一次モードのライフタイム、τIGはIG層のバルクライフタイム、Wは半導体基板の厚さをそれぞれ表す。)

【請求項3】

前記DZは、半導体基板を不活性雰囲気中または水素雰囲気中でアニールすることにより形成する請求項1または請求項2に記載の半導体基板の解析方法。

【請求項4】

前記半導体基板は、シリコン基板である請求項1乃至請求項3に記載の半導体基板の解析方法。

【請求項5】

前記一次モードのライフタイムτ11および前記一次モードのライフタイムτ12は、μ−PCD法を用いて測定する請求項1乃至請求項4に記載の半導体基板の解析方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−93434(P2013−93434A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−234579(P2011−234579)

【出願日】平成23年10月26日(2011.10.26)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月26日(2011.10.26)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]