半導体基板セグメント及びその製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法

【課題】三次元積層に好適な半導体基板セグメント及びその製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法を提供する。

【解決手段】半導体基板2のデバイス埋設側にデバイス3、感光性絶縁層4および配線5が設けられていると共に、基板端部側に第1の貫通微細導電体6が設けられている。また、デバイス電極と第1の貫通微細導電体6とが配線5により接続されている。さらにデバイス非埋設側の2bには、第1の貫通微細導電体6の先端である接続端6aが所定長さ突出すように形成されている。

【解決手段】半導体基板2のデバイス埋設側にデバイス3、感光性絶縁層4および配線5が設けられていると共に、基板端部側に第1の貫通微細導電体6が設けられている。また、デバイス電極と第1の貫通微細導電体6とが配線5により接続されている。さらにデバイス非埋設側の2bには、第1の貫通微細導電体6の先端である接続端6aが所定長さ突出すように形成されている。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体基板セグメント及びそれの製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法に係り、特に、半導体セグメントを効率よく製造する技術に関する。

【0002】

【従来の技術】

現在、LSIの更なる高性能化、高密度化を目指したウエハレベルの三次元積層技術に関し、専用のLSIを使った将来の三次元積層技術を前倒しして通常のLSIを使った三次元積層技術の開発が活発化している。

【0003】

かかる通常のLSIを使った三次元積層技術は、ウエハレベルCSP(Chip Size Package)技術に、貫通ビアの形成技術やウエハの薄型技術やチップの積層技術等を導入したものが提案されている。

【0004】

【発明が解決しようとする課題】

しかしながら、このような提案されている従来の方法においては、次のような問題がある。

すなわち、関係主要会社により、独自の開発技術が既に公表されているが、いずれも、(a)多工程であると共に、(b)高精度技術が必要とされる等の不都合および問題がある。従って、実用化には更なる改良が必要とされている。

【0005】

本発明は、このような事情を鑑みてなされたものだって、三次元積層に好適な半導体基板セグメント及びその製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法を提供することを主たる目的とする。

【0006】

【課題を解決する為の手段】

上記目的を達成する為に本発明においては、第1に、請求項1に記載するように、下記工程(a)〜(d)を経て半導体基板セグメントを製造している。そして、請求項7に記載するように、そのようにして製造した半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントの所定数を積層し一体化している。その際に上層側の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている配線に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって樹脂を硬化させて一体化するようにしている。

【0007】

従って、実用化が可能な、三次元積層に好適な半導体基板セグメントを得ることができると共に、かかる半導体基板セグメントを用いて上下層間の導通が可能なように積層し一体化することができて二層又はそれ以上に積層した積層半導体基板を容易に製造することができる。

【0008】

(a)に埋設されたデバイスの周辺部に第1の貫通微細孔のみを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程。

【0009】

(b)フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に前記第1の貫通微細孔と連通したペースト充填用微細孔を形成すると共に、前記ペースト充填用微細孔から前記第1の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程。

【0010】

(c)フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを形成すると共に、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔と前記第1の貫通微細導電体に連通する第2の配線接続用微細孔とを形成する開口パターン形成工程。

【0011】

(d)導電性金属を前記配線形成用開口パターンと前記第1の配線接続用微細孔および第2の配線接続用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線を形成した後、前記第1感光性レジスト層および第2の感光性レジスト層の残存を除去し、前記第1の感光性レジスト層の除去によって前記第1の貫通微細導電体の一端を露出させて接続端を形成する配線形成工程。

【0012】

また、本発明においては、第2に、請求項11に記載するように、下記工程(e)〜(h)を経て半導体基板セグメントを製造している。そして、請求項23に記載の積層半導体基板の製造方法で製造した半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメント上に、上述の請求項1に記載する方法によって製造された半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し一体化している。その際に上層側の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化するようにしている。

【0013】

従って、実用化が可能な、三次元積層に好適な半導体基板セグメントを得ることができると共に、かかる半導体基板セグメントを用いて上下層間の導通が可能なように積層し一体化することができて二層の積層半導体基板を容易に製造することができる。

【0014】

(e)一面側に埋設されたデバイスの周辺部に第1の貫通微細孔と前記第1の貫通微細孔よりも側端側に位置された単数列状の第2の貫通微細孔とを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程。

【0015】

(f)フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に前記第1の貫通微細孔および第2の貫通微細孔それぞれと連通したペースト充填用微細孔を形成すると共に、前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体および第2の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程。

【0016】

(g)フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔及び前記第1の貫通微細導電体に連通する第2の配線接続用微細孔をそれぞれ形成すると共に、前記第2の感光性レジスト層を貫通して前記感光性絶縁層に、前記第2の貫通微細導電体に連通する導電体延設用微細孔を形成する開口パターン形成工程。

【0017】

(h)導電性金属を前記配線形成用開口パターンと前記第1の配線用微細孔および第2の配線用微細孔と前記導電体延設用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線及び前記第2の貫通微細導電体の延設体である階層接続用貫通微細導電体を形成した後、前記第1の感光性レジスト層および第2の感光性レジスト層の残存を除去して前記階層接続用貫通微細導電体の両端を露出させて接続端を形成する配線形成工程。

【0018】

更に、本発明においては、第3に、請求項17に記載するように、下記工程(i)〜(l)を経て半導体基板セグメントを製造し、そして、請求項26に記載するように、そのようにして製造した半導体基板セグメントの所定数を、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N)であるのに対し、上層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N−1)であるように積層すると共に、前記階層接続用貫通微細導電体の個数が(N=1)の樹脂封止済み半導体基板セグメント上に、請求項6に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し、最上層の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接される。また、前記階層接続用貫通微細導電体の下側の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化するようにしている。その為、三層以上に積層した積層半導体基板を容易に得ることができる。

【0019】

(i)一面側に埋設されたデバイスの周辺部に第1の貫通微細孔と前記第1の貫通微細孔よりも側端側に位置された複数列状の第2の貫通微細孔とを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程。

【0020】

(j)フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に、前記第1の貫通微細孔および第2の貫通微細孔それぞれと連通したペースト充填用微細孔を形成すると共に前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体及び第2の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程。

【0021】

(k)フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔及び前記第1の貫通微細導電体に連通する第2の配線接続用微細孔をそれぞれ形成すると共に、前記第2の感光性レジスト層及び前記感光性絶縁層に、前記第2の貫通微細導電体に連通する導電体延設用微細孔を形成する開口パターン形成工程。

【0022】

(l)導電性金属を前記配線形成用開口パターンと前記第1の配線用微細孔および第2の配線用微細孔と前記導電体延設用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線及び前記第2の貫通微細導電体の延設体である階層接続用貫通微細導電体を形成した後、前記第1の感光性レジスト層および第2の感光性レジスト層の残存を除去して前記階層接続用貫通微細導電体の両端を露出させて接続端を形成する配線形成工程。

【0023】

【発明の実施の形態】

以下、図面を参照してこの発明の一実施形態を説明する。

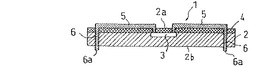

図1は、本発明に係る半導体基板セグメントの縦断面図である。

【0024】

図1に示す半導体基板セグメントの一例が示されているが、図示の半導体基板セグメント1は、半導体基板2に、デバイス3、感光性絶縁層4、配線5及び第1の貫通微細導電体6を設けている。上述のデバイス3は、半導体基板2の一面側に埋設、すなわち、デバイス電極を、デバイス埋設側の面2aの方に向けるように埋設されていると共に、配線5は、デバイス3の前記電極と第1の貫通微細導電体6とに接続されている。

【0025】

また、第1の貫通微細導電体6は、その下端である接続端6aを、半導体基板2の他面側(デバイス非埋設側)の面2bより所定長さに突出していると共に、感光性絶縁層4は、半導体基板2のデバイス埋設側の面2a上に形成されている。

【0026】

なお、図示されていないが、配線5、デバイス3の電極及び第1の貫通微細導電体6は、平面視姿において、微細ピッチで前後方向(以下、Y軸方向という。)及び前記Y軸方向と直交するX軸方向(左右方向)に複数形成されている。このように、第1の貫通微細導電体6は、デバイス3の周辺部(基板の側方)に形成されている。

【0027】

上述の半導体基板セグメント1は、基板被覆工程、導電体形成工程、配線形成前工程、配線形成工程の順を経て製造することができる。この製造に先立って、デバイス埋設側の面2aにデバイス3を埋設すると共に、デバイス3の周辺部に第1の貫通微細孔8のみを形成した半導体基板2が予め準備される(図2(A)参照)。

【0028】

貫通微細孔8は、図示されていないが、平面視姿において、デバイス3を囲むように微細ピッチでX軸方向及びY軸方向に一列状(単数列状)に形成されていると共に、デバイス3の電極は、デバイス埋設側の面2aの方に向けられている。なお、上述とは異なり、必要に応じて、X軸方向のみ又はY軸方向のみに一列状(単数列状)に貫通微細孔8を形成してもよい。

【0029】

また、半導体基板2は、貫通微細孔8を形成した後、電子デバイス等のデバイス3が埋設されて準備される。そして、基板被覆工程において、それのデバイス埋設側の面2a上に、例えば、感光性ポリイミド樹脂で構成された感光性絶縁層4を形成(図2(B)参照)すると共に、デバイス非埋設側の面2b上に、第1の感光性レジスト層9を形成する(図2(C)参照)。なお、感光性レジスト層9は、感光性ドライフィルムで構成されている。

【0030】

次いで、導電体形成工程に移行するが、この工程においては、フォトマスクを用いて第1の感光性レジスト層9側から紫外光を照射して第1の感光性レジスト層9に、貫通微細孔8と連通したペースト充填用微細孔10を形成する。そして、ペースト充填用微細孔10から貫通微細孔8に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体6を形成した後、感光性絶縁層4上に第2の感光性レジスト層11を形成する(図2(D)参照)。この第2の感光性レジスト層11も、上述の第1の感光性レジスト層9と同様に感光性ドライフィルムで構成されている。

【0031】

上述の導電性ペーストの充填は、ペースト充填用微細孔10を上側に位置させた状態において、大気圧よりも低い第1の気圧下で、第1の感光性レジスト層9上に、例えば、ノズルから導電性ペーストを吐出して塗布し、それをスキージで均して所定厚さに印刷することによってペースト充填用微細孔10の入口部に導電性ペーストを押し込み、その後、差圧充填する。このような作業は、減圧チャンバー内で行う。その際、ペースト充填用微細孔10を閉塞するように導電性ペーストを吐出して塗布するのが好ましいが、それに限定されず、他の適当な態様に行ってもよい。

【0032】

また、導電性ペーストを塗布した後の前記差圧充填は、大気圧よりも低い第1の気圧を大気圧に戻したり、或るいは、第1の気圧を上昇させて、第1の気圧より高いが大気圧より低い第2の気圧に制御したりして行う。両方法によって、高アスペクト比の第1の貫通微細孔8に対して高粘性の導電性ペーストを、ボイドの発生を防止しながら迅速、且つ均一密度に充填することができる。

【0033】

なお、大気圧に戻さない場合は、第2の気圧下で必要に応じて補充印刷を行うことができる点で大気圧に戻す場合よりも有利である。導電性ペーストは、導電性物質及び樹脂でなる熱硬化性のペーストであって、金、銀、銅、錫、炭素等の導電性物質のいずれか一つ又は複数を含有している。無溶剤タイプで電気抵抗が小さく、且つフィラーの粒径が微細で粘性が低いものが好ましい。そのような導電性ペーストによると、硬化後に高い導電性を発現することができる。

【0034】

半導体基板2の代表例としてシリコン基板が挙げられるが、これ以外に、例えば、GaAs基板等であってもよい。シリコン基板の厚さは50μm〜725μmであり、且つそれに形成されている貫通微細孔8の径は100μm以下、一般には数十μmであって、その孔壁にシリコン酸化膜からなる絶縁層が形成されている。

【0035】

また、貫通微細孔8を形成する為の手段の一例として光励起電解研磨法が挙げられるが、他の手段であってもよい。かかる光励起電解研磨法は、低コスト、高密度パターニングが期待できる湿式エッチングプロセスであり、他の方法に比して深掘、高アスペクト比の貫通孔を形成するのに適している。

【0036】

上述の第1の気圧は、200Pa以下に保たれる。かかる圧力は、貫通微細孔8中の残存空気と導電性ペーストから出るガスとのバランスを考慮して決められる。一方、上述の第2の気圧は、第1の気圧よりも100Pa以上高いが大気圧よりも低いように制御される。

【0037】

貫通微細孔8は、例えば、孔径(D)が50μm、深さ(L)が700μmといった如くに高アスペクト比(L/D)の孔である為に、高粘性の導電性ペーストを迅速、且つ均一密度に充填させることが難しいが、上述の差圧充填によって迅速、且つ均一密度に充填することができる。

【0038】

また、貫通微細孔8に充填された導電性ペーストは、その後、例えば、120℃で30分〜1時間の加熱処理によって半硬化される、結果、第1の貫通微細導電体6を形成することができる。これは、上述の差圧充填を終えた半導体基板2を減圧チャンバーから加熱処理室へ移送して行う。微細な第1の貫通微細導電体6を半硬化させているから、かかる移送等に際し、破損若しくは過度な変形を防止することができる。そして、その後に感光性絶縁層4上に第2の感光性レジスト層11を形成する。この第2の感光性レジスト層11も、第1の感光性レジスト層9と同様に感光性ドライフィルムで構成される。

【0039】

次に、開口パターン形成工程に移行する。この工程においては、フォトマスクを用いて第2の感光性レジスト層11側から紫外光を照射して、第2の感光性レジスト層11に配線形成用開口パターン12を形成すると共に、感光性絶縁層4に、デバイス3の電極に連通する第1の配線接続用微細孔13と、第1の貫通微細導電体6に連通する第2の配線接続用微細孔14とを形成する(図2(E)参照)。その際に紫外光の照射量は、所定量となるように制御される。

【0040】

次いで、配線形成工程に移行する。この配線形成工程においては、銅等の導電性金属を配線形成用開口パターン12及び第1,2配線接続用微細孔14にメッキしてデバイス3の電極と第1の貫通微細導電体6とに接続された配線15を形成する(図2(F)参照)。かかるメッキは一般に電解メッキが用いられるが、他のメッキであってもよい。そして、その後に第2の感光性レジスト層11の残存を除去すると共に、第1の感光性レジスト層9も除去する。従って、第1の感光性レジスト層9の除去により、第1の貫通微細導電体6の一端を露出させて接続端6aを形成することができる。

【0041】

このようにして、図1に示す如くの半導体基板セグメント1を次々と製造することができる。なお、第1の感光性レジスト層9及び第2の感光性レジスト層11の除去は、常法によって除去すればよい。また、上述のようにして製造された半導体基板セグメント1は、必要に応じて所定の環境下に保管される。そして、積層半導体基板を製造するに当って配線5が適時に樹脂封止される。

【0042】

図3において、樹脂封止層16を形成した状態が示されている。樹脂封止層16の形成は、大気圧より低い気圧下で行うのが好ましい。樹脂中にボイドが形成されるのを防止する為である。上述の樹脂封止層16は、半硬化状態に保たれ、そのような樹脂封止済み半導体基板セグメント17を準備し、それを積層する。

【0043】

図4において二層に積層した状態が示されていると共に、図5において三層に積層した状態が示されているが、このように、半硬化状態に保たれた樹脂封止済み半導体基板セグメント17の複数を、上層側の樹脂封止済み半導体基板セグメント17に形成されている第1の貫通微細導体6の接続端6aが、下層側の樹脂封止済み半導体基板セグメント17に形成されている配線5に当接された状態に積層する。なお、積層数は、必要に応じて適宜に選択される。

【0044】

そして、かかる積層体を大気圧より低い気圧下(例えば、220Pa以下)において加熱しながら加圧することによって前記樹脂を硬化させて一体化することができる。かかる加熱加圧の手段として、熱プレス等を用いることができると共に、前記樹脂を硬化させる為の加熱温度は、例えば、150℃以下に制御する。したがって、上下層間を確実に導通させるように積層一体化することができて量産化を図ることができる。

【0045】

以上、同一タイプの樹脂封止済み半導体基板セグメント17を積層一体化して積層半導体基板を製造する例について述べたが、本発明においては、図10,図11に示すように、異なるタイプの樹脂封止済み半導体基板セグメントを積層し一体化して積層半導体基板を製造してもよい。

【0046】

図10は、図9の樹脂封止済み半導体基板セグメント17b上に、図8の樹脂封止済み半導体基板セグメント17aを積層し一体化した二層の積層半導体基板を示している。樹脂封止済み半導体基板セグメント17aは、図3に示されている上述の樹脂封止済み半導体基板セグメント17と同タイプである。それに対し、樹脂封止済み半導体基板セグメント17bは、階層接続用貫通微細導電体18を形成している点で相違している。

【0047】

樹脂封止済み半導体基板セグメント17bは、階層接続用貫通微細導電体18を形成した半導体基板セグメント1b(図6参照)に樹脂封止層16を形成したものである。なお、階層接続用貫通微細導電体18は、デバイス3の周辺部に形成されている第1の貫通微細導電体6よりも側端側に位置され、且つその上端及び下端が突出されて接続端18a,18bを形成していると共に、第1の貫通微細導電体6と同様に、平面視姿において、デバイス3を囲むように、微細ピッチでX軸方向及びY軸方向に複数形成されている。

【0048】

上述の半導体基板セグメント1b(図6参照)は、基板被覆工程、導電体形成工程、開口パターン形成工程、配線形成工程の順を経て製造することができる。その製造フローが図7に示されている。上述の半導体基板セグメント1(図1参照)を製造する場合と同様に、それに先立って、デバイス埋設側の面2aにデバイス3を埋設すると共に、デバイス3の周辺部に第1の貫通微細孔8及び第2の貫通微細孔21を形成した半導体基板2が予め準備される(図7(A)参照)。

【0049】

第1の貫通微細孔8及び第2の貫通微細孔21はそれぞれが、平面視姿において、デバイス3を囲むように微細ピッチでX軸方向及びY軸方向に一列状(単数列状)に形成されていると共に、デバイス3の電極は、デバイス埋設側の面2aの方に向けられている。

【0050】

なお、上述とは異なり、必要に応じて、X軸方向のみ又はY軸方向のみに一列状(単数列状)に第1の貫通微細孔8及び第2の貫通微細孔21それぞれを形成してもよい。基板被覆工程、導電体形成工程、開口パターン形成工程及び配線形成工程についても半導体基板セグメント1を製造する場合とほぼ同様である。

【0051】

以下、図7に示す製造フローにおいて、上述の図2に示す製造フローと同じ工程については、ここでの詳述は省略し、異なる工程について説明する。導電体形成工程において第2の貫通微細孔21に連通されたペースト充填用微細孔10から第2の貫通微細孔21に導電性ぺーストを充填して第2の貫通微細導電体22を形成する点(図7(D)参照)と、開口パターン形成工程において第2の感光性レジスト層11及び感光性絶縁層4に第2の貫通微細導電体22に連通する導電体延設用微細孔23を形成する点(図7(E)参照)と、配線形成工程において第2の貫通微細導電体22の延設体である階層接続用貫通微細導電体18を形成する点(図7(F)参照)とで実質的に異なっているのにすぎない。

【0052】

上述の半導体基板セグメント1bは、階層接続用貫通微細導電体18を一列状(単数列状)に形成したものであるが、第2の貫通微細孔21を複数列状に形成した半導体基板2を準備することによって、階層接続用貫通微細導電体18を複数列状に形成した半導体基板セグメントを製造することができ、そして、それの配線5及び階層接続用貫通微細導電体18の上側の接続端18bを被覆するように樹脂封止層16を形成することによって、例えば、図11に示されている樹脂封止済み半導体基板セグメント17cのような他のタイプの樹脂封止済みセグメントを製造することができる。

【0053】

図11に示されている樹脂封止済み半導体基板セグメント17cは、階層接続用貫通微細導電体18を二列状に形成したものであって、配線5及び階層接続用貫通微細導電体18の上側の接続端18bを被覆するように樹脂封止層16を形成している。

【0054】

図示の三層に積層する例からして明らかのように、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N)であるのに対し、上層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N−1)であるように積層すると共に、前記階層接続用貫通微細導電体の個数が(N=1)の樹脂封止済み半導体基板セグメント上に、階層接続用貫通微細導電体を形成していない半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し、最上層の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接される。また、前記階層接続用貫通微細導電体の下側の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接させるように積層することができると共に、それを大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化して多層の積層半導体基板を製造することができる。

【0055】

【発明の効果】

以上の説明から明らかなように、本発明によると、半導体基板のデバイス埋設側の面上に感光性絶縁物層を形成すると共に、デバイス非埋設側に第1の感光性レジスト層を形成する。また、第1の感光性レジスト層にペースト充填用微細孔を形成し、導電性ペーストを充填して半硬化させて貫通微細導電体を形成した後に、感光性絶縁層を第2の感光性レジスト層を形成する。また、紫外線照射により第2の感光性レジスト層に配線形成用開口パターンを形成すると共に、感光性絶縁層にデバイス電極に連通する第1の配線接続用微細孔と第1の貫通微細導電体に連通する第2の接続用微細孔と形成する。さらに、配線形成用開口パターン、配線接続用微細孔、および貫通微細導電体とに接続された配線に導電性金属をメッキし、デバイス電極と第1の貫通微細導電体とを接続する配線を形成する。その後、第1の感光性レジスト層の除去によって第1の貫通微細導電体の一端を露出させることによって効率よく積層可能な半導体基板セグメントを製造することができる。

【0056】

さらに、この製造された半導体セグメントを用いて積層することによって、上下層間の導通が可能となる。その結果、二層又はそれ以上に積層した積層半導体基板を容易に得ることができる。

【図面の簡単な説明】

【図1】本発明に係る半導体基板セグメントの一例を示す縦断面図である。

【図2】図1に示す半導体基板セグメントの製造フローを示す図であって、(A)は被覆層形成工程前の半導体基板の縦断面を示し、(B)は被覆層形成工程において感光性絶縁層を形成した半導体基板の縦断面を示し、(C)は導電体形成工程において第1の感光レジスト層にペースト充填用微細孔を形成した半導体基板の縦断面を示し、(D)は導電体形成工程において第1の貫通微細導電体を形成した半導体基板の縦断面を示し、(E)は開口パターン形成工程において第1,2の配線接続用微細孔等を形成した半導体基板の縦断面を示し、(F)は配線形成工程において配線を形成した半導体基板の縦断面を示している。

【図3】図1の半導体基板セグメントに樹脂封止層を形成した樹脂封止済み半導体基板セグメントの縦断面図である。

【図4】図3の樹脂封止済み半導体基板セグメントを二層に積層した状態を示す縦断面図である。

【図5】図3の樹脂封止済み半導体基板セグメントを三層に積層した状態を示す縦断面図である。

【図6】本発明に係る他の半導体基板セグメントの一例を示す縦断面図である。

【図7】図6に示す半導体基板セグメントの製造フローを示す図であって、(A)は被覆層形成工程前の半導体基板の縦断面を示し、(B)は被覆層形成工程において感光性絶縁層を形成した半導体基板の縦断面を示し、(C)は導電体形成工程において第1の感光レジスト層にペースト充填用微細孔を形成した半導体基板の縦断面を示し、(D)は導電体形成工程において第1,2の貫通微細導電体を形成した半導体基板の縦断面を示し、(E)は開口パターン形成工程において第1,2の配線接続用微細孔等を形成した半導体基板の縦断面を示し、(F)は配線形成工程において配線及び階層接続用貫通微細導電体を形成した半導体基板の縦断面を示している。

【図8】最上層に積層する樹脂封止済み半導体基板セグメントの縦断面図である。

【図9】図6の半導体基板セグメントに樹脂封止層を形成した樹脂封止済み半導体基板セグメントの縦断面図である。

【図10】図9の樹脂封止済み半導体基板セグメント上に図8の樹脂封止済み半導体基板セグメントを積層した状態を示す縦断面図である。

【図11】2個の階層接続用貫通微細導電体を形成した樹脂封止済み半導体基板セグメント上に、1個の階層接続用貫通微細導電体を形成した樹脂封止済み半導体基板セグメントを積層すると共に、その上に第1の貫通微細導電体のみ形成した樹脂封止済み半導体基板セグメントを積層した状態を示す縦断面図である。

【符号の説明】

1,1b…半導体基板セグメント

2 … 半導体基板

2a… デバイス埋設側の面

2b… デバイス非埋設側の面

3 … デバイス

4 … 感光性絶縁層

5 … 配線

6 … 第1の貫通微細孔導電体

6a… 接続端

8 … 第1の貫通微細孔

9 … 第1の感光性レジスト層

10 … ペースト充填用微細孔

11 … 第2の感光性レジスト層

12 … 配線形成用開口パターン

13 … 第1の配線接続用微細孔

14 … 第2の配線接続用微細孔

15 … 配線

16 … 樹脂封止層

17(17a〜17c)… 樹脂封止済み半導体基板セグメント

18 … 階層接続用貫通微細導電体

18a,18b… 接続端

21 … 第2の貫通微細孔

22 … 第2の貫通微細孔導電体

23 … 導電体延設用微細孔

【0001】

【発明の属する技術分野】

本発明は、半導体基板セグメント及びそれの製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法に係り、特に、半導体セグメントを効率よく製造する技術に関する。

【0002】

【従来の技術】

現在、LSIの更なる高性能化、高密度化を目指したウエハレベルの三次元積層技術に関し、専用のLSIを使った将来の三次元積層技術を前倒しして通常のLSIを使った三次元積層技術の開発が活発化している。

【0003】

かかる通常のLSIを使った三次元積層技術は、ウエハレベルCSP(Chip Size Package)技術に、貫通ビアの形成技術やウエハの薄型技術やチップの積層技術等を導入したものが提案されている。

【0004】

【発明が解決しようとする課題】

しかしながら、このような提案されている従来の方法においては、次のような問題がある。

すなわち、関係主要会社により、独自の開発技術が既に公表されているが、いずれも、(a)多工程であると共に、(b)高精度技術が必要とされる等の不都合および問題がある。従って、実用化には更なる改良が必要とされている。

【0005】

本発明は、このような事情を鑑みてなされたものだって、三次元積層に好適な半導体基板セグメント及びその製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法を提供することを主たる目的とする。

【0006】

【課題を解決する為の手段】

上記目的を達成する為に本発明においては、第1に、請求項1に記載するように、下記工程(a)〜(d)を経て半導体基板セグメントを製造している。そして、請求項7に記載するように、そのようにして製造した半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントの所定数を積層し一体化している。その際に上層側の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている配線に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって樹脂を硬化させて一体化するようにしている。

【0007】

従って、実用化が可能な、三次元積層に好適な半導体基板セグメントを得ることができると共に、かかる半導体基板セグメントを用いて上下層間の導通が可能なように積層し一体化することができて二層又はそれ以上に積層した積層半導体基板を容易に製造することができる。

【0008】

(a)に埋設されたデバイスの周辺部に第1の貫通微細孔のみを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程。

【0009】

(b)フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に前記第1の貫通微細孔と連通したペースト充填用微細孔を形成すると共に、前記ペースト充填用微細孔から前記第1の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程。

【0010】

(c)フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを形成すると共に、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔と前記第1の貫通微細導電体に連通する第2の配線接続用微細孔とを形成する開口パターン形成工程。

【0011】

(d)導電性金属を前記配線形成用開口パターンと前記第1の配線接続用微細孔および第2の配線接続用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線を形成した後、前記第1感光性レジスト層および第2の感光性レジスト層の残存を除去し、前記第1の感光性レジスト層の除去によって前記第1の貫通微細導電体の一端を露出させて接続端を形成する配線形成工程。

【0012】

また、本発明においては、第2に、請求項11に記載するように、下記工程(e)〜(h)を経て半導体基板セグメントを製造している。そして、請求項23に記載の積層半導体基板の製造方法で製造した半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメント上に、上述の請求項1に記載する方法によって製造された半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し一体化している。その際に上層側の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化するようにしている。

【0013】

従って、実用化が可能な、三次元積層に好適な半導体基板セグメントを得ることができると共に、かかる半導体基板セグメントを用いて上下層間の導通が可能なように積層し一体化することができて二層の積層半導体基板を容易に製造することができる。

【0014】

(e)一面側に埋設されたデバイスの周辺部に第1の貫通微細孔と前記第1の貫通微細孔よりも側端側に位置された単数列状の第2の貫通微細孔とを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程。

【0015】

(f)フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に前記第1の貫通微細孔および第2の貫通微細孔それぞれと連通したペースト充填用微細孔を形成すると共に、前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体および第2の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程。

【0016】

(g)フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔及び前記第1の貫通微細導電体に連通する第2の配線接続用微細孔をそれぞれ形成すると共に、前記第2の感光性レジスト層を貫通して前記感光性絶縁層に、前記第2の貫通微細導電体に連通する導電体延設用微細孔を形成する開口パターン形成工程。

【0017】

(h)導電性金属を前記配線形成用開口パターンと前記第1の配線用微細孔および第2の配線用微細孔と前記導電体延設用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線及び前記第2の貫通微細導電体の延設体である階層接続用貫通微細導電体を形成した後、前記第1の感光性レジスト層および第2の感光性レジスト層の残存を除去して前記階層接続用貫通微細導電体の両端を露出させて接続端を形成する配線形成工程。

【0018】

更に、本発明においては、第3に、請求項17に記載するように、下記工程(i)〜(l)を経て半導体基板セグメントを製造し、そして、請求項26に記載するように、そのようにして製造した半導体基板セグメントの所定数を、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N)であるのに対し、上層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N−1)であるように積層すると共に、前記階層接続用貫通微細導電体の個数が(N=1)の樹脂封止済み半導体基板セグメント上に、請求項6に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し、最上層の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接される。また、前記階層接続用貫通微細導電体の下側の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化するようにしている。その為、三層以上に積層した積層半導体基板を容易に得ることができる。

【0019】

(i)一面側に埋設されたデバイスの周辺部に第1の貫通微細孔と前記第1の貫通微細孔よりも側端側に位置された複数列状の第2の貫通微細孔とを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程。

【0020】

(j)フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に、前記第1の貫通微細孔および第2の貫通微細孔それぞれと連通したペースト充填用微細孔を形成すると共に前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体及び第2の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程。

【0021】

(k)フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔及び前記第1の貫通微細導電体に連通する第2の配線接続用微細孔をそれぞれ形成すると共に、前記第2の感光性レジスト層及び前記感光性絶縁層に、前記第2の貫通微細導電体に連通する導電体延設用微細孔を形成する開口パターン形成工程。

【0022】

(l)導電性金属を前記配線形成用開口パターンと前記第1の配線用微細孔および第2の配線用微細孔と前記導電体延設用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線及び前記第2の貫通微細導電体の延設体である階層接続用貫通微細導電体を形成した後、前記第1の感光性レジスト層および第2の感光性レジスト層の残存を除去して前記階層接続用貫通微細導電体の両端を露出させて接続端を形成する配線形成工程。

【0023】

【発明の実施の形態】

以下、図面を参照してこの発明の一実施形態を説明する。

図1は、本発明に係る半導体基板セグメントの縦断面図である。

【0024】

図1に示す半導体基板セグメントの一例が示されているが、図示の半導体基板セグメント1は、半導体基板2に、デバイス3、感光性絶縁層4、配線5及び第1の貫通微細導電体6を設けている。上述のデバイス3は、半導体基板2の一面側に埋設、すなわち、デバイス電極を、デバイス埋設側の面2aの方に向けるように埋設されていると共に、配線5は、デバイス3の前記電極と第1の貫通微細導電体6とに接続されている。

【0025】

また、第1の貫通微細導電体6は、その下端である接続端6aを、半導体基板2の他面側(デバイス非埋設側)の面2bより所定長さに突出していると共に、感光性絶縁層4は、半導体基板2のデバイス埋設側の面2a上に形成されている。

【0026】

なお、図示されていないが、配線5、デバイス3の電極及び第1の貫通微細導電体6は、平面視姿において、微細ピッチで前後方向(以下、Y軸方向という。)及び前記Y軸方向と直交するX軸方向(左右方向)に複数形成されている。このように、第1の貫通微細導電体6は、デバイス3の周辺部(基板の側方)に形成されている。

【0027】

上述の半導体基板セグメント1は、基板被覆工程、導電体形成工程、配線形成前工程、配線形成工程の順を経て製造することができる。この製造に先立って、デバイス埋設側の面2aにデバイス3を埋設すると共に、デバイス3の周辺部に第1の貫通微細孔8のみを形成した半導体基板2が予め準備される(図2(A)参照)。

【0028】

貫通微細孔8は、図示されていないが、平面視姿において、デバイス3を囲むように微細ピッチでX軸方向及びY軸方向に一列状(単数列状)に形成されていると共に、デバイス3の電極は、デバイス埋設側の面2aの方に向けられている。なお、上述とは異なり、必要に応じて、X軸方向のみ又はY軸方向のみに一列状(単数列状)に貫通微細孔8を形成してもよい。

【0029】

また、半導体基板2は、貫通微細孔8を形成した後、電子デバイス等のデバイス3が埋設されて準備される。そして、基板被覆工程において、それのデバイス埋設側の面2a上に、例えば、感光性ポリイミド樹脂で構成された感光性絶縁層4を形成(図2(B)参照)すると共に、デバイス非埋設側の面2b上に、第1の感光性レジスト層9を形成する(図2(C)参照)。なお、感光性レジスト層9は、感光性ドライフィルムで構成されている。

【0030】

次いで、導電体形成工程に移行するが、この工程においては、フォトマスクを用いて第1の感光性レジスト層9側から紫外光を照射して第1の感光性レジスト層9に、貫通微細孔8と連通したペースト充填用微細孔10を形成する。そして、ペースト充填用微細孔10から貫通微細孔8に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体6を形成した後、感光性絶縁層4上に第2の感光性レジスト層11を形成する(図2(D)参照)。この第2の感光性レジスト層11も、上述の第1の感光性レジスト層9と同様に感光性ドライフィルムで構成されている。

【0031】

上述の導電性ペーストの充填は、ペースト充填用微細孔10を上側に位置させた状態において、大気圧よりも低い第1の気圧下で、第1の感光性レジスト層9上に、例えば、ノズルから導電性ペーストを吐出して塗布し、それをスキージで均して所定厚さに印刷することによってペースト充填用微細孔10の入口部に導電性ペーストを押し込み、その後、差圧充填する。このような作業は、減圧チャンバー内で行う。その際、ペースト充填用微細孔10を閉塞するように導電性ペーストを吐出して塗布するのが好ましいが、それに限定されず、他の適当な態様に行ってもよい。

【0032】

また、導電性ペーストを塗布した後の前記差圧充填は、大気圧よりも低い第1の気圧を大気圧に戻したり、或るいは、第1の気圧を上昇させて、第1の気圧より高いが大気圧より低い第2の気圧に制御したりして行う。両方法によって、高アスペクト比の第1の貫通微細孔8に対して高粘性の導電性ペーストを、ボイドの発生を防止しながら迅速、且つ均一密度に充填することができる。

【0033】

なお、大気圧に戻さない場合は、第2の気圧下で必要に応じて補充印刷を行うことができる点で大気圧に戻す場合よりも有利である。導電性ペーストは、導電性物質及び樹脂でなる熱硬化性のペーストであって、金、銀、銅、錫、炭素等の導電性物質のいずれか一つ又は複数を含有している。無溶剤タイプで電気抵抗が小さく、且つフィラーの粒径が微細で粘性が低いものが好ましい。そのような導電性ペーストによると、硬化後に高い導電性を発現することができる。

【0034】

半導体基板2の代表例としてシリコン基板が挙げられるが、これ以外に、例えば、GaAs基板等であってもよい。シリコン基板の厚さは50μm〜725μmであり、且つそれに形成されている貫通微細孔8の径は100μm以下、一般には数十μmであって、その孔壁にシリコン酸化膜からなる絶縁層が形成されている。

【0035】

また、貫通微細孔8を形成する為の手段の一例として光励起電解研磨法が挙げられるが、他の手段であってもよい。かかる光励起電解研磨法は、低コスト、高密度パターニングが期待できる湿式エッチングプロセスであり、他の方法に比して深掘、高アスペクト比の貫通孔を形成するのに適している。

【0036】

上述の第1の気圧は、200Pa以下に保たれる。かかる圧力は、貫通微細孔8中の残存空気と導電性ペーストから出るガスとのバランスを考慮して決められる。一方、上述の第2の気圧は、第1の気圧よりも100Pa以上高いが大気圧よりも低いように制御される。

【0037】

貫通微細孔8は、例えば、孔径(D)が50μm、深さ(L)が700μmといった如くに高アスペクト比(L/D)の孔である為に、高粘性の導電性ペーストを迅速、且つ均一密度に充填させることが難しいが、上述の差圧充填によって迅速、且つ均一密度に充填することができる。

【0038】

また、貫通微細孔8に充填された導電性ペーストは、その後、例えば、120℃で30分〜1時間の加熱処理によって半硬化される、結果、第1の貫通微細導電体6を形成することができる。これは、上述の差圧充填を終えた半導体基板2を減圧チャンバーから加熱処理室へ移送して行う。微細な第1の貫通微細導電体6を半硬化させているから、かかる移送等に際し、破損若しくは過度な変形を防止することができる。そして、その後に感光性絶縁層4上に第2の感光性レジスト層11を形成する。この第2の感光性レジスト層11も、第1の感光性レジスト層9と同様に感光性ドライフィルムで構成される。

【0039】

次に、開口パターン形成工程に移行する。この工程においては、フォトマスクを用いて第2の感光性レジスト層11側から紫外光を照射して、第2の感光性レジスト層11に配線形成用開口パターン12を形成すると共に、感光性絶縁層4に、デバイス3の電極に連通する第1の配線接続用微細孔13と、第1の貫通微細導電体6に連通する第2の配線接続用微細孔14とを形成する(図2(E)参照)。その際に紫外光の照射量は、所定量となるように制御される。

【0040】

次いで、配線形成工程に移行する。この配線形成工程においては、銅等の導電性金属を配線形成用開口パターン12及び第1,2配線接続用微細孔14にメッキしてデバイス3の電極と第1の貫通微細導電体6とに接続された配線15を形成する(図2(F)参照)。かかるメッキは一般に電解メッキが用いられるが、他のメッキであってもよい。そして、その後に第2の感光性レジスト層11の残存を除去すると共に、第1の感光性レジスト層9も除去する。従って、第1の感光性レジスト層9の除去により、第1の貫通微細導電体6の一端を露出させて接続端6aを形成することができる。

【0041】

このようにして、図1に示す如くの半導体基板セグメント1を次々と製造することができる。なお、第1の感光性レジスト層9及び第2の感光性レジスト層11の除去は、常法によって除去すればよい。また、上述のようにして製造された半導体基板セグメント1は、必要に応じて所定の環境下に保管される。そして、積層半導体基板を製造するに当って配線5が適時に樹脂封止される。

【0042】

図3において、樹脂封止層16を形成した状態が示されている。樹脂封止層16の形成は、大気圧より低い気圧下で行うのが好ましい。樹脂中にボイドが形成されるのを防止する為である。上述の樹脂封止層16は、半硬化状態に保たれ、そのような樹脂封止済み半導体基板セグメント17を準備し、それを積層する。

【0043】

図4において二層に積層した状態が示されていると共に、図5において三層に積層した状態が示されているが、このように、半硬化状態に保たれた樹脂封止済み半導体基板セグメント17の複数を、上層側の樹脂封止済み半導体基板セグメント17に形成されている第1の貫通微細導体6の接続端6aが、下層側の樹脂封止済み半導体基板セグメント17に形成されている配線5に当接された状態に積層する。なお、積層数は、必要に応じて適宜に選択される。

【0044】

そして、かかる積層体を大気圧より低い気圧下(例えば、220Pa以下)において加熱しながら加圧することによって前記樹脂を硬化させて一体化することができる。かかる加熱加圧の手段として、熱プレス等を用いることができると共に、前記樹脂を硬化させる為の加熱温度は、例えば、150℃以下に制御する。したがって、上下層間を確実に導通させるように積層一体化することができて量産化を図ることができる。

【0045】

以上、同一タイプの樹脂封止済み半導体基板セグメント17を積層一体化して積層半導体基板を製造する例について述べたが、本発明においては、図10,図11に示すように、異なるタイプの樹脂封止済み半導体基板セグメントを積層し一体化して積層半導体基板を製造してもよい。

【0046】

図10は、図9の樹脂封止済み半導体基板セグメント17b上に、図8の樹脂封止済み半導体基板セグメント17aを積層し一体化した二層の積層半導体基板を示している。樹脂封止済み半導体基板セグメント17aは、図3に示されている上述の樹脂封止済み半導体基板セグメント17と同タイプである。それに対し、樹脂封止済み半導体基板セグメント17bは、階層接続用貫通微細導電体18を形成している点で相違している。

【0047】

樹脂封止済み半導体基板セグメント17bは、階層接続用貫通微細導電体18を形成した半導体基板セグメント1b(図6参照)に樹脂封止層16を形成したものである。なお、階層接続用貫通微細導電体18は、デバイス3の周辺部に形成されている第1の貫通微細導電体6よりも側端側に位置され、且つその上端及び下端が突出されて接続端18a,18bを形成していると共に、第1の貫通微細導電体6と同様に、平面視姿において、デバイス3を囲むように、微細ピッチでX軸方向及びY軸方向に複数形成されている。

【0048】

上述の半導体基板セグメント1b(図6参照)は、基板被覆工程、導電体形成工程、開口パターン形成工程、配線形成工程の順を経て製造することができる。その製造フローが図7に示されている。上述の半導体基板セグメント1(図1参照)を製造する場合と同様に、それに先立って、デバイス埋設側の面2aにデバイス3を埋設すると共に、デバイス3の周辺部に第1の貫通微細孔8及び第2の貫通微細孔21を形成した半導体基板2が予め準備される(図7(A)参照)。

【0049】

第1の貫通微細孔8及び第2の貫通微細孔21はそれぞれが、平面視姿において、デバイス3を囲むように微細ピッチでX軸方向及びY軸方向に一列状(単数列状)に形成されていると共に、デバイス3の電極は、デバイス埋設側の面2aの方に向けられている。

【0050】

なお、上述とは異なり、必要に応じて、X軸方向のみ又はY軸方向のみに一列状(単数列状)に第1の貫通微細孔8及び第2の貫通微細孔21それぞれを形成してもよい。基板被覆工程、導電体形成工程、開口パターン形成工程及び配線形成工程についても半導体基板セグメント1を製造する場合とほぼ同様である。

【0051】

以下、図7に示す製造フローにおいて、上述の図2に示す製造フローと同じ工程については、ここでの詳述は省略し、異なる工程について説明する。導電体形成工程において第2の貫通微細孔21に連通されたペースト充填用微細孔10から第2の貫通微細孔21に導電性ぺーストを充填して第2の貫通微細導電体22を形成する点(図7(D)参照)と、開口パターン形成工程において第2の感光性レジスト層11及び感光性絶縁層4に第2の貫通微細導電体22に連通する導電体延設用微細孔23を形成する点(図7(E)参照)と、配線形成工程において第2の貫通微細導電体22の延設体である階層接続用貫通微細導電体18を形成する点(図7(F)参照)とで実質的に異なっているのにすぎない。

【0052】

上述の半導体基板セグメント1bは、階層接続用貫通微細導電体18を一列状(単数列状)に形成したものであるが、第2の貫通微細孔21を複数列状に形成した半導体基板2を準備することによって、階層接続用貫通微細導電体18を複数列状に形成した半導体基板セグメントを製造することができ、そして、それの配線5及び階層接続用貫通微細導電体18の上側の接続端18bを被覆するように樹脂封止層16を形成することによって、例えば、図11に示されている樹脂封止済み半導体基板セグメント17cのような他のタイプの樹脂封止済みセグメントを製造することができる。

【0053】

図11に示されている樹脂封止済み半導体基板セグメント17cは、階層接続用貫通微細導電体18を二列状に形成したものであって、配線5及び階層接続用貫通微細導電体18の上側の接続端18bを被覆するように樹脂封止層16を形成している。

【0054】

図示の三層に積層する例からして明らかのように、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N)であるのに対し、上層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N−1)であるように積層すると共に、前記階層接続用貫通微細導電体の個数が(N=1)の樹脂封止済み半導体基板セグメント上に、階層接続用貫通微細導電体を形成していない半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し、最上層の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接される。また、前記階層接続用貫通微細導電体の下側の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接させるように積層することができると共に、それを大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化して多層の積層半導体基板を製造することができる。

【0055】

【発明の効果】

以上の説明から明らかなように、本発明によると、半導体基板のデバイス埋設側の面上に感光性絶縁物層を形成すると共に、デバイス非埋設側に第1の感光性レジスト層を形成する。また、第1の感光性レジスト層にペースト充填用微細孔を形成し、導電性ペーストを充填して半硬化させて貫通微細導電体を形成した後に、感光性絶縁層を第2の感光性レジスト層を形成する。また、紫外線照射により第2の感光性レジスト層に配線形成用開口パターンを形成すると共に、感光性絶縁層にデバイス電極に連通する第1の配線接続用微細孔と第1の貫通微細導電体に連通する第2の接続用微細孔と形成する。さらに、配線形成用開口パターン、配線接続用微細孔、および貫通微細導電体とに接続された配線に導電性金属をメッキし、デバイス電極と第1の貫通微細導電体とを接続する配線を形成する。その後、第1の感光性レジスト層の除去によって第1の貫通微細導電体の一端を露出させることによって効率よく積層可能な半導体基板セグメントを製造することができる。

【0056】

さらに、この製造された半導体セグメントを用いて積層することによって、上下層間の導通が可能となる。その結果、二層又はそれ以上に積層した積層半導体基板を容易に得ることができる。

【図面の簡単な説明】

【図1】本発明に係る半導体基板セグメントの一例を示す縦断面図である。

【図2】図1に示す半導体基板セグメントの製造フローを示す図であって、(A)は被覆層形成工程前の半導体基板の縦断面を示し、(B)は被覆層形成工程において感光性絶縁層を形成した半導体基板の縦断面を示し、(C)は導電体形成工程において第1の感光レジスト層にペースト充填用微細孔を形成した半導体基板の縦断面を示し、(D)は導電体形成工程において第1の貫通微細導電体を形成した半導体基板の縦断面を示し、(E)は開口パターン形成工程において第1,2の配線接続用微細孔等を形成した半導体基板の縦断面を示し、(F)は配線形成工程において配線を形成した半導体基板の縦断面を示している。

【図3】図1の半導体基板セグメントに樹脂封止層を形成した樹脂封止済み半導体基板セグメントの縦断面図である。

【図4】図3の樹脂封止済み半導体基板セグメントを二層に積層した状態を示す縦断面図である。

【図5】図3の樹脂封止済み半導体基板セグメントを三層に積層した状態を示す縦断面図である。

【図6】本発明に係る他の半導体基板セグメントの一例を示す縦断面図である。

【図7】図6に示す半導体基板セグメントの製造フローを示す図であって、(A)は被覆層形成工程前の半導体基板の縦断面を示し、(B)は被覆層形成工程において感光性絶縁層を形成した半導体基板の縦断面を示し、(C)は導電体形成工程において第1の感光レジスト層にペースト充填用微細孔を形成した半導体基板の縦断面を示し、(D)は導電体形成工程において第1,2の貫通微細導電体を形成した半導体基板の縦断面を示し、(E)は開口パターン形成工程において第1,2の配線接続用微細孔等を形成した半導体基板の縦断面を示し、(F)は配線形成工程において配線及び階層接続用貫通微細導電体を形成した半導体基板の縦断面を示している。

【図8】最上層に積層する樹脂封止済み半導体基板セグメントの縦断面図である。

【図9】図6の半導体基板セグメントに樹脂封止層を形成した樹脂封止済み半導体基板セグメントの縦断面図である。

【図10】図9の樹脂封止済み半導体基板セグメント上に図8の樹脂封止済み半導体基板セグメントを積層した状態を示す縦断面図である。

【図11】2個の階層接続用貫通微細導電体を形成した樹脂封止済み半導体基板セグメント上に、1個の階層接続用貫通微細導電体を形成した樹脂封止済み半導体基板セグメントを積層すると共に、その上に第1の貫通微細導電体のみ形成した樹脂封止済み半導体基板セグメントを積層した状態を示す縦断面図である。

【符号の説明】

1,1b…半導体基板セグメント

2 … 半導体基板

2a… デバイス埋設側の面

2b… デバイス非埋設側の面

3 … デバイス

4 … 感光性絶縁層

5 … 配線

6 … 第1の貫通微細孔導電体

6a… 接続端

8 … 第1の貫通微細孔

9 … 第1の感光性レジスト層

10 … ペースト充填用微細孔

11 … 第2の感光性レジスト層

12 … 配線形成用開口パターン

13 … 第1の配線接続用微細孔

14 … 第2の配線接続用微細孔

15 … 配線

16 … 樹脂封止層

17(17a〜17c)… 樹脂封止済み半導体基板セグメント

18 … 階層接続用貫通微細導電体

18a,18b… 接続端

21 … 第2の貫通微細孔

22 … 第2の貫通微細孔導電体

23 … 導電体延設用微細孔

【特許請求の範囲】

【請求項1】

一面側に埋設されたデバイスの周辺部に第1の貫通微細孔のみを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程と、フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に前記第1の貫通微細孔と連通したペースト充填用微細孔を形成すると共に、前記ペースト充填用微細孔から前記第1の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程と、フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを形成すると共に、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔と前記第1の貫通微細導電体に連通する第2の配線接続用微細孔とを形成する開口パターン形成工程と、導電性金属を前記配線形成用開口パターンと前記第1の配線接続用微細孔および第2の配線接続用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線を形成した後、前記第1の感光性レジスト層および第2の感光性レジスト層の残存を除去し、前記第1の感光性レジスト層の除去によって前記第1の貫通微細導電体の一端を露出させて接続端を形成する配線形成工程とを備えたことを特徴とする半導体基板セグメントの製造方法。

【請求項2】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト層上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を上昇させて前記第1の気圧より高いが大気圧より低い第2の気圧に制御することによって前記ペースト充填用微細孔から前記第1の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項1に記載の半導体基板セグメントの製造方法。

【請求項3】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を大気圧に戻すことによって前記ペースト充填用微細孔から前記第1の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項1に記載の半導体基板セグメントの製造方法。

【請求項4】

前記第1の感光性レジスト層上への前記導電性ペーストの塗布を、前記第1の貫通微細孔を閉塞するように行うことを特徴とする請求項2又は請求項3に記載の半導体基板セグメントの製造方法。

【請求項5】

前記半導体基板がシリコン基板であることを特徴とする請求項1ないし請求項4のいずれか一つに記載の半導体基板セグメントの製造方法。

【請求項6】

請求項1ないし請求項5のいずれか一つに記載の方法によって製造したことを特徴とする半導体基板セグメント。

【請求項7】

請求項6に記載の半導体基板セグメントの配線を樹脂封止し、前記樹脂が半硬化状態に保たれた所定数の半導体基板セグメントを積層し、上層側の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている配線に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させ、所定数の半導体基板セグメントを一体化することを特徴とする積層半導体基板の製造方法。

【請求項8】

前記樹脂封止を大気圧より低い気圧下で行うことを特徴とする請求項7に記載の積層半導体基板の製造方法。

【請求項9】

請求項7又は請求項8に記載の方法によって製造したことを特徴とする積層半導体基板。

【請求項10】

一面側に埋設されたデバイスの周辺部に第1の貫通微細孔と前記第1の貫通微細孔よりも半導体基板の側端側に位置された第2の貫通微細孔とを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程と、フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に前記第1の貫通微細孔および第2の貫通微細孔それぞれと連通したペースト充填用微細孔を形成すると共に、前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体および第2の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程と、フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔及び前記第1の貫通微細導電体に連通する第2の配線接続用微細孔をそれぞれ形成すると共に、前記第2の感光性レジスト層を貫通して前記感光性絶縁層に、前記第2の貫通微細導電体に連通する導電体延設用微細孔を形成する開口パターン形成工程と、導電性金属を前記配線形成用開口パターンと前記第1の配線用微細孔および第2の配線用微細孔と前記導電体延設用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線及び前記第2の貫通微細導電体の延設体である階層接続用貫通微細導電体を形成した後、前記第1の感光性レジスト層および第2の感光性レジスト層の残存を除去して前記階層接続用貫通微細導電体の両端を露出させて接続端を形成する配線形成工程とを備えたことを特徴とする半導体基板セグメントの製造方法。

【請求項11】

前記デバイス周辺部に前記第2の貫通微細孔が単数列状に形成されていることを特徴とする請求項10に記載の半導体基板セグメントの製造方法。

【請求項12】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト層上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を上昇させて前記第1の気圧より高いが大気圧より低い第2の気圧に制御することによって前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項11に記載の半導体基板セグメントの製造方法。

【請求項13】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を大気圧に戻すことによって前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項11に記載の半導体基板セグメントの製造方法。

【請求項14】

前記第1の感光性レジスト層上への前記導電性ペーストの塗布を、前記第1及び/又は第2の貫通微細孔を閉塞するように行うことを特徴とする請求項12又は請求項13に記載の半導体基板セグメントの製造方法。

【請求項15】

前記半導体基板がシリコン基板であることを特徴とする請求項11ないし請求項14のいずれか一つに記載の半導体基板セグメントの製造方法。

【請求項16】

請求項11ないし請求項15のいずれか一つに記載の半導体基板セグメントの製造方法によって製造したことを特徴とする半導体基板セグメント。

【請求項17】

前記第2の貫通微細孔が複数列状に形成されていることを特徴とする請求項10に記載の半導体基板セグメントの製造方法。

【請求項18】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト層上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を上昇させて前記第1の気圧より高いが大気圧より低い第2の気圧に制御することによって前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項17に記載の半導体基板セグメントの製造方法。

【請求項19】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を大気圧に戻すことによって前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項17に記載の半導体基板セグメントの製造方法。

【請求項20】

前記第1の感光性レジスト層上への前記導電性ペーストの塗布を、前記第1及び/又は第2の貫通微細孔を閉塞するように行うことを特徴とする請求項18又は請求項19に記載の半導体基板セグメントの製造方法。

【請求項21】

前記半導体基板がシリコン基板であることを特徴とする請求項17ないし請求項20のいずれか一つに記載の半導体基板セグメントの製造方法。

【請求項22】

請求項17ないし請求項21のいずれか一つに記載の方法によって製造したことを特徴とする半導体基板セグメント。

【請求項23】

請求項16に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメント上に、請求項6に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し、上層側の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化することを特徴とする積層半導体基板の製造方法。

【請求項24】

前記樹脂封止を大気圧より低い気圧下で行うことを特徴とする請求項23に記載の積層半導体基板の製造方法。

【請求項25】

請求項23又は請求項24に記載の方法によって製造したことを特徴とする積層半導体基板。

【請求項26】

請求項22に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントの所定数を、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N)であるのに対し、上層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N−1)であるように積層すると共に、前記階層接続用貫通微細導電体の個数が(N=1)の樹脂封止済み半導体基板セグメント上に、請求項6に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し、最上層の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接されると共に、前記階層接続用貫通微細導電体の下側の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化することを特徴とする積層半導体基板の製造方法。

【請求項27】

前記樹脂封止を大気圧より低い気圧下で行うことを特徴とする請求項26に記載の積層半導体基板の製造方法。

【請求項28】

請求項26又は請求項27に記載の方法によって製造したことを特徴とする積層半導体基板。

【請求項1】

一面側に埋設されたデバイスの周辺部に第1の貫通微細孔のみを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程と、フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に前記第1の貫通微細孔と連通したペースト充填用微細孔を形成すると共に、前記ペースト充填用微細孔から前記第1の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程と、フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを形成すると共に、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔と前記第1の貫通微細導電体に連通する第2の配線接続用微細孔とを形成する開口パターン形成工程と、導電性金属を前記配線形成用開口パターンと前記第1の配線接続用微細孔および第2の配線接続用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線を形成した後、前記第1の感光性レジスト層および第2の感光性レジスト層の残存を除去し、前記第1の感光性レジスト層の除去によって前記第1の貫通微細導電体の一端を露出させて接続端を形成する配線形成工程とを備えたことを特徴とする半導体基板セグメントの製造方法。

【請求項2】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト層上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を上昇させて前記第1の気圧より高いが大気圧より低い第2の気圧に制御することによって前記ペースト充填用微細孔から前記第1の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項1に記載の半導体基板セグメントの製造方法。

【請求項3】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を大気圧に戻すことによって前記ペースト充填用微細孔から前記第1の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項1に記載の半導体基板セグメントの製造方法。

【請求項4】

前記第1の感光性レジスト層上への前記導電性ペーストの塗布を、前記第1の貫通微細孔を閉塞するように行うことを特徴とする請求項2又は請求項3に記載の半導体基板セグメントの製造方法。

【請求項5】

前記半導体基板がシリコン基板であることを特徴とする請求項1ないし請求項4のいずれか一つに記載の半導体基板セグメントの製造方法。

【請求項6】

請求項1ないし請求項5のいずれか一つに記載の方法によって製造したことを特徴とする半導体基板セグメント。

【請求項7】

請求項6に記載の半導体基板セグメントの配線を樹脂封止し、前記樹脂が半硬化状態に保たれた所定数の半導体基板セグメントを積層し、上層側の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている配線に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させ、所定数の半導体基板セグメントを一体化することを特徴とする積層半導体基板の製造方法。

【請求項8】

前記樹脂封止を大気圧より低い気圧下で行うことを特徴とする請求項7に記載の積層半導体基板の製造方法。

【請求項9】

請求項7又は請求項8に記載の方法によって製造したことを特徴とする積層半導体基板。

【請求項10】

一面側に埋設されたデバイスの周辺部に第1の貫通微細孔と前記第1の貫通微細孔よりも半導体基板の側端側に位置された第2の貫通微細孔とを形成した半導体基板のデバイス埋設側の面上に感光性絶縁層を形成すると共に、前記半導体基板のデバイス非埋設側の面上に第1の感光性レジスト層を形成する被覆層形成工程と、フォトマスクを用いて前記第1の感光性レジスト層側から紫外光を照射して前記第1の感光性レジスト層に前記第1の貫通微細孔および第2の貫通微細孔それぞれと連通したペースト充填用微細孔を形成すると共に、前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に導電性ペーストを充填し、且つ半硬化させて第1の貫通微細導電体および第2の貫通微細導電体を形成した後、前記感光性絶縁層上に第2の感光性レジスト層を形成する導電体形成工程と、フォトマスクを用いて前記第2の感光性レジスト層側から紫外光を照射して、前記第2の感光性レジスト層に配線形成用開口パターンを、前記感光性絶縁層に前記デバイスの電極に連通する第1の配線接続用微細孔及び前記第1の貫通微細導電体に連通する第2の配線接続用微細孔をそれぞれ形成すると共に、前記第2の感光性レジスト層を貫通して前記感光性絶縁層に、前記第2の貫通微細導電体に連通する導電体延設用微細孔を形成する開口パターン形成工程と、導電性金属を前記配線形成用開口パターンと前記第1の配線用微細孔および第2の配線用微細孔と前記導電体延設用微細孔とにメッキして前記デバイスの電極と前記第1の貫通微細導電体とに接続された配線及び前記第2の貫通微細導電体の延設体である階層接続用貫通微細導電体を形成した後、前記第1の感光性レジスト層および第2の感光性レジスト層の残存を除去して前記階層接続用貫通微細導電体の両端を露出させて接続端を形成する配線形成工程とを備えたことを特徴とする半導体基板セグメントの製造方法。

【請求項11】

前記デバイス周辺部に前記第2の貫通微細孔が単数列状に形成されていることを特徴とする請求項10に記載の半導体基板セグメントの製造方法。

【請求項12】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト層上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を上昇させて前記第1の気圧より高いが大気圧より低い第2の気圧に制御することによって前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項11に記載の半導体基板セグメントの製造方法。

【請求項13】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を大気圧に戻すことによって前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項11に記載の半導体基板セグメントの製造方法。

【請求項14】

前記第1の感光性レジスト層上への前記導電性ペーストの塗布を、前記第1及び/又は第2の貫通微細孔を閉塞するように行うことを特徴とする請求項12又は請求項13に記載の半導体基板セグメントの製造方法。

【請求項15】

前記半導体基板がシリコン基板であることを特徴とする請求項11ないし請求項14のいずれか一つに記載の半導体基板セグメントの製造方法。

【請求項16】

請求項11ないし請求項15のいずれか一つに記載の半導体基板セグメントの製造方法によって製造したことを特徴とする半導体基板セグメント。

【請求項17】

前記第2の貫通微細孔が複数列状に形成されていることを特徴とする請求項10に記載の半導体基板セグメントの製造方法。

【請求項18】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト層上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を上昇させて前記第1の気圧より高いが大気圧より低い第2の気圧に制御することによって前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項17に記載の半導体基板セグメントの製造方法。

【請求項19】

前記導電体形成工程において、大気圧より低い第1の気圧下で前記第1の感光性レジスト上に前記導電性ペーストを塗布し、且つスキージの作動により所定厚さに印刷した後に、前記第1の気圧を大気圧に戻すことによって前記ペースト充填用微細孔から前記第1の貫通微細孔および第2の貫通微細孔に前記導電性ペーストを充填することを特徴とする請求項17に記載の半導体基板セグメントの製造方法。

【請求項20】

前記第1の感光性レジスト層上への前記導電性ペーストの塗布を、前記第1及び/又は第2の貫通微細孔を閉塞するように行うことを特徴とする請求項18又は請求項19に記載の半導体基板セグメントの製造方法。

【請求項21】

前記半導体基板がシリコン基板であることを特徴とする請求項17ないし請求項20のいずれか一つに記載の半導体基板セグメントの製造方法。

【請求項22】

請求項17ないし請求項21のいずれか一つに記載の方法によって製造したことを特徴とする半導体基板セグメント。

【請求項23】

請求項16に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメント上に、請求項6に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し、上層側の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化することを特徴とする積層半導体基板の製造方法。

【請求項24】

前記樹脂封止を大気圧より低い気圧下で行うことを特徴とする請求項23に記載の積層半導体基板の製造方法。

【請求項25】

請求項23又は請求項24に記載の方法によって製造したことを特徴とする積層半導体基板。

【請求項26】

請求項22に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントの所定数を、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N)であるのに対し、上層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の個数が(N−1)であるように積層すると共に、前記階層接続用貫通微細導電体の個数が(N=1)の樹脂封止済み半導体基板セグメント上に、請求項6に記載の半導体基板セグメントの配線を樹脂封止して前記樹脂が半硬化状態に保たれている樹脂封止済み半導体基板セグメントを積層し、最上層の樹脂封止済み半導体基板セグメントに形成されている第1の貫通微細導電体の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接されると共に、前記階層接続用貫通微細導電体の下側の接続端が、下層側の樹脂封止済み半導体基板セグメントに形成されている階層接続用貫通微細導電体の上側の接続端に当接された積層状態で大気圧より低い気圧下において加熱しながら加圧することによって前記樹脂を硬化させて一体化することを特徴とする積層半導体基板の製造方法。

【請求項27】

前記樹脂封止を大気圧より低い気圧下で行うことを特徴とする請求項26に記載の積層半導体基板の製造方法。

【請求項28】

請求項26又は請求項27に記載の方法によって製造したことを特徴とする積層半導体基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2004−172453(P2004−172453A)

【公開日】平成16年6月17日(2004.6.17)

【国際特許分類】

【出願番号】特願2002−337974(P2002−337974)

【出願日】平成14年11月21日(2002.11.21)

【出願人】(000219314)東レエンジニアリング株式会社 (505)

【出願人】(000005186)株式会社フジクラ (4,463)

【Fターム(参考)】

【公開日】平成16年6月17日(2004.6.17)

【国際特許分類】

【出願日】平成14年11月21日(2002.11.21)

【出願人】(000219314)東レエンジニアリング株式会社 (505)

【出願人】(000005186)株式会社フジクラ (4,463)

【Fターム(参考)】

[ Back to top ]