半導体実装部材及び半導体実装部材の製造方法

【課題】 多配線への対応及び電源強化を図りながら歩留まりが下がらない半導体実装部材を提供する。

【解決手段】 半導体実装部材100を第2基板110と第1基板10との2つのプリント配線板で構成するため、多配線への対応及び電源強化の目的で、1枚のビルドアップ基板の層数を増やしサイズを大きくするのと比較し、歩留まりが低下しない。第1基板10と第2基板110との間に支持体188が介在するので、第1基板10と第2基板110との間にアンダーフィルを充填させる必要が無い。

【解決手段】 半導体実装部材100を第2基板110と第1基板10との2つのプリント配線板で構成するため、多配線への対応及び電源強化の目的で、1枚のビルドアップ基板の層数を増やしサイズを大きくするのと比較し、歩留まりが低下しない。第1基板10と第2基板110との間に支持体188が介在するので、第1基板10と第2基板110との間にアンダーフィルを充填させる必要が無い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、第1のプリント配線板と、この第1のプリント配線板上に実装されてなる第2のプリント配線板とからなり、半導体素子を搭載することを可能とする半導体実装部材に関するものである。

【背景技術】

【0002】

コンピュータのCPU用の実装基板としては、特許文献1に挙げられているような、コア基板上に層間絶縁層と導体回路とをビルドアップ積層して成るビルドアップ基板が用いられている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−223315号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

パーソナルコンピュータと比較して高性能なサーバ用コンピュータのCPU用の実装基板として、多層配線への対応及び電源強化の観点から、層数が多く且つサイズが大きなプリント配線板が用いられる。パーソナルコンピュータのCPU実装用のプリント配線板に比較して、層数が多く且つサイズが大きくなると、歩留まりが下がるという課題が生じる。

【0005】

本発明は、上述した課題を解決するためになされたものであり、その目的とするところは、多層配線への対応及び電源強化を図りながら歩留まりが下がらない半導体実装部材及びその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

請求項1に記載の半導体実装部材は、貫通孔を有する複数の第1絶縁層と、該第1絶縁層上に形成されている第1導体と、前記貫通孔内に設けられて前記第1導体同士を接続するビア導体と、を有する第1基板と、

貫通孔を有するコア基板と、該コア基板の両面に形成されている第2導体と、前記貫通孔の内部に形成され前記第2導体同士を接続するスルーホール導体と、前記コア基板上及び前記第2導体上に形成されて第2絶縁層と第3導体とが交互に積層されてなるビルドアップ層と、を有する第2基板と、

最外層の第1絶縁層の中央部からの外周側であって、前記第1導体のうち最外層に位置する第1導体上に設けられ、前記第1基板と前記第2基板とを接続する第1半田バンプと、

前記最外層の第1絶縁層の中央部に設けられ、前記第1基板と前記第2基板との間隔を維持する支持体と、

前記第3導体のうち最外層に位置する第3導体上に設けられ、半導体素子を接続する第2バンプと、からなることを技術的特徴とする。

【発明の効果】

【0007】

本発明の半導体実装部材は、第1基板と、該第1基板上に第1半田バンプを介して設けられる第2基板とを有する。すなわち、本発明の半導体実装部材においては、導体層の層数が多く、且つサイズの大きい従来の配線板を少なくとも2つの部材に分割するとともに各々の部材の層数を低減し、互いをバンプで接続している。これにより、従来の配線板と比較して、歩留まりの向上を図ることが可能となる。

【0008】

ここで、第1基板と第2基板との間には、通常、アンダーフィル樹脂が充填される。しかしながら、アンダーフィル樹脂を充填する際に発生するボイドにより、双方の基板同士の接続信頼性が低下するおそれがある。さらに、アンダーフィル樹脂を設けることで、製造コストも上昇する。これに対し、本願発明では、第1基板と第2基板との対向面間に支持体が設けられる。この支持体は、双方の基板同士を接続する第1バンプが形成されていない領域に設けられる。そして、この支持体により、第1基板に対する第2基板の固定が強固なものになる。このため、例えば第2基板上への半導体素子の実装性を向上させるために第2バンプの頂面を平坦化する場合、アンダーフィル樹脂が設けられていなくても双方の基板の接続が安定しているため、歩留まり良く平坦化することが可能となる。

【図面の簡単な説明】

【0009】

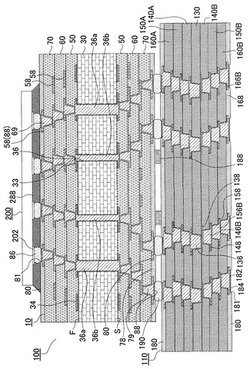

【図1】本発明の実施形態に係る、半導体装置の断面図である。

【図2】実施形態に係る第1基板の断面図である。

【図3】実施形態に係る第1基板の平面図である。

【図4】実施形態に係る第1基板の製造工程図である。

【図5】実施形態に係る第1基板の製造工程図である。

【図6】実施形態に係る第1基板の製造工程図である。

【図7】第実施形態に係る第1基板の製造工程図である。

【図8】第実施形態に係る第1基板の製造工程図である。

【図9】実施形態に係る第2基板の断面図である。

【図10】実施形態に係る第2基板の平面図である。

【図11】実施形態に係る第2基板の製造工程図である。

【図12】実施形態に係る第2基板の製造工程図である。

【図13】実施形態に係る第2基板の製造工程図である。

【図14】実施形態に係る第2基板の製造工程図である。

【図15】実施形態に係る半導体実装部材の製造工程図である。

【図16】実施形態に係る半導体実装部材の断面図である。

【図17】支持体の配置位置を示す平面図である。

【図18】支持体の形状を示す側面図である。

【発明を実施するための形態】

【0010】

図1〜図16を参照して本実施形態に係る半導体実装部材について説明する。

まず、図1は半導体実装部材100に半導体素子200が実装されている状態(半導体装置)を示している。図16は、半導体素子200を実装する前の状態の半導体実装部材100を示している。

半導体実装部材100は、第1基板110と、第1基板110上に半田バンプ190及び支持体188を介して設けられている第2基板10とを有する。

半導体素子200は、半田バンプ86を介して第2基板10上に実装されている。第2基板10と半導体素子200との間には樹脂充填剤288が充填されている。

【0011】

図3は、第1基板110の平面図である。同図に示すように、第1基板110上面に設けられるパッド186は中央部からの外周側にペリフェラル状に配列されている。これにより、第1基板110の略中央部には、バンプが形成されない領域R0が設けられる。この領域R0には、樹脂からなる角柱状の支持体188が配置されている。これら支持体188のうち、支持体188aと支持体188cとは、領域R0の略中心部を通る仮想直線189A上に配置されている。また、支持体188のうち、支持体188bと支持体188dとは、領域R0の略中心部を通る189B上に配置されている。このように配置された支持体188により、第1基板に対する第2基板の固定が行われる。

なお、上述した「仮想直線189A、189B上に配置されている」とは、仮想直線189A、189B上に支持体188の一部が位置している状態を意味する。

【0012】

これらパッド186の配列領域を構成する4辺のうち、任意の1辺の配列領域Xは、他の3辺の配列領域Yと比べて幅が広い。

また、パッド186の配列領域のうち、少なくとも1つの角部Cを形成するパッドは、斜線状に配置されている。パッドが斜線状に配置されている角部Cは、第1基板110を接続する際、双方の基板10,110を互いに位置あわせするときの目印となり得る。

【0013】

第1基板110は厚さt1(約0.8mm)に構成されている。第2基板10は、厚さt2(約1.0mm)に構成されている。本実施形態では、第1基板110及び第2基板10は、1<t2/t1<2が成立するように構成されている。

第1基板110の厚みt1と第2基板10の厚みt2とが上記の関係を満たすとき、実装部材10全体の厚みの増大を抑制しつつ、半導体素子200を実装する際に半田バンプ190に生じる応力を効果的に緩和することが可能になると推測される。

【0014】

[第1基板]

図2は、第1基板110の断面図を示す。

第1基板110は、厚み方向のほぼ中央部に、第1面Fと第2面Sとを有する第1絶縁層130を備える。絶縁層130の第1面F上には、第1導体147を有する第1絶縁層140Aが形成されている。この第1絶縁層140A上には、第1導体157を有する第1絶縁層150A、及び第1導体167を有する第1絶縁層160Aが順次形成されている。一方、絶縁層130の第2面S上には、第1導体148を有する第1絶縁層140Bが形成されている。この第1絶縁層140B上には、第1導体158を有する第1絶縁層150B、及び第1導体168を有する第1絶縁層160Bが順次形成されている。

各第1絶縁層の内部にはそれぞれ貫通孔が設けられている。各貫通孔の内部には、めっきからなるビア導体136,146A,146B,156A,156B,166A,166Bが形成されている。これらビア導体136,146A,146B,156A,156B,166A,166Bにより、異なる層に位置する第1導体同士が電気的に接続されている。

【0015】

最外層の絶縁層160A上及び160B上には、開口181の設けられたソルダーレジスト層180が形成されている。絶縁層160A上のソルダーレジスト層180の開口181内のパッド186上には、上述した第2基板10を接続するための半田ペースト187が塗布されている。絶縁層160B上のソルダーレジスト層180の開口181には、該開口により露出する第1導体168を含むパッドBが設けられている。

また、ビア導体136,146A,146B,156A,156B,166A,166Bは、柱状に積み上げられている。なお、「柱状」とは、厚み方向に隣接する一対のビア導体同士が接触している状態をいう。これにより、厚み方向における導体の距離が短縮され、配線抵抗が減少する。その結果、電源電圧や信号の損失が抑制される。

【0016】

引き続き、図2を参照して上述した第2基板10の製造方法について図4〜図7を参照し説明される。

(1)厚さ約60μmのガラスエポキシ樹脂またはBT(ビスマレイミドトリアジン)樹脂からなる絶縁層130の両面に約10μmの銅箔132がラミネートされている銅張積層板130Aを出発材料とする(図4(A))。

【0017】

(2)レーザにより、裏面側の銅箔132に至るビア用開口133が形成された後(図4(B))、全面に無電解めっき処理が施され無電解めっき膜131が設けられる(図4(C))。

【0018】

(3)電解めっき処理で、無電解めっき膜131上、及び、ビア用開口133内に電解めっき膜135が設けられる(図5(A))。

【0019】

(4)第1導体を形成する部分にエッチングレジスト137が形成される(図5(B))。

【0020】

(5)レジスト137の非形成部の電解めっき膜135、無電解めっき膜131及び銅箔132をエッチングにより溶解した後、レジスト137を除去する。これにより、ビア導体136及び第1導体137、138が形成される(図5(C))。その後、第1導体を粗化する(図示せず)。

【0021】

(6)片面のみに銅箔142Aを有するプリプレグが積層され、絶縁層130の第1面F上に絶縁層140Aが形成される。同じく、片面のみに銅箔142Bを有するプリプレグが第2面S上に積層され、絶縁層130の第2面S上に絶縁層140Bが形成される(図5(D))。

【0022】

(7)レーザにより、絶縁層140Aにビア導体用の貫通孔143Aが、絶縁層140Bにビア導体用の貫通孔143Bが形成された後(図6(A))、無電解めっき処理により無電解めっき膜141が設けられる(図6(B))。

【0023】

(8)電解めっき処理が施され、無電解めっき膜141上、及び、貫通孔143A、143B内に電解めっき膜145が設けられる(図6(C))。

【0024】

(9)第1導体を形成する部分にエッチングレジスト147が形成される(図6(D))。

【0025】

(10)レジスト147の非形成部の電解めっき膜145、無電解めっき膜141及び銅箔142A、142Bがエッチングにより溶解された後、レジスト147が除去され、ビア導体146A、146B及び第1導体147、148が形成される(図7(A))。その後、第1導体147、148を粗化する(図示せず)。

【0026】

(11)上述した(6)−(10)の工程が繰り返される。(図7(B))。

【0027】

(12)開口181を有し、厚さが約20μmのソルダーレジスト層180が形成される(図7(C))。

【0028】

(13)ソルダーレジスト層180の開口181にニッケルめっき層182が形成され、金めっき層184が形成される(図7(D))。ニッケル−金層以外にも、ニッケル−パラジウム−金層を形成してもよい。

【0029】

(14)ソルダーレジスト層180の開口181に対応する通孔190aを備えるマスク190がソルダーレジスト上に載置され(図8(A))、通孔を介して半田ペースト187が開口181内のパッド186上に載置される(図8(B))。

【0030】

(15)図3を参照して上述したように、ペリフェラル状に配列されているパッド186の形成領域の内側に支持体188を設ける(図2)。これら支持体188は、樹脂をディスペンサで塗布することで設けられる。

なお、支持体を構成する樹脂は、主として熱硬化性樹脂からなり、熱可塑性樹脂を含んでいてもよい。この支持体188を構成する樹脂の硬化温度は、後述するバンプ190の溶融温度よりも高いことが好ましい。第1基板110に対して第2基板10を接続する際、まずバンプ190が加熱溶融され、双方の基板10,110同士が位置合わせされる。その後、支持体188を構成する樹脂が硬化することで、双方の基板10,110同士を歩留まり良く接続することが可能となる。

【0031】

[第2基板]

図9は、第2基板10の断面図を示す。

第2基板10は、厚み方向のほぼ中央部に、第1面Fと第2面Sとを有するコア基板30を備える。コア基板30の第1面F上及び第2面S上には、第2導体34が形成されている。コア基板30の内部には貫通孔33a、33bが形成されている。これら貫通孔は、異なる直径を有している。本実施形態では、直径が180μmの第1貫通孔33bと、直径が250μmの第2貫通孔33aを備える。これら貫通孔の内部には、第2導体34同士を接続するスルーホール導体が設けられている。このスルーホール導体のうち、大径の第1貫通孔内に設けられるのが第1スルーホール導体36aであり、小径の第2貫通孔内に設けられるのが第2スルーホール導体36bである。

【0032】

第1スルーホール導体36aは信号用の導体であり、第2スルーホール導体36bは電源用又はグランド用の導体である。なお、スルーホール導体36a,36bそれぞれの電気的な機能はこれに限定されるものではない。

コア基板30の第1面F上及び第2面S上には、それぞれ層間樹脂絶縁層50と第3導体58とが交互に積層されてなるビルドアップ層55が設けられている。そして、第2導体34と第3導体58とはビア導体59を介して接続され、異なる層に位置する第3導体58同士はビア導体69を介して電気的に接続されている。

最外層の層間樹脂絶縁層70上には、開口を有するソルダーレジスト層80が形成されている。第1面側のソルダーレジスト層80の開口内には、半導体素子を実装するための半田バンプ86が形成されている。第2面側のソルダーレジスト層80の開口内には、第1基板へ接続するための半田バンプ89が形成されている。

【0033】

図10(A)に、第2基板10の第1面(半導体素子が実装される面)の平面図を示す。

第2基板10は略矩形状であり、第2バンプ86が形成されている半導体素子実装領域R1を有している。半導体素子実装領域R1の中心C1は、第2基板10の第1面の中心C2に対してずれている。すなわち、半導体素子実装領域R1の外周には、他よりも幅広い領域R2が存在する。領域R2は、第2基板10の中心C2から半導体素子実装領域R1の中心C1へ向かう方向とは逆方向に位置する領域である。このとき、半導体素子実装領域R1の外周のうち、領域R2以外の3辺の領域をR3とし、領域R2の幅をr2とし、領域R3の幅をr3としたとき、r2>r3を満たす。

【0034】

この幅広い領域R2に、樹脂充填剤を一旦塗布した後、半導体素子実装領域R1を形成する複数のバンプ86間及びその周辺に樹脂充填剤を流し込む。

これにより、半導体素子実装領域R1と、そこに実装される半導体素子との間に存在する樹脂充填剤に空洞が発生することを効果的に抑制することが可能となる。

また、半導体素子実装領域R1の外周のうち他の3辺の領域R3においては、相対的に幅狭となるため、樹脂充填剤がそれら3辺に沿って流れにくくなり、半導体素子実装領域R1を形成する複数のバンプ間に容易に樹脂充填剤を流動させることが可能となる。

【0035】

図10(B)に示すように、第2基板10の裏面(第2面)は、上記第1基板110のバンプ配列に対応する半田バンプ89から成る半田バンプ配列を有している。このうち、第1基板110の角部Cに相当する箇所には、三角形状の表示マークMが設けられている。この表示マークMは、第1基板110と第2基板10とを接続する際、双方を位置あわせする目的を有する。

【0036】

引き続き、第2基板10の製造方法について図11〜図14を参照し説明される。

(1)厚さ0.05〜0.8mmのガラスエポキシ樹脂またはBT(ビスマレイミドトリアジン)樹脂からなる絶縁性基材30の両面に銅箔32がラミネートされている銅張積層板30Aを出発材料とする(図11(A))。

【0037】

(2)まず、ドリル又はレーザーにより銅張積層板にスルーホール用貫通孔33が形成される(図11(B))。その後、無電解めっき処理により無電解めっき膜31が設けられる(図11(C))。この際、直径の異なる2種類の貫通孔(例えば180μm)33b、貫通孔(例えば、250μm)33aが形成される。

【0038】

(3)電解めっき処理が施され、めっき膜31上、及び、スルーホール用貫通孔33内に電解めっき膜35が設けられる(図11(D))。次いで、電解めっき膜35で形成される空間内に穴埋め樹脂が充填される。なお、穴埋め樹脂を充填することを省略し、スルーホール用貫通孔33内に電解めっき膜が充填されてもよい。

【0039】

(4)第2導体が形成される部分にエッチングレジスト37が形成される(図11(E))。

【0040】

(5)レジスト37が形成されていない箇所の電解めっき膜35、無電解めっき膜31、銅箔32がエッチングにより溶解され後、レジスト37が除去され、スルーホール導体36a,36b及び第2導体34が形成される(図12(A))。その後、第2導体34が粗化される(図示せず)。

【0041】

(6)上記工程を経たコア基板30の両面上に、厚さ約25μmの層間樹脂絶縁層用樹脂フィルム(味の素社製:商品名;ABF−45SH)が温度50〜150℃まで昇温しながら真空圧着ラミネートされ、層間樹脂絶縁層50が設けられる(図12(B))。

【0042】

(7)次に、CO2ガスレーザにて層間樹脂絶縁層50に直径約60μmのバイアホール用開口51が設けられる(図12(C))。クロム酸、過マンガン酸塩などの酸化剤等に浸漬されことによって、層間樹脂絶縁層50に粗化面が設けられる(図示せず)。

【0043】

(8)予め層間樹脂絶縁層50の表層にパラジウムなどの触媒が付与され、無電解めっき液に5〜60分間浸漬されることにより、0.1〜5μmの範囲で無電解めっき膜52が設けられる(図12(D))。

【0044】

(9)上記処理を終えた基板30に、市販の感光性ドライフィルムが貼り付けられ、フォトマスクフィルムを載置して露光した後、炭酸ナトリウムで現像処理し、厚さ15μmのめっきレジスト54が設けられる(図13(A))。

【0045】

(10)次に、電解めっきが施され、厚さ15μmの電解めっき膜56が形成される(図13(B)参照)。

【0046】

(11)めっきレジスト54がアミン溶液で剥離除去された後、そのめっきレジスト下の無電解めっき膜52が硫酸と過酸化水素との混合液を用いるエッチングにて溶解除去され、無電解めっき膜52と電解めっき膜56からなる厚さ約15μmの第2導体58及びビア導体59が形成される(図13(C))。第二銅錯体と有機酸とを含有するエッチング液によって、第3導体58及びビア導体59表面が粗化される(図示せず)。

【0047】

(12)上記(6)−(11)と同様にして、ビア導体69及び第2導体68の形成された層間樹脂絶縁層60と、ビア導体79及び第3導体58の形成された層間樹脂絶縁層70とが形成される(図13(D))。

【0048】

(13)基板の両面に、市販のソルダーレジスト組成物が20μmの厚さで塗布され、乾燥処理が行われた後、ソルダーレジスト開口部のパターンが描画された厚さ5mmのフォトマスクがソルダーレジスト層に密着され紫外線で露光され、DMTG溶液で現像処理され、上面側に小径の開口81と、下面側に大径の開口81が形成される。さらに、加熱処理によりソルダーレジスト層が硬化され、開口81を有し、その厚さが約20μmのソルダーレジストパターン層80が形成される(図14(A))。

【0049】

(14)次に、ソルダーレジスト層80を形成した基板が、無電解ニッケルめっき液に浸漬され、開口81に厚さ5μmのニッケルめっき層82が形成される。さらに、その基板が無電解金めっき液に浸漬され、ニッケルめっき層82上に、厚さ0.03μmの金めっき層84が形成される(図14(B))。ニッケル−金層以外にも、ニッケル−パラジウム−金層が形成されてもよい。

【0050】

(15)マスクを介して、第1面側のソルダーレジスト層の開口71にフラックスが塗布され、同様に、第2面側のソルダーレジスト層の開口71にフラックスが塗布される(図示せず)。開口を有するマスクが基板の第1面側の開口81に位置合わせされ、半田ボール86αが第1面側の開口81内に搭載される。同様に、開口を有するマスクが基板の第2面側の開口81に位置合わせされ、半田ボール89αが第2面側の開口81内に搭載される(図14(C))。

【0051】

(16)約200℃でリフローが行われ、半田ボール86αが半田バンプ86にされ、半田ボール89αが半田バンプ89にされ、第2基板10が完成する(図9)。なお、半田バンプ86の頂部は略平坦にすることが望ましい。仮に第2基板10に反りが生じていたとしても、半田バンプ86の高さを統一でき、ICチップの実装性を向上させることができる。

【0052】

[半導体実装部材の製造方法]

図15を参照して第2基板10と第1基板110との接続について説明される。

図15(A)に示すように、第2基板10が図示しない吸着部材で吸着され、第2基板10の半田バンプ89が、第1基板110のパッド186上の半田ペースト187と対応するように位置決めされる。そして、半田バンプ89を半田ペースト187へ当接させた状態で、約200℃でリフローを行い、半田バンプ89及び半田ペースト187を溶融させて、半田バンプ190を形成し、図15(B)に示すように第2基板10と第1基板110とを接続する。

【0053】

上述したようにリフローする場合、まず半田バンプ190が形成され、その後、支持体188を構成する樹脂が硬化する。すなわち、第1基板110と第2基板10とが半田バンプ190を介して接続された状態で、双方の基板10,110が支持体188を介してさらに強固に接続される。これによれば、アンダーフィル樹脂を用いずとも、第1基板110と第2基板10とを歩留まり良く、強固に接続することが可能となる。

図3に示すように半田バンプ186はペリフェラル配列であり、該半田バンプ196の配列領域の内側に支持体188が設けられているため、双方の基板を支持体188により安定に固定することが可能になる。

そして、半導体素子の実装性を改善するため、半田バンプ86をフラッタニングする場合、第1基板110と第2基板10との接続部分に応力が加わった場合でも、その中央部にはスペーサーの役割を果たす支持体188が配置されているので、第1基板と第2基板との間隔が狭くならず、隣接する半田バンプ190の短絡や、半田バンプ190へのクラックの発生等が生じ難い。

【0054】

ここで、サイズの大きい第1基板と第2基板との間に歩留まり良くアンダーフィル樹脂を充填することは困難であるが、実施形態では、第1基板と第2基板とを接続する第1半田バンプ190が、基板中央部からの外周側に配置され、中央部にはスペーサーの役割を果たす支持体188が配置されるので、アンダーフィル樹脂を用いずとも半田バンプ190の接続信頼性を保つことができる。すなわち、アンダーフィル樹脂を充填する場合は、充填領域が大きいほどボイドが残る可能性が高くなるが、本実施形態ではそういったおそれがない。

【0055】

支持体188を構成する樹脂の硬化温度は、半田バンプ190を構成する半田の融点よりも高い。このため、まず半田バンプ190により双方の基板が確実に接続された後で、支持体により双方の基板同士がより強固に固定される。ここで、支持体による固定はある程度自由が効くので、先に半田バンプ190を形成して基板同士を固定することで、歩留まりが向上する。

【0056】

次いで、半田バンプ86を介して半導体素子200が実装され、半導体素子200と第2基板10との間に樹脂充填剤288が充填される(図1)。

【0057】

本実施形態では、半導体実装部材100を第1基板110と第2基板10との2つのプリント配線板で構成するため、多層配線への対応及び電源強化の目的で、1枚のビルドアップ基板の層数を増やしサイズを大きくするのと比較し、歩留まりが低下しない。

【0058】

図3を参照して上述されたように、実施形態では、中央部に4箇所、角柱状支持体が設けられたが、図17(A)に示すように、支持体が円筒状で、中央部の大径のものを、周囲4箇所に小径のものを配置されることもできる。支持体186を半田バンプ188の配列領域の内側の領域の中心を通る直線上に複数設けられることで、双方の基板を支持体によりさらに安定に固定することが可能になる。また、図17(B)に示すように、楕円状の支持体を一対設けられることも、図17(C)に示すように、1の楕円状の支持体が設けられることもできる。

【0059】

更に、支持体は円筒状で無くとも、図18(A)に側面を示すように、半円状のものでも、図18(B)に示すように、楕円形状であっても良い。

また、本実施形態では、第2基板10の厚みt2を第1基板110の厚みt1よりも大きくなるよう設定したが、これに限られるものではない。すなわち、第2基板10の厚みt2を第1基板110の厚みt1よりも小さくしてもよい。これは、例えばコア基板30の厚みや、第3導体58の層数などに依存する。この場合、実装部材の厚みが低減され、小型化に好適である。

さらに、本実施形態では、コア基板30の内部に直径の異なるスルーホール導体を設けたが、全てのスルーホール導体の径が同じであってもよい。この場合、製造工程の簡素化が図られる。

【符号の説明】

【0060】

10 第2基板

30 コア基板

34 第2導体

36 スルーホール導体

50 層間樹脂絶縁層

58 第3導体

59 ビア導体

80 ソルダーレジスト層

86 第2半田バンプ

100 半導体実装部材

110 第1基板

130 絶縁層

136 ビア導体

137 第1導体

188 支持体

190 半田バンプ

200 半導体素子

【技術分野】

【0001】

本発明は、第1のプリント配線板と、この第1のプリント配線板上に実装されてなる第2のプリント配線板とからなり、半導体素子を搭載することを可能とする半導体実装部材に関するものである。

【背景技術】

【0002】

コンピュータのCPU用の実装基板としては、特許文献1に挙げられているような、コア基板上に層間絶縁層と導体回路とをビルドアップ積層して成るビルドアップ基板が用いられている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001−223315号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

パーソナルコンピュータと比較して高性能なサーバ用コンピュータのCPU用の実装基板として、多層配線への対応及び電源強化の観点から、層数が多く且つサイズが大きなプリント配線板が用いられる。パーソナルコンピュータのCPU実装用のプリント配線板に比較して、層数が多く且つサイズが大きくなると、歩留まりが下がるという課題が生じる。

【0005】

本発明は、上述した課題を解決するためになされたものであり、その目的とするところは、多層配線への対応及び電源強化を図りながら歩留まりが下がらない半導体実装部材及びその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

請求項1に記載の半導体実装部材は、貫通孔を有する複数の第1絶縁層と、該第1絶縁層上に形成されている第1導体と、前記貫通孔内に設けられて前記第1導体同士を接続するビア導体と、を有する第1基板と、

貫通孔を有するコア基板と、該コア基板の両面に形成されている第2導体と、前記貫通孔の内部に形成され前記第2導体同士を接続するスルーホール導体と、前記コア基板上及び前記第2導体上に形成されて第2絶縁層と第3導体とが交互に積層されてなるビルドアップ層と、を有する第2基板と、

最外層の第1絶縁層の中央部からの外周側であって、前記第1導体のうち最外層に位置する第1導体上に設けられ、前記第1基板と前記第2基板とを接続する第1半田バンプと、

前記最外層の第1絶縁層の中央部に設けられ、前記第1基板と前記第2基板との間隔を維持する支持体と、

前記第3導体のうち最外層に位置する第3導体上に設けられ、半導体素子を接続する第2バンプと、からなることを技術的特徴とする。

【発明の効果】

【0007】

本発明の半導体実装部材は、第1基板と、該第1基板上に第1半田バンプを介して設けられる第2基板とを有する。すなわち、本発明の半導体実装部材においては、導体層の層数が多く、且つサイズの大きい従来の配線板を少なくとも2つの部材に分割するとともに各々の部材の層数を低減し、互いをバンプで接続している。これにより、従来の配線板と比較して、歩留まりの向上を図ることが可能となる。

【0008】

ここで、第1基板と第2基板との間には、通常、アンダーフィル樹脂が充填される。しかしながら、アンダーフィル樹脂を充填する際に発生するボイドにより、双方の基板同士の接続信頼性が低下するおそれがある。さらに、アンダーフィル樹脂を設けることで、製造コストも上昇する。これに対し、本願発明では、第1基板と第2基板との対向面間に支持体が設けられる。この支持体は、双方の基板同士を接続する第1バンプが形成されていない領域に設けられる。そして、この支持体により、第1基板に対する第2基板の固定が強固なものになる。このため、例えば第2基板上への半導体素子の実装性を向上させるために第2バンプの頂面を平坦化する場合、アンダーフィル樹脂が設けられていなくても双方の基板の接続が安定しているため、歩留まり良く平坦化することが可能となる。

【図面の簡単な説明】

【0009】

【図1】本発明の実施形態に係る、半導体装置の断面図である。

【図2】実施形態に係る第1基板の断面図である。

【図3】実施形態に係る第1基板の平面図である。

【図4】実施形態に係る第1基板の製造工程図である。

【図5】実施形態に係る第1基板の製造工程図である。

【図6】実施形態に係る第1基板の製造工程図である。

【図7】第実施形態に係る第1基板の製造工程図である。

【図8】第実施形態に係る第1基板の製造工程図である。

【図9】実施形態に係る第2基板の断面図である。

【図10】実施形態に係る第2基板の平面図である。

【図11】実施形態に係る第2基板の製造工程図である。

【図12】実施形態に係る第2基板の製造工程図である。

【図13】実施形態に係る第2基板の製造工程図である。

【図14】実施形態に係る第2基板の製造工程図である。

【図15】実施形態に係る半導体実装部材の製造工程図である。

【図16】実施形態に係る半導体実装部材の断面図である。

【図17】支持体の配置位置を示す平面図である。

【図18】支持体の形状を示す側面図である。

【発明を実施するための形態】

【0010】

図1〜図16を参照して本実施形態に係る半導体実装部材について説明する。

まず、図1は半導体実装部材100に半導体素子200が実装されている状態(半導体装置)を示している。図16は、半導体素子200を実装する前の状態の半導体実装部材100を示している。

半導体実装部材100は、第1基板110と、第1基板110上に半田バンプ190及び支持体188を介して設けられている第2基板10とを有する。

半導体素子200は、半田バンプ86を介して第2基板10上に実装されている。第2基板10と半導体素子200との間には樹脂充填剤288が充填されている。

【0011】

図3は、第1基板110の平面図である。同図に示すように、第1基板110上面に設けられるパッド186は中央部からの外周側にペリフェラル状に配列されている。これにより、第1基板110の略中央部には、バンプが形成されない領域R0が設けられる。この領域R0には、樹脂からなる角柱状の支持体188が配置されている。これら支持体188のうち、支持体188aと支持体188cとは、領域R0の略中心部を通る仮想直線189A上に配置されている。また、支持体188のうち、支持体188bと支持体188dとは、領域R0の略中心部を通る189B上に配置されている。このように配置された支持体188により、第1基板に対する第2基板の固定が行われる。

なお、上述した「仮想直線189A、189B上に配置されている」とは、仮想直線189A、189B上に支持体188の一部が位置している状態を意味する。

【0012】

これらパッド186の配列領域を構成する4辺のうち、任意の1辺の配列領域Xは、他の3辺の配列領域Yと比べて幅が広い。

また、パッド186の配列領域のうち、少なくとも1つの角部Cを形成するパッドは、斜線状に配置されている。パッドが斜線状に配置されている角部Cは、第1基板110を接続する際、双方の基板10,110を互いに位置あわせするときの目印となり得る。

【0013】

第1基板110は厚さt1(約0.8mm)に構成されている。第2基板10は、厚さt2(約1.0mm)に構成されている。本実施形態では、第1基板110及び第2基板10は、1<t2/t1<2が成立するように構成されている。

第1基板110の厚みt1と第2基板10の厚みt2とが上記の関係を満たすとき、実装部材10全体の厚みの増大を抑制しつつ、半導体素子200を実装する際に半田バンプ190に生じる応力を効果的に緩和することが可能になると推測される。

【0014】

[第1基板]

図2は、第1基板110の断面図を示す。

第1基板110は、厚み方向のほぼ中央部に、第1面Fと第2面Sとを有する第1絶縁層130を備える。絶縁層130の第1面F上には、第1導体147を有する第1絶縁層140Aが形成されている。この第1絶縁層140A上には、第1導体157を有する第1絶縁層150A、及び第1導体167を有する第1絶縁層160Aが順次形成されている。一方、絶縁層130の第2面S上には、第1導体148を有する第1絶縁層140Bが形成されている。この第1絶縁層140B上には、第1導体158を有する第1絶縁層150B、及び第1導体168を有する第1絶縁層160Bが順次形成されている。

各第1絶縁層の内部にはそれぞれ貫通孔が設けられている。各貫通孔の内部には、めっきからなるビア導体136,146A,146B,156A,156B,166A,166Bが形成されている。これらビア導体136,146A,146B,156A,156B,166A,166Bにより、異なる層に位置する第1導体同士が電気的に接続されている。

【0015】

最外層の絶縁層160A上及び160B上には、開口181の設けられたソルダーレジスト層180が形成されている。絶縁層160A上のソルダーレジスト層180の開口181内のパッド186上には、上述した第2基板10を接続するための半田ペースト187が塗布されている。絶縁層160B上のソルダーレジスト層180の開口181には、該開口により露出する第1導体168を含むパッドBが設けられている。

また、ビア導体136,146A,146B,156A,156B,166A,166Bは、柱状に積み上げられている。なお、「柱状」とは、厚み方向に隣接する一対のビア導体同士が接触している状態をいう。これにより、厚み方向における導体の距離が短縮され、配線抵抗が減少する。その結果、電源電圧や信号の損失が抑制される。

【0016】

引き続き、図2を参照して上述した第2基板10の製造方法について図4〜図7を参照し説明される。

(1)厚さ約60μmのガラスエポキシ樹脂またはBT(ビスマレイミドトリアジン)樹脂からなる絶縁層130の両面に約10μmの銅箔132がラミネートされている銅張積層板130Aを出発材料とする(図4(A))。

【0017】

(2)レーザにより、裏面側の銅箔132に至るビア用開口133が形成された後(図4(B))、全面に無電解めっき処理が施され無電解めっき膜131が設けられる(図4(C))。

【0018】

(3)電解めっき処理で、無電解めっき膜131上、及び、ビア用開口133内に電解めっき膜135が設けられる(図5(A))。

【0019】

(4)第1導体を形成する部分にエッチングレジスト137が形成される(図5(B))。

【0020】

(5)レジスト137の非形成部の電解めっき膜135、無電解めっき膜131及び銅箔132をエッチングにより溶解した後、レジスト137を除去する。これにより、ビア導体136及び第1導体137、138が形成される(図5(C))。その後、第1導体を粗化する(図示せず)。

【0021】

(6)片面のみに銅箔142Aを有するプリプレグが積層され、絶縁層130の第1面F上に絶縁層140Aが形成される。同じく、片面のみに銅箔142Bを有するプリプレグが第2面S上に積層され、絶縁層130の第2面S上に絶縁層140Bが形成される(図5(D))。

【0022】

(7)レーザにより、絶縁層140Aにビア導体用の貫通孔143Aが、絶縁層140Bにビア導体用の貫通孔143Bが形成された後(図6(A))、無電解めっき処理により無電解めっき膜141が設けられる(図6(B))。

【0023】

(8)電解めっき処理が施され、無電解めっき膜141上、及び、貫通孔143A、143B内に電解めっき膜145が設けられる(図6(C))。

【0024】

(9)第1導体を形成する部分にエッチングレジスト147が形成される(図6(D))。

【0025】

(10)レジスト147の非形成部の電解めっき膜145、無電解めっき膜141及び銅箔142A、142Bがエッチングにより溶解された後、レジスト147が除去され、ビア導体146A、146B及び第1導体147、148が形成される(図7(A))。その後、第1導体147、148を粗化する(図示せず)。

【0026】

(11)上述した(6)−(10)の工程が繰り返される。(図7(B))。

【0027】

(12)開口181を有し、厚さが約20μmのソルダーレジスト層180が形成される(図7(C))。

【0028】

(13)ソルダーレジスト層180の開口181にニッケルめっき層182が形成され、金めっき層184が形成される(図7(D))。ニッケル−金層以外にも、ニッケル−パラジウム−金層を形成してもよい。

【0029】

(14)ソルダーレジスト層180の開口181に対応する通孔190aを備えるマスク190がソルダーレジスト上に載置され(図8(A))、通孔を介して半田ペースト187が開口181内のパッド186上に載置される(図8(B))。

【0030】

(15)図3を参照して上述したように、ペリフェラル状に配列されているパッド186の形成領域の内側に支持体188を設ける(図2)。これら支持体188は、樹脂をディスペンサで塗布することで設けられる。

なお、支持体を構成する樹脂は、主として熱硬化性樹脂からなり、熱可塑性樹脂を含んでいてもよい。この支持体188を構成する樹脂の硬化温度は、後述するバンプ190の溶融温度よりも高いことが好ましい。第1基板110に対して第2基板10を接続する際、まずバンプ190が加熱溶融され、双方の基板10,110同士が位置合わせされる。その後、支持体188を構成する樹脂が硬化することで、双方の基板10,110同士を歩留まり良く接続することが可能となる。

【0031】

[第2基板]

図9は、第2基板10の断面図を示す。

第2基板10は、厚み方向のほぼ中央部に、第1面Fと第2面Sとを有するコア基板30を備える。コア基板30の第1面F上及び第2面S上には、第2導体34が形成されている。コア基板30の内部には貫通孔33a、33bが形成されている。これら貫通孔は、異なる直径を有している。本実施形態では、直径が180μmの第1貫通孔33bと、直径が250μmの第2貫通孔33aを備える。これら貫通孔の内部には、第2導体34同士を接続するスルーホール導体が設けられている。このスルーホール導体のうち、大径の第1貫通孔内に設けられるのが第1スルーホール導体36aであり、小径の第2貫通孔内に設けられるのが第2スルーホール導体36bである。

【0032】

第1スルーホール導体36aは信号用の導体であり、第2スルーホール導体36bは電源用又はグランド用の導体である。なお、スルーホール導体36a,36bそれぞれの電気的な機能はこれに限定されるものではない。

コア基板30の第1面F上及び第2面S上には、それぞれ層間樹脂絶縁層50と第3導体58とが交互に積層されてなるビルドアップ層55が設けられている。そして、第2導体34と第3導体58とはビア導体59を介して接続され、異なる層に位置する第3導体58同士はビア導体69を介して電気的に接続されている。

最外層の層間樹脂絶縁層70上には、開口を有するソルダーレジスト層80が形成されている。第1面側のソルダーレジスト層80の開口内には、半導体素子を実装するための半田バンプ86が形成されている。第2面側のソルダーレジスト層80の開口内には、第1基板へ接続するための半田バンプ89が形成されている。

【0033】

図10(A)に、第2基板10の第1面(半導体素子が実装される面)の平面図を示す。

第2基板10は略矩形状であり、第2バンプ86が形成されている半導体素子実装領域R1を有している。半導体素子実装領域R1の中心C1は、第2基板10の第1面の中心C2に対してずれている。すなわち、半導体素子実装領域R1の外周には、他よりも幅広い領域R2が存在する。領域R2は、第2基板10の中心C2から半導体素子実装領域R1の中心C1へ向かう方向とは逆方向に位置する領域である。このとき、半導体素子実装領域R1の外周のうち、領域R2以外の3辺の領域をR3とし、領域R2の幅をr2とし、領域R3の幅をr3としたとき、r2>r3を満たす。

【0034】

この幅広い領域R2に、樹脂充填剤を一旦塗布した後、半導体素子実装領域R1を形成する複数のバンプ86間及びその周辺に樹脂充填剤を流し込む。

これにより、半導体素子実装領域R1と、そこに実装される半導体素子との間に存在する樹脂充填剤に空洞が発生することを効果的に抑制することが可能となる。

また、半導体素子実装領域R1の外周のうち他の3辺の領域R3においては、相対的に幅狭となるため、樹脂充填剤がそれら3辺に沿って流れにくくなり、半導体素子実装領域R1を形成する複数のバンプ間に容易に樹脂充填剤を流動させることが可能となる。

【0035】

図10(B)に示すように、第2基板10の裏面(第2面)は、上記第1基板110のバンプ配列に対応する半田バンプ89から成る半田バンプ配列を有している。このうち、第1基板110の角部Cに相当する箇所には、三角形状の表示マークMが設けられている。この表示マークMは、第1基板110と第2基板10とを接続する際、双方を位置あわせする目的を有する。

【0036】

引き続き、第2基板10の製造方法について図11〜図14を参照し説明される。

(1)厚さ0.05〜0.8mmのガラスエポキシ樹脂またはBT(ビスマレイミドトリアジン)樹脂からなる絶縁性基材30の両面に銅箔32がラミネートされている銅張積層板30Aを出発材料とする(図11(A))。

【0037】

(2)まず、ドリル又はレーザーにより銅張積層板にスルーホール用貫通孔33が形成される(図11(B))。その後、無電解めっき処理により無電解めっき膜31が設けられる(図11(C))。この際、直径の異なる2種類の貫通孔(例えば180μm)33b、貫通孔(例えば、250μm)33aが形成される。

【0038】

(3)電解めっき処理が施され、めっき膜31上、及び、スルーホール用貫通孔33内に電解めっき膜35が設けられる(図11(D))。次いで、電解めっき膜35で形成される空間内に穴埋め樹脂が充填される。なお、穴埋め樹脂を充填することを省略し、スルーホール用貫通孔33内に電解めっき膜が充填されてもよい。

【0039】

(4)第2導体が形成される部分にエッチングレジスト37が形成される(図11(E))。

【0040】

(5)レジスト37が形成されていない箇所の電解めっき膜35、無電解めっき膜31、銅箔32がエッチングにより溶解され後、レジスト37が除去され、スルーホール導体36a,36b及び第2導体34が形成される(図12(A))。その後、第2導体34が粗化される(図示せず)。

【0041】

(6)上記工程を経たコア基板30の両面上に、厚さ約25μmの層間樹脂絶縁層用樹脂フィルム(味の素社製:商品名;ABF−45SH)が温度50〜150℃まで昇温しながら真空圧着ラミネートされ、層間樹脂絶縁層50が設けられる(図12(B))。

【0042】

(7)次に、CO2ガスレーザにて層間樹脂絶縁層50に直径約60μmのバイアホール用開口51が設けられる(図12(C))。クロム酸、過マンガン酸塩などの酸化剤等に浸漬されことによって、層間樹脂絶縁層50に粗化面が設けられる(図示せず)。

【0043】

(8)予め層間樹脂絶縁層50の表層にパラジウムなどの触媒が付与され、無電解めっき液に5〜60分間浸漬されることにより、0.1〜5μmの範囲で無電解めっき膜52が設けられる(図12(D))。

【0044】

(9)上記処理を終えた基板30に、市販の感光性ドライフィルムが貼り付けられ、フォトマスクフィルムを載置して露光した後、炭酸ナトリウムで現像処理し、厚さ15μmのめっきレジスト54が設けられる(図13(A))。

【0045】

(10)次に、電解めっきが施され、厚さ15μmの電解めっき膜56が形成される(図13(B)参照)。

【0046】

(11)めっきレジスト54がアミン溶液で剥離除去された後、そのめっきレジスト下の無電解めっき膜52が硫酸と過酸化水素との混合液を用いるエッチングにて溶解除去され、無電解めっき膜52と電解めっき膜56からなる厚さ約15μmの第2導体58及びビア導体59が形成される(図13(C))。第二銅錯体と有機酸とを含有するエッチング液によって、第3導体58及びビア導体59表面が粗化される(図示せず)。

【0047】

(12)上記(6)−(11)と同様にして、ビア導体69及び第2導体68の形成された層間樹脂絶縁層60と、ビア導体79及び第3導体58の形成された層間樹脂絶縁層70とが形成される(図13(D))。

【0048】

(13)基板の両面に、市販のソルダーレジスト組成物が20μmの厚さで塗布され、乾燥処理が行われた後、ソルダーレジスト開口部のパターンが描画された厚さ5mmのフォトマスクがソルダーレジスト層に密着され紫外線で露光され、DMTG溶液で現像処理され、上面側に小径の開口81と、下面側に大径の開口81が形成される。さらに、加熱処理によりソルダーレジスト層が硬化され、開口81を有し、その厚さが約20μmのソルダーレジストパターン層80が形成される(図14(A))。

【0049】

(14)次に、ソルダーレジスト層80を形成した基板が、無電解ニッケルめっき液に浸漬され、開口81に厚さ5μmのニッケルめっき層82が形成される。さらに、その基板が無電解金めっき液に浸漬され、ニッケルめっき層82上に、厚さ0.03μmの金めっき層84が形成される(図14(B))。ニッケル−金層以外にも、ニッケル−パラジウム−金層が形成されてもよい。

【0050】

(15)マスクを介して、第1面側のソルダーレジスト層の開口71にフラックスが塗布され、同様に、第2面側のソルダーレジスト層の開口71にフラックスが塗布される(図示せず)。開口を有するマスクが基板の第1面側の開口81に位置合わせされ、半田ボール86αが第1面側の開口81内に搭載される。同様に、開口を有するマスクが基板の第2面側の開口81に位置合わせされ、半田ボール89αが第2面側の開口81内に搭載される(図14(C))。

【0051】

(16)約200℃でリフローが行われ、半田ボール86αが半田バンプ86にされ、半田ボール89αが半田バンプ89にされ、第2基板10が完成する(図9)。なお、半田バンプ86の頂部は略平坦にすることが望ましい。仮に第2基板10に反りが生じていたとしても、半田バンプ86の高さを統一でき、ICチップの実装性を向上させることができる。

【0052】

[半導体実装部材の製造方法]

図15を参照して第2基板10と第1基板110との接続について説明される。

図15(A)に示すように、第2基板10が図示しない吸着部材で吸着され、第2基板10の半田バンプ89が、第1基板110のパッド186上の半田ペースト187と対応するように位置決めされる。そして、半田バンプ89を半田ペースト187へ当接させた状態で、約200℃でリフローを行い、半田バンプ89及び半田ペースト187を溶融させて、半田バンプ190を形成し、図15(B)に示すように第2基板10と第1基板110とを接続する。

【0053】

上述したようにリフローする場合、まず半田バンプ190が形成され、その後、支持体188を構成する樹脂が硬化する。すなわち、第1基板110と第2基板10とが半田バンプ190を介して接続された状態で、双方の基板10,110が支持体188を介してさらに強固に接続される。これによれば、アンダーフィル樹脂を用いずとも、第1基板110と第2基板10とを歩留まり良く、強固に接続することが可能となる。

図3に示すように半田バンプ186はペリフェラル配列であり、該半田バンプ196の配列領域の内側に支持体188が設けられているため、双方の基板を支持体188により安定に固定することが可能になる。

そして、半導体素子の実装性を改善するため、半田バンプ86をフラッタニングする場合、第1基板110と第2基板10との接続部分に応力が加わった場合でも、その中央部にはスペーサーの役割を果たす支持体188が配置されているので、第1基板と第2基板との間隔が狭くならず、隣接する半田バンプ190の短絡や、半田バンプ190へのクラックの発生等が生じ難い。

【0054】

ここで、サイズの大きい第1基板と第2基板との間に歩留まり良くアンダーフィル樹脂を充填することは困難であるが、実施形態では、第1基板と第2基板とを接続する第1半田バンプ190が、基板中央部からの外周側に配置され、中央部にはスペーサーの役割を果たす支持体188が配置されるので、アンダーフィル樹脂を用いずとも半田バンプ190の接続信頼性を保つことができる。すなわち、アンダーフィル樹脂を充填する場合は、充填領域が大きいほどボイドが残る可能性が高くなるが、本実施形態ではそういったおそれがない。

【0055】

支持体188を構成する樹脂の硬化温度は、半田バンプ190を構成する半田の融点よりも高い。このため、まず半田バンプ190により双方の基板が確実に接続された後で、支持体により双方の基板同士がより強固に固定される。ここで、支持体による固定はある程度自由が効くので、先に半田バンプ190を形成して基板同士を固定することで、歩留まりが向上する。

【0056】

次いで、半田バンプ86を介して半導体素子200が実装され、半導体素子200と第2基板10との間に樹脂充填剤288が充填される(図1)。

【0057】

本実施形態では、半導体実装部材100を第1基板110と第2基板10との2つのプリント配線板で構成するため、多層配線への対応及び電源強化の目的で、1枚のビルドアップ基板の層数を増やしサイズを大きくするのと比較し、歩留まりが低下しない。

【0058】

図3を参照して上述されたように、実施形態では、中央部に4箇所、角柱状支持体が設けられたが、図17(A)に示すように、支持体が円筒状で、中央部の大径のものを、周囲4箇所に小径のものを配置されることもできる。支持体186を半田バンプ188の配列領域の内側の領域の中心を通る直線上に複数設けられることで、双方の基板を支持体によりさらに安定に固定することが可能になる。また、図17(B)に示すように、楕円状の支持体を一対設けられることも、図17(C)に示すように、1の楕円状の支持体が設けられることもできる。

【0059】

更に、支持体は円筒状で無くとも、図18(A)に側面を示すように、半円状のものでも、図18(B)に示すように、楕円形状であっても良い。

また、本実施形態では、第2基板10の厚みt2を第1基板110の厚みt1よりも大きくなるよう設定したが、これに限られるものではない。すなわち、第2基板10の厚みt2を第1基板110の厚みt1よりも小さくしてもよい。これは、例えばコア基板30の厚みや、第3導体58の層数などに依存する。この場合、実装部材の厚みが低減され、小型化に好適である。

さらに、本実施形態では、コア基板30の内部に直径の異なるスルーホール導体を設けたが、全てのスルーホール導体の径が同じであってもよい。この場合、製造工程の簡素化が図られる。

【符号の説明】

【0060】

10 第2基板

30 コア基板

34 第2導体

36 スルーホール導体

50 層間樹脂絶縁層

58 第3導体

59 ビア導体

80 ソルダーレジスト層

86 第2半田バンプ

100 半導体実装部材

110 第1基板

130 絶縁層

136 ビア導体

137 第1導体

188 支持体

190 半田バンプ

200 半導体素子

【特許請求の範囲】

【請求項1】

貫通孔を有する複数の第1絶縁層と、該第1絶縁層上に形成されている第1導体と、前記貫通孔内に設けられて前記第1導体同士を接続するビア導体と、を有する第1基板と、

貫通孔を有するコア基板と、該コア基板の両面に形成されている第2導体と、前記貫通孔の内部に形成され前記第2導体同士を接続するスルーホール導体と、前記コア基板上及び前記第2導体上に形成されて第2絶縁層と第3導体とが交互に積層されてなるビルドアップ層と、を有する第2基板と、

前記第1導体のうち最外層に位置する第1導体上に設けられ、前記第1基板と前記第2基板とを接続する第1バンプと、

前記第3導体のうち最外層に位置する第3導体上に設けられ、半導体素子を接続する第2バンプと、

からなる半導体実装部材であって、

前記第1基板と前記第2基板との互いの対向面間には支持体が設けられている。

【請求項2】

請求項1の半導体実装部材であって、

前記第1基板と前記第2基板との間には、アンダーフィル樹脂が設けられていない。

【請求項3】

請求項1の半導体実装部材であって、

前記第1バンプはペリフェラル配列であり、該第1バンプの配列領域の内側に前記支持体が設けられている。

【請求項4】

請求項1の半導体実装部材であって、

前記支持体は、前記第1バンプの配列領域の内側の領域の中心を通る直線上に複数設けられている。

【請求項5】

請求項1の半導体実装部材であって、

前記第2バンプの頂部は略平坦である。

【請求項6】

請求項5の半導体実装部材であって、

前記支持体を構成する樹脂の硬化温度は、前記第1半田バンプを構成する半田の融点よりも高い。

【請求項7】

請求項1の半導体実装部材であって、

前記支持体は樹脂から形成されている。

【請求項8】

請求項3の半導体実装部材であって、

前記第1バンプの配列領域を構成する4辺のうち、任意の1辺の配列領域は、該任意の1辺の配列領域に対向する1辺の配列領域と比べて幅が広い。

【請求項9】

請求項1に記載の半導体実装部材の製造方法であって、

前記第1基板上に第1バンプを形成することと、

前記第2基板のうち半導体素子を実装する側の第1面に第2バンプを形成することと、

前記第1基板の最外面上又は前記第2基板の最外面上に前記支持体を設けることと、

前記第1バンプを介して前記第1基板と前記第2基板とを電気的に接続することと、

前記支持体を介して前記第1基板と前記第2基板とを固定することと、

を有することを特徴とする半導体実装部材の製造方法。

【請求項10】

請求項9に記載の半導体実装部材の製造方法であって、

前記支持体を前記第1基板の最外面上に設ける。

【請求項11】

請求項9に記載の半導体実装部材の製造方法であって、

前記第1バンプをリフローした後に前記支持体を硬化させる。

【請求項12】

請求項9に記載の半導体実装部材の製造方法であって、

前記第1基板と前記第2基板との互いの対向面間に前記支持体を設けた後に、第2バンプを平坦化する。

【請求項1】

貫通孔を有する複数の第1絶縁層と、該第1絶縁層上に形成されている第1導体と、前記貫通孔内に設けられて前記第1導体同士を接続するビア導体と、を有する第1基板と、

貫通孔を有するコア基板と、該コア基板の両面に形成されている第2導体と、前記貫通孔の内部に形成され前記第2導体同士を接続するスルーホール導体と、前記コア基板上及び前記第2導体上に形成されて第2絶縁層と第3導体とが交互に積層されてなるビルドアップ層と、を有する第2基板と、

前記第1導体のうち最外層に位置する第1導体上に設けられ、前記第1基板と前記第2基板とを接続する第1バンプと、

前記第3導体のうち最外層に位置する第3導体上に設けられ、半導体素子を接続する第2バンプと、

からなる半導体実装部材であって、

前記第1基板と前記第2基板との互いの対向面間には支持体が設けられている。

【請求項2】

請求項1の半導体実装部材であって、

前記第1基板と前記第2基板との間には、アンダーフィル樹脂が設けられていない。

【請求項3】

請求項1の半導体実装部材であって、

前記第1バンプはペリフェラル配列であり、該第1バンプの配列領域の内側に前記支持体が設けられている。

【請求項4】

請求項1の半導体実装部材であって、

前記支持体は、前記第1バンプの配列領域の内側の領域の中心を通る直線上に複数設けられている。

【請求項5】

請求項1の半導体実装部材であって、

前記第2バンプの頂部は略平坦である。

【請求項6】

請求項5の半導体実装部材であって、

前記支持体を構成する樹脂の硬化温度は、前記第1半田バンプを構成する半田の融点よりも高い。

【請求項7】

請求項1の半導体実装部材であって、

前記支持体は樹脂から形成されている。

【請求項8】

請求項3の半導体実装部材であって、

前記第1バンプの配列領域を構成する4辺のうち、任意の1辺の配列領域は、該任意の1辺の配列領域に対向する1辺の配列領域と比べて幅が広い。

【請求項9】

請求項1に記載の半導体実装部材の製造方法であって、

前記第1基板上に第1バンプを形成することと、

前記第2基板のうち半導体素子を実装する側の第1面に第2バンプを形成することと、

前記第1基板の最外面上又は前記第2基板の最外面上に前記支持体を設けることと、

前記第1バンプを介して前記第1基板と前記第2基板とを電気的に接続することと、

前記支持体を介して前記第1基板と前記第2基板とを固定することと、

を有することを特徴とする半導体実装部材の製造方法。

【請求項10】

請求項9に記載の半導体実装部材の製造方法であって、

前記支持体を前記第1基板の最外面上に設ける。

【請求項11】

請求項9に記載の半導体実装部材の製造方法であって、

前記第1バンプをリフローした後に前記支持体を硬化させる。

【請求項12】

請求項9に記載の半導体実装部材の製造方法であって、

前記第1基板と前記第2基板との互いの対向面間に前記支持体を設けた後に、第2バンプを平坦化する。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−45999(P2013−45999A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−184447(P2011−184447)

【出願日】平成23年8月26日(2011.8.26)

【出願人】(000000158)イビデン株式会社 (856)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月26日(2011.8.26)

【出願人】(000000158)イビデン株式会社 (856)

【Fターム(参考)】

[ Back to top ]