半導体整流装置

【課題】小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体整流装置に関する。

【背景技術】

【0002】

入力される電流を整流して出力する半導体整流装置には、pn接合を有するPiNダイオードと、半導体層と金属との仕事関数の差によるキャリアのポテンシャル障壁を有するショットキーバリアダイオード(SBD)がある。そして、ショットキーバリアダイオードにおいて、半導体層(例えばn型)/金属界面にかかる電界を緩和することを目的に、半導体層表面に半導体層とは異なる導電型の不純物領域(例えばp型)を配置したJBS(Junction Barrier Schottochy barrier diode)がある。さらに、JBSの不純物領域(例えばp型)と金属とのコンタクトをオーミック接続またはオーミック接続に近付け、不純物領域と半導体層とのビルトインポテンシャル(Vbi)を超える電圧がかかった際に小数キャリア注入を起こし、伝導度変調により抵抗を下げる機能を持たせたMPS(Merged PiN−diode Schottky−diode)がある。

【0003】

一方、次世代のパワー半導体デバイス材料として例えば炭化珪素(以下、SiCとも記述する)を代表とするワイドバンドギャップ半導体が期待されている。ワイドバンドギャップ半導体はSiに対して広いバンドギャップを有し、Siよりも高い破壊電界強度及び高い熱伝導率を備える。この特性を活用すれば、低損失かつ高温動作可能なパワー半導体デバイスを実現することができる。

【0004】

MPSでは、伝導度変調を起こす電圧を下げることにより、順方向特性の低抵抗化が実現されるとともに、順方向のサージ電流が流れ込んだ際に、低い順方向電圧で大量の電流を吐き出すことが可能になる。定常状態よりも大きな電流が流れ込んだ際に、その電流は電流×電圧=エネルギーの式のもと、発熱による結晶破壊、電極などの接合破壊の原因となる。しかし、低い順方向電圧で大電流を流すことが可能になれば、発熱エネルギーが抑えられ素子の破壊率を下げることができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許公開公報2007/0278609

【発明の概要】

【発明が解決しようとする課題】

【0006】

もっとも、要求される耐圧が1200V(以下、1200V級とも称する)以上のワイドバンドギャップ半導体を用いたMPSでは、従来の構造を用いても、小数キャリアが注入され伝導度変調を起こす電圧(以下、小数キャリアがホールの場合はホール注入電圧と称する)が、十分に下げられないことが、発明者らによって明らかになった。

【0007】

例えば、従来のSiのMPSでは、SiのVbi=0.8〜1.0Vに対し、伝導度変調を起こす電圧が1〜1.5V、SiCのMPSでは、SiCのVbi=2.5〜3.0Vに対し伝導度変調を起こす電圧が、600V級耐圧の素子で3.2Vと、Vbiに対して+1V以下の電圧を印加することで少数キャリアが注入されていた(SiCのMPS:p+型不純物領域幅2um、n型ショットキー領域幅0.8um、125℃の場合)。

【0008】

MPSにおいて、p+型不純物領域は電子電流(多数キャリア)を流す際にデッドスペースとなるので、p+型不純物領域幅を狭めるのが一般的である。そこで、例えばp+型不純物領域幅を1um、n型不純物領域幅(n型ショットキー領域幅)を1umとし、125℃でのMPSのホール注入電圧を計算すると600V級で4.4V、1200V級で6.9V、3300V級では10.85V、4500V級では13.53Vとなる。したがって、1200V級以上の中耐圧素子、3300V級以上の高耐圧素子では、ホール注入電圧が極めて大きくなり、伝導度変調による低抵抗化が期待できない。

【0009】

本発明が解決しようとする課題は、小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供することにある。

【課題を解決するための手段】

【0010】

実施の形態の半導体整流装置は、ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備える。

【図面の簡単な説明】

【0011】

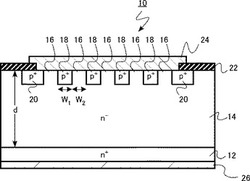

【図1】第1の実施の形態の半導体整流装置の断面図である。

【図2】第1の実施の形態の半導体整流装置の上面図である。

【図3】各種の半導体整流装置の順方向電圧とオン電流密度の関係の説明図である。

【図4】シミュレーションに用いる半導体整流装置の構造断面図である。

【図5】第1の実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。

【図6】第1の実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。

【図7】第1の実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。

【図8】第1の実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧との関係を示す図である。

【図9】第1の実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧との関係を示す図である。

【図10】第1の実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧の各成分との関係を示す図である。

【図11】第1の実施の形態の半導体整流装置のオン電流密度のn型不純物領域幅依存性のシミュレーション結果を示す図である。

【図12】第1の実施の形態の変形例の半導体整流装置の断面図である。

【図13】第2の実施の形態の半導体整流装置の上面図である。

【図14】第2の実施の形態の半導体整流装置の断面図である。

【図15】第2の実施の形態の半導体整流装置の作用の説明図である。

【図16】第2の実施の形態の半導体整流装置のオン電流密度の伝播領域間隔依存性のシミュレーション結果を示す図である。

【図17】第3の実施の形態の半導体整流装置の上面図である。

【図18】第4の実施の形態の半導体整流装置の上面図である。

【図19】第5の実施の形態の半導体整流装置の上面図である。

【図20】第5の実施の形態の半導体整流装置の断面図である。

【図21】第5の実施の形態の半導体整流装置の作用の説明図である。

【図22】第5の実施の形態の変形例の半導体整流装置の上面図である。

【図23】第5の実施の形態の変形例の半導体整流装置の上面図である。

【図24】第6の実施の形態の半導体整流装置の断面図である。

【図25】第8の実施の形態の半導体整流装置の断面図である。

【図26】第9の実施の形態の半導体整流装置の断面図である。

【図27】第10の実施の形態の半導体整流装置の断面図である。

【発明を実施するための形態】

【0012】

以下、図面を参照しつつ本発明の実施の形態を説明する。

【0013】

なお、本明細書中、半導体領域の幅とは、半導体領域を規定する図形の端部の一点からその半導体領域を挟んで存在する別の端部までの最短距離を意味するものとする。そしてある半導体領域の幅が、例えば15μm以上であるという場合、その半導体領域を規定する図形の50%以上の端部において幅が15μm以上であることを意味するものとする。

【0014】

(第1の実施の形態)

本実施の形態の半導体整流装置は、ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備える。

【0015】

上記構成を備えることにより、本実施の形態の半導体整流装置では、ホール注入電圧が十分に低減されるため、順方向のサージ電流に対する耐性を向上させることが可能となる。または、オン電流を増大させることが可能となる。

【0016】

以下、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0017】

図1および図2は、それぞれ本実施の形態の半導体整流装置であるMPSの模式的な断面図および上面図である。図1は図2のAA断面図である。

【0018】

図1に示すように、本実施の形態のMPS10は、例えばn+型の4H−SiC基板(半導体基板)12の上面に、ドリフト層(半導体層)としてn−型SiC層14が形成されている。4H−SiC基板12およびn−型SiC層14は、例えばN(窒素)を不純物として含有している。

【0019】

n+型の4H−SiC基板12は、不純物濃度が、例えば、5E+18〜1E+19atoms/cm3の低抵抗基板である。そして、n−型SiC層14は、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さ(図1中のd)が8μm以上である。

【0020】

MPS10は、要求される耐圧が1200V〜7000VのMPS、いわゆる1200V級〜7000V級の中耐圧〜高耐圧MPSである。このように、高い耐圧および十分なオン電流密度を実現するためには、n−型SiC層14は上記不純物濃度と厚さを備えることが必要条件となる。

【0021】

そして、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0022】

そして、n型不純物領域16に挟まれて、例えばAl(アルミニウム)またはB(ボロン)を、例えば1E+18atoms/cm3程度不純物として含有するp+型不純物領域(第2の半導体領域)18が形成されている。このp+型不純物領域18の深さは、例えば0.3〜1.0μm程度である。p+型不純物領域18の幅(図中W1)は、15μm以上である。p+型不純物領域18の濃度は、第1の電極との接合の特性をオーミックにする、またはオーミックに近付ける観点からできるだけ高濃度であることが望ましい。

【0023】

p+型不純物領域18の幅(図中W1)が、15μm未満であると、ホール注入電圧を十分に低減されず、順方向のサージ電流に対する耐性を向上させることができない。

【0024】

p+型不純物領域18の外側には、p+型不純物領域18よりも幅広で、例えば同程度の不純物濃度および深さを有するリサーフ(RESURF)領域20が形成されている。RESURF領域はMPSの耐圧を安定化させるために設けられる。

【0025】

そして、n−型SiC層14の表面は、例えばシリコン酸化膜かるなる絶縁膜22で覆われる。絶縁膜22の開口部に、n型不純物領域16とp+型不純物領域18とに接合するように、例えば、Niの第1の電極(アノード電極)24が形成されている。第1の電極(アノード電極)24はリサーフ領域20の一部表面にも接するよう形成されている。また、n+型の4H−SiC基板12下面には、例えば、Niの第2の電極(カソード電極)26が形成されている。

【0026】

平面的には、図2に示すように、最内周部にn型不純物領域16があり、外周側に向かって、幅W1のp+型不純物領域18、幅W2のn型不純物領域16が交互に形成されている。ここでは中心が同一であり、略一定の幅W1を有し、正方形を基本とするp+型不純物領域18が2個形成されている。

【0027】

さらに、最外周のn型不純物領域16の外側に、最外周のn型不純物領域16を囲むようにリサーフ領域20が形成されている。このリサーフ領域20に囲まれるn型不純物領域16とp+型不純物領域18がMPSの活性領域である。

【0028】

次に、図1、図2に示す本実施の形態の半導体整流装置の製造方法を説明する。まず、n+型の4H−SiC基板12上面に、エピタキシャル成長により、厚さ(図1中のd)が8μm以上のn−型SiC層14を形成する。

【0029】

次に、n−型SiC層14表面に、リソグラフィー法によりマスク材をパターニングする。このレジストをマスクに、AlまたはBをイオン注入する。その後、マスク材を除去し、基板を洗浄した後、1500℃〜2000℃の活性化アニールを行う。このようにして、p+型不純物領域18およびリサーフ領域20を形成する。

【0030】

その後、例えばシリコン酸化膜からなる絶縁膜22を形成し、n型不純物領域16、p+型不純物領域18およびサーフ領域20の一部が露出するようにリソグラフィー法およびRIE法を用いてパターニングする。そして、例えば、スパッタ法でNiを堆積した後、パターニングして第1の電極(アノード電極)24を形成する。また、4H−SiC基板12下面は、例えば、スパッタ法でNiを堆積した後、パターニングして第2の電極(カソード電極)26が形成される。

【0031】

以上の製造方法により、図1および図2に示すMPS10が製造可能である。

【0032】

図3は、各種の半導体整流装置の順方向電圧とオン電流密度の関係の説明図である。一点鎖線で示されるSBDのオン電流密度は、矢印aで示される電圧で立ち上がる。この立ち上がり電圧は、アノード電極とn型不純物領域との間のショットキー接合のショットキー障壁高さ(φB)で決定される。

【0033】

一方、点線で示されるPiNダイオードのオン電流密度は、矢印bで示される電圧で立ち上がる。この立ち上がり電圧は、pn接合のビルトインポテンシャル(Vbi)で決定される。

【0034】

ショットキー接合とpn接合の両方を備えるMPSの場合、実線で示されるオン電流密度は、矢印aで示される電圧で立ち上がり、矢印cで示されるホール注入が生ずる電圧、すなわちホール注入電圧に達した時に、伝導度変調が生じ急峻な増加を示す。このホール注入電圧を下げることによって、発熱エネルギーが抑えられ、順方向のサージ電流が生じたときの素子の破壊率が低減できる。

【0035】

また、両矢印eで示されるMPSとSBDのオン電流密度の差は、MPSに設けられるp+型不純物領域の面積の割合が大きくなるほど大きくなる。また、両矢印fで示されるMPSとPiNダイオードのオン電流密度の差は、p+型不純物領域の面積の割合が大きくなるほど小さくなる。

【0036】

図4は、電流−電圧特性のシミュレーションに用いる半導体整流装置の構造断面図である。MPSの活性領域のn型不純物領域16とp+型不純物領域18の繰り返しのハーフピッチ分を単位構造とする。

【0037】

p+型不純物領域18の幅の半分がW1/2、n型不純物領域16の幅の半分がW2/2である。また、ドリフト層であるn−型SiC層14の厚さがdである。そして、シミュレーションから、第1の電極(アノード電極)24と第2の電極(カソード電極)26間に電圧が印加され、p+型不純物領域18からn−型SiC層14に小数キャリアが注入される直前の電位分布を求める。

【0038】

シミュレーション結果から得られるSiC基板12下面からp+型不純物領域18底面まで(図中両矢印)の電圧降下をVdriftとする。また、p+型不純物領域18の端部からp+型不純物領域18底面の幅方向の中心部まで(図中両矢印)の電圧降下をVlatとする。

【0039】

図5は、本実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。耐圧が1200V級のMPSの順方向電圧とオン電流密度との関係のシミュレーション結果を示している。比較として、耐圧が1200V級のSBDとPiNダイオードの特性も示す。測定温度は150℃である。

【0040】

MPSのn−型SiC層14の厚さdは8μm、不純物濃度は6E+15atoms/cm3である。SiC基板12の厚さは1.0μm、p+型不純物領域18の深さは0.6μmである。n型不純物領域16の幅の半分W2/2は10μmに固定している。

【0041】

MPSのオン電流密度が急峻に立ち上がるホール注入電圧は、p+型不純物領域18の幅の半分W1/2に依存し、W1/2=9μmでほぼPiNダイオードと同程度の電圧となる。

【0042】

図6は、本実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。耐圧が3300V級のMPSの順方向電圧とオン電流密度との関係のシミュレーション結果を示している。比較として、耐圧が3300V級のSBDとPiNダイオードの特性も示す。測定温度は150℃である。

【0043】

MPSのn−型SiC層14の厚さdは25μm、不純物濃度は4E+15atoms/cm3である。SiC基板12の厚さは1.0μm、p+型不純物領域18の深さは0.6μmである。n型不純物領域16の幅の半分W2/2は10μmに固定している。

【0044】

MPSのオン電流密度が急峻に立ち上がるホール注入電圧は、p+型不純物領域18の幅の半分W1/2に依存し、W1/2=36μmでほぼPiNダイオードと同程度の電圧となる。

【0045】

図7は、本実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。耐圧が4500V級のMPSの順方向電圧とオン電流密度との関係のシミュレーション結果を示している。比較として、耐圧が3300V級のSBDとPiNダイオードの特性も示す。測定温度は150℃である。

【0046】

MPSのn−型SiC層14の厚さdは35μm、不純物濃度は3E+15atoms/cm3である。SiC基板12の厚さは1.0μm、p+型不純物領域18の深さは0.6μmである。n型不純物領域16の幅の半分W2/2は10μmに固定している。

【0047】

MPSのオン電流密度が急峻に立ち上がるホール注入電圧は、p+型不純物領域18の幅の半分W1/2に依存し、W1/2=36μmでほぼPiNダイオードと同程度の電圧となる。

【0048】

このように、上記シミュレーションにより、1200V級の中耐圧のMPSでは、p+型不純物領域の幅の半分で9μm(全幅18μm)程度にまで広げないと、ホール注入電圧がPiNダイオードと同程度にならない。また、3300V級以上の高耐圧のMPSでは、p+型不純物領域の幅の半分で36μm(全幅72μm)程度にまで広げないと、ホール注入電圧がPiNダイオードと同程度にならない。

【0049】

図8は、本実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧との関係を示す図である。図5〜図7の結果をまとめた図である。

【0050】

1200V級の中耐圧MPSと比較して、3300V級および4500V級の高耐圧MPSではホール注入電圧のp+型不純物領域幅依存性が大きい。そして、中耐圧MPSでは、p+型不純物領域の幅の半分が9μm(全幅18μm)程度で上記依存性が飽和される。高耐圧MPSではp+型不純物領域の幅の半分が18μm(全幅36μm)程度で上記依存性が飽和される。このため、本実施の形態は、より高い耐圧のMPSに有効である。すなわち、d=8μm程度の1200V級よりd=20μm程度の3000V級、3000V級よりd=25μm程度の3300V級、3300V級よりd=35μm程度の4500V級でより効果的である。

【0051】

図9は、本実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧との関係を示す図である。図9(a)が3300V級のMPS、図9(b)が4500V級のMPSの場合である。

【0052】

図5〜図7の結果に、測定温度25℃での結果も加えている。白四角が25℃、白丸が150℃の結果である。また、横軸はリニアスケールでプロットし、フィッティングした線を点線で示している。

【0053】

図から明らかなように、3300V級、4500V級いずれの場合も、温度に依存せずp+型不純物領域の半分の幅が7.5μm(全幅15μm)付近でホール注入電圧のp+型不純物領域幅依存性が緩和される。そして、p+型不純物領域の半分の幅が18μm(全幅36μm)以上の領域で依存性がほぼ飽和する。この傾向は、d=8μmの1200V級の中耐圧MPSでも同様である。

【0054】

したがって、d=8μm以上の1200V級以上の中・高耐圧のMPSにおいては、順方向のサージ電流が生じたときの素子の破壊率を低減させる観点および素子の破壊率ばらつきを抑制する観点から、p+型不純物領域幅が全幅で15μm以上であることが必要である。そして、d=8μm程度の中耐圧のMPSにおいては18μm以上であることが望ましく、d=25μm以上の3300V級の高耐圧MPSにおいては、36μm以上であることが望ましい。

【0055】

図10は、本実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧およびその各成分との関係を示す図である。ホール注入電圧を、ショットキーダイオードの立ち上がり電圧Vth、p+型不純物領域の端部からp+型不純物領域底面の幅方向の中心部までの電圧降下であるVlat、SiC基板下面からp+型不純物領域底面までの電圧降下であるVdriftに成分分解して表示する。なお、各成分は、ホール注入直前の電位分布、より具体的には、p+型不純物領域底面の幅方向の中心部においてホール注入濃度が1E14atoms/cm3になるときの電位分布から求めている。

【0056】

1200V級以上、特に3300V級以上の高耐圧のMPSにおいてホール注入電圧が高くなるのは、厚膜かつ低濃度になるドリフト層に起因する電圧降下が大きくなることが主因と考えられる。上述のようにp+型不純物領域の半分の幅が7.5μm(全幅15μm)付近でホール注入電圧のp+型不純物領域幅依存性が緩和される。このとき、

Vlat=0.3×Vdrift

の関係が成立する。

【0057】

また、上述のように、p+型不純物領域の半分の幅が18μm(全幅36μm)以上の領域で依存性がほぼ飽和する。このとき、

Vlat=0.89×Vdrift

の関係が成立する。

【0058】

したがって、3300V級以上の高耐圧のMPSにおいては、順方向のサージ電流が生じたときの素子の破壊率を低減させる観点および素子の破壊率ばらつきを抑制する観点から、

Vlat≧0.3×Vdrift

の関係を充足することが必要であり、

Vlat≧0.89×Vdrift

の関係を充足することが望ましい。

【0059】

上記の関係が充足されるか否かは、半導体整流装置の構造が決まれば、上述のような電位分布のシミュレーションを実行することで確認することが可能である。

【0060】

図11は、本実施の形態の半導体整流装置のオン電流密度のn型不純物領域幅依存性のシミュレーション結果を示す図である。3300級MPSの150℃における測定結果である。p+型不純物領域の半分の幅W1/2は36μmに固定している。

【0061】

MPSの実使用電圧である2〜3V近傍では、n型不純物領域幅が大きくなるとオン電流密度がSBDに近づき、p+型不純物領域幅と同程度の36μm(全幅72μm)でSBDの半分以上が確保でき、144μm(全幅288μm)以上でほぼ同等となる。したがって、オン電流密度を確保する観点からは、n型不純物領域幅が72μm以上であることが望ましく、288μmであることがより望ましい。

【0062】

本実施の形態において、半導体整流装置がMPSとして動作し、かつ、サージ電流を効果的にp+型不純物領域とn型不純物領域間に流すために、第1の電極24とn型不純物領域16とはショットキー接続しており、第1の電極24とp+型不純物領域18とはオーミック接続していることが望ましい。

【0063】

以上のように、本実施の形態の半導体整流装置によれば、低い順方向電圧で大電流を流すことが可能になり、発熱エネルギーが抑えられ、素子の破壊率を下げることができる。したがって、十分なサージ電流耐性または高いオン電流を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供することができる。

【0064】

(第1の実施の形態の変形例)

図12は、第1の実施の形態の変形例の半導体整流装置の模式的な断面図である。このMPSは、第1の電極24が、異なる材料で形成されるオーミック電極24aとショットキー電極24bで構成されること以外は第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0065】

オーミック電極24aは、少なくともp+型不純物領域18の一部に接触し、p+型不純物領域18とオーミック接続している。オーミック電極24aは、例えば、Ti/Alで形成される。また、ショットキー電極24bは、n型不純物領域16に接触し、n型不純物領域16とショットキー接続している。ショットキー電極24bは、例えば、Ti/Alで形成される。

【0066】

このように、第1の電極24を2つの電極で構成することにより、p+型不純物領域18に対する第1の電極のオーミック特性を向上させることが可能となり、さらに特性の向上した高耐圧半導体整流装置を提供することができる。

【0067】

図12の半導体整流装置は、第1の実施の形態の製造方法の第1の電極24dの形成に相当する工程で、スパッタ法で、例えば、Ti/Alを堆積しp+型不純物領域18に選択的に残るようパターニングしてオーミック電極24aを形成した後、スパッタ法で、例えば、Niを堆積してパターニングしてショットキー電極24bを形成することで製造可能である。

【0068】

なお、オーミック電極24aのオーミック性をさらに向上させるために、p+型不純物領域18の表面濃度を、1E+19〜1E+21atoms/cm3と高濃度にすることが望ましい。表面の高濃度化はp+型不純物領域18の表面に局所的にp型不純物をイオン注入することで実現が可能である。

【0069】

(第2の実施の形態)

本実施の形態の半導体整流装置は、第1の実施の形態の半導体整流装置の構成に加え、少なくとも一部が第2のワイドバンドギャップ半導体領域に接続され、第2のワイドバンドギャップ半導体領域より幅の狭い第2導電型の第3のワイドバンドギャップ半導体領域を有する。この第3のワイドバンドギャップ半導体領域を備えること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0070】

上記構成を備えることにより、本実施の形態の半導体整流装置では、順方向のサージ電流が生じたときに、電流を流す領域を拡大かつ分散させることができる。したがって、順方向のサージ電流に対する耐性をさらに向上させることが可能となる。

【0071】

図13および図14は、それぞれ本実施の形態の半導体整流装置であるMPSの模式的な上面図および断面図である。図14(a)は図12のBB断面図、図14(b)は図12のCC断面図である。

【0072】

図に示すように、本実施の形態のMPS30は、第1の実施の形態のMPSに加えて、両端がp+型不純物領域18に接続され、p+型不純物領域18より幅の狭いp+型の伝播領域32を備えている。伝播領域32は、n型不純物領域16に挟まれている。

【0073】

伝播領域32は、p+型不純物領域18と同様にAlまたはBをイオン注入を用いて形成される。伝播領域32の不純物濃度は例えば1E+18atoms/cm3程度であり、深さは、例えば0.3〜1.0μm程度である。

【0074】

図15は、本実施の形態の半導体整流装置の作用の説明図である。図は第1の実施の形態のMPSにおいて、p+型不純物領域の半分の幅を36μm(全幅72μm)、n型不純物領域の半分の幅を144μm(全幅288μm)とした場合の、ホール注入濃度の分布図である。

【0075】

図からあきらかなように、p+型不純物領域下部では選択的にホールが注入されているが、n型不純物領域にはホールが到達していない。したがって、順方向のサージ電流が生じた場合、熱の発生する領域がp+型不純物領域の存在する部分に偏ってしまうことが分かる。これは、局所的な電極剥離や、結晶破壊の要因となり、不良率が上がってしまう恐れがある。

【0076】

本実施の形態によれば、伝播領域32を設けることで、素子の活性化領域の広い範囲にわたってホール注入を分散させる。したがって、発熱領域を分散でき順方向のサージ電流による不良率を一層低減することが可能である。

【0077】

また、p+型不純物領域18より伝播領域32の幅を狭くすることで、伝播領域32を設けることによるオン電流密度の低下も抑制することができる。伝播領域32の幅が、例えば、p+型不純物領域18に要求される15μmよりも小さくなったとしても、p+型不純物領域18からのプラズマスプレッディングの効果により、ホールが伝播され伝播領域32下部でもホールが注入されることが確認されている。

【0078】

さらに、本実施の形態によれば、ダイオード動作の高周波化が可能になる。順方向にバイアスをかけて順方向電流を流す場合、ホール注入が起き、ドリフト層内にホールが蓄積される。この後、逆方向にバイアスをかけてドリフト層内に空乏層を広げ耐圧を持たせる動作をするときは、順方向バイアス時に蓄積されたホールをドリフト層から吐き出すことが必要となる。この時、ホールの吐き出し口はp+型不純物領域を介したアノード電極となるが、n型不純物領域に挟まれる伝播領域が存在することで、実効的なホールの吐き出し口が増える。したがって、ホールが吐き出しやすくなり、ダイオード動作の高周波化が可能になる。

【0079】

図16は、第2の実施の形態の半導体整流装置のオン電流密度の伝播領域間隔依存性のシミュレーション結果を示す図である。シミュレーションは、伝播領域とn型不純物領域のみの単純化した構造で実行している。伝播領域32の幅の半分(W3/2)は1.0μmに固定している。そして、伝播領域間隔の半分(S/2:図12参照)を変数としている。比較のために伝播領域のないSBDの場合も示す。

【0080】

図から明らかなように、伝播領域間隔の半分が4.0μm以上になれば、オン電流密度が伝播領域のないSBDと同等になる。したがって、オン電流密度を確保する観点から伝播領域間隔は全幅で8.0μm以上であることが望ましい。

【0081】

また、伝播領域幅は、0.5μm以上であることが望ましい。0.5μm未満では安定した不純物領域の形成が困難になるおそれがあるからである。

【0082】

また、伝播領域の両端がp+型不純物領域に接続される場合を例に説明したが、伝播領域の一部がp+型不純物領域に接続されていればホールは伝播される。したがって、例えば伝播領域の片端がp+型不純物領域に接続される構造であっても構わない。

【0083】

また、本実施の形態において、MPSとして動作し、かつ、サージ電流を効果的にp+型不純物領域とn型不純物領域間に流すために、第1の電極24とn型不純物領域16とはショットキー接続しており、第1の電極24とp+型不純物領域18、および、第1の電極24と伝播領域32とはオーミック接続していることが望ましい

【0084】

以上のように、本実施の形態の半導体整流装置によれば、第1実施の形態の効果に加え、順方向のサージ電流が生じた時の発熱領域を分散させることが可能となる。したがって、よりサージ電流耐性またはオン電流特性が向上するワイドバンドギャップ半導体を用いた半導体整流装置を提供することができる。

【0085】

また、従来、PiNダイオードを低電流で使うモードでは、ホール注入密度が低いことにより、逆バイアスから順バイアスにスイッチングが起きた時に急激にホールが消滅し、大きな振動波形を生む問題があった。このため、振動波形が収まる時間を考慮する必要があったためにインバータなどの高速化の足かせとなっていた。しかし、第1および第2の実施の形態によれば、高い電流密度ではホール注入が起こるバイポーラモードで動作し、低い電流密度では電子電流によるユニポーラモードで動作させることができる。したがって、従来PiNダイオードで問題となっていた低電流密度動作での振動を抑えることが可能となり半導体整流装置を高速に動作させることが可能となる。

【0086】

(第3の実施の形態)

本実施の形態の半導体整流装置は、第2の半導体領域の表面形状が円形であること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0087】

図17は、本実施の形態の半導体整流装置であるMPSの模式的な上面図である。

【0088】

図17に示すように、n型不純物領域16の中に、表面形状が円形であり、規則的に配列される複数の幅(直径)のp+型不純物領域18形成されている。ここでは、縦横等間隔に、円径のp+型不純物領域18が9個形成されている。

【0089】

さらに、n型不純物領域16の外側に、n型不純物領域16を囲むようにリサーフ領域20が形成されている。このリサーフ領域20に囲まれる領域がMPSの活性領域である。

【0090】

このp+型不純物領域18の深さは、例えば0.3〜1.0μm程度である。p+型不純物領域18の幅あるいは円の直径は、15μm以上である。p+型不純物領域18の濃度は、第1の電極との接合の特性をオーミックにするまたはオーミックに近付ける観点からできるだけ高濃度であることが望ましい。

【0091】

p+型不純物領域18の幅が15μm未満であると、ホール注入電圧が十分に低減されず、順方向のサージ電流に対する耐性が劣化するおそれがある。

【0092】

本実施の形態のMPS40では、p+型不純物領域18の表面形状を円形にすることにより、順方向のサージ電流耐性を保持しつつ、活性領域におけるp+型不純物領域18の占有面積を低減させ、オン電流の向上を図ることが可能となる。順方向のサージ電流耐性は、p+型不純物領域18の幅に依存するため、p+型不純物領域18の形状を円形とすることで、少ないp+型不純物領域18の占有面積で、同一の幅を有する矩形・ストライプ形状と同程度の効果を実現できる。

【0093】

(第4の実施の形態)

本実施の形態の半導体整流装置は、少なくとも一部が前記第2の半導体領域に接続され、第2の半導体領域より幅の狭いワイドギャップ半導体の第2導電型の第3の半導体領域を、さらに有すること以外は、第3の実施の形態と同様である。したがって、第3の実施の形態と重複する内容については記載を省略する。

【0094】

図18は、本実施の形態の半導体整流装置であるMPSの模式的な上面図である。

【0095】

本実施の形態のMPS50は、両端がp+型不純物領域18に接続され、p+型不純物領域18より幅の狭い複数のp+型の伝播領域32を備えている。伝播領域32は、n型不純物領域16に挟まれている。なお、一部の伝播領域32は一端がp+型不純物領域18、他端がリサーフ領域20に接続されている。

【0096】

伝播領域32は、p+型不純物領域18と同様にAlまたはBを、イオン注入を用いて形成される。伝播領域32の不純物濃度は例えば1E+18atoms/cm3程度であり、深さは、例えば0.3〜1.0μm程度である。

【0097】

本実施の形態によれば、伝播領域32を設けることで、素子の活性化領域の広い範囲にわたってホール注入を分散させる。したがって、発熱領域を分散でき順方向のサージ電流による不良率を一層低減することが可能である。

【0098】

また、p+型不純物領域18より伝播領域32の幅を狭くすることで、伝播領域32を設けることによるオン電流密度の低下も抑制することができる。さらに、本実施の形態によれば、ダイオード動作の高周波化が可能になる。

【0099】

(第5の実施の形態)

本実施の形態の半導体整流装置は、第2の半導体領域と第3の半導体領域に囲まれ、第2の半導体領域および第3の半導体領域と第1の半導体領域を介して形成されるワイドギャップ半導体の第2導電型の第4の半導体領域を、さらに有すること以外は、第4の実施の形態と同様である。したがって、第4の実施の形態と重複する内容については記載を省略する。

【0100】

上記構成を備えることにより、本実施の形態の半導体整流装置では、第3のワイドバンドギャップ半導体領域が、第2のワイドバンドギャップ半導体領域で発生したホールの伝播領域として機能する。したがって、素子の活性化領域の広い範囲にわたってホール注入を分散させることが可能になる。よって、素子の発熱領域を分散でき順方向のサージ電流による不良率を低減することが可能となる。さらに、第4のワイドバンドギャップ半導体領域を設けることにより、順方向バイアス時に、第2および第3のワイドバンドギャップ半導体領域で発生する小数キャリアを、ターンオフ時に短時間で吐き出すことが可能となる。したがって、ターンオフ特性に優れた半導体整流装置が実現される。また、第2のワイドバンドギャップ半導体領域の表面形状を円形にすることにより、順方向電流に対するデッドスペースを削減し、オン電流の高い半導体整流装置が実現される。

【0101】

なお、さらに、ターンオフ特性を向上させる観点から、上記第4のワイドバンドギャップ半導体領域の接合深さが、上記第2のワイドバンドギャップ半導体領域および上記第3のワイドバンドギャップ半導体領域の接合深さよりも深いことが望ましい。

【0102】

図19および図20は、それぞれ本実施の形態の半導体整流装置であるMPSの模式的な上面図および断面図である。図20(a)は図19のCC断面図、図20(b)は図19のDD断面図である。

【0103】

図20に示すように、本実施の形態のMPS60は、例えばn+型で六方晶の4H−SiC基板12上面に、ドリフト層としてn−型SiC層14が形成されている。4H−SiC基板12およびn−型SiC層14は、例えばN(窒素)を不純物として含有している。

【0104】

n+型の4H−SiC基板12は、不純物濃度が、例えば、5E+18〜1E+19atoms/cm3の低抵抗基板である。そして、n−型SiC層14は、例えば、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さ(図20中のd)が8μm以上である。

【0105】

n+型の4H−SiC基板12、n−型SiC層14は、例えば、SiCの<11−20>方向に対して、4〜8度のオフ角を有している。

【0106】

そして、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0107】

そして、n型不純物領域16に挟まれて、例えばAl(アルミニウム)またはB(ボロン)を、例えば1E+18atoms/cm3程度不純物として含有する、表面形状が円形のp+型不純物領域18が形成されている。以下、このp+型不純物領域18をホール発生領域とも称する。

【0108】

このp+型不純物領域18の深さは、例えば0.3〜1.0μm程度である。p+型不純物領域18の幅あるいは円の直径(図中W1)は、例えば、15μm以上である。p+型不純物領域18の濃度は、第1の電極との接合の特性をオーミックにするまたはオーミックに近付ける観点からできるだけ高濃度であることが望ましい。

【0109】

p+型不純物領域18の幅(図中W1)が15μm未満であると、ホール注入電圧が十分に低減されず、順方向のサージ電流に対する耐性が劣化するおそれがある。

【0110】

p+型不純物領域18の外側には、例えば同程度の不純物濃度および深さを有するリサーフ(RESURF)領域20が形成されている。RESURF領域はMPSの耐圧を安定化させるために設けられる。

【0111】

そして、n−型SiC層14の表面は、例えばシリコン酸化膜かるなる絶縁膜22で覆われる。絶縁膜22の開口部に、n型不純物領域16とp+型不純物領域18とに接合するように、例えば、Niの第1の電極(アノード電極)24が形成されている。第1の電極(アノード電極)24はリサーフ領域20の一部表面にも接するよう形成されている。また、n+型の4H−SiC基板12下面には、例えば、Niの第2の電極(カソード電極)26が形成されている。

【0112】

平面的には、図19に示すように、n型不純物領域16の中に、表面形状が円形であり、規則的に配列される複数の幅(直径)W1のp+型不純物領域18形成されている。ここでは、縦横等間隔に、円径のp+型不純物領域18が9個形成されている。

【0113】

さらに、n型不純物領域16の外側に、n型不純物領域16を囲むようにリサーフ領域20が形成されている。このリサーフ領域20に囲まれる領域がMPSの活性領域である。

【0114】

そして、本実施の形態のMPS600は、両端がp+型不純物領域18に接続され、p+型不純物領域18より幅の狭い複数のp+型の伝播領域32を備えている。伝播領域32は、n型不純物領域16に挟まれている。なお、一部の伝播領域32は一端がp+型不純物領域18、他端がリサーフ領域20に接続されている。

【0115】

伝播領域32は、p+型不純物領域18と同様にAlまたはBを、イオン注入を用いて形成される。伝播領域32の不純物濃度は例えば1E+18atoms/cm3程度であり、深さは、例えば0.3〜1.0μm程度である。

【0116】

さらに、MPS600は、p+型不純物領域18とp+型の伝播領域32に囲まれ、p+型不純物領域18およびp+型の伝播領域32と、n型不純物領域16を介して形成される島状のp+型のホール吐き出し領域36を備えている。

【0117】

ホール吐き出し領域36は、p+型不純物領域18および伝播領域32と同様にAlまたはBを、イオン注入を用いて形成される。ホール吐き出し領域36の不純物濃度は例えば1E+18atoms/cm3程度であり、深さは、p+型不純物領域18および伝播領域32よりも深いことが望ましい。例えば0.5〜2.0μm程度である。

【0118】

図21は、本実施の形態のMPSの作用を説明する図である。図21(a)は、図23に示した本実施の形態のMPS60に対し、ホール吐き出し領域36を削除したパターンの装置である。図21(b)は、図21(a)のパターンを有するMPSに5.0Vの順方向バイアスを印加した場合の領域Aのホール密度のシミュレーション結果である。

【0119】

まず、MPS60は、p+型不純物領域18を有することにより、ホール注入電圧が低減され、順方向のサージ電流耐性が向上する。サージ電流向上の観点からp+型不純物領域18の幅または直径(図中W1)は、15μm以上であることが望ましい。また、p+型不純物領域18の濃度は、第1の電極との接合の特性をオーミックにするまたはオーミックに近付ける観点からできるだけ高濃度であることが望ましい。

【0120】

そして、MPS60では、p+型不純物領域18の表面形状を円形にすることにより、順方向のサージ電流耐性を保持しつつ、活性領域におけるp+型不純物領域18の占有面積を低減させ、オン電流の向上を図ることが可能となる。順方向のサージ電流耐性は、p+型不純物領域18の幅に依存するため、p+型不純物領域18の形状を円形とすることで、少ないp+型不純物領域18の占有面積で、同一の幅を有する矩形・ストライプ形状と同程度の効果を実現できる。

【0121】

さらに、MPS60ではp+型不純物領域18をつなぐ、伝播領域32を設けることで、素子の発熱領域を分散でき順方向のサージ電流による不良率を低減することが可能となる。

【0122】

もっとも、この構造、すなわち図21(a)の構造では、図21(a)の破線で示す領域Aにおいて、図21(b)に示すように高密度のホールが溜まる。このため、素子のターンオフ時に、この領域に溜まったホールを吐き出すために時間がかかりMPSのターンオフ特性が劣化するという問題が生じる。

【0123】

本実施の形態では、p+型のホール吐き出し領域36をそなえている。このp+型のホール吐き出し領域36を備えることで、領域Aに溜まったホールを吐き出すための時間が短縮され、ターンオフ特性が向上する。

【0124】

よって、本実施の形態によれば、サージ電流耐性にすぐれ、オン電流が向上し、ターンオフ特性に優れた半導体整流装置が実現される。

【0125】

なお、上述のようにホール吐き出し領域36の深さが、p+型不純物領域18および伝播領域32よりも深いことが望ましい。図21(b)に示す様に、高濃度のホールはアノードのp型領域(p+型不純物領域、伝播領域)からカソード領域に広がりをもって流れる。その際、例えば、図21(a)の領域Aのように、p型領域から遠い領域は、深さ方向においてアノード下部よりも低い部分にホールが蓄積する。このため、ホール吐き出し領域が、アノードのp型領域と同じ深さに設けられると、吐き出し効率が悪くなる。したがって、ホール吐き出し領域36の深さを、p+型不純物領域18および伝播領域32よりも深くすることで、ホールの吐き出し効率を向上させることが可能となる。

【0126】

図22は、本実施の形態の半導体装置の第1の変形例を示す図である。図21のMPSに対し、p+型不純物領域18を斜めに接続する伝播領域32がさらに設けられている。本変形例によれば、素子の発熱領域の分散がさらにすすみ、順方向のサージ電流による不良率をより低減することが可能となる。

【0127】

図23は、本実施の形態の半導体装置の第2の変形例を示す図である。図22のMPSに対し、p+型不純物領域18の配列を変化させている。本変形例によっても、図22のMPSと同様の効果が期待される。

【0128】

(第6の実施の形態)

本実施の形態の半導体整流装置は、第1の半導体領域と第1の電極との間に、第2の半導体領域より浅く、かつ、不純物濃度が低い第2導電型の第5の半導体領域を有すること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。なお、第1の電極と第5の半導体領域はショットキー接続している。

【0129】

上記構成を備えることにより、本実施の形態の半導体整流装置では、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を所望の値に調整することが可能となる。

【0130】

以下、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0131】

図24は、本実施の形態の半導体整流装置であるMPSの模式的な断面図である。

【0132】

図24に示すように、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0133】

そして、n型不純物領域(n型ショットキー領域:第1の半導体領域)16と、第1の電極(アノード電極)24との間に、p型不純物領域(第5の半導体領域)40が形成されている。このp型不純物領域(第5の半導体領域)40は、p+型不純物領域(第2の半導体領域)18よりも接合深さが浅い。また、p+型不純物領域(第2の半導体領域)18よりもp型不純物濃度が低く形成されている。

【0134】

p型不純物領域(第5の半導体領域)40深さは、例えば、20〜100nm程度である。また、p型不純物濃度は、例えば、5E+16〜1E+18atoms/cm3程度である。

【0135】

そして、第1の電極(アノード電極)24とp型不純物領域(第5の半導体領域)40はショットキー接続している。ショットキー接続するよう、電極材料・不純物濃度・プロセス熱履歴等が設定される。

【0136】

本実施の形態によれば、p型不純物領域(第5の半導体領域)40の接合深さや不純物濃度を適宜選択して、p型不純物領域(第5の半導体領域)40の障壁高さを調整する。これにより、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を所望の値に調整することが可能となる。

【0137】

(第7の実施の形態)

本実施の形態の半導体整流装置は、第1の電極と第5の半導体領域はオーミック接続していること以外は、第6の実施の形態と同様である。したがって、第6の実施の形態と重複する内容については記載を省略する。

【0138】

第1の電極(アノード電極)24とp型不純物領域(第5の半導体領域)40はオーミック接続している。オーミック接続するよう、電極材料・不純物濃度・プロセス熱履歴等が設定される。

【0139】

本実施の形態によれば、p型不純物領域(第5の半導体領域)40の接合深さや不純物濃度を適宜選択することにより、p型不純物領域(第5の半導体領域)40の障壁高さを調整する。これにより、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を所望の値に調整することが可能となる。

【0140】

(第8の実施の形態)

本実施の形態の半導体整流装置は、第1の半導体領域と第1の電極との間に、第2の半導体領域より不純物濃度が低い第2導電型の第5の半導体領域を有し、第1の電極と第5の半導体領域との間に、第1導電型の第6の半導体領域を有し、第1の電極と第6の半導体領域とがオーミック接続していること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0141】

上記構成を備えることにより、本実施の形態の半導体整流装置では、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を所望の値に調整することが可能となる。

【0142】

以下、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0143】

図25は、本実施の形態の半導体整流装置であるMPSの模式的な断面図である。

【0144】

図25に示すように、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0145】

そして、n型不純物領域(n型ショットキー領域:第1の半導体領域)16と、第1の電極(アノード電極)24との間に、p型不純物領域(第5の半導体領域)40が形成されている。このp型不純物領域(第5の半導体領域)40は、p+型不純物領域(第2の半導体領域)18よりもp型不純物濃度が低く形成されている。

【0146】

p型不純物領域(第5の半導体領域)40の深さは、例えば、20〜100nm程度である。また、p型不純物濃度は、例えば、5E+16〜1E+18atoms/cm3程度である。

【0147】

さらに、第1の電極(アノード電極)24とp型不純物領域(第5の半導体領域)40との間に、n型不純物領域(第6の半導体領域)42が存在する。n型不純物濃度は、例えば、1E+18〜1E+20atoms/cm3程度である。

【0148】

そして、第1の電極(アノード電極)24とn型不純物領域(第6の半導体領域)42はオーミック接続している。オーミック接続するよう、電極材料・不純物濃度・プロセス熱履歴等が設定される。

【0149】

本実施の形態によれば、p型不純物領域(第5の半導体領域)40およびn型不純物領域(第6の半導体領域)42の接合深さや不純物濃度、を適宜選択することにより、障壁高さを調整し、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を、所望の値に調整し低減することが可能となる。

【0150】

(第9の実施の形態)

本実施の形態の半導体整流装置は、第1の半導体領域と第1の電極との間に、第1の半導体領域より不純物濃度の高い第1導電型の第8の半導体領域を有すること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0151】

上記構成を備えることにより、本実施の形態の半導体整流装置では、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を低減することが可能となる。

【0152】

以下、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0153】

図26は、本実施の形態の半導体整流装置であるMPSの模式的な断面図である。

【0154】

図26に示すように、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0155】

そして、n型不純物領域(n型ショットキー領域:第1の半導体領域)16と、第1の電極(アノード電極)24との間に、n型不純物領域(第1の半導体領域)16よりもn型不純物濃度の高いn型不純物領域(第7の半導体領域)44が形成されている。

【0156】

n型不純物領域(第7の半導体領域)40のn型不純物濃度は、例えば、1E+16〜1E+19atoms/cm3程度である。

【0157】

本実施の形態によれば、n型不純物領域(第7の半導体領域)44を備えることにより、半導体側のフェルミレベルが下がり、n型不純物領域(第1の半導体領域)16と、第1の電極(アノード電極)24との間にトンネル電流が流れやすくなる。したがって、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を低減することが可能となる。そして、立ち上がり電圧の低減幅は、n型不純物領域(第7の半導体領域)44のn型不純物濃度を調整することで実現可能である。

【0158】

(第10の実施の形態)

本実施の形態の半導体整流装置は、第2の電極が、半導体基板ではなく半導体層の下面に設けられること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0159】

図27は、本実施の形態の半導体整流装置の断面図である。第2の電極(カソード電極)26が、n−型SiC層14の下面に設けられること以外は第1の実施の形態と同様である。図1に示す第1の実施の形態に比べ、n+型の4H−SiC基板12がないことで厚さが薄くなり、低抵抗化が実現される。本実施の形態の半導体整流装置は、第2の電極(カソード電極)26形成前に、n+型の4H−SiC基板12を研磨により除去することで製造することが可能である。

【0160】

以上、具体例を参照しつつ本発明の実施の形態について説明した。上記、実施の形態はあくまで、例として挙げられているだけであり、本発明を限定するものではない。また、実施の形態の説明においては、半導体整流装置、半導体整流装置の製造方法等で、本発明の説明に直接必要としない部分等については記載を省略したが、必要とされる半導体整流装置、半導体整流装置の製造方法等に関わる要素を適宜選択して用いることができる。

【0161】

例えば、実施の形態においては、第1導電型をn型、第2導電型をp型とする半導体整流装置を例に説明したが、第1導電型をp型、第2導電型をn型とする半導体整流装置であっても構わない。

【0162】

また、実施の形態では、正方形を基本とするp+型不純物領域が2個形成される場合、および、円形の場合を例に説明したが、形状はその他の形状、例えば、所望の幅を有するストライプ状、格子状、ドット状、長方形、六角形、多角形、リング状であっても構わない。また、個数についても1個、あるいは2個より多い数であっても構わない。もっとも、発熱領域を分散させる観点からは、少なくとも複数個のp+型不純物領域を有することが望ましい。

【0163】

また、実施の形態では、ワイドバンドギャップ半導体として炭化珪素(SiC)を例に説明したが、その他のワイドバンドギャップ半導体であるダイヤモンド、窒化ガリウム(GaN)等を適用することも可能である。

【0164】

また、第1の電極はNiやTi/Alを材料とする場合を例に説明したが、MPSとして要求されるショットキー障壁高さ(φB)やコンタクト抵抗を得るために、その他の材料、例えば、Mo、W、Pt、Ta、TaNの単体、これらの合金、シリサイド、カーバイド等を用いることも可能である。

【0165】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体整流装置が、本発明の範囲に包含される。本発明の範囲は、特許請求の範囲およびその均等物の範囲によって定義されるものである。

【符号の説明】

【0166】

10 MPS

12 SiC基板(半導体基板)

14 n−型SiC層(半導体層)

16 n型不純物領域(第1の半導体領域)

18 p+型不純物領域(第2の半導体領域)

20 リサーフ領域

22 絶縁膜

24 第1の電極

26 第2の電極

30 MPS

32 伝播領域(第3の半導体領域)

36 ホール吐き出し領域(第4の半導体領域)

40 p型不純物領域(第5の半導体領域)

42 n型不純物領域(第6の半導体領域)

44 n型不純物領域(第7の半導体領域)

【技術分野】

【0001】

本発明の実施形態は、半導体整流装置に関する。

【背景技術】

【0002】

入力される電流を整流して出力する半導体整流装置には、pn接合を有するPiNダイオードと、半導体層と金属との仕事関数の差によるキャリアのポテンシャル障壁を有するショットキーバリアダイオード(SBD)がある。そして、ショットキーバリアダイオードにおいて、半導体層(例えばn型)/金属界面にかかる電界を緩和することを目的に、半導体層表面に半導体層とは異なる導電型の不純物領域(例えばp型)を配置したJBS(Junction Barrier Schottochy barrier diode)がある。さらに、JBSの不純物領域(例えばp型)と金属とのコンタクトをオーミック接続またはオーミック接続に近付け、不純物領域と半導体層とのビルトインポテンシャル(Vbi)を超える電圧がかかった際に小数キャリア注入を起こし、伝導度変調により抵抗を下げる機能を持たせたMPS(Merged PiN−diode Schottky−diode)がある。

【0003】

一方、次世代のパワー半導体デバイス材料として例えば炭化珪素(以下、SiCとも記述する)を代表とするワイドバンドギャップ半導体が期待されている。ワイドバンドギャップ半導体はSiに対して広いバンドギャップを有し、Siよりも高い破壊電界強度及び高い熱伝導率を備える。この特性を活用すれば、低損失かつ高温動作可能なパワー半導体デバイスを実現することができる。

【0004】

MPSでは、伝導度変調を起こす電圧を下げることにより、順方向特性の低抵抗化が実現されるとともに、順方向のサージ電流が流れ込んだ際に、低い順方向電圧で大量の電流を吐き出すことが可能になる。定常状態よりも大きな電流が流れ込んだ際に、その電流は電流×電圧=エネルギーの式のもと、発熱による結晶破壊、電極などの接合破壊の原因となる。しかし、低い順方向電圧で大電流を流すことが可能になれば、発熱エネルギーが抑えられ素子の破壊率を下げることができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許公開公報2007/0278609

【発明の概要】

【発明が解決しようとする課題】

【0006】

もっとも、要求される耐圧が1200V(以下、1200V級とも称する)以上のワイドバンドギャップ半導体を用いたMPSでは、従来の構造を用いても、小数キャリアが注入され伝導度変調を起こす電圧(以下、小数キャリアがホールの場合はホール注入電圧と称する)が、十分に下げられないことが、発明者らによって明らかになった。

【0007】

例えば、従来のSiのMPSでは、SiのVbi=0.8〜1.0Vに対し、伝導度変調を起こす電圧が1〜1.5V、SiCのMPSでは、SiCのVbi=2.5〜3.0Vに対し伝導度変調を起こす電圧が、600V級耐圧の素子で3.2Vと、Vbiに対して+1V以下の電圧を印加することで少数キャリアが注入されていた(SiCのMPS:p+型不純物領域幅2um、n型ショットキー領域幅0.8um、125℃の場合)。

【0008】

MPSにおいて、p+型不純物領域は電子電流(多数キャリア)を流す際にデッドスペースとなるので、p+型不純物領域幅を狭めるのが一般的である。そこで、例えばp+型不純物領域幅を1um、n型不純物領域幅(n型ショットキー領域幅)を1umとし、125℃でのMPSのホール注入電圧を計算すると600V級で4.4V、1200V級で6.9V、3300V級では10.85V、4500V級では13.53Vとなる。したがって、1200V級以上の中耐圧素子、3300V級以上の高耐圧素子では、ホール注入電圧が極めて大きくなり、伝導度変調による低抵抗化が期待できない。

【0009】

本発明が解決しようとする課題は、小数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供することにある。

【課題を解決するための手段】

【0010】

実施の形態の半導体整流装置は、ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備える。

【図面の簡単な説明】

【0011】

【図1】第1の実施の形態の半導体整流装置の断面図である。

【図2】第1の実施の形態の半導体整流装置の上面図である。

【図3】各種の半導体整流装置の順方向電圧とオン電流密度の関係の説明図である。

【図4】シミュレーションに用いる半導体整流装置の構造断面図である。

【図5】第1の実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。

【図6】第1の実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。

【図7】第1の実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。

【図8】第1の実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧との関係を示す図である。

【図9】第1の実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧との関係を示す図である。

【図10】第1の実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧の各成分との関係を示す図である。

【図11】第1の実施の形態の半導体整流装置のオン電流密度のn型不純物領域幅依存性のシミュレーション結果を示す図である。

【図12】第1の実施の形態の変形例の半導体整流装置の断面図である。

【図13】第2の実施の形態の半導体整流装置の上面図である。

【図14】第2の実施の形態の半導体整流装置の断面図である。

【図15】第2の実施の形態の半導体整流装置の作用の説明図である。

【図16】第2の実施の形態の半導体整流装置のオン電流密度の伝播領域間隔依存性のシミュレーション結果を示す図である。

【図17】第3の実施の形態の半導体整流装置の上面図である。

【図18】第4の実施の形態の半導体整流装置の上面図である。

【図19】第5の実施の形態の半導体整流装置の上面図である。

【図20】第5の実施の形態の半導体整流装置の断面図である。

【図21】第5の実施の形態の半導体整流装置の作用の説明図である。

【図22】第5の実施の形態の変形例の半導体整流装置の上面図である。

【図23】第5の実施の形態の変形例の半導体整流装置の上面図である。

【図24】第6の実施の形態の半導体整流装置の断面図である。

【図25】第8の実施の形態の半導体整流装置の断面図である。

【図26】第9の実施の形態の半導体整流装置の断面図である。

【図27】第10の実施の形態の半導体整流装置の断面図である。

【発明を実施するための形態】

【0012】

以下、図面を参照しつつ本発明の実施の形態を説明する。

【0013】

なお、本明細書中、半導体領域の幅とは、半導体領域を規定する図形の端部の一点からその半導体領域を挟んで存在する別の端部までの最短距離を意味するものとする。そしてある半導体領域の幅が、例えば15μm以上であるという場合、その半導体領域を規定する図形の50%以上の端部において幅が15μm以上であることを意味するものとする。

【0014】

(第1の実施の形態)

本実施の形態の半導体整流装置は、ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1および第2の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備える。

【0015】

上記構成を備えることにより、本実施の形態の半導体整流装置では、ホール注入電圧が十分に低減されるため、順方向のサージ電流に対する耐性を向上させることが可能となる。または、オン電流を増大させることが可能となる。

【0016】

以下、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0017】

図1および図2は、それぞれ本実施の形態の半導体整流装置であるMPSの模式的な断面図および上面図である。図1は図2のAA断面図である。

【0018】

図1に示すように、本実施の形態のMPS10は、例えばn+型の4H−SiC基板(半導体基板)12の上面に、ドリフト層(半導体層)としてn−型SiC層14が形成されている。4H−SiC基板12およびn−型SiC層14は、例えばN(窒素)を不純物として含有している。

【0019】

n+型の4H−SiC基板12は、不純物濃度が、例えば、5E+18〜1E+19atoms/cm3の低抵抗基板である。そして、n−型SiC層14は、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さ(図1中のd)が8μm以上である。

【0020】

MPS10は、要求される耐圧が1200V〜7000VのMPS、いわゆる1200V級〜7000V級の中耐圧〜高耐圧MPSである。このように、高い耐圧および十分なオン電流密度を実現するためには、n−型SiC層14は上記不純物濃度と厚さを備えることが必要条件となる。

【0021】

そして、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0022】

そして、n型不純物領域16に挟まれて、例えばAl(アルミニウム)またはB(ボロン)を、例えば1E+18atoms/cm3程度不純物として含有するp+型不純物領域(第2の半導体領域)18が形成されている。このp+型不純物領域18の深さは、例えば0.3〜1.0μm程度である。p+型不純物領域18の幅(図中W1)は、15μm以上である。p+型不純物領域18の濃度は、第1の電極との接合の特性をオーミックにする、またはオーミックに近付ける観点からできるだけ高濃度であることが望ましい。

【0023】

p+型不純物領域18の幅(図中W1)が、15μm未満であると、ホール注入電圧を十分に低減されず、順方向のサージ電流に対する耐性を向上させることができない。

【0024】

p+型不純物領域18の外側には、p+型不純物領域18よりも幅広で、例えば同程度の不純物濃度および深さを有するリサーフ(RESURF)領域20が形成されている。RESURF領域はMPSの耐圧を安定化させるために設けられる。

【0025】

そして、n−型SiC層14の表面は、例えばシリコン酸化膜かるなる絶縁膜22で覆われる。絶縁膜22の開口部に、n型不純物領域16とp+型不純物領域18とに接合するように、例えば、Niの第1の電極(アノード電極)24が形成されている。第1の電極(アノード電極)24はリサーフ領域20の一部表面にも接するよう形成されている。また、n+型の4H−SiC基板12下面には、例えば、Niの第2の電極(カソード電極)26が形成されている。

【0026】

平面的には、図2に示すように、最内周部にn型不純物領域16があり、外周側に向かって、幅W1のp+型不純物領域18、幅W2のn型不純物領域16が交互に形成されている。ここでは中心が同一であり、略一定の幅W1を有し、正方形を基本とするp+型不純物領域18が2個形成されている。

【0027】

さらに、最外周のn型不純物領域16の外側に、最外周のn型不純物領域16を囲むようにリサーフ領域20が形成されている。このリサーフ領域20に囲まれるn型不純物領域16とp+型不純物領域18がMPSの活性領域である。

【0028】

次に、図1、図2に示す本実施の形態の半導体整流装置の製造方法を説明する。まず、n+型の4H−SiC基板12上面に、エピタキシャル成長により、厚さ(図1中のd)が8μm以上のn−型SiC層14を形成する。

【0029】

次に、n−型SiC層14表面に、リソグラフィー法によりマスク材をパターニングする。このレジストをマスクに、AlまたはBをイオン注入する。その後、マスク材を除去し、基板を洗浄した後、1500℃〜2000℃の活性化アニールを行う。このようにして、p+型不純物領域18およびリサーフ領域20を形成する。

【0030】

その後、例えばシリコン酸化膜からなる絶縁膜22を形成し、n型不純物領域16、p+型不純物領域18およびサーフ領域20の一部が露出するようにリソグラフィー法およびRIE法を用いてパターニングする。そして、例えば、スパッタ法でNiを堆積した後、パターニングして第1の電極(アノード電極)24を形成する。また、4H−SiC基板12下面は、例えば、スパッタ法でNiを堆積した後、パターニングして第2の電極(カソード電極)26が形成される。

【0031】

以上の製造方法により、図1および図2に示すMPS10が製造可能である。

【0032】

図3は、各種の半導体整流装置の順方向電圧とオン電流密度の関係の説明図である。一点鎖線で示されるSBDのオン電流密度は、矢印aで示される電圧で立ち上がる。この立ち上がり電圧は、アノード電極とn型不純物領域との間のショットキー接合のショットキー障壁高さ(φB)で決定される。

【0033】

一方、点線で示されるPiNダイオードのオン電流密度は、矢印bで示される電圧で立ち上がる。この立ち上がり電圧は、pn接合のビルトインポテンシャル(Vbi)で決定される。

【0034】

ショットキー接合とpn接合の両方を備えるMPSの場合、実線で示されるオン電流密度は、矢印aで示される電圧で立ち上がり、矢印cで示されるホール注入が生ずる電圧、すなわちホール注入電圧に達した時に、伝導度変調が生じ急峻な増加を示す。このホール注入電圧を下げることによって、発熱エネルギーが抑えられ、順方向のサージ電流が生じたときの素子の破壊率が低減できる。

【0035】

また、両矢印eで示されるMPSとSBDのオン電流密度の差は、MPSに設けられるp+型不純物領域の面積の割合が大きくなるほど大きくなる。また、両矢印fで示されるMPSとPiNダイオードのオン電流密度の差は、p+型不純物領域の面積の割合が大きくなるほど小さくなる。

【0036】

図4は、電流−電圧特性のシミュレーションに用いる半導体整流装置の構造断面図である。MPSの活性領域のn型不純物領域16とp+型不純物領域18の繰り返しのハーフピッチ分を単位構造とする。

【0037】

p+型不純物領域18の幅の半分がW1/2、n型不純物領域16の幅の半分がW2/2である。また、ドリフト層であるn−型SiC層14の厚さがdである。そして、シミュレーションから、第1の電極(アノード電極)24と第2の電極(カソード電極)26間に電圧が印加され、p+型不純物領域18からn−型SiC層14に小数キャリアが注入される直前の電位分布を求める。

【0038】

シミュレーション結果から得られるSiC基板12下面からp+型不純物領域18底面まで(図中両矢印)の電圧降下をVdriftとする。また、p+型不純物領域18の端部からp+型不純物領域18底面の幅方向の中心部まで(図中両矢印)の電圧降下をVlatとする。

【0039】

図5は、本実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。耐圧が1200V級のMPSの順方向電圧とオン電流密度との関係のシミュレーション結果を示している。比較として、耐圧が1200V級のSBDとPiNダイオードの特性も示す。測定温度は150℃である。

【0040】

MPSのn−型SiC層14の厚さdは8μm、不純物濃度は6E+15atoms/cm3である。SiC基板12の厚さは1.0μm、p+型不純物領域18の深さは0.6μmである。n型不純物領域16の幅の半分W2/2は10μmに固定している。

【0041】

MPSのオン電流密度が急峻に立ち上がるホール注入電圧は、p+型不純物領域18の幅の半分W1/2に依存し、W1/2=9μmでほぼPiNダイオードと同程度の電圧となる。

【0042】

図6は、本実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。耐圧が3300V級のMPSの順方向電圧とオン電流密度との関係のシミュレーション結果を示している。比較として、耐圧が3300V級のSBDとPiNダイオードの特性も示す。測定温度は150℃である。

【0043】

MPSのn−型SiC層14の厚さdは25μm、不純物濃度は4E+15atoms/cm3である。SiC基板12の厚さは1.0μm、p+型不純物領域18の深さは0.6μmである。n型不純物領域16の幅の半分W2/2は10μmに固定している。

【0044】

MPSのオン電流密度が急峻に立ち上がるホール注入電圧は、p+型不純物領域18の幅の半分W1/2に依存し、W1/2=36μmでほぼPiNダイオードと同程度の電圧となる。

【0045】

図7は、本実施の形態の半導体整流装置のオン電流密度のp+型不純物領域幅依存性のシミュレーション結果を示す図である。耐圧が4500V級のMPSの順方向電圧とオン電流密度との関係のシミュレーション結果を示している。比較として、耐圧が3300V級のSBDとPiNダイオードの特性も示す。測定温度は150℃である。

【0046】

MPSのn−型SiC層14の厚さdは35μm、不純物濃度は3E+15atoms/cm3である。SiC基板12の厚さは1.0μm、p+型不純物領域18の深さは0.6μmである。n型不純物領域16の幅の半分W2/2は10μmに固定している。

【0047】

MPSのオン電流密度が急峻に立ち上がるホール注入電圧は、p+型不純物領域18の幅の半分W1/2に依存し、W1/2=36μmでほぼPiNダイオードと同程度の電圧となる。

【0048】

このように、上記シミュレーションにより、1200V級の中耐圧のMPSでは、p+型不純物領域の幅の半分で9μm(全幅18μm)程度にまで広げないと、ホール注入電圧がPiNダイオードと同程度にならない。また、3300V級以上の高耐圧のMPSでは、p+型不純物領域の幅の半分で36μm(全幅72μm)程度にまで広げないと、ホール注入電圧がPiNダイオードと同程度にならない。

【0049】

図8は、本実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧との関係を示す図である。図5〜図7の結果をまとめた図である。

【0050】

1200V級の中耐圧MPSと比較して、3300V級および4500V級の高耐圧MPSではホール注入電圧のp+型不純物領域幅依存性が大きい。そして、中耐圧MPSでは、p+型不純物領域の幅の半分が9μm(全幅18μm)程度で上記依存性が飽和される。高耐圧MPSではp+型不純物領域の幅の半分が18μm(全幅36μm)程度で上記依存性が飽和される。このため、本実施の形態は、より高い耐圧のMPSに有効である。すなわち、d=8μm程度の1200V級よりd=20μm程度の3000V級、3000V級よりd=25μm程度の3300V級、3300V級よりd=35μm程度の4500V級でより効果的である。

【0051】

図9は、本実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧との関係を示す図である。図9(a)が3300V級のMPS、図9(b)が4500V級のMPSの場合である。

【0052】

図5〜図7の結果に、測定温度25℃での結果も加えている。白四角が25℃、白丸が150℃の結果である。また、横軸はリニアスケールでプロットし、フィッティングした線を点線で示している。

【0053】

図から明らかなように、3300V級、4500V級いずれの場合も、温度に依存せずp+型不純物領域の半分の幅が7.5μm(全幅15μm)付近でホール注入電圧のp+型不純物領域幅依存性が緩和される。そして、p+型不純物領域の半分の幅が18μm(全幅36μm)以上の領域で依存性がほぼ飽和する。この傾向は、d=8μmの1200V級の中耐圧MPSでも同様である。

【0054】

したがって、d=8μm以上の1200V級以上の中・高耐圧のMPSにおいては、順方向のサージ電流が生じたときの素子の破壊率を低減させる観点および素子の破壊率ばらつきを抑制する観点から、p+型不純物領域幅が全幅で15μm以上であることが必要である。そして、d=8μm程度の中耐圧のMPSにおいては18μm以上であることが望ましく、d=25μm以上の3300V級の高耐圧MPSにおいては、36μm以上であることが望ましい。

【0055】

図10は、本実施の形態の半導体整流装置のp+型不純物領域幅とホール注入電圧およびその各成分との関係を示す図である。ホール注入電圧を、ショットキーダイオードの立ち上がり電圧Vth、p+型不純物領域の端部からp+型不純物領域底面の幅方向の中心部までの電圧降下であるVlat、SiC基板下面からp+型不純物領域底面までの電圧降下であるVdriftに成分分解して表示する。なお、各成分は、ホール注入直前の電位分布、より具体的には、p+型不純物領域底面の幅方向の中心部においてホール注入濃度が1E14atoms/cm3になるときの電位分布から求めている。

【0056】

1200V級以上、特に3300V級以上の高耐圧のMPSにおいてホール注入電圧が高くなるのは、厚膜かつ低濃度になるドリフト層に起因する電圧降下が大きくなることが主因と考えられる。上述のようにp+型不純物領域の半分の幅が7.5μm(全幅15μm)付近でホール注入電圧のp+型不純物領域幅依存性が緩和される。このとき、

Vlat=0.3×Vdrift

の関係が成立する。

【0057】

また、上述のように、p+型不純物領域の半分の幅が18μm(全幅36μm)以上の領域で依存性がほぼ飽和する。このとき、

Vlat=0.89×Vdrift

の関係が成立する。

【0058】

したがって、3300V級以上の高耐圧のMPSにおいては、順方向のサージ電流が生じたときの素子の破壊率を低減させる観点および素子の破壊率ばらつきを抑制する観点から、

Vlat≧0.3×Vdrift

の関係を充足することが必要であり、

Vlat≧0.89×Vdrift

の関係を充足することが望ましい。

【0059】

上記の関係が充足されるか否かは、半導体整流装置の構造が決まれば、上述のような電位分布のシミュレーションを実行することで確認することが可能である。

【0060】

図11は、本実施の形態の半導体整流装置のオン電流密度のn型不純物領域幅依存性のシミュレーション結果を示す図である。3300級MPSの150℃における測定結果である。p+型不純物領域の半分の幅W1/2は36μmに固定している。

【0061】

MPSの実使用電圧である2〜3V近傍では、n型不純物領域幅が大きくなるとオン電流密度がSBDに近づき、p+型不純物領域幅と同程度の36μm(全幅72μm)でSBDの半分以上が確保でき、144μm(全幅288μm)以上でほぼ同等となる。したがって、オン電流密度を確保する観点からは、n型不純物領域幅が72μm以上であることが望ましく、288μmであることがより望ましい。

【0062】

本実施の形態において、半導体整流装置がMPSとして動作し、かつ、サージ電流を効果的にp+型不純物領域とn型不純物領域間に流すために、第1の電極24とn型不純物領域16とはショットキー接続しており、第1の電極24とp+型不純物領域18とはオーミック接続していることが望ましい。

【0063】

以上のように、本実施の形態の半導体整流装置によれば、低い順方向電圧で大電流を流すことが可能になり、発熱エネルギーが抑えられ、素子の破壊率を下げることができる。したがって、十分なサージ電流耐性または高いオン電流を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供することができる。

【0064】

(第1の実施の形態の変形例)

図12は、第1の実施の形態の変形例の半導体整流装置の模式的な断面図である。このMPSは、第1の電極24が、異なる材料で形成されるオーミック電極24aとショットキー電極24bで構成されること以外は第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0065】

オーミック電極24aは、少なくともp+型不純物領域18の一部に接触し、p+型不純物領域18とオーミック接続している。オーミック電極24aは、例えば、Ti/Alで形成される。また、ショットキー電極24bは、n型不純物領域16に接触し、n型不純物領域16とショットキー接続している。ショットキー電極24bは、例えば、Ti/Alで形成される。

【0066】

このように、第1の電極24を2つの電極で構成することにより、p+型不純物領域18に対する第1の電極のオーミック特性を向上させることが可能となり、さらに特性の向上した高耐圧半導体整流装置を提供することができる。

【0067】

図12の半導体整流装置は、第1の実施の形態の製造方法の第1の電極24dの形成に相当する工程で、スパッタ法で、例えば、Ti/Alを堆積しp+型不純物領域18に選択的に残るようパターニングしてオーミック電極24aを形成した後、スパッタ法で、例えば、Niを堆積してパターニングしてショットキー電極24bを形成することで製造可能である。

【0068】

なお、オーミック電極24aのオーミック性をさらに向上させるために、p+型不純物領域18の表面濃度を、1E+19〜1E+21atoms/cm3と高濃度にすることが望ましい。表面の高濃度化はp+型不純物領域18の表面に局所的にp型不純物をイオン注入することで実現が可能である。

【0069】

(第2の実施の形態)

本実施の形態の半導体整流装置は、第1の実施の形態の半導体整流装置の構成に加え、少なくとも一部が第2のワイドバンドギャップ半導体領域に接続され、第2のワイドバンドギャップ半導体領域より幅の狭い第2導電型の第3のワイドバンドギャップ半導体領域を有する。この第3のワイドバンドギャップ半導体領域を備えること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0070】

上記構成を備えることにより、本実施の形態の半導体整流装置では、順方向のサージ電流が生じたときに、電流を流す領域を拡大かつ分散させることができる。したがって、順方向のサージ電流に対する耐性をさらに向上させることが可能となる。

【0071】

図13および図14は、それぞれ本実施の形態の半導体整流装置であるMPSの模式的な上面図および断面図である。図14(a)は図12のBB断面図、図14(b)は図12のCC断面図である。

【0072】

図に示すように、本実施の形態のMPS30は、第1の実施の形態のMPSに加えて、両端がp+型不純物領域18に接続され、p+型不純物領域18より幅の狭いp+型の伝播領域32を備えている。伝播領域32は、n型不純物領域16に挟まれている。

【0073】

伝播領域32は、p+型不純物領域18と同様にAlまたはBをイオン注入を用いて形成される。伝播領域32の不純物濃度は例えば1E+18atoms/cm3程度であり、深さは、例えば0.3〜1.0μm程度である。

【0074】

図15は、本実施の形態の半導体整流装置の作用の説明図である。図は第1の実施の形態のMPSにおいて、p+型不純物領域の半分の幅を36μm(全幅72μm)、n型不純物領域の半分の幅を144μm(全幅288μm)とした場合の、ホール注入濃度の分布図である。

【0075】

図からあきらかなように、p+型不純物領域下部では選択的にホールが注入されているが、n型不純物領域にはホールが到達していない。したがって、順方向のサージ電流が生じた場合、熱の発生する領域がp+型不純物領域の存在する部分に偏ってしまうことが分かる。これは、局所的な電極剥離や、結晶破壊の要因となり、不良率が上がってしまう恐れがある。

【0076】

本実施の形態によれば、伝播領域32を設けることで、素子の活性化領域の広い範囲にわたってホール注入を分散させる。したがって、発熱領域を分散でき順方向のサージ電流による不良率を一層低減することが可能である。

【0077】

また、p+型不純物領域18より伝播領域32の幅を狭くすることで、伝播領域32を設けることによるオン電流密度の低下も抑制することができる。伝播領域32の幅が、例えば、p+型不純物領域18に要求される15μmよりも小さくなったとしても、p+型不純物領域18からのプラズマスプレッディングの効果により、ホールが伝播され伝播領域32下部でもホールが注入されることが確認されている。

【0078】

さらに、本実施の形態によれば、ダイオード動作の高周波化が可能になる。順方向にバイアスをかけて順方向電流を流す場合、ホール注入が起き、ドリフト層内にホールが蓄積される。この後、逆方向にバイアスをかけてドリフト層内に空乏層を広げ耐圧を持たせる動作をするときは、順方向バイアス時に蓄積されたホールをドリフト層から吐き出すことが必要となる。この時、ホールの吐き出し口はp+型不純物領域を介したアノード電極となるが、n型不純物領域に挟まれる伝播領域が存在することで、実効的なホールの吐き出し口が増える。したがって、ホールが吐き出しやすくなり、ダイオード動作の高周波化が可能になる。

【0079】

図16は、第2の実施の形態の半導体整流装置のオン電流密度の伝播領域間隔依存性のシミュレーション結果を示す図である。シミュレーションは、伝播領域とn型不純物領域のみの単純化した構造で実行している。伝播領域32の幅の半分(W3/2)は1.0μmに固定している。そして、伝播領域間隔の半分(S/2:図12参照)を変数としている。比較のために伝播領域のないSBDの場合も示す。

【0080】

図から明らかなように、伝播領域間隔の半分が4.0μm以上になれば、オン電流密度が伝播領域のないSBDと同等になる。したがって、オン電流密度を確保する観点から伝播領域間隔は全幅で8.0μm以上であることが望ましい。

【0081】

また、伝播領域幅は、0.5μm以上であることが望ましい。0.5μm未満では安定した不純物領域の形成が困難になるおそれがあるからである。

【0082】

また、伝播領域の両端がp+型不純物領域に接続される場合を例に説明したが、伝播領域の一部がp+型不純物領域に接続されていればホールは伝播される。したがって、例えば伝播領域の片端がp+型不純物領域に接続される構造であっても構わない。

【0083】

また、本実施の形態において、MPSとして動作し、かつ、サージ電流を効果的にp+型不純物領域とn型不純物領域間に流すために、第1の電極24とn型不純物領域16とはショットキー接続しており、第1の電極24とp+型不純物領域18、および、第1の電極24と伝播領域32とはオーミック接続していることが望ましい

【0084】

以上のように、本実施の形態の半導体整流装置によれば、第1実施の形態の効果に加え、順方向のサージ電流が生じた時の発熱領域を分散させることが可能となる。したがって、よりサージ電流耐性またはオン電流特性が向上するワイドバンドギャップ半導体を用いた半導体整流装置を提供することができる。

【0085】

また、従来、PiNダイオードを低電流で使うモードでは、ホール注入密度が低いことにより、逆バイアスから順バイアスにスイッチングが起きた時に急激にホールが消滅し、大きな振動波形を生む問題があった。このため、振動波形が収まる時間を考慮する必要があったためにインバータなどの高速化の足かせとなっていた。しかし、第1および第2の実施の形態によれば、高い電流密度ではホール注入が起こるバイポーラモードで動作し、低い電流密度では電子電流によるユニポーラモードで動作させることができる。したがって、従来PiNダイオードで問題となっていた低電流密度動作での振動を抑えることが可能となり半導体整流装置を高速に動作させることが可能となる。

【0086】

(第3の実施の形態)

本実施の形態の半導体整流装置は、第2の半導体領域の表面形状が円形であること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0087】

図17は、本実施の形態の半導体整流装置であるMPSの模式的な上面図である。

【0088】

図17に示すように、n型不純物領域16の中に、表面形状が円形であり、規則的に配列される複数の幅(直径)のp+型不純物領域18形成されている。ここでは、縦横等間隔に、円径のp+型不純物領域18が9個形成されている。

【0089】

さらに、n型不純物領域16の外側に、n型不純物領域16を囲むようにリサーフ領域20が形成されている。このリサーフ領域20に囲まれる領域がMPSの活性領域である。

【0090】

このp+型不純物領域18の深さは、例えば0.3〜1.0μm程度である。p+型不純物領域18の幅あるいは円の直径は、15μm以上である。p+型不純物領域18の濃度は、第1の電極との接合の特性をオーミックにするまたはオーミックに近付ける観点からできるだけ高濃度であることが望ましい。

【0091】

p+型不純物領域18の幅が15μm未満であると、ホール注入電圧が十分に低減されず、順方向のサージ電流に対する耐性が劣化するおそれがある。

【0092】

本実施の形態のMPS40では、p+型不純物領域18の表面形状を円形にすることにより、順方向のサージ電流耐性を保持しつつ、活性領域におけるp+型不純物領域18の占有面積を低減させ、オン電流の向上を図ることが可能となる。順方向のサージ電流耐性は、p+型不純物領域18の幅に依存するため、p+型不純物領域18の形状を円形とすることで、少ないp+型不純物領域18の占有面積で、同一の幅を有する矩形・ストライプ形状と同程度の効果を実現できる。

【0093】

(第4の実施の形態)

本実施の形態の半導体整流装置は、少なくとも一部が前記第2の半導体領域に接続され、第2の半導体領域より幅の狭いワイドギャップ半導体の第2導電型の第3の半導体領域を、さらに有すること以外は、第3の実施の形態と同様である。したがって、第3の実施の形態と重複する内容については記載を省略する。

【0094】

図18は、本実施の形態の半導体整流装置であるMPSの模式的な上面図である。

【0095】

本実施の形態のMPS50は、両端がp+型不純物領域18に接続され、p+型不純物領域18より幅の狭い複数のp+型の伝播領域32を備えている。伝播領域32は、n型不純物領域16に挟まれている。なお、一部の伝播領域32は一端がp+型不純物領域18、他端がリサーフ領域20に接続されている。

【0096】

伝播領域32は、p+型不純物領域18と同様にAlまたはBを、イオン注入を用いて形成される。伝播領域32の不純物濃度は例えば1E+18atoms/cm3程度であり、深さは、例えば0.3〜1.0μm程度である。

【0097】

本実施の形態によれば、伝播領域32を設けることで、素子の活性化領域の広い範囲にわたってホール注入を分散させる。したがって、発熱領域を分散でき順方向のサージ電流による不良率を一層低減することが可能である。

【0098】

また、p+型不純物領域18より伝播領域32の幅を狭くすることで、伝播領域32を設けることによるオン電流密度の低下も抑制することができる。さらに、本実施の形態によれば、ダイオード動作の高周波化が可能になる。

【0099】

(第5の実施の形態)

本実施の形態の半導体整流装置は、第2の半導体領域と第3の半導体領域に囲まれ、第2の半導体領域および第3の半導体領域と第1の半導体領域を介して形成されるワイドギャップ半導体の第2導電型の第4の半導体領域を、さらに有すること以外は、第4の実施の形態と同様である。したがって、第4の実施の形態と重複する内容については記載を省略する。

【0100】

上記構成を備えることにより、本実施の形態の半導体整流装置では、第3のワイドバンドギャップ半導体領域が、第2のワイドバンドギャップ半導体領域で発生したホールの伝播領域として機能する。したがって、素子の活性化領域の広い範囲にわたってホール注入を分散させることが可能になる。よって、素子の発熱領域を分散でき順方向のサージ電流による不良率を低減することが可能となる。さらに、第4のワイドバンドギャップ半導体領域を設けることにより、順方向バイアス時に、第2および第3のワイドバンドギャップ半導体領域で発生する小数キャリアを、ターンオフ時に短時間で吐き出すことが可能となる。したがって、ターンオフ特性に優れた半導体整流装置が実現される。また、第2のワイドバンドギャップ半導体領域の表面形状を円形にすることにより、順方向電流に対するデッドスペースを削減し、オン電流の高い半導体整流装置が実現される。

【0101】

なお、さらに、ターンオフ特性を向上させる観点から、上記第4のワイドバンドギャップ半導体領域の接合深さが、上記第2のワイドバンドギャップ半導体領域および上記第3のワイドバンドギャップ半導体領域の接合深さよりも深いことが望ましい。

【0102】

図19および図20は、それぞれ本実施の形態の半導体整流装置であるMPSの模式的な上面図および断面図である。図20(a)は図19のCC断面図、図20(b)は図19のDD断面図である。

【0103】

図20に示すように、本実施の形態のMPS60は、例えばn+型で六方晶の4H−SiC基板12上面に、ドリフト層としてn−型SiC層14が形成されている。4H−SiC基板12およびn−型SiC層14は、例えばN(窒素)を不純物として含有している。

【0104】

n+型の4H−SiC基板12は、不純物濃度が、例えば、5E+18〜1E+19atoms/cm3の低抵抗基板である。そして、n−型SiC層14は、例えば、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さ(図20中のd)が8μm以上である。

【0105】

n+型の4H−SiC基板12、n−型SiC層14は、例えば、SiCの<11−20>方向に対して、4〜8度のオフ角を有している。

【0106】

そして、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0107】

そして、n型不純物領域16に挟まれて、例えばAl(アルミニウム)またはB(ボロン)を、例えば1E+18atoms/cm3程度不純物として含有する、表面形状が円形のp+型不純物領域18が形成されている。以下、このp+型不純物領域18をホール発生領域とも称する。

【0108】

このp+型不純物領域18の深さは、例えば0.3〜1.0μm程度である。p+型不純物領域18の幅あるいは円の直径(図中W1)は、例えば、15μm以上である。p+型不純物領域18の濃度は、第1の電極との接合の特性をオーミックにするまたはオーミックに近付ける観点からできるだけ高濃度であることが望ましい。

【0109】

p+型不純物領域18の幅(図中W1)が15μm未満であると、ホール注入電圧が十分に低減されず、順方向のサージ電流に対する耐性が劣化するおそれがある。

【0110】

p+型不純物領域18の外側には、例えば同程度の不純物濃度および深さを有するリサーフ(RESURF)領域20が形成されている。RESURF領域はMPSの耐圧を安定化させるために設けられる。

【0111】

そして、n−型SiC層14の表面は、例えばシリコン酸化膜かるなる絶縁膜22で覆われる。絶縁膜22の開口部に、n型不純物領域16とp+型不純物領域18とに接合するように、例えば、Niの第1の電極(アノード電極)24が形成されている。第1の電極(アノード電極)24はリサーフ領域20の一部表面にも接するよう形成されている。また、n+型の4H−SiC基板12下面には、例えば、Niの第2の電極(カソード電極)26が形成されている。

【0112】

平面的には、図19に示すように、n型不純物領域16の中に、表面形状が円形であり、規則的に配列される複数の幅(直径)W1のp+型不純物領域18形成されている。ここでは、縦横等間隔に、円径のp+型不純物領域18が9個形成されている。

【0113】

さらに、n型不純物領域16の外側に、n型不純物領域16を囲むようにリサーフ領域20が形成されている。このリサーフ領域20に囲まれる領域がMPSの活性領域である。

【0114】

そして、本実施の形態のMPS600は、両端がp+型不純物領域18に接続され、p+型不純物領域18より幅の狭い複数のp+型の伝播領域32を備えている。伝播領域32は、n型不純物領域16に挟まれている。なお、一部の伝播領域32は一端がp+型不純物領域18、他端がリサーフ領域20に接続されている。

【0115】

伝播領域32は、p+型不純物領域18と同様にAlまたはBを、イオン注入を用いて形成される。伝播領域32の不純物濃度は例えば1E+18atoms/cm3程度であり、深さは、例えば0.3〜1.0μm程度である。

【0116】

さらに、MPS600は、p+型不純物領域18とp+型の伝播領域32に囲まれ、p+型不純物領域18およびp+型の伝播領域32と、n型不純物領域16を介して形成される島状のp+型のホール吐き出し領域36を備えている。

【0117】

ホール吐き出し領域36は、p+型不純物領域18および伝播領域32と同様にAlまたはBを、イオン注入を用いて形成される。ホール吐き出し領域36の不純物濃度は例えば1E+18atoms/cm3程度であり、深さは、p+型不純物領域18および伝播領域32よりも深いことが望ましい。例えば0.5〜2.0μm程度である。

【0118】

図21は、本実施の形態のMPSの作用を説明する図である。図21(a)は、図23に示した本実施の形態のMPS60に対し、ホール吐き出し領域36を削除したパターンの装置である。図21(b)は、図21(a)のパターンを有するMPSに5.0Vの順方向バイアスを印加した場合の領域Aのホール密度のシミュレーション結果である。

【0119】

まず、MPS60は、p+型不純物領域18を有することにより、ホール注入電圧が低減され、順方向のサージ電流耐性が向上する。サージ電流向上の観点からp+型不純物領域18の幅または直径(図中W1)は、15μm以上であることが望ましい。また、p+型不純物領域18の濃度は、第1の電極との接合の特性をオーミックにするまたはオーミックに近付ける観点からできるだけ高濃度であることが望ましい。

【0120】

そして、MPS60では、p+型不純物領域18の表面形状を円形にすることにより、順方向のサージ電流耐性を保持しつつ、活性領域におけるp+型不純物領域18の占有面積を低減させ、オン電流の向上を図ることが可能となる。順方向のサージ電流耐性は、p+型不純物領域18の幅に依存するため、p+型不純物領域18の形状を円形とすることで、少ないp+型不純物領域18の占有面積で、同一の幅を有する矩形・ストライプ形状と同程度の効果を実現できる。

【0121】

さらに、MPS60ではp+型不純物領域18をつなぐ、伝播領域32を設けることで、素子の発熱領域を分散でき順方向のサージ電流による不良率を低減することが可能となる。

【0122】

もっとも、この構造、すなわち図21(a)の構造では、図21(a)の破線で示す領域Aにおいて、図21(b)に示すように高密度のホールが溜まる。このため、素子のターンオフ時に、この領域に溜まったホールを吐き出すために時間がかかりMPSのターンオフ特性が劣化するという問題が生じる。

【0123】

本実施の形態では、p+型のホール吐き出し領域36をそなえている。このp+型のホール吐き出し領域36を備えることで、領域Aに溜まったホールを吐き出すための時間が短縮され、ターンオフ特性が向上する。

【0124】

よって、本実施の形態によれば、サージ電流耐性にすぐれ、オン電流が向上し、ターンオフ特性に優れた半導体整流装置が実現される。

【0125】

なお、上述のようにホール吐き出し領域36の深さが、p+型不純物領域18および伝播領域32よりも深いことが望ましい。図21(b)に示す様に、高濃度のホールはアノードのp型領域(p+型不純物領域、伝播領域)からカソード領域に広がりをもって流れる。その際、例えば、図21(a)の領域Aのように、p型領域から遠い領域は、深さ方向においてアノード下部よりも低い部分にホールが蓄積する。このため、ホール吐き出し領域が、アノードのp型領域と同じ深さに設けられると、吐き出し効率が悪くなる。したがって、ホール吐き出し領域36の深さを、p+型不純物領域18および伝播領域32よりも深くすることで、ホールの吐き出し効率を向上させることが可能となる。

【0126】

図22は、本実施の形態の半導体装置の第1の変形例を示す図である。図21のMPSに対し、p+型不純物領域18を斜めに接続する伝播領域32がさらに設けられている。本変形例によれば、素子の発熱領域の分散がさらにすすみ、順方向のサージ電流による不良率をより低減することが可能となる。

【0127】

図23は、本実施の形態の半導体装置の第2の変形例を示す図である。図22のMPSに対し、p+型不純物領域18の配列を変化させている。本変形例によっても、図22のMPSと同様の効果が期待される。

【0128】

(第6の実施の形態)

本実施の形態の半導体整流装置は、第1の半導体領域と第1の電極との間に、第2の半導体領域より浅く、かつ、不純物濃度が低い第2導電型の第5の半導体領域を有すること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。なお、第1の電極と第5の半導体領域はショットキー接続している。

【0129】

上記構成を備えることにより、本実施の形態の半導体整流装置では、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を所望の値に調整することが可能となる。

【0130】

以下、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0131】

図24は、本実施の形態の半導体整流装置であるMPSの模式的な断面図である。

【0132】

図24に示すように、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0133】

そして、n型不純物領域(n型ショットキー領域:第1の半導体領域)16と、第1の電極(アノード電極)24との間に、p型不純物領域(第5の半導体領域)40が形成されている。このp型不純物領域(第5の半導体領域)40は、p+型不純物領域(第2の半導体領域)18よりも接合深さが浅い。また、p+型不純物領域(第2の半導体領域)18よりもp型不純物濃度が低く形成されている。

【0134】

p型不純物領域(第5の半導体領域)40深さは、例えば、20〜100nm程度である。また、p型不純物濃度は、例えば、5E+16〜1E+18atoms/cm3程度である。

【0135】

そして、第1の電極(アノード電極)24とp型不純物領域(第5の半導体領域)40はショットキー接続している。ショットキー接続するよう、電極材料・不純物濃度・プロセス熱履歴等が設定される。

【0136】

本実施の形態によれば、p型不純物領域(第5の半導体領域)40の接合深さや不純物濃度を適宜選択して、p型不純物領域(第5の半導体領域)40の障壁高さを調整する。これにより、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を所望の値に調整することが可能となる。

【0137】

(第7の実施の形態)

本実施の形態の半導体整流装置は、第1の電極と第5の半導体領域はオーミック接続していること以外は、第6の実施の形態と同様である。したがって、第6の実施の形態と重複する内容については記載を省略する。

【0138】

第1の電極(アノード電極)24とp型不純物領域(第5の半導体領域)40はオーミック接続している。オーミック接続するよう、電極材料・不純物濃度・プロセス熱履歴等が設定される。

【0139】

本実施の形態によれば、p型不純物領域(第5の半導体領域)40の接合深さや不純物濃度を適宜選択することにより、p型不純物領域(第5の半導体領域)40の障壁高さを調整する。これにより、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を所望の値に調整することが可能となる。

【0140】

(第8の実施の形態)

本実施の形態の半導体整流装置は、第1の半導体領域と第1の電極との間に、第2の半導体領域より不純物濃度が低い第2導電型の第5の半導体領域を有し、第1の電極と第5の半導体領域との間に、第1導電型の第6の半導体領域を有し、第1の電極と第6の半導体領域とがオーミック接続していること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0141】

上記構成を備えることにより、本実施の形態の半導体整流装置では、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を所望の値に調整することが可能となる。

【0142】

以下、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0143】

図25は、本実施の形態の半導体整流装置であるMPSの模式的な断面図である。

【0144】

図25に示すように、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0145】

そして、n型不純物領域(n型ショットキー領域:第1の半導体領域)16と、第1の電極(アノード電極)24との間に、p型不純物領域(第5の半導体領域)40が形成されている。このp型不純物領域(第5の半導体領域)40は、p+型不純物領域(第2の半導体領域)18よりもp型不純物濃度が低く形成されている。

【0146】

p型不純物領域(第5の半導体領域)40の深さは、例えば、20〜100nm程度である。また、p型不純物濃度は、例えば、5E+16〜1E+18atoms/cm3程度である。

【0147】

さらに、第1の電極(アノード電極)24とp型不純物領域(第5の半導体領域)40との間に、n型不純物領域(第6の半導体領域)42が存在する。n型不純物濃度は、例えば、1E+18〜1E+20atoms/cm3程度である。

【0148】

そして、第1の電極(アノード電極)24とn型不純物領域(第6の半導体領域)42はオーミック接続している。オーミック接続するよう、電極材料・不純物濃度・プロセス熱履歴等が設定される。

【0149】

本実施の形態によれば、p型不純物領域(第5の半導体領域)40およびn型不純物領域(第6の半導体領域)42の接合深さや不純物濃度、を適宜選択することにより、障壁高さを調整し、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を、所望の値に調整し低減することが可能となる。

【0150】

(第9の実施の形態)

本実施の形態の半導体整流装置は、第1の半導体領域と第1の電極との間に、第1の半導体領域より不純物濃度の高い第1導電型の第8の半導体領域を有すること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0151】

上記構成を備えることにより、本実施の形態の半導体整流装置では、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を低減することが可能となる。

【0152】

以下、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0153】

図26は、本実施の形態の半導体整流装置であるMPSの模式的な断面図である。

【0154】

図26に示すように、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0155】

そして、n型不純物領域(n型ショットキー領域:第1の半導体領域)16と、第1の電極(アノード電極)24との間に、n型不純物領域(第1の半導体領域)16よりもn型不純物濃度の高いn型不純物領域(第7の半導体領域)44が形成されている。

【0156】

n型不純物領域(第7の半導体領域)40のn型不純物濃度は、例えば、1E+16〜1E+19atoms/cm3程度である。

【0157】

本実施の形態によれば、n型不純物領域(第7の半導体領域)44を備えることにより、半導体側のフェルミレベルが下がり、n型不純物領域(第1の半導体領域)16と、第1の電極(アノード電極)24との間にトンネル電流が流れやすくなる。したがって、順方向の立ち上がり電圧(図3における矢印aで示される電圧)を低減することが可能となる。そして、立ち上がり電圧の低減幅は、n型不純物領域(第7の半導体領域)44のn型不純物濃度を調整することで実現可能である。

【0158】

(第10の実施の形態)

本実施の形態の半導体整流装置は、第2の電極が、半導体基板ではなく半導体層の下面に設けられること以外は、第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0159】

図27は、本実施の形態の半導体整流装置の断面図である。第2の電極(カソード電極)26が、n−型SiC層14の下面に設けられること以外は第1の実施の形態と同様である。図1に示す第1の実施の形態に比べ、n+型の4H−SiC基板12がないことで厚さが薄くなり、低抵抗化が実現される。本実施の形態の半導体整流装置は、第2の電極(カソード電極)26形成前に、n+型の4H−SiC基板12を研磨により除去することで製造することが可能である。

【0160】

以上、具体例を参照しつつ本発明の実施の形態について説明した。上記、実施の形態はあくまで、例として挙げられているだけであり、本発明を限定するものではない。また、実施の形態の説明においては、半導体整流装置、半導体整流装置の製造方法等で、本発明の説明に直接必要としない部分等については記載を省略したが、必要とされる半導体整流装置、半導体整流装置の製造方法等に関わる要素を適宜選択して用いることができる。

【0161】

例えば、実施の形態においては、第1導電型をn型、第2導電型をp型とする半導体整流装置を例に説明したが、第1導電型をp型、第2導電型をn型とする半導体整流装置であっても構わない。

【0162】

また、実施の形態では、正方形を基本とするp+型不純物領域が2個形成される場合、および、円形の場合を例に説明したが、形状はその他の形状、例えば、所望の幅を有するストライプ状、格子状、ドット状、長方形、六角形、多角形、リング状であっても構わない。また、個数についても1個、あるいは2個より多い数であっても構わない。もっとも、発熱領域を分散させる観点からは、少なくとも複数個のp+型不純物領域を有することが望ましい。

【0163】

また、実施の形態では、ワイドバンドギャップ半導体として炭化珪素(SiC)を例に説明したが、その他のワイドバンドギャップ半導体であるダイヤモンド、窒化ガリウム(GaN)等を適用することも可能である。

【0164】

また、第1の電極はNiやTi/Alを材料とする場合を例に説明したが、MPSとして要求されるショットキー障壁高さ(φB)やコンタクト抵抗を得るために、その他の材料、例えば、Mo、W、Pt、Ta、TaNの単体、これらの合金、シリサイド、カーバイド等を用いることも可能である。

【0165】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体整流装置が、本発明の範囲に包含される。本発明の範囲は、特許請求の範囲およびその均等物の範囲によって定義されるものである。

【符号の説明】

【0166】

10 MPS

12 SiC基板(半導体基板)

14 n−型SiC層(半導体層)

16 n型不純物領域(第1の半導体領域)

18 p+型不純物領域(第2の半導体領域)

20 リサーフ領域

22 絶縁膜

24 第1の電極

26 第2の電極

30 MPS

32 伝播領域(第3の半導体領域)

36 ホール吐き出し領域(第4の半導体領域)

40 p型不純物領域(第5の半導体領域)

42 n型不純物領域(第6の半導体領域)

44 n型不純物領域(第7の半導体領域)

【特許請求の範囲】

【請求項1】

ワイドギャップ半導体の第1導電型の半導体基板と、

前記半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、

前記半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、

前記第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、

前記第1および第2の半導体領域上に形成される第1の電極と、

前記半導体基板の下面に形成される第2の電極と、

を備えることを特徴とする半導体整流装置。

【請求項2】

前記第2の半導体領域の表面形状が円形であることを特徴とする請求項1記載の半導体整流装置。

【請求項3】

前記半導体層の厚さが20μm以上であることを特徴とする請求項1または請求項2記載の半導体整流装置。

【請求項4】

少なくとも一部が前記第2の半導体領域に接続され、前記第2の半導体領域より幅の狭いワイドギャップ半導体の第2導電型の第3の半導体領域を、さらに有することを特徴とする請求項1ないし請求項3いずれか一項記載の半導体整流装置。

【請求項5】

前記第2の半導体領域と前記第3の半導体領域に囲まれ、前記第2の半導体領域および前記第3の半導体領域と、前記第1の半導体領域を介して形成されるワイドギャップ半導体の第2導電型の第4の半導体領域を、さらに有することを特徴とする請求項1ないし請求項4いずれか一項記載の半導体整流装置。

【請求項6】

前記第4の半導体領域の接合深さが、前記第2の半導体領域および前記第3の半導体領域の接合深さよりも深いことを特徴とする請求項1ないし請求項5いずれか一項記載の半導体整流装置。

【請求項7】

前記第1の電極と前記第1の半導体領域とはショットキー接続しており、

前記第1の電極と前記第2の半導体領域とはオーミック接続していることを特徴とする請求項1ないし請求項6いずれか一項記載の半導体整流装置。

【請求項8】

前記第1の電極と前記第1の半導体領域とはショットキー接続しており、

前記第1の電極と前記第2の半導体領域とはオーミック接続しており、

前記第1の電極と前記第3の半導体領域とはオーミック接続していることを特徴とする請求項4記載の半導体整流装置。

【請求項9】

前記ワイドバンドギャップ半導体が炭化珪素(SiC)であることを特徴とする請求項1ないし請求項8いずれか一項記載の半導体整流装置。

【請求項10】

前記第1の半導体領域と前記第1の電極との間に、前記第2の半導体領域より浅く、かつ、不純物濃度が低い第2導電型の第5の半導体領域を有することを特徴とする請求項1ないし請求項6いずれか一項記載の半導体整流装置。

【請求項11】

前記第1の電極と前記第5の半導体領域がショットキー接続していることを特徴とする請求項10記載の半導体整流装置。

【請求項12】

前記第1の電極と前記第5の半導体領域がオーミック接続していることを特徴とする請求項10記載の半導体整流装置。

【請求項13】

前記第1の電極と前記第5の半導体領域との間に、第1導電型の第6の半導体領域を有し、前記第1の電極と前記第6の半導体領域とがオーミック接続していることを特徴とする請求項10記載の半導体整流装置。

【請求項14】

前記第1の半導体領域と前記第1の電極との間に、前記第1の半導体領域より不純物濃度の高い第1導電型の第7の半導体領域を有することを特徴とする請求項1ないし請求項6いずれか一項記載の半導体整流装置。

【請求項15】

不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、

前記半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、

前記第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、

前記第1および第2の半導体領域上に形成される第1の電極と、

前記半導体層の下面に形成される第2の電極と、

を備えることを特徴とする半導体整流装置。

【請求項16】

前記第2の半導体領域の表面形状が円形であることを特徴とする請求項15記載の半導体整流装置。

【請求項1】

ワイドギャップ半導体の第1導電型の半導体基板と、

前記半導体基板の上面に形成され、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、

前記半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、

前記第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、

前記第1および第2の半導体領域上に形成される第1の電極と、

前記半導体基板の下面に形成される第2の電極と、

を備えることを特徴とする半導体整流装置。

【請求項2】

前記第2の半導体領域の表面形状が円形であることを特徴とする請求項1記載の半導体整流装置。

【請求項3】

前記半導体層の厚さが20μm以上であることを特徴とする請求項1または請求項2記載の半導体整流装置。

【請求項4】

少なくとも一部が前記第2の半導体領域に接続され、前記第2の半導体領域より幅の狭いワイドギャップ半導体の第2導電型の第3の半導体領域を、さらに有することを特徴とする請求項1ないし請求項3いずれか一項記載の半導体整流装置。

【請求項5】

前記第2の半導体領域と前記第3の半導体領域に囲まれ、前記第2の半導体領域および前記第3の半導体領域と、前記第1の半導体領域を介して形成されるワイドギャップ半導体の第2導電型の第4の半導体領域を、さらに有することを特徴とする請求項1ないし請求項4いずれか一項記載の半導体整流装置。

【請求項6】

前記第4の半導体領域の接合深さが、前記第2の半導体領域および前記第3の半導体領域の接合深さよりも深いことを特徴とする請求項1ないし請求項5いずれか一項記載の半導体整流装置。

【請求項7】

前記第1の電極と前記第1の半導体領域とはショットキー接続しており、

前記第1の電極と前記第2の半導体領域とはオーミック接続していることを特徴とする請求項1ないし請求項6いずれか一項記載の半導体整流装置。

【請求項8】

前記第1の電極と前記第1の半導体領域とはショットキー接続しており、

前記第1の電極と前記第2の半導体領域とはオーミック接続しており、

前記第1の電極と前記第3の半導体領域とはオーミック接続していることを特徴とする請求項4記載の半導体整流装置。

【請求項9】

前記ワイドバンドギャップ半導体が炭化珪素(SiC)であることを特徴とする請求項1ないし請求項8いずれか一項記載の半導体整流装置。

【請求項10】

前記第1の半導体領域と前記第1の電極との間に、前記第2の半導体領域より浅く、かつ、不純物濃度が低い第2導電型の第5の半導体領域を有することを特徴とする請求項1ないし請求項6いずれか一項記載の半導体整流装置。

【請求項11】

前記第1の電極と前記第5の半導体領域がショットキー接続していることを特徴とする請求項10記載の半導体整流装置。

【請求項12】

前記第1の電極と前記第5の半導体領域がオーミック接続していることを特徴とする請求項10記載の半導体整流装置。

【請求項13】

前記第1の電極と前記第5の半導体領域との間に、第1導電型の第6の半導体領域を有し、前記第1の電極と前記第6の半導体領域とがオーミック接続していることを特徴とする請求項10記載の半導体整流装置。

【請求項14】

前記第1の半導体領域と前記第1の電極との間に、前記第1の半導体領域より不純物濃度の高い第1導電型の第7の半導体領域を有することを特徴とする請求項1ないし請求項6いずれか一項記載の半導体整流装置。

【請求項15】

不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、厚さが8μm以上のワイドギャップ半導体の第1導電型の半導体層と、

前記半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、

前記第1の半導体領域に挟まれて形成され、幅が15μm以上であるワイドギャップ半導体の第2導電型の第2の半導体領域と、

前記第1および第2の半導体領域上に形成される第1の電極と、

前記半導体層の下面に形成される第2の電極と、

を備えることを特徴とする半導体整流装置。

【請求項16】

前記第2の半導体領域の表面形状が円形であることを特徴とする請求項15記載の半導体整流装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図15】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図15】

【図21】

【公開番号】特開2012−182404(P2012−182404A)

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願番号】特願2011−45935(P2011−45935)

【出願日】平成23年3月3日(2011.3.3)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願日】平成23年3月3日(2011.3.3)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]