半導体整流装置

【課題】少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施の形態は、半導体整流装置に関する。

【背景技術】

【0002】

入力される電流を整流して出力する半導体整流装置として、pn接合を有するPiNダイオードと、半導体層と金属との仕事関数の差によるキャリアのポテンシャル障壁を有するショットキーバリアダイオード(SBD)がある。そして、ショットキーバリアダイオードにおいて、半導体層(例えばn型)/金属界面にかかる電界を緩和することを目的に、半導体層表面に半導体層とは異なる導電型の不純物領域(例えばp型)を配置したJBS(Junction Barrier Schottochy barrier diode)がある。さらに、JBSの不純物領域(例えばp型)と金属とのコンタクトをオーミック接合またはオーミック接合に近付け、不純物領域と半導体層とのビルトインポテンシャル(Vbi)を超える電圧がかかった際に少数キャリア注入を起こし、伝導度変調により抵抗を下げる機能を持たせたMPS(Merged PiN−diode Schottky−diode)がある。

【0003】

一方、次世代のパワー半導体デバイス材料として例えば炭化珪素(以下、SiCとも記述する)を代表とするワイドバンドギャップ半導体が期待されている。ワイドバンドギャップ半導体はシリコン(Si)に対して広いバンドギャップを有し、Siよりも高い破壊電界強度及び高い熱伝導率を備える。この特性を活用すれば、低損失かつ高温動作可能なパワー半導体デバイスを実現することができる。

【0004】

MPSでは、伝導度変調を起こす電圧を下げることにより、順方向特性の低抵抗化が実現されるとともに、順方向のサージ電流が流れ込んだ際に、低い順方向電圧で大量の電流を吐き出すことが可能になる。定常状態よりも大きな電流が流れ込んだ際に、その電流は電流×電圧=パワーの式のもと、発熱による結晶破壊、電極などの接合破壊の原因となる。しかし、低い順方向電圧で大電流を流すことが可能になれば、発熱が抑えられ素子の破壊率を下げることができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許公開公報2007/0278609

【発明の概要】

【発明が解決しようとする課題】

【0006】

もっとも、要求される耐圧が1200V(以下、1200V級とも称する)以上のワイドバンドギャップ半導体を用いたMPSでは、従来の構造を用いても、少数キャリアが注入され伝導度変調を起こす電圧(以下、少数キャリアがホールの場合はホール注入電圧と称する)が、十分に下げられないことが、発明者らによって明らかになった。

【0007】

例えば、従来のSiのMPSでは、SiのVbi=0.8〜1.0Vに対し、伝導度変調を起こす電圧が1〜1.5V、SiCのMPSでは、SiCのVbi=2.5〜3.0Vに対し伝導度変調を起こす電圧が、600V級耐圧の素子で3.2Vと、Vbiに対して+1V以下の電圧を印加することで少数キャリアが注入されていた(SiCのMPS:p型不純物領域幅2um、n型ショットキー領域幅0.8um、125℃の場合)。

【0008】

MPSにおいて、p型不純物領域は電子電流(多数キャリア)を流す際にデッドスペースとなるので、p型不純物領域幅を狭めるのが一般的である。そこで、例えばp型不純物領域幅を1um、n型不純物領域幅(n型ショットキー領域幅)を1umとし、125℃でのMPSのホール注入電圧を計算すると600V級で4.4V、1200V級で6.9V、3300V級では10.85V、4500V級では13.53Vとなる。したがって、1200V級以上の中耐圧素子、特に3300V級以上の高耐圧素子では、ホール注入電圧が極めて大きくなり、伝導度変調による低抵抗化が期待できない。

【0009】

本発明は、上記事情を考慮してなされたものであり、その目的とするところは、少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有する半導体整流装置を提供することにある。

【課題を解決するための手段】

【0010】

実施の形態の一つの半導体整流装置は、ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備える。

【図面の簡単な説明】

【0011】

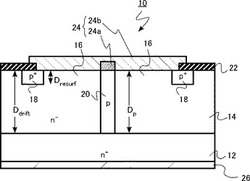

【図1】第1の実施の形態の半導体整流装置の断面図である。

【図2】第1の実施の形態の半導体整流装置の上面図である。

【図3】第1の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図4】第1の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図5】第1の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図6】各種の半導体整流装置の順方向電圧とオン電流密度の関係の説明図である。

【図7】シミュレーションに用いる半導体整流装置の構造断面図である。

【図8】第1の実施の形態の半導体整流装置のシミュレーション結果を示す図である。

【図9】第1の実施の形態の第1の変形例の半導体整流装置の断面図である。

【図10】第1の実施の形態の第2の変形例の半導体整流装置の断面図である。

【図11】第1の実施の形態の第3の変形例の半導体整流装置の上面図である。

【図12】第1の実施の形態の第4の変形例の半導体整流装置の上面図である。

【図13】第1の実施の形態の第5の変形例の半導体整流装置の上面図である。

【図14】第2の実施の形態の半導体整流装置の断面図である。

【図15】第2の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図16】第3の実施の形態の半導体整流装置の断面図である。

【図17】第3の実施の形態の半導体整流装置の上面図である。

【図18】第3の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図19】第3の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図20】第3の実施の形態の第1の変形例の半導体整流装置の断面図である。

【図21】第3の実施の形態の第2の変形例の半導体整流装置の断面図である。

【図22】第3の実施の形態の第3の変形例の半導体整流装置の断面図である。

【図23】第4の実施の形態の半導体整流装置の断面図である。

【図24】第4の実施の形態の変形例の半導体整流装置の断面図である。

【発明を実施するための形態】

【0012】

以下、図面を参照しつつ本発明の実施の形態を説明する。

【0013】

なお、本明細書中、「半導体領域の幅」とは、半導体領域を規定する図形の端部の一点からその半導体領域を挟んで存在する別の端部までの最短距離を意味するものとする。そしてある半導体領域の幅が、例えば15μm以上であるという場合、その半導体領域を規定する図形の50%以上の端部において幅が15μm以上であることを意味するものとする。

【0014】

また、本明細書中、「不純物濃度」とは、半導体中のドナー原子濃度とアクセプタ原子濃度との差分の濃度を意味するものとする。

【0015】

(第1の実施の形態)

本実施の形態の半導体整流装置は、ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面(一方の面)に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面(他方の面)に形成される第2の電極と、を備える。

【0016】

さらに、上記第3の半導体領域が半導体基板と接している。

【0017】

以下、半導体整流装置がMPSであり、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0018】

図1および図2は、それぞれ本実施の形態の半導体整流装置の模式的な断面図および上面図である。図1は図2のAA断面図である。

【0019】

図1に示すように、本実施の形態のMPS10は、例えばn+型の4H−SiC基板(半導体基板)12の上面に、ドリフト層(半導体層)として、4H−SiC基板(以下、単にSiC基板とも称する)12よりも低不純物濃度の、n−型SiC層14が形成されている。SiC基板12およびn−型SiC層14は、例えばN(窒素)を不純物として含有している。

【0020】

n+型のSiC基板12は、不純物濃度が、例えば、5E+17以上1E+19atoms/cm3以下の低抵抗基板である。そして、n−型SiC層14は、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、好ましくは、5E+14atoms/cm3以上1E+16atoms/cm3以下である。そして、厚さ(図1中のDdrift)が、例えば8μm以上である。

【0021】

MPS10は、要求される耐圧が1200V〜7000VのMPS、いわゆる1200V級〜7000V級の中耐圧〜高耐圧MPSである。このように、高い耐圧および十分なオン電流密度を実現するためには、n−型SiC層14は上記不純物濃度と厚さを備えることが望ましい。

【0022】

そして、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0023】

n−型SiC層14の周囲には、p+型のリサーフ(RESURF)領域(第2の半導体領域)18が形成されている。リサーフ領域18の接合深さ(図1中のDresurf)は、例えば0.3〜1.0μm程度である。

【0024】

リサーフ領域18は、不純物として、例えばAl(アルミニウム)またはB(ボロン)を、1E+17atoms/cm3以上1E+18atoms/cm3以下程度含有するSiCである。リサーフ領域18はMPSの耐圧を安定化させるために設けられる。

【0025】

そして、n型不純物領域16に挟まれて、不純物として、例えばAl(アルミニウム)またはB(ボロン)を、n−型SiC層14と同等から一桁高い濃度、すなわち、1E+14atoms/cm3以上5E+17atoms/cm3以下、好ましくは、5E+14atoms/cm3以上1E+17atoms/cm3以下程度含有するp型不純物領域(第3の半導体領域)20が形成されている。また、p型不純物領域の不純物濃度は、SiC基板12の不純物濃度より低い。

【0026】

このp型不純物領域20の接合深さ(図1中のDp)は、リサーフ領域18の接合深さ(図1中のDresurf)よりも深く、p型不純物領域20は、SiC基板12に接している。p型不純物領域20の幅は、例えば、1μm〜20μm程度である。

【0027】

そして、n−型SiC層14の表面は、例えばシリコン酸化膜かるなる絶縁膜22で覆われる。絶縁膜22の開口部のp型不純物領域20上に、p型不純物領域20にオーミック接合するように、例えば、Ti(チタン)/Al(アルミニウム)のオーミック電極24aが形成されている。

【0028】

また、n型不純物領域16にショットキー接合するように、例えば、Ni(ニッケル)のショットキー電極24bが形成されている。ショットキー電極24bは、リサーフ領域18の一部表面にも接するよう形成されている。

【0029】

オーミック電極24aとショットキー電極24bが、第1の電極(アノード電極)24を構成する。また、n+型のSiC基板12の下面には、例えば、Niの第2の電極(カソード電極)26が形成されている。SiC基板12と第2の電極(カソード電極)26はオーミック接合している。

【0030】

平面的には、図2に示すように、n型不純物領域16の中心部に、n型不純物領域16に囲まれ、1個の正方形のp型不純物領域20がある。

【0031】

さらに、n型不純物領域16の周囲に、n型不純物領域16を囲むようにリサーフ領域18が形成されている。このリサーフ領域18に囲まれるn型不純物領域16とp型不純物領域20がMPSの活性領域である。

【0032】

次に、図1、図2に示す本実施の形態の半導体整流装置の製造方法を説明する。図3〜図5は、本実施の形態の半導体整流装置の製造方法を示す断面図である。

【0033】

まず、n+型のSiC基板12の上面に、エピタキシャル成長により、厚さ(図1中のDdrift)が8μm以上のn−型SiC層14を形成する。その後、n−型SiC層14表面に、リソグラフィー法によりマスク材(図示せず)をパターニングする。そして、このマスク材を用いてトレンチ40を形成する(図3)。この時、トレンチ底部がSiC基板12に達するようにエッチングする。

【0034】

次に、エピタキシャル成長により、トレンチ40内をp型のSiCで埋め込み、p型不純物領域20を形成する(図4)。

【0035】

次に、n−型SiC層14表面に、リソグラフィー法によりマスク材をパターニングする。このマスク材をマスクに、AlまたはBをイオン注入する。その後、マスク材を除去し、基板を洗浄した後、1500℃〜2000℃の活性化アニールを行う。このようにして、リサーフ領域18を形成する。

【0036】

その後、例えばシリコン酸化膜からなる絶縁膜(図示せず)を形成し、p型不純物領域20が露出するようにリソグラフィー法およびRIE法を用いてパターニングする。そして、例えば、スパッタ法でTi/Alを堆積した後、パターニングしてオーミック電極24aを形成する。

【0037】

次に、例えばシリコン酸化膜からなる絶縁膜22を形成し、n型不純物領域16、p型不純物領域20およびリサーフ領域18の一部が露出するようにリソグラフィー法およびRIE法を用いてパターニングする(図5)。

【0038】

そして、例えば、スパッタ法でNiを堆積した後、パターニングしてショットキー電極24bを形成する。また、SiC基板12の下面には、例えば、スパッタ法でNiを堆積した後、パターニングして第2の電極(カソード電極)26が形成される。その後、例えば、700℃〜1000℃でシンター工程を行う。

【0039】

以上の製造方法により、図1および図2に示す半導体整流装置が製造可能である。

【0040】

図6は、各種の半導体整流装置の順方向電圧とオン電流密度の関係の説明図である。一点鎖線で示されるSBDのオン電流密度は、矢印aで示される電圧で立ち上がる。この立ち上がり電圧は、アノード電極とn型不純物領域との間のショットキー接合のショットキー障壁高さ(φB)で決定される。

【0041】

一方、点線で示されるPiNダイオードのオン電流密度は、矢印bで示される電圧で立ち上がる。この立ち上がり電圧は、pn接合のビルトインポテンシャル(Vbi)で決定される。

【0042】

ショットキー接合とpn接合の両方を備えるMPSの場合、実線で示されるオン電流密度は、矢印aで示される電圧で立ち上がり、矢印cで示されるホール注入が生ずる電圧、すなわちホール注入電圧に達した時に、伝導度変調が生じ急峻な増加を示す。このホール注入電圧を下げることによって、発熱が抑えられ、順方向のサージ電流が生じたときの素子の破壊率が低減できる。

【0043】

また、両矢印eで示されるMPSとSBDのオン電流密度の差は、MPSに設けられるp型不純物領域の面積の割合が大きくなるほど大きくなる。また、両矢印fで示されるMPSとPiNダイオードのオン電流密度の差は、p型不純物領域の面積の割合が大きくなるほど小さくなる。

【0044】

図7は、電流−電圧特性のシミュレーションに用いる半導体整流装置の構造断面図である。MPSの活性領域のn型不純物領域16とp型不純物領域20のハーフピッチ分を単位構造とする。

【0045】

p型不純物領域20の幅の半分がWp、n型不純物領域16の幅の半分がWdriftである。また、p型不純物領域20の深さがDpで、ドリフト層であるn−型SiC層14の厚さがDdriftである。n+型のSiC基板12の不純物濃度を1E+18atoms/cm3、n−型SiC層14の不純物濃度を4E+15atoms/cm3とした。

【0046】

そして、シミュレーションにより、オーミック電極24aとコンタクト電極24bで構成される第1の電極(アノード電極)24と、第2の電極(カソード電極)26間に電圧を印加し、オン電流密度(正孔電流密度)のp型不純物領域深さ依存性を評価した。p型不純物領域深さDp=n×Ddriftについて、n=0.1〜1.0をパラメータとして評価した。

【0047】

図8は、本実施の形態の半導体整流装置のオン電流密度のp型不純物領域深さ(Dp)依存性のシミュレーション結果を示す図である。図8に示すように、p型不純物領域20を深くする(nを大きくする)ことで、オン電流密度の立ち上がり電圧が低減される、すなわち、ホール注入電圧が低減されることがわかる。

【0048】

中耐圧・高耐圧のMPSにおいてホール注入電圧が高くなるのは、厚膜かつ低濃度になるドリフト層に印加される電圧が大きくなり、p型不純物領域20に電圧が印加されにくいことが主因と考えられる。したがって、図8に示すように、p型不純物領域20を深くすることで、ホール注入電圧を低減できるのは、p型不純物領域20に電圧が印加されやすくなるからであると考えられる。

【0049】

本実施の形態の半導体整流装置によれば、p型不純物領域20を深くすることにより、順方向に電圧を印加した際のホール注入電圧を低減することが可能である。したがって、低い順方向電圧で大電流を流すことが可能となる。このため、発熱が抑えられ、素子の破壊率を下げることができる。よって、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供することができる。

【0050】

また、活性領域中に占める、p型不純物領域20の占有率を上げることなくホール注入電圧を低減することが可能である。したがって、電子(多数キャリア)のみで動作している状態での低いオン抵抗が実現できる。よって、高いオン電流と十分なサージ電流耐性の両立が可能となる。

【0051】

また、本実施の形態では、p型不純物領域20がSiC基板12と接している。したがって、p型不純物領域20の底部とSiC基板12との間に、n−型SiC層14が介在しない。このため、順方向に電圧が印加された際に、n−型SiC層14での電圧降下がない。よって、低いホール注入電圧を実現することが可能である。

【0052】

なお、本実施の形態の半導体整流装置においては、逆方向電圧を印加した際に、特にp型不純物領域20の底部が空乏層によってピンチオフしないと、p型不純物領域20とSiC基板12との間で絶縁破壊が生じ耐圧が劣化する恐れがある。したがって、p型不純物領域20およびSiC基板12の不純物濃度、p型不純物領域20の幅等は、逆方向に電圧を印加した際にp型不純物領域20がピンチオフするように設計することが望ましい。

【0053】

また、同時にp型不純物領域20の不純物濃度は、p型不純物領域20中を低抵抗化し、ホール注入開始後のオン電流が十分大きくなるよう設計することが望ましい。

【0054】

(第1の実施の形態の第1の変形例)

図9は、本実施の形態の第1の変形例の半導体整流装置の模式的な断面図である。p型不純物領域20がSiC基板12と接していない、すなわち、p型不純物領域20の深さDpが、n−型SiC層14の厚さDdriftよりも浅いこと以外は第1の実施の形態と同様である。

【0055】

p型不純物領域20の深さDpが、リサーフ領域18の深さDresurfよりも深い範囲で、ホール注入電圧が効果的に低減する。そして、図8からも明らかなように、p型不純物領域20の深さDpが、n−型SiC層14の厚さDdriftの半分(n=0.5)以上であれば、ホール注入電圧が顕著に低減する。

【0056】

したがって、p型不純物領域20の深さDpは、リサーフ領域18の深さDresurfよりも深いことが必要であり、n−型SiC層14の厚さDdriftの半分(0.5倍)以上であることが望ましい。また、p型不純物領域20の深さDpは、n−型SiC層14の厚さDdriftの0.6倍以上であることがより望ましく、0.7倍以上であることがさらに望ましい。

【0057】

図8から明らかなように、0.6倍(Dp=0.6×Ddrift)以上であれば、3Vという低電圧で十分なオン電流が流れ始めるからである。また、0.7倍(Dp=0.7×Ddrift)以上であれば、p型不純物領域20がSiC基板12と接する場合(Dp=1.0×Ddrift)とほぼ同等のオン電流が流れるからである。

【0058】

本変形例によれば、p型不純物領域20の深さが浅くなるため、トレンチのエッチングや埋め込み等、p型不純物領域20の形成が容易となる。したがって、低コストで高性能な半導体整流装置が実現される。

【0059】

(第1の実施の形態の第2の変形例)

図10は、本実施の形態の第2の変形例の半導体整流装置の模式的な断面図である。p型不純物領域20が、SiC基板12内にまでおよんで形成されること以外は第1の実施の形態と同様である。

【0060】

本変形例でも、第1の実施の形態と同様の効果が実現される。加えて、p型不純物領域20形成のためのトレンチエッチングの際のプロセスマージンが拡大する。したがって、例えば、ウェハ面内での特性バラツキの少ない半導体整流装置の実現が可能である。

【0061】

(第1の実施の形態の第3の変形例)

図11は、本実施の形態の第3の変形例の半導体整流装置の模式的な上面図である。p型不純物領域20が1個ではなく、9個と複数個形成されること以外は第1の実施の形態と同様である。

【0062】

本実施の形態によれば、p型不純物領域20の活性化領域中の占有面積があがるため、MPSの順方向特性において、ホール注入開始後のオン電流量を増大させることが可能となる。

【0063】

(第1の実施の形態の第4の変形例)

図12は、本実施の形態の第4の変形例の半導体整流装置の模式的な上面図である。p型不純物領域20が正方形ではなく、長方形であること以外は第1の実施の形態と同様である。

【0064】

本実施の形態によれば、MPSの順方向特性において、ホール注入開始後のオン電流量を増大させることが可能となる。

【0065】

(第1の実施の形態の第5の変形例)

図13は、本実施の形態の第5の変形例の半導体整流装置の模式的な上面図である。p型不純物領域20が1個ではなく、3個と複数個形成されること以外は第1の実施の形態の第4の変形例と同様である。

【0066】

本実施の形態によれば、MPSの順方向特性において、第1の実施の形態の第4の変形例と比較して、ホール注入開始後のオン電流量をさらに増大させることが可能となる。

【0067】

(第2の実施の形態)

本実施の形態の半導体整流装置は、第3の半導体領域の不純物濃度が、半導体基板側に比べ第1の電極側で高くなっていること以外は第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0068】

図14は、本実施の形態の半導体整流装置の模式的な断面図である。図14に示すように、p型不純物領域(第3の半導体領域)20は、SiC基板(半導体基板)12側の、低不純物濃度の低濃度領域20aと、第1の電極24側の高不純物濃度の高濃度領域20bとで構成される。

【0069】

高濃度領域20bの不純物濃度は、例えば低濃度領域20aの不純物濃度の2倍から4倍程度である。

【0070】

本実施の形態によれば、SiC基板12側の不純物濃度を比較的低く保つことにより、逆方向電圧を印加した際のピンチオフを容易にし、逆方向特性における耐圧を保持しやすくなる。一方、第1の電極24側の不純物濃度を高濃度にすることにより、p型不純物領域20全体の抵抗が低減され、順方向電圧を印加した際のホール注入開始後のオン電流量を増大させることが可能となる。

【0071】

次に、図14に示す本実施の形態の半導体整流装置の製造方法を説明する。図15は、本実施の形態の半導体整流装置の製造方法を示す断面図である。

【0072】

まず、n+型のSiC基板12の上面に、エピタキシャル成長により、厚さが最終的に予定される厚さよりも薄いn−型SiC層14を形成する。その後、n−型SiC層14表面に、リソグラフィー法によりマスク材(図示せず)をパターニングする。そして、このマスク材を用いて第1のトレンチ(図示せず)を形成する。この時、第1のトレンチ底部がSiC基板12に達するようにエッチングする。

【0073】

次に、エピタキシャル成長により、第1のトレンチ内を低濃度のp型のSiCで埋め込み、低濃度領域20aを形成する(図15)。

【0074】

その後、エピタキシャル成長により、厚さが最終的に予定される厚さになるように追加でn−型SiC層14を形成する。その後、n−型SiC層14表面に、リソグラフィー法によりマスク材(図示せず)をパターニングする。そして、このマスク材を用いて第2のトレンチ(図示せず)を形成する。この時、第2のトレンチ底部が低濃度領域20aに達するようにエッチングする。

【0075】

次に、エピタキシャル成長により、第2のトレンチ内を高濃度のp型のSiCで埋め込み、高濃度領域20bを形成する。その後は、第1の実施の形態の製造方法と同様のプロセスを経ることで、図14に示す半導体整流装置が製造可能となる。

【0076】

なお、図14では、p型不純物領域20が2段階に変化する構成を例に説明したが、例えば、3段階以上の多段階に変化する構成であっても、連続的に濃度が変化する構成であっても構わない。

【0077】

(第3の実施の形態)

本実施の形態の半導体整流装置は、第3の半導体領域に挟まれる絶縁層を、さらに備えること以外は第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0078】

図16および図17は、それぞれ本実施の形態の半導体整流装置の模式的な断面図および上面図である。図16は図17のBB断面図である。

【0079】

図に示すように、p型不純物領域(第3の半導体領域)20に挟まれる絶縁層30を備えている。絶縁層30は、例えばシリコン酸化膜である。

【0080】

次に、図16、図17に示す本実施の形態の半導体整流装置の製造方法を説明する。図18、図19は、本実施の形態の半導体整流装置の製造方法を示す断面図である。

【0081】

n−型SiC層14にトレンチを形成する工程までは、第1の実施の形態の製造方法と

同様である。その後、トレンチの内側面に斜めイオン注入により、AlまたはBを導入する。その後、1500℃〜2000℃の活性化アニールを行う。このようにして、p型不純物領域20を形成する(図18)。

【0082】

その後、トレンチ内を、例えば、CVD法によりシリコン酸化膜で埋め込んだ後、例えばCMP法でn−型SiC層14表面のシリコン酸化膜を除去し絶縁層30を形成する(図19)。その後は、第1の実施の形態の製造方法と同様のプロセスを経ることで、図16、17に示す半導体整流装置が製造可能となる。

【0083】

本実施の形態の半導体整流装置によれば、第1の実施の形態と同様の効果を得ることが可能である。さらに、アスペクト比が高くエピタキシャル成長による埋め込みが困難なトレンチであっても、容易にp型不純物領域20を形成することが可能となる。また、エピタキシャル成長のような高価なプロセスが不要なため、プロセスコストを低減することが可能となる。

【0084】

また、幅の狭いp型不純物領域20を形成することができるため、逆方向電圧を印加した際のピンチオフを生じやすくできるため、逆方向の耐圧を保持する設計が容易になる。

【0085】

(第3の実施の形態の第1の変形例)

図20は、本実施の形態の第1の変形例の半導体整流装置の模式的な断面図である。p型不純物領域20がSiC基板12と接していない、すなわち、p型不純物領域20の深さDpが、n−型SiC層14の厚さDdriftよりも浅いこと以外は第3の実施の形態と同様である。

【0086】

本変形例によれば、p型不純物領域20の深さが浅くなるため、p型不純物領域20の形成が容易となる。したがって、低コストで高性能な半導体整流装置が実現される。

【0087】

(第3の実施の形態の第2の変形例)

図21は、本実施の形態の第2の変形例の半導体整流装置の模式的な断面図である。絶縁層30がSiC基板12内にまで形成されること以外は第3の実施の形態と同様である。

【0088】

本変形例でも、第3の実施の形態と同様の効果が実現される。加えて、p型不純物領域20形成のためのトレンチエッチングの際のプロセスマージンが拡大する。したがって、例えば、ウェハ面内での特性バラツキの少ない半導体整流装置の実現が可能である。

【0089】

(第3の実施の形態の第3の変形例)

本変形例の半導体整流装置は、p型不純物領域(第3の半導体領域)20の不純物濃度が、SiC基板(半導体基板)12側に比べ第1の電極側で高くなっていること以外は第3の実施の形態と同様である。

【0090】

図22は、本実施の形態の第3の変形例の半導体整流装置の模式的な断面図である。図22に示すように、p型不純物領域(第3の半導体領域)20は、SiC基板(半導体基板)12側の、低不純物濃度の低濃度領域20aと、第1の電極24側の高不純物濃度の高濃度領域20bとで構成される。

【0091】

本変形例によれば、第3の実施の形態の効果に加え、SiC基板12側の不純物濃度を比較的低く保つことにより、逆方向電圧を印加した際のピンチオフを容易にし、逆方向特性における耐圧を保持しやすくなる。一方、第1の電極24側の不純物濃度を高濃度にすることにより、p型不純物領域20全体の抵抗が低減され、順方向電圧を印加した際のホール注入開始後のオン電流量を増大させることが可能となる。

【0092】

なお、p型不純物領域20の濃度変化は、例えば、連続的に変化する構成であっても3段階以上の多段階に変化する構成であってもかまわない。

【0093】

(第4の実施の形態)

本実施の形態の半導体整流装置は、第3の半導体領域の断面における幅が、第1の電極側から半導体基板側に向けて狭くなること以外は第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0094】

図23は、本実施の形態の半導体整流装置の模式的な断面図である。図23に示すように、p型不純物領域(第3の半導体領域)20は、第1の電極24側からSiC基板(半導体基板)12側に向けて狭くなっている。

【0095】

本実施の形態によれば、SiC基板12側のp型不純物領域20の幅を比較的狭く保つことにより、逆方向電圧を印加した際のピンチオフを容易にし、耐圧を保持しやすくなる。一方、第1の電極24側のp型不純物領域20の幅を広くすることにより、p型不純物領域20全体の抵抗が低減され、順方向電圧を印加した際のホール注入開始後のオン電流を増大させることが可能となる。

【0096】

図23の半導体整流装置は、例えば、トレンチをエッチングする際に、順テーパを付けるエッチングを行うことで製造される。トレンチに順テーパが付いているため、トレンチ内部をエピタキシャル成長により埋め込む際にも埋め込みが容易になるという利点がある。

【0097】

(第4の実施の形態の変形例)

図24は、本実施の形態の変形例の半導体整流装置の模式的な断面図である。p型不純物領域20が、第1の電極24側からSiC基板(半導体基板)12側に向けて、連続的にではなく段階的に狭くなっている狭くなっていること以外は第4の実施の形態と同様である。

【0098】

本変形例によっても、第4の実施の形態と同様の効果を得ることが可能である。本変形例の半導体整流装置は、例えば、トレンチを形成する際に、トレンチエッチングと側壁残しを段階的に繰り返すことによって、形成することが可能である。なお、図24ではトレンチが2段階に狭くなる場合を例に説明したが、2段階に限らず、例えば、3段階以上の多段階に形成するものであってもかまわない。

【0099】

以上、具体例を参照しつつ本発明の実施の形態について説明した。上記、実施の形態はあくまで、例として挙げられているだけであり、本発明を限定するものではない。また、実施の形態の説明においては、半導体整流装置、半導体整流装置の製造方法等で、本発明の説明に直接必要としない部分等については記載を省略したが、必要とされる半導体整流装置、半導体整流装置の製造方法等に関わる要素を適宜選択して用いることができる。

【0100】

例えば、実施の形態においては、第1導電型をn型、第2導電型をp型とする半導体整流装置を例に説明したが、第1導電型をp型、第2導電型をn型とする半導体整流装置であっても構わない。

【0101】

また、実施の形態では、正方形、長方形を基本とするp不純物領域が形成される場合を例に説明したが、形状はその他の形状、例えば、所望の幅を有するストライプ状、格子状、ドット状、六角形、多角形、リング状であっても構わない。

【0102】

また、実施の形態では、p型不純物領域が、n−型SiC層を介してリサーフ領域と離間している場合を例に説明したが、p型不純物領域がリサーフ領域に接していてもかまわない。

【0103】

また、実施の形態では、ワイドバンドギャップ半導体として炭化珪素(SiC)を例に説明したが、その他のワイドバンドギャップ半導体であるダイヤモンド、窒化ガリウム(GaN)等を適用することも可能である。

【0104】

また、第1の電極はNiやTi/Alを材料とする場合を例に説明したが、MPSとして要求されるショットキー障壁高さ(φB)やコンタクト抵抗を得るために、その他の材料、例えば、Mo、W、Pt、Ta、TaNの単体、これらの合金、シリサイド、カーバイド等を用いることも可能である。

【0105】

また、実施の形態では、第1の電極とp型不純物領域がオーミック接合する場合を例に説明した。ホール注入電圧を下げオン電流を高くする観点からは、オーミック接合であることが望ましいが、完全なオーミック性が確保されず、非オーミック接合となることも許容される。

【0106】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体整流装置が、本発明の範囲に包含される。本発明の範囲は、特許請求の範囲およびその均等物の範囲によって定義されるものである。

【符号の説明】

【0107】

10 MPS

12 SiC基板(半導体基板)

14 n−型SiC層(半導体層)

16 n型不純物領域(第1の半導体領域)

18 リサーフ領域(第2の半導体領域)

20 p型不純物領域(第3の半導体領域)

22 絶縁膜

24 第1の電極

26 第2の電極

30 絶縁層

【技術分野】

【0001】

本発明の実施の形態は、半導体整流装置に関する。

【背景技術】

【0002】

入力される電流を整流して出力する半導体整流装置として、pn接合を有するPiNダイオードと、半導体層と金属との仕事関数の差によるキャリアのポテンシャル障壁を有するショットキーバリアダイオード(SBD)がある。そして、ショットキーバリアダイオードにおいて、半導体層(例えばn型)/金属界面にかかる電界を緩和することを目的に、半導体層表面に半導体層とは異なる導電型の不純物領域(例えばp型)を配置したJBS(Junction Barrier Schottochy barrier diode)がある。さらに、JBSの不純物領域(例えばp型)と金属とのコンタクトをオーミック接合またはオーミック接合に近付け、不純物領域と半導体層とのビルトインポテンシャル(Vbi)を超える電圧がかかった際に少数キャリア注入を起こし、伝導度変調により抵抗を下げる機能を持たせたMPS(Merged PiN−diode Schottky−diode)がある。

【0003】

一方、次世代のパワー半導体デバイス材料として例えば炭化珪素(以下、SiCとも記述する)を代表とするワイドバンドギャップ半導体が期待されている。ワイドバンドギャップ半導体はシリコン(Si)に対して広いバンドギャップを有し、Siよりも高い破壊電界強度及び高い熱伝導率を備える。この特性を活用すれば、低損失かつ高温動作可能なパワー半導体デバイスを実現することができる。

【0004】

MPSでは、伝導度変調を起こす電圧を下げることにより、順方向特性の低抵抗化が実現されるとともに、順方向のサージ電流が流れ込んだ際に、低い順方向電圧で大量の電流を吐き出すことが可能になる。定常状態よりも大きな電流が流れ込んだ際に、その電流は電流×電圧=パワーの式のもと、発熱による結晶破壊、電極などの接合破壊の原因となる。しかし、低い順方向電圧で大電流を流すことが可能になれば、発熱が抑えられ素子の破壊率を下げることができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許公開公報2007/0278609

【発明の概要】

【発明が解決しようとする課題】

【0006】

もっとも、要求される耐圧が1200V(以下、1200V級とも称する)以上のワイドバンドギャップ半導体を用いたMPSでは、従来の構造を用いても、少数キャリアが注入され伝導度変調を起こす電圧(以下、少数キャリアがホールの場合はホール注入電圧と称する)が、十分に下げられないことが、発明者らによって明らかになった。

【0007】

例えば、従来のSiのMPSでは、SiのVbi=0.8〜1.0Vに対し、伝導度変調を起こす電圧が1〜1.5V、SiCのMPSでは、SiCのVbi=2.5〜3.0Vに対し伝導度変調を起こす電圧が、600V級耐圧の素子で3.2Vと、Vbiに対して+1V以下の電圧を印加することで少数キャリアが注入されていた(SiCのMPS:p型不純物領域幅2um、n型ショットキー領域幅0.8um、125℃の場合)。

【0008】

MPSにおいて、p型不純物領域は電子電流(多数キャリア)を流す際にデッドスペースとなるので、p型不純物領域幅を狭めるのが一般的である。そこで、例えばp型不純物領域幅を1um、n型不純物領域幅(n型ショットキー領域幅)を1umとし、125℃でのMPSのホール注入電圧を計算すると600V級で4.4V、1200V級で6.9V、3300V級では10.85V、4500V級では13.53Vとなる。したがって、1200V級以上の中耐圧素子、特に3300V級以上の高耐圧素子では、ホール注入電圧が極めて大きくなり、伝導度変調による低抵抗化が期待できない。

【0009】

本発明は、上記事情を考慮してなされたものであり、その目的とするところは、少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有する半導体整流装置を提供することにある。

【課題を解決するための手段】

【0010】

実施の形態の一つの半導体整流装置は、ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備える。

【図面の簡単な説明】

【0011】

【図1】第1の実施の形態の半導体整流装置の断面図である。

【図2】第1の実施の形態の半導体整流装置の上面図である。

【図3】第1の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図4】第1の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図5】第1の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図6】各種の半導体整流装置の順方向電圧とオン電流密度の関係の説明図である。

【図7】シミュレーションに用いる半導体整流装置の構造断面図である。

【図8】第1の実施の形態の半導体整流装置のシミュレーション結果を示す図である。

【図9】第1の実施の形態の第1の変形例の半導体整流装置の断面図である。

【図10】第1の実施の形態の第2の変形例の半導体整流装置の断面図である。

【図11】第1の実施の形態の第3の変形例の半導体整流装置の上面図である。

【図12】第1の実施の形態の第4の変形例の半導体整流装置の上面図である。

【図13】第1の実施の形態の第5の変形例の半導体整流装置の上面図である。

【図14】第2の実施の形態の半導体整流装置の断面図である。

【図15】第2の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図16】第3の実施の形態の半導体整流装置の断面図である。

【図17】第3の実施の形態の半導体整流装置の上面図である。

【図18】第3の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図19】第3の実施の形態の半導体整流装置の製造方法を示す断面図である。

【図20】第3の実施の形態の第1の変形例の半導体整流装置の断面図である。

【図21】第3の実施の形態の第2の変形例の半導体整流装置の断面図である。

【図22】第3の実施の形態の第3の変形例の半導体整流装置の断面図である。

【図23】第4の実施の形態の半導体整流装置の断面図である。

【図24】第4の実施の形態の変形例の半導体整流装置の断面図である。

【発明を実施するための形態】

【0012】

以下、図面を参照しつつ本発明の実施の形態を説明する。

【0013】

なお、本明細書中、「半導体領域の幅」とは、半導体領域を規定する図形の端部の一点からその半導体領域を挟んで存在する別の端部までの最短距離を意味するものとする。そしてある半導体領域の幅が、例えば15μm以上であるという場合、その半導体領域を規定する図形の50%以上の端部において幅が15μm以上であることを意味するものとする。

【0014】

また、本明細書中、「不純物濃度」とは、半導体中のドナー原子濃度とアクセプタ原子濃度との差分の濃度を意味するものとする。

【0015】

(第1の実施の形態)

本実施の形態の半導体整流装置は、ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面(一方の面)に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面(他方の面)に形成される第2の電極と、を備える。

【0016】

さらに、上記第3の半導体領域が半導体基板と接している。

【0017】

以下、半導体整流装置がMPSであり、ワイドバンドギャップ半導体が炭化珪素(以下、SiCとも記述)であり、第1導電型がn型、第2導電型がp型であるMPSを例に説明する。

【0018】

図1および図2は、それぞれ本実施の形態の半導体整流装置の模式的な断面図および上面図である。図1は図2のAA断面図である。

【0019】

図1に示すように、本実施の形態のMPS10は、例えばn+型の4H−SiC基板(半導体基板)12の上面に、ドリフト層(半導体層)として、4H−SiC基板(以下、単にSiC基板とも称する)12よりも低不純物濃度の、n−型SiC層14が形成されている。SiC基板12およびn−型SiC層14は、例えばN(窒素)を不純物として含有している。

【0020】

n+型のSiC基板12は、不純物濃度が、例えば、5E+17以上1E+19atoms/cm3以下の低抵抗基板である。そして、n−型SiC層14は、不純物濃度が1E+14atoms/cm3以上5E+16atoms/cm3以下、好ましくは、5E+14atoms/cm3以上1E+16atoms/cm3以下である。そして、厚さ(図1中のDdrift)が、例えば8μm以上である。

【0021】

MPS10は、要求される耐圧が1200V〜7000VのMPS、いわゆる1200V級〜7000V級の中耐圧〜高耐圧MPSである。このように、高い耐圧および十分なオン電流密度を実現するためには、n−型SiC層14は上記不純物濃度と厚さを備えることが望ましい。

【0022】

そして、n−型SiC層14の表面に、n型不純物領域(n型ショットキー領域:第1の半導体領域)16が存在する。n型不純物領域16はn−型SiC層14の上部に相当する。

【0023】

n−型SiC層14の周囲には、p+型のリサーフ(RESURF)領域(第2の半導体領域)18が形成されている。リサーフ領域18の接合深さ(図1中のDresurf)は、例えば0.3〜1.0μm程度である。

【0024】

リサーフ領域18は、不純物として、例えばAl(アルミニウム)またはB(ボロン)を、1E+17atoms/cm3以上1E+18atoms/cm3以下程度含有するSiCである。リサーフ領域18はMPSの耐圧を安定化させるために設けられる。

【0025】

そして、n型不純物領域16に挟まれて、不純物として、例えばAl(アルミニウム)またはB(ボロン)を、n−型SiC層14と同等から一桁高い濃度、すなわち、1E+14atoms/cm3以上5E+17atoms/cm3以下、好ましくは、5E+14atoms/cm3以上1E+17atoms/cm3以下程度含有するp型不純物領域(第3の半導体領域)20が形成されている。また、p型不純物領域の不純物濃度は、SiC基板12の不純物濃度より低い。

【0026】

このp型不純物領域20の接合深さ(図1中のDp)は、リサーフ領域18の接合深さ(図1中のDresurf)よりも深く、p型不純物領域20は、SiC基板12に接している。p型不純物領域20の幅は、例えば、1μm〜20μm程度である。

【0027】

そして、n−型SiC層14の表面は、例えばシリコン酸化膜かるなる絶縁膜22で覆われる。絶縁膜22の開口部のp型不純物領域20上に、p型不純物領域20にオーミック接合するように、例えば、Ti(チタン)/Al(アルミニウム)のオーミック電極24aが形成されている。

【0028】

また、n型不純物領域16にショットキー接合するように、例えば、Ni(ニッケル)のショットキー電極24bが形成されている。ショットキー電極24bは、リサーフ領域18の一部表面にも接するよう形成されている。

【0029】

オーミック電極24aとショットキー電極24bが、第1の電極(アノード電極)24を構成する。また、n+型のSiC基板12の下面には、例えば、Niの第2の電極(カソード電極)26が形成されている。SiC基板12と第2の電極(カソード電極)26はオーミック接合している。

【0030】

平面的には、図2に示すように、n型不純物領域16の中心部に、n型不純物領域16に囲まれ、1個の正方形のp型不純物領域20がある。

【0031】

さらに、n型不純物領域16の周囲に、n型不純物領域16を囲むようにリサーフ領域18が形成されている。このリサーフ領域18に囲まれるn型不純物領域16とp型不純物領域20がMPSの活性領域である。

【0032】

次に、図1、図2に示す本実施の形態の半導体整流装置の製造方法を説明する。図3〜図5は、本実施の形態の半導体整流装置の製造方法を示す断面図である。

【0033】

まず、n+型のSiC基板12の上面に、エピタキシャル成長により、厚さ(図1中のDdrift)が8μm以上のn−型SiC層14を形成する。その後、n−型SiC層14表面に、リソグラフィー法によりマスク材(図示せず)をパターニングする。そして、このマスク材を用いてトレンチ40を形成する(図3)。この時、トレンチ底部がSiC基板12に達するようにエッチングする。

【0034】

次に、エピタキシャル成長により、トレンチ40内をp型のSiCで埋め込み、p型不純物領域20を形成する(図4)。

【0035】

次に、n−型SiC層14表面に、リソグラフィー法によりマスク材をパターニングする。このマスク材をマスクに、AlまたはBをイオン注入する。その後、マスク材を除去し、基板を洗浄した後、1500℃〜2000℃の活性化アニールを行う。このようにして、リサーフ領域18を形成する。

【0036】

その後、例えばシリコン酸化膜からなる絶縁膜(図示せず)を形成し、p型不純物領域20が露出するようにリソグラフィー法およびRIE法を用いてパターニングする。そして、例えば、スパッタ法でTi/Alを堆積した後、パターニングしてオーミック電極24aを形成する。

【0037】

次に、例えばシリコン酸化膜からなる絶縁膜22を形成し、n型不純物領域16、p型不純物領域20およびリサーフ領域18の一部が露出するようにリソグラフィー法およびRIE法を用いてパターニングする(図5)。

【0038】

そして、例えば、スパッタ法でNiを堆積した後、パターニングしてショットキー電極24bを形成する。また、SiC基板12の下面には、例えば、スパッタ法でNiを堆積した後、パターニングして第2の電極(カソード電極)26が形成される。その後、例えば、700℃〜1000℃でシンター工程を行う。

【0039】

以上の製造方法により、図1および図2に示す半導体整流装置が製造可能である。

【0040】

図6は、各種の半導体整流装置の順方向電圧とオン電流密度の関係の説明図である。一点鎖線で示されるSBDのオン電流密度は、矢印aで示される電圧で立ち上がる。この立ち上がり電圧は、アノード電極とn型不純物領域との間のショットキー接合のショットキー障壁高さ(φB)で決定される。

【0041】

一方、点線で示されるPiNダイオードのオン電流密度は、矢印bで示される電圧で立ち上がる。この立ち上がり電圧は、pn接合のビルトインポテンシャル(Vbi)で決定される。

【0042】

ショットキー接合とpn接合の両方を備えるMPSの場合、実線で示されるオン電流密度は、矢印aで示される電圧で立ち上がり、矢印cで示されるホール注入が生ずる電圧、すなわちホール注入電圧に達した時に、伝導度変調が生じ急峻な増加を示す。このホール注入電圧を下げることによって、発熱が抑えられ、順方向のサージ電流が生じたときの素子の破壊率が低減できる。

【0043】

また、両矢印eで示されるMPSとSBDのオン電流密度の差は、MPSに設けられるp型不純物領域の面積の割合が大きくなるほど大きくなる。また、両矢印fで示されるMPSとPiNダイオードのオン電流密度の差は、p型不純物領域の面積の割合が大きくなるほど小さくなる。

【0044】

図7は、電流−電圧特性のシミュレーションに用いる半導体整流装置の構造断面図である。MPSの活性領域のn型不純物領域16とp型不純物領域20のハーフピッチ分を単位構造とする。

【0045】

p型不純物領域20の幅の半分がWp、n型不純物領域16の幅の半分がWdriftである。また、p型不純物領域20の深さがDpで、ドリフト層であるn−型SiC層14の厚さがDdriftである。n+型のSiC基板12の不純物濃度を1E+18atoms/cm3、n−型SiC層14の不純物濃度を4E+15atoms/cm3とした。

【0046】

そして、シミュレーションにより、オーミック電極24aとコンタクト電極24bで構成される第1の電極(アノード電極)24と、第2の電極(カソード電極)26間に電圧を印加し、オン電流密度(正孔電流密度)のp型不純物領域深さ依存性を評価した。p型不純物領域深さDp=n×Ddriftについて、n=0.1〜1.0をパラメータとして評価した。

【0047】

図8は、本実施の形態の半導体整流装置のオン電流密度のp型不純物領域深さ(Dp)依存性のシミュレーション結果を示す図である。図8に示すように、p型不純物領域20を深くする(nを大きくする)ことで、オン電流密度の立ち上がり電圧が低減される、すなわち、ホール注入電圧が低減されることがわかる。

【0048】

中耐圧・高耐圧のMPSにおいてホール注入電圧が高くなるのは、厚膜かつ低濃度になるドリフト層に印加される電圧が大きくなり、p型不純物領域20に電圧が印加されにくいことが主因と考えられる。したがって、図8に示すように、p型不純物領域20を深くすることで、ホール注入電圧を低減できるのは、p型不純物領域20に電圧が印加されやすくなるからであると考えられる。

【0049】

本実施の形態の半導体整流装置によれば、p型不純物領域20を深くすることにより、順方向に電圧を印加した際のホール注入電圧を低減することが可能である。したがって、低い順方向電圧で大電流を流すことが可能となる。このため、発熱が抑えられ、素子の破壊率を下げることができる。よって、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供することができる。

【0050】

また、活性領域中に占める、p型不純物領域20の占有率を上げることなくホール注入電圧を低減することが可能である。したがって、電子(多数キャリア)のみで動作している状態での低いオン抵抗が実現できる。よって、高いオン電流と十分なサージ電流耐性の両立が可能となる。

【0051】

また、本実施の形態では、p型不純物領域20がSiC基板12と接している。したがって、p型不純物領域20の底部とSiC基板12との間に、n−型SiC層14が介在しない。このため、順方向に電圧が印加された際に、n−型SiC層14での電圧降下がない。よって、低いホール注入電圧を実現することが可能である。

【0052】

なお、本実施の形態の半導体整流装置においては、逆方向電圧を印加した際に、特にp型不純物領域20の底部が空乏層によってピンチオフしないと、p型不純物領域20とSiC基板12との間で絶縁破壊が生じ耐圧が劣化する恐れがある。したがって、p型不純物領域20およびSiC基板12の不純物濃度、p型不純物領域20の幅等は、逆方向に電圧を印加した際にp型不純物領域20がピンチオフするように設計することが望ましい。

【0053】

また、同時にp型不純物領域20の不純物濃度は、p型不純物領域20中を低抵抗化し、ホール注入開始後のオン電流が十分大きくなるよう設計することが望ましい。

【0054】

(第1の実施の形態の第1の変形例)

図9は、本実施の形態の第1の変形例の半導体整流装置の模式的な断面図である。p型不純物領域20がSiC基板12と接していない、すなわち、p型不純物領域20の深さDpが、n−型SiC層14の厚さDdriftよりも浅いこと以外は第1の実施の形態と同様である。

【0055】

p型不純物領域20の深さDpが、リサーフ領域18の深さDresurfよりも深い範囲で、ホール注入電圧が効果的に低減する。そして、図8からも明らかなように、p型不純物領域20の深さDpが、n−型SiC層14の厚さDdriftの半分(n=0.5)以上であれば、ホール注入電圧が顕著に低減する。

【0056】

したがって、p型不純物領域20の深さDpは、リサーフ領域18の深さDresurfよりも深いことが必要であり、n−型SiC層14の厚さDdriftの半分(0.5倍)以上であることが望ましい。また、p型不純物領域20の深さDpは、n−型SiC層14の厚さDdriftの0.6倍以上であることがより望ましく、0.7倍以上であることがさらに望ましい。

【0057】

図8から明らかなように、0.6倍(Dp=0.6×Ddrift)以上であれば、3Vという低電圧で十分なオン電流が流れ始めるからである。また、0.7倍(Dp=0.7×Ddrift)以上であれば、p型不純物領域20がSiC基板12と接する場合(Dp=1.0×Ddrift)とほぼ同等のオン電流が流れるからである。

【0058】

本変形例によれば、p型不純物領域20の深さが浅くなるため、トレンチのエッチングや埋め込み等、p型不純物領域20の形成が容易となる。したがって、低コストで高性能な半導体整流装置が実現される。

【0059】

(第1の実施の形態の第2の変形例)

図10は、本実施の形態の第2の変形例の半導体整流装置の模式的な断面図である。p型不純物領域20が、SiC基板12内にまでおよんで形成されること以外は第1の実施の形態と同様である。

【0060】

本変形例でも、第1の実施の形態と同様の効果が実現される。加えて、p型不純物領域20形成のためのトレンチエッチングの際のプロセスマージンが拡大する。したがって、例えば、ウェハ面内での特性バラツキの少ない半導体整流装置の実現が可能である。

【0061】

(第1の実施の形態の第3の変形例)

図11は、本実施の形態の第3の変形例の半導体整流装置の模式的な上面図である。p型不純物領域20が1個ではなく、9個と複数個形成されること以外は第1の実施の形態と同様である。

【0062】

本実施の形態によれば、p型不純物領域20の活性化領域中の占有面積があがるため、MPSの順方向特性において、ホール注入開始後のオン電流量を増大させることが可能となる。

【0063】

(第1の実施の形態の第4の変形例)

図12は、本実施の形態の第4の変形例の半導体整流装置の模式的な上面図である。p型不純物領域20が正方形ではなく、長方形であること以外は第1の実施の形態と同様である。

【0064】

本実施の形態によれば、MPSの順方向特性において、ホール注入開始後のオン電流量を増大させることが可能となる。

【0065】

(第1の実施の形態の第5の変形例)

図13は、本実施の形態の第5の変形例の半導体整流装置の模式的な上面図である。p型不純物領域20が1個ではなく、3個と複数個形成されること以外は第1の実施の形態の第4の変形例と同様である。

【0066】

本実施の形態によれば、MPSの順方向特性において、第1の実施の形態の第4の変形例と比較して、ホール注入開始後のオン電流量をさらに増大させることが可能となる。

【0067】

(第2の実施の形態)

本実施の形態の半導体整流装置は、第3の半導体領域の不純物濃度が、半導体基板側に比べ第1の電極側で高くなっていること以外は第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0068】

図14は、本実施の形態の半導体整流装置の模式的な断面図である。図14に示すように、p型不純物領域(第3の半導体領域)20は、SiC基板(半導体基板)12側の、低不純物濃度の低濃度領域20aと、第1の電極24側の高不純物濃度の高濃度領域20bとで構成される。

【0069】

高濃度領域20bの不純物濃度は、例えば低濃度領域20aの不純物濃度の2倍から4倍程度である。

【0070】

本実施の形態によれば、SiC基板12側の不純物濃度を比較的低く保つことにより、逆方向電圧を印加した際のピンチオフを容易にし、逆方向特性における耐圧を保持しやすくなる。一方、第1の電極24側の不純物濃度を高濃度にすることにより、p型不純物領域20全体の抵抗が低減され、順方向電圧を印加した際のホール注入開始後のオン電流量を増大させることが可能となる。

【0071】

次に、図14に示す本実施の形態の半導体整流装置の製造方法を説明する。図15は、本実施の形態の半導体整流装置の製造方法を示す断面図である。

【0072】

まず、n+型のSiC基板12の上面に、エピタキシャル成長により、厚さが最終的に予定される厚さよりも薄いn−型SiC層14を形成する。その後、n−型SiC層14表面に、リソグラフィー法によりマスク材(図示せず)をパターニングする。そして、このマスク材を用いて第1のトレンチ(図示せず)を形成する。この時、第1のトレンチ底部がSiC基板12に達するようにエッチングする。

【0073】

次に、エピタキシャル成長により、第1のトレンチ内を低濃度のp型のSiCで埋め込み、低濃度領域20aを形成する(図15)。

【0074】

その後、エピタキシャル成長により、厚さが最終的に予定される厚さになるように追加でn−型SiC層14を形成する。その後、n−型SiC層14表面に、リソグラフィー法によりマスク材(図示せず)をパターニングする。そして、このマスク材を用いて第2のトレンチ(図示せず)を形成する。この時、第2のトレンチ底部が低濃度領域20aに達するようにエッチングする。

【0075】

次に、エピタキシャル成長により、第2のトレンチ内を高濃度のp型のSiCで埋め込み、高濃度領域20bを形成する。その後は、第1の実施の形態の製造方法と同様のプロセスを経ることで、図14に示す半導体整流装置が製造可能となる。

【0076】

なお、図14では、p型不純物領域20が2段階に変化する構成を例に説明したが、例えば、3段階以上の多段階に変化する構成であっても、連続的に濃度が変化する構成であっても構わない。

【0077】

(第3の実施の形態)

本実施の形態の半導体整流装置は、第3の半導体領域に挟まれる絶縁層を、さらに備えること以外は第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0078】

図16および図17は、それぞれ本実施の形態の半導体整流装置の模式的な断面図および上面図である。図16は図17のBB断面図である。

【0079】

図に示すように、p型不純物領域(第3の半導体領域)20に挟まれる絶縁層30を備えている。絶縁層30は、例えばシリコン酸化膜である。

【0080】

次に、図16、図17に示す本実施の形態の半導体整流装置の製造方法を説明する。図18、図19は、本実施の形態の半導体整流装置の製造方法を示す断面図である。

【0081】

n−型SiC層14にトレンチを形成する工程までは、第1の実施の形態の製造方法と

同様である。その後、トレンチの内側面に斜めイオン注入により、AlまたはBを導入する。その後、1500℃〜2000℃の活性化アニールを行う。このようにして、p型不純物領域20を形成する(図18)。

【0082】

その後、トレンチ内を、例えば、CVD法によりシリコン酸化膜で埋め込んだ後、例えばCMP法でn−型SiC層14表面のシリコン酸化膜を除去し絶縁層30を形成する(図19)。その後は、第1の実施の形態の製造方法と同様のプロセスを経ることで、図16、17に示す半導体整流装置が製造可能となる。

【0083】

本実施の形態の半導体整流装置によれば、第1の実施の形態と同様の効果を得ることが可能である。さらに、アスペクト比が高くエピタキシャル成長による埋め込みが困難なトレンチであっても、容易にp型不純物領域20を形成することが可能となる。また、エピタキシャル成長のような高価なプロセスが不要なため、プロセスコストを低減することが可能となる。

【0084】

また、幅の狭いp型不純物領域20を形成することができるため、逆方向電圧を印加した際のピンチオフを生じやすくできるため、逆方向の耐圧を保持する設計が容易になる。

【0085】

(第3の実施の形態の第1の変形例)

図20は、本実施の形態の第1の変形例の半導体整流装置の模式的な断面図である。p型不純物領域20がSiC基板12と接していない、すなわち、p型不純物領域20の深さDpが、n−型SiC層14の厚さDdriftよりも浅いこと以外は第3の実施の形態と同様である。

【0086】

本変形例によれば、p型不純物領域20の深さが浅くなるため、p型不純物領域20の形成が容易となる。したがって、低コストで高性能な半導体整流装置が実現される。

【0087】

(第3の実施の形態の第2の変形例)

図21は、本実施の形態の第2の変形例の半導体整流装置の模式的な断面図である。絶縁層30がSiC基板12内にまで形成されること以外は第3の実施の形態と同様である。

【0088】

本変形例でも、第3の実施の形態と同様の効果が実現される。加えて、p型不純物領域20形成のためのトレンチエッチングの際のプロセスマージンが拡大する。したがって、例えば、ウェハ面内での特性バラツキの少ない半導体整流装置の実現が可能である。

【0089】

(第3の実施の形態の第3の変形例)

本変形例の半導体整流装置は、p型不純物領域(第3の半導体領域)20の不純物濃度が、SiC基板(半導体基板)12側に比べ第1の電極側で高くなっていること以外は第3の実施の形態と同様である。

【0090】

図22は、本実施の形態の第3の変形例の半導体整流装置の模式的な断面図である。図22に示すように、p型不純物領域(第3の半導体領域)20は、SiC基板(半導体基板)12側の、低不純物濃度の低濃度領域20aと、第1の電極24側の高不純物濃度の高濃度領域20bとで構成される。

【0091】

本変形例によれば、第3の実施の形態の効果に加え、SiC基板12側の不純物濃度を比較的低く保つことにより、逆方向電圧を印加した際のピンチオフを容易にし、逆方向特性における耐圧を保持しやすくなる。一方、第1の電極24側の不純物濃度を高濃度にすることにより、p型不純物領域20全体の抵抗が低減され、順方向電圧を印加した際のホール注入開始後のオン電流量を増大させることが可能となる。

【0092】

なお、p型不純物領域20の濃度変化は、例えば、連続的に変化する構成であっても3段階以上の多段階に変化する構成であってもかまわない。

【0093】

(第4の実施の形態)

本実施の形態の半導体整流装置は、第3の半導体領域の断面における幅が、第1の電極側から半導体基板側に向けて狭くなること以外は第1の実施の形態と同様である。したがって、第1の実施の形態と重複する内容については記載を省略する。

【0094】

図23は、本実施の形態の半導体整流装置の模式的な断面図である。図23に示すように、p型不純物領域(第3の半導体領域)20は、第1の電極24側からSiC基板(半導体基板)12側に向けて狭くなっている。

【0095】

本実施の形態によれば、SiC基板12側のp型不純物領域20の幅を比較的狭く保つことにより、逆方向電圧を印加した際のピンチオフを容易にし、耐圧を保持しやすくなる。一方、第1の電極24側のp型不純物領域20の幅を広くすることにより、p型不純物領域20全体の抵抗が低減され、順方向電圧を印加した際のホール注入開始後のオン電流を増大させることが可能となる。

【0096】

図23の半導体整流装置は、例えば、トレンチをエッチングする際に、順テーパを付けるエッチングを行うことで製造される。トレンチに順テーパが付いているため、トレンチ内部をエピタキシャル成長により埋め込む際にも埋め込みが容易になるという利点がある。

【0097】

(第4の実施の形態の変形例)

図24は、本実施の形態の変形例の半導体整流装置の模式的な断面図である。p型不純物領域20が、第1の電極24側からSiC基板(半導体基板)12側に向けて、連続的にではなく段階的に狭くなっている狭くなっていること以外は第4の実施の形態と同様である。

【0098】

本変形例によっても、第4の実施の形態と同様の効果を得ることが可能である。本変形例の半導体整流装置は、例えば、トレンチを形成する際に、トレンチエッチングと側壁残しを段階的に繰り返すことによって、形成することが可能である。なお、図24ではトレンチが2段階に狭くなる場合を例に説明したが、2段階に限らず、例えば、3段階以上の多段階に形成するものであってもかまわない。

【0099】

以上、具体例を参照しつつ本発明の実施の形態について説明した。上記、実施の形態はあくまで、例として挙げられているだけであり、本発明を限定するものではない。また、実施の形態の説明においては、半導体整流装置、半導体整流装置の製造方法等で、本発明の説明に直接必要としない部分等については記載を省略したが、必要とされる半導体整流装置、半導体整流装置の製造方法等に関わる要素を適宜選択して用いることができる。

【0100】

例えば、実施の形態においては、第1導電型をn型、第2導電型をp型とする半導体整流装置を例に説明したが、第1導電型をp型、第2導電型をn型とする半導体整流装置であっても構わない。

【0101】

また、実施の形態では、正方形、長方形を基本とするp不純物領域が形成される場合を例に説明したが、形状はその他の形状、例えば、所望の幅を有するストライプ状、格子状、ドット状、六角形、多角形、リング状であっても構わない。

【0102】

また、実施の形態では、p型不純物領域が、n−型SiC層を介してリサーフ領域と離間している場合を例に説明したが、p型不純物領域がリサーフ領域に接していてもかまわない。

【0103】

また、実施の形態では、ワイドバンドギャップ半導体として炭化珪素(SiC)を例に説明したが、その他のワイドバンドギャップ半導体であるダイヤモンド、窒化ガリウム(GaN)等を適用することも可能である。

【0104】

また、第1の電極はNiやTi/Alを材料とする場合を例に説明したが、MPSとして要求されるショットキー障壁高さ(φB)やコンタクト抵抗を得るために、その他の材料、例えば、Mo、W、Pt、Ta、TaNの単体、これらの合金、シリサイド、カーバイド等を用いることも可能である。

【0105】

また、実施の形態では、第1の電極とp型不純物領域がオーミック接合する場合を例に説明した。ホール注入電圧を下げオン電流を高くする観点からは、オーミック接合であることが望ましいが、完全なオーミック性が確保されず、非オーミック接合となることも許容される。

【0106】

その他、本発明の要素を具備し、当業者が適宜設計変更しうる全ての半導体整流装置が、本発明の範囲に包含される。本発明の範囲は、特許請求の範囲およびその均等物の範囲によって定義されるものである。

【符号の説明】

【0107】

10 MPS

12 SiC基板(半導体基板)

14 n−型SiC層(半導体層)

16 n型不純物領域(第1の半導体領域)

18 リサーフ領域(第2の半導体領域)

20 p型不純物領域(第3の半導体領域)

22 絶縁膜

24 第1の電極

26 第2の電極

30 絶縁層

【特許請求の範囲】

【請求項1】

ワイドギャップ半導体の第1導電型の半導体基板と、

前記半導体基板の上面に形成され、前記半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、

前記半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、

前記第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、

前記第1の半導体領域に挟まれ、接合深さが前記第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、

前記第1、第2および第3の半導体領域上に形成される第1の電極と、

前記半導体基板の下面に形成される第2の電極と、

を備えることを特徴とする半導体整流装置。

【請求項2】

前記第3の半導体領域の接合深さが、前記半導体層の厚さの半分以上であることを特徴とする請求項1記載の半導体整流装置。

【請求項3】

前記第3の半導体領域の不純物濃度が、前記半導体基板の不純物濃度より低く、前記半導体層よりも高いことを特徴とする請求項1または請求項2記載の半導体整流装置。

【請求項4】

前記第3の半導体領域が前記半導体基板と接することを特徴とする請求項1ないし請求項3いずれか一項記載の半導体整流装置。

【請求項5】

前記第3の半導体領域の不純物濃度が、前記半導体基板側に比べ前記第1の電極側で高くなっていることを特徴とする請求項1ないし請求項4いずれか一項記載の半導体整流装置。

【請求項6】

前記第3の半導体領域に挟まれる絶縁層を、さらに備えることを特徴とする請求項1ないし請求項5いずれか一項記載の半導体整流装置。

【請求項7】

前記第3の半導体領域の幅が、前記第1の電極側から前記半導体基板側に向けて狭くなることを特徴とする請求項1ないし請求項6いずれか一項記載の半導体整流装置。

【請求項8】

前記第1の電極と前記第1の半導体領域とはショットキー接合しており、

前記第1の電極と前記第3の半導体領域とはオーミック接合していることを特徴とする請求項1ないし請求項7いずれか一項記載の半導体整流装置。

【請求項9】

前記ワイドバンドギャップ半導体が炭化珪素(SiC)であることを特徴とする請求項1ないし請求項8いずれか一項記載の半導体整流装置。

【請求項1】

ワイドギャップ半導体の第1導電型の半導体基板と、

前記半導体基板の上面に形成され、前記半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、

前記半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、

前記第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、

前記第1の半導体領域に挟まれ、接合深さが前記第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、

前記第1、第2および第3の半導体領域上に形成される第1の電極と、

前記半導体基板の下面に形成される第2の電極と、

を備えることを特徴とする半導体整流装置。

【請求項2】

前記第3の半導体領域の接合深さが、前記半導体層の厚さの半分以上であることを特徴とする請求項1記載の半導体整流装置。

【請求項3】

前記第3の半導体領域の不純物濃度が、前記半導体基板の不純物濃度より低く、前記半導体層よりも高いことを特徴とする請求項1または請求項2記載の半導体整流装置。

【請求項4】

前記第3の半導体領域が前記半導体基板と接することを特徴とする請求項1ないし請求項3いずれか一項記載の半導体整流装置。

【請求項5】

前記第3の半導体領域の不純物濃度が、前記半導体基板側に比べ前記第1の電極側で高くなっていることを特徴とする請求項1ないし請求項4いずれか一項記載の半導体整流装置。

【請求項6】

前記第3の半導体領域に挟まれる絶縁層を、さらに備えることを特徴とする請求項1ないし請求項5いずれか一項記載の半導体整流装置。

【請求項7】

前記第3の半導体領域の幅が、前記第1の電極側から前記半導体基板側に向けて狭くなることを特徴とする請求項1ないし請求項6いずれか一項記載の半導体整流装置。

【請求項8】

前記第1の電極と前記第1の半導体領域とはショットキー接合しており、

前記第1の電極と前記第3の半導体領域とはオーミック接合していることを特徴とする請求項1ないし請求項7いずれか一項記載の半導体整流装置。

【請求項9】

前記ワイドバンドギャップ半導体が炭化珪素(SiC)であることを特徴とする請求項1ないし請求項8いずれか一項記載の半導体整流装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【公開番号】特開2012−182405(P2012−182405A)

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願番号】特願2011−45936(P2011−45936)

【出願日】平成23年3月3日(2011.3.3)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願日】平成23年3月3日(2011.3.3)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]