半導体発光素子およびその製造方法

【課題】放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法。

【解決手段】半導体基板2と、半導体基板2上に配置された第1導電型クラッド層32と、第1導電型クラッド層32上に配置された活性層33と、活性層33上に配置された第2導電型クラッド層34と、第2導電型クラッド層34上に配置された蒸着層35と、蒸着層35上に配置されたメッキ電極層36とを備え、メッキ電極層36の両端部は、メッキ電極層36の中央部に比べ薄いことを特徴とする半導体発光素子およびその製造方法。

【解決手段】半導体基板2と、半導体基板2上に配置された第1導電型クラッド層32と、第1導電型クラッド層32上に配置された活性層33と、活性層33上に配置された第2導電型クラッド層34と、第2導電型クラッド層34上に配置された蒸着層35と、蒸着層35上に配置されたメッキ電極層36とを備え、メッキ電極層36の両端部は、メッキ電極層36の中央部に比べ薄いことを特徴とする半導体発光素子およびその製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体発光素子およびその製造方法に関し、特に、放熱性とダイボンディング強度を向上させた半導体発光素子およびその製造方法に関する。

【背景技術】

【0002】

従来の半導体レーザダイオード(LD:Laser Diode)は、放熱性とダイボンディング強度を確保するために、金(Au)メッキ層が、LD素子表面に形成されている。すなわち、図17に示すように、半導体レーザダイオード部50上にAuの蒸着層35を介してAuのメッキ電極層36が形成されている。このようなLD素子は、図17に示すように、サブマウント部54に対して、例えば、Au−Sn層52を介して、ダイボンディングされる。

【0003】

しかしながら、従来のLD素子においては、図17に示すように、メッキ電極層36の端部が中央部に比べて厚い。このため、図18に示すように、ダイボンディング後に空洞部56が形成され易い。このような空洞部56が発生すると、ダイボンディング後において、LD素子における放熱性とダイボンディング強度が得られないという問題点がある。

【0004】

電極膜の応力による結晶破壊を回避するために、電極膜の端部にステップ形状またはテテーパ形状を有する半導体光装置については、既に開示されている(例えば、特許文献1参照。)。

【特許文献1】特開2008−244414号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明の目的は、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するための本発明の一態様によれば、半導体基板と、前記半導体基板上に配置された第1導電型クラッド層と、前記第1導電型クラッド層上に配置された活性層と、前記活性層上に配置された第2導電型クラッド層と、前記第2導電型クラッド層上に配置された蒸着層と、前記蒸着層上に配置されたメッキ電極層とを備え、前記メッキ電極層の両端部は、前記メッキ電極層の中央部に比べ薄い半導体発光素子が提供される。

【0007】

本発明の他の態様によれば、半導体基板と、前記半導体基板上に配置された第1の第1導電型クラッド層と、前記第1の第1導電型クラッド層上に配置された第1活性層と、前記第1活性層上に配置された第1の第2導電型クラッド層と、前記第1の第2導電型クラッド層上に配置された第1蒸着層と、前記第1蒸着層上に配置された第1メッキ電極層と、前記半導体基板上に配置された第2の第1導電型クラッド層と、前記第2の第1導電型クラッド層上に配置された第2活性層と、前記第2活性層上に配置された第2の第2導電型クラッド層と、前記第2の第2導電型クラッド層上に配置された第2蒸着層と、前記第2蒸着層上に配置された第2メッキ電極層と、を備え、前記第1メッキ電極層の両端部は、前記第1メッキ電極層の中央部に比べ薄く、かつ前記第2メッキ電極層の両端部は、前記第2メッキ電極層の中央部に比べ薄い半導体発光素子が提供される。

【0008】

本発明の他の態様によれば、半導体基板と、前記半導体基板上に配置され、複数の互いに分離された第1導電型クラッド層と、前記複数の互いに分離された第1導電型クラッド層上にそれぞれ配置され、互いに分離された複数の活性層と、前記複数の活性層上にそれぞれ配置され、互いに分離された複数の第2導電型クラッド層と、前記複数の第2導電型クラッド層上に配置され、互いに分離された複数の蒸着層と、前記複数の蒸着層上に配置され、互いに分離された複数のメッキ電極層とを備え、前記複数のメッキ電極層の端部は前記複数のメッキ電極層の中央部に比べ薄い半導体発光素子が提供される。

【0009】

本発明の他の態様によれば、半導体基板上に第1導電型クラッド層を形成する工程と、前記第1導電型クラッド層上に活性層を形成する工程と、前記活性層上に第2導電型クラッド層を形成する工程と、前記第2導電型クラッド層、前記活性層および前記第1導電型クラッド層をエッチングする工程と、前記半導体基板上および前記第2導電型クラッド層上全面に蒸着層を形成する工程と、前記第2導電型クラッド層上の前記蒸着層上にメッキ電極層を形成する工程と、前記メッキ電極層の両端部をエッチングにより薄層化するとともに、前記蒸着層を除去する工程とを有する半導体発光素子の製造方法が提供される。

【発明の効果】

【0010】

本発明によれば、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法を提供することができる。

【発明を実施するための最良の形態】

【0011】

次に、図面を参照して、本発明の実施の形態を説明する。以下において、同じブロックまたは要素には同じ符号を付して説明の重複を避け、説明を簡略にする。図面は模式的なものであり、現実のものとは異なることに留意すべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0012】

以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施の形態は、各構成部品の配置などを下記のものに特定するものでない。この発明の実施の形態は、特許請求の範囲において、種々の変更を加えることができる。

【0013】

[第1の実施の形態]

(素子構造)

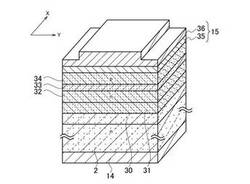

本発明の第1の実施の形態に係る半導体発光素子は、図1に示すように、半導体基板2と、半導体基板2上に配置された第1導電型クラッド層32と、第1導電型クラッド層32上に配置された活性層33と、活性層33上に配置された第2導電型クラッド層34と、第2導電型クラッド層34上に配置された蒸着層35と、蒸着層35上に配置されたメッキ電極層36とを備える。

【0014】

メッキ電極層36の両端部は、図1に示すように、メッキ電極層36の中央部に比べ薄い。

【0015】

第1の実施の形態に係る半導体発光素子は、後述する図10に示すように、素子分離部90によって、互いに分離されている。

【0016】

また、半導体基板2と第1導電型クラッド層32間には、第1導電型クラッド層30と、第1導電型クラッド層30上に配置されたエッチングストップ層31を備えている。すなわち、第1導電型クラッド層30および32内にエッチングストップ層31が形成されている。

【0017】

半導体基板2、第1導電型クラッド層30および32、活性層33、第2導電型クラッド層34としては、例えば、赤外光である780nm波長発光用のAlGaAs系化合物半導体や、赤色光である650nm波長発光用のInGaAlP系化合物半導体が適用可能である。

【0018】

これらの半導体材料を積層するための半導体基板2としては、GaAs基板が一般的に用いられるが、他の半導体でも適用可能である。

【0019】

また、半導体基板2の導電型は、LDを組み込むセットとの関係で、基板側に望まれる導電型のn型またはp型のいずれかが用いられ、この半導体基板2の導電型にしたがって、積層される半導体層の導電型も決定される。以下の具体例では、半導体基板2がn型の例で説明する。

【0020】

第1の実施の形態に係る半導体発光素子は、図1に示すように、半導体基板2と、半導体基板2上に配置されたn型クラッド層30と、n型クラッド層30上に配置されたエッチングストップ層31と、エッチングストップ層31上に配置されたn型クラッド層32と、n型クラッド層32上に配置された活性層33と、活性層33上に配置されたp型クラッド層34と、p型クラッド層34上に配置された蒸着層35と、蒸着層35上に配置されたメッキ電極層36とを備える。

【0021】

半導体基板2の裏面には、n側電極14が形成される。また、蒸着層35およびメッキ電極層36によって、p側電極15が形成される。

【0022】

n型クラッド層30および32は、例えば、Alx1Ga1-x1As(0.3≦x1≦0.7、例えば、x1=0.5)からなる。n型クラッド層30および32には、例えば、Siを約2×1018cm-3程度ドープしている。

【0023】

エッチングストップ層31は、n型またはノンドープの、例えばIn0.49Ga0.51Pからなり、例えば、約0.01μm〜0.05μm程度に形成されている。

【0024】

n型クラッド層30、エッチングストップ層31およびn型クラッド層32の全体の厚さは、例えば、約2μm〜4μm程度に形成される。

【0025】

活性層33は、Aly1Ga1-y1As(0.05≦y1≦0.2、例えば、y1=0.15)のバルク構造またはAly2Ga1-y2As(0.01≦y2≦0.1、例えば、y2=0.05)からなるウェル層とAly3Ga1-y3As(0.2≦y3≦0.5、y2<y3、例えば、y3=0.3)からなるバリア層とのシングル量子井戸(SQW:Single Quantum Well)

若しくはマルチ量子井戸(MQW:Multi Quantum Well)構造によって、全体として、例えば、約0.01μm〜0.2μm程度に形成される。

【0026】

p型クラッド層34は、例えば、Alx2Ga1-x2As(0.3≦x2≦0.7、例えば、x2=0.5)からなり、例えば、約0.5μm〜4μm程度に形成される。p型クラッド層34内には、p型またはノンドープの、例えばIn0.49Ga0.51Pからなるエッチストップ層が、例えば、約0.01μm〜0.05μm程度に形成されていても良い。

【0027】

尚、活性層33とn型クラッド層32との間、活性層33とp型クラッド層34との間に光ガイド層を設ける構造、活性層33とn型クラッド層32との間にビーム拡大層を設ける構造など、他の半導体層がいずれかの層間に介在されていても良い。

【0028】

前述の例では、AlGaAs系化合物半導体の例であったが、InGaAlP系化合物で構成する場合には、例えば、In0.49(Ga1-uAlu)0.51P(0.45≦u≦0.8、例えば、u=0.7)層によって、n型クラッド層32およびp型クラッド層34を形成することができ、In0.49(Ga1-v1Alv1)0.51P(0≦v1≦0.25、例えば、v1=0)/In0.49(Ga1-v2Alv2)0.51P(0.3≦v2≦0.7、例えば、v2=0.4)によるSQW構造若しくはMQW構造などによって、活性層33を形成することができる。

【0029】

尚、エッチングストップ層31は、In0.49Ga0.51Pに限定されるものではなく、例えば、In0.49(Ga0.8Al0.2)0.51Pなどを使用することもできる。

【0030】

(製造方法)

第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造は、図2〜図6に示すように表される。図2〜図6を参照して、第1の実施の形態に係る半導体発光素子の製造方法を説明する。

【0031】

第1の実施の形態に係る半導体発光素子の製造方法は、図2〜図6に示すように、半導体基板上にn型クラッド層30を形成する工程と、n型クラッド層30上にエッチングストップ層31を形成する工程と、エッチングストップ層31上にn型クラッド層32を形成する工程と、n型クラッド層32上に活性層33を形成する工程と、活性層33上にp型クラッド層34を形成する工程と、p型クラッド層34、活性層33およびn型クラッド層32をエッチングする工程と、半導体基板2上およびp型クラッド層34上全面に蒸着層35を形成する工程と、p型クラッド層34上の蒸着層35上にメッキ電極層36を形成する工程と、メッキ電極層36の両端部をエッチングにより薄層化するとともに、蒸着層35を除去する工程とを有する。

【0032】

(a)具体的には、図2に示すように、n型半導体基板2を、例えば、有機金属気相成長(MOCVD:Metal Organic Chemical Vapor Deposition)装置内に入れ、反応ガスのトリエチルガリウム(TEG)、トリメチルアルミニウム(TMA)、トリメチルインジウム(TMI)、ホスフィン(PH3)、アルシン(AsH3)および半導体層の導電型に応じて、n型ドーパントガスとしてSi若しくはSe含有ガス、p型ドーパントとしてジメチル亜鉛(DMZn)若しくはBe含有ガスをキャリアガスの水素(H2)と共に導入し、500℃〜700℃程度で各半導体層(30,31,32,33,34)をエピタキシャル成長する。

【0033】

(b)次に、図2に示すように、フォトリソグラフィーとマスクパターニング工程によって、p型クラッド層34、活性層33およびn型クラッド層32をエッチングし、リッジ部を形成する。例えば、CVD法などにより、SiO2またはSiNxなどからなるマスクを形成し、例えば、ドライエッチングなどにより、p型クラッド層34、活性層33およびn型クラッド層32を、エッチングストップ層31が露出するまで選択的にエッチングすることにより、図2に示されるように、リッジ部がストライプ状に形成される。

【0034】

(c)次に、図2に示すように、半導体基板2上のエッチングストップ層31上およびp型クラッド層34上全面に蒸着層35を形成する。蒸着層35としては、Au層若しくはTi/Au層などを適用することができる。蒸着層35の厚さは、例えば、Au層の場合、約0.5μm程度である。

【0035】

(d)次に、図2に示すように、例えば、フォトリソグラフィーとマスクパターニング工程によって、レジスト層40をパターン形成し、このレジスト層40をマスクとして、p型クラッド層34上の蒸着層35上にメッキ電極層36を、電界メッキにより形成する。メッキ電極層36は、図2中の破線により模式的に示されるように、層構造に形成される。しかも、このように層構造に形成されるメッキ電極層36は、レジスト層40に接する部分近傍のメッキ電極層36が厚く形成され易いという傾向がある。これは、電界メッキ工程中において、メッキ電極層36に接するレジスト層40の表面に微弱な電流が流れ、メッキ電極層36も成長が促進されるためである。

【0036】

(e)次に、図3に示すように、レジスト層40を除去する。図7および図8に示すリッジ構造の左端部分及び右端部分のSEM写真例から明らかなように、メッキ電極層36の両端部の厚さは中央部の厚さに比べて厚い。中央部におけるメッキ電極層36の厚さは、例えば、約2.5μm程度である。メッキ電極層36の両端部の厚さと中央部の厚さの差は、例えば、0.3μm〜1.0μm程度である。

【0037】

(f)次に、図4に示すように、フォトリソグラフィーとマスクパターニング工程によって、レジスト層38をパターン形成する。

【0038】

(g)次に、図5に示すように、例えば、ウェットエッチングにより、メッキ電極層36

の両端部および蒸着層35を除去する。ウェットエッチングに使用するエッチング液としては、王水、ヨウ素水溶液などを適用することができる。メッキ電極層36は、蒸着層35に比べて金属原子の密度が低いため、同一のウェットエッチング工程によって、容易にエッチングされ易いため、メッキ電極層36の厚さは、蒸着層35の厚さの例えば、約5倍程度に形成する必要がある。

【0039】

(h)次に、図6に示すように、レジスト層38を除去することによって、両端部が薄層化されたメッキ電極層36を得ることができる。

【0040】

(i)次に、図1に示すように、研磨により半導体基板2を薄層化した後、半導体基板2の裏面に、Au/Ge/NiまたはTi/Auなどからなるn側電極14を形成する。

【0041】

第1の実施の形態に係る半導体発光素子のLDバー100の半導体ウェハ110上における配置構成は、図9に示すように表される。また、第1の実施の形態に係る半導体発光素子のLDバー100の平面パターン構成例は、図10(a)に示すように表され、図10(a)のの拡大図は、図10(b)に示すように表される。

【0042】

(j)次に、図9〜図10に示すように、レーザ共振器80の延伸方向Xと垂直なY方向にスクライブを入れ、ブレークを行うことにより、容易に安定した劈開面100a,100bを形成し、LDバー100を形成する。つまり、安定した共振器ミラーを作成することができる。上記のように劈開面を形成したLDバー100の内の1個の半導体発光素子のレーザ共振器80の拡大された模式的断面構造例が、図1に相当する。

【0043】

p側電極36を有するレーザ共振器80がX方向に延伸し、Y方向に複数個、並列に配置されて、1個のLDバー100を形成している。LDバー100の幅W1は、レーザ共振器80の長さに相当し、例えば約数10μm〜数100μm程度である。一方、LDバー100の長さW2は、約数100μm〜数10mm程度である。1個のLD素子のチップ幅は、約250μm程度であり、LDバー100上に隣接するLD素子の間隔は、約10μm〜100μm程度であり、望ましくは14μm〜30μm程度である。

【0044】

第1の実施の形態に係る半導体発光素子のマウント構造は、図11に示すように表される。すなわち、半導体レーザダイオード部50上にAuの蒸着層35を介して、両端部を薄層化したAuのメッキ電極層36が形成されている。このようなLD素子は、図11に示すように、サブマウント部54に対して、例えば、Au−Sn層52を介して、ダイボンディングされる。

【0045】

第1の実施の形態に係る半導体発光素子は、放熱性とダイボンディング強度を確保するために、両端部が中央部に比べて薄いメッキ電極層36を適用することによって、ダイボンディングの隙間が無くなる。このため、濡れ性に優れ、剥離強度が強化され、密着性が良好となる。このため、熱放散が良好となり、結果として、活性層33の動作温度が減少し、動作電流が減少するため、LD素子の寿命が延びる傾向が得られる。

【0046】

第1の実施の形態によれば、LD素子をステム若しくはサブマウントにダイボンディングする際に、ダイボンディングを阻害するメッキ電極層端部を取り除くことによって、安定したダイボンディングを行うことができ、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法を提供することができる。

【0047】

[第2の実施の形態]

(素子構造)

本発明の第2の実施の形態に係る半導体発光素子は、図12に示すように、半導体基板2と、半導体基板2上に配置された第1の第1導電型クラッド層32と、第1の第1導電型クラッド層32上に配置された第1活性層33と、第1活性層33上に配置された第1の第2導電型クラッド層34と、第1の第2導電型クラッド層34上に配置された第1蒸着層35aと、第1蒸着層35a上に配置された第1メッキ電極層36aと、半導体基板2上に配置された第2の第1導電型クラッド層42と、第2の第1導電型クラッド層42上に配置された第2活性層43と、第2活性層43上に配置された第2の第2導電型クラッド層44と、第2の第2導電型クラッド層44上に配置された第2蒸着層35bと、第2蒸着層35b上に配置された第2メッキ電極層36bと備える。

【0048】

第1メッキ電極層36aの両端部は中央部に比べ薄く、かつ第2メッキ電極層36bの両端部も中央部に比べ薄い。

【0049】

第2の実施の形態に係る半導体発光素子は、図12に示すように、素子分離部90って、互いに分離されている。

【0050】

また、半導体基板2と第1の第1導電型クラッド層32間には、第1導電型クラッド層30と、第1導電型クラッド層30上に配置されたエッチングストップ層31を備えている。すなわち、第1導電型クラッド層30および32内にエッチングストップ層31が形成されている。

【0051】

また、半導体基板2と第2の第1導電型クラッド層42間には、第1導電型クラッド層30と、第1導電型クラッド層30上に配置されたエッチングストップ層31を備えている。すなわち、第1導電型クラッド層30および42内にエッチングストップ層31が形成されている。

【0052】

また、第2の実施の形態に係る半導体発光素子は、2波長レーザ光を発生することができる。

【0053】

第1の第1導電型クラッド層32、第1活性層33、第1の第2導電型クラッド層34としては、例えば、赤外光である780nm波長発光用のAlGaAs系化合物半導体が適用可能であり、第2の第1導電型クラッド層42、第2活性層43、第2の第2導電型クラッド層44としては、例えば、赤色光である650nm波長発光用のInGaAlP系化合物半導体が適用可能である。

【0054】

これらの半導体材料を積層するための半導体基板2としては、GaAs基板が一般的に用いられるが、他の半導体でも適用可能である。

【0055】

また、半導体基板2の導電型は、LDを組み込むセットとの関係で、基板側に望まれる導電型のn型またはp型のいずれかが用いられ、この半導体基板2の導電型にしたがって、積層される半導体層の導電型も決定される。以下の具体例では、半導体基板2がn型の例で説明する。

【0056】

第2の実施の形態に係る半導体発光素子は、図12に示すように、半導体基板2と、半導体基板2上に配置されたn型クラッド層30と、n型クラッド層30上に配置されたエッチングストップ層31と、エッチングストップ層31上に配置されたn型クラッド層32と、n型クラッド層32上に配置された活性層33と、活性層33上に配置されたp型クラッド層34と、p型クラッド層34上に配置された蒸着層35aと、蒸着層35a上に配置されたメッキ電極層36aと、エッチングストップ層31上に配置されたn型クラッド層42と、n型クラッド層42上に配置された活性層43と、活性層43上に配置されたp型クラッド層44と、p型クラッド層44上に配置された蒸着層35bと、蒸着層35b上に配置されたメッキ電極層36bとを備える。

【0057】

半導体基板2の裏面には、n側電極14が形成される。また、蒸着層35aおよびメッキ電極層36aによって、p側電極15が形成され、同様に、蒸着層35bおよびメッキ電極層36bによっても、p側電極15が形成される。

【0058】

n型クラッド層30および32は、例えば、Alx1Ga1-x1As(0.3≦x1≦0.7、例えば、x1=0.5)からなる。n型クラッド層30および32には、例えば、Siを約2×1018cm-3程度ドープしている。

【0059】

エッチングストップ層31は、n型またはノンドープの、例えばIn0.49Ga0.51Pからなり、例えば、約0.01μm〜0.05μm程度に形成されている。

【0060】

n型クラッド層30、エッチングストップ層31およびn型クラッド層32の全体の厚さは、例えば、約2μm〜4μm程度に形成される。

【0061】

活性層33は、Aly1Ga1-y1As(0.05≦y1≦0.2、例えば、y1=0.15)のバルク構造またはAly2Ga1-y2As(0.01≦y2≦0.1、例えば、y2=0.05)からなるウェル層とAly3Ga1-y3As(0.2≦y3≦0.5、y2<y3、例えば、y3=0.3)からなるバリア層とのシングル量子井戸(SQW:Single Quantum Well)

若しくはマルチ量子井戸(MQW:Multi Quantum Well)構造によって、全体として、例えば、約0.01μm〜0.2μm程度に形成される。

【0062】

p型クラッド層34は、例えば、Alx2Ga1-x2As(0.3≦x2≦0.7、例えば、x2=0.5)からなり、例えば、約0.5μm〜4μm程度に形成される。p型クラッド層34内には、p型またはノンドープの、例えばIn0.49Ga0.51Pからなるエッチストップ層が、例えば、約0.01μm〜0.05μm程度に形成されていても良い。

【0063】

尚、活性層33とn型クラッド層32との間、活性層33とp型クラッド層34との間に光ガイド層を設ける構造、活性層33とn型クラッド層32との間にビーム拡大層を設ける構造など、他の半導体層がいずれかの層間に介在されていても良い。

【0064】

さらに、例えば、In0.49(Ga1-uAlu)0.51P(0.45≦u≦0.8、例えば、u=0.7)層によって、n型クラッド層42およびp型クラッド層44を形成することができ、In0.49(Ga1-v1Alv1)0.51P(0≦v1≦0.25、例えば、v1=0)/In0.49(Ga1-v2Alv2)0.51P(0.3≦v2≦0.7、例えば、v2=0.4)によるSQW構造若しくはMQW構造などによって、活性層43を形成する。

【0065】

尚、エッチングストップ層31は、In0.49Ga0.51Pに限定されるものではなく、例えば、In0.49(Ga0.8Al0.2)0.51Pなどを使用することもできる。

【0066】

n型クラッド層32、活性層33、p型クラッド層34としてAlGaAs系化合物半導体を適用し、n型クラッド層42、活性層43、p型クラッド層44として、InGaAlP系化合物半導体が適用する場合、InGaPによるエッチングストップ層31は、赤外用のAlGaAsによる活性層33よりもバンドギャップが大きいため、エッチングストップ層31による赤外光の吸収・損失は少ない。一方、AlGaAsにより形成されるn型クラッド層30は、赤色用のInGaAlPによる活性層43よりもバンドギャップが大きいため、n型クラッド層30による赤色光の吸収・損失は少ない。

【0067】

第2の実施の形態に係る半導体発光素子は、2波長のレーザ光を高輝度で得ることができる。

【0068】

第2の実施の形態に係る半導体発光素子のLDバー100の平面パターン構成例は、図13(a)に示すように表され、図13(a)の拡大図は、図13(b)に示すように表される。

【0069】

互いに隣接して、図12に示す2波長のレーザ光を発生する半導体発光素子が形成されている。

【0070】

第2の実施の形態においても製造工程は、赤外用のAlGaAs系化合物半導体層構造と赤色用のInGaAlP系半導体層構造を別々に形成する以外は、第1の実施の形態と同様である。

【0071】

両端部が薄層化されたメッキ電極層36a、36bを形成する工程も第1の実施の形態と同様である。

【0072】

また、第2の実施の形態に係る半導体発光素子のマウント構造も、第1の実施の形態と同様である。

【0073】

第2の実施の形態に係る半導体発光素子は、放熱性とダイボンディング強度を確保するために、両端部が中央部に比べて薄いメッキ電極層36a,36bを適用することによって、ダイボンディングの隙間が無くなる。このため、濡れ性に優れ、剥離強度が強化され、密着性が良好となる。このため、熱放散が良好となり、結果として、活性層33、43の動作温度が減少し、動作電流が減少するため、LD素子の寿命が延びる傾向が得られる。

【0074】

第2の実施の形態によれば、LD素子をステム若しくはサブマウントにダイボンディングする際に、ダイボンディングを阻害するメッキ電極層端部を取り除くことによって、安定したダイボンディングを行うことができ、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した2波長の半導体発光素子およびその製造方法を提供することができる。

【0075】

[第3の実施の形態]

(素子構造)

本発明の第3の実施の形態に係る半導体発光素子は、図14に示すように、半導体基板2と、半導体基板2上に配置され、複数の互いに分離されたn型クラッド層32と、複数の互いに分離されたn型クラッド層32上にそれぞれ配置され、互いに分離された複数の活性層33と、複数の活性層33上にそれぞれ配置され、互いに分離された複数のp型クラッド層34と、複数のp型クラッド層34上に配置され、互いに分離された複数の蒸着層35と、複数の蒸着層35上に配置され、互いに分離された複数のメッキ電極層36a,36b,36c,36dとを備える。

【0076】

複数のメッキ電極層36a,36b,36c,36dのそれぞれの両端部は中央部に比べ薄い。

【0077】

第3の実施の形態に係る半導体発光素子は、図14に示すように、素子分離部90って、互いに分離されている。

【0078】

また、半導体基板2と複数のn型クラッド層32間には、n型クラッド層30と、n型クラッド層30上に配置されたエッチングストップ層31を備えている。すなわち、n型クラッド層30および複数のn型クラッド層32内にエッチングストップ層31が形成されている。

【0079】

第3の実施の形態に係る半導体発光素子は、マルチビームのレーザ光を発生することができる。

【0080】

第3の実施の形態に係る半導体発光素子のLDバー100の平面パターン構成例は、図15(a)に示すように表され、図15(a)の拡大図は、図15(b)に示すように表される。

【0081】

互いに隣接して、図14に示すクワッドビームのレーザ光を発生する半導体発光素子が形成されている。

【0082】

第3の実施の形態に係る半導体発光素子は、このようにLDバー100上に配置されるLD素子の数をさらに増加させて、クワッドビーム以上のマルチビームのレーザ光を発生することもできる。

【0083】

第3の実施の形態に係る半導体発光素子においても第1の実施の形態と同様に、n型クラッド層32、活性層33、p型クラッド層34としては、例えば、赤外光である780nm波長発光用のAlGaAs系化合物半導体や、例えば、赤色光である650nm波長発光用のInGaAlP系化合物半導体が適用可能である。

【0084】

また、第3の実施の形態に係る半導体発光素子においても、半導体基板2、n型クラッド層30、エッチングストップ層31、n型クラッド層32、活性層33、p型クラッド層34は、第1の実施の形態と同様の構造で形成することができる。

【0085】

第3の実施の形態に係る半導体発光素子においては、両端部が薄層化されたメッキ電極層36a,36b,36c,36dを形成する工程も第1の実施の形態と同様である。

【0086】

また、第3の実施の形態に係る半導体発光素子のマウント構造も、第1の実施の形態と同様である。

【0087】

第3の実施の形態に係る半導体発光素子は、放熱性とダイボンディング強度を確保するために、両端部が中央部に比べて薄いメッキ電極層36a,36b,36c,36dを適用することによって、ダイボンディングの隙間が無くなる。このため、濡れ性に優れ、剥離強度が強化され、密着性が良好となる。このため、熱放散が良好となり、結果として、活性層33の動作温度が減少し、動作電流が減少するため、LD素子の寿命が延びる傾向が得られる。

【0088】

第3の実施の形態によれば、LD素子をステム若しくはサブマウントにダイボンディングする際に、ダイボンディングを阻害するメッキ電極層端部を取り除くことによって、安定したダイボンディングを行うことができ、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上したマルチビームの半導体発光素子およびその製造方法を提供することができる。

【0089】

[第4の実施の形態]

(素子構造)

本発明の第4の実施の形態に係る半導体発光素子は、図16に示すように、半導体基板2と、半導体基板2上に配置されたn型クラッド層32と、n型クラッド層32上に配置された活性層33と、活性層33上に配置されたp型クラッド層34と、p型クラッド層34上に配置されたキャップ層4と、p型クラッド層34およびキャップ層4の側壁部に配置された電流ブロック層5,6と、キャップ層4および電流ブロック層5,6上に配置されたコンタクト層1と、コンタクト層1上に配置された蒸着層35と、蒸着層35上に配置されたメッキ電極層36とを備える。

【0090】

メッキ電極層36の両端部は、図16に示すように、中央部に比べ薄い。

【0091】

n型クラッド層30および32は、例えば、Alx1Ga1-x1As(0.3≦x1≦0.7、例えば、x1=0.5)からなる。n型クラッド層30および32には、例えば、Siを約2×1018cm-3程度ドープしている。

【0092】

エッチングストップ層31は、n型またはノンドープの、例えばIn0.49Ga0.51Pからなり、例えば、約0.01μm〜0.05μm程度に形成されている。

【0093】

n型クラッド層30、エッチングストップ層31およびn型クラッド層32の全体の厚さは、例えば、約2μm〜4μm程度に形成される。

【0094】

活性層33は、Aly1Ga1-y1As(0.05≦y1≦0.2、例えば、y1=0.15)のバルク構造またはAly2Ga1-y2As(0.01≦y2≦0.1、例えば、y2=0.05)からなるウェル層とAly3Ga1-y3As(0.2≦y3≦0.5、y2<y3、例えば、y3=0.3)からなるバリア層とのシングル量子井戸(SQW:Single Quantum Well)

若しくはマルチ量子井戸(MQW:Multi Quantum Well)構造によって、全体として、例えば、約0.01μm〜0.2μm程度に形成される。

【0095】

p型クラッド層34は、例えば、Alx2Ga1-x2As(0.3≦x2≦0.7、例えば、x2=0.5)からなり、例えば、約0.5μm〜4μm程度に形成される。p型クラッド層34内には、p型またはノンドープの、例えばIn0.49Ga0.51Pからなるエッチストップ層(図示省略)が、例えば、約0.01μm〜0.05μm程度に形成されている。

【0096】

尚、活性層33とn型クラッド層32との間、活性層33とp型クラッド層34との間に光ガイド層を設ける構造、活性層33とn型クラッド層32との間にビーム拡大層を設ける構造など、他の半導体層がいずれかの層間に介在されていても良い。

【0097】

前述の例では、AlGaAs系化合物半導体の例であったが、InGaAlP系化合物で構成する場合には、例えば、In0.49(Ga1-uAlu)0.51P(0.45≦u≦0.8、例えば、u=0.7)層によって、n型クラッド層32およびp型クラッド層34を形成することができ、In0.49(Ga1-v1Alv1)0.51P(0≦v1≦0.25、例えば、v1=0)/In0.49(Ga1-v2Alv2)0.51P(0.3≦v2≦0.7、例えば、v2=0.4)によるSQW構造若しくはMQW構造などによって、活性層33を形成することができる。

【0098】

尚、エッチングストップ層31は、In0.49Ga0.51Pに限定されるものではなく、例えば、In0.49(Ga0.8Al0.2)0.51Pなどを使用することもできる。

【0099】

また、p型クラッド層34にリッジ部を形成するためのエッチングは以下の通りである。例えば、CVD法などにより、SiO2またはSiNxなどからなるマスクを形成し、例えば、ドライエッチングなどにより、キャップ層4を選択的にエッチングし、引き続きHClのようなエッチング液により、p型クラッド層34をエッチングすることにより、図16に示されるように、リッジ部がストライプ状に形成される。

【0100】

キャップ層4は、例えば、p型In0.49Ga0.51Pからなり、厚さは、例えば、約0.01μm〜0.05μm程度である。キャップ層4は、後の工程でコンタクト層1を形成する際に、半導体積層部の表面に酸化膜などが形成されて、汚れるのを防止するためのものである。GaAsなどの他の半導体層で形成されていても良い。また、表面の汚れさえ防止することできるのであれば、無くても良い。

【0101】

コンタクト層1は、キャップ層4および電流ブロック層5,6上に、例えば、p型GaAs層により、その厚さが0.05μm〜10μm程度に形成される。

【0102】

電流ブロック層5,6としては、AlGaAs、GaAs、INAlPなどを用いることができる。

【0103】

第4の実施の形態に係る半導体発光素子においても、図10と同様に、LDバー100上に配置されるLD素子の数を増加させて、クワッドビーム以上のマルチビームのレーザ光を発生することもできる。

【0104】

第4の実施の形態に係る半導体発光素子においても第1の実施の形態と同様に、n型クラッド層32、活性層33、p型クラッド層34としては、例えば、赤外光である780nm波長発光用のAlGaAs系化合物半導体や、例えば、赤色光である650nm波長発光用のInGaAlP系化合物半導体が適用可能である。

【0105】

第4の実施の形態に係る半導体発光素子においては、両端部が薄層化されたメッキ電極層36を形成する工程も第1の実施の形態と同様である。

【0106】

また、第4の実施の形態に係る半導体発光素子のマウント構造も、第1の実施の形態と同様である。

【0107】

第4の実施の形態に係る半導体発光素子は、放熱性とダイボンディング強度を確保するために、両端部が中央部に比べて薄いメッキ電極層36を適用することによって、ダイボンディングの隙間が無くなる。このため、濡れ性に優れ、剥離強度が強化され、密着性が良好となる。このため、熱放散が良好となり、結果として、活性層33の動作温度が減少し、動作電流が減少するため、LD素子の寿命が延びる傾向が得られる。

【0108】

第4の実施の形態によれば、LD素子をステム若しくはサブマウントにダイボンディングする際に、ダイボンディングを阻害するメッキ電極層端部を取り除くことによって、安定したダイボンディングを行うことができ、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法を提供することができる。

【0109】

[その他の実施の形態]

上記のように、本発明は第1〜第4の実施の形態によって記載したが、この開示の一部をなす論述および図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0110】

本発明の第1〜第4の実施の形態に係る半導体発光素子として、主としてストライプ型LDを例に説明したが、その他の例としては、分布帰還型(DFB:Distributed Feedback)LD、分布ブラッグ反射型(DBR:Distributed Bragg Reflector)LD、面発光LDなどを構成しても良い。

【0111】

また、本発明の第1〜第4の実施の形態に係る半導体発光素子として、LED(Light Emitting Diode)を構成しても良い。

【0112】

既に述べた実施の形態の説明においては、活性層が、それぞれバリア層で挟まれた複数の井戸層を有するMQW構造である場合を示したが、活性層が1つの井戸層を有する構造であってもよい。

【0113】

このように、本発明はここでは記載していない様々な実施の形態などを含む。

【産業上の利用可能性】

【0114】

本発明の半導体発光素子は、2波長レーザ、クワッドビームレーザ、マルチビームレーザなどの半導体発光素子全般に適用可能であり、CD、DVD、DVD−ROM、データ書込み可能なCD−RW等のピックアップ用のLD素子、プリンター用のLD素子、光通信用のLD素子として適用可能である。

【図面の簡単な説明】

【0115】

【図1】本発明の第1の実施の形態に係る半導体発光素子の模式的鳥瞰構造図。

【図2】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図3】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図4】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図5】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図6】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図7】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明するリッジ構造の左端部分のSEM写真例。

【図8】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明するリッジ構造の右端部分のSEM写真例。

【図9】本発明の第1の実施の形態に係る半導体発光素子のLDバーの半導体ウェハ上における配置構成例。

【図10】(a)本発明の第1の実施の形態に係る半導体発光素子のLDバーの平面パターン構成例、(b)(a)の拡大図。

【図11】本発明の第1の実施の形態に係る半導体発光素子のマウント構造の模式的断面構造図。

【図12】本発明の第2の実施の形態に係る半導体発光素子の模式的断面構造図。

【図13】(a)本発明の第2の実施の形態に係る半導体発光素子のLDバーの平面パターン構成例、(b)(a)の拡大図。

【図14】本発明の第3の実施の形態に係る半導体発光素子の模式的断面構造図。

【図15】(a)本発明の第3の実施の形態に係る半導体発光素子のLDバーの平面パターン構成例、(b)(a)の拡大図。

【図16】本発明の第4の実施の形態に係る半導体発光素子の模式的鳥瞰構造図。

【図17】従来の半導体発光素子のマウント工程を説明する模式的断面構造図。

【図18】従来の半導体発光素子のマウント構造の模式的断面構造図。

【符号の説明】

【0116】

1…コンタクト層

2…半導体基板

4…キャップ層

5,6…埋め込み層

14…n側電極

15…p側電極

31…エッチングストップ層

32、42…第1導電型(n型)クラッド層

33、43…活性層

34、44…第2導電型(p型)クラッド層

35,35a,35b…蒸着層

36、36a,36b,36c,36d…メッキ電極層

38、40…レジスト層

50…半導体レーザダイオード部

52…Au−Sn層

54…サブマウント部

56…空洞部

80…レーザ共振器

90…素子分離部

100…LDバー

100a,100b…劈開面

【技術分野】

【0001】

本発明は、半導体発光素子およびその製造方法に関し、特に、放熱性とダイボンディング強度を向上させた半導体発光素子およびその製造方法に関する。

【背景技術】

【0002】

従来の半導体レーザダイオード(LD:Laser Diode)は、放熱性とダイボンディング強度を確保するために、金(Au)メッキ層が、LD素子表面に形成されている。すなわち、図17に示すように、半導体レーザダイオード部50上にAuの蒸着層35を介してAuのメッキ電極層36が形成されている。このようなLD素子は、図17に示すように、サブマウント部54に対して、例えば、Au−Sn層52を介して、ダイボンディングされる。

【0003】

しかしながら、従来のLD素子においては、図17に示すように、メッキ電極層36の端部が中央部に比べて厚い。このため、図18に示すように、ダイボンディング後に空洞部56が形成され易い。このような空洞部56が発生すると、ダイボンディング後において、LD素子における放熱性とダイボンディング強度が得られないという問題点がある。

【0004】

電極膜の応力による結晶破壊を回避するために、電極膜の端部にステップ形状またはテテーパ形状を有する半導体光装置については、既に開示されている(例えば、特許文献1参照。)。

【特許文献1】特開2008−244414号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明の目的は、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

上記目的を達成するための本発明の一態様によれば、半導体基板と、前記半導体基板上に配置された第1導電型クラッド層と、前記第1導電型クラッド層上に配置された活性層と、前記活性層上に配置された第2導電型クラッド層と、前記第2導電型クラッド層上に配置された蒸着層と、前記蒸着層上に配置されたメッキ電極層とを備え、前記メッキ電極層の両端部は、前記メッキ電極層の中央部に比べ薄い半導体発光素子が提供される。

【0007】

本発明の他の態様によれば、半導体基板と、前記半導体基板上に配置された第1の第1導電型クラッド層と、前記第1の第1導電型クラッド層上に配置された第1活性層と、前記第1活性層上に配置された第1の第2導電型クラッド層と、前記第1の第2導電型クラッド層上に配置された第1蒸着層と、前記第1蒸着層上に配置された第1メッキ電極層と、前記半導体基板上に配置された第2の第1導電型クラッド層と、前記第2の第1導電型クラッド層上に配置された第2活性層と、前記第2活性層上に配置された第2の第2導電型クラッド層と、前記第2の第2導電型クラッド層上に配置された第2蒸着層と、前記第2蒸着層上に配置された第2メッキ電極層と、を備え、前記第1メッキ電極層の両端部は、前記第1メッキ電極層の中央部に比べ薄く、かつ前記第2メッキ電極層の両端部は、前記第2メッキ電極層の中央部に比べ薄い半導体発光素子が提供される。

【0008】

本発明の他の態様によれば、半導体基板と、前記半導体基板上に配置され、複数の互いに分離された第1導電型クラッド層と、前記複数の互いに分離された第1導電型クラッド層上にそれぞれ配置され、互いに分離された複数の活性層と、前記複数の活性層上にそれぞれ配置され、互いに分離された複数の第2導電型クラッド層と、前記複数の第2導電型クラッド層上に配置され、互いに分離された複数の蒸着層と、前記複数の蒸着層上に配置され、互いに分離された複数のメッキ電極層とを備え、前記複数のメッキ電極層の端部は前記複数のメッキ電極層の中央部に比べ薄い半導体発光素子が提供される。

【0009】

本発明の他の態様によれば、半導体基板上に第1導電型クラッド層を形成する工程と、前記第1導電型クラッド層上に活性層を形成する工程と、前記活性層上に第2導電型クラッド層を形成する工程と、前記第2導電型クラッド層、前記活性層および前記第1導電型クラッド層をエッチングする工程と、前記半導体基板上および前記第2導電型クラッド層上全面に蒸着層を形成する工程と、前記第2導電型クラッド層上の前記蒸着層上にメッキ電極層を形成する工程と、前記メッキ電極層の両端部をエッチングにより薄層化するとともに、前記蒸着層を除去する工程とを有する半導体発光素子の製造方法が提供される。

【発明の効果】

【0010】

本発明によれば、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法を提供することができる。

【発明を実施するための最良の形態】

【0011】

次に、図面を参照して、本発明の実施の形態を説明する。以下において、同じブロックまたは要素には同じ符号を付して説明の重複を避け、説明を簡略にする。図面は模式的なものであり、現実のものとは異なることに留意すべきである。また、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0012】

以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施の形態は、各構成部品の配置などを下記のものに特定するものでない。この発明の実施の形態は、特許請求の範囲において、種々の変更を加えることができる。

【0013】

[第1の実施の形態]

(素子構造)

本発明の第1の実施の形態に係る半導体発光素子は、図1に示すように、半導体基板2と、半導体基板2上に配置された第1導電型クラッド層32と、第1導電型クラッド層32上に配置された活性層33と、活性層33上に配置された第2導電型クラッド層34と、第2導電型クラッド層34上に配置された蒸着層35と、蒸着層35上に配置されたメッキ電極層36とを備える。

【0014】

メッキ電極層36の両端部は、図1に示すように、メッキ電極層36の中央部に比べ薄い。

【0015】

第1の実施の形態に係る半導体発光素子は、後述する図10に示すように、素子分離部90によって、互いに分離されている。

【0016】

また、半導体基板2と第1導電型クラッド層32間には、第1導電型クラッド層30と、第1導電型クラッド層30上に配置されたエッチングストップ層31を備えている。すなわち、第1導電型クラッド層30および32内にエッチングストップ層31が形成されている。

【0017】

半導体基板2、第1導電型クラッド層30および32、活性層33、第2導電型クラッド層34としては、例えば、赤外光である780nm波長発光用のAlGaAs系化合物半導体や、赤色光である650nm波長発光用のInGaAlP系化合物半導体が適用可能である。

【0018】

これらの半導体材料を積層するための半導体基板2としては、GaAs基板が一般的に用いられるが、他の半導体でも適用可能である。

【0019】

また、半導体基板2の導電型は、LDを組み込むセットとの関係で、基板側に望まれる導電型のn型またはp型のいずれかが用いられ、この半導体基板2の導電型にしたがって、積層される半導体層の導電型も決定される。以下の具体例では、半導体基板2がn型の例で説明する。

【0020】

第1の実施の形態に係る半導体発光素子は、図1に示すように、半導体基板2と、半導体基板2上に配置されたn型クラッド層30と、n型クラッド層30上に配置されたエッチングストップ層31と、エッチングストップ層31上に配置されたn型クラッド層32と、n型クラッド層32上に配置された活性層33と、活性層33上に配置されたp型クラッド層34と、p型クラッド層34上に配置された蒸着層35と、蒸着層35上に配置されたメッキ電極層36とを備える。

【0021】

半導体基板2の裏面には、n側電極14が形成される。また、蒸着層35およびメッキ電極層36によって、p側電極15が形成される。

【0022】

n型クラッド層30および32は、例えば、Alx1Ga1-x1As(0.3≦x1≦0.7、例えば、x1=0.5)からなる。n型クラッド層30および32には、例えば、Siを約2×1018cm-3程度ドープしている。

【0023】

エッチングストップ層31は、n型またはノンドープの、例えばIn0.49Ga0.51Pからなり、例えば、約0.01μm〜0.05μm程度に形成されている。

【0024】

n型クラッド層30、エッチングストップ層31およびn型クラッド層32の全体の厚さは、例えば、約2μm〜4μm程度に形成される。

【0025】

活性層33は、Aly1Ga1-y1As(0.05≦y1≦0.2、例えば、y1=0.15)のバルク構造またはAly2Ga1-y2As(0.01≦y2≦0.1、例えば、y2=0.05)からなるウェル層とAly3Ga1-y3As(0.2≦y3≦0.5、y2<y3、例えば、y3=0.3)からなるバリア層とのシングル量子井戸(SQW:Single Quantum Well)

若しくはマルチ量子井戸(MQW:Multi Quantum Well)構造によって、全体として、例えば、約0.01μm〜0.2μm程度に形成される。

【0026】

p型クラッド層34は、例えば、Alx2Ga1-x2As(0.3≦x2≦0.7、例えば、x2=0.5)からなり、例えば、約0.5μm〜4μm程度に形成される。p型クラッド層34内には、p型またはノンドープの、例えばIn0.49Ga0.51Pからなるエッチストップ層が、例えば、約0.01μm〜0.05μm程度に形成されていても良い。

【0027】

尚、活性層33とn型クラッド層32との間、活性層33とp型クラッド層34との間に光ガイド層を設ける構造、活性層33とn型クラッド層32との間にビーム拡大層を設ける構造など、他の半導体層がいずれかの層間に介在されていても良い。

【0028】

前述の例では、AlGaAs系化合物半導体の例であったが、InGaAlP系化合物で構成する場合には、例えば、In0.49(Ga1-uAlu)0.51P(0.45≦u≦0.8、例えば、u=0.7)層によって、n型クラッド層32およびp型クラッド層34を形成することができ、In0.49(Ga1-v1Alv1)0.51P(0≦v1≦0.25、例えば、v1=0)/In0.49(Ga1-v2Alv2)0.51P(0.3≦v2≦0.7、例えば、v2=0.4)によるSQW構造若しくはMQW構造などによって、活性層33を形成することができる。

【0029】

尚、エッチングストップ層31は、In0.49Ga0.51Pに限定されるものではなく、例えば、In0.49(Ga0.8Al0.2)0.51Pなどを使用することもできる。

【0030】

(製造方法)

第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造は、図2〜図6に示すように表される。図2〜図6を参照して、第1の実施の形態に係る半導体発光素子の製造方法を説明する。

【0031】

第1の実施の形態に係る半導体発光素子の製造方法は、図2〜図6に示すように、半導体基板上にn型クラッド層30を形成する工程と、n型クラッド層30上にエッチングストップ層31を形成する工程と、エッチングストップ層31上にn型クラッド層32を形成する工程と、n型クラッド層32上に活性層33を形成する工程と、活性層33上にp型クラッド層34を形成する工程と、p型クラッド層34、活性層33およびn型クラッド層32をエッチングする工程と、半導体基板2上およびp型クラッド層34上全面に蒸着層35を形成する工程と、p型クラッド層34上の蒸着層35上にメッキ電極層36を形成する工程と、メッキ電極層36の両端部をエッチングにより薄層化するとともに、蒸着層35を除去する工程とを有する。

【0032】

(a)具体的には、図2に示すように、n型半導体基板2を、例えば、有機金属気相成長(MOCVD:Metal Organic Chemical Vapor Deposition)装置内に入れ、反応ガスのトリエチルガリウム(TEG)、トリメチルアルミニウム(TMA)、トリメチルインジウム(TMI)、ホスフィン(PH3)、アルシン(AsH3)および半導体層の導電型に応じて、n型ドーパントガスとしてSi若しくはSe含有ガス、p型ドーパントとしてジメチル亜鉛(DMZn)若しくはBe含有ガスをキャリアガスの水素(H2)と共に導入し、500℃〜700℃程度で各半導体層(30,31,32,33,34)をエピタキシャル成長する。

【0033】

(b)次に、図2に示すように、フォトリソグラフィーとマスクパターニング工程によって、p型クラッド層34、活性層33およびn型クラッド層32をエッチングし、リッジ部を形成する。例えば、CVD法などにより、SiO2またはSiNxなどからなるマスクを形成し、例えば、ドライエッチングなどにより、p型クラッド層34、活性層33およびn型クラッド層32を、エッチングストップ層31が露出するまで選択的にエッチングすることにより、図2に示されるように、リッジ部がストライプ状に形成される。

【0034】

(c)次に、図2に示すように、半導体基板2上のエッチングストップ層31上およびp型クラッド層34上全面に蒸着層35を形成する。蒸着層35としては、Au層若しくはTi/Au層などを適用することができる。蒸着層35の厚さは、例えば、Au層の場合、約0.5μm程度である。

【0035】

(d)次に、図2に示すように、例えば、フォトリソグラフィーとマスクパターニング工程によって、レジスト層40をパターン形成し、このレジスト層40をマスクとして、p型クラッド層34上の蒸着層35上にメッキ電極層36を、電界メッキにより形成する。メッキ電極層36は、図2中の破線により模式的に示されるように、層構造に形成される。しかも、このように層構造に形成されるメッキ電極層36は、レジスト層40に接する部分近傍のメッキ電極層36が厚く形成され易いという傾向がある。これは、電界メッキ工程中において、メッキ電極層36に接するレジスト層40の表面に微弱な電流が流れ、メッキ電極層36も成長が促進されるためである。

【0036】

(e)次に、図3に示すように、レジスト層40を除去する。図7および図8に示すリッジ構造の左端部分及び右端部分のSEM写真例から明らかなように、メッキ電極層36の両端部の厚さは中央部の厚さに比べて厚い。中央部におけるメッキ電極層36の厚さは、例えば、約2.5μm程度である。メッキ電極層36の両端部の厚さと中央部の厚さの差は、例えば、0.3μm〜1.0μm程度である。

【0037】

(f)次に、図4に示すように、フォトリソグラフィーとマスクパターニング工程によって、レジスト層38をパターン形成する。

【0038】

(g)次に、図5に示すように、例えば、ウェットエッチングにより、メッキ電極層36

の両端部および蒸着層35を除去する。ウェットエッチングに使用するエッチング液としては、王水、ヨウ素水溶液などを適用することができる。メッキ電極層36は、蒸着層35に比べて金属原子の密度が低いため、同一のウェットエッチング工程によって、容易にエッチングされ易いため、メッキ電極層36の厚さは、蒸着層35の厚さの例えば、約5倍程度に形成する必要がある。

【0039】

(h)次に、図6に示すように、レジスト層38を除去することによって、両端部が薄層化されたメッキ電極層36を得ることができる。

【0040】

(i)次に、図1に示すように、研磨により半導体基板2を薄層化した後、半導体基板2の裏面に、Au/Ge/NiまたはTi/Auなどからなるn側電極14を形成する。

【0041】

第1の実施の形態に係る半導体発光素子のLDバー100の半導体ウェハ110上における配置構成は、図9に示すように表される。また、第1の実施の形態に係る半導体発光素子のLDバー100の平面パターン構成例は、図10(a)に示すように表され、図10(a)のの拡大図は、図10(b)に示すように表される。

【0042】

(j)次に、図9〜図10に示すように、レーザ共振器80の延伸方向Xと垂直なY方向にスクライブを入れ、ブレークを行うことにより、容易に安定した劈開面100a,100bを形成し、LDバー100を形成する。つまり、安定した共振器ミラーを作成することができる。上記のように劈開面を形成したLDバー100の内の1個の半導体発光素子のレーザ共振器80の拡大された模式的断面構造例が、図1に相当する。

【0043】

p側電極36を有するレーザ共振器80がX方向に延伸し、Y方向に複数個、並列に配置されて、1個のLDバー100を形成している。LDバー100の幅W1は、レーザ共振器80の長さに相当し、例えば約数10μm〜数100μm程度である。一方、LDバー100の長さW2は、約数100μm〜数10mm程度である。1個のLD素子のチップ幅は、約250μm程度であり、LDバー100上に隣接するLD素子の間隔は、約10μm〜100μm程度であり、望ましくは14μm〜30μm程度である。

【0044】

第1の実施の形態に係る半導体発光素子のマウント構造は、図11に示すように表される。すなわち、半導体レーザダイオード部50上にAuの蒸着層35を介して、両端部を薄層化したAuのメッキ電極層36が形成されている。このようなLD素子は、図11に示すように、サブマウント部54に対して、例えば、Au−Sn層52を介して、ダイボンディングされる。

【0045】

第1の実施の形態に係る半導体発光素子は、放熱性とダイボンディング強度を確保するために、両端部が中央部に比べて薄いメッキ電極層36を適用することによって、ダイボンディングの隙間が無くなる。このため、濡れ性に優れ、剥離強度が強化され、密着性が良好となる。このため、熱放散が良好となり、結果として、活性層33の動作温度が減少し、動作電流が減少するため、LD素子の寿命が延びる傾向が得られる。

【0046】

第1の実施の形態によれば、LD素子をステム若しくはサブマウントにダイボンディングする際に、ダイボンディングを阻害するメッキ電極層端部を取り除くことによって、安定したダイボンディングを行うことができ、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法を提供することができる。

【0047】

[第2の実施の形態]

(素子構造)

本発明の第2の実施の形態に係る半導体発光素子は、図12に示すように、半導体基板2と、半導体基板2上に配置された第1の第1導電型クラッド層32と、第1の第1導電型クラッド層32上に配置された第1活性層33と、第1活性層33上に配置された第1の第2導電型クラッド層34と、第1の第2導電型クラッド層34上に配置された第1蒸着層35aと、第1蒸着層35a上に配置された第1メッキ電極層36aと、半導体基板2上に配置された第2の第1導電型クラッド層42と、第2の第1導電型クラッド層42上に配置された第2活性層43と、第2活性層43上に配置された第2の第2導電型クラッド層44と、第2の第2導電型クラッド層44上に配置された第2蒸着層35bと、第2蒸着層35b上に配置された第2メッキ電極層36bと備える。

【0048】

第1メッキ電極層36aの両端部は中央部に比べ薄く、かつ第2メッキ電極層36bの両端部も中央部に比べ薄い。

【0049】

第2の実施の形態に係る半導体発光素子は、図12に示すように、素子分離部90って、互いに分離されている。

【0050】

また、半導体基板2と第1の第1導電型クラッド層32間には、第1導電型クラッド層30と、第1導電型クラッド層30上に配置されたエッチングストップ層31を備えている。すなわち、第1導電型クラッド層30および32内にエッチングストップ層31が形成されている。

【0051】

また、半導体基板2と第2の第1導電型クラッド層42間には、第1導電型クラッド層30と、第1導電型クラッド層30上に配置されたエッチングストップ層31を備えている。すなわち、第1導電型クラッド層30および42内にエッチングストップ層31が形成されている。

【0052】

また、第2の実施の形態に係る半導体発光素子は、2波長レーザ光を発生することができる。

【0053】

第1の第1導電型クラッド層32、第1活性層33、第1の第2導電型クラッド層34としては、例えば、赤外光である780nm波長発光用のAlGaAs系化合物半導体が適用可能であり、第2の第1導電型クラッド層42、第2活性層43、第2の第2導電型クラッド層44としては、例えば、赤色光である650nm波長発光用のInGaAlP系化合物半導体が適用可能である。

【0054】

これらの半導体材料を積層するための半導体基板2としては、GaAs基板が一般的に用いられるが、他の半導体でも適用可能である。

【0055】

また、半導体基板2の導電型は、LDを組み込むセットとの関係で、基板側に望まれる導電型のn型またはp型のいずれかが用いられ、この半導体基板2の導電型にしたがって、積層される半導体層の導電型も決定される。以下の具体例では、半導体基板2がn型の例で説明する。

【0056】

第2の実施の形態に係る半導体発光素子は、図12に示すように、半導体基板2と、半導体基板2上に配置されたn型クラッド層30と、n型クラッド層30上に配置されたエッチングストップ層31と、エッチングストップ層31上に配置されたn型クラッド層32と、n型クラッド層32上に配置された活性層33と、活性層33上に配置されたp型クラッド層34と、p型クラッド層34上に配置された蒸着層35aと、蒸着層35a上に配置されたメッキ電極層36aと、エッチングストップ層31上に配置されたn型クラッド層42と、n型クラッド層42上に配置された活性層43と、活性層43上に配置されたp型クラッド層44と、p型クラッド層44上に配置された蒸着層35bと、蒸着層35b上に配置されたメッキ電極層36bとを備える。

【0057】

半導体基板2の裏面には、n側電極14が形成される。また、蒸着層35aおよびメッキ電極層36aによって、p側電極15が形成され、同様に、蒸着層35bおよびメッキ電極層36bによっても、p側電極15が形成される。

【0058】

n型クラッド層30および32は、例えば、Alx1Ga1-x1As(0.3≦x1≦0.7、例えば、x1=0.5)からなる。n型クラッド層30および32には、例えば、Siを約2×1018cm-3程度ドープしている。

【0059】

エッチングストップ層31は、n型またはノンドープの、例えばIn0.49Ga0.51Pからなり、例えば、約0.01μm〜0.05μm程度に形成されている。

【0060】

n型クラッド層30、エッチングストップ層31およびn型クラッド層32の全体の厚さは、例えば、約2μm〜4μm程度に形成される。

【0061】

活性層33は、Aly1Ga1-y1As(0.05≦y1≦0.2、例えば、y1=0.15)のバルク構造またはAly2Ga1-y2As(0.01≦y2≦0.1、例えば、y2=0.05)からなるウェル層とAly3Ga1-y3As(0.2≦y3≦0.5、y2<y3、例えば、y3=0.3)からなるバリア層とのシングル量子井戸(SQW:Single Quantum Well)

若しくはマルチ量子井戸(MQW:Multi Quantum Well)構造によって、全体として、例えば、約0.01μm〜0.2μm程度に形成される。

【0062】

p型クラッド層34は、例えば、Alx2Ga1-x2As(0.3≦x2≦0.7、例えば、x2=0.5)からなり、例えば、約0.5μm〜4μm程度に形成される。p型クラッド層34内には、p型またはノンドープの、例えばIn0.49Ga0.51Pからなるエッチストップ層が、例えば、約0.01μm〜0.05μm程度に形成されていても良い。

【0063】

尚、活性層33とn型クラッド層32との間、活性層33とp型クラッド層34との間に光ガイド層を設ける構造、活性層33とn型クラッド層32との間にビーム拡大層を設ける構造など、他の半導体層がいずれかの層間に介在されていても良い。

【0064】

さらに、例えば、In0.49(Ga1-uAlu)0.51P(0.45≦u≦0.8、例えば、u=0.7)層によって、n型クラッド層42およびp型クラッド層44を形成することができ、In0.49(Ga1-v1Alv1)0.51P(0≦v1≦0.25、例えば、v1=0)/In0.49(Ga1-v2Alv2)0.51P(0.3≦v2≦0.7、例えば、v2=0.4)によるSQW構造若しくはMQW構造などによって、活性層43を形成する。

【0065】

尚、エッチングストップ層31は、In0.49Ga0.51Pに限定されるものではなく、例えば、In0.49(Ga0.8Al0.2)0.51Pなどを使用することもできる。

【0066】

n型クラッド層32、活性層33、p型クラッド層34としてAlGaAs系化合物半導体を適用し、n型クラッド層42、活性層43、p型クラッド層44として、InGaAlP系化合物半導体が適用する場合、InGaPによるエッチングストップ層31は、赤外用のAlGaAsによる活性層33よりもバンドギャップが大きいため、エッチングストップ層31による赤外光の吸収・損失は少ない。一方、AlGaAsにより形成されるn型クラッド層30は、赤色用のInGaAlPによる活性層43よりもバンドギャップが大きいため、n型クラッド層30による赤色光の吸収・損失は少ない。

【0067】

第2の実施の形態に係る半導体発光素子は、2波長のレーザ光を高輝度で得ることができる。

【0068】

第2の実施の形態に係る半導体発光素子のLDバー100の平面パターン構成例は、図13(a)に示すように表され、図13(a)の拡大図は、図13(b)に示すように表される。

【0069】

互いに隣接して、図12に示す2波長のレーザ光を発生する半導体発光素子が形成されている。

【0070】

第2の実施の形態においても製造工程は、赤外用のAlGaAs系化合物半導体層構造と赤色用のInGaAlP系半導体層構造を別々に形成する以外は、第1の実施の形態と同様である。

【0071】

両端部が薄層化されたメッキ電極層36a、36bを形成する工程も第1の実施の形態と同様である。

【0072】

また、第2の実施の形態に係る半導体発光素子のマウント構造も、第1の実施の形態と同様である。

【0073】

第2の実施の形態に係る半導体発光素子は、放熱性とダイボンディング強度を確保するために、両端部が中央部に比べて薄いメッキ電極層36a,36bを適用することによって、ダイボンディングの隙間が無くなる。このため、濡れ性に優れ、剥離強度が強化され、密着性が良好となる。このため、熱放散が良好となり、結果として、活性層33、43の動作温度が減少し、動作電流が減少するため、LD素子の寿命が延びる傾向が得られる。

【0074】

第2の実施の形態によれば、LD素子をステム若しくはサブマウントにダイボンディングする際に、ダイボンディングを阻害するメッキ電極層端部を取り除くことによって、安定したダイボンディングを行うことができ、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した2波長の半導体発光素子およびその製造方法を提供することができる。

【0075】

[第3の実施の形態]

(素子構造)

本発明の第3の実施の形態に係る半導体発光素子は、図14に示すように、半導体基板2と、半導体基板2上に配置され、複数の互いに分離されたn型クラッド層32と、複数の互いに分離されたn型クラッド層32上にそれぞれ配置され、互いに分離された複数の活性層33と、複数の活性層33上にそれぞれ配置され、互いに分離された複数のp型クラッド層34と、複数のp型クラッド層34上に配置され、互いに分離された複数の蒸着層35と、複数の蒸着層35上に配置され、互いに分離された複数のメッキ電極層36a,36b,36c,36dとを備える。

【0076】

複数のメッキ電極層36a,36b,36c,36dのそれぞれの両端部は中央部に比べ薄い。

【0077】

第3の実施の形態に係る半導体発光素子は、図14に示すように、素子分離部90って、互いに分離されている。

【0078】

また、半導体基板2と複数のn型クラッド層32間には、n型クラッド層30と、n型クラッド層30上に配置されたエッチングストップ層31を備えている。すなわち、n型クラッド層30および複数のn型クラッド層32内にエッチングストップ層31が形成されている。

【0079】

第3の実施の形態に係る半導体発光素子は、マルチビームのレーザ光を発生することができる。

【0080】

第3の実施の形態に係る半導体発光素子のLDバー100の平面パターン構成例は、図15(a)に示すように表され、図15(a)の拡大図は、図15(b)に示すように表される。

【0081】

互いに隣接して、図14に示すクワッドビームのレーザ光を発生する半導体発光素子が形成されている。

【0082】

第3の実施の形態に係る半導体発光素子は、このようにLDバー100上に配置されるLD素子の数をさらに増加させて、クワッドビーム以上のマルチビームのレーザ光を発生することもできる。

【0083】

第3の実施の形態に係る半導体発光素子においても第1の実施の形態と同様に、n型クラッド層32、活性層33、p型クラッド層34としては、例えば、赤外光である780nm波長発光用のAlGaAs系化合物半導体や、例えば、赤色光である650nm波長発光用のInGaAlP系化合物半導体が適用可能である。

【0084】

また、第3の実施の形態に係る半導体発光素子においても、半導体基板2、n型クラッド層30、エッチングストップ層31、n型クラッド層32、活性層33、p型クラッド層34は、第1の実施の形態と同様の構造で形成することができる。

【0085】

第3の実施の形態に係る半導体発光素子においては、両端部が薄層化されたメッキ電極層36a,36b,36c,36dを形成する工程も第1の実施の形態と同様である。

【0086】

また、第3の実施の形態に係る半導体発光素子のマウント構造も、第1の実施の形態と同様である。

【0087】

第3の実施の形態に係る半導体発光素子は、放熱性とダイボンディング強度を確保するために、両端部が中央部に比べて薄いメッキ電極層36a,36b,36c,36dを適用することによって、ダイボンディングの隙間が無くなる。このため、濡れ性に優れ、剥離強度が強化され、密着性が良好となる。このため、熱放散が良好となり、結果として、活性層33の動作温度が減少し、動作電流が減少するため、LD素子の寿命が延びる傾向が得られる。

【0088】

第3の実施の形態によれば、LD素子をステム若しくはサブマウントにダイボンディングする際に、ダイボンディングを阻害するメッキ電極層端部を取り除くことによって、安定したダイボンディングを行うことができ、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上したマルチビームの半導体発光素子およびその製造方法を提供することができる。

【0089】

[第4の実施の形態]

(素子構造)

本発明の第4の実施の形態に係る半導体発光素子は、図16に示すように、半導体基板2と、半導体基板2上に配置されたn型クラッド層32と、n型クラッド層32上に配置された活性層33と、活性層33上に配置されたp型クラッド層34と、p型クラッド層34上に配置されたキャップ層4と、p型クラッド層34およびキャップ層4の側壁部に配置された電流ブロック層5,6と、キャップ層4および電流ブロック層5,6上に配置されたコンタクト層1と、コンタクト層1上に配置された蒸着層35と、蒸着層35上に配置されたメッキ電極層36とを備える。

【0090】

メッキ電極層36の両端部は、図16に示すように、中央部に比べ薄い。

【0091】

n型クラッド層30および32は、例えば、Alx1Ga1-x1As(0.3≦x1≦0.7、例えば、x1=0.5)からなる。n型クラッド層30および32には、例えば、Siを約2×1018cm-3程度ドープしている。

【0092】

エッチングストップ層31は、n型またはノンドープの、例えばIn0.49Ga0.51Pからなり、例えば、約0.01μm〜0.05μm程度に形成されている。

【0093】

n型クラッド層30、エッチングストップ層31およびn型クラッド層32の全体の厚さは、例えば、約2μm〜4μm程度に形成される。

【0094】

活性層33は、Aly1Ga1-y1As(0.05≦y1≦0.2、例えば、y1=0.15)のバルク構造またはAly2Ga1-y2As(0.01≦y2≦0.1、例えば、y2=0.05)からなるウェル層とAly3Ga1-y3As(0.2≦y3≦0.5、y2<y3、例えば、y3=0.3)からなるバリア層とのシングル量子井戸(SQW:Single Quantum Well)

若しくはマルチ量子井戸(MQW:Multi Quantum Well)構造によって、全体として、例えば、約0.01μm〜0.2μm程度に形成される。

【0095】

p型クラッド層34は、例えば、Alx2Ga1-x2As(0.3≦x2≦0.7、例えば、x2=0.5)からなり、例えば、約0.5μm〜4μm程度に形成される。p型クラッド層34内には、p型またはノンドープの、例えばIn0.49Ga0.51Pからなるエッチストップ層(図示省略)が、例えば、約0.01μm〜0.05μm程度に形成されている。

【0096】

尚、活性層33とn型クラッド層32との間、活性層33とp型クラッド層34との間に光ガイド層を設ける構造、活性層33とn型クラッド層32との間にビーム拡大層を設ける構造など、他の半導体層がいずれかの層間に介在されていても良い。

【0097】

前述の例では、AlGaAs系化合物半導体の例であったが、InGaAlP系化合物で構成する場合には、例えば、In0.49(Ga1-uAlu)0.51P(0.45≦u≦0.8、例えば、u=0.7)層によって、n型クラッド層32およびp型クラッド層34を形成することができ、In0.49(Ga1-v1Alv1)0.51P(0≦v1≦0.25、例えば、v1=0)/In0.49(Ga1-v2Alv2)0.51P(0.3≦v2≦0.7、例えば、v2=0.4)によるSQW構造若しくはMQW構造などによって、活性層33を形成することができる。

【0098】

尚、エッチングストップ層31は、In0.49Ga0.51Pに限定されるものではなく、例えば、In0.49(Ga0.8Al0.2)0.51Pなどを使用することもできる。

【0099】

また、p型クラッド層34にリッジ部を形成するためのエッチングは以下の通りである。例えば、CVD法などにより、SiO2またはSiNxなどからなるマスクを形成し、例えば、ドライエッチングなどにより、キャップ層4を選択的にエッチングし、引き続きHClのようなエッチング液により、p型クラッド層34をエッチングすることにより、図16に示されるように、リッジ部がストライプ状に形成される。

【0100】

キャップ層4は、例えば、p型In0.49Ga0.51Pからなり、厚さは、例えば、約0.01μm〜0.05μm程度である。キャップ層4は、後の工程でコンタクト層1を形成する際に、半導体積層部の表面に酸化膜などが形成されて、汚れるのを防止するためのものである。GaAsなどの他の半導体層で形成されていても良い。また、表面の汚れさえ防止することできるのであれば、無くても良い。

【0101】

コンタクト層1は、キャップ層4および電流ブロック層5,6上に、例えば、p型GaAs層により、その厚さが0.05μm〜10μm程度に形成される。

【0102】

電流ブロック層5,6としては、AlGaAs、GaAs、INAlPなどを用いることができる。

【0103】

第4の実施の形態に係る半導体発光素子においても、図10と同様に、LDバー100上に配置されるLD素子の数を増加させて、クワッドビーム以上のマルチビームのレーザ光を発生することもできる。

【0104】

第4の実施の形態に係る半導体発光素子においても第1の実施の形態と同様に、n型クラッド層32、活性層33、p型クラッド層34としては、例えば、赤外光である780nm波長発光用のAlGaAs系化合物半導体や、例えば、赤色光である650nm波長発光用のInGaAlP系化合物半導体が適用可能である。

【0105】

第4の実施の形態に係る半導体発光素子においては、両端部が薄層化されたメッキ電極層36を形成する工程も第1の実施の形態と同様である。

【0106】

また、第4の実施の形態に係る半導体発光素子のマウント構造も、第1の実施の形態と同様である。

【0107】

第4の実施の形態に係る半導体発光素子は、放熱性とダイボンディング強度を確保するために、両端部が中央部に比べて薄いメッキ電極層36を適用することによって、ダイボンディングの隙間が無くなる。このため、濡れ性に優れ、剥離強度が強化され、密着性が良好となる。このため、熱放散が良好となり、結果として、活性層33の動作温度が減少し、動作電流が減少するため、LD素子の寿命が延びる傾向が得られる。

【0108】

第4の実施の形態によれば、LD素子をステム若しくはサブマウントにダイボンディングする際に、ダイボンディングを阻害するメッキ電極層端部を取り除くことによって、安定したダイボンディングを行うことができ、放熱性とダイボンディング強度を増大し、ダイボンディングの信頼性と歩留りの向上した半導体発光素子およびその製造方法を提供することができる。

【0109】

[その他の実施の形態]

上記のように、本発明は第1〜第4の実施の形態によって記載したが、この開示の一部をなす論述および図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0110】

本発明の第1〜第4の実施の形態に係る半導体発光素子として、主としてストライプ型LDを例に説明したが、その他の例としては、分布帰還型(DFB:Distributed Feedback)LD、分布ブラッグ反射型(DBR:Distributed Bragg Reflector)LD、面発光LDなどを構成しても良い。

【0111】

また、本発明の第1〜第4の実施の形態に係る半導体発光素子として、LED(Light Emitting Diode)を構成しても良い。

【0112】

既に述べた実施の形態の説明においては、活性層が、それぞれバリア層で挟まれた複数の井戸層を有するMQW構造である場合を示したが、活性層が1つの井戸層を有する構造であってもよい。

【0113】

このように、本発明はここでは記載していない様々な実施の形態などを含む。

【産業上の利用可能性】

【0114】

本発明の半導体発光素子は、2波長レーザ、クワッドビームレーザ、マルチビームレーザなどの半導体発光素子全般に適用可能であり、CD、DVD、DVD−ROM、データ書込み可能なCD−RW等のピックアップ用のLD素子、プリンター用のLD素子、光通信用のLD素子として適用可能である。

【図面の簡単な説明】

【0115】

【図1】本発明の第1の実施の形態に係る半導体発光素子の模式的鳥瞰構造図。

【図2】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図3】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図4】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図5】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図6】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明する模式的断面構造図。

【図7】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明するリッジ構造の左端部分のSEM写真例。

【図8】本発明の第1の実施の形態に係る半導体発光素子の製造方法の一工程を説明するリッジ構造の右端部分のSEM写真例。

【図9】本発明の第1の実施の形態に係る半導体発光素子のLDバーの半導体ウェハ上における配置構成例。

【図10】(a)本発明の第1の実施の形態に係る半導体発光素子のLDバーの平面パターン構成例、(b)(a)の拡大図。

【図11】本発明の第1の実施の形態に係る半導体発光素子のマウント構造の模式的断面構造図。

【図12】本発明の第2の実施の形態に係る半導体発光素子の模式的断面構造図。

【図13】(a)本発明の第2の実施の形態に係る半導体発光素子のLDバーの平面パターン構成例、(b)(a)の拡大図。

【図14】本発明の第3の実施の形態に係る半導体発光素子の模式的断面構造図。

【図15】(a)本発明の第3の実施の形態に係る半導体発光素子のLDバーの平面パターン構成例、(b)(a)の拡大図。

【図16】本発明の第4の実施の形態に係る半導体発光素子の模式的鳥瞰構造図。

【図17】従来の半導体発光素子のマウント工程を説明する模式的断面構造図。

【図18】従来の半導体発光素子のマウント構造の模式的断面構造図。

【符号の説明】

【0116】

1…コンタクト層

2…半導体基板

4…キャップ層

5,6…埋め込み層

14…n側電極

15…p側電極

31…エッチングストップ層

32、42…第1導電型(n型)クラッド層

33、43…活性層

34、44…第2導電型(p型)クラッド層

35,35a,35b…蒸着層

36、36a,36b,36c,36d…メッキ電極層

38、40…レジスト層

50…半導体レーザダイオード部

52…Au−Sn層

54…サブマウント部

56…空洞部

80…レーザ共振器

90…素子分離部

100…LDバー

100a,100b…劈開面

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上に配置された第1導電型クラッド層と、

前記第1導電型クラッド層上に配置された活性層と、

前記活性層上に配置された第2導電型クラッド層と、

前記第2導電型クラッド層上に配置された蒸着層と、

前記蒸着層上に配置されたメッキ電極層と

を備え、前記メッキ電極層の両端部は、前記メッキ電極層の中央部に比べ薄いことを特徴とする半導体発光素子。

【請求項2】

半導体基板と、

前記半導体基板上に配置された第1の第1導電型クラッド層と、

前記第1の第1導電型クラッド層上に配置された第1活性層と、

前記第1活性層上に配置された第1の第2導電型クラッド層と、

前記第1の第2導電型クラッド層上に配置された第1蒸着層と、

前記第1蒸着層上に配置された第1メッキ電極層と、

前記半導体基板上に配置された第2の第1導電型クラッド層と、

前記第2の第1導電型クラッド層上に配置された第2活性層と、

前記第2活性層上に配置された第2の第2導電型クラッド層と、

前記第2の第2導電型クラッド層上に配置された第2蒸着層と、

前記第2蒸着層上に配置された第2メッキ電極層と、

を備え、前記第1メッキ電極層の両端部は、前記第1メッキ電極層の中央部に比べ薄く、かつ前記第2メッキ電極層の両端部は、前記第2メッキ電極層の中央部に比べ薄いことを特徴とする半導体発光素子。

【請求項3】

前記半導体素子は、2波長レーザ光を発生することを特徴とする請求項2に記載の半導体発光素子。

【請求項4】

半導体基板と、

前記半導体基板上に配置され、複数の互いに分離された第1導電型クラッド層と、

前記複数の互いに分離された第1導電型クラッド層上にそれぞれ配置され、互いに分離された複数の活性層と、

前記複数の活性層上にそれぞれ配置され、互いに分離された複数の第2導電型クラッド層と、

前記複数の第2導電型クラッド層上に配置され、互いに分離された複数の蒸着層と、

前記複数の蒸着層上に配置され、互いに分離された複数のメッキ電極層と

を備え、前記複数のメッキ電極層の端部は前記複数のメッキ電極層の中央部に比べ薄いことを特徴とする半導体発光素子。

【請求項5】

前記半導体素子は、マルチビームのレーザ光を発生することを特徴とする請求項4に記載の半導体発光素子。

【請求項6】

半導体基板上に第1導電型クラッド層を形成する工程と、

前記第1導電型クラッド層上に活性層を形成する工程と、

前記活性層上に第2導電型クラッド層を形成する工程と、

前記第2導電型クラッド層、前記活性層および前記第1導電型クラッド層をエッチングする工程と、

前記半導体基板上および前記第2導電型クラッド層上全面に蒸着層を形成する工程と、

前記第2導電型クラッド層上の前記蒸着層上にメッキ電極層を形成する工程と、

前記メッキ電極層の両端部をエッチングにより薄層化するとともに、前記蒸着層を除去する工程と

を有することを特徴とする半導体発光素子の製造方法。

【請求項1】

半導体基板と、

前記半導体基板上に配置された第1導電型クラッド層と、

前記第1導電型クラッド層上に配置された活性層と、

前記活性層上に配置された第2導電型クラッド層と、

前記第2導電型クラッド層上に配置された蒸着層と、

前記蒸着層上に配置されたメッキ電極層と

を備え、前記メッキ電極層の両端部は、前記メッキ電極層の中央部に比べ薄いことを特徴とする半導体発光素子。

【請求項2】

半導体基板と、

前記半導体基板上に配置された第1の第1導電型クラッド層と、

前記第1の第1導電型クラッド層上に配置された第1活性層と、

前記第1活性層上に配置された第1の第2導電型クラッド層と、

前記第1の第2導電型クラッド層上に配置された第1蒸着層と、

前記第1蒸着層上に配置された第1メッキ電極層と、

前記半導体基板上に配置された第2の第1導電型クラッド層と、

前記第2の第1導電型クラッド層上に配置された第2活性層と、

前記第2活性層上に配置された第2の第2導電型クラッド層と、

前記第2の第2導電型クラッド層上に配置された第2蒸着層と、

前記第2蒸着層上に配置された第2メッキ電極層と、

を備え、前記第1メッキ電極層の両端部は、前記第1メッキ電極層の中央部に比べ薄く、かつ前記第2メッキ電極層の両端部は、前記第2メッキ電極層の中央部に比べ薄いことを特徴とする半導体発光素子。

【請求項3】

前記半導体素子は、2波長レーザ光を発生することを特徴とする請求項2に記載の半導体発光素子。

【請求項4】

半導体基板と、

前記半導体基板上に配置され、複数の互いに分離された第1導電型クラッド層と、

前記複数の互いに分離された第1導電型クラッド層上にそれぞれ配置され、互いに分離された複数の活性層と、

前記複数の活性層上にそれぞれ配置され、互いに分離された複数の第2導電型クラッド層と、

前記複数の第2導電型クラッド層上に配置され、互いに分離された複数の蒸着層と、

前記複数の蒸着層上に配置され、互いに分離された複数のメッキ電極層と

を備え、前記複数のメッキ電極層の端部は前記複数のメッキ電極層の中央部に比べ薄いことを特徴とする半導体発光素子。

【請求項5】

前記半導体素子は、マルチビームのレーザ光を発生することを特徴とする請求項4に記載の半導体発光素子。

【請求項6】

半導体基板上に第1導電型クラッド層を形成する工程と、

前記第1導電型クラッド層上に活性層を形成する工程と、

前記活性層上に第2導電型クラッド層を形成する工程と、

前記第2導電型クラッド層、前記活性層および前記第1導電型クラッド層をエッチングする工程と、

前記半導体基板上および前記第2導電型クラッド層上全面に蒸着層を形成する工程と、

前記第2導電型クラッド層上の前記蒸着層上にメッキ電極層を形成する工程と、

前記メッキ電極層の両端部をエッチングにより薄層化するとともに、前記蒸着層を除去する工程と

を有することを特徴とする半導体発光素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2010−147154(P2010−147154A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−321039(P2008−321039)

【出願日】平成20年12月17日(2008.12.17)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月17日(2008.12.17)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]