半導体発光素子及びその製造方法

【課題】 凹凸を有する基板上に形成する膜の表面が平坦になるまでの成長時間を短縮することが可能な半導体発光素子を提供する。

【解決手段】 コランダム構造のc面基板の表面に複数の凸部が形成されている。この表面に、Ga及びNを含むIII−V族半導体からなり、基板表面よりも平坦な下地膜が配置されている。下地膜の上に、Ga及びNを含む発光構造が配置されている。下地膜のa軸方向とのなす角度が15°未満の方向を第1方向とし、それと直交する方向を第2方向とする。凸部は、第1方向及び第2方向に規則的に配列している。凸部の各々は、m軸方向とのなす角度が15°未満の第1の辺と、a軸方向とのなす角度が15°未満の第2の辺とを有する。第1方向に隣り合う2つの凸部の相互に対向する第1の辺は平行であり、第2方向に隣り合う2つの凸部の相互に対向する第2の辺は平行である。対向する第2の辺のm軸方向の間隔は、対向する第1の辺のa軸方向の間隔よりも広い。

【解決手段】 コランダム構造のc面基板の表面に複数の凸部が形成されている。この表面に、Ga及びNを含むIII−V族半導体からなり、基板表面よりも平坦な下地膜が配置されている。下地膜の上に、Ga及びNを含む発光構造が配置されている。下地膜のa軸方向とのなす角度が15°未満の方向を第1方向とし、それと直交する方向を第2方向とする。凸部は、第1方向及び第2方向に規則的に配列している。凸部の各々は、m軸方向とのなす角度が15°未満の第1の辺と、a軸方向とのなす角度が15°未満の第2の辺とを有する。第1方向に隣り合う2つの凸部の相互に対向する第1の辺は平行であり、第2方向に隣り合う2つの凸部の相互に対向する第2の辺は平行である。対向する第2の辺のm軸方向の間隔は、対向する第1の辺のa軸方向の間隔よりも広い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、Ga及びNを発光層に含む半導体発光素子及びその製造方法に関する。

【背景技術】

【0002】

サファイア基板の表面に凹凸を付して、その上に半導体発光層を形成する技術が提案されている(特許文献1)。この凹凸は、半導体発光層に結晶欠陥を生じさせない形状にされている。発光層で発生した光が、凹凸で散乱または回折されることにより、外部量子効率を高めることができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003−318441号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

凹凸が付されたサファイア基板の上にGaN層を成長させると、凸部の上面から成長した膜と、凹部の底面から成長した膜とが融合することにより、平坦な表面を有する膜が得られる。平坦な表面を得るためには、凸部の上面から成長した膜と、凹部の底面から成長した膜とが融合し、平坦な状態になるまでGaN層を成長させなければならない。成長時間が十分でない場合には、GaN層の表面に凹凸が残ってしまう。

【0005】

本発明の目的は、凹凸を有する基板上に形成する膜の表面が平坦になるまでの成長時間を短縮することが可能な半導体発光素子及びその製造方法を提供することである。

【課題を解決するための手段】

【0006】

本発明の一観点によると、

c軸が厚さ方向を向くコランダム構造の結晶構造を持ち、表面に複数の凸部が形成された基板と、

前記基板の前記凸部が形成された表面の上に配置され、Ga及びNを含むIII−V族化合物半導体からなり、表面が前記基板の表面よりも平坦である下地膜と、

前記下地膜の上に形成され、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造と

を有し、

前記下地膜のa軸方向とのなす角度が15°未満の方向を第1の方向とし、前記第1の方向と直交する方向を第2の方向としたとき、

前記凸部は、前記第1の方向、及び第2の方向に規則的に配列しており、前記凸部の各々の平面形状は、四角形の4つの辺に整合する縁を持ち、該四角形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記第1の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第1の辺は相互に平行であり、前記第2の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第2の辺は相互に平行であり、相互に対向する前記第2の辺の前記m軸方向の間隔は、相互に対向する前記第1の辺の前記a軸方向の間隔よりも広い半導体発光素子が提供される。

【0007】

本発明の他の観点によると、

c軸が厚さ方向を向くコランダム構造の結晶構造を持つ基板の表層部を部分的にエッチングすることにより、前記表面をに複数の凸部を形成する工程と、

前記基板の前記凸部が形成された表面の上に、Ga及びNを含むIII−V族化合物半導体からなる下地膜を形成する工程と、

前記下地膜の上に、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造を形成する工程と

を有し、

前記下地膜のa軸方向とのなす角度が15°未満の方向を第1の方向とし、前記第1の方向と直交する方向を第2の方向としたとき、

前記凸部は、前記第1の方向、及び第2の方向に規則的に配列しており、前記凸部の各々の平面形状は、四角形の4つの辺に整合する縁を持ち、該四角形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記第1の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第1の辺は相互に平行であり、前記第2の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第2の辺は相互に平行であり、相互に対向する前記第2の辺の前記m軸方向の間隔は、相互に対向する前記第1の辺の前記a軸方向の間隔よりも広い半導体発光素子の製造方法が提供される。

【発明の効果】

【0008】

下地膜の上面が平坦になるまでの成長時間を短縮することができる。

【図面の簡単な説明】

【0009】

【図1】(1A)は、評価実験の対象となる試料の断面図であり、(1B)〜(1H)は、各試料の凹凸パターンの平面図である。

【図2】(2A)は、評価実験の対象となる試料の正規化外部量子効率の測定結果を示すグラフであり、(2B)は、試料の断面図である。

【図3】評価実験の対象となる試料のGaN層のピット数の測定結果を示すグラフである。

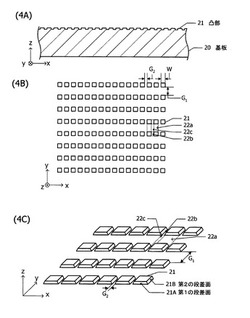

【図4】(4A)は、実施例1による半導体発光素子の基板の断面図であり、(4B)は、基板の平面図であり、(4C)は、基板の斜視図である。

【図5】実施例1による半導体発光素子のn型半導体層形成工程までの製造途中段階の素子の断面図である。

【図6】(6A)〜(6C)は、実施例1による半導体発光素子の製造途中段階の素子の断面図であり、(6D)は、半導体発光素子の断面図である。

【図7】比較例による方法でGaN層を形成する場合の基板及びGaN層の断面図である。

【図8】(8A)及び(8B)は、それぞれ実施例1の変形例1及び変形例2による半導体発光素子の基板の平面図である。

【図9】(9A)及び(9B)は、それぞれ実施例1の変形例3及び変形例4による半導体発光素子の基板の平面図である。

【図10】(10A)は、実施例2による半導体発光素子の基板の断面図であり、(10B)は、基板の平面図であり、(10C)は、基板の斜視図である。

【図11】(11A)及び(11B)は、それぞれ実施例2及び比較例による半導体発光素子の下地層の成長の様子を説明するための平面図である。

【図12】(12A)は、実施例3による半導体発光素子の基板の断面図であり、(12B)は、基板の平面図である。

【図13】実施例3による半導体発光素子の下地層形成工程までを示す製造途中段階の素子の断面図である。

【発明を実施するための形態】

【0010】

実施例について説明する前に、本願発明者らが行った評価実験、及びその結果について説明する。

【0011】

図1Aに示すように、表面に複数の凸部11が形成されたC面サファイア単結晶基板10の上に、GaN層12を、有機金属化学気相成長(MOCVD)を用いて成長させることにより、複数の試料を作製した。基板10を構成するサファイア単結晶はコランダム構造を有し、基板10の厚さ方向が、サファイア単結晶のc軸に平行になる。サファイア単結晶基板10のa軸方向をx軸、m軸方向をy軸、c軸方向をz軸とするxyz直交座標系を定義する。GaN膜12のa軸は、基板10のa軸から30°回転した方位を向く。このため、GaN膜12のa軸及びm軸は、それぞれy軸及びx軸に平行になる。

【0012】

図1B〜図1Hに、凸部11の形状及び分布を示す。図1B及び図1Cに示した試料では、凸部11の各々の平面形状が、一辺の長さが3μmの正三角形であり、1つの辺がx軸に平行である。図1Dに示した試料では、凸部11の各々の平面形状が、直径3μmの円形である。図1E及び図1Fに示した試料では、凸部11の平面形状が、一辺の長さが3μmの正方形である。図1Eに示した試料の凸部11の一辺は、y軸に平行であり、図1Fに示した凸部11の一辺は、x軸に対して45°傾いている。図1G及び図1Hに示した試料では、凸部11の各々の平面形状が正六角形であり、その外接円の直径が3μmである。図1Gに示した試料の凸部11の1つの辺はy軸に平行であり、図1Hに示した試料の凸部11の1つの辺はx軸に平行である。

【0013】

図1Bに示した試料では、1つの格子線がy軸に平行な正三角格子の格子点の位置に、凸部11が配置される。図1C、図1D、図1G、図1Hに示した試料では、1つの格子線がx軸に平行な正三角格子の格子点の位置に、凸部11が配置される。図1Eに示した試料では、1つの格子線がx軸に平行な正方格子の格子点の位置に、凸部11が配置される。図1Fに示した試料では、1つの格子線がx軸に対して45°傾いている正方格子の格子点の位置に、凸部11が配置される。いずれの試料においても、格子点の間隔は4.5μmである。

【0014】

図2Aに、各試料のGaN膜12の上に形成した発光ダイオードの外部量子効率の測定結果を示す。図2Bに、作製した発光ダイオードの断面図を示す。GaN膜の上に、n型GaN層13、発光層14、及びp型GaN層15が積層されている。n型GaN層13の上面の一部に、n側電極17が形成され、p型GaN層15の上に、p側電極16が形成されている。

【0015】

図2Aの横軸は、図1B〜図1Hに示した試料に対応する。縦軸は、平坦なサファイア基板上に形成した発光ダイオードの外部量子効率を1として正規化した外部量子効率を表す。図2Aの円形、正方形、三角形、及び菱形の記号は、それぞれ凸部11の高さが1.0μm、1.45μm、1.66μm、及び2.0μmの試料の上に形成した発光ダイオードの正規化外部量子効率を示す。

【0016】

凸部11の高さが2.0μm以外の試料では、平坦なサファイア基板上に形成した発光ダイオードよりも高い外部量子効率が得られていることがわかる。これは、サファイア基板10の表面に形成された凹凸が、素子内への光の閉じ込めを抑制しているためである。特に、図1Eに示した試料の上に発光ダイオードを形成した素子の外部量子効率が、他の試料に比べて高いことがわかる。

【0017】

図3に、各試料のGaN層12の表面を走査型プローブ顕微鏡(SPM)で観察し、転位(ピット)を計数した結果を示す。縦軸は、5μm×5μmの正方形の範囲内に検出されたピット数を表す。横軸は、各試料に対応する。試料「参照」は、平坦なサファイア基板上にGaN層を成長させたものである。試料「1B」〜「1H」は、それぞれ図1B〜図1Hに示した凸部11の形状及び配列を持つ試料に対応する。パターン寸法は、凸部11の各々の寸法を示す。パターン寸法は、図1B、図1C、図1E、図1Fの試料では、凸部11の一辺の長さに相当し、図1Dの試料では、凸部11の直径に相当し、図1G、図1Hの試料では、正六角形の外接円の直径に相当する。図3の周期は、凸部11の配列に対応する格子模様の格子点の間隔に相当する。

【0018】

図3に示した評価結果から、図1Eに示した試料のGaN層12のピット数が、他の試料のGaN層12のピット数に比べて少ないことがわかる。これは、結晶性の高いGaN層が形成されていることを意味する。

【0019】

図2A及び図3に示した評価結果からわかるように、サファイア基板の表面に形成する凸部11の平面形状を正方形にすることが好ましい。さらに、この正方形の1つの辺をx軸(サファイア基板のa軸)に平行にすることが好ましい。

[実施例1]

次に、図4A〜図6Dを参照して、実施例1による半導体発光素子ついて説明する。

【0020】

図4Aに、実施例1による半導体発光素子に用いられる基板20の断面図を示す。基板20には、C面サファイア単結晶基板が用いられる。サファイア単結晶は、コランダム構造を有する。基板20のa軸、m軸、及びc軸方向を、それぞれx軸、y軸、及びz軸とするxyz直交座標系を定義する。

【0021】

基板20の表面に、レジストパターンを形成し、基板20の表層部を部分的にエッチングすることにより、凹凸パターンを形成する。凹凸パターンは、複数の凸部21を含む。基板20のエッチングには、例えばBCl3、Cl2、及びArの誘導結合プラズマ(ICP)を用いた反応性イオンエッチング(RIE)を適用することができる。基板20をエッチングした後、レジストパターンを除去する。エッチングの深さは1μmとする。このため、凸部21の高さが1μmになる。レジストパターンに代えて、SiO2や金属等のハードマスクを用いてもよい。

【0022】

図4Bに、表面をエッチングした基板20の平面図を示す。凸部21が、x方向及びy方向に周期的に配列している。凸部21の各々の平面形状は、例えば一辺の長さがWの正方形である。なお、平面形状は、四角形であることが好ましく、例えば長方形にしてもよい。実施例1においては、一辺の長さWを3μmとした。y方向に並ぶ2つの凸部21の間隔G1は6μmであり、x方向に並ぶ2つの凸部21の間隔G2は2μmである。

【0023】

図4Cに、基板20の表面に形成された凹凸パターンの斜視図を示す。凸部21の各々は、正方形の上面と、上面の4つの縁に連続する4つの側面(段差面)を含む。4つの段差面は、xy面に対して傾斜している。傾斜角(段差面とxy面とのなす角度)は、基板20のエッチング条件に依存し、例えば30°〜85°である。

【0024】

1つの凸部21の4つの段差面は、x軸に平行な1対の第1の段差面21Aと、y軸に平行な1対の第2の段差面21Bとを含む。y方向に隣り合う2つの凸部21の間に、第1の段差面21Aを側面とする凹部(相対的に低い領域)22aが画定される。この凹部22aの底面の幅が、間隔G1に等しい。x方向に隣り合う2つの凸部21の間に、第2の段差面21Bを側面とする凹部(相対的に低い領域)22bが画定される。この凹部22bの底面の幅が、間隔G2に等しい。2つの凹部22aと2つの凹部22bとで囲まれた領域22cは、凹部22a、22bの底面と同じ高さを有する相対的に低い領域である。

【0025】

図5Aa及び図5Abに示すように、基板20の上に、GaNからなる厚さ30nmのバッファ層23をMOCVDにより形成する。図5Aaは、y軸に垂直な断面を示し、図5Abは、x軸に垂直な断面を示す。成膜条件は、例えば下記の通りである。

・基板温度 525℃

・トリメチルガリウム(TMG)供給量 10.4μmol/分

・アンモニア(NH3)供給量 3.3slm

バッファ層23は、凸部21の上面、及び凸部21の間の凹部の底面の上に形成される。バッファ層23を形成した後、1000℃で30秒間のアニールを行う。アニール雰囲気は、N2とH2との混合ガスとし、例えばN2流量を6slm、H2流量を12slmとする。

【0026】

図5Ba及び図5Bbに示すように、バッファ層23の上に、GaNからなる下地層24をMOCVDにより形成する。図5Baは、y軸に垂直な断面を示し、図5Bbは、x軸に垂直な断面を示す。下地層24は、第1の成膜条件と、第2の成膜条件とを交互に4回繰り返すことにより形成される。

【0027】

第1の成膜条件は下記の通りである。

・基板温度 1000℃

・TMG供給量 23μmol/分

・NH3供給量 2.2slm

・成膜厚さ 20nm

第2の成膜条件は下記の通りである。

・基板温度 1000℃

・TMG供給量 45μmol/分

・NH3供給量 4.4slm

・成膜厚さ 80nm

第1の成膜条件では、横方向の成長に比べて縦方向の成長が優先的に生じる。第2の成膜条件では、第1の成膜条件よりも、横方向成長が速くなる。第1の成長条件による成長と、第2の成長条件による成長とを4回繰り返すことにより、凸部21上に形成された下地層24と、凹部に形成された下地層24とが融合し始めた。このとき、凸部21の上に堆積した下地層24の厚さは約400nmである。なお、下地膜24の表面は、幾何学的に完全な平坦面であることまでは必要とされない。例えば、下地膜24の表面が、基板20の表面に比べて平坦であればよい。また、下地膜24の表面の高低差が、基板20の表面の高低差の1/2以下であれば、半導体発光素子の下地として、より好ましい。

【0028】

図5Ca及び図5Cbに示すように、下地層24の上に、n型GaNからなる厚さ3μmのn型半導体層25をMOCVDにより形成する。図5Caは、y軸に垂直な断面を示し、図5Cbは、x軸に垂直な断面を示す。n型不純物としてSiが用いられ、不純物濃度は5×1018cm−3である。成膜条件は下記の通りである。

・基板温度 1000℃

・TMG供給量 45μmol/分

・NH3供給量 5.5slm

・成膜時間 1時間

バッファ層23、下地層24、及びn型半導体層25は、ウルツ鉱(ウルツァイト)構造を持ち、そのa軸は、基板20のa軸に対して30°回転した方位を向く。このため、バッファ層23、下地層24、及びn型半導体層25のa軸はy軸に平行になり、m軸はx軸に平行になる。

【0029】

図6Aに示すように、n型半導体層25の上に、発光層26を形成する。発光層26は、例えば交互に積層された厚さ14nmのGaN層と厚さ2nmのIn0.3Ga0.7N層とを含む。積層の繰り返し回数は、例えば5回である。発光層26の成膜条件は下記の通りである。

・基板温度 730℃

・TMG供給量 3.6μmol/分

・トリメチルインジウム(TMI)供給量 10μmol/分

・NH3供給量 4.4slm

なお、GaN層の成膜時には、TMIの供給は停止される。

【0030】

発光層26の上に、p型AlGaNからなる厚さ40nmのp型半導体層27を形成する。p型不純物としてMgが用いられ、不純物濃度は1×1020cm−3である。成膜条件は下記の通りである。

・基板温度 870℃

・TMG供給量 8.1μmol/分

・トリメチルアルミニウム(TMA)供給量 7.56μmol/分

・NH3供給量 4.4slm

p型半導体層27の上に、p型GaNからなるp型半導体層28を形成する。p型半導体層28は、厚さが100nm、Mg濃度が2×1019cm−3の下層部分と、厚さが20nm、Mg濃度が2×1020cm−3の上層部分とを含む。成膜条件は下記の通りである。

・基板温度 870℃

・TMG供給量 18μmol/分

・NH3供給量 4.4slm

p型半導体層28を形成した後、900℃で1分の熱処理を行う。

【0031】

図6Bに示すように、p型半導体層28の表面から、n型半導体層25の厚さ方向の途中までエッチングを行うことにより、複数のメサ30を残す。メサ30の各々は、例えば一辺の長さが350μmの正方形のうち、1つの頂点近傍が、その頂点を中心とする扇形状に切り取られた平面形状を有する。扇形に切り取られた領域には、n型半導体層25が露出している。メサ30の高さは、例えば700nmである。

【0032】

図6Cに示すように、メサ30の上面に、インジウム錫酸化物(ITO)からなる透明電極31を形成する。透明電極31の厚さは、例えば200nmとする。正方形のメサから扇形に切り取られた領域に露出しているn型半導体層25の上に、n側電極32を形成する。n側電極32は、例えば厚さ1nmのTi膜と、その上に形成された厚さ1000nmのAl膜との2層構造を有する。

【0033】

透明電極31の一部の領域上に、p側パッド33を形成する。p側パッド33は、厚さ0.5nmのTi膜、厚さ100nmのRh膜、厚さ50nmのTi膜、及び厚さ1000nmのAu膜がこの順番に積層された積層構造を有する。なお、p側パッド33の一部が、p型半導体層28に直接接触するようにしてもよい。

【0034】

図6Dに示すように、基板20の背面に溝を形成した後、ダイシングすることにより、チップ40に分割する。チップ40の背面と端面との接続部分に、ダイシング用の溝に対応する斜面41が形成される。

【0035】

図7Aa〜図7Bbを参照して、比較例によるGaN層の形成方法について説明する。比較例では、実施例1の図4Bに示した凸部21に対応する凸部が、x方向及びy方向に等しい間隔で配列している。GaNのa軸方向の成長速度は、m軸方向の成長速度よりも速い。このため、図7Abに示したx軸に平行な段差面上に形成されるGaN膜50が、図7Aaに示したy軸に平行な段差面上に形成されるGaN膜50よりも厚い。

【0036】

図7Bbに示すように、y軸方向に隣り合う凸部の間が埋め込まれて、その部分のGaN膜の上面がほぼ平坦になったとき、図7Baに示すように、x軸方向に隣り合う凸部の間のGaN膜50の上面には、窪みが残った状態になる。この窪みが埋め込まれて平坦になるまでGaN膜50を形成することは、図7Bbに示した断面においては、GaN膜50上面が平坦になった後も、継続して成膜が行われることになる。

【0037】

実施例1では、図4Bに示したように、x方向に隣り合う凸部21の間隔G2を、y方向に隣り合う凸部21の間の間隔G1よりも狭くしている。このため、x方向に隣り合う凸部21の間の凹部22bにおいてGaN層の上面が平坦になるまでの成長時間が、y方向に隣り合う凸部21の間の凹部22aにおいてGaN層の表面が平坦になるまでの成長時間に近づく。これにより、GaN層の上面が平坦になるまでの成長時間を短縮することができる。

【0038】

相対的に低い領域22cにおいては、厚さ方向の成長と、領域22cに隣接する凹部22a、22bに形成されたGaN層からの横方向成長により、GaN層が形成される。

【0039】

凸部21のx方向及びy方向の間隔を共に6μmにしたとき、上述の第1の成膜条件による成膜と、第2の成膜条件による成膜とを12回繰り返した時点で、GaN層の上面が融合し始める。実施例1においては、4回の繰り返しで平坦な下地層24が得られている。このように、実施例1の方法により、比較例に比べて成膜時間を約1/3に短縮することができる。

【0040】

次に、実施例1の変形例について説明する。この変形例では、図4Bに示した間隔G2を6μmにし、間隔G1を18μmにした。この構造で下地層24を形成したところ、上述の第1の成膜条件による成膜と、第2の成膜条件による成膜とを12回繰り返すことにより、上面がほぼ平坦な下地層24が得られた。すなわち、上記比較例と対比すると、間隔G1を6μmから18μmに広げているにも関わらず、平坦な上面が得られるまでの成膜時間はほぼ同等であることがわかる。

【0041】

なお、厚さ方向の成長が優先的に生じる第1の成膜条件として、下記の条件を採用してもよい。

・TMG供給量 10〜30μmol/分

・NH3供給量 1〜3slm

・成膜厚さ 10〜60nm

また、第1の成膜条件よりも横方向成長の速度が速い第2の成膜条件として、下記の条件を採用してもよい。

・TMG供給量 30〜70μmol/分

・NH3供給量 3〜7slm

・成膜厚さ 30〜140nm

第2の成膜条件で成膜する厚さは、第1の成膜条件で成膜する厚さよりも厚くすることが好ましい。

【0042】

図4Bに示した間隔G2が、間隔G1に比べて狭くなりすぎると、広い間隔G1に対応する凹部22aが埋め込まれる前に、狭い間隔G2に対応する凹部22bが埋め込まれてしまう。狭い間隔G2の凹部22bが埋め込まれるのに必要な成長時間と、広い間隔G1の凹部22aが埋め込まれるのに必要な成長時間との差が小さいと、より効率的な埋込が可能になる。埋込効率を高めるために、広い間隔G1を狭い間隔G2の4.5倍以下にすることが好ましい。さらに、広い間隔G1を狭い間隔G2の1.5倍以上にすることが好ましい。

【0043】

実施例1では、凸部21の1つの辺を、x軸(基板20のa軸)に平行にした。この1つの辺と、x軸とは、完全に平行である必要はない。例えば、1つの辺が延在する方向と、x軸との角度のずれが±15°以下であれば、実質的に実施例1と同様の効果が得られる。さらに、他の1つの辺が延在する方向と、y軸との角度のずれが±15°以下であれば、実質的に実施例1と同様の効果が得られる。

【0044】

図8Aに、実施例1の変形例1による半導体発光素子の製造方法で用いられる基板20の平面図を示す。凸部21が、x軸方向及びy軸方向に規則的に配列している。凸部21の各々の平面形状は平行四辺形であるが、長方形及び正方形のいずれでもない。相互に対向する一対の辺21Xの各々と、x軸とのなす角度は15°以下であり、他の一対の辺21Yの各々と、y軸とのなす角度も15°以下である。

【0045】

y軸方向に隣り合う2つの凸部21の、相互に向かい合う辺21Xは平行であり、x軸方向に隣り合う2つの凸部21の、相互に向かい合う辺21Yも平行である。凸部21のy軸方向の間隔G1を、y軸方向に隣り合う2つの凸部21の相互に対向する辺21Xの、y軸方向の間隔と定義する。同様に、凸部21のx軸方向の間隔G2を、x軸方向に隣り合う2つの凸部21の相互に対向する辺21Yの、x軸方向の間隔と定義する。このとき、間隔G1を、間隔G2の1.5倍以上4.5倍以下とすることが好ましい。

【0046】

図8Bに、実施例1の変形例2による半導体発光素子の製造方法で用いられる基板20の平面図を示す。変形例2では、凸部21の各々の平面形状が台形である。台形の上底及び下底に対応する辺21Xはx軸に平行である。台形の斜辺に対応する辺21Yは、y軸に対して傾いており、y軸とのなす角度は15°以下である。

【0047】

x軸方向に隣り合う2つの凸部21は、一方の凸部21を180°回転させると、他方の凸部21に重なる位置関係を持つ。このため、x軸方向に隣り合う2つの凸部21の、相互に対向する辺21Yは平行になる。各凸部21の辺21Xは、x軸に平行でありため、y軸方向に隣り合う2つの凸部21の、相互に対向する辺21Xも平行になる。凸部21のy軸方向の間隔G1及びx軸方向の間隔G2の定義は、図8Aに示した変形例1の場合と同一である。

【0048】

変形例2においても、間隔G1を、間隔G2の1.5倍以上4.5倍以下とすることが好ましい。

【0049】

図9Aに、実施例1の変形例3による半導体発光素子の製造方法で用いられる基板20の平面図を示す。凸部21が、第1の方向80及び第2の方向81に規則的に配列している。第1の方向80は、x軸に対して傾斜しており、第1の方向80とx軸とのなす角度θは15°以下である。第2の方向81は、第1の方向80と直交する。

【0050】

凸部21の相互に対向するひと組の辺21Xは第1の方向80と平行であり、他のひと組の辺21Yは第2の方向81に平行である。このため、凸部21の各々の平面形状は、正方形または長方形になる。

【0051】

y軸方向に隣り合う2つの凸部21の間隔G1として、第2の方向81に隣り合う2つの凸部21のy軸方向に関する距離を採用する。同様に、x軸方向に隣り合う2つの凸部21の間隔G2として、第1の方向80に隣り合う2つの凸部21のx軸方向に関する距離を採用する。第1の方向80に関する距離及び第2の方向81に関する距離を採用しないのは、結晶成長が、第1の方向80及び第2の方向81に進むのではなく、x軸方向及びy軸方向に進むことによる。この変形例3においては、間隔G1を、間隔G2の1.5倍以上、かつ4.5倍以下とすることが好ましい。

【0052】

図9Bに、実施例1の変形例4による半導体発光素子の製造方法で用いられる基板20の平面図を示す。凸部21が、第1の方向80及び第2の方向81に規則的に配列している。第1の方向80及び第2の方向81は、図9Aに示した変形例3の場合と同一である。

【0053】

凸部21の相互に対向するひと組の辺21Xはx軸と平行であり、他のひと組の辺21Yはy軸と平行である。このため、凸部21の各々の平面形状は、正方形または長方形になる。図9Aに示した変形例3の場合と同様に、y軸方向に隣り合う2つの凸部21の間隔G1として、第2の方向81に隣り合う2つの凸部21のy軸方向に関する距離を採用し、x軸方向に隣り合う2つの凸部21の間隔G2として、第1の方向80に隣り合う2つの凸部21のx軸方向に関する距離を採用する。この変形例4においても、間隔G1を、間隔G2の1.5倍以上、かつ4.5倍以下とすることが好ましい。

【0054】

なお、上記実施例1、及び変形例1〜4において、間隔G1を間隔G2の3倍以下とすることがより好ましい。また、実施例1の変形例1〜4では、凸部21の辺がx軸及びy軸に対して傾いている構成、及び凸部21の配列方向はx軸及びy軸に対して傾いている構成を示した。これらの構成でも、図4Bに示した実施例1の構成に近い効果が得られるが、凸部21の各辺、及び凸部21の配列する方向を、x軸及びy軸に平行にすることが最も好ましい。

【0055】

実施例1では、基板20に、C面サファイア単結晶基板を用いたが、他のコランダム構造の結晶からなるC面基板を用いてもよい。また、基板上に形成する下地膜に、Ga及びNを含むIII−V族化合物半導体を用いてもよい。

[実施例2]

図10Aに、実施例2による半導体発光素子の製造方法で用いる基板20の断面図を示す。以下の説明では、実施例1との相違点に着目し、同一の構成については説明を省略する。基板20の表面に形成された凹凸パターンは、複数の凹部60を含む。

【0056】

図10Bに、基板20の平面図を示す。複数の凹部60が、x方向及びy方向に周期的に配列している。凹部60の各々の平面形状は、1つの辺がx軸に平行な長方形である。y軸に平行な辺の長さW1は、x軸に平行な辺の長さW2よりも短い。x方向に隣り合う凹部60の間隔、及びy方向に隣り合う凹部60の間隔は、共にGである。

【0057】

図10Cに、基板20に形成された凹凸パターンの斜視図を示す。凹部60の各々は、x方向に向かい合う一対の第1の段差面60A、y方向に向かい合う一対の第2の段差面60B、及び底面を有する。段差面60A、60Bは、xy面に対して傾斜している。傾斜角(段差面とxy面とのなす角度)は、基板20のエッチング条件に依存し、例えば30°〜85°である。

【0058】

図11Aに、基板20の上にGaN層を成長させたときの結晶成長の様子を示す。段差面60Aから凹部60の内側に向かってGaNのa軸方向の横方向成長が生じ、段差面60Bから凹部60の内側に向かってGaNのm軸方向の横方向成長が生じる。a軸方向の成長速度が、m軸方向の成長速度よりも速い。このため、凹部60の短辺の長さW1の1/2の長さのa軸方向の成長が生じると、凹部60内がGaN層で埋め込まれる。

【0059】

図11Bに、凹部60がy方向に長い例を示す。この場合にも、凹部60の長辺の長さW1の1/2の長さのa軸方向の成長が生じた時点で、凹部60内がGaN層で埋め込まれる。

【0060】

従って、凹部60の平面形状を凹部60のy方向の寸法を、x方向の寸法よりも短くすることにより、凹部60内をGaN層で埋め込むまでの成長時間を短縮することが可能になる。長辺の長さW2を短辺の長さW1の1.5倍〜4.5倍の範囲内にすることが好ましい。この範囲内にすることにより、成長時間短縮の有意な効果が期待できる。

【0061】

実施例2では、凹部60の1つの辺を、x軸(基板20のa軸)に平行にした。この1つの辺と、x軸とは、完全に平行である必要はない。例えば、1つの辺の延在する方向と、x軸との角度のずれが15°以下であれば、実質的に実施例2と同様の効果が得られる。また、他の辺の延在する方向と、y軸との角度のずれが15°以下であれば、必ずしもy軸に平行である必要はない。

【0062】

凹部60の辺がx軸及びy軸と平行ではない場合には、凹部60の平面形状が長方形になるとは限らない。この場合でも、相互に対向する辺は平行であることが好ましい。すなわち、凹部60の平面形状は平行四辺形であることが好ましい。このとき、図8Bに示したy軸方向の寸法W1として、x軸との角度のずれが15°以下のひと組の対辺のy軸方向に関する間隔を採用する。同様に、x軸方向の寸法W2として、y軸との角度のずれが15°以下のひと組の対辺のx軸方向に関する間隔を採用する。

【0063】

x軸方向の寸法W2を、y軸方向の寸法W1の1.5倍以上4.5倍以下とすることが好ましい。なお、図8Bに示したように、凹部60の辺を、x軸及びy軸に平行にすることが最も好ましく、寸法W2を寸法W1の3倍以下とすることがより好ましい。

【0064】

基板20の上に形成されたGaN層の上に、実施例1と同様の発光構造を形成することにより、半導体発光素子が得られる。凹部60が、光を屈折または散乱させることにより、外部量子効率を高めることができる。

[実施例3]

図12Aに、実施例3による半導体発光素子の製造方法で用いる基板70の断面図を示す。基板70には、C面GaN単結晶基板が用いられる。基板70の表面に、SiO2等の絶縁材料からなる複数のマスクパターン71が形成されている。基板70のm軸方向をx軸、a軸方向をy軸、c軸方向をz軸とするxyz直交座標系を定義する。

【0065】

図12Bに、マスクパターン71の平面図を示す。マスクパターン71の各々の平面形状は、1つの辺がx軸に平行な長方形である。x軸に平行な辺の長さをWx、y軸に平行な辺の長さをWyとする。

【0066】

図13A〜図13Cに、基板70の上にGaN層を成長させたときの断面図を時系列で示す。

【0067】

図13Aに示すように、基板70が露出した領域にGaN層75が形成される。マスクパターン71の上には、GaN層が成長しない。成長したGaN層75が、マスクパターン71の上面まで達すると、図13Bに示すように、マスクパターン71の縁から内側に向かって横方向の成長が始まる。横方向の成長が進むと、図13Cに示すように、マスクパターン71がGaN層75で完全に覆われる。

【0068】

このGaN層75を下地層として、その上に実施例1と同様の発光構造を形成することができる。マスクパターン71が、光を屈折及び散乱させることにより、外部量子効率を高めることができる。

【0069】

マスクパターン71の上方で生じるy方向(a軸方向)への横方向成長が、x方向(m軸方向)への横方向成長よりも速い。従って、マスクパターン71のy方向の寸法を、x方向の寸法よりも短くすることにより、マスクパターン71の上面を、より速くGaN層75で被覆することができる。

【0070】

マスクパターン71のx方向の寸法Wxを、y方向の寸法Wyの1.5倍〜4.5倍の範囲内とすることにより、GaN層の成膜時間を短縮する有意な効果が期待できる。

【0071】

実施例3では、マスクパターン71の1つの辺を、x軸(基板70のm軸)に平行にした。この1つの辺と、x軸とは、完全に平行である必要はない。例えば、1つの辺が延在する方向と、x軸との角度のずれが15°以下であれば、実質的に実施例3と同様の効果が得られる。また、他の辺が延在する方向と、y軸との角度のずれが15°以下であれば、必ずしもy軸に平行である必要はない。この場合、マスクパターン71の平面形状は平行四辺形であることが好ましい。このとき、図10Bに示したx軸方向の寸法Wxとして、y軸との角度のずれが15°以下のひと組の対辺のx軸方向に関する間隔を採用する。同様に、y軸方向の寸法Wyとして、x軸との角度のずれが15°以下のひと組の対辺のy軸方向に関する間隔を採用する。

【0072】

x軸方向の寸法Wxを、y軸方向の寸法Wyの1.5倍以上4.5倍以下とすることが好ましい。なお、図10Bに示したように、マスクパターン71の辺を、x軸及びy軸に平行にすることが最も好ましく、寸法Wxを寸法Wyの3倍以下とすることがより好ましい。

【0073】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0074】

10 サファイア基板

11 凸部

12 GaN層

13 n型GaN層

14 発光層

15 p型GaN層

16 p側電極

17 n側電極

20 基板

21 凸部

21A 第1の段差面

21B 第2の段差面

21X、21Y 辺

23 バッファ層

24 下地層

25 n型半導体層

26 発光層

27、28 p型半導体層

30 メサ

31 透明電極

32 n側電極

33 p側パッド

40 半導体発光素子のチップ

41 斜面

50 GaN層

60 凹部

70 基板

71 マスクパターン

75 GaN層

【技術分野】

【0001】

本発明は、Ga及びNを発光層に含む半導体発光素子及びその製造方法に関する。

【背景技術】

【0002】

サファイア基板の表面に凹凸を付して、その上に半導体発光層を形成する技術が提案されている(特許文献1)。この凹凸は、半導体発光層に結晶欠陥を生じさせない形状にされている。発光層で発生した光が、凹凸で散乱または回折されることにより、外部量子効率を高めることができる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003−318441号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

凹凸が付されたサファイア基板の上にGaN層を成長させると、凸部の上面から成長した膜と、凹部の底面から成長した膜とが融合することにより、平坦な表面を有する膜が得られる。平坦な表面を得るためには、凸部の上面から成長した膜と、凹部の底面から成長した膜とが融合し、平坦な状態になるまでGaN層を成長させなければならない。成長時間が十分でない場合には、GaN層の表面に凹凸が残ってしまう。

【0005】

本発明の目的は、凹凸を有する基板上に形成する膜の表面が平坦になるまでの成長時間を短縮することが可能な半導体発光素子及びその製造方法を提供することである。

【課題を解決するための手段】

【0006】

本発明の一観点によると、

c軸が厚さ方向を向くコランダム構造の結晶構造を持ち、表面に複数の凸部が形成された基板と、

前記基板の前記凸部が形成された表面の上に配置され、Ga及びNを含むIII−V族化合物半導体からなり、表面が前記基板の表面よりも平坦である下地膜と、

前記下地膜の上に形成され、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造と

を有し、

前記下地膜のa軸方向とのなす角度が15°未満の方向を第1の方向とし、前記第1の方向と直交する方向を第2の方向としたとき、

前記凸部は、前記第1の方向、及び第2の方向に規則的に配列しており、前記凸部の各々の平面形状は、四角形の4つの辺に整合する縁を持ち、該四角形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記第1の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第1の辺は相互に平行であり、前記第2の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第2の辺は相互に平行であり、相互に対向する前記第2の辺の前記m軸方向の間隔は、相互に対向する前記第1の辺の前記a軸方向の間隔よりも広い半導体発光素子が提供される。

【0007】

本発明の他の観点によると、

c軸が厚さ方向を向くコランダム構造の結晶構造を持つ基板の表層部を部分的にエッチングすることにより、前記表面をに複数の凸部を形成する工程と、

前記基板の前記凸部が形成された表面の上に、Ga及びNを含むIII−V族化合物半導体からなる下地膜を形成する工程と、

前記下地膜の上に、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造を形成する工程と

を有し、

前記下地膜のa軸方向とのなす角度が15°未満の方向を第1の方向とし、前記第1の方向と直交する方向を第2の方向としたとき、

前記凸部は、前記第1の方向、及び第2の方向に規則的に配列しており、前記凸部の各々の平面形状は、四角形の4つの辺に整合する縁を持ち、該四角形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記第1の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第1の辺は相互に平行であり、前記第2の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第2の辺は相互に平行であり、相互に対向する前記第2の辺の前記m軸方向の間隔は、相互に対向する前記第1の辺の前記a軸方向の間隔よりも広い半導体発光素子の製造方法が提供される。

【発明の効果】

【0008】

下地膜の上面が平坦になるまでの成長時間を短縮することができる。

【図面の簡単な説明】

【0009】

【図1】(1A)は、評価実験の対象となる試料の断面図であり、(1B)〜(1H)は、各試料の凹凸パターンの平面図である。

【図2】(2A)は、評価実験の対象となる試料の正規化外部量子効率の測定結果を示すグラフであり、(2B)は、試料の断面図である。

【図3】評価実験の対象となる試料のGaN層のピット数の測定結果を示すグラフである。

【図4】(4A)は、実施例1による半導体発光素子の基板の断面図であり、(4B)は、基板の平面図であり、(4C)は、基板の斜視図である。

【図5】実施例1による半導体発光素子のn型半導体層形成工程までの製造途中段階の素子の断面図である。

【図6】(6A)〜(6C)は、実施例1による半導体発光素子の製造途中段階の素子の断面図であり、(6D)は、半導体発光素子の断面図である。

【図7】比較例による方法でGaN層を形成する場合の基板及びGaN層の断面図である。

【図8】(8A)及び(8B)は、それぞれ実施例1の変形例1及び変形例2による半導体発光素子の基板の平面図である。

【図9】(9A)及び(9B)は、それぞれ実施例1の変形例3及び変形例4による半導体発光素子の基板の平面図である。

【図10】(10A)は、実施例2による半導体発光素子の基板の断面図であり、(10B)は、基板の平面図であり、(10C)は、基板の斜視図である。

【図11】(11A)及び(11B)は、それぞれ実施例2及び比較例による半導体発光素子の下地層の成長の様子を説明するための平面図である。

【図12】(12A)は、実施例3による半導体発光素子の基板の断面図であり、(12B)は、基板の平面図である。

【図13】実施例3による半導体発光素子の下地層形成工程までを示す製造途中段階の素子の断面図である。

【発明を実施するための形態】

【0010】

実施例について説明する前に、本願発明者らが行った評価実験、及びその結果について説明する。

【0011】

図1Aに示すように、表面に複数の凸部11が形成されたC面サファイア単結晶基板10の上に、GaN層12を、有機金属化学気相成長(MOCVD)を用いて成長させることにより、複数の試料を作製した。基板10を構成するサファイア単結晶はコランダム構造を有し、基板10の厚さ方向が、サファイア単結晶のc軸に平行になる。サファイア単結晶基板10のa軸方向をx軸、m軸方向をy軸、c軸方向をz軸とするxyz直交座標系を定義する。GaN膜12のa軸は、基板10のa軸から30°回転した方位を向く。このため、GaN膜12のa軸及びm軸は、それぞれy軸及びx軸に平行になる。

【0012】

図1B〜図1Hに、凸部11の形状及び分布を示す。図1B及び図1Cに示した試料では、凸部11の各々の平面形状が、一辺の長さが3μmの正三角形であり、1つの辺がx軸に平行である。図1Dに示した試料では、凸部11の各々の平面形状が、直径3μmの円形である。図1E及び図1Fに示した試料では、凸部11の平面形状が、一辺の長さが3μmの正方形である。図1Eに示した試料の凸部11の一辺は、y軸に平行であり、図1Fに示した凸部11の一辺は、x軸に対して45°傾いている。図1G及び図1Hに示した試料では、凸部11の各々の平面形状が正六角形であり、その外接円の直径が3μmである。図1Gに示した試料の凸部11の1つの辺はy軸に平行であり、図1Hに示した試料の凸部11の1つの辺はx軸に平行である。

【0013】

図1Bに示した試料では、1つの格子線がy軸に平行な正三角格子の格子点の位置に、凸部11が配置される。図1C、図1D、図1G、図1Hに示した試料では、1つの格子線がx軸に平行な正三角格子の格子点の位置に、凸部11が配置される。図1Eに示した試料では、1つの格子線がx軸に平行な正方格子の格子点の位置に、凸部11が配置される。図1Fに示した試料では、1つの格子線がx軸に対して45°傾いている正方格子の格子点の位置に、凸部11が配置される。いずれの試料においても、格子点の間隔は4.5μmである。

【0014】

図2Aに、各試料のGaN膜12の上に形成した発光ダイオードの外部量子効率の測定結果を示す。図2Bに、作製した発光ダイオードの断面図を示す。GaN膜の上に、n型GaN層13、発光層14、及びp型GaN層15が積層されている。n型GaN層13の上面の一部に、n側電極17が形成され、p型GaN層15の上に、p側電極16が形成されている。

【0015】

図2Aの横軸は、図1B〜図1Hに示した試料に対応する。縦軸は、平坦なサファイア基板上に形成した発光ダイオードの外部量子効率を1として正規化した外部量子効率を表す。図2Aの円形、正方形、三角形、及び菱形の記号は、それぞれ凸部11の高さが1.0μm、1.45μm、1.66μm、及び2.0μmの試料の上に形成した発光ダイオードの正規化外部量子効率を示す。

【0016】

凸部11の高さが2.0μm以外の試料では、平坦なサファイア基板上に形成した発光ダイオードよりも高い外部量子効率が得られていることがわかる。これは、サファイア基板10の表面に形成された凹凸が、素子内への光の閉じ込めを抑制しているためである。特に、図1Eに示した試料の上に発光ダイオードを形成した素子の外部量子効率が、他の試料に比べて高いことがわかる。

【0017】

図3に、各試料のGaN層12の表面を走査型プローブ顕微鏡(SPM)で観察し、転位(ピット)を計数した結果を示す。縦軸は、5μm×5μmの正方形の範囲内に検出されたピット数を表す。横軸は、各試料に対応する。試料「参照」は、平坦なサファイア基板上にGaN層を成長させたものである。試料「1B」〜「1H」は、それぞれ図1B〜図1Hに示した凸部11の形状及び配列を持つ試料に対応する。パターン寸法は、凸部11の各々の寸法を示す。パターン寸法は、図1B、図1C、図1E、図1Fの試料では、凸部11の一辺の長さに相当し、図1Dの試料では、凸部11の直径に相当し、図1G、図1Hの試料では、正六角形の外接円の直径に相当する。図3の周期は、凸部11の配列に対応する格子模様の格子点の間隔に相当する。

【0018】

図3に示した評価結果から、図1Eに示した試料のGaN層12のピット数が、他の試料のGaN層12のピット数に比べて少ないことがわかる。これは、結晶性の高いGaN層が形成されていることを意味する。

【0019】

図2A及び図3に示した評価結果からわかるように、サファイア基板の表面に形成する凸部11の平面形状を正方形にすることが好ましい。さらに、この正方形の1つの辺をx軸(サファイア基板のa軸)に平行にすることが好ましい。

[実施例1]

次に、図4A〜図6Dを参照して、実施例1による半導体発光素子ついて説明する。

【0020】

図4Aに、実施例1による半導体発光素子に用いられる基板20の断面図を示す。基板20には、C面サファイア単結晶基板が用いられる。サファイア単結晶は、コランダム構造を有する。基板20のa軸、m軸、及びc軸方向を、それぞれx軸、y軸、及びz軸とするxyz直交座標系を定義する。

【0021】

基板20の表面に、レジストパターンを形成し、基板20の表層部を部分的にエッチングすることにより、凹凸パターンを形成する。凹凸パターンは、複数の凸部21を含む。基板20のエッチングには、例えばBCl3、Cl2、及びArの誘導結合プラズマ(ICP)を用いた反応性イオンエッチング(RIE)を適用することができる。基板20をエッチングした後、レジストパターンを除去する。エッチングの深さは1μmとする。このため、凸部21の高さが1μmになる。レジストパターンに代えて、SiO2や金属等のハードマスクを用いてもよい。

【0022】

図4Bに、表面をエッチングした基板20の平面図を示す。凸部21が、x方向及びy方向に周期的に配列している。凸部21の各々の平面形状は、例えば一辺の長さがWの正方形である。なお、平面形状は、四角形であることが好ましく、例えば長方形にしてもよい。実施例1においては、一辺の長さWを3μmとした。y方向に並ぶ2つの凸部21の間隔G1は6μmであり、x方向に並ぶ2つの凸部21の間隔G2は2μmである。

【0023】

図4Cに、基板20の表面に形成された凹凸パターンの斜視図を示す。凸部21の各々は、正方形の上面と、上面の4つの縁に連続する4つの側面(段差面)を含む。4つの段差面は、xy面に対して傾斜している。傾斜角(段差面とxy面とのなす角度)は、基板20のエッチング条件に依存し、例えば30°〜85°である。

【0024】

1つの凸部21の4つの段差面は、x軸に平行な1対の第1の段差面21Aと、y軸に平行な1対の第2の段差面21Bとを含む。y方向に隣り合う2つの凸部21の間に、第1の段差面21Aを側面とする凹部(相対的に低い領域)22aが画定される。この凹部22aの底面の幅が、間隔G1に等しい。x方向に隣り合う2つの凸部21の間に、第2の段差面21Bを側面とする凹部(相対的に低い領域)22bが画定される。この凹部22bの底面の幅が、間隔G2に等しい。2つの凹部22aと2つの凹部22bとで囲まれた領域22cは、凹部22a、22bの底面と同じ高さを有する相対的に低い領域である。

【0025】

図5Aa及び図5Abに示すように、基板20の上に、GaNからなる厚さ30nmのバッファ層23をMOCVDにより形成する。図5Aaは、y軸に垂直な断面を示し、図5Abは、x軸に垂直な断面を示す。成膜条件は、例えば下記の通りである。

・基板温度 525℃

・トリメチルガリウム(TMG)供給量 10.4μmol/分

・アンモニア(NH3)供給量 3.3slm

バッファ層23は、凸部21の上面、及び凸部21の間の凹部の底面の上に形成される。バッファ層23を形成した後、1000℃で30秒間のアニールを行う。アニール雰囲気は、N2とH2との混合ガスとし、例えばN2流量を6slm、H2流量を12slmとする。

【0026】

図5Ba及び図5Bbに示すように、バッファ層23の上に、GaNからなる下地層24をMOCVDにより形成する。図5Baは、y軸に垂直な断面を示し、図5Bbは、x軸に垂直な断面を示す。下地層24は、第1の成膜条件と、第2の成膜条件とを交互に4回繰り返すことにより形成される。

【0027】

第1の成膜条件は下記の通りである。

・基板温度 1000℃

・TMG供給量 23μmol/分

・NH3供給量 2.2slm

・成膜厚さ 20nm

第2の成膜条件は下記の通りである。

・基板温度 1000℃

・TMG供給量 45μmol/分

・NH3供給量 4.4slm

・成膜厚さ 80nm

第1の成膜条件では、横方向の成長に比べて縦方向の成長が優先的に生じる。第2の成膜条件では、第1の成膜条件よりも、横方向成長が速くなる。第1の成長条件による成長と、第2の成長条件による成長とを4回繰り返すことにより、凸部21上に形成された下地層24と、凹部に形成された下地層24とが融合し始めた。このとき、凸部21の上に堆積した下地層24の厚さは約400nmである。なお、下地膜24の表面は、幾何学的に完全な平坦面であることまでは必要とされない。例えば、下地膜24の表面が、基板20の表面に比べて平坦であればよい。また、下地膜24の表面の高低差が、基板20の表面の高低差の1/2以下であれば、半導体発光素子の下地として、より好ましい。

【0028】

図5Ca及び図5Cbに示すように、下地層24の上に、n型GaNからなる厚さ3μmのn型半導体層25をMOCVDにより形成する。図5Caは、y軸に垂直な断面を示し、図5Cbは、x軸に垂直な断面を示す。n型不純物としてSiが用いられ、不純物濃度は5×1018cm−3である。成膜条件は下記の通りである。

・基板温度 1000℃

・TMG供給量 45μmol/分

・NH3供給量 5.5slm

・成膜時間 1時間

バッファ層23、下地層24、及びn型半導体層25は、ウルツ鉱(ウルツァイト)構造を持ち、そのa軸は、基板20のa軸に対して30°回転した方位を向く。このため、バッファ層23、下地層24、及びn型半導体層25のa軸はy軸に平行になり、m軸はx軸に平行になる。

【0029】

図6Aに示すように、n型半導体層25の上に、発光層26を形成する。発光層26は、例えば交互に積層された厚さ14nmのGaN層と厚さ2nmのIn0.3Ga0.7N層とを含む。積層の繰り返し回数は、例えば5回である。発光層26の成膜条件は下記の通りである。

・基板温度 730℃

・TMG供給量 3.6μmol/分

・トリメチルインジウム(TMI)供給量 10μmol/分

・NH3供給量 4.4slm

なお、GaN層の成膜時には、TMIの供給は停止される。

【0030】

発光層26の上に、p型AlGaNからなる厚さ40nmのp型半導体層27を形成する。p型不純物としてMgが用いられ、不純物濃度は1×1020cm−3である。成膜条件は下記の通りである。

・基板温度 870℃

・TMG供給量 8.1μmol/分

・トリメチルアルミニウム(TMA)供給量 7.56μmol/分

・NH3供給量 4.4slm

p型半導体層27の上に、p型GaNからなるp型半導体層28を形成する。p型半導体層28は、厚さが100nm、Mg濃度が2×1019cm−3の下層部分と、厚さが20nm、Mg濃度が2×1020cm−3の上層部分とを含む。成膜条件は下記の通りである。

・基板温度 870℃

・TMG供給量 18μmol/分

・NH3供給量 4.4slm

p型半導体層28を形成した後、900℃で1分の熱処理を行う。

【0031】

図6Bに示すように、p型半導体層28の表面から、n型半導体層25の厚さ方向の途中までエッチングを行うことにより、複数のメサ30を残す。メサ30の各々は、例えば一辺の長さが350μmの正方形のうち、1つの頂点近傍が、その頂点を中心とする扇形状に切り取られた平面形状を有する。扇形に切り取られた領域には、n型半導体層25が露出している。メサ30の高さは、例えば700nmである。

【0032】

図6Cに示すように、メサ30の上面に、インジウム錫酸化物(ITO)からなる透明電極31を形成する。透明電極31の厚さは、例えば200nmとする。正方形のメサから扇形に切り取られた領域に露出しているn型半導体層25の上に、n側電極32を形成する。n側電極32は、例えば厚さ1nmのTi膜と、その上に形成された厚さ1000nmのAl膜との2層構造を有する。

【0033】

透明電極31の一部の領域上に、p側パッド33を形成する。p側パッド33は、厚さ0.5nmのTi膜、厚さ100nmのRh膜、厚さ50nmのTi膜、及び厚さ1000nmのAu膜がこの順番に積層された積層構造を有する。なお、p側パッド33の一部が、p型半導体層28に直接接触するようにしてもよい。

【0034】

図6Dに示すように、基板20の背面に溝を形成した後、ダイシングすることにより、チップ40に分割する。チップ40の背面と端面との接続部分に、ダイシング用の溝に対応する斜面41が形成される。

【0035】

図7Aa〜図7Bbを参照して、比較例によるGaN層の形成方法について説明する。比較例では、実施例1の図4Bに示した凸部21に対応する凸部が、x方向及びy方向に等しい間隔で配列している。GaNのa軸方向の成長速度は、m軸方向の成長速度よりも速い。このため、図7Abに示したx軸に平行な段差面上に形成されるGaN膜50が、図7Aaに示したy軸に平行な段差面上に形成されるGaN膜50よりも厚い。

【0036】

図7Bbに示すように、y軸方向に隣り合う凸部の間が埋め込まれて、その部分のGaN膜の上面がほぼ平坦になったとき、図7Baに示すように、x軸方向に隣り合う凸部の間のGaN膜50の上面には、窪みが残った状態になる。この窪みが埋め込まれて平坦になるまでGaN膜50を形成することは、図7Bbに示した断面においては、GaN膜50上面が平坦になった後も、継続して成膜が行われることになる。

【0037】

実施例1では、図4Bに示したように、x方向に隣り合う凸部21の間隔G2を、y方向に隣り合う凸部21の間の間隔G1よりも狭くしている。このため、x方向に隣り合う凸部21の間の凹部22bにおいてGaN層の上面が平坦になるまでの成長時間が、y方向に隣り合う凸部21の間の凹部22aにおいてGaN層の表面が平坦になるまでの成長時間に近づく。これにより、GaN層の上面が平坦になるまでの成長時間を短縮することができる。

【0038】

相対的に低い領域22cにおいては、厚さ方向の成長と、領域22cに隣接する凹部22a、22bに形成されたGaN層からの横方向成長により、GaN層が形成される。

【0039】

凸部21のx方向及びy方向の間隔を共に6μmにしたとき、上述の第1の成膜条件による成膜と、第2の成膜条件による成膜とを12回繰り返した時点で、GaN層の上面が融合し始める。実施例1においては、4回の繰り返しで平坦な下地層24が得られている。このように、実施例1の方法により、比較例に比べて成膜時間を約1/3に短縮することができる。

【0040】

次に、実施例1の変形例について説明する。この変形例では、図4Bに示した間隔G2を6μmにし、間隔G1を18μmにした。この構造で下地層24を形成したところ、上述の第1の成膜条件による成膜と、第2の成膜条件による成膜とを12回繰り返すことにより、上面がほぼ平坦な下地層24が得られた。すなわち、上記比較例と対比すると、間隔G1を6μmから18μmに広げているにも関わらず、平坦な上面が得られるまでの成膜時間はほぼ同等であることがわかる。

【0041】

なお、厚さ方向の成長が優先的に生じる第1の成膜条件として、下記の条件を採用してもよい。

・TMG供給量 10〜30μmol/分

・NH3供給量 1〜3slm

・成膜厚さ 10〜60nm

また、第1の成膜条件よりも横方向成長の速度が速い第2の成膜条件として、下記の条件を採用してもよい。

・TMG供給量 30〜70μmol/分

・NH3供給量 3〜7slm

・成膜厚さ 30〜140nm

第2の成膜条件で成膜する厚さは、第1の成膜条件で成膜する厚さよりも厚くすることが好ましい。

【0042】

図4Bに示した間隔G2が、間隔G1に比べて狭くなりすぎると、広い間隔G1に対応する凹部22aが埋め込まれる前に、狭い間隔G2に対応する凹部22bが埋め込まれてしまう。狭い間隔G2の凹部22bが埋め込まれるのに必要な成長時間と、広い間隔G1の凹部22aが埋め込まれるのに必要な成長時間との差が小さいと、より効率的な埋込が可能になる。埋込効率を高めるために、広い間隔G1を狭い間隔G2の4.5倍以下にすることが好ましい。さらに、広い間隔G1を狭い間隔G2の1.5倍以上にすることが好ましい。

【0043】

実施例1では、凸部21の1つの辺を、x軸(基板20のa軸)に平行にした。この1つの辺と、x軸とは、完全に平行である必要はない。例えば、1つの辺が延在する方向と、x軸との角度のずれが±15°以下であれば、実質的に実施例1と同様の効果が得られる。さらに、他の1つの辺が延在する方向と、y軸との角度のずれが±15°以下であれば、実質的に実施例1と同様の効果が得られる。

【0044】

図8Aに、実施例1の変形例1による半導体発光素子の製造方法で用いられる基板20の平面図を示す。凸部21が、x軸方向及びy軸方向に規則的に配列している。凸部21の各々の平面形状は平行四辺形であるが、長方形及び正方形のいずれでもない。相互に対向する一対の辺21Xの各々と、x軸とのなす角度は15°以下であり、他の一対の辺21Yの各々と、y軸とのなす角度も15°以下である。

【0045】

y軸方向に隣り合う2つの凸部21の、相互に向かい合う辺21Xは平行であり、x軸方向に隣り合う2つの凸部21の、相互に向かい合う辺21Yも平行である。凸部21のy軸方向の間隔G1を、y軸方向に隣り合う2つの凸部21の相互に対向する辺21Xの、y軸方向の間隔と定義する。同様に、凸部21のx軸方向の間隔G2を、x軸方向に隣り合う2つの凸部21の相互に対向する辺21Yの、x軸方向の間隔と定義する。このとき、間隔G1を、間隔G2の1.5倍以上4.5倍以下とすることが好ましい。

【0046】

図8Bに、実施例1の変形例2による半導体発光素子の製造方法で用いられる基板20の平面図を示す。変形例2では、凸部21の各々の平面形状が台形である。台形の上底及び下底に対応する辺21Xはx軸に平行である。台形の斜辺に対応する辺21Yは、y軸に対して傾いており、y軸とのなす角度は15°以下である。

【0047】

x軸方向に隣り合う2つの凸部21は、一方の凸部21を180°回転させると、他方の凸部21に重なる位置関係を持つ。このため、x軸方向に隣り合う2つの凸部21の、相互に対向する辺21Yは平行になる。各凸部21の辺21Xは、x軸に平行でありため、y軸方向に隣り合う2つの凸部21の、相互に対向する辺21Xも平行になる。凸部21のy軸方向の間隔G1及びx軸方向の間隔G2の定義は、図8Aに示した変形例1の場合と同一である。

【0048】

変形例2においても、間隔G1を、間隔G2の1.5倍以上4.5倍以下とすることが好ましい。

【0049】

図9Aに、実施例1の変形例3による半導体発光素子の製造方法で用いられる基板20の平面図を示す。凸部21が、第1の方向80及び第2の方向81に規則的に配列している。第1の方向80は、x軸に対して傾斜しており、第1の方向80とx軸とのなす角度θは15°以下である。第2の方向81は、第1の方向80と直交する。

【0050】

凸部21の相互に対向するひと組の辺21Xは第1の方向80と平行であり、他のひと組の辺21Yは第2の方向81に平行である。このため、凸部21の各々の平面形状は、正方形または長方形になる。

【0051】

y軸方向に隣り合う2つの凸部21の間隔G1として、第2の方向81に隣り合う2つの凸部21のy軸方向に関する距離を採用する。同様に、x軸方向に隣り合う2つの凸部21の間隔G2として、第1の方向80に隣り合う2つの凸部21のx軸方向に関する距離を採用する。第1の方向80に関する距離及び第2の方向81に関する距離を採用しないのは、結晶成長が、第1の方向80及び第2の方向81に進むのではなく、x軸方向及びy軸方向に進むことによる。この変形例3においては、間隔G1を、間隔G2の1.5倍以上、かつ4.5倍以下とすることが好ましい。

【0052】

図9Bに、実施例1の変形例4による半導体発光素子の製造方法で用いられる基板20の平面図を示す。凸部21が、第1の方向80及び第2の方向81に規則的に配列している。第1の方向80及び第2の方向81は、図9Aに示した変形例3の場合と同一である。

【0053】

凸部21の相互に対向するひと組の辺21Xはx軸と平行であり、他のひと組の辺21Yはy軸と平行である。このため、凸部21の各々の平面形状は、正方形または長方形になる。図9Aに示した変形例3の場合と同様に、y軸方向に隣り合う2つの凸部21の間隔G1として、第2の方向81に隣り合う2つの凸部21のy軸方向に関する距離を採用し、x軸方向に隣り合う2つの凸部21の間隔G2として、第1の方向80に隣り合う2つの凸部21のx軸方向に関する距離を採用する。この変形例4においても、間隔G1を、間隔G2の1.5倍以上、かつ4.5倍以下とすることが好ましい。

【0054】

なお、上記実施例1、及び変形例1〜4において、間隔G1を間隔G2の3倍以下とすることがより好ましい。また、実施例1の変形例1〜4では、凸部21の辺がx軸及びy軸に対して傾いている構成、及び凸部21の配列方向はx軸及びy軸に対して傾いている構成を示した。これらの構成でも、図4Bに示した実施例1の構成に近い効果が得られるが、凸部21の各辺、及び凸部21の配列する方向を、x軸及びy軸に平行にすることが最も好ましい。

【0055】

実施例1では、基板20に、C面サファイア単結晶基板を用いたが、他のコランダム構造の結晶からなるC面基板を用いてもよい。また、基板上に形成する下地膜に、Ga及びNを含むIII−V族化合物半導体を用いてもよい。

[実施例2]

図10Aに、実施例2による半導体発光素子の製造方法で用いる基板20の断面図を示す。以下の説明では、実施例1との相違点に着目し、同一の構成については説明を省略する。基板20の表面に形成された凹凸パターンは、複数の凹部60を含む。

【0056】

図10Bに、基板20の平面図を示す。複数の凹部60が、x方向及びy方向に周期的に配列している。凹部60の各々の平面形状は、1つの辺がx軸に平行な長方形である。y軸に平行な辺の長さW1は、x軸に平行な辺の長さW2よりも短い。x方向に隣り合う凹部60の間隔、及びy方向に隣り合う凹部60の間隔は、共にGである。

【0057】

図10Cに、基板20に形成された凹凸パターンの斜視図を示す。凹部60の各々は、x方向に向かい合う一対の第1の段差面60A、y方向に向かい合う一対の第2の段差面60B、及び底面を有する。段差面60A、60Bは、xy面に対して傾斜している。傾斜角(段差面とxy面とのなす角度)は、基板20のエッチング条件に依存し、例えば30°〜85°である。

【0058】

図11Aに、基板20の上にGaN層を成長させたときの結晶成長の様子を示す。段差面60Aから凹部60の内側に向かってGaNのa軸方向の横方向成長が生じ、段差面60Bから凹部60の内側に向かってGaNのm軸方向の横方向成長が生じる。a軸方向の成長速度が、m軸方向の成長速度よりも速い。このため、凹部60の短辺の長さW1の1/2の長さのa軸方向の成長が生じると、凹部60内がGaN層で埋め込まれる。

【0059】

図11Bに、凹部60がy方向に長い例を示す。この場合にも、凹部60の長辺の長さW1の1/2の長さのa軸方向の成長が生じた時点で、凹部60内がGaN層で埋め込まれる。

【0060】

従って、凹部60の平面形状を凹部60のy方向の寸法を、x方向の寸法よりも短くすることにより、凹部60内をGaN層で埋め込むまでの成長時間を短縮することが可能になる。長辺の長さW2を短辺の長さW1の1.5倍〜4.5倍の範囲内にすることが好ましい。この範囲内にすることにより、成長時間短縮の有意な効果が期待できる。

【0061】

実施例2では、凹部60の1つの辺を、x軸(基板20のa軸)に平行にした。この1つの辺と、x軸とは、完全に平行である必要はない。例えば、1つの辺の延在する方向と、x軸との角度のずれが15°以下であれば、実質的に実施例2と同様の効果が得られる。また、他の辺の延在する方向と、y軸との角度のずれが15°以下であれば、必ずしもy軸に平行である必要はない。

【0062】

凹部60の辺がx軸及びy軸と平行ではない場合には、凹部60の平面形状が長方形になるとは限らない。この場合でも、相互に対向する辺は平行であることが好ましい。すなわち、凹部60の平面形状は平行四辺形であることが好ましい。このとき、図8Bに示したy軸方向の寸法W1として、x軸との角度のずれが15°以下のひと組の対辺のy軸方向に関する間隔を採用する。同様に、x軸方向の寸法W2として、y軸との角度のずれが15°以下のひと組の対辺のx軸方向に関する間隔を採用する。

【0063】

x軸方向の寸法W2を、y軸方向の寸法W1の1.5倍以上4.5倍以下とすることが好ましい。なお、図8Bに示したように、凹部60の辺を、x軸及びy軸に平行にすることが最も好ましく、寸法W2を寸法W1の3倍以下とすることがより好ましい。

【0064】

基板20の上に形成されたGaN層の上に、実施例1と同様の発光構造を形成することにより、半導体発光素子が得られる。凹部60が、光を屈折または散乱させることにより、外部量子効率を高めることができる。

[実施例3]

図12Aに、実施例3による半導体発光素子の製造方法で用いる基板70の断面図を示す。基板70には、C面GaN単結晶基板が用いられる。基板70の表面に、SiO2等の絶縁材料からなる複数のマスクパターン71が形成されている。基板70のm軸方向をx軸、a軸方向をy軸、c軸方向をz軸とするxyz直交座標系を定義する。

【0065】

図12Bに、マスクパターン71の平面図を示す。マスクパターン71の各々の平面形状は、1つの辺がx軸に平行な長方形である。x軸に平行な辺の長さをWx、y軸に平行な辺の長さをWyとする。

【0066】

図13A〜図13Cに、基板70の上にGaN層を成長させたときの断面図を時系列で示す。

【0067】

図13Aに示すように、基板70が露出した領域にGaN層75が形成される。マスクパターン71の上には、GaN層が成長しない。成長したGaN層75が、マスクパターン71の上面まで達すると、図13Bに示すように、マスクパターン71の縁から内側に向かって横方向の成長が始まる。横方向の成長が進むと、図13Cに示すように、マスクパターン71がGaN層75で完全に覆われる。

【0068】

このGaN層75を下地層として、その上に実施例1と同様の発光構造を形成することができる。マスクパターン71が、光を屈折及び散乱させることにより、外部量子効率を高めることができる。

【0069】

マスクパターン71の上方で生じるy方向(a軸方向)への横方向成長が、x方向(m軸方向)への横方向成長よりも速い。従って、マスクパターン71のy方向の寸法を、x方向の寸法よりも短くすることにより、マスクパターン71の上面を、より速くGaN層75で被覆することができる。

【0070】

マスクパターン71のx方向の寸法Wxを、y方向の寸法Wyの1.5倍〜4.5倍の範囲内とすることにより、GaN層の成膜時間を短縮する有意な効果が期待できる。

【0071】

実施例3では、マスクパターン71の1つの辺を、x軸(基板70のm軸)に平行にした。この1つの辺と、x軸とは、完全に平行である必要はない。例えば、1つの辺が延在する方向と、x軸との角度のずれが15°以下であれば、実質的に実施例3と同様の効果が得られる。また、他の辺が延在する方向と、y軸との角度のずれが15°以下であれば、必ずしもy軸に平行である必要はない。この場合、マスクパターン71の平面形状は平行四辺形であることが好ましい。このとき、図10Bに示したx軸方向の寸法Wxとして、y軸との角度のずれが15°以下のひと組の対辺のx軸方向に関する間隔を採用する。同様に、y軸方向の寸法Wyとして、x軸との角度のずれが15°以下のひと組の対辺のy軸方向に関する間隔を採用する。

【0072】

x軸方向の寸法Wxを、y軸方向の寸法Wyの1.5倍以上4.5倍以下とすることが好ましい。なお、図10Bに示したように、マスクパターン71の辺を、x軸及びy軸に平行にすることが最も好ましく、寸法Wxを寸法Wyの3倍以下とすることがより好ましい。

【0073】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0074】

10 サファイア基板

11 凸部

12 GaN層

13 n型GaN層

14 発光層

15 p型GaN層

16 p側電極

17 n側電極

20 基板

21 凸部

21A 第1の段差面

21B 第2の段差面

21X、21Y 辺

23 バッファ層

24 下地層

25 n型半導体層

26 発光層

27、28 p型半導体層

30 メサ

31 透明電極

32 n側電極

33 p側パッド

40 半導体発光素子のチップ

41 斜面

50 GaN層

60 凹部

70 基板

71 マスクパターン

75 GaN層

【特許請求の範囲】

【請求項1】

c軸が厚さ方向を向くコランダム構造の結晶構造を持ち、表面に複数の凸部が形成された基板と、

前記基板の前記凸部が形成された表面の上に配置され、Ga及びNを含むIII−V族化合物半導体からなり、表面が前記基板の表面よりも平坦である下地膜と、

前記下地膜の上に形成され、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造と

を有し、

前記下地膜のa軸方向とのなす角度が15°未満の方向を第1の方向とし、前記第1の方向と直交する方向を第2の方向としたとき、

前記凸部は、前記第1の方向、及び第2の方向に規則的に配列しており、前記凸部の各々の平面形状は、四角形の4つの辺に整合する縁を持ち、該四角形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記第1の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第1の辺は相互に平行であり、前記第2の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第2の辺は相互に平行であり、相互に対向する前記第2の辺の前記m軸方向の間隔は、相互に対向する前記第1の辺の前記a軸方向の間隔よりも広い半導体発光素子。

【請求項2】

前記第1の方向に隣り合う前記凸部の、前記a軸方向に関する間隔が、前記第2の方向に隣り合う前記凸部の、前記m軸方向に関する間隔の4.5倍以下である請求項1に記載の半導体発光素子。

【請求項3】

c軸が厚さ方向を向くコランダム構造の結晶構造を持ち、表面に複数の凹部が形成された基板と、

前記基板の前記凹部が形成された表面の上に配置され、Ga及びNを含むIII−V族化合物半導体からなり、表面が前記基板の表面よりも平坦である下地膜と、

前記下地膜の上に形成され、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造と

を有し、

前記凹部の各々の平面形状は、平行四辺形の4つの辺に整合する縁を持ち、該平行四辺形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記平行四辺形の各々の前記第1の辺の前記a軸方向に関する間隔は、前記第2の辺の前記m軸方向に関する間隔よりも広い半導体発光素子。

【請求項4】

c軸が厚さ方向を向き、Ga及びNを含むウルツ鉱構造を持つIII−V族化合物半導体からなる支持基板と、

前記支持基板の上に形成され、前記支持基板のa軸方向及びm軸方向に周期的に配置されたマスクパターンと、

前記支持基板からエピタキシャル成長し、さらに、横方向成長して前記マスクパターンを覆う下地膜と、

前記下地膜の上に形成され、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造と

を有し、

前記マスクパターンの各々の平面形状は、平行四辺形の4つの辺に整合する縁を持ち、該平行四辺形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記平行四辺形の各々の前記第1の辺の前記a軸方向に関する間隔は、前記第2の辺の前記m軸方向に関する間隔よりも広い半導体発光素子。

【請求項5】

c軸が厚さ方向を向くコランダム構造の結晶構造を持つ基板の表層部を部分的にエッチングすることにより、前記表面をに複数の凸部を形成する工程と、

前記基板の前記凸部が形成された表面の上に、Ga及びNを含むIII−V族化合物半導体からなる下地膜を形成する工程と、

前記下地膜の上に、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造を形成する工程と

を有し、

前記下地膜のa軸方向とのなす角度が15°未満の方向を第1の方向とし、前記第1の方向と直交する方向を第2の方向としたとき、

前記凸部は、前記第1の方向、及び第2の方向に規則的に配列しており、前記凸部の各々の平面形状は、四角形の4つの辺に整合する縁を持ち、該四角形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記第1の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第1の辺は相互に平行であり、前記第2の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第2の辺は相互に平行であり、相互に対向する前記第2の辺の前記m軸方向の間隔は、相互に対向する前記第1の辺の前記a軸方向の間隔よりも広い半導体発光素子の製造方法。

【請求項1】

c軸が厚さ方向を向くコランダム構造の結晶構造を持ち、表面に複数の凸部が形成された基板と、

前記基板の前記凸部が形成された表面の上に配置され、Ga及びNを含むIII−V族化合物半導体からなり、表面が前記基板の表面よりも平坦である下地膜と、

前記下地膜の上に形成され、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造と

を有し、

前記下地膜のa軸方向とのなす角度が15°未満の方向を第1の方向とし、前記第1の方向と直交する方向を第2の方向としたとき、

前記凸部は、前記第1の方向、及び第2の方向に規則的に配列しており、前記凸部の各々の平面形状は、四角形の4つの辺に整合する縁を持ち、該四角形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記第1の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第1の辺は相互に平行であり、前記第2の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第2の辺は相互に平行であり、相互に対向する前記第2の辺の前記m軸方向の間隔は、相互に対向する前記第1の辺の前記a軸方向の間隔よりも広い半導体発光素子。

【請求項2】

前記第1の方向に隣り合う前記凸部の、前記a軸方向に関する間隔が、前記第2の方向に隣り合う前記凸部の、前記m軸方向に関する間隔の4.5倍以下である請求項1に記載の半導体発光素子。

【請求項3】

c軸が厚さ方向を向くコランダム構造の結晶構造を持ち、表面に複数の凹部が形成された基板と、

前記基板の前記凹部が形成された表面の上に配置され、Ga及びNを含むIII−V族化合物半導体からなり、表面が前記基板の表面よりも平坦である下地膜と、

前記下地膜の上に形成され、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造と

を有し、

前記凹部の各々の平面形状は、平行四辺形の4つの辺に整合する縁を持ち、該平行四辺形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記平行四辺形の各々の前記第1の辺の前記a軸方向に関する間隔は、前記第2の辺の前記m軸方向に関する間隔よりも広い半導体発光素子。

【請求項4】

c軸が厚さ方向を向き、Ga及びNを含むウルツ鉱構造を持つIII−V族化合物半導体からなる支持基板と、

前記支持基板の上に形成され、前記支持基板のa軸方向及びm軸方向に周期的に配置されたマスクパターンと、

前記支持基板からエピタキシャル成長し、さらに、横方向成長して前記マスクパターンを覆う下地膜と、

前記下地膜の上に形成され、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造と

を有し、

前記マスクパターンの各々の平面形状は、平行四辺形の4つの辺に整合する縁を持ち、該平行四辺形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記平行四辺形の各々の前記第1の辺の前記a軸方向に関する間隔は、前記第2の辺の前記m軸方向に関する間隔よりも広い半導体発光素子。

【請求項5】

c軸が厚さ方向を向くコランダム構造の結晶構造を持つ基板の表層部を部分的にエッチングすることにより、前記表面をに複数の凸部を形成する工程と、

前記基板の前記凸部が形成された表面の上に、Ga及びNを含むIII−V族化合物半導体からなる下地膜を形成する工程と、

前記下地膜の上に、Ga及びNを含むIII−V族化合物半導体からなるn型半導体層とp型半導体層とを含む発光構造を形成する工程と

を有し、

前記下地膜のa軸方向とのなす角度が15°未満の方向を第1の方向とし、前記第1の方向と直交する方向を第2の方向としたとき、

前記凸部は、前記第1の方向、及び第2の方向に規則的に配列しており、前記凸部の各々の平面形状は、四角形の4つの辺に整合する縁を持ち、該四角形の各々は、前記下地膜のm軸方向とのなす角度が15°未満の一対の第1の辺と、前記下地膜のa軸方向とのなす角度が15°未満の一対の第2の辺とを有し、

前記第1の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第1の辺は相互に平行であり、前記第2の方向に隣り合う2つの凸部に整合する四角形の相互に対向する前記第2の辺は相互に平行であり、相互に対向する前記第2の辺の前記m軸方向の間隔は、相互に対向する前記第1の辺の前記a軸方向の間隔よりも広い半導体発光素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2011−146589(P2011−146589A)

【公開日】平成23年7月28日(2011.7.28)

【国際特許分類】

【出願番号】特願2010−7154(P2010−7154)

【出願日】平成22年1月15日(2010.1.15)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

【公開日】平成23年7月28日(2011.7.28)

【国際特許分類】

【出願日】平成22年1月15日(2010.1.15)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

[ Back to top ]