半導体発光素子

【課題】チップサイズを変えること無く、出力を下げることもなく、順方向電圧のみを下げることが可能な半導体発光素子およびその製造方法を提供することを目的とする。

【解決手段】1つの発光素子に1つのピーク波長を発する2つの発光層を具え、第1導電型の半導体層に接続する電極に対し、2つの第2導電型の半導体層に接続する2つの電極による並列回路を形成し、2つの発光層を並列で発光させることで、擬似的に発光層の面積を増やし、順方向電圧を下げることができる。

【解決手段】1つの発光素子に1つのピーク波長を発する2つの発光層を具え、第1導電型の半導体層に接続する電極に対し、2つの第2導電型の半導体層に接続する2つの電極による並列回路を形成し、2つの発光層を並列で発光させることで、擬似的に発光層の面積を増やし、順方向電圧を下げることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体発光素子に関する。

【背景技術】

【0002】

近年、発光ダイオード(LED)の用途の多様化と共に、LEDの光出力の向上が求められている。

【0003】

一般にLEDは、表面電極と裏面電極との間に、p型半導体層、n型半導体層、およびこれら半導体層間に設けられた発光層を具える構造を有する半導体発光素子である。高品質のLEDには、一般に高出力と低消費電力(低い順方向電圧)、そして長寿命が求められる。

【0004】

発光層での発光出力は発光層に流れる電流密度に依存し、電流密度を大きくすれば発光出力は大きくなる。しかしながら、過度の電流密度は発熱を生じて発光出力を低下させ、LEDの寿命を短くする原因となり、LEDに流すことの出来る電流には上限がある。

【0005】

そのため、発光出力を低下させずに大電流を流すためにも、順方向電圧を低くしたLEDが求められている。

【0006】

なお、特許文献1には、異種材料を垂直に組み合わせて、複数の波長を放出するLEDが記載されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開昭55−148477号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

大電流を流すことの出来るLEDとして、チップサイズが大きいLEDがある。チップサイズが大きいLEDとは、垂直方向を光放射方向とした場合の発光面積が大きいLEDである。この発光面積が大きいLEDとは、すなわち基板上に形成した半導体層間に設けられた発光層の面積が大きいことであり、大電流でも発光層の電流密度は抑えられる。しかしながら、チップサイズが大きいことは、基板1枚あたりから作製できるチップ個数が減少することであり、製造コストを上げてしまう。さらに、チップサイズに起因する発光素子および発光装置の大きさが大きくても問題無い用途には良いが、携帯電話などその大きさ自体が問題となる用途もある。

【0009】

そこで本発明は、上記課題に鑑み、チップサイズの大型化以外の方法で順方向電圧を下げることのできるLEDを得ることが可能な半導体発光素子およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

ここで本発明者らは、活性層を垂直方向に複数積層し、かつ、活性層に並列回路により電流が流れる構造とすることを見出した。

【0011】

このような層構造を有する半導体発光素子300によれば、活性層の積層により実質的な活性層の合計面積を大きくし、チップサイズを大きくすること無く、順方向電圧を下げることができる。

【0012】

すなわち、本発明の要旨構成は以下の通りである。

1つのピーク波長を発する2つの発光層の間に位置する第1導電型の半導体層と、該2つの発光層を該第1導電型の半導体層と挟む位置にある2つの第2導電型の半導体層とを有し、該第1導電型の半導体層に接続する電極に対し、該2つの第2導電型の半導体層に接続する2つの電極が電気的に並列に接続される半導体発光素子。

【発明の効果】

【0013】

本発明によれば、同じチップサイズにおいても発光層の面積を広げ、発光出力を下げること無く低順方向電圧を有する発光素子を提供することが可能となった。

【図面の簡単な説明】

【0014】

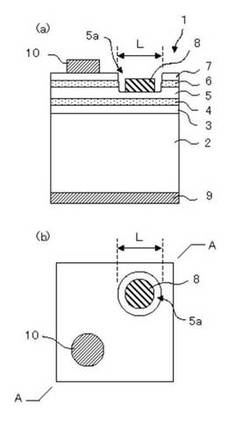

【図1】本発明に従う半導体発光素子を拡大して示す模式断面図(a)、上面図(b)である。

【図2】本発明に従う半導体発光素子の実装時の模式断面図である。

【図3】従来の半導体発光素子を拡大して示す模式断面図(a)、上面図(b)である。

【発明を実施するための形態】

【0015】

以下、図面を参照しつつ本発明をより詳細に説明する。なお、本明細書において、本発明に従う半導体発光素子と比較例の半導体発光素子とで共通する構成要素には、原則として下1桁が同一の参照番号を付し、説明は省略する。また、発光素子の模式断面図においては、説明の便宜上、各層の厚さが実状とは異なる比率で誇張して示す。

【0016】

本発明の一実施形態である半導体発光素子1は、図1(a)のA−A断面図に例示するとおり、基板2上に第1のn型半導体層3、第1の発光層4、p型半導体層5、第2の発光層6、第2のn型半導体層7を有する。図1(b)の上面図に例示する配置のように、p型半導体層5の一部が露出した溝部5aの中に、p型電極8を有する。そして、基板2側に第1のn型電極9を有し、第2のn型半導体層7上に第2のn型電極10を有する。

【0017】

このような構成を採用した半導体発光素子1を、図2に例示するようにTO−18等のステムに実装し、p側電極8に陽極端子を電気的に接続し、第1のn型電極9と第2のn型電極10の両方に陰極端子を電気的に接続することで、第1の発光層4と第2の発光層6に対する並列回路を形成する。

【0018】

このように、第1の発光層4と第2の発光層6に対する並列回路を形成することにより、擬似的に発光層の面積が増加し、半導体発光素子1の発光出力を下げること無く、順方向電圧を低減することができる。

【0019】

基板2を構成する好適な材料としては、例えばSi、GaAs、Ge等の半導体材料のほか、AlやCuなどの金属またはその合金材料等が挙げられ、好適には100〜300μmの厚さを有する。

【0020】

本発明は、順方向電圧の低減を目的としている。そのため、第1の発光層4および第2の発光層6とは同じ材料により形成され、単一波長をもつ。ここで、単一波長とは、半導体発光素子1の発する波長が1つのピーク波長を有することを意味するものであり、2つの発光層を形成する上で目的とする組成や波長が等しければよく、製造上の数%の誤差は許容する。なお、基板2による二次発光は考慮しない。

【0021】

半導体層の各層を構成する好適な材料としては、化合物半導体が挙げられ、例えばIII−V族化合物半導体とすることができる。III−V族化合物半導体としては、例えばn型半導体層101およびp型半導体層103をそれぞれAlGaAs系材料、AlGaInP系材料、AlGaN系材料などとすることができる。p型不純物としては、Mg,Zn,C,Si,Ge、n型不純物としては、Te,Si,Se,Sが例示できる。発光層は単層、あるいは多重量子井戸のような積層構造などとすることができる。これらはいずれも、MOCVD法など既知の手法を用いてエピタキシャル成長させることにより形成することができる。各層の厚みは、例えばn型半導体層101は1〜10μm、発光層102は10〜500nm、p型半導体層103は1〜10μmとすることができる。

【0022】

これまで本発明における第1伝導型をn型、第2伝導型をp型として、半導体層104を説明したが、本発明はこれに限定されず、第1伝導型をp型、第2伝導型をn型としても良いことは勿論である。

【0023】

第1の第1導電型電極9は第1の第1導電型半導体層3またはそれに接続する基板2との良好なオーミック接触を形成するための電極であり、基板2として金属基板を使用した場合には、第1の第1導電型電極9のない構造を選択することも可能である。第2の第1導電型電極10は第2の第1導電型半導体層7(本実施形態ではn型半導体層)との良好なオーミック接触を形成するための電極である。第2導電型電極8は第2導電型半導体層5(本実施形態ではp型半導体層)との良好なオーミック接触を形成するための電極である。電極を構成する好適な材料としては、NiやTi等の金属にAuやAl等の金属を組み合わせたものが挙げられ、AlGaAs系材料に対しては例えばAuGe,NiおよびAuを順次形成したAuGe/Ni/Au電極があり、好適には100〜2000nmの厚さを有する。オーミック接触には熱処理が必要な場合がある。なお、上記第2の第1導電型電極10および第2導電型電極8には、電極上にワイヤーボンディングの際に必要なパッド電極をさらに設けても良い。

【0024】

図1には図示していないが、p型電極8と第2のn発光層6および第2のn型半導体層7とが直接接触しないように、両者の間に絶縁膜が設けられることがより好ましい。

【0025】

次に、半導体発光素子1の製造方法の一例を説明する。まず、n型GaAs基板などの導電性成長用基板(基板2)に既述のような材料からなる第1のn型半導体層3、第1の発光層4、p型半導体層5、第2の発光層6、第2のn型半導体層7をこの順に、例えばMOCVD法などによりエピタキシャル成長させて形成する。

【0026】

次に、第2のn型半導体層7上に所定パターンの第2のn型電極10を形成する。例えば既述のような材料を抵抗加熱による蒸着法や電子ビーム蒸着などにより成膜し、フォトリソグラフィーによりレジストパターン形成後、エッチングして、所定パターンを形成する。その後、第2のn型半導体層7上に例えば図1のLで示す部分を除いてレジストパターンなどのマスクを形成し、ウェットエッチングまたはドライエッチングにより、Lで示す部分の第2のn型半導体層7、第2の発光層をエッチング除去し、p型半導体層5の一部を露出させて溝部5aを形成する。このように形成された溝部5a内のp型半導体層5上に、所定パターンのp型電極8を形成する。例えば既述のような材料を抵抗加熱による蒸着法や電子ビーム蒸着などにより成膜し、フォトリソグラフィーによりレジストパターン形成後、エッチングして、所定パターンを形成する。その後、基板2の裏面側全面に第1のn型電極を形成する。その後、必要に応じてアニール処理(RTA:Rapid Thermal Annealing)を行い、成膜した各電極のオーミック接触を形成する。

【0027】

最後に、メサパターンを形成後、ダイシングを行い、半導体発光素子1を用いたLED素子を作製することができる。

【0028】

これまで本発明の一実施形態として、半導体層と同種の導電性半導体基板を用いた半導体発光素子1とその製造方法を説明してきたが、異種基板上のLED素子としても良い。また、上述したところはいずれも代表的な実施形態の例を示したものであって、本発明はこれらの実施形態に限定されるものではない。また、以下、実施例を用いて本発明をさらに詳細に説明するが、本発明は以下の実施例に何ら限定されるものではない。

【実施例】

【0029】

(実施例)

図1に示す本発明に従う半導体発光素子を作製した。まず、導電性n型GaAs基板(Siドープ、厚さ350μm)上に、MOCVD法により、第1のn型半導体層(Al0.4Ga0.6As、Teドープ、厚さ5μm)、第1の発光層(GaAs井戸層(8nm)とAl0.2Ga0.8Asバリア層(6nm)によるアンドープ量子井戸型(3QW)構造)、p型半導体層(Al0.2Ga0.8As、Cドープ、厚さ2μm)、第2の発光層(上記第1の発光層と同じ)、第2のn型半導体層(上記第1のn型半導体層と同じ)からなる半導体層を順に形成した。

【0030】

次に、第2のn型半導体層上に、第2のn型電極(AuGe/Ni/Au、厚さ800nm)およびパッド電極(Ti/Au、厚さ1.5μm)を直径90μmの円形に形成した。形成方法は真空蒸着器(抵抗加熱)を用いて全面に成膜後、フォトリソグラフィーによるレジストパターンを形成し、ウェットエッチングにより行った。その後、第2のn型半導体層上にフォトリソグラフィーによるレジストパターンを形成し、アンモニアと過酸化水素水を含むエッチング液を用いてp型半導体層が露出するまでエッチングを行い、直径100μm(図1のL)の溝部5aを形成した。次に、フォトリソグラフィーによりレジストパターンを形成し、真空蒸着器(抵抗加熱)による成膜とリフトオフ法を用いて、上記により露出したp型半導体層上の中央に直径80μmのp型電極(AuZn、厚さ300nm)およびパッド電極(Ti/Au、厚さ1μm)を形成した。その後、導電性n型GaAs基板の裏面に第1のn型電極(AuGe/Ni/Au、厚さ800nm)を形成した。上記の電極のオーミック接触形成のため、N2雰囲気中で400〜450℃による熱処理を行った。その後、ダイシングを行い、チップサイズ320μm角の発光素子を得た。

【0031】

(比較例1)

図3に示す従来例に従う半導体発光素子を作製した。導電性n型GaAs基板(Siドープ、厚さ350μm)上に、MOCVD法により、第1のn型半導体層(Al0.4Ga0.6As、Teドープ、厚さ5μm)、第1の発光層(GaAs井戸層(8nm)とAl0.2Ga0.8Asバリア層(6nm)によるアンドープ量子井戸型(3QW)構造)、p型半導体層(Al0.2Ga0.8As、Cドープ、厚さ2μm)を形成した。その後、フォトリソグラフィーによりレジストパターンを形成し、真空蒸着器(抵抗加熱)による成膜とリフトオフ法を用いて、p型半導体層上に直径80μmのp型電極(AuZn、厚さ300nm)およびパッド電極(Ti/Au、厚さ1μm)を形成した。その後、導電性n型GaAs基板の裏面に第1のn型電極(AuGe/Ni/Au、厚さ800nm)を形成した。上記の電極のオーミック接触形成のため、N2雰囲気中で400〜450℃による熱処理を行った。その後、ダイシングを行い、チップサイズ320μm角の発光素子を得た。

【0032】

(比較例2)

比較例2のp型電極の直径を120μmとした以外は、比較例1と同様に従来例に従う半導体発光素子を作製した。光放射方向における遮光部となる電極の面積を実施例と合わせるように、すなわち、比較例2のp型電極の面積3600π(μm2)が実施例のp型電極の面積1600π(μm2)と第2のn型電極の面積2025π(μm2)との和とほぼ一致するようにしている。

【0033】

(評価方法)

実施例および比較例1、2の半導体発光素子を、ステム(TO−18)のマウント用ステージ(負極)に銀ペーストを用いて接続し、Auワイヤーを用いたワイヤーボンディングにより陽極とp型電極とを接続した。実施例の半導体発光素子の場合には、図2のように、さらにAuワイヤーを用いたワイヤーボンディングにより第2のn型電極とマウント用ステージ(負極)とを接続することにより、第1と第2の発光層に並列に電気が流れるようにした。

【0034】

Auワイヤーをボンディングした各実施例・比較例の半導体発光素子を20個作製し、それぞれの半導体発光素子について、定電流電圧電源を用いて20mAの電流を流したときの順方向電圧Vf、発光ピーク波長および積分球による発光出力Poを測定し、測定結果の中間値の結果を表1に示した。

【0035】

【表1】

【0036】

(評価結果)

表1に示すとおり、実施例の順方向電圧は1.43Vであり、比較例1の1.50V、比較例2の1.48Vに比べて順方向電圧Vfが低い。これは、発光層が1層から2層となったことにより、発光層面積が増え、電流密度が低下したためと考えられる。比較例1の出力が高いが、これは、光放射方向の遮光となる電極(比較例1ではp型電極)の面積が小さいためであり、この遮光面積を同等とした比較例2と実施例とを比べると、実施例は出力を下げることなく、順方向電圧を大きく低減することが出来ていることがわかる。

【産業上の利用可能性】

【0037】

本発明によれば、1つの半導体発光素子に、同じ波長をもつ2つの発光層を垂直方向に具え、その2つの発光層に並列に電流を流す構造とすることにより、チップサイズを変えること無く、出力を下げることもなく、順方向電圧のみを下げることができ、従来に無い省電力の発光素子を提供することができる。

【符号の説明】

【0038】

1 半導体発光素子

2 基板

3 第1のn型半導体層(第1の第1導電型半導体層)

4 第1の発光層

5 p型半導体層(第2導電型半導体層)

5a 溝部

6 第2の発光層

7 第2のn型半導体層(第2の第1導電型半導体層)

8 p型電極(第2導電型電極)

9 第1のn型電極(第1導電型電極)

10 第2のn型電極(第2の第1導電型電極)

【技術分野】

【0001】

本発明は半導体発光素子に関する。

【背景技術】

【0002】

近年、発光ダイオード(LED)の用途の多様化と共に、LEDの光出力の向上が求められている。

【0003】

一般にLEDは、表面電極と裏面電極との間に、p型半導体層、n型半導体層、およびこれら半導体層間に設けられた発光層を具える構造を有する半導体発光素子である。高品質のLEDには、一般に高出力と低消費電力(低い順方向電圧)、そして長寿命が求められる。

【0004】

発光層での発光出力は発光層に流れる電流密度に依存し、電流密度を大きくすれば発光出力は大きくなる。しかしながら、過度の電流密度は発熱を生じて発光出力を低下させ、LEDの寿命を短くする原因となり、LEDに流すことの出来る電流には上限がある。

【0005】

そのため、発光出力を低下させずに大電流を流すためにも、順方向電圧を低くしたLEDが求められている。

【0006】

なお、特許文献1には、異種材料を垂直に組み合わせて、複数の波長を放出するLEDが記載されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開昭55−148477号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

大電流を流すことの出来るLEDとして、チップサイズが大きいLEDがある。チップサイズが大きいLEDとは、垂直方向を光放射方向とした場合の発光面積が大きいLEDである。この発光面積が大きいLEDとは、すなわち基板上に形成した半導体層間に設けられた発光層の面積が大きいことであり、大電流でも発光層の電流密度は抑えられる。しかしながら、チップサイズが大きいことは、基板1枚あたりから作製できるチップ個数が減少することであり、製造コストを上げてしまう。さらに、チップサイズに起因する発光素子および発光装置の大きさが大きくても問題無い用途には良いが、携帯電話などその大きさ自体が問題となる用途もある。

【0009】

そこで本発明は、上記課題に鑑み、チップサイズの大型化以外の方法で順方向電圧を下げることのできるLEDを得ることが可能な半導体発光素子およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

ここで本発明者らは、活性層を垂直方向に複数積層し、かつ、活性層に並列回路により電流が流れる構造とすることを見出した。

【0011】

このような層構造を有する半導体発光素子300によれば、活性層の積層により実質的な活性層の合計面積を大きくし、チップサイズを大きくすること無く、順方向電圧を下げることができる。

【0012】

すなわち、本発明の要旨構成は以下の通りである。

1つのピーク波長を発する2つの発光層の間に位置する第1導電型の半導体層と、該2つの発光層を該第1導電型の半導体層と挟む位置にある2つの第2導電型の半導体層とを有し、該第1導電型の半導体層に接続する電極に対し、該2つの第2導電型の半導体層に接続する2つの電極が電気的に並列に接続される半導体発光素子。

【発明の効果】

【0013】

本発明によれば、同じチップサイズにおいても発光層の面積を広げ、発光出力を下げること無く低順方向電圧を有する発光素子を提供することが可能となった。

【図面の簡単な説明】

【0014】

【図1】本発明に従う半導体発光素子を拡大して示す模式断面図(a)、上面図(b)である。

【図2】本発明に従う半導体発光素子の実装時の模式断面図である。

【図3】従来の半導体発光素子を拡大して示す模式断面図(a)、上面図(b)である。

【発明を実施するための形態】

【0015】

以下、図面を参照しつつ本発明をより詳細に説明する。なお、本明細書において、本発明に従う半導体発光素子と比較例の半導体発光素子とで共通する構成要素には、原則として下1桁が同一の参照番号を付し、説明は省略する。また、発光素子の模式断面図においては、説明の便宜上、各層の厚さが実状とは異なる比率で誇張して示す。

【0016】

本発明の一実施形態である半導体発光素子1は、図1(a)のA−A断面図に例示するとおり、基板2上に第1のn型半導体層3、第1の発光層4、p型半導体層5、第2の発光層6、第2のn型半導体層7を有する。図1(b)の上面図に例示する配置のように、p型半導体層5の一部が露出した溝部5aの中に、p型電極8を有する。そして、基板2側に第1のn型電極9を有し、第2のn型半導体層7上に第2のn型電極10を有する。

【0017】

このような構成を採用した半導体発光素子1を、図2に例示するようにTO−18等のステムに実装し、p側電極8に陽極端子を電気的に接続し、第1のn型電極9と第2のn型電極10の両方に陰極端子を電気的に接続することで、第1の発光層4と第2の発光層6に対する並列回路を形成する。

【0018】

このように、第1の発光層4と第2の発光層6に対する並列回路を形成することにより、擬似的に発光層の面積が増加し、半導体発光素子1の発光出力を下げること無く、順方向電圧を低減することができる。

【0019】

基板2を構成する好適な材料としては、例えばSi、GaAs、Ge等の半導体材料のほか、AlやCuなどの金属またはその合金材料等が挙げられ、好適には100〜300μmの厚さを有する。

【0020】

本発明は、順方向電圧の低減を目的としている。そのため、第1の発光層4および第2の発光層6とは同じ材料により形成され、単一波長をもつ。ここで、単一波長とは、半導体発光素子1の発する波長が1つのピーク波長を有することを意味するものであり、2つの発光層を形成する上で目的とする組成や波長が等しければよく、製造上の数%の誤差は許容する。なお、基板2による二次発光は考慮しない。

【0021】

半導体層の各層を構成する好適な材料としては、化合物半導体が挙げられ、例えばIII−V族化合物半導体とすることができる。III−V族化合物半導体としては、例えばn型半導体層101およびp型半導体層103をそれぞれAlGaAs系材料、AlGaInP系材料、AlGaN系材料などとすることができる。p型不純物としては、Mg,Zn,C,Si,Ge、n型不純物としては、Te,Si,Se,Sが例示できる。発光層は単層、あるいは多重量子井戸のような積層構造などとすることができる。これらはいずれも、MOCVD法など既知の手法を用いてエピタキシャル成長させることにより形成することができる。各層の厚みは、例えばn型半導体層101は1〜10μm、発光層102は10〜500nm、p型半導体層103は1〜10μmとすることができる。

【0022】

これまで本発明における第1伝導型をn型、第2伝導型をp型として、半導体層104を説明したが、本発明はこれに限定されず、第1伝導型をp型、第2伝導型をn型としても良いことは勿論である。

【0023】

第1の第1導電型電極9は第1の第1導電型半導体層3またはそれに接続する基板2との良好なオーミック接触を形成するための電極であり、基板2として金属基板を使用した場合には、第1の第1導電型電極9のない構造を選択することも可能である。第2の第1導電型電極10は第2の第1導電型半導体層7(本実施形態ではn型半導体層)との良好なオーミック接触を形成するための電極である。第2導電型電極8は第2導電型半導体層5(本実施形態ではp型半導体層)との良好なオーミック接触を形成するための電極である。電極を構成する好適な材料としては、NiやTi等の金属にAuやAl等の金属を組み合わせたものが挙げられ、AlGaAs系材料に対しては例えばAuGe,NiおよびAuを順次形成したAuGe/Ni/Au電極があり、好適には100〜2000nmの厚さを有する。オーミック接触には熱処理が必要な場合がある。なお、上記第2の第1導電型電極10および第2導電型電極8には、電極上にワイヤーボンディングの際に必要なパッド電極をさらに設けても良い。

【0024】

図1には図示していないが、p型電極8と第2のn発光層6および第2のn型半導体層7とが直接接触しないように、両者の間に絶縁膜が設けられることがより好ましい。

【0025】

次に、半導体発光素子1の製造方法の一例を説明する。まず、n型GaAs基板などの導電性成長用基板(基板2)に既述のような材料からなる第1のn型半導体層3、第1の発光層4、p型半導体層5、第2の発光層6、第2のn型半導体層7をこの順に、例えばMOCVD法などによりエピタキシャル成長させて形成する。

【0026】

次に、第2のn型半導体層7上に所定パターンの第2のn型電極10を形成する。例えば既述のような材料を抵抗加熱による蒸着法や電子ビーム蒸着などにより成膜し、フォトリソグラフィーによりレジストパターン形成後、エッチングして、所定パターンを形成する。その後、第2のn型半導体層7上に例えば図1のLで示す部分を除いてレジストパターンなどのマスクを形成し、ウェットエッチングまたはドライエッチングにより、Lで示す部分の第2のn型半導体層7、第2の発光層をエッチング除去し、p型半導体層5の一部を露出させて溝部5aを形成する。このように形成された溝部5a内のp型半導体層5上に、所定パターンのp型電極8を形成する。例えば既述のような材料を抵抗加熱による蒸着法や電子ビーム蒸着などにより成膜し、フォトリソグラフィーによりレジストパターン形成後、エッチングして、所定パターンを形成する。その後、基板2の裏面側全面に第1のn型電極を形成する。その後、必要に応じてアニール処理(RTA:Rapid Thermal Annealing)を行い、成膜した各電極のオーミック接触を形成する。

【0027】

最後に、メサパターンを形成後、ダイシングを行い、半導体発光素子1を用いたLED素子を作製することができる。

【0028】

これまで本発明の一実施形態として、半導体層と同種の導電性半導体基板を用いた半導体発光素子1とその製造方法を説明してきたが、異種基板上のLED素子としても良い。また、上述したところはいずれも代表的な実施形態の例を示したものであって、本発明はこれらの実施形態に限定されるものではない。また、以下、実施例を用いて本発明をさらに詳細に説明するが、本発明は以下の実施例に何ら限定されるものではない。

【実施例】

【0029】

(実施例)

図1に示す本発明に従う半導体発光素子を作製した。まず、導電性n型GaAs基板(Siドープ、厚さ350μm)上に、MOCVD法により、第1のn型半導体層(Al0.4Ga0.6As、Teドープ、厚さ5μm)、第1の発光層(GaAs井戸層(8nm)とAl0.2Ga0.8Asバリア層(6nm)によるアンドープ量子井戸型(3QW)構造)、p型半導体層(Al0.2Ga0.8As、Cドープ、厚さ2μm)、第2の発光層(上記第1の発光層と同じ)、第2のn型半導体層(上記第1のn型半導体層と同じ)からなる半導体層を順に形成した。

【0030】

次に、第2のn型半導体層上に、第2のn型電極(AuGe/Ni/Au、厚さ800nm)およびパッド電極(Ti/Au、厚さ1.5μm)を直径90μmの円形に形成した。形成方法は真空蒸着器(抵抗加熱)を用いて全面に成膜後、フォトリソグラフィーによるレジストパターンを形成し、ウェットエッチングにより行った。その後、第2のn型半導体層上にフォトリソグラフィーによるレジストパターンを形成し、アンモニアと過酸化水素水を含むエッチング液を用いてp型半導体層が露出するまでエッチングを行い、直径100μm(図1のL)の溝部5aを形成した。次に、フォトリソグラフィーによりレジストパターンを形成し、真空蒸着器(抵抗加熱)による成膜とリフトオフ法を用いて、上記により露出したp型半導体層上の中央に直径80μmのp型電極(AuZn、厚さ300nm)およびパッド電極(Ti/Au、厚さ1μm)を形成した。その後、導電性n型GaAs基板の裏面に第1のn型電極(AuGe/Ni/Au、厚さ800nm)を形成した。上記の電極のオーミック接触形成のため、N2雰囲気中で400〜450℃による熱処理を行った。その後、ダイシングを行い、チップサイズ320μm角の発光素子を得た。

【0031】

(比較例1)

図3に示す従来例に従う半導体発光素子を作製した。導電性n型GaAs基板(Siドープ、厚さ350μm)上に、MOCVD法により、第1のn型半導体層(Al0.4Ga0.6As、Teドープ、厚さ5μm)、第1の発光層(GaAs井戸層(8nm)とAl0.2Ga0.8Asバリア層(6nm)によるアンドープ量子井戸型(3QW)構造)、p型半導体層(Al0.2Ga0.8As、Cドープ、厚さ2μm)を形成した。その後、フォトリソグラフィーによりレジストパターンを形成し、真空蒸着器(抵抗加熱)による成膜とリフトオフ法を用いて、p型半導体層上に直径80μmのp型電極(AuZn、厚さ300nm)およびパッド電極(Ti/Au、厚さ1μm)を形成した。その後、導電性n型GaAs基板の裏面に第1のn型電極(AuGe/Ni/Au、厚さ800nm)を形成した。上記の電極のオーミック接触形成のため、N2雰囲気中で400〜450℃による熱処理を行った。その後、ダイシングを行い、チップサイズ320μm角の発光素子を得た。

【0032】

(比較例2)

比較例2のp型電極の直径を120μmとした以外は、比較例1と同様に従来例に従う半導体発光素子を作製した。光放射方向における遮光部となる電極の面積を実施例と合わせるように、すなわち、比較例2のp型電極の面積3600π(μm2)が実施例のp型電極の面積1600π(μm2)と第2のn型電極の面積2025π(μm2)との和とほぼ一致するようにしている。

【0033】

(評価方法)

実施例および比較例1、2の半導体発光素子を、ステム(TO−18)のマウント用ステージ(負極)に銀ペーストを用いて接続し、Auワイヤーを用いたワイヤーボンディングにより陽極とp型電極とを接続した。実施例の半導体発光素子の場合には、図2のように、さらにAuワイヤーを用いたワイヤーボンディングにより第2のn型電極とマウント用ステージ(負極)とを接続することにより、第1と第2の発光層に並列に電気が流れるようにした。

【0034】

Auワイヤーをボンディングした各実施例・比較例の半導体発光素子を20個作製し、それぞれの半導体発光素子について、定電流電圧電源を用いて20mAの電流を流したときの順方向電圧Vf、発光ピーク波長および積分球による発光出力Poを測定し、測定結果の中間値の結果を表1に示した。

【0035】

【表1】

【0036】

(評価結果)

表1に示すとおり、実施例の順方向電圧は1.43Vであり、比較例1の1.50V、比較例2の1.48Vに比べて順方向電圧Vfが低い。これは、発光層が1層から2層となったことにより、発光層面積が増え、電流密度が低下したためと考えられる。比較例1の出力が高いが、これは、光放射方向の遮光となる電極(比較例1ではp型電極)の面積が小さいためであり、この遮光面積を同等とした比較例2と実施例とを比べると、実施例は出力を下げることなく、順方向電圧を大きく低減することが出来ていることがわかる。

【産業上の利用可能性】

【0037】

本発明によれば、1つの半導体発光素子に、同じ波長をもつ2つの発光層を垂直方向に具え、その2つの発光層に並列に電流を流す構造とすることにより、チップサイズを変えること無く、出力を下げることもなく、順方向電圧のみを下げることができ、従来に無い省電力の発光素子を提供することができる。

【符号の説明】

【0038】

1 半導体発光素子

2 基板

3 第1のn型半導体層(第1の第1導電型半導体層)

4 第1の発光層

5 p型半導体層(第2導電型半導体層)

5a 溝部

6 第2の発光層

7 第2のn型半導体層(第2の第1導電型半導体層)

8 p型電極(第2導電型電極)

9 第1のn型電極(第1導電型電極)

10 第2のn型電極(第2の第1導電型電極)

【特許請求の範囲】

【請求項1】

1つのピーク波長を発する2つの発光層の間に位置する第1導電型の半導体層と、上記2つの発光層を上記第1導電型の半導体層と挟む位置にある2つの第2導電型の半導体層とを有し、該第1導電型の半導体層に接続する電極に対し、前記2つの第2導電型の半導体層に接続する2つの電極が電気的に並列に接続される半導体発光素子。

【請求項1】

1つのピーク波長を発する2つの発光層の間に位置する第1導電型の半導体層と、上記2つの発光層を上記第1導電型の半導体層と挟む位置にある2つの第2導電型の半導体層とを有し、該第1導電型の半導体層に接続する電極に対し、前記2つの第2導電型の半導体層に接続する2つの電極が電気的に並列に接続される半導体発光素子。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−209451(P2012−209451A)

【公開日】平成24年10月25日(2012.10.25)

【国際特許分類】

【出願番号】特願2011−74522(P2011−74522)

【出願日】平成23年3月30日(2011.3.30)

【出願人】(000224798)DOWAホールディングス株式会社 (550)

【Fターム(参考)】

【公開日】平成24年10月25日(2012.10.25)

【国際特許分類】

【出願日】平成23年3月30日(2011.3.30)

【出願人】(000224798)DOWAホールディングス株式会社 (550)

【Fターム(参考)】

[ Back to top ]