半導体積層体、半導体デバイス、及びそれらの製造方法

【課題】本発明の目的は、比較的低温において効率的に半導体シリコン膜を製造する方法を提供することである。また、本発明の目的は、基材がポリマー材料を有する半導体積層体を提供することである。

【解決手段】半導体積層体(110)を製造する本発明の方法は、(a)基材上にシリコン粒子分散体膜を形成する工程、(b)シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び(c)未焼結半導体シリコン膜に光を照射して、半導体シリコン膜を形成する工程を含む。また、本発明の半導体積層体(110)は、基材(112)及び半導体シリコン膜(118)を有し、基材が、ポリマー材料を有し、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が、1.0cm2/V・s以上である。

【解決手段】半導体積層体(110)を製造する本発明の方法は、(a)基材上にシリコン粒子分散体膜を形成する工程、(b)シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び(c)未焼結半導体シリコン膜に光を照射して、半導体シリコン膜を形成する工程を含む。また、本発明の半導体積層体(110)は、基材(112)及び半導体シリコン膜(118)を有し、基材が、ポリマー材料を有し、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が、1.0cm2/V・s以上である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基材及びこの基材上に積層されている半導体シリコン膜を有する半導体積層体、及びその製造方法に関する。また、本発明は、このような半導体積層体を有する半導体デバイス、及びその製造方法に関する。

【背景技術】

【0002】

半導体シリコン膜、例えばアモルファスシリコン膜及びポリシリコン膜等は、半導体デバイス、例えば薄膜トランジスタ(TFT)のために使用されている。このような半導体シリコン膜を半導体デバイスで使用する場合、半導体シリコン膜が所望のパターン、例えば回路パターンを有することが必要である。したがって一般に、半導体シリコン膜を、スパッタリングのような物理気相堆積(PVD)、プラズマ化学気相堆積のような化学気相堆積(CVD)等の真空プロセスにより基材の全面に形成し、そしてその後で、得られた半導体シリコン膜の不要部分を、フォトリソグラフィー等によって除去して、所望のパターンを有する半導体シリコン膜を提供することが行われてきた。

【0003】

しかしながら、これらの従来の方法では、大掛かりな装置が必要であること、多大なエネルギーを消費すること、プロセス温度が高温(250℃超)であるのでプロセス毎の冷却に多大な時間を要すること、原料の使用効率が悪いこと(5%未満)、原料が気体であるので扱いにくいこと、大量の廃棄物が発生すること等の問題を有しており、それによって複雑かつ高コストの方法であった。

【0004】

したがって近年、比較的低温で薄膜トランジスタ等のための半導体膜を形成する方法として、液相法が検討されている。液相法では、一般に、プロセス全体を、比較的低温、例えばポリマー材料のガラス転移温度以下の温度で行うことができる。このような低温プロセスでは、安価な汎用ポリマー材料を半導体膜の基材において用いることが可能になり、それによって半導体デバイスの大面積化、フレキシブル化、軽量化、低コスト化も期待できる。また、こうした低温プロセスでは、プロセス毎の冷却が必要ないのでプロセス時間を短縮できる。

【0005】

このような液相法による半導体膜の製造に関して、有機半導体材料を用いることが検討されている。

【0006】

しかしながら、有機半導体膜は、シリコン半導体膜に比して、キャリア移動度のような性能、及び大気中での安定性のような耐久性が不充分であり、したがって用途が限定されると共に、製品化が難しいのが現状である。

【0007】

また、液相法を用いた半導体膜の製造に関して、無機化合物半導体材料を用いることも検討されている。

【0008】

これに関して例えば、特許文献1では、ナノ粒子分散液を用いて、InGaZnO4膜を成膜する方法が開示されている。特許文献1では、室温で乾燥したInGaZnO4膜を、紫外線(UV)オゾンクリーナーで前処理し、そしてその後で、KrFエキシマレーザー(波長:248nm)で照射することによって、比較的均一なInGaZnO4の結晶膜を成膜している。特許文献1では、このような方法によって、キャリア移動度1.2cm2/V・sの薄膜トランジスタを作製している。

【0009】

しかしながら、InGaZnO4など無機化合物半導体材料は、原材料入手の問題から、シリコン半導体に比して非常に高価であり、一般的なTFT材料として実用的ではない。

【0010】

また、液相法を用いた半導体膜の製造に関して、有機シリコン化合物溶液、例えば水素化環状シラン化合物を含有するシリコン溶液を用いて、半導体ポリシリコン膜を製造することが検討されている。

【0011】

これに関して例えば、特許文献2及び3では、高分子量の低揮発性ポリシラン化合物を含有する有機シリコン化合物溶液を使用している。ここで、この低揮発性ポリシラン化合物は、シクロペンタシランを前駆体として得ている。

【0012】

しかしながら、有機シリコン化合物溶液では、爆発性を低減するために、脱水素アニール処理(400〜500℃)をすることが必要な場合があり、したがってプロセス全体を低温化することが困難である。

【0013】

また、特許文献4では、シリコン粒子を含有する分散体を用いて、半導体シリコン膜を形成することを提案している。

【0014】

液相法の使用に関して、半導体シリコン膜の所望のパターンを基材上に直接に描く直接描画技術を利用することも検討されている。直接描画技術としては、半導体シリコン膜の構成材料を含む原料液を塗布印刷する印刷法、例えばインクジェットプリンティング法、スクリーン印刷法等が挙げられる。

【0015】

このような印刷法では、真空プロセスは不要であり、また直接描画によりパターン形成を行うことができるので、簡易かつ低コストで、半導体デバイスを製造することができる。

【0016】

なお、ある種の半導体デバイスの製造においては、リン又はホウ素のようなドーパントを選択された領域において半導体層又は基板に注入して、選択された領域に拡散領域を形成することが行われている。特に、ある種の太陽電池の製造においては、ドーパントを選択された領域において半導体層又は基板に注入して、選択された領域に拡散領域又はドープ領域を形成することが行われている。

【0017】

このような拡散領域又はドープ領域を必要とする太陽電池としては、セレクティブ(選択)エミッタ型太陽電池、及びバックコンタクト型太陽電池を挙げることができる。

【0018】

セレクティブエミッタ型太陽電池は例えば、特許文献5で示されるようなものである。

【0019】

例えば具体的には、セレクティブエミッタ型太陽電池(500)は、図10に示すように、n型半導体層(12、12a)及びp型半導体層(14、14a)を有する半導体基板(10)、半導体基板(10)の受光面側の受光面側電極(22)及び保護層(24)、半導体基板(10)の裏面側の裏面側電極(32)及び保護層(34)を有し、n型半導体層(12、12a)のうちの電極(32)に接触する領域(12a)において選択的に、ドーパントの濃度が高くされている。

【0020】

セレクティブエミッタ型太陽電池は、このように、電極に接触する領域(12a)において選択的にドーパントの濃度が高くされていることによって、受光面側のドーパントの濃度が高いことによって起こる問題、すなわち例えば高ドーパント濃度層による受光側表面による反射の増加という問題を防ぎつつ、電極に接触する領域においてドーパントの濃度が高いことによる利益、すなわち例えば電極と半導体層との間のオーミック接触という利益を達成するものである。

【0021】

なお、図10において、発電のために太陽電池(500)に照射される光は、番号100で示されている。また、図10において、光起電力の発生のためにn及びpドープされている領域は、それぞれ記号n及びpで示されており、またエミッタを形成するために高濃度にn及びpドープされている領域は、それぞれ記号n++及びp++で示されている。具体的には、例えば、シリコンからなる太陽電池素子の場合であれば、n++及びp++の領域におけるドーパント濃度は、約1〜2×1021atom/cm3の量である。

【0022】

バックコンタクト型太陽電池は例えば、特許文献6及び7で示されるようなものである。

【0023】

例えば具体的には、バックコンタクト型太陽電池(600)は、図11に示すように、n型(又はp型若しくは真性)半導体からなる半導体基板(10)、半導体基板(10)の受光面側の保護層(24)、半導体基板(10)の裏面側の裏面側電極(22、32)及び保護層(34)を有し、n型半導体からなる半導体基板(10)のうちの電極(32、34)に接触する領域(12a、14a)において選択的に、ドーパントの濃度が高くされている。

【0024】

バックコンタクト型太陽電池(600)は、このように、裏面側において、高濃度にpドープされた領域(14a)と高濃度にnドープされた領域(12a)とが交互に配置されている。その他の部分は、真性半導体領域、低濃度にp若しくはnドープされた領域、又はp−n接合が形成されている領域であり、その領域に光が照射されることによって起電力が発生する。このようにして発生した起電力は、高濃度にドープされた領域を介して接している電極により取り出される。ここで、高濃度にp又はnドープされた領域を設けることで、接触抵抗による起電のロスを低く抑えて、電力を取り出すことができるという利点を有している。

【0025】

なお、図11において、発電のために太陽電池(600)に照射される光は、番号100で示されている。また、図11において、光起電力の発生のためにn(又はp)ドープされている領域は、記号n(p)で示されており、また高濃度にn及びpドープされている領域は、それぞれ記号n++及びp++で示されている。

【0026】

拡散領域又はドープ領域を必要とするトランジスタとしては、電界効果トランジスタ(FET:Field Effect Transistor)を挙げることができる。

【0027】

具体的には例えば、電界効果トランジスタ(700)は、図13に示すように、基材(72)、半導体層(78)、ゲート絶縁膜(73)、ゲート電極(74)、ソース電極(75)及びドレイン電極(76)を有し、ソース電極及びドレイン電極と半導体層とが接触する箇所において、半導体層(78)が、n型又はp型にドープされているドープ領域(78b)を有している。このような電界効果トランジスタでは、このドープ領域によって、半導体基板と電極との間のオーミック接触が促進されている。

【0028】

上記セレクティブエミッタ型太陽電池、バックコンタクト型太陽電池、又は電界効果トランジスタでのように、選択された領域に拡散領域又はドープ領域を形成するためには一般に、ドーパント源を層又は基板と接触させ、熱やレーザー照射を行って、層又は基板にドーパントを注入する方法が知られている。ここで用いられるドーパント源としては、ボロンシリケートガラス又はリンガラス(特許文献7)、無機ドーパントを含む液体(特許文献8)、又はシリコン及び/又はゲルマニウムのナノ粒子を含有するインク(特許文献9及び10)を使用することが知られている。

【先行技術文献】

【特許文献】

【0029】

【特許文献1】特開2009−147192号公報

【特許文献2】特開2004−87546号公報(特許4016419号に対応)

【特許文献3】特表2010−506001号公報

【特許文献4】特表2010−514585号公報

【特許文献5】特開2010−186900号公報

【特許文献6】特表2009−521805号公報

【特許文献7】特開2010−262979号公報

【特許文献8】特開平07−297429号公報

【特許文献9】特表2010−519731号公報

【特許文献10】特表2010−514585号公報

【発明の概要】

【発明が解決しようとする課題】

【0030】

本発明の目的は、比較的低温において効率的に半導体シリコン膜を製造する方法を提供することである。より具体的には、本発明の目的は、高価かつエネルギー多消費型の大掛かりな装置を必要とせずに、プラスチック基板等の比較的耐熱性が低い基板上に半導体膜を形成できる、半導体積層体の製造方法を提供することである。

【0031】

また、本発明の目的は、ポリマー材料を有する基材、及びこの基材上に積層されている半導体シリコン膜を有する半導体積層体を提供することである。

【0032】

さらに、本発明の目的は、フォトリソグラフィ工程を用いずに、選択された領域に拡散領域を形成することができる半導体積層体の製造方法を提供することである。

【0033】

本発明の他の目的は、本願の明細書及び特許請求の範囲の記載から明らかになる。

【課題を解決するための手段】

【0034】

基材及びこの基材上に積層されている半導体シリコン膜を有する半導体積層体を製造する本発明の方法は、下記の工程(a)〜(c)を含む:

(a)分散媒及び上記分散媒中に分散しているシリコン粒子を含有するシリコン粒子分散体を、基材上に塗布して、シリコン粒子分散体膜を形成する工程、

(b)上記シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び

(c)上記未焼結半導体シリコン膜に光を照射して、上記未焼結半導体シリコン膜中の上記シリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程、

【0035】

また、本発明の半導体積層体は、ポリマー材料を有する基材、及びこの基材上に積層されている半導体シリコン膜を有する。ここで、この半導体積層体では、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が1.0cm2/V・s以上である。

【0036】

また、本発明の半導体積層体は、基材、この基材上に積層されている半導体シリコン膜、及びこの半導体シリコン膜上に積層されているドーパント注入膜を有する。ここで、この半導体積層体では、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つドーパント注入膜が、互いに焼結されている複数のシリコン粒子から作られている。

【発明の効果】

【0037】

半導体積層体を製造する本発明の方法によれば、所望の半導体特性を有する半導体積層体を簡便な方法により形成できる。具体的には、この本発明の方法によれば、従来技術のプロセス温度と比較して低温で、良好な半導体特性を有する半導体積層体を製造することができる。

【0038】

また、本発明の半導体積層体は、半導体特性、コスト、可撓性、及び/又は軽量性に関して好ましい半導体デバイスのために利用することができる。

【図面の簡単な説明】

【0039】

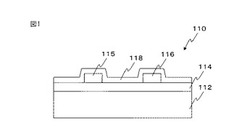

【図1】実施例1〜5において製造したボトムゲート・ボトムコンタクト構造の電界効果トランジスタ(FET)を示す図である。

【図2】実施例6〜8において製造したボトムゲート・ボトムコンタクト構造の電界効果トランジスタ(FET)を示す図である。

【図3】実施例9において製造したボトムゲート・トップコンタクト構造の電界効果トランジスタ(FET)を示す図である。

【図4】本発明のセレクティブエミッタ型太陽電池を説明するための図である。

【図5】本発明のバックコンタクト型太陽電池を説明するための図である。

【図6】セレクティブエミッタ型太陽電池を製造する本発明の方法を説明するための図である。

【図7】セレクティブエミッタ型太陽電池を製造する本発明の方法を説明するための図である。

【図8】セレクティブエミッタ型太陽電池を製造する本発明の方法を説明するための図である。

【図9】セレクティブエミッタ型太陽電池を製造する本発明の方法を説明するための図である。

【図10】従来のセレクティブエミッタ型太陽電池を説明するための図である。

【図11】従来のバックコンタクト型太陽電池を説明するための図である。

【図12】本発明の電界効果トランジスタを説明するための図である。

【図13】従来の本発明の電界効果トランジスタを説明するための図である。

【発明を実施するための形態】

【0040】

《半導体積層体の製造方法》

基材及びこの基材上に積層されている半導体シリコン膜を有する半導体積層体を製造する本発明の方法は、下記の工程(a)〜(c)を含む:

(a)分散媒及び上記分散媒中に分散しているシリコン粒子を含有するシリコン粒子分散体を、基材上に塗布して、シリコン粒子分散体膜を形成する工程、

(b)上記シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び

(c)上記未焼結半導体シリコン膜に光を照射して、上記未焼結半導体シリコン膜中の上記シリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程。

【0041】

《半導体積層体の製造方法−工程(a)》

本発明の方法の工程(a)では、分散媒及び上記分散媒中に分散しているシリコン粒子を含有するシリコン粒子分散体を、基材上に塗布して、シリコン粒子分散体膜を形成する。

【0042】

(分散媒)

シリコン粒子分散体の分散媒は、本発明の目的及び効果を損なわない限り制限されるものではなく、したがって例えばシリコン粒子と反応しない有機溶媒を用いることができる。具体的にはこの分散媒は、非水系溶媒、例えばアルコール、アルカン、アルケン、アルキン、ケトン、エーテル、エステル、芳香族化合物、又は含窒素環化合物、特にイソプロピルアルコール(IPA)、N−メチル−2−ピロリドン(NMP)等であってよい。また、アルコールとしては、エチレングリコールのようなグリコール(2価アルコール)を用いることもできる。なお、分散媒は、シリコン粒子の酸化を抑制するために、脱水溶媒であることが好ましい。

【0043】

(シリコン粒子)

シリコン粒子分散体のシリコン粒子は、本発明の目的及び効果を損なわない限り制限されるものではなく、例えば特許文献4で示されるようなシリコン粒子を用いることができる。具体的には、このシリコン粒子としては、レーザー熱分解法、特にCO2レーザーを用いたレーザー熱分解法によって得られたシリコン粒子を挙げることができる。

【0044】

このシリコン粒子は、多結晶又は単結晶のコア、及びアモルファスの外側層からなるシリコン粒子であってよい。この場合には、多結晶又は単結晶のコアによる半導体特性と、アモルファスの外側層による焼結容易性との組合せを利用することができる。

【0045】

また、シリコン粒子は好ましくは、平均一次粒子径が、100nm以下である。したがってシリコン粒子は例えば、1nm以上、又は5nm以上であって、100nm以下、50nm以下、又は30nm以下であってよい。平均一次粒子径が100nm以下であることは、光によるシリコン粒子の焼結を行うために好ましい。

【0046】

なお、シリコン粒子の平均一次粒子径は、走査型電子顕微鏡(SEM)、透過型電子顕微鏡(TEM)等による観察によって、撮影した画像を元に直接粒子径を計測し、集合数100以上からなる粒子群を解析することで、数平均平均一次粒子径として求めることができる。

【0047】

本発明の方法で用いられるシリコン粒子分散体は、上記の分散媒及びシリコン粒子以外に、リン、ホウ素等のドーパントや公知の添加剤を含んでいてもよい。

【0048】

(基材)

本発明の方法で用いられる基材は、本発明の目的及び効果を損なわない限り制限されるものではない。しかしながら、本発明の方法では、比較的低温において、基材上で半導体シリコン膜を形成することができるので、耐熱性が比較的低い基材、例えばポリマー材料を有する基材を用いることができる。ポリマー材料を有する基材としては特に、表面に導電性膜を付与されたポリマー材料からなる基材を用いることができる。また、導電性膜は、金属、金属酸化物、特にインジウム亜鉛酸化物(IZO)、インジウムスズ酸化物(ITO)のような透明導電性酸化物であってよい。

【0049】

本発明の製造方法は低温プロセスで行うことができるため、基材のためのポリマー材料としては、ガラス転移温度が、300℃以下、250℃以下、200℃以下、100℃以下、又は50℃以下であるポリマー材料を用いることができる。

【0050】

したがって例えばポリマー材料としては、ポリイミド、ポリエーテルスルホン、ポリカーボネート、ポリエチレンテレフタレート、及びポリエチレンナフタレートからなる群から選択される少なくとも1種を含むポリマー材料を用いることができる。また、これらのうちで、ポリカーボネート、ポリエチレンテレフタレート及びポリエチレンナフタレートからなる群から選択される少なくとも1種を含むポリマー材料、特にポリカーボネートを50質量%以上含むポリマー材料は、これらのポリマーが汎用性であり、かつ安価である点で好ましい。

【0051】

(塗布)

シリコン粒子分散体の塗布は、シリコン粒子分散体を所望の厚さ及び均一性で塗布できる方法であれば特に限定されず、例えばインクジェット法、スピンコーティング法等によって行うことができる。

【0052】

また、この塗布は、シリコン粒子分散体膜を乾燥したときに得られる未焼結半導体シリコン膜の厚さが、50nm以上、100nm以上、又は200nm以上であって、2000nm以下、1000nm以下、500nm以下、又は300nm以下であるように行うことができる。具体的には、例えば電界効果トランジスタ(FET)を得る場合には、未焼結半導体シリコン膜の厚さが、50nm以上、100nm以上であって、500nm以下、300nm以下であるように塗布を行うことができる。また、太陽電池を得る場合には、未焼結半導体シリコン膜の厚さが、100nm以上、200nm以上であって、2000nm以下、1000nm以下、500nm以下、又は300nm以下であるように塗布を行うことができる。

【0053】

《半導体積層体の製造方法−工程(b)》

本発明の方法の工程(b)では、シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する。

【0054】

(乾燥)

この乾燥は、シリコン粒子分散体膜から分散媒を実質的に除去することができる方法であれば特に限定されず、例えばシリコン粒子分散体膜を有する基材を、ホットプレート上に配置して行うことができる。

【0055】

乾燥温度は例えば、基材を変形、劣化等させないように選択することができ、例えば50℃以上、70℃以上、90℃以上であって、100℃以下、150℃以下、200℃以下、又は250℃以下であるように選択できる。

【0056】

《半導体積層体の製造方法−工程(c)》

本発明の方法の工程(c)では、未焼結半導体シリコン膜に光を照射して、未焼結半導体シリコン膜中のシリコン粒子を焼結させ、それによって半導体シリコン膜を形成する。

【0057】

(照射される光)

ここで照射される光としては、未焼結半導体シリコン膜中のシリコン粒子の焼結を達成できれば任意の光を用いることができ、例えばレーザー光、特に波長600nm以下、500nm以下又は400nm以下であって、300nm以上のレーザーを用いて行なうことができる。また、シリコン粒子の焼結は、キセノンフラッシュランプのようなフラッシュランプを用いて行うこともできる。

【0058】

光照射をパルス状の光を用いて行う場合、パルス状の光の照射回数は例えば、1回以上、2回以上、5回以上、又は10回以上であって、100回以下、80回以下、又は50回以下にすることができる。また、パルス状の光の照射エネルギーは例えば、15mJ/(cm2・shot)以上、50mJ/(cm2・shot)以上、100mJ/(cm2・shot)以上、150mJ/(cm2・shot)以上、又は200mJ/(cm2・shot)以上であって、500mJ/(cm2・shot)以下、300mJ/(cm2・shot)以下、又は250mJ/(cm2・shot)以下にすることができる。さらに、パルス状の光の照射時間は、例えば200ナノ秒/shot以下、100ナノ秒/shot以下、50ナノ秒/shot以下にすることができる。

【0059】

ここで、光の照射回数が少なすぎる場合には、所望の焼結を達成するために必要とされる1回のパルス当たりのエネルギーが大きくなり、したがって半導体シリコン膜が破損する恐れがある。また、光の照射回数が少なすぎる場合には、必要とされる処理時間が過度に長くなる恐れがある。

【0060】

また、上記のようにパルス状の光の照射回数、照射エネルギー、及び照射時間を選択することは、特に基材がポリマー材料を有する場合に、熱によるポリマー材料の劣化を抑制しつつ、シリコン粒子の焼結を達成するために好ましいことがある。

【0061】

(照射雰囲気)

シリコン粒子を焼結するための光照射は、非酸化性雰囲気、例えば水素、希ガス、窒素、及びそれらの組合せからなる雰囲気において行うことが、シリコン粒子の酸化を防ぐために好ましい。ここで、希ガスとしては、特にアルゴン、ヘリウム、及びネオンを挙げることができる。なお、雰囲気が水素を含有することは、未焼結半導体シリコン膜のシリコン粒子の酸化を抑制するために好ましい。また、非酸化性雰囲気とするために、雰囲気の酸素含有率は、1体積%以下、0.5体積%以下、0.1体積%以下、又は0.01体積%以下とすることができる。

【0062】

《半導体積層体の製造方法−追加の工程(第2の半導体シリコン膜)》

また、半導体積層体を製造する本発明の方法は、下記の工程(a’)〜(c’)を更に含むことができる:

(a’)第2の分散媒及び上記第2の分散媒中に分散している第2のシリコン粒子を含有する第2のシリコン粒子分散体を、工程(c)において得られた上記半導体シリコン膜に塗布して、第2のシリコン粒子分散体膜を形成する工程、

(b’)上記第2のシリコン粒子分散体膜を乾燥して、第2の未焼結半導体シリコン膜を形成する工程、及び

(c’)上記第2の未焼結半導体シリコン膜に光を照射して、上記第2の未焼結半導体シリコン膜中の上記第2のシリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程。

【0063】

このように工程(a’)〜(c’)を更に含む本発明の方法では、半導体特性が更に優れた半導体シリコン膜を得ることができる。本発明は原理によって限定されるものではないが、これは、工程(a)〜(c)によって得られた半導体シリコン膜の空隙を、工程(a’)及び(b’)において塗布及び乾燥された第2のシリコン粒子分散体中のシリコン粒子が充填し、そして工程(c’)においてこのシリコン粒子が焼結して半導体シリコン膜の一部となることによって、緻密な半導体シリコン膜が得られることによると考えられる。

【0064】

なお、工程(a’)〜(c’)の詳細及びそこで言及されている材料については、工程(a)〜(c)に関する上記の記載をそれぞれ参照できる。

【0065】

《半導体積層体の製造方法−追加の工程(ドーパント注入膜)》

また、半導体積層体を製造する本発明の方法は、下記の工程(a”)〜(c”)を更に含むことができる:

(a”)第3の分散媒及び上記第3の分散媒中に分散している第3のシリコン粒子を含有する第3のシリコン粒子分散体を、工程(c)又は(c’)において得られた上記半導体シリコン膜の選択された領域に塗布して、第3のシリコン粒子分散体膜を形成する工程であって、上記第3のシリコン粒子が、p型又はn型ドーパントによってドープされている工程、

(b”)上記第3のシリコン粒子分散体膜を乾燥して、未焼結ドーパント注入膜を形成する工程、及び

(c”)上記未焼結ドーパント注入膜に光を照射することによって、上記未焼結ドーパント注入膜中の上記第3のシリコン粒子を焼結させてドーパント注入膜を形成し、かつ上記半導体シリコン膜の選択された領域を、上記p型又はn型ドーパントによってドープする工程。

【0066】

このように工程(a”)〜(c”)を更に含む本発明の方法では、フォトリソグラフィ工程を用いずに、選択された領域に拡散領域を形成することができる。

【0067】

具体的には例えば、本発明の方法を用いて得られるセレクティブエミッタ型太陽電池(500a)では、図4に示すように、n型半導体層(12、12a)及びp型半導体層(14、14a)を有する半導体基板(10)、半導体基板(10)の受光面側の受光面側電極(22)及び保護層(24)、半導体基板(10)の裏面側の裏面側電極(32)及び保護層(34)を有し、n型半導体層(12、12a)のうちの電極(22)に接触する領域(12a)が、ドーパント注入膜(52)に由来するn型ドーパントによって、ドーパント濃度を高められている。なお、本発明に関して、半導体基板(10)は、半導体シリコン膜、特に複数のシリコン粒子が互いに焼結されて形成された半導体シリコン膜であってよい。また、ドーパント注入膜(52)は、領域(12a)にドーパント注入した後は除去されてもよい。

【0068】

また例えば、本発明の方法を用いて得られるバックコンタクト型太陽電池(600a)では、図5に示すように、n型(又はp型)半導体からなる半導体基板(10)、半導体基板(10)の受光面側の保護層(24)、半導体基板(10)の裏面側の裏面側電極(22、32)及び保護層(34)を有し、n型半導体からなる半導体基板(10)のうちの電極(22、32)に接触する領域(12a、14a)が、ドーパント注入膜(52、62)に由来するn型及びp型ドーパントによって、ドーパント濃度を高められている。なお、本発明に関して、半導体基板(10)は、半導体シリコン膜、特に複数のシリコン粒子が互いに焼結されて形成された半導体シリコン膜であってよい。また、ドーパント注入膜(52、62)は、領域(12a、14a)にドーパント注入した後は除去されてもよい。

【0069】

本発明の方法によって、セレクティブエミッタ型太陽電池(500a)を作成する場合、例えば図6〜9で示すようにして作成することができる。

【0070】

すなわち例えば、本発明の方法を用いて、セレクティブエミッタ型太陽電池(500a)を作成する場合、n型半導体層(12)の特定の領域に、p型又はn型ドーパントによってドープされている粒子を含有する分散体を適用し、これを乾燥して、未焼結ドーパント注入膜(52a)とし(図3)、そしてこの未焼結ドーパント注入膜(52a)に光照射(200)を行うことによって、半導体層又は基板の特定の領域(12a)を、p型又はn型ドーパントによってドープすると共に、未焼結ドーパント注入膜を焼結させて、半導体層又は基板(12)と一体化したドーパント注入膜(52)とすることができる。また、その後、随意に、保護層(24)を形成し(図8)、その上から電極(22)を形成し、熱拡散によってこの電極がドーパント注入膜(52)に達するようにすることができる。

【0071】

また、例えば本発明の方法を用いて得られる電界効果トランジスタでは、図12に示すように、基材(72)、半導体シリコン膜である半導体層(78)、ゲート絶縁膜(73)、ゲート電極(74)、ソース電極(75)及びドレイン電極(76)を有し、かつソース電極及びドレイン電極と半導体層とが接触する箇所において、半導体層(78)が、n型又はp型にドープされているドープ領域(78b)を有している。ここで、ドープ領域(78b)は、ドーパント注入膜(78a)に由来するドーパントによって、ドーパント濃度を高められている。

【0072】

本発明の方法を用いて、図12で示される電界効果トランジスタを作製する場合、半導体層(78)の特定の領域に、ドーパントによってドープされている粒子を含有する分散体を適用し、これを乾燥して、未焼結ドーパント注入膜とし、そしてこの未焼結ドーパント注入膜に光照射を行うことによって、半導体層の特定の領域を、n型又はp型ドーパントによってドープすると共に、未焼結ドーパント注入膜を焼結させて、半導体層と一体化したドーパント注入膜(78a)とすることができる。

【0073】

なお、本発明の方法においては、p型又はn型ドーパントによってドープされているシリコン粒子を用いて、ドーパント注入膜を形成するのと併せて、このシリコン粒子のドーパントとは異なる型のドーパントによってドープされている他のシリコン粒子を用いて、他の型のドーパント注入膜を形成することもできる。

【0074】

ドーパントは、p型又はn型ドーパントのいずれであってもよく、例えばホウ素(B)、アルミニウム(Al)、ガリウム(Ga)、インジウム(In)、チタン(Ti)、リン(P)、ヒ素(As)、アンチモン(Sb)、又はそれらの組み合わせからなる群より選択される。

【0075】

第3のシリコン粒子がドーピングされている程度は、ドーパント注入膜、及び真性半導体元素からなる半導体層又は基板における所望のドーパント濃度等に依存して決定することができる。具体的には例えば、第3のシリコン粒子は、ドーパントを、1×1019atoms/cm3以上、1×1020atoms/cm3以上、5×1020atoms/cm3以上、又は1×1021atoms/cm3以上含むことができる。

【0076】

なお、工程(a”)〜(c”)の詳細及びそこで言及されている材料については、工程(a)〜(c)に関する上記の記載をそれぞれ参照できる。

【0077】

《半導体積層体の製造方法−半導体シリコン膜》

本発明の方法によって製造された半導体積層体の半導体シリコン膜は、キャリア移動度が、例えば0.1cm2/V・s以上、0.5cm2/V・s以上、1.0cm2/V・s以上、2.0cm2/V・s以上、5.0cm2/V・s以上、又は10.0cm2/V・s以上である。またこの半導体シリコン膜は、オン−オフ比が、例えば102以上、103以上、又は104以上である。

【0078】

《半導体デバイスの製造方法》

半導体デバイス、例えば電界効果トランジスタ(FET)又は太陽電池を製造する本発明の方法は、本発明の方法によって半導体積層体を作る工程を含む。例えば、電界効果トランジスタを製造する本発明の方法は更に、ゲート絶縁体を製造する工程、ソース及びドレイン電極を製造する工程等を含むことができる。また例えば、太陽電池を製造する本発明の方法は、本発明の方法によってN型及びP型半導体の少なくとも一方を製造する工程、集電電極を形成する工程等を含むことができる。

【0079】

《本発明の半導体積層体及び半導体デバイス》

本発明の半導体積層体は、ポリマー材料を有する基材、及びこの基材上に積層されている半導体シリコン膜を有する。ここで、この半導体積層体では、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が1.0cm2/V・s以上である。

【0080】

このような半導体積層体は、半導体シリコン膜による有益な半導体特性を提供しつつも、基材としてポリマー材料を有する基材を用いることによって、可撓性、軽量性及び/又は低コスト性を有することができる。

【0081】

このような半導体積層体は、半導体積層体を製造する本発明の方法によって製造することができる。

【0082】

本発明の半導体デバイスは、本発明の半導体積層体を有する。本発明の半導体デバイスは例えば、電界効果トランジスタ、太陽電池等であってよい。

【0083】

なお、本発明の半導体積層体及び半導体デバイスに関して、基材、シリコン粒子、キャリア移動度、オン−オフ比等については、半導体積層体を製造する本発明の方法に関する記載を参照することができる。

【実施例】

【0084】

以下では、実施例1〜5において、図1に示すボトムゲート/ボトムコンタクト構造の電界効果トランジスタ(FET)を製造し、また実施例6〜8において、図2に示すボトムゲート/ボトムコンタクト構造の電界効果トランジスタ(FET)を製造した。

【0085】

〈実施例1〉

(シリコン粒子分散体の調製)

シリコン粒子は、SiH4ガスを原料として、CO2レーザーを用いたレーザー熱分解(LP:Laser Pyrolysis)法により作製した。得られたシリコン粒子は、平均一次粒子径が約20nmであった。このシリコン粒子を、イソプロピルアルコール(IPA)中に超音波分散させて、固形分濃度3wt%のシリコン粒子分散体を得た。

【0086】

(基材の準備)

SiO2(1000nm)付きリン(P)ドープシリコン基材(オプトスター社製、比抵抗0.005Ωcm以下)を、アセトン及びイソプロピルアルコール中で各5分間ずつ超音波洗浄し、そして30分間にわたって紫外線(UV)−オゾン洗浄して、清浄化された基材を準備した。

【0087】

その後、抵抗加熱式の真空蒸着装置を用いて、基材に銀を真空蒸着して、FETのためのソース電極及びドレイン電極(チャネル長50μm及びチャネル幅1.5mm)を形成した。

【0088】

(シリコン粒子分散体の塗布)

シリコン粒子分散体を基材上に数滴滴下し、500rpmで5秒間にわたって、そして4000rpmで10秒間にわたって、スピンコートすることにより、基材にシリコン粒子分散体を塗布した。

【0089】

(シリコン粒子分散体の乾燥)

シリコン粒子分散体が塗布された基材を、70℃のホットプレート上で乾燥させることによって、シリコン粒子分散体中の分散媒であるイソプロピルアルコールを除去し、それによってシリコン粒子(平均一次粒子径約20nm)を含む未焼結シリコン粒子膜(膜厚300nm)を形成した。

【0090】

(光照射)

次に、この未焼結シリコン粒子膜に対して、レーザー光照射装置(Quantronix社製、商品名Osprey 355−2−0)を用いてYVO4レーザー(波長355nm)を照射して、未焼結シリコン粒子膜中のシリコン粒子を焼結し、それによって図1に示すFETを作製した。

【0091】

次に、この未焼結シリコン粒子膜に対して、レーザー光照射装置(Quantronix社製、商品名Osprey 355−2−0)を用いてYVO4レーザー(波長355nm)を照射して、未焼結シリコン粒子膜中のシリコン粒子を焼結し、それによって図1に示すFETを作製した。

【0092】

(評価)

作製されたFETの電気的特性評価を、半導体特性評価装置(KEITHLEY社製、商品名2636A型2chシステムソースメータ)を用いて行った。銀のソース及びドレイン電極間に10〜50V程度の一定電圧を印加した状態で、ゲートであるリン(P)ドープシリコン基材に−50〜50Vの可変電圧を印加して、ソース及びドレイン電極間に流れる電流(ドレイン電流)のゲート電圧に対する応答性を調べた。このFETの電気的特性評価の結果を表1に示す。

【0093】

〈実施例2〉

シリコン粒子分散体の固形分濃度を1wt%とし、それによって未焼結シリコン膜の厚さを100nmにしたこと、及び光照射を以下のように行なったこと以外は実施例1と同様にして、図1に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0094】

(光照射)

この実施例で使用したYVO4レーザー(波長355nm)は、断面が幅72μm及び長さ130μmの楕円形であり、それを基材上で走査させることにより、アルゴン雰囲気においてシリコン粒子を焼結した。レーザー光照射条件は、照射エネルギー75mJ/(cm2・shot)、ショット数33回、及び1ショットあたりの照射時間30ナノ秒とした。

【0095】

〈実施例3〉

光照射の際の照射エネルギーを105mJ/(cm2・shot)にしたこと以外は実施例2と同様にして、図1に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0096】

〈実施例4〉

光照射の際の照射エネルギーを104mJ/(cm2・shot)にしたこと、及び光照射後の半導体シリコン膜を下記のようにして更に処理したこと以外は実施例2と同様にして、図1に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0097】

(光照射後の半導体シリコン膜の更なる処理)

光照射の後の半導体シリコン膜上に、固形分濃度1wt%のシリコン粒子分散体を数滴滴下し、500rpmで5秒間にわたって、そして4000rpmで10秒間にわたってスピンコートして、シリコン粒子分散体を塗布した。その後、シリコン粒子分散体を、70℃のホットプレートで乾燥させ、再度、104mJ/(cm2・shot)の照射エネルギーで光照射を行った。

【0098】

〈実施例5〉

光照射を行なう雰囲気を水素(H2)を約2%含有する窒素(N2)雰囲気としたこと、照射エネルギーを104mJ/(cm2・shot)にしたこと以外は実施例2と同様にして、図1に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0099】

〈実施例6〉

(シリコン粒子分散体の調製)

固形分濃度を1wt%としたこと以外は実施例1と同様にして、シリコン粒子分散体を得た。

【0100】

(基材の準備)

インジウム亜鉛酸化物(IZO)電極付き耐熱性ポリカーボネート基材(帝人株式会社製、SS120−B30、ガラス転移温度:215℃)を、30分間にわたって紫外線(UV)−オゾン洗浄して、清浄化された基材を準備した。

【0101】

その後、この基材上に、FETのゲート絶縁膜となるメチルシルセスキオキサン(MSQ)膜を作製した。具体的には、プロピレングリコールモノメチルエーテルアセテート(PGMEA)中にMSQが溶解した固形分濃度30wt%の溶液(Honeywell社製、商品名PTS R−6)を、IZO電極付きポリカーボネート基材に数滴滴下し、500rpmで5秒間にわたって、そして3200rpmで20秒間にわたってスピンコートし、そしてその後で、炉中で80℃で5分間にわたって、そして大気中で180℃で30分間にわたって加熱及び乾燥して、MSQ膜を得た。MSQ膜の膜厚は800nmであった。

【0102】

その後、実施例1と同様にして、基材に銀を真空蒸着して、FETのためのソース電極及びドレイン電極を形成した。

【0103】

(シリコン粒子分散体の塗布及び乾燥)

実施例1と同様にして、基材にシリコン粒子分散体を塗布し、そして乾燥した。ただし、この実施例では、得られた未焼結シリコン粒子膜の膜厚は100nmであった。

【0104】

(光照射)

次に、実施例1と同様にして、光照射を行って、図2に示すFETを作製した。

【0105】

ただし、ここで、照射したYVO4レーザーは、断面が幅72μm及び長さ130μmの楕円形であり、それを基材上で走査させることにより、アルゴン雰囲気中においてシリコン粒子を焼結した。レーザー光照射条件は、照射エネルギー75mJ/(cm2・shot)、ショット数33回であり、及び1ショットあたりの照射時間30ナノ秒とした。

【0106】

(評価)

このFETの電気的特性評価の結果を表1に示す。

【0107】

〈実施例7〉

光照射の際の照射エネルギーを89mJ/(cm2・shot)にしたこと以外は実施例6と同様にして、図2に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0108】

〈実施例8〉

光照射の際の照射エネルギーを104mJ/(cm2・shot)にしたこと以外は実施例6と同様にして、図2に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0109】

〈実施例9〉

(シリコン粒子分散体の調製)

シリコン粒子の平均一次粒子径が約7nmであること、シリコン粒子分散体の固形分濃度が2.7wt%であること以外は実施例1と同様にして、シリコン粒子分散体を調製した。

【0110】

(基材の準備)

基材としては実施例6と同様に、IZO電極付きポリカーボネート基材上にMSQ膜(膜厚800nm)を積層したものを用いた。

【0111】

(シリコン粒子分散体の塗布及び乾燥)

実施例1と同様にして、基材にシリコン粒子分散体を塗布し、そして乾燥した。未焼結シリコン粒子膜の膜厚は300nmであった。

【0112】

(光照射)

照射エネルギーが140mJ/(cm2・Shot)であること、ショット数20回であること以外は実施例1と同様にして、YVO4レーザー照射を行って、半導体シリコン膜を得た。

【0113】

(リンドープシリコン層の形成)

得られた半導体シリコン膜上に、固形分濃度2.6wt%のリン(P)でドープされたシリコン粒子の分散体を数滴滴下し、実施例1と同様に塗布及び乾燥を行って、リンドープシリコン粒子からなる未焼結シリコン粒子膜を得た。得られた未焼結シリコン粒子膜の厚さは250nmであった。

【0114】

その後、ソース電極及びドレイン電極を配置する予定の領域を、照射エネルギー120mJ/(cm2・shot)及びショット数20回の条件で光照射した。

【0115】

その後、前記光照射を行った領域に、抵抗加熱式の真空蒸着装置を用いて、銀を真空蒸着して、ソース電極およびドレイン電極(チャネル長120μ及びチャネル幅1.5mm)を形成した。

【0116】

このようにして得られたリンドープシリコン層は、薄膜トランジスタのソース電極及びドレイン電極と半導体シリコン層との間のコンタクトを容易にするために有益である。

得られたFETを図3に示す。このFETの電気的特性評価の結果を表1に示す。

【0117】

【表1】

【符号の説明】

【0118】

110、120、130 半導体積層体

112 リン(P)ドープシリコン基材

114 酸化ケイ素(SiO2)ゲート絶縁膜

115、116、125、126 銀(Ag)のソース電極及びドレイン電極

118、128 半導体シリコン膜

122 ポリカーボネート(PC)基材

123 酸化インジウム亜鉛(IZO)ゲート電極

124 メチルシルセスキオキサン(MSQ)ゲート絶縁膜

128 半導体シリコン膜

128a ドーパント注入膜

128b 半導体シリコン膜のドープ領域

10 半導体基板

12、12a n型半導体層

14、14a p型半導体層

22 受光面側電極

24 保護層

32 裏面側電極

34 保護層

52 ドーパント注入膜

52a 未焼結ドーパント注入膜

62 ドーパント注入膜

72 基材

73 ゲート絶縁膜

74 ゲート電極

75 ソース電極

76 ドレイン電極

78 半導体層

78a ドーパント注入膜

78b ドープ領域

500 従来のセレクティブエミッタ型太陽電池

600 従来のバックコンタクト型太陽電池

500a 本発明のセレクティブエミッタ型太陽電池

600a 本発明のバックコンタクト型太陽電池

700 従来の電界効果トランジスタ

700a 本発明の電界効果トランジスタ

【技術分野】

【0001】

本発明は、基材及びこの基材上に積層されている半導体シリコン膜を有する半導体積層体、及びその製造方法に関する。また、本発明は、このような半導体積層体を有する半導体デバイス、及びその製造方法に関する。

【背景技術】

【0002】

半導体シリコン膜、例えばアモルファスシリコン膜及びポリシリコン膜等は、半導体デバイス、例えば薄膜トランジスタ(TFT)のために使用されている。このような半導体シリコン膜を半導体デバイスで使用する場合、半導体シリコン膜が所望のパターン、例えば回路パターンを有することが必要である。したがって一般に、半導体シリコン膜を、スパッタリングのような物理気相堆積(PVD)、プラズマ化学気相堆積のような化学気相堆積(CVD)等の真空プロセスにより基材の全面に形成し、そしてその後で、得られた半導体シリコン膜の不要部分を、フォトリソグラフィー等によって除去して、所望のパターンを有する半導体シリコン膜を提供することが行われてきた。

【0003】

しかしながら、これらの従来の方法では、大掛かりな装置が必要であること、多大なエネルギーを消費すること、プロセス温度が高温(250℃超)であるのでプロセス毎の冷却に多大な時間を要すること、原料の使用効率が悪いこと(5%未満)、原料が気体であるので扱いにくいこと、大量の廃棄物が発生すること等の問題を有しており、それによって複雑かつ高コストの方法であった。

【0004】

したがって近年、比較的低温で薄膜トランジスタ等のための半導体膜を形成する方法として、液相法が検討されている。液相法では、一般に、プロセス全体を、比較的低温、例えばポリマー材料のガラス転移温度以下の温度で行うことができる。このような低温プロセスでは、安価な汎用ポリマー材料を半導体膜の基材において用いることが可能になり、それによって半導体デバイスの大面積化、フレキシブル化、軽量化、低コスト化も期待できる。また、こうした低温プロセスでは、プロセス毎の冷却が必要ないのでプロセス時間を短縮できる。

【0005】

このような液相法による半導体膜の製造に関して、有機半導体材料を用いることが検討されている。

【0006】

しかしながら、有機半導体膜は、シリコン半導体膜に比して、キャリア移動度のような性能、及び大気中での安定性のような耐久性が不充分であり、したがって用途が限定されると共に、製品化が難しいのが現状である。

【0007】

また、液相法を用いた半導体膜の製造に関して、無機化合物半導体材料を用いることも検討されている。

【0008】

これに関して例えば、特許文献1では、ナノ粒子分散液を用いて、InGaZnO4膜を成膜する方法が開示されている。特許文献1では、室温で乾燥したInGaZnO4膜を、紫外線(UV)オゾンクリーナーで前処理し、そしてその後で、KrFエキシマレーザー(波長:248nm)で照射することによって、比較的均一なInGaZnO4の結晶膜を成膜している。特許文献1では、このような方法によって、キャリア移動度1.2cm2/V・sの薄膜トランジスタを作製している。

【0009】

しかしながら、InGaZnO4など無機化合物半導体材料は、原材料入手の問題から、シリコン半導体に比して非常に高価であり、一般的なTFT材料として実用的ではない。

【0010】

また、液相法を用いた半導体膜の製造に関して、有機シリコン化合物溶液、例えば水素化環状シラン化合物を含有するシリコン溶液を用いて、半導体ポリシリコン膜を製造することが検討されている。

【0011】

これに関して例えば、特許文献2及び3では、高分子量の低揮発性ポリシラン化合物を含有する有機シリコン化合物溶液を使用している。ここで、この低揮発性ポリシラン化合物は、シクロペンタシランを前駆体として得ている。

【0012】

しかしながら、有機シリコン化合物溶液では、爆発性を低減するために、脱水素アニール処理(400〜500℃)をすることが必要な場合があり、したがってプロセス全体を低温化することが困難である。

【0013】

また、特許文献4では、シリコン粒子を含有する分散体を用いて、半導体シリコン膜を形成することを提案している。

【0014】

液相法の使用に関して、半導体シリコン膜の所望のパターンを基材上に直接に描く直接描画技術を利用することも検討されている。直接描画技術としては、半導体シリコン膜の構成材料を含む原料液を塗布印刷する印刷法、例えばインクジェットプリンティング法、スクリーン印刷法等が挙げられる。

【0015】

このような印刷法では、真空プロセスは不要であり、また直接描画によりパターン形成を行うことができるので、簡易かつ低コストで、半導体デバイスを製造することができる。

【0016】

なお、ある種の半導体デバイスの製造においては、リン又はホウ素のようなドーパントを選択された領域において半導体層又は基板に注入して、選択された領域に拡散領域を形成することが行われている。特に、ある種の太陽電池の製造においては、ドーパントを選択された領域において半導体層又は基板に注入して、選択された領域に拡散領域又はドープ領域を形成することが行われている。

【0017】

このような拡散領域又はドープ領域を必要とする太陽電池としては、セレクティブ(選択)エミッタ型太陽電池、及びバックコンタクト型太陽電池を挙げることができる。

【0018】

セレクティブエミッタ型太陽電池は例えば、特許文献5で示されるようなものである。

【0019】

例えば具体的には、セレクティブエミッタ型太陽電池(500)は、図10に示すように、n型半導体層(12、12a)及びp型半導体層(14、14a)を有する半導体基板(10)、半導体基板(10)の受光面側の受光面側電極(22)及び保護層(24)、半導体基板(10)の裏面側の裏面側電極(32)及び保護層(34)を有し、n型半導体層(12、12a)のうちの電極(32)に接触する領域(12a)において選択的に、ドーパントの濃度が高くされている。

【0020】

セレクティブエミッタ型太陽電池は、このように、電極に接触する領域(12a)において選択的にドーパントの濃度が高くされていることによって、受光面側のドーパントの濃度が高いことによって起こる問題、すなわち例えば高ドーパント濃度層による受光側表面による反射の増加という問題を防ぎつつ、電極に接触する領域においてドーパントの濃度が高いことによる利益、すなわち例えば電極と半導体層との間のオーミック接触という利益を達成するものである。

【0021】

なお、図10において、発電のために太陽電池(500)に照射される光は、番号100で示されている。また、図10において、光起電力の発生のためにn及びpドープされている領域は、それぞれ記号n及びpで示されており、またエミッタを形成するために高濃度にn及びpドープされている領域は、それぞれ記号n++及びp++で示されている。具体的には、例えば、シリコンからなる太陽電池素子の場合であれば、n++及びp++の領域におけるドーパント濃度は、約1〜2×1021atom/cm3の量である。

【0022】

バックコンタクト型太陽電池は例えば、特許文献6及び7で示されるようなものである。

【0023】

例えば具体的には、バックコンタクト型太陽電池(600)は、図11に示すように、n型(又はp型若しくは真性)半導体からなる半導体基板(10)、半導体基板(10)の受光面側の保護層(24)、半導体基板(10)の裏面側の裏面側電極(22、32)及び保護層(34)を有し、n型半導体からなる半導体基板(10)のうちの電極(32、34)に接触する領域(12a、14a)において選択的に、ドーパントの濃度が高くされている。

【0024】

バックコンタクト型太陽電池(600)は、このように、裏面側において、高濃度にpドープされた領域(14a)と高濃度にnドープされた領域(12a)とが交互に配置されている。その他の部分は、真性半導体領域、低濃度にp若しくはnドープされた領域、又はp−n接合が形成されている領域であり、その領域に光が照射されることによって起電力が発生する。このようにして発生した起電力は、高濃度にドープされた領域を介して接している電極により取り出される。ここで、高濃度にp又はnドープされた領域を設けることで、接触抵抗による起電のロスを低く抑えて、電力を取り出すことができるという利点を有している。

【0025】

なお、図11において、発電のために太陽電池(600)に照射される光は、番号100で示されている。また、図11において、光起電力の発生のためにn(又はp)ドープされている領域は、記号n(p)で示されており、また高濃度にn及びpドープされている領域は、それぞれ記号n++及びp++で示されている。

【0026】

拡散領域又はドープ領域を必要とするトランジスタとしては、電界効果トランジスタ(FET:Field Effect Transistor)を挙げることができる。

【0027】

具体的には例えば、電界効果トランジスタ(700)は、図13に示すように、基材(72)、半導体層(78)、ゲート絶縁膜(73)、ゲート電極(74)、ソース電極(75)及びドレイン電極(76)を有し、ソース電極及びドレイン電極と半導体層とが接触する箇所において、半導体層(78)が、n型又はp型にドープされているドープ領域(78b)を有している。このような電界効果トランジスタでは、このドープ領域によって、半導体基板と電極との間のオーミック接触が促進されている。

【0028】

上記セレクティブエミッタ型太陽電池、バックコンタクト型太陽電池、又は電界効果トランジスタでのように、選択された領域に拡散領域又はドープ領域を形成するためには一般に、ドーパント源を層又は基板と接触させ、熱やレーザー照射を行って、層又は基板にドーパントを注入する方法が知られている。ここで用いられるドーパント源としては、ボロンシリケートガラス又はリンガラス(特許文献7)、無機ドーパントを含む液体(特許文献8)、又はシリコン及び/又はゲルマニウムのナノ粒子を含有するインク(特許文献9及び10)を使用することが知られている。

【先行技術文献】

【特許文献】

【0029】

【特許文献1】特開2009−147192号公報

【特許文献2】特開2004−87546号公報(特許4016419号に対応)

【特許文献3】特表2010−506001号公報

【特許文献4】特表2010−514585号公報

【特許文献5】特開2010−186900号公報

【特許文献6】特表2009−521805号公報

【特許文献7】特開2010−262979号公報

【特許文献8】特開平07−297429号公報

【特許文献9】特表2010−519731号公報

【特許文献10】特表2010−514585号公報

【発明の概要】

【発明が解決しようとする課題】

【0030】

本発明の目的は、比較的低温において効率的に半導体シリコン膜を製造する方法を提供することである。より具体的には、本発明の目的は、高価かつエネルギー多消費型の大掛かりな装置を必要とせずに、プラスチック基板等の比較的耐熱性が低い基板上に半導体膜を形成できる、半導体積層体の製造方法を提供することである。

【0031】

また、本発明の目的は、ポリマー材料を有する基材、及びこの基材上に積層されている半導体シリコン膜を有する半導体積層体を提供することである。

【0032】

さらに、本発明の目的は、フォトリソグラフィ工程を用いずに、選択された領域に拡散領域を形成することができる半導体積層体の製造方法を提供することである。

【0033】

本発明の他の目的は、本願の明細書及び特許請求の範囲の記載から明らかになる。

【課題を解決するための手段】

【0034】

基材及びこの基材上に積層されている半導体シリコン膜を有する半導体積層体を製造する本発明の方法は、下記の工程(a)〜(c)を含む:

(a)分散媒及び上記分散媒中に分散しているシリコン粒子を含有するシリコン粒子分散体を、基材上に塗布して、シリコン粒子分散体膜を形成する工程、

(b)上記シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び

(c)上記未焼結半導体シリコン膜に光を照射して、上記未焼結半導体シリコン膜中の上記シリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程、

【0035】

また、本発明の半導体積層体は、ポリマー材料を有する基材、及びこの基材上に積層されている半導体シリコン膜を有する。ここで、この半導体積層体では、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が1.0cm2/V・s以上である。

【0036】

また、本発明の半導体積層体は、基材、この基材上に積層されている半導体シリコン膜、及びこの半導体シリコン膜上に積層されているドーパント注入膜を有する。ここで、この半導体積層体では、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つドーパント注入膜が、互いに焼結されている複数のシリコン粒子から作られている。

【発明の効果】

【0037】

半導体積層体を製造する本発明の方法によれば、所望の半導体特性を有する半導体積層体を簡便な方法により形成できる。具体的には、この本発明の方法によれば、従来技術のプロセス温度と比較して低温で、良好な半導体特性を有する半導体積層体を製造することができる。

【0038】

また、本発明の半導体積層体は、半導体特性、コスト、可撓性、及び/又は軽量性に関して好ましい半導体デバイスのために利用することができる。

【図面の簡単な説明】

【0039】

【図1】実施例1〜5において製造したボトムゲート・ボトムコンタクト構造の電界効果トランジスタ(FET)を示す図である。

【図2】実施例6〜8において製造したボトムゲート・ボトムコンタクト構造の電界効果トランジスタ(FET)を示す図である。

【図3】実施例9において製造したボトムゲート・トップコンタクト構造の電界効果トランジスタ(FET)を示す図である。

【図4】本発明のセレクティブエミッタ型太陽電池を説明するための図である。

【図5】本発明のバックコンタクト型太陽電池を説明するための図である。

【図6】セレクティブエミッタ型太陽電池を製造する本発明の方法を説明するための図である。

【図7】セレクティブエミッタ型太陽電池を製造する本発明の方法を説明するための図である。

【図8】セレクティブエミッタ型太陽電池を製造する本発明の方法を説明するための図である。

【図9】セレクティブエミッタ型太陽電池を製造する本発明の方法を説明するための図である。

【図10】従来のセレクティブエミッタ型太陽電池を説明するための図である。

【図11】従来のバックコンタクト型太陽電池を説明するための図である。

【図12】本発明の電界効果トランジスタを説明するための図である。

【図13】従来の本発明の電界効果トランジスタを説明するための図である。

【発明を実施するための形態】

【0040】

《半導体積層体の製造方法》

基材及びこの基材上に積層されている半導体シリコン膜を有する半導体積層体を製造する本発明の方法は、下記の工程(a)〜(c)を含む:

(a)分散媒及び上記分散媒中に分散しているシリコン粒子を含有するシリコン粒子分散体を、基材上に塗布して、シリコン粒子分散体膜を形成する工程、

(b)上記シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び

(c)上記未焼結半導体シリコン膜に光を照射して、上記未焼結半導体シリコン膜中の上記シリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程。

【0041】

《半導体積層体の製造方法−工程(a)》

本発明の方法の工程(a)では、分散媒及び上記分散媒中に分散しているシリコン粒子を含有するシリコン粒子分散体を、基材上に塗布して、シリコン粒子分散体膜を形成する。

【0042】

(分散媒)

シリコン粒子分散体の分散媒は、本発明の目的及び効果を損なわない限り制限されるものではなく、したがって例えばシリコン粒子と反応しない有機溶媒を用いることができる。具体的にはこの分散媒は、非水系溶媒、例えばアルコール、アルカン、アルケン、アルキン、ケトン、エーテル、エステル、芳香族化合物、又は含窒素環化合物、特にイソプロピルアルコール(IPA)、N−メチル−2−ピロリドン(NMP)等であってよい。また、アルコールとしては、エチレングリコールのようなグリコール(2価アルコール)を用いることもできる。なお、分散媒は、シリコン粒子の酸化を抑制するために、脱水溶媒であることが好ましい。

【0043】

(シリコン粒子)

シリコン粒子分散体のシリコン粒子は、本発明の目的及び効果を損なわない限り制限されるものではなく、例えば特許文献4で示されるようなシリコン粒子を用いることができる。具体的には、このシリコン粒子としては、レーザー熱分解法、特にCO2レーザーを用いたレーザー熱分解法によって得られたシリコン粒子を挙げることができる。

【0044】

このシリコン粒子は、多結晶又は単結晶のコア、及びアモルファスの外側層からなるシリコン粒子であってよい。この場合には、多結晶又は単結晶のコアによる半導体特性と、アモルファスの外側層による焼結容易性との組合せを利用することができる。

【0045】

また、シリコン粒子は好ましくは、平均一次粒子径が、100nm以下である。したがってシリコン粒子は例えば、1nm以上、又は5nm以上であって、100nm以下、50nm以下、又は30nm以下であってよい。平均一次粒子径が100nm以下であることは、光によるシリコン粒子の焼結を行うために好ましい。

【0046】

なお、シリコン粒子の平均一次粒子径は、走査型電子顕微鏡(SEM)、透過型電子顕微鏡(TEM)等による観察によって、撮影した画像を元に直接粒子径を計測し、集合数100以上からなる粒子群を解析することで、数平均平均一次粒子径として求めることができる。

【0047】

本発明の方法で用いられるシリコン粒子分散体は、上記の分散媒及びシリコン粒子以外に、リン、ホウ素等のドーパントや公知の添加剤を含んでいてもよい。

【0048】

(基材)

本発明の方法で用いられる基材は、本発明の目的及び効果を損なわない限り制限されるものではない。しかしながら、本発明の方法では、比較的低温において、基材上で半導体シリコン膜を形成することができるので、耐熱性が比較的低い基材、例えばポリマー材料を有する基材を用いることができる。ポリマー材料を有する基材としては特に、表面に導電性膜を付与されたポリマー材料からなる基材を用いることができる。また、導電性膜は、金属、金属酸化物、特にインジウム亜鉛酸化物(IZO)、インジウムスズ酸化物(ITO)のような透明導電性酸化物であってよい。

【0049】

本発明の製造方法は低温プロセスで行うことができるため、基材のためのポリマー材料としては、ガラス転移温度が、300℃以下、250℃以下、200℃以下、100℃以下、又は50℃以下であるポリマー材料を用いることができる。

【0050】

したがって例えばポリマー材料としては、ポリイミド、ポリエーテルスルホン、ポリカーボネート、ポリエチレンテレフタレート、及びポリエチレンナフタレートからなる群から選択される少なくとも1種を含むポリマー材料を用いることができる。また、これらのうちで、ポリカーボネート、ポリエチレンテレフタレート及びポリエチレンナフタレートからなる群から選択される少なくとも1種を含むポリマー材料、特にポリカーボネートを50質量%以上含むポリマー材料は、これらのポリマーが汎用性であり、かつ安価である点で好ましい。

【0051】

(塗布)

シリコン粒子分散体の塗布は、シリコン粒子分散体を所望の厚さ及び均一性で塗布できる方法であれば特に限定されず、例えばインクジェット法、スピンコーティング法等によって行うことができる。

【0052】

また、この塗布は、シリコン粒子分散体膜を乾燥したときに得られる未焼結半導体シリコン膜の厚さが、50nm以上、100nm以上、又は200nm以上であって、2000nm以下、1000nm以下、500nm以下、又は300nm以下であるように行うことができる。具体的には、例えば電界効果トランジスタ(FET)を得る場合には、未焼結半導体シリコン膜の厚さが、50nm以上、100nm以上であって、500nm以下、300nm以下であるように塗布を行うことができる。また、太陽電池を得る場合には、未焼結半導体シリコン膜の厚さが、100nm以上、200nm以上であって、2000nm以下、1000nm以下、500nm以下、又は300nm以下であるように塗布を行うことができる。

【0053】

《半導体積層体の製造方法−工程(b)》

本発明の方法の工程(b)では、シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する。

【0054】

(乾燥)

この乾燥は、シリコン粒子分散体膜から分散媒を実質的に除去することができる方法であれば特に限定されず、例えばシリコン粒子分散体膜を有する基材を、ホットプレート上に配置して行うことができる。

【0055】

乾燥温度は例えば、基材を変形、劣化等させないように選択することができ、例えば50℃以上、70℃以上、90℃以上であって、100℃以下、150℃以下、200℃以下、又は250℃以下であるように選択できる。

【0056】

《半導体積層体の製造方法−工程(c)》

本発明の方法の工程(c)では、未焼結半導体シリコン膜に光を照射して、未焼結半導体シリコン膜中のシリコン粒子を焼結させ、それによって半導体シリコン膜を形成する。

【0057】

(照射される光)

ここで照射される光としては、未焼結半導体シリコン膜中のシリコン粒子の焼結を達成できれば任意の光を用いることができ、例えばレーザー光、特に波長600nm以下、500nm以下又は400nm以下であって、300nm以上のレーザーを用いて行なうことができる。また、シリコン粒子の焼結は、キセノンフラッシュランプのようなフラッシュランプを用いて行うこともできる。

【0058】

光照射をパルス状の光を用いて行う場合、パルス状の光の照射回数は例えば、1回以上、2回以上、5回以上、又は10回以上であって、100回以下、80回以下、又は50回以下にすることができる。また、パルス状の光の照射エネルギーは例えば、15mJ/(cm2・shot)以上、50mJ/(cm2・shot)以上、100mJ/(cm2・shot)以上、150mJ/(cm2・shot)以上、又は200mJ/(cm2・shot)以上であって、500mJ/(cm2・shot)以下、300mJ/(cm2・shot)以下、又は250mJ/(cm2・shot)以下にすることができる。さらに、パルス状の光の照射時間は、例えば200ナノ秒/shot以下、100ナノ秒/shot以下、50ナノ秒/shot以下にすることができる。

【0059】

ここで、光の照射回数が少なすぎる場合には、所望の焼結を達成するために必要とされる1回のパルス当たりのエネルギーが大きくなり、したがって半導体シリコン膜が破損する恐れがある。また、光の照射回数が少なすぎる場合には、必要とされる処理時間が過度に長くなる恐れがある。

【0060】

また、上記のようにパルス状の光の照射回数、照射エネルギー、及び照射時間を選択することは、特に基材がポリマー材料を有する場合に、熱によるポリマー材料の劣化を抑制しつつ、シリコン粒子の焼結を達成するために好ましいことがある。

【0061】

(照射雰囲気)

シリコン粒子を焼結するための光照射は、非酸化性雰囲気、例えば水素、希ガス、窒素、及びそれらの組合せからなる雰囲気において行うことが、シリコン粒子の酸化を防ぐために好ましい。ここで、希ガスとしては、特にアルゴン、ヘリウム、及びネオンを挙げることができる。なお、雰囲気が水素を含有することは、未焼結半導体シリコン膜のシリコン粒子の酸化を抑制するために好ましい。また、非酸化性雰囲気とするために、雰囲気の酸素含有率は、1体積%以下、0.5体積%以下、0.1体積%以下、又は0.01体積%以下とすることができる。

【0062】

《半導体積層体の製造方法−追加の工程(第2の半導体シリコン膜)》

また、半導体積層体を製造する本発明の方法は、下記の工程(a’)〜(c’)を更に含むことができる:

(a’)第2の分散媒及び上記第2の分散媒中に分散している第2のシリコン粒子を含有する第2のシリコン粒子分散体を、工程(c)において得られた上記半導体シリコン膜に塗布して、第2のシリコン粒子分散体膜を形成する工程、

(b’)上記第2のシリコン粒子分散体膜を乾燥して、第2の未焼結半導体シリコン膜を形成する工程、及び

(c’)上記第2の未焼結半導体シリコン膜に光を照射して、上記第2の未焼結半導体シリコン膜中の上記第2のシリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程。

【0063】

このように工程(a’)〜(c’)を更に含む本発明の方法では、半導体特性が更に優れた半導体シリコン膜を得ることができる。本発明は原理によって限定されるものではないが、これは、工程(a)〜(c)によって得られた半導体シリコン膜の空隙を、工程(a’)及び(b’)において塗布及び乾燥された第2のシリコン粒子分散体中のシリコン粒子が充填し、そして工程(c’)においてこのシリコン粒子が焼結して半導体シリコン膜の一部となることによって、緻密な半導体シリコン膜が得られることによると考えられる。

【0064】

なお、工程(a’)〜(c’)の詳細及びそこで言及されている材料については、工程(a)〜(c)に関する上記の記載をそれぞれ参照できる。

【0065】

《半導体積層体の製造方法−追加の工程(ドーパント注入膜)》

また、半導体積層体を製造する本発明の方法は、下記の工程(a”)〜(c”)を更に含むことができる:

(a”)第3の分散媒及び上記第3の分散媒中に分散している第3のシリコン粒子を含有する第3のシリコン粒子分散体を、工程(c)又は(c’)において得られた上記半導体シリコン膜の選択された領域に塗布して、第3のシリコン粒子分散体膜を形成する工程であって、上記第3のシリコン粒子が、p型又はn型ドーパントによってドープされている工程、

(b”)上記第3のシリコン粒子分散体膜を乾燥して、未焼結ドーパント注入膜を形成する工程、及び

(c”)上記未焼結ドーパント注入膜に光を照射することによって、上記未焼結ドーパント注入膜中の上記第3のシリコン粒子を焼結させてドーパント注入膜を形成し、かつ上記半導体シリコン膜の選択された領域を、上記p型又はn型ドーパントによってドープする工程。

【0066】

このように工程(a”)〜(c”)を更に含む本発明の方法では、フォトリソグラフィ工程を用いずに、選択された領域に拡散領域を形成することができる。

【0067】

具体的には例えば、本発明の方法を用いて得られるセレクティブエミッタ型太陽電池(500a)では、図4に示すように、n型半導体層(12、12a)及びp型半導体層(14、14a)を有する半導体基板(10)、半導体基板(10)の受光面側の受光面側電極(22)及び保護層(24)、半導体基板(10)の裏面側の裏面側電極(32)及び保護層(34)を有し、n型半導体層(12、12a)のうちの電極(22)に接触する領域(12a)が、ドーパント注入膜(52)に由来するn型ドーパントによって、ドーパント濃度を高められている。なお、本発明に関して、半導体基板(10)は、半導体シリコン膜、特に複数のシリコン粒子が互いに焼結されて形成された半導体シリコン膜であってよい。また、ドーパント注入膜(52)は、領域(12a)にドーパント注入した後は除去されてもよい。

【0068】

また例えば、本発明の方法を用いて得られるバックコンタクト型太陽電池(600a)では、図5に示すように、n型(又はp型)半導体からなる半導体基板(10)、半導体基板(10)の受光面側の保護層(24)、半導体基板(10)の裏面側の裏面側電極(22、32)及び保護層(34)を有し、n型半導体からなる半導体基板(10)のうちの電極(22、32)に接触する領域(12a、14a)が、ドーパント注入膜(52、62)に由来するn型及びp型ドーパントによって、ドーパント濃度を高められている。なお、本発明に関して、半導体基板(10)は、半導体シリコン膜、特に複数のシリコン粒子が互いに焼結されて形成された半導体シリコン膜であってよい。また、ドーパント注入膜(52、62)は、領域(12a、14a)にドーパント注入した後は除去されてもよい。

【0069】

本発明の方法によって、セレクティブエミッタ型太陽電池(500a)を作成する場合、例えば図6〜9で示すようにして作成することができる。

【0070】

すなわち例えば、本発明の方法を用いて、セレクティブエミッタ型太陽電池(500a)を作成する場合、n型半導体層(12)の特定の領域に、p型又はn型ドーパントによってドープされている粒子を含有する分散体を適用し、これを乾燥して、未焼結ドーパント注入膜(52a)とし(図3)、そしてこの未焼結ドーパント注入膜(52a)に光照射(200)を行うことによって、半導体層又は基板の特定の領域(12a)を、p型又はn型ドーパントによってドープすると共に、未焼結ドーパント注入膜を焼結させて、半導体層又は基板(12)と一体化したドーパント注入膜(52)とすることができる。また、その後、随意に、保護層(24)を形成し(図8)、その上から電極(22)を形成し、熱拡散によってこの電極がドーパント注入膜(52)に達するようにすることができる。

【0071】

また、例えば本発明の方法を用いて得られる電界効果トランジスタでは、図12に示すように、基材(72)、半導体シリコン膜である半導体層(78)、ゲート絶縁膜(73)、ゲート電極(74)、ソース電極(75)及びドレイン電極(76)を有し、かつソース電極及びドレイン電極と半導体層とが接触する箇所において、半導体層(78)が、n型又はp型にドープされているドープ領域(78b)を有している。ここで、ドープ領域(78b)は、ドーパント注入膜(78a)に由来するドーパントによって、ドーパント濃度を高められている。

【0072】

本発明の方法を用いて、図12で示される電界効果トランジスタを作製する場合、半導体層(78)の特定の領域に、ドーパントによってドープされている粒子を含有する分散体を適用し、これを乾燥して、未焼結ドーパント注入膜とし、そしてこの未焼結ドーパント注入膜に光照射を行うことによって、半導体層の特定の領域を、n型又はp型ドーパントによってドープすると共に、未焼結ドーパント注入膜を焼結させて、半導体層と一体化したドーパント注入膜(78a)とすることができる。

【0073】

なお、本発明の方法においては、p型又はn型ドーパントによってドープされているシリコン粒子を用いて、ドーパント注入膜を形成するのと併せて、このシリコン粒子のドーパントとは異なる型のドーパントによってドープされている他のシリコン粒子を用いて、他の型のドーパント注入膜を形成することもできる。

【0074】

ドーパントは、p型又はn型ドーパントのいずれであってもよく、例えばホウ素(B)、アルミニウム(Al)、ガリウム(Ga)、インジウム(In)、チタン(Ti)、リン(P)、ヒ素(As)、アンチモン(Sb)、又はそれらの組み合わせからなる群より選択される。

【0075】

第3のシリコン粒子がドーピングされている程度は、ドーパント注入膜、及び真性半導体元素からなる半導体層又は基板における所望のドーパント濃度等に依存して決定することができる。具体的には例えば、第3のシリコン粒子は、ドーパントを、1×1019atoms/cm3以上、1×1020atoms/cm3以上、5×1020atoms/cm3以上、又は1×1021atoms/cm3以上含むことができる。

【0076】

なお、工程(a”)〜(c”)の詳細及びそこで言及されている材料については、工程(a)〜(c)に関する上記の記載をそれぞれ参照できる。

【0077】

《半導体積層体の製造方法−半導体シリコン膜》

本発明の方法によって製造された半導体積層体の半導体シリコン膜は、キャリア移動度が、例えば0.1cm2/V・s以上、0.5cm2/V・s以上、1.0cm2/V・s以上、2.0cm2/V・s以上、5.0cm2/V・s以上、又は10.0cm2/V・s以上である。またこの半導体シリコン膜は、オン−オフ比が、例えば102以上、103以上、又は104以上である。

【0078】

《半導体デバイスの製造方法》

半導体デバイス、例えば電界効果トランジスタ(FET)又は太陽電池を製造する本発明の方法は、本発明の方法によって半導体積層体を作る工程を含む。例えば、電界効果トランジスタを製造する本発明の方法は更に、ゲート絶縁体を製造する工程、ソース及びドレイン電極を製造する工程等を含むことができる。また例えば、太陽電池を製造する本発明の方法は、本発明の方法によってN型及びP型半導体の少なくとも一方を製造する工程、集電電極を形成する工程等を含むことができる。

【0079】

《本発明の半導体積層体及び半導体デバイス》

本発明の半導体積層体は、ポリマー材料を有する基材、及びこの基材上に積層されている半導体シリコン膜を有する。ここで、この半導体積層体では、半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ半導体シリコン膜のキャリア移動度が1.0cm2/V・s以上である。

【0080】

このような半導体積層体は、半導体シリコン膜による有益な半導体特性を提供しつつも、基材としてポリマー材料を有する基材を用いることによって、可撓性、軽量性及び/又は低コスト性を有することができる。

【0081】

このような半導体積層体は、半導体積層体を製造する本発明の方法によって製造することができる。

【0082】

本発明の半導体デバイスは、本発明の半導体積層体を有する。本発明の半導体デバイスは例えば、電界効果トランジスタ、太陽電池等であってよい。

【0083】

なお、本発明の半導体積層体及び半導体デバイスに関して、基材、シリコン粒子、キャリア移動度、オン−オフ比等については、半導体積層体を製造する本発明の方法に関する記載を参照することができる。

【実施例】

【0084】

以下では、実施例1〜5において、図1に示すボトムゲート/ボトムコンタクト構造の電界効果トランジスタ(FET)を製造し、また実施例6〜8において、図2に示すボトムゲート/ボトムコンタクト構造の電界効果トランジスタ(FET)を製造した。

【0085】

〈実施例1〉

(シリコン粒子分散体の調製)

シリコン粒子は、SiH4ガスを原料として、CO2レーザーを用いたレーザー熱分解(LP:Laser Pyrolysis)法により作製した。得られたシリコン粒子は、平均一次粒子径が約20nmであった。このシリコン粒子を、イソプロピルアルコール(IPA)中に超音波分散させて、固形分濃度3wt%のシリコン粒子分散体を得た。

【0086】

(基材の準備)

SiO2(1000nm)付きリン(P)ドープシリコン基材(オプトスター社製、比抵抗0.005Ωcm以下)を、アセトン及びイソプロピルアルコール中で各5分間ずつ超音波洗浄し、そして30分間にわたって紫外線(UV)−オゾン洗浄して、清浄化された基材を準備した。

【0087】

その後、抵抗加熱式の真空蒸着装置を用いて、基材に銀を真空蒸着して、FETのためのソース電極及びドレイン電極(チャネル長50μm及びチャネル幅1.5mm)を形成した。

【0088】

(シリコン粒子分散体の塗布)

シリコン粒子分散体を基材上に数滴滴下し、500rpmで5秒間にわたって、そして4000rpmで10秒間にわたって、スピンコートすることにより、基材にシリコン粒子分散体を塗布した。

【0089】

(シリコン粒子分散体の乾燥)

シリコン粒子分散体が塗布された基材を、70℃のホットプレート上で乾燥させることによって、シリコン粒子分散体中の分散媒であるイソプロピルアルコールを除去し、それによってシリコン粒子(平均一次粒子径約20nm)を含む未焼結シリコン粒子膜(膜厚300nm)を形成した。

【0090】

(光照射)

次に、この未焼結シリコン粒子膜に対して、レーザー光照射装置(Quantronix社製、商品名Osprey 355−2−0)を用いてYVO4レーザー(波長355nm)を照射して、未焼結シリコン粒子膜中のシリコン粒子を焼結し、それによって図1に示すFETを作製した。

【0091】

次に、この未焼結シリコン粒子膜に対して、レーザー光照射装置(Quantronix社製、商品名Osprey 355−2−0)を用いてYVO4レーザー(波長355nm)を照射して、未焼結シリコン粒子膜中のシリコン粒子を焼結し、それによって図1に示すFETを作製した。

【0092】

(評価)

作製されたFETの電気的特性評価を、半導体特性評価装置(KEITHLEY社製、商品名2636A型2chシステムソースメータ)を用いて行った。銀のソース及びドレイン電極間に10〜50V程度の一定電圧を印加した状態で、ゲートであるリン(P)ドープシリコン基材に−50〜50Vの可変電圧を印加して、ソース及びドレイン電極間に流れる電流(ドレイン電流)のゲート電圧に対する応答性を調べた。このFETの電気的特性評価の結果を表1に示す。

【0093】

〈実施例2〉

シリコン粒子分散体の固形分濃度を1wt%とし、それによって未焼結シリコン膜の厚さを100nmにしたこと、及び光照射を以下のように行なったこと以外は実施例1と同様にして、図1に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0094】

(光照射)

この実施例で使用したYVO4レーザー(波長355nm)は、断面が幅72μm及び長さ130μmの楕円形であり、それを基材上で走査させることにより、アルゴン雰囲気においてシリコン粒子を焼結した。レーザー光照射条件は、照射エネルギー75mJ/(cm2・shot)、ショット数33回、及び1ショットあたりの照射時間30ナノ秒とした。

【0095】

〈実施例3〉

光照射の際の照射エネルギーを105mJ/(cm2・shot)にしたこと以外は実施例2と同様にして、図1に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0096】

〈実施例4〉

光照射の際の照射エネルギーを104mJ/(cm2・shot)にしたこと、及び光照射後の半導体シリコン膜を下記のようにして更に処理したこと以外は実施例2と同様にして、図1に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0097】

(光照射後の半導体シリコン膜の更なる処理)

光照射の後の半導体シリコン膜上に、固形分濃度1wt%のシリコン粒子分散体を数滴滴下し、500rpmで5秒間にわたって、そして4000rpmで10秒間にわたってスピンコートして、シリコン粒子分散体を塗布した。その後、シリコン粒子分散体を、70℃のホットプレートで乾燥させ、再度、104mJ/(cm2・shot)の照射エネルギーで光照射を行った。

【0098】

〈実施例5〉

光照射を行なう雰囲気を水素(H2)を約2%含有する窒素(N2)雰囲気としたこと、照射エネルギーを104mJ/(cm2・shot)にしたこと以外は実施例2と同様にして、図1に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0099】

〈実施例6〉

(シリコン粒子分散体の調製)

固形分濃度を1wt%としたこと以外は実施例1と同様にして、シリコン粒子分散体を得た。

【0100】

(基材の準備)

インジウム亜鉛酸化物(IZO)電極付き耐熱性ポリカーボネート基材(帝人株式会社製、SS120−B30、ガラス転移温度:215℃)を、30分間にわたって紫外線(UV)−オゾン洗浄して、清浄化された基材を準備した。

【0101】

その後、この基材上に、FETのゲート絶縁膜となるメチルシルセスキオキサン(MSQ)膜を作製した。具体的には、プロピレングリコールモノメチルエーテルアセテート(PGMEA)中にMSQが溶解した固形分濃度30wt%の溶液(Honeywell社製、商品名PTS R−6)を、IZO電極付きポリカーボネート基材に数滴滴下し、500rpmで5秒間にわたって、そして3200rpmで20秒間にわたってスピンコートし、そしてその後で、炉中で80℃で5分間にわたって、そして大気中で180℃で30分間にわたって加熱及び乾燥して、MSQ膜を得た。MSQ膜の膜厚は800nmであった。

【0102】

その後、実施例1と同様にして、基材に銀を真空蒸着して、FETのためのソース電極及びドレイン電極を形成した。

【0103】

(シリコン粒子分散体の塗布及び乾燥)

実施例1と同様にして、基材にシリコン粒子分散体を塗布し、そして乾燥した。ただし、この実施例では、得られた未焼結シリコン粒子膜の膜厚は100nmであった。

【0104】

(光照射)

次に、実施例1と同様にして、光照射を行って、図2に示すFETを作製した。

【0105】

ただし、ここで、照射したYVO4レーザーは、断面が幅72μm及び長さ130μmの楕円形であり、それを基材上で走査させることにより、アルゴン雰囲気中においてシリコン粒子を焼結した。レーザー光照射条件は、照射エネルギー75mJ/(cm2・shot)、ショット数33回であり、及び1ショットあたりの照射時間30ナノ秒とした。

【0106】

(評価)

このFETの電気的特性評価の結果を表1に示す。

【0107】

〈実施例7〉

光照射の際の照射エネルギーを89mJ/(cm2・shot)にしたこと以外は実施例6と同様にして、図2に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0108】

〈実施例8〉

光照射の際の照射エネルギーを104mJ/(cm2・shot)にしたこと以外は実施例6と同様にして、図2に示すFETを作製した。このFETの電気的特性評価の結果を表1に示す。

【0109】

〈実施例9〉

(シリコン粒子分散体の調製)

シリコン粒子の平均一次粒子径が約7nmであること、シリコン粒子分散体の固形分濃度が2.7wt%であること以外は実施例1と同様にして、シリコン粒子分散体を調製した。

【0110】

(基材の準備)

基材としては実施例6と同様に、IZO電極付きポリカーボネート基材上にMSQ膜(膜厚800nm)を積層したものを用いた。

【0111】

(シリコン粒子分散体の塗布及び乾燥)

実施例1と同様にして、基材にシリコン粒子分散体を塗布し、そして乾燥した。未焼結シリコン粒子膜の膜厚は300nmであった。

【0112】

(光照射)

照射エネルギーが140mJ/(cm2・Shot)であること、ショット数20回であること以外は実施例1と同様にして、YVO4レーザー照射を行って、半導体シリコン膜を得た。

【0113】

(リンドープシリコン層の形成)

得られた半導体シリコン膜上に、固形分濃度2.6wt%のリン(P)でドープされたシリコン粒子の分散体を数滴滴下し、実施例1と同様に塗布及び乾燥を行って、リンドープシリコン粒子からなる未焼結シリコン粒子膜を得た。得られた未焼結シリコン粒子膜の厚さは250nmであった。

【0114】

その後、ソース電極及びドレイン電極を配置する予定の領域を、照射エネルギー120mJ/(cm2・shot)及びショット数20回の条件で光照射した。

【0115】

その後、前記光照射を行った領域に、抵抗加熱式の真空蒸着装置を用いて、銀を真空蒸着して、ソース電極およびドレイン電極(チャネル長120μ及びチャネル幅1.5mm)を形成した。

【0116】

このようにして得られたリンドープシリコン層は、薄膜トランジスタのソース電極及びドレイン電極と半導体シリコン層との間のコンタクトを容易にするために有益である。

得られたFETを図3に示す。このFETの電気的特性評価の結果を表1に示す。

【0117】

【表1】

【符号の説明】

【0118】

110、120、130 半導体積層体

112 リン(P)ドープシリコン基材

114 酸化ケイ素(SiO2)ゲート絶縁膜

115、116、125、126 銀(Ag)のソース電極及びドレイン電極

118、128 半導体シリコン膜

122 ポリカーボネート(PC)基材

123 酸化インジウム亜鉛(IZO)ゲート電極

124 メチルシルセスキオキサン(MSQ)ゲート絶縁膜

128 半導体シリコン膜

128a ドーパント注入膜

128b 半導体シリコン膜のドープ領域

10 半導体基板

12、12a n型半導体層

14、14a p型半導体層

22 受光面側電極

24 保護層

32 裏面側電極

34 保護層

52 ドーパント注入膜

52a 未焼結ドーパント注入膜

62 ドーパント注入膜

72 基材

73 ゲート絶縁膜

74 ゲート電極

75 ソース電極

76 ドレイン電極

78 半導体層

78a ドーパント注入膜

78b ドープ領域

500 従来のセレクティブエミッタ型太陽電池

600 従来のバックコンタクト型太陽電池

500a 本発明のセレクティブエミッタ型太陽電池

600a 本発明のバックコンタクト型太陽電池

700 従来の電界効果トランジスタ

700a 本発明の電界効果トランジスタ

【特許請求の範囲】

【請求項1】

(a)分散媒及び前記分散媒中に分散しているシリコン粒子を含有するシリコン粒子分散体を、基材上に塗布して、シリコン粒子分散体膜を形成する工程、

(b)前記シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び

(c)前記未焼結半導体シリコン膜に光を照射して、前記未焼結半導体シリコン膜中の前記シリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程、

を含む、基材及び前記基材上に積層されている半導体シリコン膜を有する半導体積層体の製造方法。

【請求項2】

前記基材が、ポリマー材料を有する、請求項1に記載の方法。

【請求項3】

前記ポリマー材料のガラス転移温度が、300℃以下である、請求項1又は2に記載の方法。

【請求項4】

前記シリコン粒子の平均一次粒子径が100nm以下である、請求項1〜3のいずれか一項に記載の方法。

【請求項5】

(a’)第2の分散媒及び前記第2の分散媒中に分散している第2のシリコン粒子を含有する第2のシリコン粒子分散体を、工程(c)において得られた前記半導体シリコン膜に塗布して、第2のシリコン粒子分散体膜を形成する工程、

(b’)前記第2のシリコン粒子分散体膜を乾燥して、第2の未焼結半導体シリコン膜を形成する工程、及び

(c’)前記第2の未焼結半導体シリコン膜に光を照射して、前記第2の未焼結半導体シリコン膜中の前記第2のシリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程、

を更に含む、請求項1〜4のいずれか一項に記載の方法。

【請求項6】

(a”)第3の分散媒及び前記第3の分散媒中に分散している第3のシリコン粒子を含有する第3のシリコン粒子分散体を、工程(c)又は(c’)において得られた前記半導体シリコン膜の選択された領域に塗布して、第3のシリコン粒子分散体膜を形成する工程であって、前記第3のシリコン粒子が、p型又はn型ドーパントによってドープされている工程、

(b”)前記第3のシリコン粒子分散体膜を乾燥して、未焼結ドーパント注入膜を形成する工程、及び

(c”)前記未焼結ドーパント注入膜に光を照射することによって、前記未焼結ドーパント注入膜中の前記第3のシリコン粒子を焼結させてドーパント注入膜を形成し、かつ前記半導体シリコン膜の選択された領域を、前記p型又はn型ドーパントによってドープする工程、

を更に含む、請求項1〜5のいずれか一項に記載の方法。

【請求項7】

前記ドーパントが、B、Al、Ga、In、Ti、P、As、Sb、又はそれらの組み合わせからなる群より選択される、請求項1〜6のいずれか一項に記載の方法。

【請求項8】

前記粒子が、前記ドーパントを1×1020atoms/cm3以上含む、請求項1〜7のいずれか一項に記載の方法。

【請求項9】

前記ドーパント注入膜上に、電極を形成することを更に含む、請求項1〜8のいずれか一項に記載の方法。

【請求項10】

最終的に得られる前記半導体シリコン膜のキャリア移動度が、0.1cm2/V・s以上である、請求項1〜9のいずれか一項に記載の方法。

【請求項11】

最終的に得られる前記半導体シリコン膜のオン−オフ比が、102以上である、請求項1〜10のいずれか一項に記載の方法。

【請求項12】

前記シリコン粒子が、レーザー熱分解法によって得られたシリコン粒子である、請求項1〜11のいずれか一項に記載の方法。

【請求項13】

前記未焼結半導体シリコン膜が、50〜2000nmの厚さを有する、請求項1〜12のいずれか一項に記載の方法。

【請求項14】

前記光照射をパルス状の光を用いて行い、且つ前記パルス状の光の照射エネルギーが、15mJ/(cm2・shot)〜250mJ/(cm2・shot)である、請求項1〜13のいずれか一項に記載の方法。

【請求項15】

前記光照射をパルス状の光を用いて行い、且つ前記パルス状の光の照射回数が、5〜100回である、請求項1〜14のいずれか一項に記載の方法。

【請求項16】

前記光照射をパルス状の光を用いて行い、且つ前記パルス状の光の照射時間が、200ナノ秒/shot以下である、請求項1〜15のいずれか一項に記載の方法。

【請求項17】

前記光照射を、レーザーを用いて行なう、請求項1〜16のいずれか一項に記載の方法。

【請求項18】

前記レーザーの波長が600nm以下である、請求項17に記載の方法。

【請求項19】

前記光照射を非酸化性雰囲気下で行なう、請求項1〜18のいずれか一項に記載の方法。

【請求項20】

請求項1〜19のいずれか一項に記載の方法によって半導体積層体を作ることを含む、半導体デバイスの製造方法。

【請求項21】

請求項1〜19のいずれか一項に記載の方法によって得られる、半導体積層体。

【請求項22】

請求項20に記載の方法によって得られる、半導体デバイス。

【請求項23】

基材及び前記基材上に積層されている半導体シリコン膜を有する半導体積層体であって、

前記基材が、ポリマー材料を有し、

前記半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ

前記半導体シリコン膜のキャリア移動度が、1.0cm2/V・s以上である、

半導体積層体。

【請求項24】

前記半導体シリコン膜上に、互いに焼結されている複数のシリコン粒子から作られているドーパント注入膜を更に有する、請求項23に記載の半導体積層体。

【請求項25】

基材、前記基材上に積層されている半導体シリコン膜、及び前記半導体シリコン膜上に積層されているドーパント注入膜を有する半導体積層体であって、

前記半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ

前記ドーパント注入膜が、互いに焼結されている複数のシリコン粒子から作られている、

半導体積層体。

【請求項26】

請求項23〜25のいずれか一項に記載の半導体積層体を有する、半導体デバイス。

【請求項1】

(a)分散媒及び前記分散媒中に分散しているシリコン粒子を含有するシリコン粒子分散体を、基材上に塗布して、シリコン粒子分散体膜を形成する工程、

(b)前記シリコン粒子分散体膜を乾燥して、未焼結半導体シリコン膜を形成する工程、及び

(c)前記未焼結半導体シリコン膜に光を照射して、前記未焼結半導体シリコン膜中の前記シリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程、

を含む、基材及び前記基材上に積層されている半導体シリコン膜を有する半導体積層体の製造方法。

【請求項2】

前記基材が、ポリマー材料を有する、請求項1に記載の方法。

【請求項3】

前記ポリマー材料のガラス転移温度が、300℃以下である、請求項1又は2に記載の方法。

【請求項4】

前記シリコン粒子の平均一次粒子径が100nm以下である、請求項1〜3のいずれか一項に記載の方法。

【請求項5】

(a’)第2の分散媒及び前記第2の分散媒中に分散している第2のシリコン粒子を含有する第2のシリコン粒子分散体を、工程(c)において得られた前記半導体シリコン膜に塗布して、第2のシリコン粒子分散体膜を形成する工程、

(b’)前記第2のシリコン粒子分散体膜を乾燥して、第2の未焼結半導体シリコン膜を形成する工程、及び

(c’)前記第2の未焼結半導体シリコン膜に光を照射して、前記第2の未焼結半導体シリコン膜中の前記第2のシリコン粒子を焼結させ、それによって半導体シリコン膜を形成する工程、

を更に含む、請求項1〜4のいずれか一項に記載の方法。

【請求項6】

(a”)第3の分散媒及び前記第3の分散媒中に分散している第3のシリコン粒子を含有する第3のシリコン粒子分散体を、工程(c)又は(c’)において得られた前記半導体シリコン膜の選択された領域に塗布して、第3のシリコン粒子分散体膜を形成する工程であって、前記第3のシリコン粒子が、p型又はn型ドーパントによってドープされている工程、

(b”)前記第3のシリコン粒子分散体膜を乾燥して、未焼結ドーパント注入膜を形成する工程、及び

(c”)前記未焼結ドーパント注入膜に光を照射することによって、前記未焼結ドーパント注入膜中の前記第3のシリコン粒子を焼結させてドーパント注入膜を形成し、かつ前記半導体シリコン膜の選択された領域を、前記p型又はn型ドーパントによってドープする工程、

を更に含む、請求項1〜5のいずれか一項に記載の方法。

【請求項7】

前記ドーパントが、B、Al、Ga、In、Ti、P、As、Sb、又はそれらの組み合わせからなる群より選択される、請求項1〜6のいずれか一項に記載の方法。

【請求項8】

前記粒子が、前記ドーパントを1×1020atoms/cm3以上含む、請求項1〜7のいずれか一項に記載の方法。

【請求項9】

前記ドーパント注入膜上に、電極を形成することを更に含む、請求項1〜8のいずれか一項に記載の方法。

【請求項10】

最終的に得られる前記半導体シリコン膜のキャリア移動度が、0.1cm2/V・s以上である、請求項1〜9のいずれか一項に記載の方法。

【請求項11】

最終的に得られる前記半導体シリコン膜のオン−オフ比が、102以上である、請求項1〜10のいずれか一項に記載の方法。

【請求項12】

前記シリコン粒子が、レーザー熱分解法によって得られたシリコン粒子である、請求項1〜11のいずれか一項に記載の方法。

【請求項13】

前記未焼結半導体シリコン膜が、50〜2000nmの厚さを有する、請求項1〜12のいずれか一項に記載の方法。

【請求項14】

前記光照射をパルス状の光を用いて行い、且つ前記パルス状の光の照射エネルギーが、15mJ/(cm2・shot)〜250mJ/(cm2・shot)である、請求項1〜13のいずれか一項に記載の方法。

【請求項15】

前記光照射をパルス状の光を用いて行い、且つ前記パルス状の光の照射回数が、5〜100回である、請求項1〜14のいずれか一項に記載の方法。

【請求項16】

前記光照射をパルス状の光を用いて行い、且つ前記パルス状の光の照射時間が、200ナノ秒/shot以下である、請求項1〜15のいずれか一項に記載の方法。

【請求項17】

前記光照射を、レーザーを用いて行なう、請求項1〜16のいずれか一項に記載の方法。

【請求項18】

前記レーザーの波長が600nm以下である、請求項17に記載の方法。

【請求項19】

前記光照射を非酸化性雰囲気下で行なう、請求項1〜18のいずれか一項に記載の方法。

【請求項20】

請求項1〜19のいずれか一項に記載の方法によって半導体積層体を作ることを含む、半導体デバイスの製造方法。

【請求項21】

請求項1〜19のいずれか一項に記載の方法によって得られる、半導体積層体。

【請求項22】

請求項20に記載の方法によって得られる、半導体デバイス。

【請求項23】

基材及び前記基材上に積層されている半導体シリコン膜を有する半導体積層体であって、

前記基材が、ポリマー材料を有し、

前記半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ

前記半導体シリコン膜のキャリア移動度が、1.0cm2/V・s以上である、

半導体積層体。

【請求項24】

前記半導体シリコン膜上に、互いに焼結されている複数のシリコン粒子から作られているドーパント注入膜を更に有する、請求項23に記載の半導体積層体。

【請求項25】

基材、前記基材上に積層されている半導体シリコン膜、及び前記半導体シリコン膜上に積層されているドーパント注入膜を有する半導体積層体であって、

前記半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、且つ

前記ドーパント注入膜が、互いに焼結されている複数のシリコン粒子から作られている、

半導体積層体。

【請求項26】

請求項23〜25のいずれか一項に記載の半導体積層体を有する、半導体デバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−138565(P2012−138565A)

【公開日】平成24年7月19日(2012.7.19)

【国際特許分類】

【出願番号】特願2011−251098(P2011−251098)

【出願日】平成23年11月16日(2011.11.16)

【出願人】(000003001)帝人株式会社 (1,209)

【Fターム(参考)】

【公開日】平成24年7月19日(2012.7.19)

【国際特許分類】

【出願日】平成23年11月16日(2011.11.16)

【出願人】(000003001)帝人株式会社 (1,209)

【Fターム(参考)】

[ Back to top ]