半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

【発明の詳細な説明】

【技術分野】

【0001】

半導体素子、該半導体素子を用いた半導体装置、及び半導体素子の作製方法に関する。

【0002】

なお、本明細書中において、半導体素子は半導体特性を利用することで機能する素子を指し、複数のトランジスタが集積された構成も含む。また、本明細書中において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路、電子部品、及び電子機器はすべて半導体装置である。

【背景技術】

【0003】

電力変換装置に使用される半導体装置、いわゆるパワーデバイスは、高耐圧、かつ低損失であることが望ましい。従来から、シリコン半導体を用いたパワーデバイスが開示されている。しかし、シリコンを用いた半導体素子では、その物理的な特性が理論値の限界に来ていると言われており、さらなる高耐圧と大電流の制御が可能なパワーデバイスを実現するためには、特性の向上が可能な新たな半導体材料や、半導体装置の新しい構造を提供することが求められている。

【0004】

シリコン半導体と代わる、高耐圧、高変換効率、高速スイッチングなどの諸特性を向上させる可能性がある半導体材料として、例えば、炭化ケイ素や窒化ガリウムなどが開示されている(特許文献1及び特許文献2)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−129628号公報

【特許文献2】特開2010―171416号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところが、炭化ケイ素の成膜温度は約1500℃、窒化ガリウムの成膜温度は約1100℃と、これらの化合物半導体は、成膜温度が極めて高く、基板の大型化が困難であるため、量産性が低いといった問題がある。

【0007】

本発明はこのような技術的背景のもとでなされたものである。したがって、その目的は、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする、また、該半導体素子の作製方法を提供することを課題の一とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、本発明者は、酸化物半導体に着目した。

【0009】

酸化物半導体は、広いバンドギャップを示すため、シリコン等に比べ高い耐圧を示し、パワーデバイス用の半導体材料に求められる高い絶縁破壊耐性を備えている。

【0010】

また、酸化物半導体膜の成膜温度は700℃程度であるため、基板の大型化にも対応できる。さらに、酸化物半導体膜は、スパッタリング法や湿式法(例えば、印刷法)などにより作製可能であり、ドープ工程が不要であることなどからも、量産性に優れている。

【0011】

一方、酸化物半導体の移動度は、大電流を流すパワーデバイス用の半導体材料としては、必ずしも十分ではない場合がある。移動度の低い半導体材料を用いてパワーデバイス用トランジスタを作製すると、大電流を速やかに流すことができず、また、大電流を流そうとするとトランジスタが発熱するといった問題が生じる場合がある。

【0012】

こうした問題を解決する手段としては、トランジスタのW長(チャネル幅)を長くする方法がある。

【0013】

しかし、トランジスタのW長を長くすると、トランジスタの面積が大きくなり、該トランジスタが回路に占める面積が大きくなってしまう問題がある。さらに、トランジスタ1つあたりの面積が大きくなると、1基板あたりで作製できるトランジスタの数が減ってしまう。また、パーティクル等による欠陥を1箇所でも含むと、トランジスタは信頼性が損なわれてしまう。従ってパーティクル等による欠陥が1基板あたりに同数生じる場合においては、トランジスタの面積が大きいほど、不良となる確率が高まってしまう。

【0014】

したがって、上記課題を解決するためには、広いバンドギャップを有する酸化物半導体をチャネル形成領域に用いた1以上のトランジスタと、該トランジスタを電気的に接続する貫通電極とを含む半導体チップを積層し、該貫通電極を介してトランジスタを電気的に並列接続することによって、素子の面積を巨大化することなく、実質的にW長の長いトランジスタを作製すればよい。

【0015】

すなわち、本発明の一態様は、半導体層に酸化物半導体を用いる第1のトランジスタと、第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第1の基板と、半導体層に酸化物半導体を用いる第2のトランジスタと、第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第2の基板と、を積層して備え、第1のトランジスタと第2のトランジスタは、それぞれの貫通電極を介して電気的に並列接続された半導体素子である。

【0016】

上記本発明の一態様によれば、半導体材料に酸化物半導体を用いることによって、高耐圧で、低損失である、パワーデバイスに適した性質を兼ね備えたトランジスタを作製できる。また、酸化物半導体膜は成膜温度が他のパワーデバイス用半導体材料と比較して低いため、基板の大型化にも対応でき、量産性のよいトランジスタを作製できる。

【0017】

また、本発明の一態様は、基板を積層して、トランジスタを電気的に並列接続することにより、素子の面積を巨大化させることなく、実質的なW長を長くすることが可能であり、パワーデバイスに必要な大電流を速やかに流すことのできる半導体素子を提供できる。

【0018】

また、本発明の一態様は、基板を貫通する貫通電極を用いる半導体素子である。貫通電極による積層方法では、電極層から引き出す配線の長さが自由に設定できるため、基板が巨大化しても配線の長さを自由に設定することができ、配線からの熱の発生や、配線抵抗を低減できる。

【0019】

また、上記半導体素子において、酸化物半導体は、3eV以上のバンドギャップ有する酸化物半導体からなることが好ましい。その結果、耐圧性に優れたトランジスタを提供することができる。

【0020】

また、上記半導体素子において、第1の基板及び第2の基板にシリコン基板を用いることが好ましい。シリコン基板を用いることで、半導体チップを積層しても、シリコンの優れた放熱性により、熱による半導体素子の劣化を防止できる。また、シリコンは加工性がよいため、貫通電極作製時の孔あけ加工を容易に行うことができる。

【0021】

また、上記半導体素子において、第1の基板及び第2の基板に絶縁性基板を用いてもよい。絶縁性基板を用いることで、貫通電極と基板の導通を防ぐ絶縁膜の形成が不要となり、工程が簡略化されるため好ましい。

【0022】

また、本発明の一態様は、上記半導体素子を用いた半導体装置である。その結果、高耐圧で、大電流の制御が可能である、高性能な半導体装置を提供することができる。

【0023】

また、本発明の一態様は、基板の第1の領域に第1のトランジスタと、基板の第2の領域に第2のトランジスタとを作製し、第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層、並びに第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層と、それぞれ電気的に接続する6つの貫通電極を作製し、第1の領域を備える第1の半導体チップと、第2の領域を備える第2の半導体チップとを、基板を分断して形成する第1のステップと、第1の半導体チップ及び第2の半導体チップを積層し、第1のトランジスタと第2のトランジスタを、貫通電極を介して電気的に並列接続させる第2のステップを有する半導体素子の作製方法である。その結果、W長の長い半導体素子を、素子の面積を巨大化させることなく作製することができるため、基板の不良等の影響を受けにくく、効率よく半導体素子を作製することができる。

【0024】

なお、本明細書中において、半導体チップとは半導体層に酸化物半導体を用いるトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極、を有する基板を有する。

【0025】

また、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」又は「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極層」の表現であれば、ゲート絶縁層とゲート電極層との間に他の構成要素を含むものを除外しない。また、「上」「下」の用語は説明の便宜のために用いる表現に過ぎず、特に言及する場合を除き、その上下を入れ替えたものも含む。

【0026】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

【0027】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【発明の効果】

【0028】

本発明の一態様によれば、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供できる。

また、該半導体素子を用いた半導体装置を提供できる。また、該半導体素子の作製方法を提供できる。

【図面の簡単な説明】

【0029】

【図1】実施の態様に係る半導体素子を説明する図。

【図2】実施の態様に係る半導体素子の作製方法を説明する図。

【図3】実施の態様に係る半導体素子の作製方法を説明する図。

【図4】実施の態様に係る半導体素子の作製方法を説明する図。

【図5】実施の態様に係るトランジスタの作製方法を説明する図。

【図6】実施の態様に係るコンバータ回路を説明する図。

【発明を実施するための形態】

【0030】

実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0031】

(実施の形態1)

本実施の形態では、本発明の一態様の半導体素子の構造及び作製方法について図1〜図4を用いて説明する。

【0032】

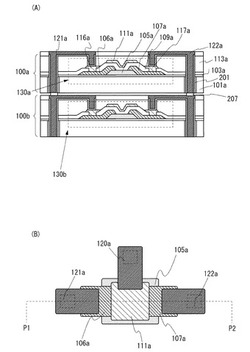

図1(A)(B)に、本発明の一態様の半導体素子の構造の一例を示す。図1(B)は本発明の一態様の半導体素子の上面図を示す。図1(A)は、図1(B)におけるP1−P2間の断面図である。

【0033】

本発明の一態様は図4(C)に示すように、半導体チップを複数積層して作製する半導体素子である。積層する半導体チップの枚数は2枚以上であれば何枚でもよく、要求される性能に合わせて適宜決定することができる。本実施の形態では、半導体チップが導電体を介して2つ積層されている構成について説明する。図1(A)に示すように、半導体素子は、半導体チップ100aと半導体チップ100bとが導電体207を介して接続する構成となっている。

【0034】

<半導体チップの構成>

続いて、半導体チップについて図1を用いて説明する。図1(A)(B)に示す半導体チップ100aは、1つのトランジスタ130aと、該トランジスタ130aのゲート電極層111aと電気的に接続する貫通電極120a、ソース電極層106aと電気的に接続する貫通電極121a、ドレイン電極層107aと電気的に接続する貫通電極122aの3つの貫通電極を備えている。また、図1(A)に示すように、半導体チップ100bはトランジスタ130b及び3つの貫通電極を備える。本実施の形態において、半導体チップが備えるトランジスタはすべて同一の構成とする。なお、本発明の一態様の半導体チップの構成はこれに限らず、1つの半導体チップが複数のトランジスタを備えていてもよい。

【0035】

<トランジスタの構成>

本実施の形態の半導体チップが備えるトランジスタは半導体層に酸化物半導体を用いる。

【0036】

以下にトランジスタ130aの構成を説明する。トランジスタ130bは、トランジスタ130aと同様の構成を有する。重複する説明を避けるため、トランジスタ130aの構成の説明をもってトランジスタ130bの説明に援用する。

【0037】

本実施の形態では、トップゲート・トップコンタクト構造のトランジスタを半導体チップが有する構成を例に用いて説明するが、本発明の一態様の半導体素子に用いることができるトランジスタの構成はこの構成に特に限定されず、ボトムゲート型構造を用いてもトップゲート型構造を用いても良い。さらに、ボトムコンタクト構造を用いても、トップコンタクト構造を用いても良い。

【0038】

図1(A)において、トランジスタ130aはシリコン基板101a上に、シリコン基板101aを覆う下地膜103aと、下地膜103a上の島状の酸化物半導体層105aと、酸化物半導体層105aと接する一対のソース電極層106a及びドレイン電極層107aと、酸化物半導体層105a、ソース電極層106a及びドレイン電極層107aを覆うように形成されたゲート絶縁層109aと、ゲート絶縁層109a上において、酸化物半導体層105aのチャネル形成領域と重なるゲート電極層111aと、ゲート電極層111a、及びゲート絶縁層109aを覆う保護絶縁層113aを有する。また、ソース配線116aはゲート絶縁層109aに形成した開口部を介してソース電極層106aと電気的に接続しており、ドレイン配線117aはゲート絶縁層109aに形成した開口部を介してドレイン電極層107aと電気的に接続する。

【0039】

なお、本実施の形態では基板にシリコン基板を用いたが、半導体チップを作製する基板には特に制限はない。シリコン基板は加工性に優れ、貫通電極作製時の孔あけが容易であることから、好適に用いることができる。さらに、シリコンの優れた放熱性により、トランジスタを積層しても、熱による半導体素子の劣化を防止できる。なお、絶縁体よりなる絶縁性基板を用いると、貫通電極と基板の導通を防ぐ絶縁膜201の形成工程が不要となる。絶縁性基板としては、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板や、BCB(ベンゾシクロブタン)、エポキシ等の絶縁性樹脂基板(有機絶縁性基板)や、セラミック基板、石英基板、サファイア基板などを用いることができる。

【0040】

<貫通電極の構成>

半導体チップには、トランジスタとは重畳しない領域において、貫通電極が設けられている。ゲート電極層111aは貫通電極120aと電気的に接続し、ソース電極層106aは貫通電極121aと電気的に接続し、ドレイン電極層107aは貫通電極122aと電気的に接続している(図1(B)参照)

【0041】

それぞれの貫通電極は半導体チップの上面及び半導体チップの下面に露出している。

【0042】

<電気的な接続関係>

すでに説明したように、半導体素子は半導体チップ100aと半導体チップ100bとを接続した素子である。具体的には、ゲート電極層と接続した貫通電極同士、ソース電極層と接続した貫通電極同士、ならびにドレイン電極層と接続した貫通電極同士が、それぞれ導電体207によって電気的に接続している。すなわち、トランジスタ130aと、トランジスタ130bは電気的に並列接続している。

【0043】

以上のように、本実施の形態の半導体素子は半導体層に酸化物半導体を用いる第1のトランジスタと、第1のトランジスタのゲート電極層と、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第1の基板と、半導体層に酸化物半導体を用いる第2のトランジスタと、第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第2の基板とが積層された構成となっている。さらに、第1のトランジスタと第2のトランジスタは、それぞれの貫通電極を介して電気的に並列接続されている。

【0044】

本実施の形態の半導体素子は、貫通電極によってトランジスタが並列接続されているため、トランジスタの面積を大きくすることなく、実質的なW長を長くすることが可能であり、高移動度の半導体素子を提供することができる。

【0045】

また、本実施の形態の半導体素子は、半導体層に酸化物半導体を用いているため、高耐圧で、大電流の制御が可能であるという特性を有する。そのため、大電流を扱うパワーデバイス等の半導体素子に適している。

【0046】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0047】

(実施の形態2)

本実施の形態では、実施の形態1に例示した半導体素子の作製方法について図2〜図4を用いて説明する。

【0048】

半導体素子の作製方法は2つのステップからなる。具体的には、複数のトランジスタと、トランジスタのゲート電極層、ソース電極層、並びにドレイン電極層の各々に電気的に接続する貫通電極とをシリコン基板101上に作製し(図4(A)参照)、シリコン基板101を分断して半導体チップ100を作製する第1のステップ(図4(B)参照)と、複数の半導体チップ100を積層して(図4(C)参照)、互いの貫通電極を接続する第2のステップ(図4(D)参照)からなる。

【0049】

つまり、基板の第1の領域に第1のトランジスタと、基板の第2の領域に第2のトランジスタとを作製し、第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極を第1の領域に、第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極を第2の領域に作製し、第1の領域を備える第1の半導体チップと、第2の領域を備える第2の半導体チップとを、基板を分断して形成する第1のステップと、第1の半導体チップ及び第2の半導体チップを積層し、第1のトランジスタと第2のトランジスタを、貫通電極を介して電気的に並列接続させる第2のステップを有する半導体素子の作製方法である。

【0050】

<第1のステップ>

シリコン基板101上に半導体層に酸化物半導体を用いたトランジスタを複数作製する。なお、トランジスタの作製方法の詳細は実施の形態3で説明する。

【0051】

続いて、トランジスタ同士を接続する貫通電極を作製する。

【0052】

貫通電極の作製プロセスを、図2及び図3を用いて説明する。なお、図2及び図3にはトランジスタのドレイン電極層107と導通する貫通電極122の作製プロセスのみについて図示し、ソース電極層または、ゲート電極層111と導通する貫通電極については、ドレイン電極層107と導通する貫通電極122と同様の工程で作製するものとし、説明及び図示を省略する。

【0053】

図2(B)に示すように、貫通電極122を埋め込むためのビア200を形成する。ビア200は、保護絶縁層113にドレイン配線117の上面に達する開口と、トランジスタとは重畳しない領域に保護絶縁層113、ゲート絶縁層109、下地膜103を貫き、シリコン基板101に凹部を形成する開口とからなる(図2(B)参照)。なお、ビア200は基板にシリコンウェハを用いた場合にはエッチングやレーザを用いて形成し、ガラスを用いた場合には異方性エッチングが困難であることから、サンドブラストやレーザ等を用いて形成する。

【0054】

次いで、図2(C)に示すように、基板を熱処理することによって絶縁膜201(酸化膜もしくは窒化膜)をシリコン基板101に形成する。本実施の形態では、シリコン基板101に熱酸化処理を行うことにより、酸化膜を形成する。熱酸化処理は、酸化性雰囲気中にハロゲンを添加して行うことが好ましい。例えば、塩素(Cl)が添加された酸化性雰囲気中で単結晶シリコン基板に熱酸化処理を行うことにより、塩素酸化された酸化膜を形成することができる。なお、基板に絶縁体からなる絶縁性基板を用いる場合、熱処理は不要である。

【0055】

なお、基板の熱処理によって、ゲート電極層111、ソース配線及びドレイン配線117上に絶縁膜が形成された場合は、該絶縁膜をエッチングして、導電層を露出する必要がある。

【0056】

次いで、図2(D)に示すように、ビア200に導電性バリア膜203を形成する。導電性バリア膜203は配線205からの金属の拡散を防ぐ保護膜としての機能を有している。導電性バリア膜203には、窒化タンタル、窒化チタン,又は窒化タングステン、炭化タンタル(TaC)、炭化チタン(TiC)から選ばれた一種或いは複数種の材料を用いればよい。また、シリコンを有する3次元系アモルファスバリア膜を用いてもよい。

【0057】

導電性バリア膜203の形成はPVD法やCVD法等の成膜法、スパッタリング法を用いて行うことができる。例えば窒化チタン膜の場合、窒素とアルゴンとをスパッタリングガスとし、出力150Wで成膜すればよい。多結晶構造を有し、粒界の存在により拡散防止機能が向上される。なお、このとき、スパッタの出力をあげること、アルゴンガスの流量比を大きくすること、基板の温度を高くして成膜すること等により、緻密な膜を形成し、バリア性を高めることができる。本実施の形態では、窒化タンタル膜を用いる。窒化タンタル膜は、バリア性が高い導電膜であること、また、後の工程で、研磨することを考えた場合、CMP法(Chemical−Mechanical−Polishing:化学的・機械的研磨法)を用いて容易に加工が可能であることから、本実施の形態に用いる導電性バリア膜に適している。

【0058】

次いで、図2(E)に示すように、ビア200に配線205を埋め込む。配線には、Cu、Ag、Ni等の金属を用いる。配線方法としてはCVD法、スパッタリング法、リモートプラズマ法、メッキ法等を用いて形成される。マルチチャンバーを用いることで、導電性バリア膜と配線とを大気にさらすことなく連続成膜することが可能となる。このように連続成膜を行うことにより、界面への不純物の付着を防止することができ、良好な成膜を行うことが可能になる。

【0059】

エッチングにより、導電性バリア膜203及び配線205を所望の形状にエッチングする。なお、メッキによる配線の埋め込みでは、最初から選択的に配線205を形成することも可能である。

【0060】

次いで、図3(A)に示すように、配線205上に保護層115を形成する。保護層115は、プラズマCVD法またはスパッタリング法等を用いて形成することができる。また、保護層115は、酸化ケイ素膜、窒化ケイ素膜、酸化窒化ケイ素膜、窒化酸化ケイ素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ハフニウム膜、または酸化タンタル膜などから選ばれた一又は複数の膜により単層で、又は積層させて形成することができる。

【0061】

次いで、図3(B)に示すように、配線205を上面及び下面に露出させる。上面において、保護層115及び配線205を研磨することによって、配線205を上面に露出させるとともに、該上面を平坦化する。下面においては、基板101、絶縁膜201、及び導電性バリア膜203を研磨して、配線205を露出させるとともに、該下面を平坦化する。平坦化処理としては、研磨処理やレーザの照射処理を行うことができる。研磨処理や、レーザ光の照射処理は複数回行ってもよいし、組み合わせて行ってもよい。また、処理の順序も限定されず、適宜選択することができる。レーザ光の照射処理に代えてランプ光の照射処理を行ってもよい。

【0062】

配線205が上面及び下面に露出したことによって、ドレイン電極層107が半導体チップの上面及び下面に導通した。図3(B)に示すとおり、トランジスタの上面及び下面と各電極層をつなぐ、配線205及び導電性バリア膜203のことを貫通電極122と呼ぶ。

【0063】

次いで、図3(C)に示すように、導電体207を形成する。

【0064】

導電体207は、導電性微粒子、導電性粉末を含む導電性ペースト、または、導電性微粒子、導電性粉末を含む導電性液体のような流動性を有する導電性材料で形成することが好ましい。このような導電性材料を用いることで、液滴吐出法(インクジェット法、ディスペンサ法などの方法が含まれる)、スクリーン印刷法などの印刷法などにより、導電体207を形成することが可能である。これらの方法は、CVD装置、スパッタ装置のような複雑な成膜装置での成膜工程、およびフォトマスクを形成するための露光工程を行うことなく、必要な箇所に凸状の導電体207を形成することが可能である。

【0065】

導電性ペースト及び導電性液体は、導電性微粒子、導電性粉末が分散された材料、またはこれらが溶解している導電性材料である。例えば、導電性液体に含まれる導電性粉体または導電性微粒子の材料としては、例えばAg、Au、Cu、Ni、Pt、Pd、Ndなどの金属、これらの金属材料の合金(例えばAg−Pd)、酸化インジウム、酸化亜鉛などの導電性酸化物材料などがあげられる。また、導電性粉体、または導電性微粒子を溶解させるまたは分散させるための媒質(溶媒、分散剤)としては、例えば、紫外線硬化樹脂などの光硬化性樹脂や、熱硬化性樹脂の前駆体材料があげられる。紫外線硬化樹脂としてはアクリル系樹脂、エポキシ系樹脂があげられる。また、熱硬化樹脂としてはポリイミド系樹脂があげられる。

【0066】

続いて、基板101を切断し、個々の半導体チップ100に分断する(図4(B)参照)。切り分けには、ダイシング、スクライビング、又はレーザーカット法等を用いて、選択的に分断することができる。

【0067】

上記のように、基板上に複数のトランジスタを作製してから切り分けることによって、良品のトランジスタと、パーティクル等の影響を受けた不良品のトランジスタとに選別することが可能であり、良品のみを選択的に積層することができるため、半導体素子を効率的に作製することが可能である。

【0068】

以上の工程で半導体チップ100を形成できる。

【0069】

<第2のステップ>

次いで、図3(D)に示すように、切り分けた半導体チップ100を上下に積層させ、貫通電極122及び導電体207を介して並列接続する。

【0070】

導電体207と基板下面に露出した貫通電極が重なるように接触させて、半導体チップ同士を電気的に接続する。半導体チップ同士の固定方法としては、貫通電極同士をはんだ等で固定し、さらに、接続信頼性を向上させるため、封止樹脂によって固定することも可能である。使用する樹脂としては光硬化性の樹脂や熱硬化性のもの或いは自然硬化性の樹脂等を用いることができる。

【0071】

上下に積層する半導体チップの個数は自由に決めることができ、要求される性能に応じて積層する個数を変えればよい。

【0072】

以上のように、本実施の形態の半導体素子を作製することができる。

【0073】

本実施の形態の半導体素子は、半導体層に、酸化物半導体を用いているため、高耐圧で、大電流の制御が可能であるという特性を有する。そのため、大電流を扱うパワーデバイス等の半導体素子に適している。

【0074】

本実施の形態の半導体素子は、貫通電極によって、トランジスタを並列接続させているため、トランジスタの実質的なW長を長くすることができ、パワーデバイスに適した高移動度を実現する。

【0075】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0076】

(実施の形態3)

本実施の形態では、実施の形態1乃至2で示した半導体素子に適用可能なトランジスタの作製方法について図5を用いて説明する。

【0077】

本実施の形態のトランジスタは半導体層に酸化物半導体を用いる。本実施の形態の半導体層に用いる酸化物半導体は、n型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することによりI型(真性)の酸化物半導体、またはI型(真性)に限りなく近い酸化物半導体としたものである。

【0078】

なお、高純度化された酸化物半導体中ではキャリアが極めて少なく、キャリア濃度は1×1014/cm3未満、好ましくは1×1012/cm3未満、さらに好ましくは1×1011/am3未満となる。また、このようにキャリアが少ないことで、オフ状態における電流(オフ電流)は十分に小さくなる。

【0079】

具体的には、上述の酸化物半導体層を具備するトランジスタでは、オフ状態でのソースとドレイン間のチャネル幅1μmあたりのリーク電流密度(オフ電流密度)は、ソースとドレイン間の電圧が3.5V、使用時の温度条件下(例えば、25℃)において、100zA/μm(1×10−19A/μm)以下、もしくは10zA/μm(1×10−20A/μm)以下、さらには、1zA/μm(1×10−21A/μm)以下とすることができる。

【0080】

また、高純度化された酸化物半導体層を具備するトランジスタは、オン電流の温度依存性がほとんど見られず、高温状態においてもオフ電流は非常に小さいままである。

【0081】

まず、基板101上に下地膜103を形成する。

【0082】

下地膜としては、例えば、酸化ケイ素膜、酸化窒化ケイ素膜、窒化ケイ素膜、窒化酸化ケイ素膜、窒化アルミニウム膜、または、窒化酸化アルミニウム膜のいずれか一つを単層で、あるいは複数を積層させて用いることができる。

【0083】

本実施の形態では、シリコン基板に熱酸化処理を行うことにより、下地膜103として熱酸化膜(ここでは酸化ケイ素膜)を形成する。

【0084】

基板101の裏面(トランジスタが形成されない面)に形成された熱酸化膜が不要であれば、エッチングや研磨によって除去してもよい。

【0085】

なお、本明細書中において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として酸素よりも窒素の含有量が多い物質をいう。例えば、酸化窒化ケイ素とは、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以上、ケイ素が25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれる物質とすることができる。また、窒化酸化ケイ素とは、酸素が5原子%以上35原子%以下、窒素が20原子%以上55原子%以下、ケイ素が25原子%以上35原子%以下、水素が10原子%以上30原子%以下の範囲で含まれる物質とすることができる。ただし、上記組成の範囲は、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS:Hydrogen Forward Scattering)を用いて測定した場合のものである。また、構成元素の含有比率は、その合計が100原子%を超えない値をとる。

【0086】

特に、下地膜103に、バリア性の高い絶縁膜、例えば窒化ケイ素膜、窒化酸化ケイ素膜窒化アルミニウム膜、または、窒化酸化アルミニウム膜などを用いることで、水分、または、水素などの雰囲気中の不純物、或いは基板101内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体層105内に入り込むのを防ぐことができる。

【0087】

なお、酸化物半導体中に含まれる、Li、Na等のアルカリ金属、及びCa等のアルカリ土類金属等の不純物は低減されていることが好ましい。具体的にはSIMSに検出されるNaが5×1016/cm3以下、好ましくは1×1016/cm3以下、さらに好ましくは1×1015/cm3以下であり、Liが5×1015/cm3以下、好ましくは1×1015/cm3以下であり、Kは5×1015/cm3以下、好ましくは1×1015/cm3以下であることが好ましい。

【0088】

アルカリ金属、及びアルカリ土類金属は酸化物半導体にとっては悪性の不純物であり、少ない方がよい。特にアルカリ金属のうち、Naは酸化物半導体と接する絶縁膜が酸化物であった場合、その中に拡散し、Na+となる。また、酸化物半導体内において、金属と酸素の結合を分析し、あるいは結合中に割り込む。その結果、トランジスタ特性の劣化(例えば、ノーマリオン化、閾値の負へのシフト)をもたらす。加えて、特性のばらつきの原因ともなる。このような問題は特に酸化物半導体中の水素の濃度が十分に低い場合において顕著となる。したがって、酸化物半導体中の水素の濃度が5×1019/cm3以下、特に5×1018/cm3以下である場合には、アルカリ金属の濃度を上記の値にすることが強く求められる。

【0089】

次に、下地膜103上に、酸化物半導体成膜用ターゲットを用い、スパッタ法により酸化物半導体膜を成膜する。また、酸化物半導体膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素混合雰囲気下においてスパッタ法により形成することができる。

【0090】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、下地膜103に付着している粉状物質(パーティクル、ごみともいう)を除去することが好ましい。逆スパッタとは、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素等を用いてもよい。また、アルゴン雰囲気に酸素、及び亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、及び四フッ化炭素などを加えた雰囲気で行ってもよい。

【0091】

酸化物半導体膜に用いられる酸化物半導体としては、四元系金属酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体や、三元系金属酸化物であるIn−Ga−Zn―O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系や、二元系金属酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体や、一元系金属酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体などの酸化物半導体を用いることができる。また、上記酸化物半導体膜に酸化ケイ素を含ませてもよい。酸化物半導体膜に結晶化を阻害する酸化ケイ素(SiOx(X>0))を含ませることで、製造プロセス中において酸化物半導体層の形成後に加熱処理した場合に、結晶化してしまうのを抑制することができる。なお、酸化物半導体層は非晶質な状態であることが好ましく、一部結晶化していてもよい。ここで、例えば、In−Ga−Zn−O系酸化物半導体とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物膜という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでもよい。

【0092】

また、酸化物半導体膜は、InMO3(ZnO)m(m>0)で表記される薄膜を用いることができる。ここで、MはGa、Al、Mn、Coから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、又はGa及びCoなどがある。

【0093】

本実施の形態の酸化物半導体は、好ましくはInを含有する酸化物半導体、さらに好ましくは、In及びGaを含有する酸化物半導体である。酸化物半導体層をI型(真性)とするため、脱水化または脱水素化は有効である。本実施の形態では、酸化物半導体膜としてIn―Ga―Zn−O系酸化物半導体成膜用ターゲットを用いてスパッタリング法により成膜する。

【0094】

In−Ga−Zn−O系酸化物半導体成膜用ターゲットの例としては、In、Ga、及びZnを含む酸化物半導体成膜用ターゲット(組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol数比])などを用いることもできる。また、In、Ga、およびZnを含む酸化物半導体成膜用ターゲットとして、In2O3:Ga2O3:ZnO=1:1:2[mol数比]、又はIn2O3:Ga2O3:ZnO=1:1:4[mol数比]の組成比を有するターゲットを用いることもできる。酸化物半導体成膜用ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

【0095】

減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板101上に酸化物半導膜を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H2O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱してもよい。

【0096】

次いで、酸化物半導体膜を第1のフォトリソグラフィ工程により島状の酸化物半導体層105に加工する。(図5(A)参照)。また、島状の酸化物半導体層105を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0097】

なお、ここでの酸化物半導体膜のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

【0098】

ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、塩化硼素(BCl3)、塩化ケイ素(SiCl4)、四塩化炭素(CCl4)など)が好ましい。

【0099】

また、フッ素を含むガス(フッ素系ガス、例えば四フッ化炭素(CF4)、フッ化硫黄(SF6)、フッ化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(HBr)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、等を用いることが出来る。

【0100】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。

【0101】

ウェットエッチングに用いるエッチング液としては、燐酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO07N(関東化学社製)を用いてもよい。

【0102】

また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効に活用し低コスト化することができる。

【0103】

所望の加工形状にエッチングできるように、材料に合わせてエッチング条件(エッチング液、エッチング時間、温度等)を適宜調節する。

【0104】

本実施の形態では、エッチング液として燐酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッチング法により、酸化物半導体膜を島状の酸化物半導体層105に加工する。

【0105】

次いで、酸化物半導体層105に第1の加熱処理を施す。酸素、窒素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウムなど)雰囲気下において酸化物半導体層105に加熱処理を施すことで、水分、水素が脱離した酸化物半導体層105が形成される。第1の加熱処理の温度は、250℃以上750℃以下、または、400℃以上基板の歪み点未満とする。例えば、500℃、3分間以上6分間以下程度で行ってもよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、基板の歪み点を超える温度でも処理することができる。

【0106】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA装置(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0107】

例えば、第1の加熱処理として、650℃〜700℃の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

【0108】

なお、第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0109】

また、第1の加熱処理で酸化物半導体層を加熱した後、同じ炉に高純度の酸素ガス、高純度のN2Oガス、又は超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で−55℃)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)を導入してもよい。酸素ガスまたはN2Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN2Oガスの純度を、6N以上好ましくは7N以上(即ち、酸素ガスまたはN2Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。酸素ガス又はN2Oガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型(真性)化する。

【0110】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

【0111】

酸化物半導体層105に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層105上にソース電極層106及びドレイン電極層107を積層させた後、ソース電極層及び、ドレイン電極層上にゲート絶縁層109を形成した後、などのいずれで行ってもよい。

【0112】

以上の工程により、島状の酸化物半導体層中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体層の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体層を形成することができる。このため大面積基板を用いてトランジスタを作製することができ、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体層を用いることで、耐圧性が高く、オフ電流の著しく低いトランジスタを作製することができる。上記加熱処理は、酸化物半導体膜の成膜以降であれば、いつでも行うことができる。

【0113】

なお、酸化物半導体膜を加熱する場合、酸化物半導体膜の材料や加熱条件にもよるが、その表面に板状結晶が形成されることがある。板状結晶は、酸化物半導体膜の表面に対して略垂直にc軸配向した単結晶体であることが好ましい。なお、酸化物半導体膜下の下地膜の表面に凹凸がある場合、板状結晶は多結晶体となる。したがって、下地表面は可能な限り平坦であることが望まれる。

【0114】

また、酸化物半導体層を2回に分けて成膜し、2回に分けて加熱処理を行うことで、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜厚の厚い結晶領域(単結晶領域)、即ち、膜表面に垂直にc軸配向した結晶領域を有する酸化物半導体層を形成してもよい。例えば、3nm以上15nm以下の第1の酸化物半導体膜を成膜し、窒素、酸素、希ガス、または乾燥空気の雰囲気下で450℃以上850℃以下、好ましくは550℃以上750℃以下の第1の加熱処理を行い、表面を含む領域に結晶領域(板状結晶を含む)を有する第1の酸化物半導体膜を形成する。そして、第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、450℃以上850℃以下、好ましくは600℃以上700℃以下の第2の加熱処理を行い、第1の酸化物半導体膜を結晶成長の種として、上方に結晶成長させ、第2の酸化物半導体膜の全体を結晶化させ、結果として膜厚の厚い結晶領域を有する酸化物半導体層を形成してもよい。

【0115】

次いで、酸化物半導体層105上にソース電極層106及びドレイン電極層107となる導電膜を形成する。ソース電極及びドレイン電極となる導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wからから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、Al、Cuなどの金属膜の下側もしくは上側にCr、Ta、Ti、Mo、Wなどの高融点金属膜を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどAl膜に生ずるヒロックやウィスカーの発生を防止する元素が添加されているAl材料を用いることで耐熱性を向上させることが可能となる。

【0116】

また、導電膜は単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を成膜する3層構造などがあげられる。

【0117】

また、導電膜は導電性の金属酸化物で形成してもよい。導電性の金属酸化物としては酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3―SnO2、ITOと略記する)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)または前記金属酸化物材料にシリコンもしくは酸化ケイ素を含ませたものを用いることができる。

【0118】

導電膜成膜後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

【0119】

次いで、第2のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層106及びドレイン電極層107を形成した後、レジストマスクを除去する。(図5(B)参照)。

【0120】

第2のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体層105上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm〜数10nmと極めて波長が短い超紫外線(Extrem Ultraviolet)を用いてフォトリソグラフィ工程でのレジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流が極めて小さいため、低消費電力も図ることができる。

【0121】

なお、導電膜のエッチングの際に、酸化物半導体層105がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。

【0122】

本実施の形態では、導電膜にチタン膜を用い、アンモニア過水(31重量%過酸化水素水:28重量%アンモニア水:水=5:2:2)を用いて、導電膜をウェットエッチングすることで、ソース電極及びドレイン電極層107を形成する。あるいは、塩素(Cl2)、塩化ホウ素(BCl3)などを含むガスを用いて、導電膜をドライエッチングしてもよい。

【0123】

上記パターニングによりソース電極層106及びドレイン電極層107を形成する際に、島状の酸化物半導体層105の露出した部分が一部エッチングされることで、島状の酸化物半導体層105に溝部(凹部)が形成されることもある。また、ソース電極層106及びドレイン電極層107を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0124】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度を持たせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクによって形成されたレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形させることができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも異なる2種類以上のパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

【0125】

次いで、N2O、N2、またはAr等のガスを用いたプラズマ処理を行ってもよい。このプラズマ処理によって露出している酸化物半導体層105の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いて、プラズマ処理を行ってもよい。

【0126】

次いで、ゲート絶縁層109を形成する。ゲート絶縁層109は、スパッタリング法等を用いて、酸化ケイ素層、窒化ケイ素層、酸化窒化ケイ素層、窒化酸化ケイ素層、酸化ハフニウム層、酸化タンタル層、又は酸化アルミニウム層を単層で又は積層して形成することができる。なお、ゲート絶縁層109中に水素が多量に含まれないようにするためには、スパッタリング法でゲート絶縁層109を成膜することが好ましい。スパッタリング法により酸化ケイ素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

【0127】

酸化物半導体は、水素が含有されると特性に悪影響を及ぼす。そのため、酸化物半導体層105と接するゲート絶縁層109は、水素、酸素等の不純物を極力含まないことが望ましい。スパッタリング法により酸化窒化ケイ素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は、石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

【0128】

本実施の形態の酸化物半導体は、不純物を除去することによりI型化又は実質的にI型化された酸化物半導体(高純度化された酸化物半導体)を用いる。このような高純度化された酸化物半導体は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁層109との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層(GI)は高品質が要求される。

【0129】

バリア性の高い材料を用いた絶縁層と、含まれる窒素の比率が低い酸化ケイ素膜、酸化窒化ケイ素膜などの絶縁膜とを積層させた構造を有するゲート絶縁層109を形成してもよい。この場合、酸化ケイ素膜、酸化窒化ケイ素膜などの絶縁膜は、バリア性を有する絶縁膜と酸化物半導体層の間に形成する。バリア性の高い絶縁膜として、例えば窒化ケイ素膜、窒化酸化ケイ素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などがあげられる。バリア性を有する絶縁膜を用いることで、水分、または水素などの雰囲気中の不純物、または基板内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体層内、ゲート絶縁層109内、その近傍等に入り込むのを防ぐことができる。また、酸化物半導体層に接するように、含まれる窒素の比率が低い酸化ケイ素膜、酸化窒化ケイ素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が直接酸化物半導体層に接するのを防ぐことができる。

【0130】

なお、ゲート絶縁層109を形成した後に、第2の加熱処理を施してもよい。加熱処理は、窒素、超乾燥空気、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、好ましくは200℃以上400℃以下(例えば250℃以下350℃以下)で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下であることが望ましい。例えば、窒素雰囲気下で250℃、1時間の加熱処理を行う。或いは、第1の加熱処理と同様に高温短時間のRTA処理を行ってもよい。酸素を含むゲート絶縁層109が埋められた後に加熱処理が施されることによって、第1の加熱処理により、酸化物半導体層105に酸素欠損が発生していたとしても、ゲート絶縁層109から酸化物半導体層105に酸素が供与される。そして、酸化物半導体層105に酸素が供与されることで、酸化物半導体層105においてドナーとなる酸素欠損を低減し、化学量論比を満たすことが可能である。その結果、酸化物半導体層105をI型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。この第2の加熱処理を行うタイミングは、ゲート絶縁層109の形成後であれば特に限定されない。

【0131】

また、酸素雰囲気下で、酸化物半導体層105に加熱処理を施すことで、酸化物半導体に酸素を添加し、酸化物半導体層105中においてドナーとなる酸素欠損を低減させてもよい。加熱処理の温度は、例えば100℃以上350℃未満、好ましくは150℃以上250℃未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素などが含まれていないことが好ましい。または、加熱処理装置に導入する酸素ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち酸素中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0132】

本実施の形態では、不活性ガス雰囲気下、または、酸素ガス雰囲気下で第2の加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上350℃以下)を行う。例えば、窒素雰囲気下で250℃、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル形成領域)がゲート絶縁層109と接した状態で加熱される。

【0133】

次いで、ゲート絶縁層109に、ソース電極層106及びドレイン電極層107上面に達する開口を形成する(図5(C)参照)。例えば、第3のフォトリソグラフィ工程を行い、ゲート絶縁層109をエッチングすることにより、開口を形成することができる。エッチングとしてはウェットエッチング、ドライエッチングのいずれを用いてもよいが、微細加工の観点からは、ドライエッチングを用いることが好適である。

【0134】

次に、当該開口を埋め込み、さらにゲート絶縁層109上を覆うように導電膜を形成する。導電膜の形成はPVD法やCVD法等の成膜法を用いて行うことができる。導電膜の材料は、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等の金属材料、これら金属材料を主成分とする合金材料を用いた導電膜、或いはこれらの金属の窒化物を用いることができる。

【0135】

導電膜を形成した後には、エッチング等の方法を用いて導電膜の一部を除去し、ゲート電極層111、ソース電極層106及びドレイン電極層107と導通したソース配線116及びドレイン配線117を作製する(図5(D)参照)。

【0136】

なお、ソース配線とは、少なくとも一つのソース電極と別の電極を接続させるための配線のことをいう。

【0137】

次いで、ゲート絶縁層109、ゲート電極層111、ソース配線116及びドレイン配線117を覆う保護絶縁層113を成膜する(図5(E)参照)。保護絶縁層113は例えば、RFスパッタ法を用いて窒化ケイ素膜を形成する。RFスパッタ法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化ケイ素膜、窒化アルミニウム膜などを用いる。本実施の形態では、窒化ケイ素膜を用いて保護絶縁層113を形成する。

【0138】

本実施の形態では、保護絶縁層113として、ゲート電極層111まで形成された基板101を100℃から、400℃の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入し、シリコン半導体のターゲットを用いて窒化ケイ素膜を成膜する。この場合においても、処理室内の残留水分を除去しつつ保護絶縁層113を形成することが好ましい。

【0139】

以上の工程で本実施の形態に示すトランジスタが形成される。

【0140】

本実施の形態のトランジスタは、半導体層に、酸化物半導体を用いているため、高耐圧で、大電流の制御が可能である。そのため、大電流を扱うパワーデバイス等に用いるトランジスタに適している。

【0141】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0142】

(実施の形態4)

本実施の形態では、本発明の半導体装置の一例である電圧変換回路(DC−DCコンバータ)について示す。

【0143】

図6(A)に示すコンバータ回路301は、トランジスタ302、コイル303、ダイオード304、コンデンサ305、直流電源306を有する昇圧回路である。

【0144】

なお、本実施の形態において、トランジスタ302またはトランジスタ312として例えば、本発明の一態様の半導体素子を使用することができる。

【0145】

コイル303の一方の端子は、直流電源306の陽極に電気的に接続されている。コイル303の他方の端子はトランジスタ302のソース或いはドレインの一方と電気的に接続されている。トランジスタ302のソース或いはドレインの他方は直流電源306の陰極及び、コンデンサ305の一方の端子と電気的に接続されている。コンデンサ305の他方の端子は、ダイオード304の出力端子及び出力端子OUTに電気的に接続されている。なお、直流電源306の陰極、トランジスタ302のソースあるいはドレインの他方、及びコンデンサ305の一方の端子は接地されている。

【0146】

トランジスタ302はスイッチング素子として機能する。またトランジスタ302のゲートは、コンバータ回路301の制御回路に接続されている。コンバータ回路301の制御回路からの信号により、トランジスタ302はオン状態あるいはオフ状態となる。

【0147】

スイッチング素子であるトランジスタ302がオン状態のとき、コイル303に流れ込む電流により、コイル303には励磁エネルギーが蓄えられる。

【0148】

トランジスタ302がオフ状態になると、コイル303に蓄えられた励磁エネルギーが放出される。コイル303から放出される励磁エネルギーに起因する電圧V2が、電圧V1に上積みされる。これによりコンバータ回路301は昇圧回路として機能する。

【0149】

トランジスタ302がオン状態の時間が長く、コイル303に蓄えたエネルギーが大きいほど、大電力を取り出すことができる。

【0150】

図6(B)に示すコンバータ回路311は、トランジスタ312、コイル313、ダイオード314、コンデンサ315を有する降圧回路である。

【0151】

トランジスタ312のソースあるいはドレインの一方は、直流電源316の陽極に電気的に接続されている。トランジスタ312のソースあるいはドレインの他方は、ダイオード314の出力端子及びコイル313の一方の端子と電気的に接続されている。ダイオード314の入力端子は、直流電源316の陰極及びコンデンサ315の一方の端子に電気的に接続されている。ダイオードの出力端子は、トランジスタ312のソースあるいはドレインの他方及びコイル313の一方の端子と電気的に接続されている。コイル313の一方の端子は、トランジスタ312のソース或いはドレインの他方及びダイオード314の出力端子に電気的に接続されている。コイル313の他方の端子は、コンデンサ315の他方の端子及び出力端子OUTに電気的に接続されている。なお、直流電源316の陰極、ダイオード314の入力端子、及びコンデンサ315の一方の端子は接地されている。

【0152】

トランジスタ312はスイッチング素子として機能する。またトランジスタ312のゲートは、コンバータ回路311の制御回路に接続されている。コンバータ回路311の制御回路からの信号により、トランジスタ312はオン状態あるいはオフ状態となる。

【0153】

スイッチング素子であるトランジスタ312がオン状態のとき、入力から出力に流れる降圧回路の電流により、コイル313には励磁エネルギーが蓄えられる。

【0154】

トランジスタ312がオフ状態になると、コイル313は電流を保とうとして起電力を発生させ、ダイオード314をオン状態にする。ダイオード314を通じて電流が流れることによって、電圧V2が低下する。電圧V1より電圧V2が低下するため、コンバータ回路311は降圧回路として機能する。なお本実施の形態において、トランジスタ312として例えば電界効果トランジスタを用いることができる。

【0155】

また本実施の形態において、コイル303とコイル313として、基板上にコイル状に形成した配線を用いることができる。

【0156】

また本実施の形態において、ダイオード304とダイオード314として、例えばショットキーバリアダイオードを用いることができる。

【0157】

また、本実施の形態において、コンデンサ305とコンデンサ315として、例えば第1の電極と、第2の電極と、誘電体と、を有する構成のコンデンサを用いることができる。

【0158】

本発明の一態様に示した半導体素子は、半導体層に酸化物半導体を用いているため、高耐圧で、大電流の制御が可能であるという特性を有する。そのため、本実施の形態で示した電圧変換回路に用いることによって、大電流を駆動できる回路を作製できる。

【0159】

本発明の一態様に示した半導体素子は、貫通電極によって、トランジスタを並列接続させているため、トランジスタの実質的なW長を長くすることができ、パワーデバイスに適した高移動度の半導体素子を提供できる。そのため、本実施の形態で示した電圧変換回路に用いることによって、回路の駆動速度が上昇する。

【0160】

また、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【符号の説明】

【0161】

100 半導体チップ

100a 半導体チップ

100b 半導体チップ

101 基板

101a 基板

103 下地膜

103a 下地膜

105 酸化物半導体層

105a 酸化物半導体層

106 ソース電極層

106a ソース電極層

107 ドレイン電極層

107a ドレイン電極層

109 ゲート絶縁層

109a ゲート絶縁層

111 ゲート電極層

111a ゲート電極層

113 保護絶縁層

113a 保護絶縁層

115 保護層

116 ソース配線

116a ソース配線

117 ドレイン配線

117a ドレイン配線

120a 貫通電極

121a 貫通電極

122 貫通電極

122a 貫通電極

130a トランジスタ

130b トランジスタ

200 ビア

201 絶縁膜

203 導電性バリア膜

205 配線

207 導電体

301 コンバータ回路

302 トランジスタ

303 コイル

304 ダイオード

305 コンデンサ

306 直流電源

311 コンバータ回路

312 トランジスタ

313 コイル

314 ダイオード

315 コンデンサ

316 直流電源

【技術分野】

【0001】

半導体素子、該半導体素子を用いた半導体装置、及び半導体素子の作製方法に関する。

【0002】

なお、本明細書中において、半導体素子は半導体特性を利用することで機能する素子を指し、複数のトランジスタが集積された構成も含む。また、本明細書中において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路、電子部品、及び電子機器はすべて半導体装置である。

【背景技術】

【0003】

電力変換装置に使用される半導体装置、いわゆるパワーデバイスは、高耐圧、かつ低損失であることが望ましい。従来から、シリコン半導体を用いたパワーデバイスが開示されている。しかし、シリコンを用いた半導体素子では、その物理的な特性が理論値の限界に来ていると言われており、さらなる高耐圧と大電流の制御が可能なパワーデバイスを実現するためには、特性の向上が可能な新たな半導体材料や、半導体装置の新しい構造を提供することが求められている。

【0004】

シリコン半導体と代わる、高耐圧、高変換効率、高速スイッチングなどの諸特性を向上させる可能性がある半導体材料として、例えば、炭化ケイ素や窒化ガリウムなどが開示されている(特許文献1及び特許文献2)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−129628号公報

【特許文献2】特開2010―171416号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところが、炭化ケイ素の成膜温度は約1500℃、窒化ガリウムの成膜温度は約1100℃と、これらの化合物半導体は、成膜温度が極めて高く、基板の大型化が困難であるため、量産性が低いといった問題がある。

【0007】

本発明はこのような技術的背景のもとでなされたものである。したがって、その目的は、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする、また、該半導体素子の作製方法を提供することを課題の一とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、本発明者は、酸化物半導体に着目した。

【0009】

酸化物半導体は、広いバンドギャップを示すため、シリコン等に比べ高い耐圧を示し、パワーデバイス用の半導体材料に求められる高い絶縁破壊耐性を備えている。

【0010】

また、酸化物半導体膜の成膜温度は700℃程度であるため、基板の大型化にも対応できる。さらに、酸化物半導体膜は、スパッタリング法や湿式法(例えば、印刷法)などにより作製可能であり、ドープ工程が不要であることなどからも、量産性に優れている。

【0011】

一方、酸化物半導体の移動度は、大電流を流すパワーデバイス用の半導体材料としては、必ずしも十分ではない場合がある。移動度の低い半導体材料を用いてパワーデバイス用トランジスタを作製すると、大電流を速やかに流すことができず、また、大電流を流そうとするとトランジスタが発熱するといった問題が生じる場合がある。

【0012】

こうした問題を解決する手段としては、トランジスタのW長(チャネル幅)を長くする方法がある。

【0013】

しかし、トランジスタのW長を長くすると、トランジスタの面積が大きくなり、該トランジスタが回路に占める面積が大きくなってしまう問題がある。さらに、トランジスタ1つあたりの面積が大きくなると、1基板あたりで作製できるトランジスタの数が減ってしまう。また、パーティクル等による欠陥を1箇所でも含むと、トランジスタは信頼性が損なわれてしまう。従ってパーティクル等による欠陥が1基板あたりに同数生じる場合においては、トランジスタの面積が大きいほど、不良となる確率が高まってしまう。

【0014】

したがって、上記課題を解決するためには、広いバンドギャップを有する酸化物半導体をチャネル形成領域に用いた1以上のトランジスタと、該トランジスタを電気的に接続する貫通電極とを含む半導体チップを積層し、該貫通電極を介してトランジスタを電気的に並列接続することによって、素子の面積を巨大化することなく、実質的にW長の長いトランジスタを作製すればよい。

【0015】

すなわち、本発明の一態様は、半導体層に酸化物半導体を用いる第1のトランジスタと、第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第1の基板と、半導体層に酸化物半導体を用いる第2のトランジスタと、第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第2の基板と、を積層して備え、第1のトランジスタと第2のトランジスタは、それぞれの貫通電極を介して電気的に並列接続された半導体素子である。

【0016】

上記本発明の一態様によれば、半導体材料に酸化物半導体を用いることによって、高耐圧で、低損失である、パワーデバイスに適した性質を兼ね備えたトランジスタを作製できる。また、酸化物半導体膜は成膜温度が他のパワーデバイス用半導体材料と比較して低いため、基板の大型化にも対応でき、量産性のよいトランジスタを作製できる。

【0017】

また、本発明の一態様は、基板を積層して、トランジスタを電気的に並列接続することにより、素子の面積を巨大化させることなく、実質的なW長を長くすることが可能であり、パワーデバイスに必要な大電流を速やかに流すことのできる半導体素子を提供できる。

【0018】

また、本発明の一態様は、基板を貫通する貫通電極を用いる半導体素子である。貫通電極による積層方法では、電極層から引き出す配線の長さが自由に設定できるため、基板が巨大化しても配線の長さを自由に設定することができ、配線からの熱の発生や、配線抵抗を低減できる。

【0019】

また、上記半導体素子において、酸化物半導体は、3eV以上のバンドギャップ有する酸化物半導体からなることが好ましい。その結果、耐圧性に優れたトランジスタを提供することができる。

【0020】

また、上記半導体素子において、第1の基板及び第2の基板にシリコン基板を用いることが好ましい。シリコン基板を用いることで、半導体チップを積層しても、シリコンの優れた放熱性により、熱による半導体素子の劣化を防止できる。また、シリコンは加工性がよいため、貫通電極作製時の孔あけ加工を容易に行うことができる。

【0021】

また、上記半導体素子において、第1の基板及び第2の基板に絶縁性基板を用いてもよい。絶縁性基板を用いることで、貫通電極と基板の導通を防ぐ絶縁膜の形成が不要となり、工程が簡略化されるため好ましい。

【0022】

また、本発明の一態様は、上記半導体素子を用いた半導体装置である。その結果、高耐圧で、大電流の制御が可能である、高性能な半導体装置を提供することができる。

【0023】

また、本発明の一態様は、基板の第1の領域に第1のトランジスタと、基板の第2の領域に第2のトランジスタとを作製し、第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層、並びに第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層と、それぞれ電気的に接続する6つの貫通電極を作製し、第1の領域を備える第1の半導体チップと、第2の領域を備える第2の半導体チップとを、基板を分断して形成する第1のステップと、第1の半導体チップ及び第2の半導体チップを積層し、第1のトランジスタと第2のトランジスタを、貫通電極を介して電気的に並列接続させる第2のステップを有する半導体素子の作製方法である。その結果、W長の長い半導体素子を、素子の面積を巨大化させることなく作製することができるため、基板の不良等の影響を受けにくく、効率よく半導体素子を作製することができる。

【0024】

なお、本明細書中において、半導体チップとは半導体層に酸化物半導体を用いるトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極、を有する基板を有する。

【0025】

また、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」又は「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極層」の表現であれば、ゲート絶縁層とゲート電極層との間に他の構成要素を含むものを除外しない。また、「上」「下」の用語は説明の便宜のために用いる表現に過ぎず、特に言及する場合を除き、その上下を入れ替えたものも含む。

【0026】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

【0027】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【発明の効果】

【0028】

本発明の一態様によれば、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供できる。

また、該半導体素子を用いた半導体装置を提供できる。また、該半導体素子の作製方法を提供できる。

【図面の簡単な説明】

【0029】

【図1】実施の態様に係る半導体素子を説明する図。

【図2】実施の態様に係る半導体素子の作製方法を説明する図。

【図3】実施の態様に係る半導体素子の作製方法を説明する図。

【図4】実施の態様に係る半導体素子の作製方法を説明する図。

【図5】実施の態様に係るトランジスタの作製方法を説明する図。

【図6】実施の態様に係るコンバータ回路を説明する図。

【発明を実施するための形態】

【0030】

実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0031】

(実施の形態1)

本実施の形態では、本発明の一態様の半導体素子の構造及び作製方法について図1〜図4を用いて説明する。

【0032】

図1(A)(B)に、本発明の一態様の半導体素子の構造の一例を示す。図1(B)は本発明の一態様の半導体素子の上面図を示す。図1(A)は、図1(B)におけるP1−P2間の断面図である。

【0033】

本発明の一態様は図4(C)に示すように、半導体チップを複数積層して作製する半導体素子である。積層する半導体チップの枚数は2枚以上であれば何枚でもよく、要求される性能に合わせて適宜決定することができる。本実施の形態では、半導体チップが導電体を介して2つ積層されている構成について説明する。図1(A)に示すように、半導体素子は、半導体チップ100aと半導体チップ100bとが導電体207を介して接続する構成となっている。

【0034】

<半導体チップの構成>

続いて、半導体チップについて図1を用いて説明する。図1(A)(B)に示す半導体チップ100aは、1つのトランジスタ130aと、該トランジスタ130aのゲート電極層111aと電気的に接続する貫通電極120a、ソース電極層106aと電気的に接続する貫通電極121a、ドレイン電極層107aと電気的に接続する貫通電極122aの3つの貫通電極を備えている。また、図1(A)に示すように、半導体チップ100bはトランジスタ130b及び3つの貫通電極を備える。本実施の形態において、半導体チップが備えるトランジスタはすべて同一の構成とする。なお、本発明の一態様の半導体チップの構成はこれに限らず、1つの半導体チップが複数のトランジスタを備えていてもよい。

【0035】

<トランジスタの構成>

本実施の形態の半導体チップが備えるトランジスタは半導体層に酸化物半導体を用いる。

【0036】

以下にトランジスタ130aの構成を説明する。トランジスタ130bは、トランジスタ130aと同様の構成を有する。重複する説明を避けるため、トランジスタ130aの構成の説明をもってトランジスタ130bの説明に援用する。

【0037】

本実施の形態では、トップゲート・トップコンタクト構造のトランジスタを半導体チップが有する構成を例に用いて説明するが、本発明の一態様の半導体素子に用いることができるトランジスタの構成はこの構成に特に限定されず、ボトムゲート型構造を用いてもトップゲート型構造を用いても良い。さらに、ボトムコンタクト構造を用いても、トップコンタクト構造を用いても良い。

【0038】

図1(A)において、トランジスタ130aはシリコン基板101a上に、シリコン基板101aを覆う下地膜103aと、下地膜103a上の島状の酸化物半導体層105aと、酸化物半導体層105aと接する一対のソース電極層106a及びドレイン電極層107aと、酸化物半導体層105a、ソース電極層106a及びドレイン電極層107aを覆うように形成されたゲート絶縁層109aと、ゲート絶縁層109a上において、酸化物半導体層105aのチャネル形成領域と重なるゲート電極層111aと、ゲート電極層111a、及びゲート絶縁層109aを覆う保護絶縁層113aを有する。また、ソース配線116aはゲート絶縁層109aに形成した開口部を介してソース電極層106aと電気的に接続しており、ドレイン配線117aはゲート絶縁層109aに形成した開口部を介してドレイン電極層107aと電気的に接続する。

【0039】

なお、本実施の形態では基板にシリコン基板を用いたが、半導体チップを作製する基板には特に制限はない。シリコン基板は加工性に優れ、貫通電極作製時の孔あけが容易であることから、好適に用いることができる。さらに、シリコンの優れた放熱性により、トランジスタを積層しても、熱による半導体素子の劣化を防止できる。なお、絶縁体よりなる絶縁性基板を用いると、貫通電極と基板の導通を防ぐ絶縁膜201の形成工程が不要となる。絶縁性基板としては、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板や、BCB(ベンゾシクロブタン)、エポキシ等の絶縁性樹脂基板(有機絶縁性基板)や、セラミック基板、石英基板、サファイア基板などを用いることができる。

【0040】

<貫通電極の構成>

半導体チップには、トランジスタとは重畳しない領域において、貫通電極が設けられている。ゲート電極層111aは貫通電極120aと電気的に接続し、ソース電極層106aは貫通電極121aと電気的に接続し、ドレイン電極層107aは貫通電極122aと電気的に接続している(図1(B)参照)

【0041】

それぞれの貫通電極は半導体チップの上面及び半導体チップの下面に露出している。

【0042】

<電気的な接続関係>

すでに説明したように、半導体素子は半導体チップ100aと半導体チップ100bとを接続した素子である。具体的には、ゲート電極層と接続した貫通電極同士、ソース電極層と接続した貫通電極同士、ならびにドレイン電極層と接続した貫通電極同士が、それぞれ導電体207によって電気的に接続している。すなわち、トランジスタ130aと、トランジスタ130bは電気的に並列接続している。

【0043】

以上のように、本実施の形態の半導体素子は半導体層に酸化物半導体を用いる第1のトランジスタと、第1のトランジスタのゲート電極層と、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第1の基板と、半導体層に酸化物半導体を用いる第2のトランジスタと、第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第2の基板とが積層された構成となっている。さらに、第1のトランジスタと第2のトランジスタは、それぞれの貫通電極を介して電気的に並列接続されている。

【0044】

本実施の形態の半導体素子は、貫通電極によってトランジスタが並列接続されているため、トランジスタの面積を大きくすることなく、実質的なW長を長くすることが可能であり、高移動度の半導体素子を提供することができる。

【0045】

また、本実施の形態の半導体素子は、半導体層に酸化物半導体を用いているため、高耐圧で、大電流の制御が可能であるという特性を有する。そのため、大電流を扱うパワーデバイス等の半導体素子に適している。

【0046】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0047】

(実施の形態2)

本実施の形態では、実施の形態1に例示した半導体素子の作製方法について図2〜図4を用いて説明する。

【0048】

半導体素子の作製方法は2つのステップからなる。具体的には、複数のトランジスタと、トランジスタのゲート電極層、ソース電極層、並びにドレイン電極層の各々に電気的に接続する貫通電極とをシリコン基板101上に作製し(図4(A)参照)、シリコン基板101を分断して半導体チップ100を作製する第1のステップ(図4(B)参照)と、複数の半導体チップ100を積層して(図4(C)参照)、互いの貫通電極を接続する第2のステップ(図4(D)参照)からなる。

【0049】

つまり、基板の第1の領域に第1のトランジスタと、基板の第2の領域に第2のトランジスタとを作製し、第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極を第1の領域に、第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極を第2の領域に作製し、第1の領域を備える第1の半導体チップと、第2の領域を備える第2の半導体チップとを、基板を分断して形成する第1のステップと、第1の半導体チップ及び第2の半導体チップを積層し、第1のトランジスタと第2のトランジスタを、貫通電極を介して電気的に並列接続させる第2のステップを有する半導体素子の作製方法である。

【0050】

<第1のステップ>

シリコン基板101上に半導体層に酸化物半導体を用いたトランジスタを複数作製する。なお、トランジスタの作製方法の詳細は実施の形態3で説明する。

【0051】

続いて、トランジスタ同士を接続する貫通電極を作製する。

【0052】

貫通電極の作製プロセスを、図2及び図3を用いて説明する。なお、図2及び図3にはトランジスタのドレイン電極層107と導通する貫通電極122の作製プロセスのみについて図示し、ソース電極層または、ゲート電極層111と導通する貫通電極については、ドレイン電極層107と導通する貫通電極122と同様の工程で作製するものとし、説明及び図示を省略する。

【0053】

図2(B)に示すように、貫通電極122を埋め込むためのビア200を形成する。ビア200は、保護絶縁層113にドレイン配線117の上面に達する開口と、トランジスタとは重畳しない領域に保護絶縁層113、ゲート絶縁層109、下地膜103を貫き、シリコン基板101に凹部を形成する開口とからなる(図2(B)参照)。なお、ビア200は基板にシリコンウェハを用いた場合にはエッチングやレーザを用いて形成し、ガラスを用いた場合には異方性エッチングが困難であることから、サンドブラストやレーザ等を用いて形成する。

【0054】

次いで、図2(C)に示すように、基板を熱処理することによって絶縁膜201(酸化膜もしくは窒化膜)をシリコン基板101に形成する。本実施の形態では、シリコン基板101に熱酸化処理を行うことにより、酸化膜を形成する。熱酸化処理は、酸化性雰囲気中にハロゲンを添加して行うことが好ましい。例えば、塩素(Cl)が添加された酸化性雰囲気中で単結晶シリコン基板に熱酸化処理を行うことにより、塩素酸化された酸化膜を形成することができる。なお、基板に絶縁体からなる絶縁性基板を用いる場合、熱処理は不要である。

【0055】

なお、基板の熱処理によって、ゲート電極層111、ソース配線及びドレイン配線117上に絶縁膜が形成された場合は、該絶縁膜をエッチングして、導電層を露出する必要がある。

【0056】

次いで、図2(D)に示すように、ビア200に導電性バリア膜203を形成する。導電性バリア膜203は配線205からの金属の拡散を防ぐ保護膜としての機能を有している。導電性バリア膜203には、窒化タンタル、窒化チタン,又は窒化タングステン、炭化タンタル(TaC)、炭化チタン(TiC)から選ばれた一種或いは複数種の材料を用いればよい。また、シリコンを有する3次元系アモルファスバリア膜を用いてもよい。

【0057】

導電性バリア膜203の形成はPVD法やCVD法等の成膜法、スパッタリング法を用いて行うことができる。例えば窒化チタン膜の場合、窒素とアルゴンとをスパッタリングガスとし、出力150Wで成膜すればよい。多結晶構造を有し、粒界の存在により拡散防止機能が向上される。なお、このとき、スパッタの出力をあげること、アルゴンガスの流量比を大きくすること、基板の温度を高くして成膜すること等により、緻密な膜を形成し、バリア性を高めることができる。本実施の形態では、窒化タンタル膜を用いる。窒化タンタル膜は、バリア性が高い導電膜であること、また、後の工程で、研磨することを考えた場合、CMP法(Chemical−Mechanical−Polishing:化学的・機械的研磨法)を用いて容易に加工が可能であることから、本実施の形態に用いる導電性バリア膜に適している。

【0058】

次いで、図2(E)に示すように、ビア200に配線205を埋め込む。配線には、Cu、Ag、Ni等の金属を用いる。配線方法としてはCVD法、スパッタリング法、リモートプラズマ法、メッキ法等を用いて形成される。マルチチャンバーを用いることで、導電性バリア膜と配線とを大気にさらすことなく連続成膜することが可能となる。このように連続成膜を行うことにより、界面への不純物の付着を防止することができ、良好な成膜を行うことが可能になる。

【0059】

エッチングにより、導電性バリア膜203及び配線205を所望の形状にエッチングする。なお、メッキによる配線の埋め込みでは、最初から選択的に配線205を形成することも可能である。

【0060】

次いで、図3(A)に示すように、配線205上に保護層115を形成する。保護層115は、プラズマCVD法またはスパッタリング法等を用いて形成することができる。また、保護層115は、酸化ケイ素膜、窒化ケイ素膜、酸化窒化ケイ素膜、窒化酸化ケイ素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ハフニウム膜、または酸化タンタル膜などから選ばれた一又は複数の膜により単層で、又は積層させて形成することができる。

【0061】

次いで、図3(B)に示すように、配線205を上面及び下面に露出させる。上面において、保護層115及び配線205を研磨することによって、配線205を上面に露出させるとともに、該上面を平坦化する。下面においては、基板101、絶縁膜201、及び導電性バリア膜203を研磨して、配線205を露出させるとともに、該下面を平坦化する。平坦化処理としては、研磨処理やレーザの照射処理を行うことができる。研磨処理や、レーザ光の照射処理は複数回行ってもよいし、組み合わせて行ってもよい。また、処理の順序も限定されず、適宜選択することができる。レーザ光の照射処理に代えてランプ光の照射処理を行ってもよい。

【0062】

配線205が上面及び下面に露出したことによって、ドレイン電極層107が半導体チップの上面及び下面に導通した。図3(B)に示すとおり、トランジスタの上面及び下面と各電極層をつなぐ、配線205及び導電性バリア膜203のことを貫通電極122と呼ぶ。

【0063】

次いで、図3(C)に示すように、導電体207を形成する。

【0064】

導電体207は、導電性微粒子、導電性粉末を含む導電性ペースト、または、導電性微粒子、導電性粉末を含む導電性液体のような流動性を有する導電性材料で形成することが好ましい。このような導電性材料を用いることで、液滴吐出法(インクジェット法、ディスペンサ法などの方法が含まれる)、スクリーン印刷法などの印刷法などにより、導電体207を形成することが可能である。これらの方法は、CVD装置、スパッタ装置のような複雑な成膜装置での成膜工程、およびフォトマスクを形成するための露光工程を行うことなく、必要な箇所に凸状の導電体207を形成することが可能である。

【0065】

導電性ペースト及び導電性液体は、導電性微粒子、導電性粉末が分散された材料、またはこれらが溶解している導電性材料である。例えば、導電性液体に含まれる導電性粉体または導電性微粒子の材料としては、例えばAg、Au、Cu、Ni、Pt、Pd、Ndなどの金属、これらの金属材料の合金(例えばAg−Pd)、酸化インジウム、酸化亜鉛などの導電性酸化物材料などがあげられる。また、導電性粉体、または導電性微粒子を溶解させるまたは分散させるための媒質(溶媒、分散剤)としては、例えば、紫外線硬化樹脂などの光硬化性樹脂や、熱硬化性樹脂の前駆体材料があげられる。紫外線硬化樹脂としてはアクリル系樹脂、エポキシ系樹脂があげられる。また、熱硬化樹脂としてはポリイミド系樹脂があげられる。

【0066】

続いて、基板101を切断し、個々の半導体チップ100に分断する(図4(B)参照)。切り分けには、ダイシング、スクライビング、又はレーザーカット法等を用いて、選択的に分断することができる。

【0067】

上記のように、基板上に複数のトランジスタを作製してから切り分けることによって、良品のトランジスタと、パーティクル等の影響を受けた不良品のトランジスタとに選別することが可能であり、良品のみを選択的に積層することができるため、半導体素子を効率的に作製することが可能である。

【0068】

以上の工程で半導体チップ100を形成できる。

【0069】

<第2のステップ>

次いで、図3(D)に示すように、切り分けた半導体チップ100を上下に積層させ、貫通電極122及び導電体207を介して並列接続する。

【0070】

導電体207と基板下面に露出した貫通電極が重なるように接触させて、半導体チップ同士を電気的に接続する。半導体チップ同士の固定方法としては、貫通電極同士をはんだ等で固定し、さらに、接続信頼性を向上させるため、封止樹脂によって固定することも可能である。使用する樹脂としては光硬化性の樹脂や熱硬化性のもの或いは自然硬化性の樹脂等を用いることができる。

【0071】

上下に積層する半導体チップの個数は自由に決めることができ、要求される性能に応じて積層する個数を変えればよい。

【0072】

以上のように、本実施の形態の半導体素子を作製することができる。

【0073】

本実施の形態の半導体素子は、半導体層に、酸化物半導体を用いているため、高耐圧で、大電流の制御が可能であるという特性を有する。そのため、大電流を扱うパワーデバイス等の半導体素子に適している。

【0074】

本実施の形態の半導体素子は、貫通電極によって、トランジスタを並列接続させているため、トランジスタの実質的なW長を長くすることができ、パワーデバイスに適した高移動度を実現する。

【0075】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0076】

(実施の形態3)

本実施の形態では、実施の形態1乃至2で示した半導体素子に適用可能なトランジスタの作製方法について図5を用いて説明する。

【0077】

本実施の形態のトランジスタは半導体層に酸化物半導体を用いる。本実施の形態の半導体層に用いる酸化物半導体は、n型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することによりI型(真性)の酸化物半導体、またはI型(真性)に限りなく近い酸化物半導体としたものである。

【0078】

なお、高純度化された酸化物半導体中ではキャリアが極めて少なく、キャリア濃度は1×1014/cm3未満、好ましくは1×1012/cm3未満、さらに好ましくは1×1011/am3未満となる。また、このようにキャリアが少ないことで、オフ状態における電流(オフ電流)は十分に小さくなる。

【0079】

具体的には、上述の酸化物半導体層を具備するトランジスタでは、オフ状態でのソースとドレイン間のチャネル幅1μmあたりのリーク電流密度(オフ電流密度)は、ソースとドレイン間の電圧が3.5V、使用時の温度条件下(例えば、25℃)において、100zA/μm(1×10−19A/μm)以下、もしくは10zA/μm(1×10−20A/μm)以下、さらには、1zA/μm(1×10−21A/μm)以下とすることができる。

【0080】

また、高純度化された酸化物半導体層を具備するトランジスタは、オン電流の温度依存性がほとんど見られず、高温状態においてもオフ電流は非常に小さいままである。

【0081】

まず、基板101上に下地膜103を形成する。

【0082】

下地膜としては、例えば、酸化ケイ素膜、酸化窒化ケイ素膜、窒化ケイ素膜、窒化酸化ケイ素膜、窒化アルミニウム膜、または、窒化酸化アルミニウム膜のいずれか一つを単層で、あるいは複数を積層させて用いることができる。

【0083】

本実施の形態では、シリコン基板に熱酸化処理を行うことにより、下地膜103として熱酸化膜(ここでは酸化ケイ素膜)を形成する。

【0084】

基板101の裏面(トランジスタが形成されない面)に形成された熱酸化膜が不要であれば、エッチングや研磨によって除去してもよい。

【0085】

なお、本明細書中において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として酸素よりも窒素の含有量が多い物質をいう。例えば、酸化窒化ケイ素とは、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以上、ケイ素が25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれる物質とすることができる。また、窒化酸化ケイ素とは、酸素が5原子%以上35原子%以下、窒素が20原子%以上55原子%以下、ケイ素が25原子%以上35原子%以下、水素が10原子%以上30原子%以下の範囲で含まれる物質とすることができる。ただし、上記組成の範囲は、ラザフォード後方散乱法(RBS:Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS:Hydrogen Forward Scattering)を用いて測定した場合のものである。また、構成元素の含有比率は、その合計が100原子%を超えない値をとる。

【0086】

特に、下地膜103に、バリア性の高い絶縁膜、例えば窒化ケイ素膜、窒化酸化ケイ素膜窒化アルミニウム膜、または、窒化酸化アルミニウム膜などを用いることで、水分、または、水素などの雰囲気中の不純物、或いは基板101内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体層105内に入り込むのを防ぐことができる。

【0087】

なお、酸化物半導体中に含まれる、Li、Na等のアルカリ金属、及びCa等のアルカリ土類金属等の不純物は低減されていることが好ましい。具体的にはSIMSに検出されるNaが5×1016/cm3以下、好ましくは1×1016/cm3以下、さらに好ましくは1×1015/cm3以下であり、Liが5×1015/cm3以下、好ましくは1×1015/cm3以下であり、Kは5×1015/cm3以下、好ましくは1×1015/cm3以下であることが好ましい。

【0088】

アルカリ金属、及びアルカリ土類金属は酸化物半導体にとっては悪性の不純物であり、少ない方がよい。特にアルカリ金属のうち、Naは酸化物半導体と接する絶縁膜が酸化物であった場合、その中に拡散し、Na+となる。また、酸化物半導体内において、金属と酸素の結合を分析し、あるいは結合中に割り込む。その結果、トランジスタ特性の劣化(例えば、ノーマリオン化、閾値の負へのシフト)をもたらす。加えて、特性のばらつきの原因ともなる。このような問題は特に酸化物半導体中の水素の濃度が十分に低い場合において顕著となる。したがって、酸化物半導体中の水素の濃度が5×1019/cm3以下、特に5×1018/cm3以下である場合には、アルカリ金属の濃度を上記の値にすることが強く求められる。

【0089】

次に、下地膜103上に、酸化物半導体成膜用ターゲットを用い、スパッタ法により酸化物半導体膜を成膜する。また、酸化物半導体膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素混合雰囲気下においてスパッタ法により形成することができる。

【0090】

なお、酸化物半導体膜をスパッタ法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、下地膜103に付着している粉状物質(パーティクル、ごみともいう)を除去することが好ましい。逆スパッタとは、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素等を用いてもよい。また、アルゴン雰囲気に酸素、及び亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、及び四フッ化炭素などを加えた雰囲気で行ってもよい。

【0091】

酸化物半導体膜に用いられる酸化物半導体としては、四元系金属酸化物であるIn−Sn−Ga−Zn−O系酸化物半導体や、三元系金属酸化物であるIn−Ga−Zn―O系酸化物半導体、In−Sn−Zn−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系や、二元系金属酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体や、一元系金属酸化物であるIn−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体などの酸化物半導体を用いることができる。また、上記酸化物半導体膜に酸化ケイ素を含ませてもよい。酸化物半導体膜に結晶化を阻害する酸化ケイ素(SiOx(X>0))を含ませることで、製造プロセス中において酸化物半導体層の形成後に加熱処理した場合に、結晶化してしまうのを抑制することができる。なお、酸化物半導体層は非晶質な状態であることが好ましく、一部結晶化していてもよい。ここで、例えば、In−Ga−Zn−O系酸化物半導体とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物膜という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでもよい。

【0092】

また、酸化物半導体膜は、InMO3(ZnO)m(m>0)で表記される薄膜を用いることができる。ここで、MはGa、Al、Mn、Coから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、又はGa及びCoなどがある。

【0093】

本実施の形態の酸化物半導体は、好ましくはInを含有する酸化物半導体、さらに好ましくは、In及びGaを含有する酸化物半導体である。酸化物半導体層をI型(真性)とするため、脱水化または脱水素化は有効である。本実施の形態では、酸化物半導体膜としてIn―Ga―Zn−O系酸化物半導体成膜用ターゲットを用いてスパッタリング法により成膜する。

【0094】

In−Ga−Zn−O系酸化物半導体成膜用ターゲットの例としては、In、Ga、及びZnを含む酸化物半導体成膜用ターゲット(組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol数比])などを用いることもできる。また、In、Ga、およびZnを含む酸化物半導体成膜用ターゲットとして、In2O3:Ga2O3:ZnO=1:1:2[mol数比]、又はIn2O3:Ga2O3:ZnO=1:1:4[mol数比]の組成比を有するターゲットを用いることもできる。酸化物半導体成膜用ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

【0095】

減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板101上に酸化物半導膜を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H2O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱してもよい。

【0096】

次いで、酸化物半導体膜を第1のフォトリソグラフィ工程により島状の酸化物半導体層105に加工する。(図5(A)参照)。また、島状の酸化物半導体層105を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0097】

なお、ここでの酸化物半導体膜のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

【0098】

ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、塩化硼素(BCl3)、塩化ケイ素(SiCl4)、四塩化炭素(CCl4)など)が好ましい。

【0099】

また、フッ素を含むガス(フッ素系ガス、例えば四フッ化炭素(CF4)、フッ化硫黄(SF6)、フッ化窒素(NF3)、トリフルオロメタン(CHF3)など)、臭化水素(HBr)、酸素(O2)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、等を用いることが出来る。

【0100】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。

【0101】

ウェットエッチングに用いるエッチング液としては、燐酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO07N(関東化学社製)を用いてもよい。

【0102】

また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効に活用し低コスト化することができる。

【0103】

所望の加工形状にエッチングできるように、材料に合わせてエッチング条件(エッチング液、エッチング時間、温度等)を適宜調節する。

【0104】

本実施の形態では、エッチング液として燐酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッチング法により、酸化物半導体膜を島状の酸化物半導体層105に加工する。

【0105】

次いで、酸化物半導体層105に第1の加熱処理を施す。酸素、窒素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウムなど)雰囲気下において酸化物半導体層105に加熱処理を施すことで、水分、水素が脱離した酸化物半導体層105が形成される。第1の加熱処理の温度は、250℃以上750℃以下、または、400℃以上基板の歪み点未満とする。例えば、500℃、3分間以上6分間以下程度で行ってもよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、基板の歪み点を超える温度でも処理することができる。

【0106】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA装置(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0107】

例えば、第1の加熱処理として、650℃〜700℃の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

【0108】

なお、第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0109】

また、第1の加熱処理で酸化物半導体層を加熱した後、同じ炉に高純度の酸素ガス、高純度のN2Oガス、又は超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で−55℃)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)を導入してもよい。酸素ガスまたはN2Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN2Oガスの純度を、6N以上好ましくは7N以上(即ち、酸素ガスまたはN2Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。酸素ガス又はN2Oガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型(真性)化する。

【0110】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

【0111】

酸化物半導体層105に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層105上にソース電極層106及びドレイン電極層107を積層させた後、ソース電極層及び、ドレイン電極層上にゲート絶縁層109を形成した後、などのいずれで行ってもよい。

【0112】

以上の工程により、島状の酸化物半導体層中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体層の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体層を形成することができる。このため大面積基板を用いてトランジスタを作製することができ、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体層を用いることで、耐圧性が高く、オフ電流の著しく低いトランジスタを作製することができる。上記加熱処理は、酸化物半導体膜の成膜以降であれば、いつでも行うことができる。

【0113】

なお、酸化物半導体膜を加熱する場合、酸化物半導体膜の材料や加熱条件にもよるが、その表面に板状結晶が形成されることがある。板状結晶は、酸化物半導体膜の表面に対して略垂直にc軸配向した単結晶体であることが好ましい。なお、酸化物半導体膜下の下地膜の表面に凹凸がある場合、板状結晶は多結晶体となる。したがって、下地表面は可能な限り平坦であることが望まれる。

【0114】

また、酸化物半導体層を2回に分けて成膜し、2回に分けて加熱処理を行うことで、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜厚の厚い結晶領域(単結晶領域)、即ち、膜表面に垂直にc軸配向した結晶領域を有する酸化物半導体層を形成してもよい。例えば、3nm以上15nm以下の第1の酸化物半導体膜を成膜し、窒素、酸素、希ガス、または乾燥空気の雰囲気下で450℃以上850℃以下、好ましくは550℃以上750℃以下の第1の加熱処理を行い、表面を含む領域に結晶領域(板状結晶を含む)を有する第1の酸化物半導体膜を形成する。そして、第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、450℃以上850℃以下、好ましくは600℃以上700℃以下の第2の加熱処理を行い、第1の酸化物半導体膜を結晶成長の種として、上方に結晶成長させ、第2の酸化物半導体膜の全体を結晶化させ、結果として膜厚の厚い結晶領域を有する酸化物半導体層を形成してもよい。

【0115】

次いで、酸化物半導体層105上にソース電極層106及びドレイン電極層107となる導電膜を形成する。ソース電極及びドレイン電極となる導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wからから選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、Al、Cuなどの金属膜の下側もしくは上側にCr、Ta、Ti、Mo、Wなどの高融点金属膜を積層させた構成としても良い。また、Si、Ti、Ta、W、Mo、Cr、Nd、Sc、YなどAl膜に生ずるヒロックやウィスカーの発生を防止する元素が添加されているAl材料を用いることで耐熱性を向上させることが可能となる。

【0116】

また、導電膜は単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、さらにその上にチタン膜を成膜する3層構造などがあげられる。

【0117】

また、導電膜は導電性の金属酸化物で形成してもよい。導電性の金属酸化物としては酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3―SnO2、ITOと略記する)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)または前記金属酸化物材料にシリコンもしくは酸化ケイ素を含ませたものを用いることができる。

【0118】

導電膜成膜後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

【0119】

次いで、第2のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層106及びドレイン電極層107を形成した後、レジストマスクを除去する。(図5(B)参照)。

【0120】

第2のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体層105上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm〜数10nmと極めて波長が短い超紫外線(Extrem Ultraviolet)を用いてフォトリソグラフィ工程でのレジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流が極めて小さいため、低消費電力も図ることができる。

【0121】

なお、導電膜のエッチングの際に、酸化物半導体層105がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。

【0122】

本実施の形態では、導電膜にチタン膜を用い、アンモニア過水(31重量%過酸化水素水:28重量%アンモニア水:水=5:2:2)を用いて、導電膜をウェットエッチングすることで、ソース電極及びドレイン電極層107を形成する。あるいは、塩素(Cl2)、塩化ホウ素(BCl3)などを含むガスを用いて、導電膜をドライエッチングしてもよい。

【0123】

上記パターニングによりソース電極層106及びドレイン電極層107を形成する際に、島状の酸化物半導体層105の露出した部分が一部エッチングされることで、島状の酸化物半導体層105に溝部(凹部)が形成されることもある。また、ソース電極層106及びドレイン電極層107を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0124】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度を持たせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクによって形成されたレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形させることができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも異なる2種類以上のパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

【0125】

次いで、N2O、N2、またはAr等のガスを用いたプラズマ処理を行ってもよい。このプラズマ処理によって露出している酸化物半導体層105の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いて、プラズマ処理を行ってもよい。

【0126】

次いで、ゲート絶縁層109を形成する。ゲート絶縁層109は、スパッタリング法等を用いて、酸化ケイ素層、窒化ケイ素層、酸化窒化ケイ素層、窒化酸化ケイ素層、酸化ハフニウム層、酸化タンタル層、又は酸化アルミニウム層を単層で又は積層して形成することができる。なお、ゲート絶縁層109中に水素が多量に含まれないようにするためには、スパッタリング法でゲート絶縁層109を成膜することが好ましい。スパッタリング法により酸化ケイ素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

【0127】

酸化物半導体は、水素が含有されると特性に悪影響を及ぼす。そのため、酸化物半導体層105と接するゲート絶縁層109は、水素、酸素等の不純物を極力含まないことが望ましい。スパッタリング法により酸化窒化ケイ素膜を成膜する場合には、ターゲットとしてシリコンターゲット又は、石英ターゲットを用い、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

【0128】

本実施の形態の酸化物半導体は、不純物を除去することによりI型化又は実質的にI型化された酸化物半導体(高純度化された酸化物半導体)を用いる。このような高純度化された酸化物半導体は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁層109との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層(GI)は高品質が要求される。

【0129】

バリア性の高い材料を用いた絶縁層と、含まれる窒素の比率が低い酸化ケイ素膜、酸化窒化ケイ素膜などの絶縁膜とを積層させた構造を有するゲート絶縁層109を形成してもよい。この場合、酸化ケイ素膜、酸化窒化ケイ素膜などの絶縁膜は、バリア性を有する絶縁膜と酸化物半導体層の間に形成する。バリア性の高い絶縁膜として、例えば窒化ケイ素膜、窒化酸化ケイ素膜、窒化アルミニウム膜、または窒化酸化アルミニウム膜などがあげられる。バリア性を有する絶縁膜を用いることで、水分、または水素などの雰囲気中の不純物、または基板内に含まれるアルカリ金属、重金属などの不純物が、酸化物半導体層内、ゲート絶縁層109内、その近傍等に入り込むのを防ぐことができる。また、酸化物半導体層に接するように、含まれる窒素の比率が低い酸化ケイ素膜、酸化窒化ケイ素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が直接酸化物半導体層に接するのを防ぐことができる。

【0130】

なお、ゲート絶縁層109を形成した後に、第2の加熱処理を施してもよい。加熱処理は、窒素、超乾燥空気、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、好ましくは200℃以上400℃以下(例えば250℃以下350℃以下)で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下であることが望ましい。例えば、窒素雰囲気下で250℃、1時間の加熱処理を行う。或いは、第1の加熱処理と同様に高温短時間のRTA処理を行ってもよい。酸素を含むゲート絶縁層109が埋められた後に加熱処理が施されることによって、第1の加熱処理により、酸化物半導体層105に酸素欠損が発生していたとしても、ゲート絶縁層109から酸化物半導体層105に酸素が供与される。そして、酸化物半導体層105に酸素が供与されることで、酸化物半導体層105においてドナーとなる酸素欠損を低減し、化学量論比を満たすことが可能である。その結果、酸化物半導体層105をI型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。この第2の加熱処理を行うタイミングは、ゲート絶縁層109の形成後であれば特に限定されない。

【0131】

また、酸素雰囲気下で、酸化物半導体層105に加熱処理を施すことで、酸化物半導体に酸素を添加し、酸化物半導体層105中においてドナーとなる酸素欠損を低減させてもよい。加熱処理の温度は、例えば100℃以上350℃未満、好ましくは150℃以上250℃未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素などが含まれていないことが好ましい。または、加熱処理装置に導入する酸素ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち酸素中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0132】

本実施の形態では、不活性ガス雰囲気下、または、酸素ガス雰囲気下で第2の加熱処理(好ましくは200℃以上400℃以下、例えば250℃以上350℃以下)を行う。例えば、窒素雰囲気下で250℃、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル形成領域)がゲート絶縁層109と接した状態で加熱される。

【0133】

次いで、ゲート絶縁層109に、ソース電極層106及びドレイン電極層107上面に達する開口を形成する(図5(C)参照)。例えば、第3のフォトリソグラフィ工程を行い、ゲート絶縁層109をエッチングすることにより、開口を形成することができる。エッチングとしてはウェットエッチング、ドライエッチングのいずれを用いてもよいが、微細加工の観点からは、ドライエッチングを用いることが好適である。

【0134】

次に、当該開口を埋め込み、さらにゲート絶縁層109上を覆うように導電膜を形成する。導電膜の形成はPVD法やCVD法等の成膜法を用いて行うことができる。導電膜の材料は、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム等の金属材料、これら金属材料を主成分とする合金材料を用いた導電膜、或いはこれらの金属の窒化物を用いることができる。

【0135】

導電膜を形成した後には、エッチング等の方法を用いて導電膜の一部を除去し、ゲート電極層111、ソース電極層106及びドレイン電極層107と導通したソース配線116及びドレイン配線117を作製する(図5(D)参照)。

【0136】

なお、ソース配線とは、少なくとも一つのソース電極と別の電極を接続させるための配線のことをいう。

【0137】

次いで、ゲート絶縁層109、ゲート電極層111、ソース配線116及びドレイン配線117を覆う保護絶縁層113を成膜する(図5(E)参照)。保護絶縁層113は例えば、RFスパッタ法を用いて窒化ケイ素膜を形成する。RFスパッタ法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化ケイ素膜、窒化アルミニウム膜などを用いる。本実施の形態では、窒化ケイ素膜を用いて保護絶縁層113を形成する。

【0138】

本実施の形態では、保護絶縁層113として、ゲート電極層111まで形成された基板101を100℃から、400℃の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入し、シリコン半導体のターゲットを用いて窒化ケイ素膜を成膜する。この場合においても、処理室内の残留水分を除去しつつ保護絶縁層113を形成することが好ましい。

【0139】

以上の工程で本実施の形態に示すトランジスタが形成される。

【0140】

本実施の形態のトランジスタは、半導体層に、酸化物半導体を用いているため、高耐圧で、大電流の制御が可能である。そのため、大電流を扱うパワーデバイス等に用いるトランジスタに適している。

【0141】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0142】

(実施の形態4)

本実施の形態では、本発明の半導体装置の一例である電圧変換回路(DC−DCコンバータ)について示す。

【0143】

図6(A)に示すコンバータ回路301は、トランジスタ302、コイル303、ダイオード304、コンデンサ305、直流電源306を有する昇圧回路である。

【0144】

なお、本実施の形態において、トランジスタ302またはトランジスタ312として例えば、本発明の一態様の半導体素子を使用することができる。

【0145】

コイル303の一方の端子は、直流電源306の陽極に電気的に接続されている。コイル303の他方の端子はトランジスタ302のソース或いはドレインの一方と電気的に接続されている。トランジスタ302のソース或いはドレインの他方は直流電源306の陰極及び、コンデンサ305の一方の端子と電気的に接続されている。コンデンサ305の他方の端子は、ダイオード304の出力端子及び出力端子OUTに電気的に接続されている。なお、直流電源306の陰極、トランジスタ302のソースあるいはドレインの他方、及びコンデンサ305の一方の端子は接地されている。

【0146】

トランジスタ302はスイッチング素子として機能する。またトランジスタ302のゲートは、コンバータ回路301の制御回路に接続されている。コンバータ回路301の制御回路からの信号により、トランジスタ302はオン状態あるいはオフ状態となる。

【0147】

スイッチング素子であるトランジスタ302がオン状態のとき、コイル303に流れ込む電流により、コイル303には励磁エネルギーが蓄えられる。

【0148】

トランジスタ302がオフ状態になると、コイル303に蓄えられた励磁エネルギーが放出される。コイル303から放出される励磁エネルギーに起因する電圧V2が、電圧V1に上積みされる。これによりコンバータ回路301は昇圧回路として機能する。

【0149】

トランジスタ302がオン状態の時間が長く、コイル303に蓄えたエネルギーが大きいほど、大電力を取り出すことができる。

【0150】

図6(B)に示すコンバータ回路311は、トランジスタ312、コイル313、ダイオード314、コンデンサ315を有する降圧回路である。

【0151】

トランジスタ312のソースあるいはドレインの一方は、直流電源316の陽極に電気的に接続されている。トランジスタ312のソースあるいはドレインの他方は、ダイオード314の出力端子及びコイル313の一方の端子と電気的に接続されている。ダイオード314の入力端子は、直流電源316の陰極及びコンデンサ315の一方の端子に電気的に接続されている。ダイオードの出力端子は、トランジスタ312のソースあるいはドレインの他方及びコイル313の一方の端子と電気的に接続されている。コイル313の一方の端子は、トランジスタ312のソース或いはドレインの他方及びダイオード314の出力端子に電気的に接続されている。コイル313の他方の端子は、コンデンサ315の他方の端子及び出力端子OUTに電気的に接続されている。なお、直流電源316の陰極、ダイオード314の入力端子、及びコンデンサ315の一方の端子は接地されている。

【0152】

トランジスタ312はスイッチング素子として機能する。またトランジスタ312のゲートは、コンバータ回路311の制御回路に接続されている。コンバータ回路311の制御回路からの信号により、トランジスタ312はオン状態あるいはオフ状態となる。

【0153】

スイッチング素子であるトランジスタ312がオン状態のとき、入力から出力に流れる降圧回路の電流により、コイル313には励磁エネルギーが蓄えられる。

【0154】

トランジスタ312がオフ状態になると、コイル313は電流を保とうとして起電力を発生させ、ダイオード314をオン状態にする。ダイオード314を通じて電流が流れることによって、電圧V2が低下する。電圧V1より電圧V2が低下するため、コンバータ回路311は降圧回路として機能する。なお本実施の形態において、トランジスタ312として例えば電界効果トランジスタを用いることができる。

【0155】

また本実施の形態において、コイル303とコイル313として、基板上にコイル状に形成した配線を用いることができる。

【0156】

また本実施の形態において、ダイオード304とダイオード314として、例えばショットキーバリアダイオードを用いることができる。

【0157】

また、本実施の形態において、コンデンサ305とコンデンサ315として、例えば第1の電極と、第2の電極と、誘電体と、を有する構成のコンデンサを用いることができる。

【0158】

本発明の一態様に示した半導体素子は、半導体層に酸化物半導体を用いているため、高耐圧で、大電流の制御が可能であるという特性を有する。そのため、本実施の形態で示した電圧変換回路に用いることによって、大電流を駆動できる回路を作製できる。

【0159】

本発明の一態様に示した半導体素子は、貫通電極によって、トランジスタを並列接続させているため、トランジスタの実質的なW長を長くすることができ、パワーデバイスに適した高移動度の半導体素子を提供できる。そのため、本実施の形態で示した電圧変換回路に用いることによって、回路の駆動速度が上昇する。

【0160】

また、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【符号の説明】

【0161】

100 半導体チップ

100a 半導体チップ

100b 半導体チップ

101 基板

101a 基板

103 下地膜

103a 下地膜

105 酸化物半導体層

105a 酸化物半導体層

106 ソース電極層

106a ソース電極層

107 ドレイン電極層

107a ドレイン電極層

109 ゲート絶縁層

109a ゲート絶縁層

111 ゲート電極層

111a ゲート電極層

113 保護絶縁層

113a 保護絶縁層

115 保護層

116 ソース配線

116a ソース配線

117 ドレイン配線

117a ドレイン配線

120a 貫通電極

121a 貫通電極

122 貫通電極

122a 貫通電極

130a トランジスタ

130b トランジスタ

200 ビア

201 絶縁膜

203 導電性バリア膜

205 配線

207 導電体

301 コンバータ回路

302 トランジスタ

303 コイル

304 ダイオード

305 コンデンサ

306 直流電源

311 コンバータ回路

312 トランジスタ

313 コイル

314 ダイオード

315 コンデンサ

316 直流電源

【特許請求の範囲】

【請求項1】

半導体層に酸化物半導体を用いる第1のトランジスタと、前記第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第1の基板と、

半導体層に酸化物半導体を用いる第2のトランジスタと、前記第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第2の基板と、を積層して備え、

前記第1のトランジスタと前記第2のトランジスタは、それぞれの貫通電極を介して電気的に並列接続された半導体素子。

【請求項2】

前記酸化物半導体は、3eV以上のバンドギャップを有する、請求項1に記載の半導体素子。

【請求項3】

前記第1の基板及び前記第2の基板はシリコン基板である、請求項1乃至2のいずれか一項に記載の半導体素子。

【請求項4】

前記第1の基板及び前記第2の基板は絶縁性基板である、請求項1乃至3のいずれか一項に記載の半導体素子。

【請求項5】

請求項1乃至4のいずれか一項に記載の半導体素子を用いた半導体装置。

【請求項6】

基板の第1の領域に第1のトランジスタと、前記基板の第2の領域に第2のトランジスタとを作製し、

前記第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極を前記第1の領域に、前記第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極を前記第2の領域に作製し、

前記第1の領域を備える第1の半導体チップと、前記第2の領域を備える第2の半導体チップとを、前記基板を分断して形成する第1のステップと、

前記第1の半導体チップ及び前記第2の半導体チップを積層し、

前記第1のトランジスタと前記第2のトランジスタを、前記貫通電極を介して電気的に並列接続させる第2のステップを有する半導体素子の作製方法。

【請求項1】

半導体層に酸化物半導体を用いる第1のトランジスタと、前記第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第1の基板と、

半導体層に酸化物半導体を用いる第2のトランジスタと、前記第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極と、を有する第2の基板と、を積層して備え、

前記第1のトランジスタと前記第2のトランジスタは、それぞれの貫通電極を介して電気的に並列接続された半導体素子。

【請求項2】

前記酸化物半導体は、3eV以上のバンドギャップを有する、請求項1に記載の半導体素子。

【請求項3】

前記第1の基板及び前記第2の基板はシリコン基板である、請求項1乃至2のいずれか一項に記載の半導体素子。

【請求項4】

前記第1の基板及び前記第2の基板は絶縁性基板である、請求項1乃至3のいずれか一項に記載の半導体素子。

【請求項5】

請求項1乃至4のいずれか一項に記載の半導体素子を用いた半導体装置。

【請求項6】

基板の第1の領域に第1のトランジスタと、前記基板の第2の領域に第2のトランジスタとを作製し、

前記第1のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極を前記第1の領域に、前記第2のトランジスタのゲート電極層、ソース電極層及びドレイン電極層とそれぞれ電気的に接続する3つの貫通電極を前記第2の領域に作製し、

前記第1の領域を備える第1の半導体チップと、前記第2の領域を備える第2の半導体チップとを、前記基板を分断して形成する第1のステップと、

前記第1の半導体チップ及び前記第2の半導体チップを積層し、

前記第1のトランジスタと前記第2のトランジスタを、前記貫通電極を介して電気的に並列接続させる第2のステップを有する半導体素子の作製方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−60091(P2012−60091A)

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願番号】特願2010−204926(P2010−204926)

【出願日】平成22年9月13日(2010.9.13)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願日】平成22年9月13日(2010.9.13)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]