半導体素子およびその製造方法

【課題】二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子を提供する。

【解決手段】半導体素子10は、多結晶シリコン膜4と、絶縁膜5,9と、金属量子ドット8とを備える。多結晶シリコン膜4は、絶縁基板1上に配置され、アモルファスシリコン膜を熱プラズマジェットによってアニールして作製される。絶縁膜5は、SiO2からなり、多結晶シリコン膜4に接して多結晶シリコン膜4上に形成される。金属量子ドット8は、Ptからなり、Pt薄膜を熱プラズマジェットによってアニールして絶縁膜5上に形成される。絶縁膜9は、SiO2からなり、金属量子ドット8を覆うように絶縁膜5上に形成される。

【解決手段】半導体素子10は、多結晶シリコン膜4と、絶縁膜5,9と、金属量子ドット8とを備える。多結晶シリコン膜4は、絶縁基板1上に配置され、アモルファスシリコン膜を熱プラズマジェットによってアニールして作製される。絶縁膜5は、SiO2からなり、多結晶シリコン膜4に接して多結晶シリコン膜4上に形成される。金属量子ドット8は、Ptからなり、Pt薄膜を熱プラズマジェットによってアニールして絶縁膜5上に形成される。絶縁膜9は、SiO2からなり、金属量子ドット8を覆うように絶縁膜5上に形成される。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体素子およびその製造方法に関するものである。

【背景技術】

【0002】

従来、複合フローティングゲートを用いた半導体メモリが知られている(特許文献1)。この半導体メモリは、Si酸化膜によって被覆したSi系量子ドット、高誘電率絶縁膜によって被覆したシリサイド量子ドット、および高誘電率絶縁膜によって被覆したSi系量子ドットをSiO2膜を介して半導体基板上に、順次、積層した構造からなる。そして、電荷は、シリサイド量子ドット中に蓄積される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−270705号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかし、従来の半導体メモリにおいては、SiO2膜は、シリコンからなる半導体基板を1000℃で熱酸化して形成されるため、二酸化シリコンとシリコンとの界面特性が良好な半導体素子をガラス等の絶縁基板上に作製することが困難であった。

【0005】

そこで、この発明は、かかる問題を解決するためになされたものであり、その目的は、二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子を提供することである。

【0006】

また、この発明の別の目的は、二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子の製造方法を提供することである。

【課題を解決するための手段】

【0007】

この発明の実施の形態によれば、半導体素子は、絶縁基板と、多結晶シリコン膜と、第1および第2の二酸化シリコン膜と、金属量子ドットとを備える。多結晶シリコン膜は、絶縁基板上に形成される。第1の二酸化シリコン膜は、多結晶シリコン膜に接して形成され、キャリアがトンネル可能な膜厚を有する。金属量子ドットは、第1の二酸化シリコン膜に接して形成され、白金またはニッケルからなる。第2の二酸化シリコン膜は、金属量子ドットを覆うように形成される。そして、多結晶シリコン膜は、熱プラズマジェットをアモルファスシリコン膜に照射して製造された多結晶シリコン膜からなる。また、第1の二酸化シリコン膜は、リモートプラズマを用いて堆積された二酸化シリコンに熱プラズマジェットを照射することによって製造された二酸化シリコンからなる。更に、金属量子ドットは、白金またはニッケルからなる金属薄膜に熱プラズマジェットを照射することによって製造された金属量子ドットからなる。

【0008】

また、この発明の実施の形態によれば、半導体素子の製造方法は、絶縁基板上にアモルファスシリコン膜を形成する第1の工程と、アモルファスシリコン膜に接して第1の二酸化シリコン膜を形成する第2の工程と、第1の二酸化シリコン膜に接して白金またはニッケルからなる金属薄膜を形成する第3の工程と、アモルファスシリコン膜に熱プラズマジェットを照射する第4の工程と、第1の二酸化シリコン膜に熱プラズマジェットを照射する第5の工程と、金属薄膜に熱プラズマジェットを照射する第6の工程と、熱プラズマジェットの照射によって金属薄膜から形成された金属量子ドットを覆うように第2の二酸化シリコン膜を形成する第7の工程とを備える。

【発明の効果】

【0009】

この発明の実施の形態による半導体素子においては、多結晶シリコン膜は、第1の二酸化シリコン膜に接して形成され、多結晶シリコン膜は、アモルファスシリコン膜を熱プラズマジェットによってアニールすることによって製造され、第1の二酸化シリコン膜は、リモートプラズマを用いて堆積された二酸化シリコンに熱プラズマジェットを照射することによって製造される。また、金属量子ドットは、金属薄膜を熱プラズマジェットによってアニールすることによって製造される。その結果、第1の二酸化シリコン膜と多結晶シリコン膜との界面準位密度は、1010(個/cm2eV)台と低く、シリコンウエハを熱酸化して二酸化シリコン膜を作製したときの二酸化シリコン膜とシリコンとの界面準位密度とほぼ同じである。

【0010】

従って、二酸化シリコンとシリコンとの良好な界面特性を有する半導体素子を絶縁基板上に製造できる。

【0011】

また、この発明の実施の形態による半導体素子においては、多結晶シリコン膜中の電子を絶縁膜によって挟み込まれた金属量子ドットへ注入してメモリの書込を行なう。

【0012】

従って、量子ドットとしてSi系量子ドットを用いた場合よりも電子の保持時間を長くできる。

【図面の簡単な説明】

【0013】

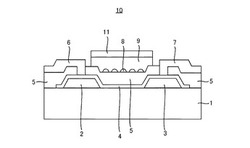

【図1】この発明の実施の形態による半導体素子の断面構造図である。

【図2】リモートプラズマ処理を行なうプラズマ装置の概略図である。

【図3】熱プラズマジェットによる処理を行なうプラズマ装置の構成を示す概略図である。

【図4】図3に示すプラズマ装置において結晶を製造する例を説明するための図である。

【図5】図1に示す半導体素子の製造方法を示す第1の工程図である。

【図6】図1に示す半導体素子の製造方法を示す第2の工程図である。

【図7】図1に示す半導体素子の製造方法を示す第3の工程図である。

【図8】図1に示す半導体素子の製造方法を示す第4の工程図である。

【図9】図1に示す半導体素子におけるメモリ書込動作とメモリ消去動作とを説明するための第1のエネルギーバンド図である。

【図10】図1に示す半導体素子におけるメモリ書込動作とメモリ消去動作とを説明するための第2のエネルギーバンド図である。

【図11】図1に示す半導体素子におけるメモリ書込動作とメモリ消去動作とを説明するための第3のエネルギーバンド図である。

【図12】図1に示す半導体素子におけるメモリ書込動作とメモリ消去動作とを説明するための第4のエネルギーバンド図である。

【図13】フーリエ変換赤外分光光度計(FT−IR)を用いたSiO2膜の赤外線分光のスペクトルを示す図である。

【図14】SiO2膜におけるSi−OHの相対積分強度、Si−O−Siの相対積分強度、およびピーク波数と、最大表面温度との関係を示す図である。

【図15】MOS(Metal Oxide Semiconductor)キャパシタの高周波C−V特性を示す図である。

【図16】固定電荷密度と最大表面温度との関係を示す図である。

【図17】この発明の実施の形態による他の半導体素子の断面構造図である。

【図18】図17に示す半導体素子の製造方法を示す第1の工程図である。

【図19】図17に示す半導体素子の製造方法を示す第2の工程図である。

【図20】図17に示す半導体素子の製造方法を示す第3の工程図である。

【図21】シート抵抗と最大表面温度との関係を示す図である。

【発明を実施するための形態】

【0014】

本発明の実施の形態について図面を参照しながら詳細に説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰返さない。

【0015】

図1は、この発明の実施の形態による半導体素子の断面構造図である。図1を参照して、この発明の実施の形態による半導体素子10は、絶縁基板1と、n+型多結晶シリコン層2,3と、多結晶シリコン膜4と、絶縁膜5,9と、ソース電極6と、ドレイン電極7と、金属量子ドット8と、ゲート電極11とを備える。

【0016】

絶縁基板1は、例えば、ガラスまたは有機フィルムからなる。n+型多結晶シリコン層2は、絶縁基板1に接して形成される。n+型多結晶シリコン層3は、絶縁基板1の面内方向においてn+型多結晶シリコン層2から離れた位置で絶縁基板1に接して形成される。

【0017】

n+型多結晶シリコン層2,3の各々は、例えば、20nmの膜厚を有し、例えば、約1×1020cm−3のリン(P)濃度を有する。

【0018】

多結晶シリコン膜4は、n+型多結晶シリコン層2,3を覆うように絶縁基板1上に形成される。多結晶シリコン膜4は、例えば、ノンドープの多結晶シリコンからなり、例えば、10〜20nmの膜厚を有する。

【0019】

絶縁膜5は、多結晶シリコン膜4を覆うように絶縁基板1上に形成される。そして、絶縁膜5は、例えば、二酸化シリコン(SiO2)膜からなり、例えば、5nmの膜厚を有する。この5nmの膜厚は、キャリア(電子または正孔)がトンネル可能な膜厚である。

【0020】

ソース電極6は、一方端がn+型多結晶シリコン層2上において絶縁膜5を貫通して多結晶シリコン膜4に接するように絶縁膜5上に形成される。そして、ソース電極6は、例えば、アルミニウム(Al)からなる。

【0021】

ドレイン電極7は、一方端がn+型多結晶シリコン層3上において絶縁膜5を貫通して多結晶シリコン膜4に接するように絶縁膜5上に形成される。そして、ドレイン電極7は、例えば、Alからなる。

【0022】

金属量子ドット8は、ソース電極6とドレイン電極7との間において、絶縁膜5に接して形成される。そして、金属量子ドット8は、例えば、白金(Pt)ドットからなる。また、金属量子ドット8は、例えば、9.0nmの高さ、10nmの幅を有する。更に、金属量子ドット8の密度は、例えば、1.6×1011cm−2である。

【0023】

絶縁膜9は、金属量子ドット8を覆うように絶縁膜5上に形成される。そして、絶縁膜9は、例えば、SiO2膜からなる。また、絶縁膜9は、例えば、20nmの膜厚を有する。

【0024】

ゲート電極11は、絶縁膜9に接して絶縁膜9上に形成される。そして、ゲート電極11は、例えば、不純物半導体または半透明金属からなる。不純物半導体は、B等の不純物がドーピングされた半導体である。

【0025】

半導体素子10においては、金属量子ドット8は、絶縁膜5,9によって挟まれており、絶縁膜5は、キャリアがトンネル可能な膜厚を有する。従って、半導体素子10においては、ゲート電極11に印加する電圧を制御することによって、チャネル層である多結晶シリコン膜4中の電子は、金属量子ドット8へ注入される。

【0026】

また、金属量子ドット8に光を照射することによって、金属量子ドット8に保持された電子は、多結晶シリコン膜4へ放出される。

【0027】

このように、半導体素子10は、キャリアの書込みおよび消去が可能なフローティングゲート型の薄膜トランジスタである。

【0028】

図2は、リモートプラズマ処理を行なうプラズマ装置の概略図である。図2を参照して、プラズマ装置600は、石英管610と、反応室620と、基板ホルダー630と、ヒーター640と、配管650と、バルブ660と、アンテナ670と、マッチング回路680と、高周波電源690とを備える。

【0029】

石英管610は、10cmφの直径を有し、その一方端が反応室620内に挿入されるように固定される。反応室620は、中空の円筒形状からなり、上面620Aに石英管610の一方端を挿入するための開口部621を有し、側面620Bに排気口622を有する。そして、反応室620は、開口部621から石英管610の一方端が挿入されることによって、内部空間が石英管610の内部空間と連通する。従って、ポンプ(図示せず)によって反応室620および石英管610の内部の気体を排気口622を介して排気できる。

【0030】

基板ホルダー630は、反応室620の下面620C上に配置される。ヒーター640は、シリコンカーバイド(SiC)からなり、基板ホルダー630内に配置される。

【0031】

配管650は、バルブ660を介して石英管610の他方端に連結される。バルブ660は、配管650に装着される。アンテナ670は、基板ホルダー630上に設置された基板800から23cmの位置で石英管610の周囲を取り巻くように配置される。そして、アンテナ670は、その一方端がマッチング回路680に接続され、他方端が接地される。

【0032】

マッチング回路680は、アンテナ670の一方端と高周波電源690との間に接続される。高周波電源690は、マッチング回路680と、接地ノードとの間に接続される。

【0033】

ヒーター640は、基板ホルダー630を介して基板800を所定の温度に加熱する。配管650は、水素(H2)ガス、アルゴン(Ar)ガス、窒素(N2)ガス、およびシラン(SiH4)ガスのいずれかをボンベ(図示せず)から石英管610内に導く。この場合、配管650は、

バルブ660は、H2ガス、Arガス、N2ガス、およびSiH4ガスを石英管610内へ供給し、またはH2ガス、Arガス、N2ガス、およびSiH4ガスの石英管610内への供給を遮断する。

【0034】

マッチング回路680は、高周波電源690から供給された高周波電力の高周波電源690側への反射を低くして高周波電力をアンテナ670へ供給する。高周波電源690は、60MHzの高周波電力をマッチング回路680を介してアンテナ670へ供給する。

【0035】

プラズマ装置600における処理動作について説明する。基板800が基板ホルダー630上に配置され、排気口622から反応室620および石英管610の真空引きが行なわれる。

【0036】

その後、バルブ660が開けられ、ボンベ(図示せず)から所定量のH2ガス等が配管650を介して石英管610内へ導入される。そして、石英管610内の圧力が所定の圧力に達すると、高周波電源690は、60MHzの高周波電力をマッチング回路680を介してアンテナ670に供給する。この場合、マッチング回路680は、高周波電源690から供給された高周波電力の高周波電源690側への反射が最も低くなるように調整される。

【0037】

そうすると、石英管610内でプラズマ730が発生し、主に原子状水素等がプラズマ730の発生領域から基板800の方向へ石英管610内を拡散し、基板800表面に到達する。そして、原子状水素等は、基板800表面を処理する。

【0038】

所定の処理時間が経過すると、高周波電源690がオフされ、バルブ660が閉じられて処理動作が終了する。

【0039】

なお、プラズマ装置600を用いてリモートプラズマ処理を行なう場合、基板800は、電気的にフローティングされた状態でリモートプラズマによって処理される。

【0040】

図3は、熱プラズマジェットによる処理を行なうプラズマ装置の構成を示す概略図である。図3を参照して、プラズマ装置100は、反応容器101と、陰極102と、陽極103と、絶縁部材104と、配管105と、試料ホルダー106と、ガスボンベ107と、直流電源108と、移動装置109とを備える。

【0041】

反応容器101は、中空の円柱形状からなる。陰極102は、3%のLaO2を含むタングステン(W)からなる。そして、陰極102は、略円柱形状を有し、一方端が尖っている。また、陰極102は、他方端が絶縁部材104および反応容器101を貫通し、反応容器101の外部に配置されるとともに、絶縁部材104に固定される。

【0042】

陽極103は、陰極102との間に空間SPを形成するように陰極102の周囲に配置され、絶縁部材104に固定される。そして、陽極103は、試料ホルダー106側に熱プラズマジェットが通過するための孔111を有する。

【0043】

絶縁部材104は、反応容器101の天井に固定される。配管105は、一方端が空間SPに接するように陽極103を貫通し、他方端がガスボンベ107に連結される。

【0044】

試料ホルダー106は、陰極102および陽極103に対向して配置される。ガスボンベ107は、配管105の他方端に連結され、Arガスを保持する。

【0045】

試料ホルダー106は、試料110を保持する。ガスボンベ107は、Arガスを配管105を介して空間SPに供給する。

【0046】

直流電源108は、直流電圧源1081と、電流計1082とを含む。そして、直流電源108は、所望の電流が流れるように、陰極102と陽極103との間に直流電圧を印加する。

【0047】

移動装置109は、試料ホルダー106を一定速度で方向DR1へ移動させる。

【0048】

図4は、図3に示すプラズマ装置100において結晶を製造する例を説明するための図である。図4を参照して、基板121上に多結晶シリコン膜を作製する場合、大気圧下で基板/アモルファスシリコン(a−Si)からなる試料120が試料ホルダー106上に配置される。そして、a−Siは、たとえば、プラズマCVD(Chemical Vapour Deposition)によって作製され、その膜厚は、50nmである。

【0049】

ガスボンベ107は、9.8リットル/分の流量でArガスを空間SPへ供給する。

【0050】

また、直流電源108は、直流電流が150A程度になるように、陰極102と陽極103との間に13〜16Vの直流電圧を印加する。

【0051】

そうすると、陰極102は、熱プラズマジェット140を出射し、その出射した熱プラズマジェット140を孔111を介して試料120に照射する。

【0052】

また、移動装置109は、1m/s〜2m/sの速度で矢印132の方向へ試料ホルダー106を移動させる。

【0053】

その結果、熱プラズマジェット140が照射された部分は、2〜3msecで1200℃まで昇温され、多結晶シリコン膜122になる。

【0054】

図5から図8は、それぞれ、図1に示す半導体素子10の製造方法を示す第1から第4の工程図である。

【0055】

図5を参照して、半導体素子10の製造が開始されると、ガラス等の絶縁基板1は、RCA洗浄等のウェットによる洗浄が行われ、容量結合型(CCP:Capacitively Coupled Plasma)プラズマ装置(図示せず)の一方の電極上にセットされる。この場合、平行に配置された2つの電極間の距離は、45mmである。

【0056】

そして、0.5sccmの100%SiH4ガスと、15sccmの1%フォスフィン(PH3)ガスと、34.5sccmのH2ガスとを配管を介して反応室内に流す。その後、排気装置(図示せず)によって反応室内の圧力を13.3Paに設定する。また、ヒーターによって絶縁基板1の温度を250℃に設定する。

【0057】

そうすると、高周波電源は、13.56MHzの周波数を有する50Wのパワーをマッチング回路を介して2つの電極間に印加する。

【0058】

これによって、リン(P)ドープのアモルファスシリコン膜201が絶縁基板1上に堆積される(工程(a)参照)。この場合、アモルファスシリコン膜201の膜厚は、20nmである。

【0059】

その後、アモルファスシリコン膜201上にレジストを塗布し、その塗布したレジスタをフォトリソグラフィによってパターンニングしてレジストパターン210をアモルファスシリコン膜201上に形成する(工程(b)参照)。

【0060】

そして、レジストパターン210をマスクとしてアモルファスシリコン膜201をエッチングし、n型アモルファスシリコン膜202,203を絶縁基板1上に形成する(工程(c)参照)。その後、レジストパターン210を除去する。

【0061】

引き続いて、n型アモルファスシリコン膜202,203/絶縁基板1を容量結合型プラズマ装置から取り出し、その取り出したn型アモルファスシリコン膜202,203/絶縁基板1の表面を希フッ酸で処理し、n型アモルファスシリコン膜202,203の表面を水素によって終端する。

【0062】

そして、表面が水素によって終端されたn型アモルファスシリコン膜202,203/絶縁基板1を誘導結合型(ICP:Inductively Coupled Plasma)プラズマ装置の基板ホルダー上にセットする。この場合、誘導結合型プラズマ装置における電極と基板との間の距離は、45mmである。

【0063】

そうすると、5sccmの100%SiH4ガスと、5sccmのH2ガスとを配管を介して反応室内に流す。そして、排気装置(図示せず)によって反応室内の圧力を6.65Paに設定する。また、ヒーターによって絶縁基板1の温度を250℃に設定する。

【0064】

そうすると、高周波電源は、13.56MHzの周波数を有する30Wのパワーをマッチング回路を介して電極に印加する。

【0065】

これによって、ノンドープのアモルファスシリコン膜204が絶縁基板1およびn型アモルファスシリコン膜202,203上に形成される(工程(d)参照)。この場合、アモルファスシリコン膜204の膜厚は、10nm〜20nmである。

【0066】

その後、アモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1を誘導結合型プラズマ装置から取り出し、その取り出したアモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1をプラズマ装置600の基板ホルダー630上にセットする。

【0067】

そして、0.6sccmのSiH4ガスと、10sccmのO2ガスと、40sccmのArガスとを配管650を介して石英管610および反応室620内に流す。そして、排気装置(図示せず)によって反応室620内の圧力を40Paに設定する。また、ヒーター640によって絶縁基板1の温度を350℃以下に設定する。

【0068】

そうすると、高周波電源690は、10Wのパワーをマッチング回路680を介してアンテナ670に印加する。

【0069】

これによって、SiO2膜205がアモルファスシリコン膜204上に形成される(工程(e)参照)。この場合、SiO2膜205の膜厚は、5nmである。

【0070】

図6を参照して、工程(e)の後、試料(=SiO2膜205/アモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1)をスパッタリング装置にセットし、試料の温度を室温に保持したまま、白金からなる金属薄膜206をSiO2膜205上にArスパッタリングによって形成する(工程(f)参照)。この場合、金属薄膜206の膜厚は、5nmである。

【0071】

その後、試料(=金属薄膜206/SiO2膜205/アモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1)をプラズマ装置100の試料ホルダー106上にセットする。

【0072】

そして、7リットル/minのArガスを配管105を介して空間SPへ供給し、直流電源108は、直流電流が152Aになるように、陰極102と陽極103との間に16Vの直流電圧を印加する。また、移動装置109は、1m/sまたは2m/sの速さで試料ホルダー106を絶縁基板1の面内方向へ移動させる。

【0073】

これによって、陰極102は、熱プラズマジェットを発生し、その発生した熱プラズマジェットを試料(=金属薄膜206/SiO2膜205/アモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1)に照射する(工程(g)参照)。この場合、試料と熱プラズマジェットとの距離は、4mmまたは5mmであり、試料の温度は、室温である。

【0074】

その結果、n+型多結晶シリコン層2,3は、それぞれ、n型アモルファスシリコン膜202,203から形成され、多結晶シリコン膜4は、アモルファスシリコン膜204から形成され、絶縁膜(=SiO2膜)5がSiO2膜205から形成され、金属量子ドット8が金属薄膜206から形成される(工程(h)参照)。

【0075】

そして、PMA(PostMetalization Annealing)処理を行なう。このPMA処理は、SiO2/Si界面を水素原子によって終端することによってSiO2/Si界面特性を向上させる技術である。そして、PMA処理は、試料(=金属量子ドット8/絶縁膜(=SiO2膜)5/多結晶シリコン膜4/n+型多結晶シリコン層2,3/絶縁基板1)をH2ガス中で670Kの温度で熱処理することによって行われた。

【0076】

その後、試料(=金属量子ドット8/SiO2膜5/多結晶シリコン膜4/n型アモルファスシリコン膜202,203/絶縁基板1)をプラズマ装置600の基板ホルダー630上にセットする。そして、SiO2膜205の形成条件と同じ形成条件を用いてSiO2膜207を金属量子ドット8を覆うように形成する(工程(i)参照)。この場合、SiO2膜207の膜厚は、20nmである。

【0077】

図7を参照して、工程(i)の後、レジストをSiO2膜207の全面に塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン220をSiO2膜207上に形成する(工程(j)参照)。

【0078】

そして、レジストパターン220をマスクとしてSiO2膜207および金属量子ドット8をエッチングする(工程(k)参照)。これによって、SiO2膜9が金属量子ドット8上に形成される。その後、レジストパターン220を除去する。

【0079】

引き続いて、レジストをSiO2膜5,9上に塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン230をレジストをSiO2膜5,9上に形成する(工程(l)参照)。

【0080】

そして、レジストパターン230をマスクとしてSiO2膜5をエッチングし、スルーホール208,209を絶縁膜(=SiO2膜)5に形成する(工程(m)参照)。その後、レジストパターン230を除去する。

【0081】

図8を参照して、工程(m)の後、SiO2膜5,9上にレジストを塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン240をSiO2膜5,9上に形成する(工程(n)参照)。

【0082】

そして、レジストパターン240をマスクとしてAlを蒸着し、その後、レジストパターン240を除去する。これによって、ソース電極6およびドレイン電極7が形成される(工程(o)参照)。

【0083】

引き続いて、SiO2膜5,9、ソース電極6およびドレイン電極7上にレジストを塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン250を形成する(工程(p)参照)。

【0084】

そして、レジストパターン250をマスクとして不純物半導体または半透明金属を形成し、その後、レジストパターン250を除去する。これによって、ゲート電極11がSiO2膜9上に形成され、半導体素子10が完成する(工程(q)参照)。

【0085】

なお、金属量子ドット8がNiからなる場合も、半導体素子10は、上述した工程(a)〜工程(q)に従って製造される。

【0086】

図9〜図12は、それぞれ、図1に示す半導体素子10におけるメモリ書込動作とメモリ消去動作とを説明するための第1から第4のエネルギーバンド図である。

【0087】

以下の説明では、半導体素子10におけるトランジスタキャパシタ部のエネルギーバンド図を参照してメモリ書き込み動作およびメモリ消去動作を説明する。

【0088】

まず、図9を参照して、半導体素子10のゲート電極11に正の電圧が印加されていないときのエネルギーバンド図について説明する。金属量子ドット8は、絶縁膜5と絶縁膜9とによって挟まれており、ナノサイズを有するため、離散的なエネルギー準位LV1が金属量子ドット8の伝導帯中に存在する。エネルギー準位LV1は、電子に対するエネルギー準位である。

【0089】

そして、金属量子ドット8は、多結晶シリコン膜4と異なる材料からなっているので、エネルギー準位LV1は、多結晶シリコン膜4の伝導帯よりも低い。

【0090】

このように、半導体素子10においては、金属量子ドット8の電子に対するエネルギー準位LV1は、多結晶シリコン膜4の伝導帯よりも低い。

【0091】

次に、図10を参照して、図9に示すエネルギーバンド図を有する半導体素子10におけるメモリの書き込み動作は、ゲート電極11に正の電圧を印加し、多結晶シリコン膜4から電子を金属量子ドット8に注入することにより行われる。

【0092】

ゲート電極11に正の電圧を印加すると、多結晶シリコン膜4の電子30が絶縁膜5をトンネルして金属量子ドット8へと注入される。金属量子ドット8へ電子が注入されると、金属量子ドット8の静電エネルギーが上昇するため、金属量子ドット8中の電子保持によって多結晶シリコン膜4のバンドは、下側に曲げられる。この状態は、論理上の「1」と判定される。

【0093】

正の電圧をゲート電極11に更に印加すると、さらに、多結晶シリコン膜4の電子が絶縁膜5をトンネルして金属量子ドット8へと注入される。これによって、金属量子ドット8へ2個目の電子40が注入される(図11参照)。この状態は、論理上の「2」と判定される。

【0094】

このように、ゲート電極11に正電圧を印加することによって、多結晶シリコン膜4の電子が1個ずつ絶縁膜5をトンネルして金属量子ドット8へと注入される。この状態をもって多値表現が可能となる。

【0095】

金属量子ドット8に注入された数個の電子は、光入力または電子放出操作のない間は金属量子ドット8に保持される。

【0096】

また、半導体素子10のゲート電極11に正電圧を更に印加すると、上記同様に、多結晶シリコン膜4から電子が金属量子ドット8内に注入される。

【0097】

金属量子ドット8は、ナノ(量子)構造であるため、離散化したエネルギー準位LV1が存在し、このエネルギー準位LV1は、多結晶シリコン膜4の伝導帯よりも低い。その結果、金属量子ドット8は、電子保持によるしきい値シフトの検知が可能であり、さらには、金属材料を用いているため、保持電子数の制限がなく、多数の電子を安定に保持できる。そのため、電子保持時間が長くなり、結果として情報の保持時間が長くなる。さらには、電荷保持ノードとして金属量子ドット8を用いることで、電子の注入に必要な時間、即ち、情報書き込み時間に大きく影響を及ぼす絶縁膜5を極めて薄膜化することが可能となるため、書き込み速度も同時に効率良く改善できる。

【0098】

以上説明した半導体素子10によれば、ゲート電極11を不純物半導体または半透明金属によって構成し、不純物半導体または半透明金属からの電気的パルスまたは光パルスにより金属量子ドット8への電子の注入を高速で効率的に行なうことが可能となる。

【0099】

また、半導体素子10においては、多結晶シリコン膜4と絶縁膜5との境界面がSiとSiO2との界面なので、閾値電圧の増加や電界効果移動度の低下を招くことなく、良好なトランジスタ特性を実現できる。

【0100】

次に、半導体素子10におけるメモリの消去動作について説明する。半導体素子10におけるメモリの消去は、ゲート電極11に光を照射したり、負の電圧を印加したりして、金属量子ドット8に注入された電子を多結晶シリコン膜4へ放出することによって行なわれる。

【0101】

以下、図12を参照して、半導体素子10におけるメモリの消去動作を説明する。なお、半導体素子10の構造におけるトランジスタキャパシタ部の構造で説明を行う。

【0102】

一旦、書き込んだ情報を消去する場合、ゲート電極11から微弱な光50を入射する。微弱な光50がゲート電極11に入射されると、内部光電効果によって、金属量子ドット8に保持された電子が励起される。その結果、半導体素子10では、金属量子ドット8に保持された電子60は、多結晶シリコン膜4中へ放出される。

【0103】

そして、ゲート電極11に負電圧をさらに印加することによって、金属量子ドット8中のより低いエネルギー準位LV1に保持された電子は、多結晶シリコン膜4へ放出される。

【0104】

このように、半導体素子10では、金属量子ドット8に保持された電子を放出する際、ゲート電極11に印加する負電圧を制御することによって、金属量子ドット8に保持された電子を段階的に多結晶シリコン膜4へ放出するようにしている。

【0105】

その結果、多値メモリの部分的な消去動作が可能となるので、メモリ消去動作の制御をより確実化させることができる。

【0106】

また、一度に全ての電子を放出する場合は、ゲート電極11に負電圧を印加した状態でゲート電極11に微弱な光50を照射する。これにより、内部光電効果によって金属量子ドット8内の保持電子を一挙に多結晶シリコン膜4へ放出でき、保持電子がなくなるため、データは消去されたことになる。

【0107】

なお、金属量子ドット8に対する多結晶シリコン膜4のバリアは、低いために赤外域の光でも容易に電子を放出できるので、現在、光データ通信に広く使われている赤外域の光で半導体素子10からのデータ出力が可能であるという利点を有する。

【0108】

なお、微弱な光50の光源として、メモリパッケージ内部に有機EL材料を塗布することで実現してもよい。

【0109】

以上、説明したように、半導体素子10においては、多値記憶動作を実現できる。

【0110】

また、Si量子ドットに比べ電子系に対する深いポテンシャル井戸が実現できる金属量子ドットに電子を注入することにより、注入された電子は、金属量子ドット内に安定して蓄積可能となり、電子を放出しにくくなる。その結果、絶縁膜5の薄膜化による書き込み・消去時間の低減が改善できるため、多値記憶動作を安定かつ高速に実現可能となる。

【0111】

半導体素子10の製造においては、n型アモルファスシリコン膜202,203、アモルファスシリコン膜204、SiO2膜205および金属薄膜206を、順次、絶縁基板1上に堆積した後に、プラズマ装置100によって熱プラズマジェットをn型アモルファスシリコン膜202,203、アモルファスシリコン膜204、SiO2膜205および金属薄膜206に照射してn+型多結晶シリコン層2,3、多結晶シリコン膜4、絶縁膜(=SiO2膜)5および金属量子ドット8を形成する(工程(a)〜工程(h)参照)。

【0112】

即ち、絶縁膜(=SiO2膜)5は、プラズマ装置600を用いたリモートプラズマによって堆積されたSiO2膜205に熱プラズマジェットを照射することによって作製される。また、多結晶シリコン膜4と絶縁膜(=SiO2膜)5との界面も、アモルファスシリコン膜204/SiO2膜205に熱プラズマジェットを照射することによって作製される。

【0113】

そこで、熱プラズマジェットによって作製された絶縁膜(=SiO2膜)5、および多結晶シリコン膜4と絶縁膜(=SiO2膜)5との界面特性について説明する。

【0114】

図13は、フーリエ変換赤外分光光度計(FT−IR)を用いたSiO2膜の赤外線分光のスペクトルを示す図である。図13において、縦軸は、吸収を表し、横軸は、波数を表す。

【0115】

図13を参照して、SiO2膜205においては、Si−O−Siの伸縮振動が1053cm−1に観測された。この1053cm−1の波数は、1000℃程度の高温でシリコンウェハを熱酸化して形成されたSiO2膜におけるSi−O−Siの伸縮振動の波数(=1078cm−1)よりも小さい。

【0116】

また、SiO2膜205においては、3400〜3600cm−1の範囲において、Si−OHの結合に基づく吸収が観測された。

【0117】

これらの結果は、SiO2膜205の堆積中に、Si−OHの結合が導入され、Si−O−Siネットワークにおいて酸素欠陥を生じることを示す。

【0118】

また、PMA処理を行なうことによって、Si−OH結合およびSi−O−Si結合の強度は、殆ど、変化せず、Si−O−Siのピーク波数も、殆ど、変化しない。従って、Si−O−Siネットワークの化学結合は、670KでのPMAによっては改善されない。

【0119】

一方、プラズマ装置100を用いた熱プラズマジェットの照射によるアニールを行なうと、SiO2膜205の温度は、2.8msの間、815℃に昇温され、3400〜3600cm−1の範囲におけるSi−OHの伸縮振動による吸収強度が大きく減少する。また、Si−O−Siの非対称伸縮振動に関連した信号強度は、1053cm−1から1066cm−1へ著しく増加し、吸収バンドの半値幅は、90cm−1から85cm−1へ減少する。

【0120】

これらの結果は、膜中のOH結合がH2O分子として脱着し、Si−O−Siネットワークを形成することを示す。即ち、熱プラズマジェットによるアニールは、Si−O−Siの化学結合成分を増加し、ネットワークを緩和する。

【0121】

図14は、SiO2膜におけるSi−OHの相対積分強度、Si−O−Siの相対積分強度、およびピーク波数と、最大表面温度との関係を示す図である。

【0122】

図14において、縦軸は、SiO2膜におけるSi−OHの相対積分強度、Si−O−Siの相対積分強度、およびピーク波数を表し、横軸は、最大表面温度を表す。なお、この最大表面温度は、プラズマ装置100を用いて熱プラズマジェットによってSiO2膜をアニールするときのSiO2膜の表面温度の最大値であり、試料ホルダー106上の試料全体の温度ではない。

【0123】

図14を参照して、最大表面温度が889(K)から1088(K)まで上昇すると、Si−OH結合の量は、単調に24%まで減少し、Si−O−Si結合の量は、1.15倍まで増加する。また、ピーク波数は、最大表面温度の上昇に伴って線形に大きくなる。

【0124】

そして、1088Kにおける熱プラズマジェットによるアニールは、973(K)における熱酸化膜と実質的に同等である。

【0125】

従って、基板表面の局所的な加熱は、厳しい熱的ダメージを基板に与えることなしに膜の品質を改善する有効な方法である。

【0126】

図15は、MOS(Metal Oxide Semiconductor)キャパシタの高周波C−V特性を示す図である。

【0127】

図15において、縦軸は、規格化された容量を表し、横軸は、ゲート電圧を表す。

【0128】

図15を参照して、プラズマ装置600を用いて堆積された直後のSiO2膜(As−deposited)を用いたMOSキャパシタのC−V特性は、注入電荷のためにヒステリシスを示すとともに、正の固定電荷のために、負のフラットバンド電圧シフトが観測された。

【0129】

一方、PMA処理および熱プラズマジェットによるアニールを行なったSiO2膜を用いてMOSキャパシタのC−V特性においては、ヒステリシスの幅および負のフラットバンド電圧シフトが著しく減少した。

【0130】

これらの結果は、トラップサイト数および固定電荷量の減少を表すものである。

【0131】

図16は、固定電荷密度と最大表面温度との関係を示す図である。図16において、縦軸は、固定電荷密度を表し、横軸は、最大表面温度を表す。なお、固定電荷密度は、全ての固定電荷がSiO2/Si界面に存在すると仮定して計算された。

【0132】

図16を参照して、プラズマ装置600を用いて堆積された直後のSiO2膜(As−deposited)を用いたMOSキャパシタの固定電荷密度は、1×1012(cm−2)よりも高い。

【0133】

一方、熱プラズマジェットによるアニールを行なったSiO2膜を用いたMOSキャパシタの固定電荷密度は、最大表面温度が1200Kまで上昇するに伴って、1.2×1011(cm−2)まで減少した。

【0134】

この1.2×1011(cm−2)の値は、PMA処理を行なったSiO2膜を用いたMOSキャパシタの固定電荷密度よりも低い値である。

【0135】

熱プラズマジェットによるアニールを行なったSiO2膜を用いたMOSキャパシタのC−V特性は、PMA処理を行なったSiO2膜を用いたMOSキャパシタのC−V特性よりも向上しない。

【0136】

そして、図15に示すように、熱プラズマジェットによるアニールを行なった後に、PMA処理を行なったSiO2膜を用いたMOSキャパシタ(TPJ+PMA)のC−V特性は、殆ど、理想的なC−V特性に一致する。

【0137】

これらの結果は、SiO2膜中の固定電荷密度および界面トラップ密度がPMA処理によって更に減少することを意味する。これを確認するために、界面トラップ密度を高周波C−V特性およびquasi-static C−V特性から定量的に評価した。その結果、熱プラズマジェットによるアニールを行なうことによって、界面トラップ密度は、2.0×1012(cm−2eV−1)から5.0×1011(cm−2eV−1)へ減少した。

【0138】

そして、熱プラズマジェットによるアニールを行なった後に、PMA処理を行なうことによって、界面トラップ密度は、3.0×1010(cm−2eV−1)まで減少した。この3.0×1010(cm−2eV−1)は、約1000℃において熱酸化によって作製されたSiO2の界面トラップ密度と同等である。

【0139】

このように、熱プラズマジェットによるアニールとPMA処理とを連続的に行なうことによって、熱酸化によって作製されたSiO2の界面トラップ密度と同等の界面トラップ密度を有するSiO2/Si界面が得られる。

【0140】

従って、半導体素子10における多結晶シリコン膜4と絶縁膜5(=SiO2膜)との界面は、良好な界面特性を示す。

【0141】

その結果、この発明の実施の形態によれば、ガラス等の絶縁基板1上に作製された半導体素子10において、二酸化シリコンとシリコンとの界面特性を向上できる。

【0142】

金属量子ドット8は、金属薄膜206を熱プラズマジェットによってアニールすることによって製造されるが、金属量子ドット8の密度および高さは、熱プラズマジェットが照射されたときの金属薄膜206の表面温度によって変化する。

【0143】

即ち、金属量子ドット8の密度は、金属薄膜206の表面温度が500℃から700℃へ高くなるに従って約2.0×1011(cm−2)から約1.4×1011(cm−2)へ低下し、金属量子ドット8の高さは、金属薄膜206の表面温度が500℃から700℃へ高くなるに従って約6.0nmから約13.7nmまで大きくなる。

【0144】

従って、金属薄膜206の表面温度が500℃であるとき、金属量子ドット8は、最も高い密度および最も低い高さを有し、金属薄膜206の表面温度が700℃であるとき、金属量子ドット8は、最も低い密度および最も高い高さを有する。

【0145】

そして、金属薄膜206の表面温度は、熱プラズマジェットの走査速度および熱プラズマジェットと試料との距離によって変化する。熱プラズマジェットと試料との距離を一定に保持して、熱プラズマジェットの走査速度を2m/sに設定すると、金属薄膜206の表面温度は、500℃になり、熱プラズマジェットの走査速度を1m/sに設定すると、金属薄膜206の表面温度は、650℃になる。

【0146】

従って、熱プラズマジェットと試料との距離を一定に保持した場合、金属薄膜206の表面温度は、熱プラズマジェットの走査速度が相対的に速くなれば、相対的に低くなり、熱プラズマジェットの走査速度が相対的に遅くなれば、相対的に高くなる。

【0147】

また、熱プラズマジェットの走査速度を一定に保持して、熱プラズマジェットと試料との距離を4mmに設定すると、金属薄膜206の表面温度は、650℃になり、熱プラズマジェットと試料との距離を5mmに設定すると、金属薄膜206の表面温度は、700℃になる。

【0148】

従って、熱プラズマジェットの走査速度を一定に保持した場合、金属薄膜206の表面温度は、熱プラズマジェットと試料との距離が相対的に短くなれば、相対的に高くなり、熱プラズマジェットの走査速度が相対的に長くなれば、相対的に低くなる。

【0149】

その結果、熱プラズマジェットの走査速度、および熱プラズマジェットと試料との距離を制御することによって、金属量子ドット8の密度および高さを所望の密度および所望の高さに設定できる。

【0150】

図17は、この発明の実施の形態による他の半導体素子の断面構造図である。この発明の実施の形態による半導体素子は、図17に示す半導体素子10Aであってもよい。

【0151】

図17を参照して、半導体素子10Aは、絶縁基板1と、多結晶シリコン膜21と、ソース電極22と、ドレイン電極23と、絶縁膜24,26と、金属量子ドット25と、ゲート電極27とを備える。

【0152】

多結晶シリコン膜21は、ノンドープの多結晶シリコンからなり、多結晶シリコン膜4と同じ膜厚を有する。そして、多結晶シリコン膜21は、絶縁基板1の表面に形成される。

【0153】

ソース電極22は、n+型多結晶シリコンからなり、多結晶シリコン膜21中に形成される。そして、ソース電極22は、半導体素子10のn+型多結晶シリコン層2,3と略同じ膜厚を有する。また、ソース電極22は、約1×1020cm−3のP濃度を有する。

【0154】

ドレイン電極23は、絶縁基板1の面内方向において、ソース電極22から離れた位置において多結晶シリコン膜21中に配置される。そして、ドレイン電極23は、半導体素子10のn+型多結晶シリコン層2,3と略同じ膜厚を有する。また、ドレイン電極23は、約1×1020cm−3のP濃度を有するn+型多結晶シリコンからなる。

【0155】

絶縁膜24は、SiO2膜からなり、ソース電極22とドレイン電極23との間の多結晶シリコン膜21上に多結晶シリコン膜21に接して形成される。そして、絶縁膜24は、キャリアがトンネル可能な5nmの膜厚を有する。

【0156】

金属量子ドット25は、PtまたはNiからなり、絶縁膜24に接して絶縁膜24上に形成される。そして、金属量子ドット25は、半導体素子10の金属量子ドット8と同じサイズを有する。

【0157】

絶縁膜26は、SiO2膜からなり、金属量子ドット25を覆うように絶縁膜24上に形成される。そして、絶縁膜26は、半導体素子10の絶縁膜9と同じ膜厚を有する。

【0158】

ゲート電極27は、不純物半導体または半透明金属からなる。そして、ゲート電極27は、絶縁膜26上に形成される。

【0159】

図18から図20は、それぞれ、図17に示す半導体素子10Aの製造方法を示す第1から第3の工程図である。

【0160】

図18を参照して、半導体素子10Aの製造が開始されると、ガラス等の絶縁基板1は、RCA洗浄等のウェットによる洗浄が行われ、誘導結合型プラズマ装置の基板ホルダー上にセットされる。

【0161】

そして、上述したアモルファスシリコン膜204の形成条件と同じ形成条件を用いてアモルファスシリコン膜301を絶縁基板1上に形成する(工程(a)参照)。この場合、アモルファスシリコン膜301の膜厚は、アモルファスシリコン膜204の膜厚と同じである。

【0162】

その後、アモルファスシリコン膜301/絶縁基板1を誘導結合型プラズマ装置から取り出し、その取り出したアモルファスシリコン膜301/絶縁基板1をプラズマ装置600の基板ホルダー630上にセットする。

【0163】

そして、SiO2膜205の形成条件と同じ形成条件を用いてSiO2膜302をアモルファスシリコン膜301上に形成する(工程(b)参照)。この場合、SiO2膜302の膜厚は、SiO2膜205の膜厚と同じである。

【0164】

引き続いて、試料(=SiO2膜302/アモルファスシリコン膜301/絶縁基板1)をスパッタリング装置にセットし、試料の温度を室温に保持したまま、白金からなる金属薄膜303をSiO2膜302上にArスパッタリングによって形成する(工程(c)参照)。この場合、金属薄膜303の膜厚は、5nmである。

【0165】

その後、試料(=金属薄膜303/SiO2膜302/アモルファスシリコン膜301/絶縁基板1)をプラズマ装置100の試料ホルダー106上にセットする。

【0166】

そして、7リットル/minのArガスを配管105を介して空間SPへ供給し、直流電源108は、直流電流が152Aになるように、陰極102と陽極103との間に16Vの直流電圧を印加する。また、移動装置109は、1m/sまたは2m/sの速さで試料ホルダー106を絶縁基板1の面内方向へ移動させる。

【0167】

これによって、陰極102は、熱プラズマジェットを発生し、その発生した熱プラズマジェットを試料(=金属薄膜303/SiO2膜302/アモルファスシリコン膜301/絶縁基板1)に照射する(工程(d)参照)。この場合、試料と熱プラズマジェットとの距離は、4mmまたは5mmであり、試料の温度は、室温である。

【0168】

これによって、多結晶シリコン膜304は、アモルファスシリコン膜301から形成され、SiO2膜305は、SiO2膜302から形成され、金属量子ドット25が金属薄膜303から形成される(工程(e)参照)。

【0169】

そして、試料(=金属量子ドット25/SiO2膜305/多結晶シリコン膜304/絶縁基板1)をH2ガス中で670Kの温度で熱処理することによってPMA処理を行なう。

【0170】

図19を参照して、工程(e)の後、プラズマ装置600を用いてSiO2膜302の形成条件と同じ形成条件を用いてSiO2膜306を金属量子ドット25を覆うようにSiO2膜305上に形成する(工程(f)参照)。この場合、SiO2膜306の膜厚は、半導体素子10の絶縁膜9の膜厚と同じである。

【0171】

その後、レジストをSiO2膜306上に塗布し、その塗布したレジストをフォトリソグラフィによりパターンニングしてレジストパターン310を形成する(工程(g)参照)。

【0172】

そして、レジストパターン310をマスクとしてSiO2膜306、金属量子ドット25およびSiO2膜305をエッチングする。これによって、多結晶シリコン膜304上に絶縁膜24、金属量子ドット25および絶縁膜26が形成される(工程(h)参照)。

【0173】

引き続いて、レジストパターン310をマスクとしてPを多結晶シリコン膜304にイオン注入する(工程(i)参照)。そして、レジストパターン310を除去する。この場合、イオン注入の加速電圧は、5keVであり、Pのドーズ量は、5×1014(イオン/cm2)である。

【0174】

図20を参照して、工程(i)の後、試料(=絶縁膜26/金属量子ドット25/絶縁膜24/Pドープ領域307,308/多結晶シリコン膜21/絶縁基板1)を570(K)で熱処理する。そして、試料(=絶縁膜26/金属量子ドット25/絶縁膜24/Pドープ領域307,308/多結晶シリコン膜21/絶縁基板1)をプラズマ装置100の試料ホルダー106上にセットする。

【0175】

そして、7リットル/minのArガスを配管105を介して空間SPへ供給し、直流電源108は、直流電流が150Aになるように、陰極102と陽極103との間に14.0〜18.5Vの直流電圧を印加する。また、移動装置109は、400mm/s〜1400mm/sの速さで試料ホルダー106を絶縁基板1の面内方向へ移動させる。

【0176】

これによって、陰極102は、熱プラズマジェットを発生し、その発生した熱プラズマジェットをPドープ領域307,308に照射する(工程(j)参照)。この場合、試料と熱プラズマジェットとの距離は、1.5mmであり、試料の温度は、室温である。

【0177】

その結果、イオン注入されたP原子が電気的に活性化され、ソース電極22およびドレイン電極23が多結晶シリコン層21中に形成される。

【0178】

そして、レジストを塗布し、その塗布したレジストをフォトリソグラフィによりパターングしてレジストパターン320を形成する(工程(k)参照)。

【0179】

そうすうと、レジストパターン320をマスクとして不純物半導体または半透明金属からなるゲート電極27を絶縁膜26上に形成する。これによって、半導体素子10Aが完成する(工程(l)参照)。

【0180】

なお、半導体素子10Aの製造方法においては、Pをプラズマ処理によって多結晶シリコン膜304中へ注入してもよい。

【0181】

また、金属量子ドット25がNiからなる場合も、半導体素子10Aは、図18から図20に示す工程(a)〜工程(l)に従って製造される。

【0182】

図21は、シート抵抗と最大表面温度との関係を示す図である。図21において、縦軸は、シート抵抗を表し、横軸は、最大表面温度を表す。

【0183】

なお、図21において、Preheating Temperatureは、プラズマ装置100を用いたプラズマジェットによるアニールの前に行なわれる熱処理温度である。

【0184】

図21を参照して、Bをイオン注入した試料、および砒素(As)をイオン注入した試料において、シート抵抗は、最大表面温度の上昇に伴って大きく低下する。従って、熱プラズマジェットによるアニールを行なうことによって、イオン注入されたBおよびAsは、電気的に活性化されることが解った。

【0185】

このように、熱プラズマジェットによるアニールによって、イオン注入された原子を電気的に活性化できる。

【0186】

なお、図21においては、図示されていないが、Pをイオン注入した場合も、熱プラズマジェットによるアニールによって、イオン注入されたPを電気的に活性化できることを確認している。

【0187】

半導体素子10Aにおける金属量子ドット25へのメモリの書込動作および消去動作は、半導体素子10における金属量子ドット8へのメモリの書込動作および消去動作と同じである。

【0188】

半導体素子10Aのその他の部分については、半導体素子10と同じである。

【0189】

なお、上述した半導体素子10の製造方法においては、n型アモルファスシリコン膜202,203、アモルファスシリコン膜204、SiO2膜205および金属薄膜206を絶縁基板1上に、順次、堆積した後に、熱プラズマジェットによるアニールを行なうと説明したが、この発明の実施の形態においては、これに限らず、次のような方法によって、n型アモルファスシリコン膜202,203、アモルファスシリコン膜204、SiO2膜205および金属薄膜206に対して熱プラズマジェットによるアニールを行なっても良い。

(I)n型アモルファスシリコン膜202,203を堆積後、n型アモルファスシリコン膜202,203を熱プラズマジェットによってアニールし、その後、アモルファスシリコン膜204をn+型多結晶シリコン膜2,3上に堆積し、アモルファスシリコン膜204を熱プラズマジェットによってアニールし、その後、多結晶シリコン膜4上にSiO2膜205を堆積し、SiO2膜205を熱プラズマジェットによってアニールし、その後、絶縁膜(=SiO2膜)5上に金属薄膜206を堆積し、金属薄膜206を熱プラズマジェットによってアニールする。

(II)n型アモルファスシリコン膜202,203を堆積後、n型アモルファスシリコン膜202,203を熱プラズマジェットによってアニールし、その後、アモルファスシリコン膜204およびSiO2膜205をn+型多結晶シリコン膜2,3上に堆積し、アモルファスシリコン膜204およびSiO2膜205を熱プラズマジェットによってアニールし、その後、絶縁膜(=SiO2膜)5上に金属薄膜206を堆積し、金属薄膜206を熱プラズマジェットによってアニールする。

(III)n型アモルファスシリコン膜202,203を堆積後、n型アモルファスシリコン膜202,203を熱プラズマジェットによってアニールし、その後、アモルファスシリコン膜204、SiO2膜205および金属薄膜206をn+型多結晶シリコン膜2,3上に堆積し、アモルファスシリコン膜204/SiO2膜205/金属薄膜206を熱プラズマジェットによってアニールする。

(IV)n型アモルファスシリコン膜202,203を堆積後、n型アモルファスシリコン膜202,203を熱プラズマジェットによってアニールし、その後、アモルファスシリコン膜204をn+型多結晶シリコン膜2,3上に堆積し、アモルファスシリコン膜204を熱プラズマジェットによってアニールし、その後、多結晶シリコン膜4上にSiO2膜205および金属薄膜206を堆積し、SiO2膜205/金属薄膜206を熱プラズマジェットによってアニールする。

【0190】

また、上述した半導体素子10Aの製造方法においては、アモルファスシリコン膜301、SiO2膜302および金属薄膜303を絶縁基板1上に、順次、堆積した後に、熱プラズマジェットによるアニールを行なうと説明したが、この発明の実施の形態においては、これに限らず、次のような方法によって、アモルファスシリコン膜301、SiO2膜302および金属薄膜303に対する熱プラズマジェットによるアニールを行なっても良い。

(V)アモルファスシリコン膜301を絶縁基板1上に堆積し、アモルファスシリコン膜301を熱プラズマジェットによってアニールし、その後、多結晶シリコン膜304上にSiO2膜302を堆積し、SiO2膜302を熱プラズマジェットによってアニールし、その後、SiO2膜305上に金属薄膜303を堆積し、金属薄膜303を熱プラズマジェットによってアニールする。

(VI)アモルファスシリコン膜301およびSiO2膜302を絶縁基板1上に堆積し、アモルファスシリコン膜301およびSiO2膜302を熱プラズマジェットによってアニールし、その後、SiO2膜305上に金属薄膜303を堆積し、金属薄膜303を熱プラズマジェットによってアニールする。

(VII)アモルファスシリコン膜301を絶縁基板1上に堆積し、その後、アモルファスシリコン膜301を熱プラズマジェットによってアニールし、その後、多結晶シリコン膜304上にSiO2膜302および金属薄膜303を堆積し、SiO2膜302/金属薄膜303を熱プラズマジェットによってアニールする。

【0191】

そして、上述した方法(I)〜(VII)のうちのいずれの方法を用いても、多結晶シリコン膜4と絶縁膜(SiO2膜)5との界面における界面トラップ密度、および多結晶シリコン膜21と絶縁膜(SiO2膜)24との界面における界面トラップ密度は、3.0×1010(cm−2eV−1)になる。従って、SiO2とSiとの良い界面特性を持った半導体素子10,10Aを絶縁基板1上に作製できる。

【0192】

このように、この発明の実施の形態による半導体素子の製造方法は、アモルファスシリコン膜の堆積、アモルファスシリコン膜の熱プラズマジェットによるアニール、SiO2膜の堆積、SiO2膜の熱プラズマジェットによるアニール、金属薄膜の堆積、および金属薄膜の熱プラズマジェットによるアニールを備えるものであればよい。

【0193】

この発明の実施の形態による半導体素子10,10Aの製造方法は、プラズマを用いたアモルファスシリコン膜およびSiO2膜の堆積、スパッタリングによる金属薄膜の堆積、室温における熱プラズマジェットによるアモルファスシリコン膜、SiO2膜および金属薄膜のアニールを用いて半導体素子10,10Aを製造する。

【0194】

従って、500℃以下の低温において半導体素子10,10Aを製造できる。つまり、SiO2とSiとの界面準位密度を熱酸化膜(=SiO2膜)とシリコンとの界面準位密度(=3.0×1010(cm−2eV−1))まで低減した半導体素子10,10Aを絶縁基板1上に製造できる。

【0195】

なお、上記においては、ソース電極6,22およびドレイン電極7,23は、n型多結晶シリコンからなると説明したが、この発明の実施の形態においては、これに限らず、ソース電極6,22およびドレイン電極7,23は、p型多結晶シリコンからなっていてもよい。この場合、図5の工程(a)において、容量結合型プラズマ装置を用いてボロン(B)をドープしたp型アモルファスシリコン膜が絶縁基板1上に堆積される。また、図19の工程(i)において、ボロン(B)が多結晶シリコン膜304へイオン注入される。

【0196】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施の形態の説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【産業上の利用可能性】

【0197】

この発明は、半導体素子およびその製造方法に適用される。

【符号の説明】

【0198】

1 絶縁基板、2,3 n+型多結晶シリコン層、4,21 多結晶シリコン膜、5,9,24,26 絶縁膜、6,22 ソース電極、7,23 ドレイン電極、8,25 金属量子ドット、10,10A 半導体素子、11,27 ゲート電極、100,600 プラズマ装置、101 反応容器、102 陰極、103 陽極、104 絶縁部材、105 配管、106 試料ホルダー、107 ガスボンベ、108 直流電源、109 移動装置、610 石英管、620 反応室、630 基板ホルダー、640 ヒーター、650 配管、660 バルブ、670 アンテナ、680 マッチング回路、690 高周波電源。

【技術分野】

【0001】

この発明は、半導体素子およびその製造方法に関するものである。

【背景技術】

【0002】

従来、複合フローティングゲートを用いた半導体メモリが知られている(特許文献1)。この半導体メモリは、Si酸化膜によって被覆したSi系量子ドット、高誘電率絶縁膜によって被覆したシリサイド量子ドット、および高誘電率絶縁膜によって被覆したSi系量子ドットをSiO2膜を介して半導体基板上に、順次、積層した構造からなる。そして、電荷は、シリサイド量子ドット中に蓄積される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−270705号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかし、従来の半導体メモリにおいては、SiO2膜は、シリコンからなる半導体基板を1000℃で熱酸化して形成されるため、二酸化シリコンとシリコンとの界面特性が良好な半導体素子をガラス等の絶縁基板上に作製することが困難であった。

【0005】

そこで、この発明は、かかる問題を解決するためになされたものであり、その目的は、二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子を提供することである。

【0006】

また、この発明の別の目的は、二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子の製造方法を提供することである。

【課題を解決するための手段】

【0007】

この発明の実施の形態によれば、半導体素子は、絶縁基板と、多結晶シリコン膜と、第1および第2の二酸化シリコン膜と、金属量子ドットとを備える。多結晶シリコン膜は、絶縁基板上に形成される。第1の二酸化シリコン膜は、多結晶シリコン膜に接して形成され、キャリアがトンネル可能な膜厚を有する。金属量子ドットは、第1の二酸化シリコン膜に接して形成され、白金またはニッケルからなる。第2の二酸化シリコン膜は、金属量子ドットを覆うように形成される。そして、多結晶シリコン膜は、熱プラズマジェットをアモルファスシリコン膜に照射して製造された多結晶シリコン膜からなる。また、第1の二酸化シリコン膜は、リモートプラズマを用いて堆積された二酸化シリコンに熱プラズマジェットを照射することによって製造された二酸化シリコンからなる。更に、金属量子ドットは、白金またはニッケルからなる金属薄膜に熱プラズマジェットを照射することによって製造された金属量子ドットからなる。

【0008】

また、この発明の実施の形態によれば、半導体素子の製造方法は、絶縁基板上にアモルファスシリコン膜を形成する第1の工程と、アモルファスシリコン膜に接して第1の二酸化シリコン膜を形成する第2の工程と、第1の二酸化シリコン膜に接して白金またはニッケルからなる金属薄膜を形成する第3の工程と、アモルファスシリコン膜に熱プラズマジェットを照射する第4の工程と、第1の二酸化シリコン膜に熱プラズマジェットを照射する第5の工程と、金属薄膜に熱プラズマジェットを照射する第6の工程と、熱プラズマジェットの照射によって金属薄膜から形成された金属量子ドットを覆うように第2の二酸化シリコン膜を形成する第7の工程とを備える。

【発明の効果】

【0009】

この発明の実施の形態による半導体素子においては、多結晶シリコン膜は、第1の二酸化シリコン膜に接して形成され、多結晶シリコン膜は、アモルファスシリコン膜を熱プラズマジェットによってアニールすることによって製造され、第1の二酸化シリコン膜は、リモートプラズマを用いて堆積された二酸化シリコンに熱プラズマジェットを照射することによって製造される。また、金属量子ドットは、金属薄膜を熱プラズマジェットによってアニールすることによって製造される。その結果、第1の二酸化シリコン膜と多結晶シリコン膜との界面準位密度は、1010(個/cm2eV)台と低く、シリコンウエハを熱酸化して二酸化シリコン膜を作製したときの二酸化シリコン膜とシリコンとの界面準位密度とほぼ同じである。

【0010】

従って、二酸化シリコンとシリコンとの良好な界面特性を有する半導体素子を絶縁基板上に製造できる。

【0011】

また、この発明の実施の形態による半導体素子においては、多結晶シリコン膜中の電子を絶縁膜によって挟み込まれた金属量子ドットへ注入してメモリの書込を行なう。

【0012】

従って、量子ドットとしてSi系量子ドットを用いた場合よりも電子の保持時間を長くできる。

【図面の簡単な説明】

【0013】

【図1】この発明の実施の形態による半導体素子の断面構造図である。

【図2】リモートプラズマ処理を行なうプラズマ装置の概略図である。

【図3】熱プラズマジェットによる処理を行なうプラズマ装置の構成を示す概略図である。

【図4】図3に示すプラズマ装置において結晶を製造する例を説明するための図である。

【図5】図1に示す半導体素子の製造方法を示す第1の工程図である。

【図6】図1に示す半導体素子の製造方法を示す第2の工程図である。

【図7】図1に示す半導体素子の製造方法を示す第3の工程図である。

【図8】図1に示す半導体素子の製造方法を示す第4の工程図である。

【図9】図1に示す半導体素子におけるメモリ書込動作とメモリ消去動作とを説明するための第1のエネルギーバンド図である。

【図10】図1に示す半導体素子におけるメモリ書込動作とメモリ消去動作とを説明するための第2のエネルギーバンド図である。

【図11】図1に示す半導体素子におけるメモリ書込動作とメモリ消去動作とを説明するための第3のエネルギーバンド図である。

【図12】図1に示す半導体素子におけるメモリ書込動作とメモリ消去動作とを説明するための第4のエネルギーバンド図である。

【図13】フーリエ変換赤外分光光度計(FT−IR)を用いたSiO2膜の赤外線分光のスペクトルを示す図である。

【図14】SiO2膜におけるSi−OHの相対積分強度、Si−O−Siの相対積分強度、およびピーク波数と、最大表面温度との関係を示す図である。

【図15】MOS(Metal Oxide Semiconductor)キャパシタの高周波C−V特性を示す図である。

【図16】固定電荷密度と最大表面温度との関係を示す図である。

【図17】この発明の実施の形態による他の半導体素子の断面構造図である。

【図18】図17に示す半導体素子の製造方法を示す第1の工程図である。

【図19】図17に示す半導体素子の製造方法を示す第2の工程図である。

【図20】図17に示す半導体素子の製造方法を示す第3の工程図である。

【図21】シート抵抗と最大表面温度との関係を示す図である。

【発明を実施するための形態】

【0014】

本発明の実施の形態について図面を参照しながら詳細に説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰返さない。

【0015】

図1は、この発明の実施の形態による半導体素子の断面構造図である。図1を参照して、この発明の実施の形態による半導体素子10は、絶縁基板1と、n+型多結晶シリコン層2,3と、多結晶シリコン膜4と、絶縁膜5,9と、ソース電極6と、ドレイン電極7と、金属量子ドット8と、ゲート電極11とを備える。

【0016】

絶縁基板1は、例えば、ガラスまたは有機フィルムからなる。n+型多結晶シリコン層2は、絶縁基板1に接して形成される。n+型多結晶シリコン層3は、絶縁基板1の面内方向においてn+型多結晶シリコン層2から離れた位置で絶縁基板1に接して形成される。

【0017】

n+型多結晶シリコン層2,3の各々は、例えば、20nmの膜厚を有し、例えば、約1×1020cm−3のリン(P)濃度を有する。

【0018】

多結晶シリコン膜4は、n+型多結晶シリコン層2,3を覆うように絶縁基板1上に形成される。多結晶シリコン膜4は、例えば、ノンドープの多結晶シリコンからなり、例えば、10〜20nmの膜厚を有する。

【0019】

絶縁膜5は、多結晶シリコン膜4を覆うように絶縁基板1上に形成される。そして、絶縁膜5は、例えば、二酸化シリコン(SiO2)膜からなり、例えば、5nmの膜厚を有する。この5nmの膜厚は、キャリア(電子または正孔)がトンネル可能な膜厚である。

【0020】

ソース電極6は、一方端がn+型多結晶シリコン層2上において絶縁膜5を貫通して多結晶シリコン膜4に接するように絶縁膜5上に形成される。そして、ソース電極6は、例えば、アルミニウム(Al)からなる。

【0021】

ドレイン電極7は、一方端がn+型多結晶シリコン層3上において絶縁膜5を貫通して多結晶シリコン膜4に接するように絶縁膜5上に形成される。そして、ドレイン電極7は、例えば、Alからなる。

【0022】

金属量子ドット8は、ソース電極6とドレイン電極7との間において、絶縁膜5に接して形成される。そして、金属量子ドット8は、例えば、白金(Pt)ドットからなる。また、金属量子ドット8は、例えば、9.0nmの高さ、10nmの幅を有する。更に、金属量子ドット8の密度は、例えば、1.6×1011cm−2である。

【0023】

絶縁膜9は、金属量子ドット8を覆うように絶縁膜5上に形成される。そして、絶縁膜9は、例えば、SiO2膜からなる。また、絶縁膜9は、例えば、20nmの膜厚を有する。

【0024】

ゲート電極11は、絶縁膜9に接して絶縁膜9上に形成される。そして、ゲート電極11は、例えば、不純物半導体または半透明金属からなる。不純物半導体は、B等の不純物がドーピングされた半導体である。

【0025】

半導体素子10においては、金属量子ドット8は、絶縁膜5,9によって挟まれており、絶縁膜5は、キャリアがトンネル可能な膜厚を有する。従って、半導体素子10においては、ゲート電極11に印加する電圧を制御することによって、チャネル層である多結晶シリコン膜4中の電子は、金属量子ドット8へ注入される。

【0026】

また、金属量子ドット8に光を照射することによって、金属量子ドット8に保持された電子は、多結晶シリコン膜4へ放出される。

【0027】

このように、半導体素子10は、キャリアの書込みおよび消去が可能なフローティングゲート型の薄膜トランジスタである。

【0028】

図2は、リモートプラズマ処理を行なうプラズマ装置の概略図である。図2を参照して、プラズマ装置600は、石英管610と、反応室620と、基板ホルダー630と、ヒーター640と、配管650と、バルブ660と、アンテナ670と、マッチング回路680と、高周波電源690とを備える。

【0029】

石英管610は、10cmφの直径を有し、その一方端が反応室620内に挿入されるように固定される。反応室620は、中空の円筒形状からなり、上面620Aに石英管610の一方端を挿入するための開口部621を有し、側面620Bに排気口622を有する。そして、反応室620は、開口部621から石英管610の一方端が挿入されることによって、内部空間が石英管610の内部空間と連通する。従って、ポンプ(図示せず)によって反応室620および石英管610の内部の気体を排気口622を介して排気できる。

【0030】

基板ホルダー630は、反応室620の下面620C上に配置される。ヒーター640は、シリコンカーバイド(SiC)からなり、基板ホルダー630内に配置される。

【0031】

配管650は、バルブ660を介して石英管610の他方端に連結される。バルブ660は、配管650に装着される。アンテナ670は、基板ホルダー630上に設置された基板800から23cmの位置で石英管610の周囲を取り巻くように配置される。そして、アンテナ670は、その一方端がマッチング回路680に接続され、他方端が接地される。

【0032】

マッチング回路680は、アンテナ670の一方端と高周波電源690との間に接続される。高周波電源690は、マッチング回路680と、接地ノードとの間に接続される。

【0033】

ヒーター640は、基板ホルダー630を介して基板800を所定の温度に加熱する。配管650は、水素(H2)ガス、アルゴン(Ar)ガス、窒素(N2)ガス、およびシラン(SiH4)ガスのいずれかをボンベ(図示せず)から石英管610内に導く。この場合、配管650は、

バルブ660は、H2ガス、Arガス、N2ガス、およびSiH4ガスを石英管610内へ供給し、またはH2ガス、Arガス、N2ガス、およびSiH4ガスの石英管610内への供給を遮断する。

【0034】

マッチング回路680は、高周波電源690から供給された高周波電力の高周波電源690側への反射を低くして高周波電力をアンテナ670へ供給する。高周波電源690は、60MHzの高周波電力をマッチング回路680を介してアンテナ670へ供給する。

【0035】

プラズマ装置600における処理動作について説明する。基板800が基板ホルダー630上に配置され、排気口622から反応室620および石英管610の真空引きが行なわれる。

【0036】

その後、バルブ660が開けられ、ボンベ(図示せず)から所定量のH2ガス等が配管650を介して石英管610内へ導入される。そして、石英管610内の圧力が所定の圧力に達すると、高周波電源690は、60MHzの高周波電力をマッチング回路680を介してアンテナ670に供給する。この場合、マッチング回路680は、高周波電源690から供給された高周波電力の高周波電源690側への反射が最も低くなるように調整される。

【0037】

そうすると、石英管610内でプラズマ730が発生し、主に原子状水素等がプラズマ730の発生領域から基板800の方向へ石英管610内を拡散し、基板800表面に到達する。そして、原子状水素等は、基板800表面を処理する。

【0038】

所定の処理時間が経過すると、高周波電源690がオフされ、バルブ660が閉じられて処理動作が終了する。

【0039】

なお、プラズマ装置600を用いてリモートプラズマ処理を行なう場合、基板800は、電気的にフローティングされた状態でリモートプラズマによって処理される。

【0040】

図3は、熱プラズマジェットによる処理を行なうプラズマ装置の構成を示す概略図である。図3を参照して、プラズマ装置100は、反応容器101と、陰極102と、陽極103と、絶縁部材104と、配管105と、試料ホルダー106と、ガスボンベ107と、直流電源108と、移動装置109とを備える。

【0041】

反応容器101は、中空の円柱形状からなる。陰極102は、3%のLaO2を含むタングステン(W)からなる。そして、陰極102は、略円柱形状を有し、一方端が尖っている。また、陰極102は、他方端が絶縁部材104および反応容器101を貫通し、反応容器101の外部に配置されるとともに、絶縁部材104に固定される。

【0042】

陽極103は、陰極102との間に空間SPを形成するように陰極102の周囲に配置され、絶縁部材104に固定される。そして、陽極103は、試料ホルダー106側に熱プラズマジェットが通過するための孔111を有する。

【0043】

絶縁部材104は、反応容器101の天井に固定される。配管105は、一方端が空間SPに接するように陽極103を貫通し、他方端がガスボンベ107に連結される。

【0044】

試料ホルダー106は、陰極102および陽極103に対向して配置される。ガスボンベ107は、配管105の他方端に連結され、Arガスを保持する。

【0045】

試料ホルダー106は、試料110を保持する。ガスボンベ107は、Arガスを配管105を介して空間SPに供給する。

【0046】

直流電源108は、直流電圧源1081と、電流計1082とを含む。そして、直流電源108は、所望の電流が流れるように、陰極102と陽極103との間に直流電圧を印加する。

【0047】

移動装置109は、試料ホルダー106を一定速度で方向DR1へ移動させる。

【0048】

図4は、図3に示すプラズマ装置100において結晶を製造する例を説明するための図である。図4を参照して、基板121上に多結晶シリコン膜を作製する場合、大気圧下で基板/アモルファスシリコン(a−Si)からなる試料120が試料ホルダー106上に配置される。そして、a−Siは、たとえば、プラズマCVD(Chemical Vapour Deposition)によって作製され、その膜厚は、50nmである。

【0049】

ガスボンベ107は、9.8リットル/分の流量でArガスを空間SPへ供給する。

【0050】

また、直流電源108は、直流電流が150A程度になるように、陰極102と陽極103との間に13〜16Vの直流電圧を印加する。

【0051】

そうすると、陰極102は、熱プラズマジェット140を出射し、その出射した熱プラズマジェット140を孔111を介して試料120に照射する。

【0052】

また、移動装置109は、1m/s〜2m/sの速度で矢印132の方向へ試料ホルダー106を移動させる。

【0053】

その結果、熱プラズマジェット140が照射された部分は、2〜3msecで1200℃まで昇温され、多結晶シリコン膜122になる。

【0054】

図5から図8は、それぞれ、図1に示す半導体素子10の製造方法を示す第1から第4の工程図である。

【0055】

図5を参照して、半導体素子10の製造が開始されると、ガラス等の絶縁基板1は、RCA洗浄等のウェットによる洗浄が行われ、容量結合型(CCP:Capacitively Coupled Plasma)プラズマ装置(図示せず)の一方の電極上にセットされる。この場合、平行に配置された2つの電極間の距離は、45mmである。

【0056】

そして、0.5sccmの100%SiH4ガスと、15sccmの1%フォスフィン(PH3)ガスと、34.5sccmのH2ガスとを配管を介して反応室内に流す。その後、排気装置(図示せず)によって反応室内の圧力を13.3Paに設定する。また、ヒーターによって絶縁基板1の温度を250℃に設定する。

【0057】

そうすると、高周波電源は、13.56MHzの周波数を有する50Wのパワーをマッチング回路を介して2つの電極間に印加する。

【0058】

これによって、リン(P)ドープのアモルファスシリコン膜201が絶縁基板1上に堆積される(工程(a)参照)。この場合、アモルファスシリコン膜201の膜厚は、20nmである。

【0059】

その後、アモルファスシリコン膜201上にレジストを塗布し、その塗布したレジスタをフォトリソグラフィによってパターンニングしてレジストパターン210をアモルファスシリコン膜201上に形成する(工程(b)参照)。

【0060】

そして、レジストパターン210をマスクとしてアモルファスシリコン膜201をエッチングし、n型アモルファスシリコン膜202,203を絶縁基板1上に形成する(工程(c)参照)。その後、レジストパターン210を除去する。

【0061】

引き続いて、n型アモルファスシリコン膜202,203/絶縁基板1を容量結合型プラズマ装置から取り出し、その取り出したn型アモルファスシリコン膜202,203/絶縁基板1の表面を希フッ酸で処理し、n型アモルファスシリコン膜202,203の表面を水素によって終端する。

【0062】

そして、表面が水素によって終端されたn型アモルファスシリコン膜202,203/絶縁基板1を誘導結合型(ICP:Inductively Coupled Plasma)プラズマ装置の基板ホルダー上にセットする。この場合、誘導結合型プラズマ装置における電極と基板との間の距離は、45mmである。

【0063】

そうすると、5sccmの100%SiH4ガスと、5sccmのH2ガスとを配管を介して反応室内に流す。そして、排気装置(図示せず)によって反応室内の圧力を6.65Paに設定する。また、ヒーターによって絶縁基板1の温度を250℃に設定する。

【0064】

そうすると、高周波電源は、13.56MHzの周波数を有する30Wのパワーをマッチング回路を介して電極に印加する。

【0065】

これによって、ノンドープのアモルファスシリコン膜204が絶縁基板1およびn型アモルファスシリコン膜202,203上に形成される(工程(d)参照)。この場合、アモルファスシリコン膜204の膜厚は、10nm〜20nmである。

【0066】

その後、アモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1を誘導結合型プラズマ装置から取り出し、その取り出したアモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1をプラズマ装置600の基板ホルダー630上にセットする。

【0067】

そして、0.6sccmのSiH4ガスと、10sccmのO2ガスと、40sccmのArガスとを配管650を介して石英管610および反応室620内に流す。そして、排気装置(図示せず)によって反応室620内の圧力を40Paに設定する。また、ヒーター640によって絶縁基板1の温度を350℃以下に設定する。

【0068】

そうすると、高周波電源690は、10Wのパワーをマッチング回路680を介してアンテナ670に印加する。

【0069】

これによって、SiO2膜205がアモルファスシリコン膜204上に形成される(工程(e)参照)。この場合、SiO2膜205の膜厚は、5nmである。

【0070】

図6を参照して、工程(e)の後、試料(=SiO2膜205/アモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1)をスパッタリング装置にセットし、試料の温度を室温に保持したまま、白金からなる金属薄膜206をSiO2膜205上にArスパッタリングによって形成する(工程(f)参照)。この場合、金属薄膜206の膜厚は、5nmである。

【0071】

その後、試料(=金属薄膜206/SiO2膜205/アモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1)をプラズマ装置100の試料ホルダー106上にセットする。

【0072】

そして、7リットル/minのArガスを配管105を介して空間SPへ供給し、直流電源108は、直流電流が152Aになるように、陰極102と陽極103との間に16Vの直流電圧を印加する。また、移動装置109は、1m/sまたは2m/sの速さで試料ホルダー106を絶縁基板1の面内方向へ移動させる。

【0073】

これによって、陰極102は、熱プラズマジェットを発生し、その発生した熱プラズマジェットを試料(=金属薄膜206/SiO2膜205/アモルファスシリコン膜204/n型アモルファスシリコン膜202,203/絶縁基板1)に照射する(工程(g)参照)。この場合、試料と熱プラズマジェットとの距離は、4mmまたは5mmであり、試料の温度は、室温である。

【0074】

その結果、n+型多結晶シリコン層2,3は、それぞれ、n型アモルファスシリコン膜202,203から形成され、多結晶シリコン膜4は、アモルファスシリコン膜204から形成され、絶縁膜(=SiO2膜)5がSiO2膜205から形成され、金属量子ドット8が金属薄膜206から形成される(工程(h)参照)。

【0075】

そして、PMA(PostMetalization Annealing)処理を行なう。このPMA処理は、SiO2/Si界面を水素原子によって終端することによってSiO2/Si界面特性を向上させる技術である。そして、PMA処理は、試料(=金属量子ドット8/絶縁膜(=SiO2膜)5/多結晶シリコン膜4/n+型多結晶シリコン層2,3/絶縁基板1)をH2ガス中で670Kの温度で熱処理することによって行われた。

【0076】

その後、試料(=金属量子ドット8/SiO2膜5/多結晶シリコン膜4/n型アモルファスシリコン膜202,203/絶縁基板1)をプラズマ装置600の基板ホルダー630上にセットする。そして、SiO2膜205の形成条件と同じ形成条件を用いてSiO2膜207を金属量子ドット8を覆うように形成する(工程(i)参照)。この場合、SiO2膜207の膜厚は、20nmである。

【0077】

図7を参照して、工程(i)の後、レジストをSiO2膜207の全面に塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン220をSiO2膜207上に形成する(工程(j)参照)。

【0078】

そして、レジストパターン220をマスクとしてSiO2膜207および金属量子ドット8をエッチングする(工程(k)参照)。これによって、SiO2膜9が金属量子ドット8上に形成される。その後、レジストパターン220を除去する。

【0079】

引き続いて、レジストをSiO2膜5,9上に塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン230をレジストをSiO2膜5,9上に形成する(工程(l)参照)。

【0080】

そして、レジストパターン230をマスクとしてSiO2膜5をエッチングし、スルーホール208,209を絶縁膜(=SiO2膜)5に形成する(工程(m)参照)。その後、レジストパターン230を除去する。

【0081】

図8を参照して、工程(m)の後、SiO2膜5,9上にレジストを塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン240をSiO2膜5,9上に形成する(工程(n)参照)。

【0082】

そして、レジストパターン240をマスクとしてAlを蒸着し、その後、レジストパターン240を除去する。これによって、ソース電極6およびドレイン電極7が形成される(工程(o)参照)。

【0083】

引き続いて、SiO2膜5,9、ソース電極6およびドレイン電極7上にレジストを塗布し、その塗布したレジストをフォトリソグラフィによってパターンニングしてレジストパターン250を形成する(工程(p)参照)。

【0084】

そして、レジストパターン250をマスクとして不純物半導体または半透明金属を形成し、その後、レジストパターン250を除去する。これによって、ゲート電極11がSiO2膜9上に形成され、半導体素子10が完成する(工程(q)参照)。

【0085】

なお、金属量子ドット8がNiからなる場合も、半導体素子10は、上述した工程(a)〜工程(q)に従って製造される。

【0086】

図9〜図12は、それぞれ、図1に示す半導体素子10におけるメモリ書込動作とメモリ消去動作とを説明するための第1から第4のエネルギーバンド図である。

【0087】

以下の説明では、半導体素子10におけるトランジスタキャパシタ部のエネルギーバンド図を参照してメモリ書き込み動作およびメモリ消去動作を説明する。

【0088】

まず、図9を参照して、半導体素子10のゲート電極11に正の電圧が印加されていないときのエネルギーバンド図について説明する。金属量子ドット8は、絶縁膜5と絶縁膜9とによって挟まれており、ナノサイズを有するため、離散的なエネルギー準位LV1が金属量子ドット8の伝導帯中に存在する。エネルギー準位LV1は、電子に対するエネルギー準位である。

【0089】

そして、金属量子ドット8は、多結晶シリコン膜4と異なる材料からなっているので、エネルギー準位LV1は、多結晶シリコン膜4の伝導帯よりも低い。

【0090】

このように、半導体素子10においては、金属量子ドット8の電子に対するエネルギー準位LV1は、多結晶シリコン膜4の伝導帯よりも低い。

【0091】

次に、図10を参照して、図9に示すエネルギーバンド図を有する半導体素子10におけるメモリの書き込み動作は、ゲート電極11に正の電圧を印加し、多結晶シリコン膜4から電子を金属量子ドット8に注入することにより行われる。

【0092】

ゲート電極11に正の電圧を印加すると、多結晶シリコン膜4の電子30が絶縁膜5をトンネルして金属量子ドット8へと注入される。金属量子ドット8へ電子が注入されると、金属量子ドット8の静電エネルギーが上昇するため、金属量子ドット8中の電子保持によって多結晶シリコン膜4のバンドは、下側に曲げられる。この状態は、論理上の「1」と判定される。

【0093】

正の電圧をゲート電極11に更に印加すると、さらに、多結晶シリコン膜4の電子が絶縁膜5をトンネルして金属量子ドット8へと注入される。これによって、金属量子ドット8へ2個目の電子40が注入される(図11参照)。この状態は、論理上の「2」と判定される。

【0094】

このように、ゲート電極11に正電圧を印加することによって、多結晶シリコン膜4の電子が1個ずつ絶縁膜5をトンネルして金属量子ドット8へと注入される。この状態をもって多値表現が可能となる。

【0095】

金属量子ドット8に注入された数個の電子は、光入力または電子放出操作のない間は金属量子ドット8に保持される。

【0096】

また、半導体素子10のゲート電極11に正電圧を更に印加すると、上記同様に、多結晶シリコン膜4から電子が金属量子ドット8内に注入される。

【0097】

金属量子ドット8は、ナノ(量子)構造であるため、離散化したエネルギー準位LV1が存在し、このエネルギー準位LV1は、多結晶シリコン膜4の伝導帯よりも低い。その結果、金属量子ドット8は、電子保持によるしきい値シフトの検知が可能であり、さらには、金属材料を用いているため、保持電子数の制限がなく、多数の電子を安定に保持できる。そのため、電子保持時間が長くなり、結果として情報の保持時間が長くなる。さらには、電荷保持ノードとして金属量子ドット8を用いることで、電子の注入に必要な時間、即ち、情報書き込み時間に大きく影響を及ぼす絶縁膜5を極めて薄膜化することが可能となるため、書き込み速度も同時に効率良く改善できる。

【0098】

以上説明した半導体素子10によれば、ゲート電極11を不純物半導体または半透明金属によって構成し、不純物半導体または半透明金属からの電気的パルスまたは光パルスにより金属量子ドット8への電子の注入を高速で効率的に行なうことが可能となる。

【0099】

また、半導体素子10においては、多結晶シリコン膜4と絶縁膜5との境界面がSiとSiO2との界面なので、閾値電圧の増加や電界効果移動度の低下を招くことなく、良好なトランジスタ特性を実現できる。

【0100】

次に、半導体素子10におけるメモリの消去動作について説明する。半導体素子10におけるメモリの消去は、ゲート電極11に光を照射したり、負の電圧を印加したりして、金属量子ドット8に注入された電子を多結晶シリコン膜4へ放出することによって行なわれる。

【0101】

以下、図12を参照して、半導体素子10におけるメモリの消去動作を説明する。なお、半導体素子10の構造におけるトランジスタキャパシタ部の構造で説明を行う。

【0102】

一旦、書き込んだ情報を消去する場合、ゲート電極11から微弱な光50を入射する。微弱な光50がゲート電極11に入射されると、内部光電効果によって、金属量子ドット8に保持された電子が励起される。その結果、半導体素子10では、金属量子ドット8に保持された電子60は、多結晶シリコン膜4中へ放出される。

【0103】

そして、ゲート電極11に負電圧をさらに印加することによって、金属量子ドット8中のより低いエネルギー準位LV1に保持された電子は、多結晶シリコン膜4へ放出される。

【0104】

このように、半導体素子10では、金属量子ドット8に保持された電子を放出する際、ゲート電極11に印加する負電圧を制御することによって、金属量子ドット8に保持された電子を段階的に多結晶シリコン膜4へ放出するようにしている。

【0105】

その結果、多値メモリの部分的な消去動作が可能となるので、メモリ消去動作の制御をより確実化させることができる。

【0106】

また、一度に全ての電子を放出する場合は、ゲート電極11に負電圧を印加した状態でゲート電極11に微弱な光50を照射する。これにより、内部光電効果によって金属量子ドット8内の保持電子を一挙に多結晶シリコン膜4へ放出でき、保持電子がなくなるため、データは消去されたことになる。

【0107】

なお、金属量子ドット8に対する多結晶シリコン膜4のバリアは、低いために赤外域の光でも容易に電子を放出できるので、現在、光データ通信に広く使われている赤外域の光で半導体素子10からのデータ出力が可能であるという利点を有する。

【0108】

なお、微弱な光50の光源として、メモリパッケージ内部に有機EL材料を塗布することで実現してもよい。

【0109】

以上、説明したように、半導体素子10においては、多値記憶動作を実現できる。

【0110】

また、Si量子ドットに比べ電子系に対する深いポテンシャル井戸が実現できる金属量子ドットに電子を注入することにより、注入された電子は、金属量子ドット内に安定して蓄積可能となり、電子を放出しにくくなる。その結果、絶縁膜5の薄膜化による書き込み・消去時間の低減が改善できるため、多値記憶動作を安定かつ高速に実現可能となる。

【0111】

半導体素子10の製造においては、n型アモルファスシリコン膜202,203、アモルファスシリコン膜204、SiO2膜205および金属薄膜206を、順次、絶縁基板1上に堆積した後に、プラズマ装置100によって熱プラズマジェットをn型アモルファスシリコン膜202,203、アモルファスシリコン膜204、SiO2膜205および金属薄膜206に照射してn+型多結晶シリコン層2,3、多結晶シリコン膜4、絶縁膜(=SiO2膜)5および金属量子ドット8を形成する(工程(a)〜工程(h)参照)。

【0112】

即ち、絶縁膜(=SiO2膜)5は、プラズマ装置600を用いたリモートプラズマによって堆積されたSiO2膜205に熱プラズマジェットを照射することによって作製される。また、多結晶シリコン膜4と絶縁膜(=SiO2膜)5との界面も、アモルファスシリコン膜204/SiO2膜205に熱プラズマジェットを照射することによって作製される。

【0113】

そこで、熱プラズマジェットによって作製された絶縁膜(=SiO2膜)5、および多結晶シリコン膜4と絶縁膜(=SiO2膜)5との界面特性について説明する。

【0114】

図13は、フーリエ変換赤外分光光度計(FT−IR)を用いたSiO2膜の赤外線分光のスペクトルを示す図である。図13において、縦軸は、吸収を表し、横軸は、波数を表す。

【0115】

図13を参照して、SiO2膜205においては、Si−O−Siの伸縮振動が1053cm−1に観測された。この1053cm−1の波数は、1000℃程度の高温でシリコンウェハを熱酸化して形成されたSiO2膜におけるSi−O−Siの伸縮振動の波数(=1078cm−1)よりも小さい。

【0116】

また、SiO2膜205においては、3400〜3600cm−1の範囲において、Si−OHの結合に基づく吸収が観測された。

【0117】

これらの結果は、SiO2膜205の堆積中に、Si−OHの結合が導入され、Si−O−Siネットワークにおいて酸素欠陥を生じることを示す。

【0118】

また、PMA処理を行なうことによって、Si−OH結合およびSi−O−Si結合の強度は、殆ど、変化せず、Si−O−Siのピーク波数も、殆ど、変化しない。従って、Si−O−Siネットワークの化学結合は、670KでのPMAによっては改善されない。

【0119】

一方、プラズマ装置100を用いた熱プラズマジェットの照射によるアニールを行なうと、SiO2膜205の温度は、2.8msの間、815℃に昇温され、3400〜3600cm−1の範囲におけるSi−OHの伸縮振動による吸収強度が大きく減少する。また、Si−O−Siの非対称伸縮振動に関連した信号強度は、1053cm−1から1066cm−1へ著しく増加し、吸収バンドの半値幅は、90cm−1から85cm−1へ減少する。

【0120】

これらの結果は、膜中のOH結合がH2O分子として脱着し、Si−O−Siネットワークを形成することを示す。即ち、熱プラズマジェットによるアニールは、Si−O−Siの化学結合成分を増加し、ネットワークを緩和する。

【0121】

図14は、SiO2膜におけるSi−OHの相対積分強度、Si−O−Siの相対積分強度、およびピーク波数と、最大表面温度との関係を示す図である。

【0122】

図14において、縦軸は、SiO2膜におけるSi−OHの相対積分強度、Si−O−Siの相対積分強度、およびピーク波数を表し、横軸は、最大表面温度を表す。なお、この最大表面温度は、プラズマ装置100を用いて熱プラズマジェットによってSiO2膜をアニールするときのSiO2膜の表面温度の最大値であり、試料ホルダー106上の試料全体の温度ではない。

【0123】

図14を参照して、最大表面温度が889(K)から1088(K)まで上昇すると、Si−OH結合の量は、単調に24%まで減少し、Si−O−Si結合の量は、1.15倍まで増加する。また、ピーク波数は、最大表面温度の上昇に伴って線形に大きくなる。

【0124】

そして、1088Kにおける熱プラズマジェットによるアニールは、973(K)における熱酸化膜と実質的に同等である。

【0125】

従って、基板表面の局所的な加熱は、厳しい熱的ダメージを基板に与えることなしに膜の品質を改善する有効な方法である。

【0126】

図15は、MOS(Metal Oxide Semiconductor)キャパシタの高周波C−V特性を示す図である。

【0127】

図15において、縦軸は、規格化された容量を表し、横軸は、ゲート電圧を表す。

【0128】

図15を参照して、プラズマ装置600を用いて堆積された直後のSiO2膜(As−deposited)を用いたMOSキャパシタのC−V特性は、注入電荷のためにヒステリシスを示すとともに、正の固定電荷のために、負のフラットバンド電圧シフトが観測された。

【0129】

一方、PMA処理および熱プラズマジェットによるアニールを行なったSiO2膜を用いてMOSキャパシタのC−V特性においては、ヒステリシスの幅および負のフラットバンド電圧シフトが著しく減少した。

【0130】

これらの結果は、トラップサイト数および固定電荷量の減少を表すものである。

【0131】

図16は、固定電荷密度と最大表面温度との関係を示す図である。図16において、縦軸は、固定電荷密度を表し、横軸は、最大表面温度を表す。なお、固定電荷密度は、全ての固定電荷がSiO2/Si界面に存在すると仮定して計算された。

【0132】

図16を参照して、プラズマ装置600を用いて堆積された直後のSiO2膜(As−deposited)を用いたMOSキャパシタの固定電荷密度は、1×1012(cm−2)よりも高い。

【0133】

一方、熱プラズマジェットによるアニールを行なったSiO2膜を用いたMOSキャパシタの固定電荷密度は、最大表面温度が1200Kまで上昇するに伴って、1.2×1011(cm−2)まで減少した。

【0134】

この1.2×1011(cm−2)の値は、PMA処理を行なったSiO2膜を用いたMOSキャパシタの固定電荷密度よりも低い値である。

【0135】

熱プラズマジェットによるアニールを行なったSiO2膜を用いたMOSキャパシタのC−V特性は、PMA処理を行なったSiO2膜を用いたMOSキャパシタのC−V特性よりも向上しない。

【0136】

そして、図15に示すように、熱プラズマジェットによるアニールを行なった後に、PMA処理を行なったSiO2膜を用いたMOSキャパシタ(TPJ+PMA)のC−V特性は、殆ど、理想的なC−V特性に一致する。

【0137】

これらの結果は、SiO2膜中の固定電荷密度および界面トラップ密度がPMA処理によって更に減少することを意味する。これを確認するために、界面トラップ密度を高周波C−V特性およびquasi-static C−V特性から定量的に評価した。その結果、熱プラズマジェットによるアニールを行なうことによって、界面トラップ密度は、2.0×1012(cm−2eV−1)から5.0×1011(cm−2eV−1)へ減少した。

【0138】

そして、熱プラズマジェットによるアニールを行なった後に、PMA処理を行なうことによって、界面トラップ密度は、3.0×1010(cm−2eV−1)まで減少した。この3.0×1010(cm−2eV−1)は、約1000℃において熱酸化によって作製されたSiO2の界面トラップ密度と同等である。

【0139】

このように、熱プラズマジェットによるアニールとPMA処理とを連続的に行なうことによって、熱酸化によって作製されたSiO2の界面トラップ密度と同等の界面トラップ密度を有するSiO2/Si界面が得られる。

【0140】

従って、半導体素子10における多結晶シリコン膜4と絶縁膜5(=SiO2膜)との界面は、良好な界面特性を示す。

【0141】

その結果、この発明の実施の形態によれば、ガラス等の絶縁基板1上に作製された半導体素子10において、二酸化シリコンとシリコンとの界面特性を向上できる。

【0142】

金属量子ドット8は、金属薄膜206を熱プラズマジェットによってアニールすることによって製造されるが、金属量子ドット8の密度および高さは、熱プラズマジェットが照射されたときの金属薄膜206の表面温度によって変化する。

【0143】

即ち、金属量子ドット8の密度は、金属薄膜206の表面温度が500℃から700℃へ高くなるに従って約2.0×1011(cm−2)から約1.4×1011(cm−2)へ低下し、金属量子ドット8の高さは、金属薄膜206の表面温度が500℃から700℃へ高くなるに従って約6.0nmから約13.7nmまで大きくなる。

【0144】

従って、金属薄膜206の表面温度が500℃であるとき、金属量子ドット8は、最も高い密度および最も低い高さを有し、金属薄膜206の表面温度が700℃であるとき、金属量子ドット8は、最も低い密度および最も高い高さを有する。

【0145】

そして、金属薄膜206の表面温度は、熱プラズマジェットの走査速度および熱プラズマジェットと試料との距離によって変化する。熱プラズマジェットと試料との距離を一定に保持して、熱プラズマジェットの走査速度を2m/sに設定すると、金属薄膜206の表面温度は、500℃になり、熱プラズマジェットの走査速度を1m/sに設定すると、金属薄膜206の表面温度は、650℃になる。

【0146】

従って、熱プラズマジェットと試料との距離を一定に保持した場合、金属薄膜206の表面温度は、熱プラズマジェットの走査速度が相対的に速くなれば、相対的に低くなり、熱プラズマジェットの走査速度が相対的に遅くなれば、相対的に高くなる。

【0147】

また、熱プラズマジェットの走査速度を一定に保持して、熱プラズマジェットと試料との距離を4mmに設定すると、金属薄膜206の表面温度は、650℃になり、熱プラズマジェットと試料との距離を5mmに設定すると、金属薄膜206の表面温度は、700℃になる。

【0148】

従って、熱プラズマジェットの走査速度を一定に保持した場合、金属薄膜206の表面温度は、熱プラズマジェットと試料との距離が相対的に短くなれば、相対的に高くなり、熱プラズマジェットの走査速度が相対的に長くなれば、相対的に低くなる。

【0149】

その結果、熱プラズマジェットの走査速度、および熱プラズマジェットと試料との距離を制御することによって、金属量子ドット8の密度および高さを所望の密度および所望の高さに設定できる。

【0150】

図17は、この発明の実施の形態による他の半導体素子の断面構造図である。この発明の実施の形態による半導体素子は、図17に示す半導体素子10Aであってもよい。

【0151】

図17を参照して、半導体素子10Aは、絶縁基板1と、多結晶シリコン膜21と、ソース電極22と、ドレイン電極23と、絶縁膜24,26と、金属量子ドット25と、ゲート電極27とを備える。

【0152】

多結晶シリコン膜21は、ノンドープの多結晶シリコンからなり、多結晶シリコン膜4と同じ膜厚を有する。そして、多結晶シリコン膜21は、絶縁基板1の表面に形成される。

【0153】

ソース電極22は、n+型多結晶シリコンからなり、多結晶シリコン膜21中に形成される。そして、ソース電極22は、半導体素子10のn+型多結晶シリコン層2,3と略同じ膜厚を有する。また、ソース電極22は、約1×1020cm−3のP濃度を有する。

【0154】

ドレイン電極23は、絶縁基板1の面内方向において、ソース電極22から離れた位置において多結晶シリコン膜21中に配置される。そして、ドレイン電極23は、半導体素子10のn+型多結晶シリコン層2,3と略同じ膜厚を有する。また、ドレイン電極23は、約1×1020cm−3のP濃度を有するn+型多結晶シリコンからなる。

【0155】

絶縁膜24は、SiO2膜からなり、ソース電極22とドレイン電極23との間の多結晶シリコン膜21上に多結晶シリコン膜21に接して形成される。そして、絶縁膜24は、キャリアがトンネル可能な5nmの膜厚を有する。

【0156】

金属量子ドット25は、PtまたはNiからなり、絶縁膜24に接して絶縁膜24上に形成される。そして、金属量子ドット25は、半導体素子10の金属量子ドット8と同じサイズを有する。

【0157】

絶縁膜26は、SiO2膜からなり、金属量子ドット25を覆うように絶縁膜24上に形成される。そして、絶縁膜26は、半導体素子10の絶縁膜9と同じ膜厚を有する。

【0158】

ゲート電極27は、不純物半導体または半透明金属からなる。そして、ゲート電極27は、絶縁膜26上に形成される。

【0159】

図18から図20は、それぞれ、図17に示す半導体素子10Aの製造方法を示す第1から第3の工程図である。

【0160】

図18を参照して、半導体素子10Aの製造が開始されると、ガラス等の絶縁基板1は、RCA洗浄等のウェットによる洗浄が行われ、誘導結合型プラズマ装置の基板ホルダー上にセットされる。

【0161】

そして、上述したアモルファスシリコン膜204の形成条件と同じ形成条件を用いてアモルファスシリコン膜301を絶縁基板1上に形成する(工程(a)参照)。この場合、アモルファスシリコン膜301の膜厚は、アモルファスシリコン膜204の膜厚と同じである。

【0162】

その後、アモルファスシリコン膜301/絶縁基板1を誘導結合型プラズマ装置から取り出し、その取り出したアモルファスシリコン膜301/絶縁基板1をプラズマ装置600の基板ホルダー630上にセットする。

【0163】

そして、SiO2膜205の形成条件と同じ形成条件を用いてSiO2膜302をアモルファスシリコン膜301上に形成する(工程(b)参照)。この場合、SiO2膜302の膜厚は、SiO2膜205の膜厚と同じである。

【0164】

引き続いて、試料(=SiO2膜302/アモルファスシリコン膜301/絶縁基板1)をスパッタリング装置にセットし、試料の温度を室温に保持したまま、白金からなる金属薄膜303をSiO2膜302上にArスパッタリングによって形成する(工程(c)参照)。この場合、金属薄膜303の膜厚は、5nmである。

【0165】

その後、試料(=金属薄膜303/SiO2膜302/アモルファスシリコン膜301/絶縁基板1)をプラズマ装置100の試料ホルダー106上にセットする。

【0166】

そして、7リットル/minのArガスを配管105を介して空間SPへ供給し、直流電源108は、直流電流が152Aになるように、陰極102と陽極103との間に16Vの直流電圧を印加する。また、移動装置109は、1m/sまたは2m/sの速さで試料ホルダー106を絶縁基板1の面内方向へ移動させる。

【0167】

これによって、陰極102は、熱プラズマジェットを発生し、その発生した熱プラズマジェットを試料(=金属薄膜303/SiO2膜302/アモルファスシリコン膜301/絶縁基板1)に照射する(工程(d)参照)。この場合、試料と熱プラズマジェットとの距離は、4mmまたは5mmであり、試料の温度は、室温である。

【0168】

これによって、多結晶シリコン膜304は、アモルファスシリコン膜301から形成され、SiO2膜305は、SiO2膜302から形成され、金属量子ドット25が金属薄膜303から形成される(工程(e)参照)。

【0169】

そして、試料(=金属量子ドット25/SiO2膜305/多結晶シリコン膜304/絶縁基板1)をH2ガス中で670Kの温度で熱処理することによってPMA処理を行なう。

【0170】

図19を参照して、工程(e)の後、プラズマ装置600を用いてSiO2膜302の形成条件と同じ形成条件を用いてSiO2膜306を金属量子ドット25を覆うようにSiO2膜305上に形成する(工程(f)参照)。この場合、SiO2膜306の膜厚は、半導体素子10の絶縁膜9の膜厚と同じである。

【0171】

その後、レジストをSiO2膜306上に塗布し、その塗布したレジストをフォトリソグラフィによりパターンニングしてレジストパターン310を形成する(工程(g)参照)。

【0172】

そして、レジストパターン310をマスクとしてSiO2膜306、金属量子ドット25およびSiO2膜305をエッチングする。これによって、多結晶シリコン膜304上に絶縁膜24、金属量子ドット25および絶縁膜26が形成される(工程(h)参照)。

【0173】

引き続いて、レジストパターン310をマスクとしてPを多結晶シリコン膜304にイオン注入する(工程(i)参照)。そして、レジストパターン310を除去する。この場合、イオン注入の加速電圧は、5keVであり、Pのドーズ量は、5×1014(イオン/cm2)である。

【0174】

図20を参照して、工程(i)の後、試料(=絶縁膜26/金属量子ドット25/絶縁膜24/Pドープ領域307,308/多結晶シリコン膜21/絶縁基板1)を570(K)で熱処理する。そして、試料(=絶縁膜26/金属量子ドット25/絶縁膜24/Pドープ領域307,308/多結晶シリコン膜21/絶縁基板1)をプラズマ装置100の試料ホルダー106上にセットする。

【0175】

そして、7リットル/minのArガスを配管105を介して空間SPへ供給し、直流電源108は、直流電流が150Aになるように、陰極102と陽極103との間に14.0〜18.5Vの直流電圧を印加する。また、移動装置109は、400mm/s〜1400mm/sの速さで試料ホルダー106を絶縁基板1の面内方向へ移動させる。

【0176】

これによって、陰極102は、熱プラズマジェットを発生し、その発生した熱プラズマジェットをPドープ領域307,308に照射する(工程(j)参照)。この場合、試料と熱プラズマジェットとの距離は、1.5mmであり、試料の温度は、室温である。

【0177】

その結果、イオン注入されたP原子が電気的に活性化され、ソース電極22およびドレイン電極23が多結晶シリコン層21中に形成される。

【0178】

そして、レジストを塗布し、その塗布したレジストをフォトリソグラフィによりパターングしてレジストパターン320を形成する(工程(k)参照)。

【0179】

そうすうと、レジストパターン320をマスクとして不純物半導体または半透明金属からなるゲート電極27を絶縁膜26上に形成する。これによって、半導体素子10Aが完成する(工程(l)参照)。

【0180】

なお、半導体素子10Aの製造方法においては、Pをプラズマ処理によって多結晶シリコン膜304中へ注入してもよい。

【0181】

また、金属量子ドット25がNiからなる場合も、半導体素子10Aは、図18から図20に示す工程(a)〜工程(l)に従って製造される。

【0182】

図21は、シート抵抗と最大表面温度との関係を示す図である。図21において、縦軸は、シート抵抗を表し、横軸は、最大表面温度を表す。

【0183】

なお、図21において、Preheating Temperatureは、プラズマ装置100を用いたプラズマジェットによるアニールの前に行なわれる熱処理温度である。

【0184】

図21を参照して、Bをイオン注入した試料、および砒素(As)をイオン注入した試料において、シート抵抗は、最大表面温度の上昇に伴って大きく低下する。従って、熱プラズマジェットによるアニールを行なうことによって、イオン注入されたBおよびAsは、電気的に活性化されることが解った。

【0185】

このように、熱プラズマジェットによるアニールによって、イオン注入された原子を電気的に活性化できる。

【0186】

なお、図21においては、図示されていないが、Pをイオン注入した場合も、熱プラズマジェットによるアニールによって、イオン注入されたPを電気的に活性化できることを確認している。

【0187】

半導体素子10Aにおける金属量子ドット25へのメモリの書込動作および消去動作は、半導体素子10における金属量子ドット8へのメモリの書込動作および消去動作と同じである。

【0188】

半導体素子10Aのその他の部分については、半導体素子10と同じである。

【0189】

なお、上述した半導体素子10の製造方法においては、n型アモルファスシリコン膜202,203、アモルファスシリコン膜204、SiO2膜205および金属薄膜206を絶縁基板1上に、順次、堆積した後に、熱プラズマジェットによるアニールを行なうと説明したが、この発明の実施の形態においては、これに限らず、次のような方法によって、n型アモルファスシリコン膜202,203、アモルファスシリコン膜204、SiO2膜205および金属薄膜206に対して熱プラズマジェットによるアニールを行なっても良い。

(I)n型アモルファスシリコン膜202,203を堆積後、n型アモルファスシリコン膜202,203を熱プラズマジェットによってアニールし、その後、アモルファスシリコン膜204をn+型多結晶シリコン膜2,3上に堆積し、アモルファスシリコン膜204を熱プラズマジェットによってアニールし、その後、多結晶シリコン膜4上にSiO2膜205を堆積し、SiO2膜205を熱プラズマジェットによってアニールし、その後、絶縁膜(=SiO2膜)5上に金属薄膜206を堆積し、金属薄膜206を熱プラズマジェットによってアニールする。

(II)n型アモルファスシリコン膜202,203を堆積後、n型アモルファスシリコン膜202,203を熱プラズマジェットによってアニールし、その後、アモルファスシリコン膜204およびSiO2膜205をn+型多結晶シリコン膜2,3上に堆積し、アモルファスシリコン膜204およびSiO2膜205を熱プラズマジェットによってアニールし、その後、絶縁膜(=SiO2膜)5上に金属薄膜206を堆積し、金属薄膜206を熱プラズマジェットによってアニールする。

(III)n型アモルファスシリコン膜202,203を堆積後、n型アモルファスシリコン膜202,203を熱プラズマジェットによってアニールし、その後、アモルファスシリコン膜204、SiO2膜205および金属薄膜206をn+型多結晶シリコン膜2,3上に堆積し、アモルファスシリコン膜204/SiO2膜205/金属薄膜206を熱プラズマジェットによってアニールする。

(IV)n型アモルファスシリコン膜202,203を堆積後、n型アモルファスシリコン膜202,203を熱プラズマジェットによってアニールし、その後、アモルファスシリコン膜204をn+型多結晶シリコン膜2,3上に堆積し、アモルファスシリコン膜204を熱プラズマジェットによってアニールし、その後、多結晶シリコン膜4上にSiO2膜205および金属薄膜206を堆積し、SiO2膜205/金属薄膜206を熱プラズマジェットによってアニールする。

【0190】

また、上述した半導体素子10Aの製造方法においては、アモルファスシリコン膜301、SiO2膜302および金属薄膜303を絶縁基板1上に、順次、堆積した後に、熱プラズマジェットによるアニールを行なうと説明したが、この発明の実施の形態においては、これに限らず、次のような方法によって、アモルファスシリコン膜301、SiO2膜302および金属薄膜303に対する熱プラズマジェットによるアニールを行なっても良い。

(V)アモルファスシリコン膜301を絶縁基板1上に堆積し、アモルファスシリコン膜301を熱プラズマジェットによってアニールし、その後、多結晶シリコン膜304上にSiO2膜302を堆積し、SiO2膜302を熱プラズマジェットによってアニールし、その後、SiO2膜305上に金属薄膜303を堆積し、金属薄膜303を熱プラズマジェットによってアニールする。

(VI)アモルファスシリコン膜301およびSiO2膜302を絶縁基板1上に堆積し、アモルファスシリコン膜301およびSiO2膜302を熱プラズマジェットによってアニールし、その後、SiO2膜305上に金属薄膜303を堆積し、金属薄膜303を熱プラズマジェットによってアニールする。

(VII)アモルファスシリコン膜301を絶縁基板1上に堆積し、その後、アモルファスシリコン膜301を熱プラズマジェットによってアニールし、その後、多結晶シリコン膜304上にSiO2膜302および金属薄膜303を堆積し、SiO2膜302/金属薄膜303を熱プラズマジェットによってアニールする。

【0191】

そして、上述した方法(I)〜(VII)のうちのいずれの方法を用いても、多結晶シリコン膜4と絶縁膜(SiO2膜)5との界面における界面トラップ密度、および多結晶シリコン膜21と絶縁膜(SiO2膜)24との界面における界面トラップ密度は、3.0×1010(cm−2eV−1)になる。従って、SiO2とSiとの良い界面特性を持った半導体素子10,10Aを絶縁基板1上に作製できる。

【0192】

このように、この発明の実施の形態による半導体素子の製造方法は、アモルファスシリコン膜の堆積、アモルファスシリコン膜の熱プラズマジェットによるアニール、SiO2膜の堆積、SiO2膜の熱プラズマジェットによるアニール、金属薄膜の堆積、および金属薄膜の熱プラズマジェットによるアニールを備えるものであればよい。

【0193】

この発明の実施の形態による半導体素子10,10Aの製造方法は、プラズマを用いたアモルファスシリコン膜およびSiO2膜の堆積、スパッタリングによる金属薄膜の堆積、室温における熱プラズマジェットによるアモルファスシリコン膜、SiO2膜および金属薄膜のアニールを用いて半導体素子10,10Aを製造する。

【0194】

従って、500℃以下の低温において半導体素子10,10Aを製造できる。つまり、SiO2とSiとの界面準位密度を熱酸化膜(=SiO2膜)とシリコンとの界面準位密度(=3.0×1010(cm−2eV−1))まで低減した半導体素子10,10Aを絶縁基板1上に製造できる。

【0195】

なお、上記においては、ソース電極6,22およびドレイン電極7,23は、n型多結晶シリコンからなると説明したが、この発明の実施の形態においては、これに限らず、ソース電極6,22およびドレイン電極7,23は、p型多結晶シリコンからなっていてもよい。この場合、図5の工程(a)において、容量結合型プラズマ装置を用いてボロン(B)をドープしたp型アモルファスシリコン膜が絶縁基板1上に堆積される。また、図19の工程(i)において、ボロン(B)が多結晶シリコン膜304へイオン注入される。

【0196】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施の形態の説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【産業上の利用可能性】

【0197】

この発明は、半導体素子およびその製造方法に適用される。

【符号の説明】

【0198】

1 絶縁基板、2,3 n+型多結晶シリコン層、4,21 多結晶シリコン膜、5,9,24,26 絶縁膜、6,22 ソース電極、7,23 ドレイン電極、8,25 金属量子ドット、10,10A 半導体素子、11,27 ゲート電極、100,600 プラズマ装置、101 反応容器、102 陰極、103 陽極、104 絶縁部材、105 配管、106 試料ホルダー、107 ガスボンベ、108 直流電源、109 移動装置、610 石英管、620 反応室、630 基板ホルダー、640 ヒーター、650 配管、660 バルブ、670 アンテナ、680 マッチング回路、690 高周波電源。

【特許請求の範囲】

【請求項1】

絶縁基板と、

前記絶縁基板上に形成された多結晶シリコン膜と、

前記多結晶シリコン膜に接して形成され、キャリアがトンネル可能な膜厚を有する第1の二酸化シリコン膜と、

前記第1の二酸化シリコン膜に接して形成され、白金またはニッケルからなる金属量子ドットと、

前記金属量子ドットを覆うように形成された第2の二酸化シリコン膜とを備え、

前記多結晶シリコン膜は、熱プラズマジェットをアモルファスシリコン膜に照射して製造された多結晶シリコン膜からなり、

前記第1の二酸化シリコン膜は、リモートプラズマを用いて堆積された二酸化シリコンに前記熱プラズマジェットを照射することによって製造された二酸化シリコンからなり、

前記金属量子ドットは、前記白金または前記ニッケルからなる金属薄膜に前記熱プラズマジェットを照射することによって製造された金属量子ドットからなる、半導体素子。

【請求項2】

絶縁基板上にアモルファスシリコン膜を形成する第1の工程と、

前記アモルファスシリコン膜に接して第1の二酸化シリコン膜を形成する第2の工程と、

前記第1の二酸化シリコン膜に接して白金またはニッケルからなる金属薄膜を形成する第3の工程と、

前記アモルファスシリコン膜に熱プラズマジェットを照射する第4の工程と、

前記第1の二酸化シリコン膜に熱プラズマジェットを照射する第5の工程と、

前記金属薄膜に熱プラズマジェットを照射する第6の工程と、

前記熱プラズマジェットの照射によって前記金属薄膜から形成された金属量子ドットを覆うように第2の二酸化シリコン膜を形成する第7の工程とを備える半導体素子の製造方法。

【請求項3】

前記第4から第6の工程は、同時に実行される、請求項2に記載の半導体素子の製造方法。

【請求項4】

前記第4から第6の工程において、前記熱プラズマジェットは、前記絶縁基板の面内方向へ走査されながら前記アモルファスシリコン膜、前記第1の二酸化シリコン膜および前記金属薄膜に照射される、請求項2または請求項3に記載の半導体素子の製造方法。

【請求項5】

前記第1の工程において、前記アモルファスシリコン膜は、400℃以下の温度で前記絶縁基板上に形成され、

前記第2の工程において、前記第1の二酸化シリコン膜は、350℃以下の温度で前記アモルファスシリコン膜に接して形成され、

前記第3の工程において、前記金属薄膜は、室温で前記第1の二酸化シリコン膜に接して形成され、

前記第4から第6の工程において、前記熱プラズマジェットは、室温で前記アモルファスシリコン膜、前記第1の二酸化シリコン膜および前記金属薄膜に照射され、

前記第7の工程において、前記第2の二酸化シリコン膜は、350℃以下の温度で前記アモルファスシリコン膜に接して形成される、請求項2から請求項4のいずれか1項に記載の半導体素子の製造方法。

【請求項1】

絶縁基板と、

前記絶縁基板上に形成された多結晶シリコン膜と、

前記多結晶シリコン膜に接して形成され、キャリアがトンネル可能な膜厚を有する第1の二酸化シリコン膜と、

前記第1の二酸化シリコン膜に接して形成され、白金またはニッケルからなる金属量子ドットと、

前記金属量子ドットを覆うように形成された第2の二酸化シリコン膜とを備え、

前記多結晶シリコン膜は、熱プラズマジェットをアモルファスシリコン膜に照射して製造された多結晶シリコン膜からなり、

前記第1の二酸化シリコン膜は、リモートプラズマを用いて堆積された二酸化シリコンに前記熱プラズマジェットを照射することによって製造された二酸化シリコンからなり、

前記金属量子ドットは、前記白金または前記ニッケルからなる金属薄膜に前記熱プラズマジェットを照射することによって製造された金属量子ドットからなる、半導体素子。

【請求項2】

絶縁基板上にアモルファスシリコン膜を形成する第1の工程と、

前記アモルファスシリコン膜に接して第1の二酸化シリコン膜を形成する第2の工程と、

前記第1の二酸化シリコン膜に接して白金またはニッケルからなる金属薄膜を形成する第3の工程と、

前記アモルファスシリコン膜に熱プラズマジェットを照射する第4の工程と、

前記第1の二酸化シリコン膜に熱プラズマジェットを照射する第5の工程と、

前記金属薄膜に熱プラズマジェットを照射する第6の工程と、

前記熱プラズマジェットの照射によって前記金属薄膜から形成された金属量子ドットを覆うように第2の二酸化シリコン膜を形成する第7の工程とを備える半導体素子の製造方法。

【請求項3】

前記第4から第6の工程は、同時に実行される、請求項2に記載の半導体素子の製造方法。

【請求項4】

前記第4から第6の工程において、前記熱プラズマジェットは、前記絶縁基板の面内方向へ走査されながら前記アモルファスシリコン膜、前記第1の二酸化シリコン膜および前記金属薄膜に照射される、請求項2または請求項3に記載の半導体素子の製造方法。

【請求項5】

前記第1の工程において、前記アモルファスシリコン膜は、400℃以下の温度で前記絶縁基板上に形成され、

前記第2の工程において、前記第1の二酸化シリコン膜は、350℃以下の温度で前記アモルファスシリコン膜に接して形成され、

前記第3の工程において、前記金属薄膜は、室温で前記第1の二酸化シリコン膜に接して形成され、

前記第4から第6の工程において、前記熱プラズマジェットは、室温で前記アモルファスシリコン膜、前記第1の二酸化シリコン膜および前記金属薄膜に照射され、

前記第7の工程において、前記第2の二酸化シリコン膜は、350℃以下の温度で前記アモルファスシリコン膜に接して形成される、請求項2から請求項4のいずれか1項に記載の半導体素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2012−89556(P2012−89556A)

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願番号】特願2010−232456(P2010−232456)

【出願日】平成22年10月15日(2010.10.15)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成22年 8月20日 http://jjap.jsap.jp/cgi−bin/getarticle?magazine=JJAP&volume=49&page=08JJ01を通じて発表

【出願人】(504136568)国立大学法人広島大学 (924)

【Fターム(参考)】

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願日】平成22年10月15日(2010.10.15)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 平成22年 8月20日 http://jjap.jsap.jp/cgi−bin/getarticle?magazine=JJAP&volume=49&page=08JJ01を通じて発表

【出願人】(504136568)国立大学法人広島大学 (924)

【Fターム(参考)】

[ Back to top ]