半導体素子および作製方法

【課題】ソフトエラー率を有意に低下させる半導体素子およびその作製方法に関する。

【解決手段】半導体基板(100)には、第1の型の不純物でドープされた第1ウェル領域(104)の下に第1の型の第1ドープ領域(102)がある。第1ウェル領域は、第1ドープ領域と電気的に接続されている。第1ウェル領域と第1ドープ領域(102)との間に分離領域(206)を形成する。分離領域は第2ウェル領域と電気接続されている。分離領域および第2ウェル領域は、第1の不純物型と反対の型の第2の不純物型でドープされている。前記方法はさらに、第1ウェル領域内および分離領域下に第2ドープ領域を形成する工程をさらに有し得る。第1の型の不純物を有する第3ドープ領域を、分離領域の上に形成することができる。

【解決手段】半導体基板(100)には、第1の型の不純物でドープされた第1ウェル領域(104)の下に第1の型の第1ドープ領域(102)がある。第1ウェル領域は、第1ドープ領域と電気的に接続されている。第1ウェル領域と第1ドープ領域(102)との間に分離領域(206)を形成する。分離領域は第2ウェル領域と電気接続されている。分離領域および第2ウェル領域は、第1の不純物型と反対の型の第2の不純物型でドープされている。前記方法はさらに、第1ウェル領域内および分離領域下に第2ドープ領域を形成する工程をさらに有し得る。第1の型の不純物を有する第3ドープ領域を、分離領域の上に形成することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体作製の分野に関する。より詳細には半導体回路におけるソフトエラー率を低減する方法および構造に関する。

【背景技術】

【0002】

半導体メモリ製品は、一般にソフトエラーと称されるデータ損失現象を受けやすい。半導体製品におけるソフトエラーは環境放射線によって生じ得る。この放射線はスタティック・ランダム・アクセス・メモリ(SRAM)またはダイナミック・ランダム・アクセス・メモリ(DRAM)素子などの半導体回路に蓄積された電荷量を変化させる。SRAMおよびDRAMなどの多くの集積回路において、集積回路の論理状態は極めて少量の蓄積電荷に依存している。各種発生源に由来する環境粒子放射線は、メモリ素子のセルまたは要素に蓄積された電荷量を変化させる場合がある。メモリ素子の保存ノードに蓄積された電荷量に伴ってソフトエラー率が変動することは明らかであろう。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平05−129429

【特許文献2】米国特許第5394007号明細書

【特許文献3】特開平10−199993号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

電源装置電圧およびメモリ素子のセルの大きさが小さくなるに連れて、それに応じて蓄積される電荷量が低下することで、ソフトエラー事象の確率が高くなる。従って、方法のコストや複雑さをほとんど大きくすることなく、ソフトエラー率をかなり低下させることができると考えられる方法および素子を実現することが非常に望ましいものと考えられる。

【課題を解決するための手段】

【0005】

本発明の一実施形態は、フィールド構造を有する半導体素子の製造方法において、第1ウェル領域(104)の下に第1ドープ領域(102)を有した半導体基板(100)に前記第1ウェル領域(104)を形成する工程であって、前記第1ウェル領域(104)および前記第1ドープ領域(102)はp型不純物及びn型不純物からなる群から選択された第1導電型の不純物を含有し、前記第1ウェル領域(104)が前記第1ドープ領域(102)と電気接続され、かつ、フィールド構造(106)が前記第1ウェル領域(104)のいずれかの側に形成されている、第1ウェル領域(104)を形成する工程と、

分離領域(206)を前記第1ウェル領域(104)と第1ドープ領域(102)との間に形成する工程であって、前記分離領域(206)は前記フィールド構造(106)の一部の下方まで伸びている、前記分離領域(206)を形成する工程と、

前記フィールド構造(106)の下方に第2ウェル領域(404)を形成する工程とを備え、

前記分離構造(206)は前記第2ウェル領域(404)に電気接続され、及び、前記分離領域(206)及び前記第2ウェル領域(404)は、前記第1導電型とは反対の第2導電型の不純物を含有していることを要旨とする。

【図面の簡単な説明】

【0006】

【図1】半導体基板の部分断面図。

【図2】図1の工程後の工程であって、半導体基板の特定の領域においてp型基板にn型分離層を導入する工程を示す部分断面図。

【図3】図2の工程後に第2p−ウェル不純物を半導体基板に注入する工程を示す部分断面図。

【図4】図3の工程後であって、上記不純物が導入された領域以外の半導体基板領域にn−ウェル不純物を導入する工程を示す部分断面図。

【図5】図4の後の工程であって、ゲート構造およびソース/ドレーン領域を有するトランジスタを半導体基板上に作製する工程を示す部分断面図。

【図6】図5の後の工程であって、保護電荷収集層を半導体基板に導入する工程を示す部分断面図。

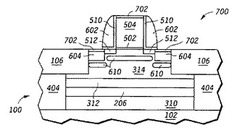

【図7】図6の後の工程であって、図5のトランジスタの動作領域およびゲート領域上にシリサイド領域を形成する工程を示す部分断面図。

【図8】半導体ウェハの部分平面図。

【図9】図8の半導体ウェハの部分断面図。

【発明を実施するための形態】

【0007】

以下において本発明を、実施例および添付の図面(それに限定されるものではない)によって説明するが、図面において同様の参照符号は類似の構成要素を示す。

当業者には、これら図中の構成要素は簡潔さおよび明瞭さを目的として描かれており、必ずしも大きさに比例して描かれているわけではないことは明らかである。例えば、図中の要素の一部の寸法を他の要素と比較して誇張して描いて、本発明の実施形態の理解を深めるようにすることができる。

【0008】

図面を参照する。図1には半導体ウェハ100の部分断面図を示す。半導体基板100は好適には、シリコンその他の好適な半導体材料の単結晶ウェハを有する。

ここに示した実施形態ではウェハ100には、基板102の第1ウェル領域(p−ウェル領域)104のいずれかの側にフィールド構造106が形成されたp型基板102の形態での第1ドープ領域がある。フィールド構造106には、浅型溝分離(STI)構造、局所シリコン酸化(LOCOS)構造、または半導体作製の分野の知識を有する者であれば熟知している他の何らかの好適な分離構造があっても良い。ここに描いた半導体基板102の実施形態はp型基板を示しているが、本発明は、n型基板を含む原材料を用いる方法での使用に好適なことも明らかであろう。

【0009】

図1にはさらに、半導体基板102の上側表面103上に形成された犠牲酸化物層108を示してある。犠牲酸化物層108は、その後の加工時における半導体基板102に対する損傷を低減するために形成する。犠牲酸化物層108は、熱酸化工程または低温成膜工程を用いて作製することができる。

【0010】

図2について説明すると、図1のウェハ100のさらなる加工を描いてある。ここに描いた実施形態では、n型不純物分布(分離領域)206を、第1の注入202によって、p−ウェル領域104と半導体基板102の間のウェハ100に導入する。好ましい実施形態では、第1の注入202は、約1E13〜10E13原子/cm2の導入量にて、約500〜1000KeVの範囲のエネルギーで行うリン注入とすることで、約1E17〜1E19原子/cm3の範囲のピーク不純物濃度を得るようにする。第1の注入202は、半導体基板102の上側表面(主表面)103の下に分離領域206ウェルを形成するのに好適である。本発明で想到されるn型分離領域206は、p−ウェル領域104からp型基板領域102を局所的に分離する上で役立つ。p−ウェル領域104からのp型基板102の分離は、環境放射線によって基板102で生じる(または他の機構によって発生)電子−ホール対が、ウェハ100のp−ウェル領域104に後に形成されるトランジスタと相互作用するのを防止する電気障壁を提供することで、ソフトエラー率を効果的に低下させる。

【0011】

図2に示したように、参照符号204で示した第2の注入を行って、n型不純物層206の近位にp型不純物層208を形成する。好ましい実施形態では、第2の注入204を、約1E13〜10E13原子/cm2の範囲の注入量にて、約100〜400KeVの範囲のエネルギーを用いるホウ素注入によって行う。さらに好ましくは第2の注入204では、注入エネルギー200KeVおよび注入量3.2E13原子/cm2を用いる。第1および第2の注入202および204は好ましくは、犠牲酸化物層108上の参照符号200によって示した注入マスクを形成してから行う。注入マスク200は、従来のフォトリソグラフィ工程で形成され、注入202および204が分離(磁場)領域106の下の基板102領域を通過するのを防止しながら、同時に不純物分布206および208をウェハ100のp−ウェル領域104の下に形成できるようにする。ウェハ100を利用してSRAMおよびDRAMなどのメモリ素子を作製する本発明の実施形態では、注入マスク200はさらに、第1および第2の注入202および204がメモリ素子の周辺部分に不純物分布を形成するのを防止しながら、ウェハ100のメモリアレー部分に不純物分布206および208を形成できるようにすることができる。図示した実施形態はp型基板102および第1および第2の注入202および204用の記載の不純物型を示したものであるが、基板102がn型基板を有することができ、第1および第2の注入202および204の不純物型を逆にして、第1の不純物分布206がp型不純物分布となり、第2の不純物分布がn型不純物分布となるようにすることができることは明らかであろう。さらに、本明細書で使用の型の不純物の範囲を広げて、元素の周期律表における同じ族の不純物からの他の不純物を含むことができる(すなわち、III族型不純物またはV族型不純物)。

【0012】

分離領域206を形成した後、注入マスク200をウェハ100から外し、ウェハ100を熱処理して(アニーリング)、半導体基板102を再結晶させ、第1および第2不純物分布206および208を活性化させる。好ましい実施形態では、ウェハ100に対して行う熱処理には、約5〜60秒の範囲の期間にわたり、約900〜1100℃の範囲の温度まで半導体基板102を加熱する急速熱アニール処理がある。熱処理工程の好ましい実施形態での急速熱アニーリングの短期間は、第1および第2不純物分布206および208を活性化させながら、不純物分布の実質的再分布を防止するのには十分である。別の実施形態においては熱処理には、従来の炉内アニーリングがあり得る。さらに別の実施形態では、アニーリングは、図4に関して後述するn−ウェル領域404の形成後まで遅らせることができる。この実施形態により、前記方法におけるアニーリングサイクルの総数が低減される効果がある。

【0013】

図3について説明すると、第2マスク301を、ウェハ100の犠牲酸化物108の上に形成する。第2マスク層301は、図2に関して説明した工程で第1マスク200が露出したものと、アレーでのウェハ100の実質的に同じ部分を露出させる。さらに第2マスク301は、素子の周辺部分(すなわち非アレー領域)でp−ウェル領域(不図示)を露出させる。第2マスク301を形成後、参照符号302、304、306および308によって示された一連の注入を、本発明の1実施形態で行って、各種p型不純物分布を基板102およびp−ウェル領域104に導入する。1実施形態では、第3の注入302を行って、参照符号310で示される第2p型不純物分布(ドープ領域)をp型基板102に導入する。好ましい実施形態では、第2p型不純物分布310を注入工程によって得て、第2p型分布310の深さがn型不純物分布206の深さより大きく、不純物分布310のピーク濃度が約1E17〜1E19原子/cm3の範囲となるようにする。p型不純物分布310によって、不純物分布206のピーク以下の分布ピークを形成して、n型分離領域206とp型基板102の間に形成されるp−n接合の電気障壁特性がさらに改善される。図3に示した第4の注入304によって、図2の第1不純物分布208と組み合わせて、分離領域分布206の深さより小さい基板102の上側表面103より低い深さにピーク濃度を有するp型不純物分布を生じる第3の不純物分布(ドープ領域)312を形成する(すなわち、第3の不純物分布312が分離領域206より上である)。好ましい実施形態では、第4の注入工程304は、約150〜250KeVの範囲の注入エネルギーを用いるホウ素注入である。その好ましい実施形態では、第4の注入工程304に使用される注入エネルギーは、図2に示した第2の注入工程204で用いる注入エネルギーにほぼ等しい。注入工程204および注入工程304で同じ注入エネルギーを用いることで、不純物分布206のピーク不純物濃度より高い位置にあるピーク不純物濃度を有する不純物分布312が生じ、好ましくは約1E17〜1E19原子/cm3である。その好ましい実施形態では、第2の注入工程204および第3の注入工程304から得られる不純物分布のピーク不純物濃度は約1E17〜1E19原子/cm3の範囲である。さらに好ましくはピーク不純物濃度は約1E18原子/cm3である。第5および第6の注入工程306および308は好適には、p型不純物分布の比較的低いエネルギー注入によって行って、ウェハ100のp−ウェル領域104にp−ウェル不純物分布314を生じさせる。その好ましい実施形態では、第5の注入306は、約50〜150KeVの範囲のエネルギーおよび約2E12〜3E12原子/cm2の範囲の注入量を用いるホウ素注入である。さらに好ましくは、第5の注入306では、約100KeVの注入エネルギーおよび約2.5E12原子/cm2の注入量を用いる。図示した実施形態では、約25〜75KeVの範囲のエネルギーおよび約2E12〜3E12原子/cm2の注入量でのホウ素注入を行う第6の注入308によって、p−ウェル不純物分布314をさらに形成する。この好ましい実施形態では、第6の注入308でのエネルギーは約50KeVであり、注入量は約2.5E12原子/cm2である。この実施形態では、第5および第6の注入306および308の組み合わせによって、ウェハ100の上側表面103から約250ナノメートルの深さまで広がる比較的均一なp−ウェル不純物分布314が得られる。

【0014】

図4について説明すると、第3のマスク工程を用いて、ウェハ100の犠牲酸化物層108上に第3のマスク400を形成する。第3のマスク400は、n型不純物分布を導入してウェハ100のn−ウェル領域404を形成する基板102の領域を画定するものである。好ましい実施形態では、n−ウェル領域404の各種部分が、分離領域206を介して互いに電気的に接続されている。第2の不純物分布206のいずれかの側でn−ウェル領域404を組み合わせることで、p−基板102から各p−ウェル領域104を局所的に分離する。p−ウェル104のp−基板102からの局所分離によって、環境放射線によって基板102で発生する電子−ホール対がp−ウェル領域104を通過し、そこに形成されている素子の動作に影響するのを実質的に防止する有効な障壁が得られる。p−ウェル領域104はウェハ100のアレー部分においてp−基板領域102から局所的に分離されるが、各p−ウェル領域104はp−ウェルコンタクト(図4では不図示)を介してp−基板領域102に電気的に接続されている。

【0015】

図8について説明すると、ウェハ100の一部の平面図であり、n−ウェル領域404とp−ウェル不純物分布314の間に形成されたp−ウェルコンタクト領域800を示している。コンタクト領域800以外のウェハ100のいずれの領域においても、n型不純物領域206はp−ウェル不純物分布314の下に広がっている。しかしながら領域800では、第2の型の不純物分布206がウェハ100に進入するのは防止されている。n型不純物分布206がないと、pウェル不純物分布314がp型基板102と電気的に接続されることは明らかであろう。本発明におけるp−ウェル領域314とp型基板102との間のこの電気的接続は、各p−ウェル不純物分布314の直列抵抗を低下させる効果があり、各p−ウェル不純物分布314を電気的に接地させる機構を提供するものである。

【0016】

図9の部分断面図について説明すると、n型不純物分布206が形成されるのを防止することで、p−ウェル不純物分布314がp型基板102に電気的に接続され得るウィンドウを、領域800が画定しているのがわかる。この好ましい実施形態では領域800は、図2に示した第1マスク200によって画定されている。すなわち、第1マスク200には、フォトレジストによって第1および第2の注入202および204が下層の基板に進入できない領域800がある。

【0017】

図4について説明すると、n型不純物分布206のいずれかの側にn−ウェル領域を形成する以外に、注入402によって、半導体ウェハ100のアレー部分および周辺部分の両方に、p型トランジスタ用のn−ウェル領域が形成される。別の実施形態では、別の光工程(図示せず)を用いて、素子100の周辺部分でのn−ウェル形成を制御するための別の注入工程を提供することができる。

【0018】

次に図5について説明すると、図4に示した注入工程402後のさらなる加工を図示したウェハ100の部分断面図を描いてある。図4での注入402後、マスク層400および犠牲酸化物層108をウェハ100から除去する。その後、熱酸化工程を行って、ウェハ100の上側表面にゲート酸化物502を形成する。代表的には、ゲート酸化物502の酸化物の厚さは約20〜75Åの範囲である。ゲート酸化物502を形成した後、ゲート構造504をゲート酸化物502上に形成する。ゲート構造504は、ウェハ100のp−ウェル領域104におけるソース/ドレーン領域508からのチャンネル領域506の境界を画定している。1実施形態では、ゲート構造504はポリシリコンから構成される。別の形態ではゲート構造504は、耐熱金属およびその合金などの金属含有材料を用いて形成することができる。ゲート構造504を形成するのに用いる層の成膜層後、マスク形成およびエッチング工程を行って、ゲート構造504をパターニングする。ゲート構造504を形成した後、再酸化工程を行って、ゲート構造504の外側領域上に誘電体材料の狭い領域(参照番号510によって示している)を形成する。ゲート構造504の再酸化後、注入マスクとしてゲート構造504を用いてソース/ドレーン拡張注入を行って、チャンネル領域506のいずれかの側にソース/ドレーン拡張領域512を形成する。好ましい実施形態では、ソース/ドレーン拡張領域512の形成に使用されるソース/ドレーン拡張注入は、リンまたはヒ素などのn型不純物注入を用いて行う。1実施形態では、ハロゲン注入を行って、p−ウェル領域104におけるソース/ドレーン領域508に比較的軽くドープしたp型不純物分布を導入することができる。

【0019】

図6について説明すると、スペーサー構造602を、ゲート構造504の側壁に形成する。1実施形態では、スペーサー構造602の形成は、窒化ケイ素の化学蒸着とそれに続く異方性エッチング工程によって行う。スペーサー構造602の形成後、ソース/ドレーン不純物分布604を、参照符号606によって図6で示したソース/ドレーン注入により、p−ウェル領域104のソース/ドレーン領域508に導入する。好ましくは、ソース/ドレーン注入606では、高ドープソース/ドレーン領域604(すなわち、ドーピング濃度が約1E19原子/cm3を超えるソース/ドレーン領域)を形成するだけの注入量でのn型注入を行う。

【0020】

1実施形態によれば、保護電荷収集層610を形成することで、ソフトエラー率をさらに低下させることができる。電荷収集層610を、本発明の実施形態と併用して、あるいは従来の半導体素子構造と併用して、ソフトエラー率を低下させることができる。保護電荷収集層610は、参照符号608によって示した保護電荷収集層注入によって、p−ウェル領域314に導入する。保護電荷収集層610は好ましくは、環境放射線によって発生する電子−ホール対の間接再結合を促進するp−ウェル領域104での不純物分布を有する。1実施形態では、保護電荷収集層(保護電荷再結合領域とも称する)610には、ゲート構造504の下の第1部分およびソース/ドレーン領域512下の第2部分がある。この実施形態では、ウェハ100の上側表面103の下の保護電荷収集層610における第1部分の深さは、第2部分の深さより小さい。1実施形態では、保護電荷収集層610は、アルゴン、シリコン、ゲルマニウム、窒素、酸素その他の再結合を促進する上で好適な注入化学種などの不純物を注入することで作製される。保護電荷収集層610注入の好適な注入量は、約1E12〜1E15原子/cm2の範囲である。1実施形態によれば、保護電荷収集層注入608は、約1E13〜5E13原子/cm2の範囲の注入量および約200〜800KeVの範囲のエネルギーでのアルゴン注入を用いる。

【0021】

1実施形態によれば、急速熱アニーリングを、ソース/ドレーン拡張領域512の形成後およびソース/ドレーン領域604の形成後に行う。ある具体的な実施形態では、ソース/ドレーン拡張領域512の急速熱アニーリングは、約950℃の温度での急速熱アニーリングによって行い、ソース/ドレーン領域604の急速熱アニーリングは好適には、約1025℃のアニーリングで行う。ソース/ドレーン拡張領域512およびソース/ドレーン不純物分布604の急速熱アニーリングは、相当する不純物分布を活性化し、好ましくはp−ウェル不純物分布314の大幅な再分布を防止するだけの短いアニーリング時間で行う。1実施形態では、ソース/ドレーン不純物分布604の急速熱アニーリングの前に、保護電荷収集層注入608を行うことができる。この実施形態では、保護電荷収集層注入608によって生じる格子損傷を、急速熱アニーリング工程によってアニールすることができる。別の実施形態では、保護電荷収集層注入608をソース/ドレーン領域604の急速熱アニーリング後に行って、保護電荷収集層610の大幅な再分布を防止することができる。

【0022】

図7について説明すると、ウェハ100のさらなる加工を示してある。図7において、ウェハ全面の上にコバルトなどの導電性材料を成膜し、その後比較的低温(すなわち、約400〜600℃の範囲の温度)でのアニーリングを行って、ソース/ドレーン不純物分布604およびゲート構造504の露出部分をケイ化する。シリサイドのアニーリング後、酸化物または窒化物などの誘電体材料と接触している成膜金属部分を、従来のエッチング法を用いて除去する。ケイ素と接触している導電体材料の部分は、アニーリング工程時にそのケイ素と結合して、エッチング工程の影響を受けないCoSiなどの導電性材料を形成する。その後、約700〜900℃の温度での別の急速熱アニーリング工程を行う。シリサイド形成後、図1〜7に示した半導体作製方法によって、ソフトエラーソフトエラー回避性の高い素子700が形成される。ウェハ100のp型基板102からp−ウェル領域104を局所的に分離することで、基板102に発生する電子−ホール対を、素子700のp−ウェル領域104およびソース/ドレーン領域から電気的に分離する。さらに、p−ウェル領域104で発生した電子−ホール対の間接再結合を促進する保護電荷収集層610を導入することで、ソフトエラー率のさらなる低下が得られる。保護電荷収集層610の結合およびn−ウェル/n型不純物分布構造の分離によって、従来法で形成される半導体素子よりソフトエラー率がかなり低くなる。

【0023】

上記の明細書では、本発明について具体的な実施形態を参照しながら説明した。しかしながら当業者であれば、添付の特許請求の範囲に記載の本発明の範囲から逸脱しない限りにおいて、各種の修正および変更が可能であることは明らかである。従って、明細書および図は限定的な意味ではなく例示的な意味のものと理解すべきであり、そのような修正はいずれも、本発明の範囲に含まれる。

【0024】

以上においては、具体的な実施形態に関して、効果、他の利点および問題解決について説明した。しかしながら、効果、利点および問題解決ならびに何らかの効果、利点もしくは解決を生じさせたりさらに顕著なものとし得る要素に関しては、いずれかまたは全ての特許請求の範囲の必須、必要または本質的な特徴もしくは要素と見なすべきではない。本明細書で使用する場合に、「含む」、「包含」または他の何らかのそれらの派生表現は、挙げられた要素を含む工程、方法、製造品または装置がその要素のみを含むのではなく、そのような工程、方法、製造品または装置に明瞭に挙げられたり、それらに固有のものではない他の要素を含み得るという形で、非排他的包含を網羅するものである。

【技術分野】

【0001】

本発明は、半導体作製の分野に関する。より詳細には半導体回路におけるソフトエラー率を低減する方法および構造に関する。

【背景技術】

【0002】

半導体メモリ製品は、一般にソフトエラーと称されるデータ損失現象を受けやすい。半導体製品におけるソフトエラーは環境放射線によって生じ得る。この放射線はスタティック・ランダム・アクセス・メモリ(SRAM)またはダイナミック・ランダム・アクセス・メモリ(DRAM)素子などの半導体回路に蓄積された電荷量を変化させる。SRAMおよびDRAMなどの多くの集積回路において、集積回路の論理状態は極めて少量の蓄積電荷に依存している。各種発生源に由来する環境粒子放射線は、メモリ素子のセルまたは要素に蓄積された電荷量を変化させる場合がある。メモリ素子の保存ノードに蓄積された電荷量に伴ってソフトエラー率が変動することは明らかであろう。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平05−129429

【特許文献2】米国特許第5394007号明細書

【特許文献3】特開平10−199993号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

電源装置電圧およびメモリ素子のセルの大きさが小さくなるに連れて、それに応じて蓄積される電荷量が低下することで、ソフトエラー事象の確率が高くなる。従って、方法のコストや複雑さをほとんど大きくすることなく、ソフトエラー率をかなり低下させることができると考えられる方法および素子を実現することが非常に望ましいものと考えられる。

【課題を解決するための手段】

【0005】

本発明の一実施形態は、フィールド構造を有する半導体素子の製造方法において、第1ウェル領域(104)の下に第1ドープ領域(102)を有した半導体基板(100)に前記第1ウェル領域(104)を形成する工程であって、前記第1ウェル領域(104)および前記第1ドープ領域(102)はp型不純物及びn型不純物からなる群から選択された第1導電型の不純物を含有し、前記第1ウェル領域(104)が前記第1ドープ領域(102)と電気接続され、かつ、フィールド構造(106)が前記第1ウェル領域(104)のいずれかの側に形成されている、第1ウェル領域(104)を形成する工程と、

分離領域(206)を前記第1ウェル領域(104)と第1ドープ領域(102)との間に形成する工程であって、前記分離領域(206)は前記フィールド構造(106)の一部の下方まで伸びている、前記分離領域(206)を形成する工程と、

前記フィールド構造(106)の下方に第2ウェル領域(404)を形成する工程とを備え、

前記分離構造(206)は前記第2ウェル領域(404)に電気接続され、及び、前記分離領域(206)及び前記第2ウェル領域(404)は、前記第1導電型とは反対の第2導電型の不純物を含有していることを要旨とする。

【図面の簡単な説明】

【0006】

【図1】半導体基板の部分断面図。

【図2】図1の工程後の工程であって、半導体基板の特定の領域においてp型基板にn型分離層を導入する工程を示す部分断面図。

【図3】図2の工程後に第2p−ウェル不純物を半導体基板に注入する工程を示す部分断面図。

【図4】図3の工程後であって、上記不純物が導入された領域以外の半導体基板領域にn−ウェル不純物を導入する工程を示す部分断面図。

【図5】図4の後の工程であって、ゲート構造およびソース/ドレーン領域を有するトランジスタを半導体基板上に作製する工程を示す部分断面図。

【図6】図5の後の工程であって、保護電荷収集層を半導体基板に導入する工程を示す部分断面図。

【図7】図6の後の工程であって、図5のトランジスタの動作領域およびゲート領域上にシリサイド領域を形成する工程を示す部分断面図。

【図8】半導体ウェハの部分平面図。

【図9】図8の半導体ウェハの部分断面図。

【発明を実施するための形態】

【0007】

以下において本発明を、実施例および添付の図面(それに限定されるものではない)によって説明するが、図面において同様の参照符号は類似の構成要素を示す。

当業者には、これら図中の構成要素は簡潔さおよび明瞭さを目的として描かれており、必ずしも大きさに比例して描かれているわけではないことは明らかである。例えば、図中の要素の一部の寸法を他の要素と比較して誇張して描いて、本発明の実施形態の理解を深めるようにすることができる。

【0008】

図面を参照する。図1には半導体ウェハ100の部分断面図を示す。半導体基板100は好適には、シリコンその他の好適な半導体材料の単結晶ウェハを有する。

ここに示した実施形態ではウェハ100には、基板102の第1ウェル領域(p−ウェル領域)104のいずれかの側にフィールド構造106が形成されたp型基板102の形態での第1ドープ領域がある。フィールド構造106には、浅型溝分離(STI)構造、局所シリコン酸化(LOCOS)構造、または半導体作製の分野の知識を有する者であれば熟知している他の何らかの好適な分離構造があっても良い。ここに描いた半導体基板102の実施形態はp型基板を示しているが、本発明は、n型基板を含む原材料を用いる方法での使用に好適なことも明らかであろう。

【0009】

図1にはさらに、半導体基板102の上側表面103上に形成された犠牲酸化物層108を示してある。犠牲酸化物層108は、その後の加工時における半導体基板102に対する損傷を低減するために形成する。犠牲酸化物層108は、熱酸化工程または低温成膜工程を用いて作製することができる。

【0010】

図2について説明すると、図1のウェハ100のさらなる加工を描いてある。ここに描いた実施形態では、n型不純物分布(分離領域)206を、第1の注入202によって、p−ウェル領域104と半導体基板102の間のウェハ100に導入する。好ましい実施形態では、第1の注入202は、約1E13〜10E13原子/cm2の導入量にて、約500〜1000KeVの範囲のエネルギーで行うリン注入とすることで、約1E17〜1E19原子/cm3の範囲のピーク不純物濃度を得るようにする。第1の注入202は、半導体基板102の上側表面(主表面)103の下に分離領域206ウェルを形成するのに好適である。本発明で想到されるn型分離領域206は、p−ウェル領域104からp型基板領域102を局所的に分離する上で役立つ。p−ウェル領域104からのp型基板102の分離は、環境放射線によって基板102で生じる(または他の機構によって発生)電子−ホール対が、ウェハ100のp−ウェル領域104に後に形成されるトランジスタと相互作用するのを防止する電気障壁を提供することで、ソフトエラー率を効果的に低下させる。

【0011】

図2に示したように、参照符号204で示した第2の注入を行って、n型不純物層206の近位にp型不純物層208を形成する。好ましい実施形態では、第2の注入204を、約1E13〜10E13原子/cm2の範囲の注入量にて、約100〜400KeVの範囲のエネルギーを用いるホウ素注入によって行う。さらに好ましくは第2の注入204では、注入エネルギー200KeVおよび注入量3.2E13原子/cm2を用いる。第1および第2の注入202および204は好ましくは、犠牲酸化物層108上の参照符号200によって示した注入マスクを形成してから行う。注入マスク200は、従来のフォトリソグラフィ工程で形成され、注入202および204が分離(磁場)領域106の下の基板102領域を通過するのを防止しながら、同時に不純物分布206および208をウェハ100のp−ウェル領域104の下に形成できるようにする。ウェハ100を利用してSRAMおよびDRAMなどのメモリ素子を作製する本発明の実施形態では、注入マスク200はさらに、第1および第2の注入202および204がメモリ素子の周辺部分に不純物分布を形成するのを防止しながら、ウェハ100のメモリアレー部分に不純物分布206および208を形成できるようにすることができる。図示した実施形態はp型基板102および第1および第2の注入202および204用の記載の不純物型を示したものであるが、基板102がn型基板を有することができ、第1および第2の注入202および204の不純物型を逆にして、第1の不純物分布206がp型不純物分布となり、第2の不純物分布がn型不純物分布となるようにすることができることは明らかであろう。さらに、本明細書で使用の型の不純物の範囲を広げて、元素の周期律表における同じ族の不純物からの他の不純物を含むことができる(すなわち、III族型不純物またはV族型不純物)。

【0012】

分離領域206を形成した後、注入マスク200をウェハ100から外し、ウェハ100を熱処理して(アニーリング)、半導体基板102を再結晶させ、第1および第2不純物分布206および208を活性化させる。好ましい実施形態では、ウェハ100に対して行う熱処理には、約5〜60秒の範囲の期間にわたり、約900〜1100℃の範囲の温度まで半導体基板102を加熱する急速熱アニール処理がある。熱処理工程の好ましい実施形態での急速熱アニーリングの短期間は、第1および第2不純物分布206および208を活性化させながら、不純物分布の実質的再分布を防止するのには十分である。別の実施形態においては熱処理には、従来の炉内アニーリングがあり得る。さらに別の実施形態では、アニーリングは、図4に関して後述するn−ウェル領域404の形成後まで遅らせることができる。この実施形態により、前記方法におけるアニーリングサイクルの総数が低減される効果がある。

【0013】

図3について説明すると、第2マスク301を、ウェハ100の犠牲酸化物108の上に形成する。第2マスク層301は、図2に関して説明した工程で第1マスク200が露出したものと、アレーでのウェハ100の実質的に同じ部分を露出させる。さらに第2マスク301は、素子の周辺部分(すなわち非アレー領域)でp−ウェル領域(不図示)を露出させる。第2マスク301を形成後、参照符号302、304、306および308によって示された一連の注入を、本発明の1実施形態で行って、各種p型不純物分布を基板102およびp−ウェル領域104に導入する。1実施形態では、第3の注入302を行って、参照符号310で示される第2p型不純物分布(ドープ領域)をp型基板102に導入する。好ましい実施形態では、第2p型不純物分布310を注入工程によって得て、第2p型分布310の深さがn型不純物分布206の深さより大きく、不純物分布310のピーク濃度が約1E17〜1E19原子/cm3の範囲となるようにする。p型不純物分布310によって、不純物分布206のピーク以下の分布ピークを形成して、n型分離領域206とp型基板102の間に形成されるp−n接合の電気障壁特性がさらに改善される。図3に示した第4の注入304によって、図2の第1不純物分布208と組み合わせて、分離領域分布206の深さより小さい基板102の上側表面103より低い深さにピーク濃度を有するp型不純物分布を生じる第3の不純物分布(ドープ領域)312を形成する(すなわち、第3の不純物分布312が分離領域206より上である)。好ましい実施形態では、第4の注入工程304は、約150〜250KeVの範囲の注入エネルギーを用いるホウ素注入である。その好ましい実施形態では、第4の注入工程304に使用される注入エネルギーは、図2に示した第2の注入工程204で用いる注入エネルギーにほぼ等しい。注入工程204および注入工程304で同じ注入エネルギーを用いることで、不純物分布206のピーク不純物濃度より高い位置にあるピーク不純物濃度を有する不純物分布312が生じ、好ましくは約1E17〜1E19原子/cm3である。その好ましい実施形態では、第2の注入工程204および第3の注入工程304から得られる不純物分布のピーク不純物濃度は約1E17〜1E19原子/cm3の範囲である。さらに好ましくはピーク不純物濃度は約1E18原子/cm3である。第5および第6の注入工程306および308は好適には、p型不純物分布の比較的低いエネルギー注入によって行って、ウェハ100のp−ウェル領域104にp−ウェル不純物分布314を生じさせる。その好ましい実施形態では、第5の注入306は、約50〜150KeVの範囲のエネルギーおよび約2E12〜3E12原子/cm2の範囲の注入量を用いるホウ素注入である。さらに好ましくは、第5の注入306では、約100KeVの注入エネルギーおよび約2.5E12原子/cm2の注入量を用いる。図示した実施形態では、約25〜75KeVの範囲のエネルギーおよび約2E12〜3E12原子/cm2の注入量でのホウ素注入を行う第6の注入308によって、p−ウェル不純物分布314をさらに形成する。この好ましい実施形態では、第6の注入308でのエネルギーは約50KeVであり、注入量は約2.5E12原子/cm2である。この実施形態では、第5および第6の注入306および308の組み合わせによって、ウェハ100の上側表面103から約250ナノメートルの深さまで広がる比較的均一なp−ウェル不純物分布314が得られる。

【0014】

図4について説明すると、第3のマスク工程を用いて、ウェハ100の犠牲酸化物層108上に第3のマスク400を形成する。第3のマスク400は、n型不純物分布を導入してウェハ100のn−ウェル領域404を形成する基板102の領域を画定するものである。好ましい実施形態では、n−ウェル領域404の各種部分が、分離領域206を介して互いに電気的に接続されている。第2の不純物分布206のいずれかの側でn−ウェル領域404を組み合わせることで、p−基板102から各p−ウェル領域104を局所的に分離する。p−ウェル104のp−基板102からの局所分離によって、環境放射線によって基板102で発生する電子−ホール対がp−ウェル領域104を通過し、そこに形成されている素子の動作に影響するのを実質的に防止する有効な障壁が得られる。p−ウェル領域104はウェハ100のアレー部分においてp−基板領域102から局所的に分離されるが、各p−ウェル領域104はp−ウェルコンタクト(図4では不図示)を介してp−基板領域102に電気的に接続されている。

【0015】

図8について説明すると、ウェハ100の一部の平面図であり、n−ウェル領域404とp−ウェル不純物分布314の間に形成されたp−ウェルコンタクト領域800を示している。コンタクト領域800以外のウェハ100のいずれの領域においても、n型不純物領域206はp−ウェル不純物分布314の下に広がっている。しかしながら領域800では、第2の型の不純物分布206がウェハ100に進入するのは防止されている。n型不純物分布206がないと、pウェル不純物分布314がp型基板102と電気的に接続されることは明らかであろう。本発明におけるp−ウェル領域314とp型基板102との間のこの電気的接続は、各p−ウェル不純物分布314の直列抵抗を低下させる効果があり、各p−ウェル不純物分布314を電気的に接地させる機構を提供するものである。

【0016】

図9の部分断面図について説明すると、n型不純物分布206が形成されるのを防止することで、p−ウェル不純物分布314がp型基板102に電気的に接続され得るウィンドウを、領域800が画定しているのがわかる。この好ましい実施形態では領域800は、図2に示した第1マスク200によって画定されている。すなわち、第1マスク200には、フォトレジストによって第1および第2の注入202および204が下層の基板に進入できない領域800がある。

【0017】

図4について説明すると、n型不純物分布206のいずれかの側にn−ウェル領域を形成する以外に、注入402によって、半導体ウェハ100のアレー部分および周辺部分の両方に、p型トランジスタ用のn−ウェル領域が形成される。別の実施形態では、別の光工程(図示せず)を用いて、素子100の周辺部分でのn−ウェル形成を制御するための別の注入工程を提供することができる。

【0018】

次に図5について説明すると、図4に示した注入工程402後のさらなる加工を図示したウェハ100の部分断面図を描いてある。図4での注入402後、マスク層400および犠牲酸化物層108をウェハ100から除去する。その後、熱酸化工程を行って、ウェハ100の上側表面にゲート酸化物502を形成する。代表的には、ゲート酸化物502の酸化物の厚さは約20〜75Åの範囲である。ゲート酸化物502を形成した後、ゲート構造504をゲート酸化物502上に形成する。ゲート構造504は、ウェハ100のp−ウェル領域104におけるソース/ドレーン領域508からのチャンネル領域506の境界を画定している。1実施形態では、ゲート構造504はポリシリコンから構成される。別の形態ではゲート構造504は、耐熱金属およびその合金などの金属含有材料を用いて形成することができる。ゲート構造504を形成するのに用いる層の成膜層後、マスク形成およびエッチング工程を行って、ゲート構造504をパターニングする。ゲート構造504を形成した後、再酸化工程を行って、ゲート構造504の外側領域上に誘電体材料の狭い領域(参照番号510によって示している)を形成する。ゲート構造504の再酸化後、注入マスクとしてゲート構造504を用いてソース/ドレーン拡張注入を行って、チャンネル領域506のいずれかの側にソース/ドレーン拡張領域512を形成する。好ましい実施形態では、ソース/ドレーン拡張領域512の形成に使用されるソース/ドレーン拡張注入は、リンまたはヒ素などのn型不純物注入を用いて行う。1実施形態では、ハロゲン注入を行って、p−ウェル領域104におけるソース/ドレーン領域508に比較的軽くドープしたp型不純物分布を導入することができる。

【0019】

図6について説明すると、スペーサー構造602を、ゲート構造504の側壁に形成する。1実施形態では、スペーサー構造602の形成は、窒化ケイ素の化学蒸着とそれに続く異方性エッチング工程によって行う。スペーサー構造602の形成後、ソース/ドレーン不純物分布604を、参照符号606によって図6で示したソース/ドレーン注入により、p−ウェル領域104のソース/ドレーン領域508に導入する。好ましくは、ソース/ドレーン注入606では、高ドープソース/ドレーン領域604(すなわち、ドーピング濃度が約1E19原子/cm3を超えるソース/ドレーン領域)を形成するだけの注入量でのn型注入を行う。

【0020】

1実施形態によれば、保護電荷収集層610を形成することで、ソフトエラー率をさらに低下させることができる。電荷収集層610を、本発明の実施形態と併用して、あるいは従来の半導体素子構造と併用して、ソフトエラー率を低下させることができる。保護電荷収集層610は、参照符号608によって示した保護電荷収集層注入によって、p−ウェル領域314に導入する。保護電荷収集層610は好ましくは、環境放射線によって発生する電子−ホール対の間接再結合を促進するp−ウェル領域104での不純物分布を有する。1実施形態では、保護電荷収集層(保護電荷再結合領域とも称する)610には、ゲート構造504の下の第1部分およびソース/ドレーン領域512下の第2部分がある。この実施形態では、ウェハ100の上側表面103の下の保護電荷収集層610における第1部分の深さは、第2部分の深さより小さい。1実施形態では、保護電荷収集層610は、アルゴン、シリコン、ゲルマニウム、窒素、酸素その他の再結合を促進する上で好適な注入化学種などの不純物を注入することで作製される。保護電荷収集層610注入の好適な注入量は、約1E12〜1E15原子/cm2の範囲である。1実施形態によれば、保護電荷収集層注入608は、約1E13〜5E13原子/cm2の範囲の注入量および約200〜800KeVの範囲のエネルギーでのアルゴン注入を用いる。

【0021】

1実施形態によれば、急速熱アニーリングを、ソース/ドレーン拡張領域512の形成後およびソース/ドレーン領域604の形成後に行う。ある具体的な実施形態では、ソース/ドレーン拡張領域512の急速熱アニーリングは、約950℃の温度での急速熱アニーリングによって行い、ソース/ドレーン領域604の急速熱アニーリングは好適には、約1025℃のアニーリングで行う。ソース/ドレーン拡張領域512およびソース/ドレーン不純物分布604の急速熱アニーリングは、相当する不純物分布を活性化し、好ましくはp−ウェル不純物分布314の大幅な再分布を防止するだけの短いアニーリング時間で行う。1実施形態では、ソース/ドレーン不純物分布604の急速熱アニーリングの前に、保護電荷収集層注入608を行うことができる。この実施形態では、保護電荷収集層注入608によって生じる格子損傷を、急速熱アニーリング工程によってアニールすることができる。別の実施形態では、保護電荷収集層注入608をソース/ドレーン領域604の急速熱アニーリング後に行って、保護電荷収集層610の大幅な再分布を防止することができる。

【0022】

図7について説明すると、ウェハ100のさらなる加工を示してある。図7において、ウェハ全面の上にコバルトなどの導電性材料を成膜し、その後比較的低温(すなわち、約400〜600℃の範囲の温度)でのアニーリングを行って、ソース/ドレーン不純物分布604およびゲート構造504の露出部分をケイ化する。シリサイドのアニーリング後、酸化物または窒化物などの誘電体材料と接触している成膜金属部分を、従来のエッチング法を用いて除去する。ケイ素と接触している導電体材料の部分は、アニーリング工程時にそのケイ素と結合して、エッチング工程の影響を受けないCoSiなどの導電性材料を形成する。その後、約700〜900℃の温度での別の急速熱アニーリング工程を行う。シリサイド形成後、図1〜7に示した半導体作製方法によって、ソフトエラーソフトエラー回避性の高い素子700が形成される。ウェハ100のp型基板102からp−ウェル領域104を局所的に分離することで、基板102に発生する電子−ホール対を、素子700のp−ウェル領域104およびソース/ドレーン領域から電気的に分離する。さらに、p−ウェル領域104で発生した電子−ホール対の間接再結合を促進する保護電荷収集層610を導入することで、ソフトエラー率のさらなる低下が得られる。保護電荷収集層610の結合およびn−ウェル/n型不純物分布構造の分離によって、従来法で形成される半導体素子よりソフトエラー率がかなり低くなる。

【0023】

上記の明細書では、本発明について具体的な実施形態を参照しながら説明した。しかしながら当業者であれば、添付の特許請求の範囲に記載の本発明の範囲から逸脱しない限りにおいて、各種の修正および変更が可能であることは明らかである。従って、明細書および図は限定的な意味ではなく例示的な意味のものと理解すべきであり、そのような修正はいずれも、本発明の範囲に含まれる。

【0024】

以上においては、具体的な実施形態に関して、効果、他の利点および問題解決について説明した。しかしながら、効果、利点および問題解決ならびに何らかの効果、利点もしくは解決を生じさせたりさらに顕著なものとし得る要素に関しては、いずれかまたは全ての特許請求の範囲の必須、必要または本質的な特徴もしくは要素と見なすべきではない。本明細書で使用する場合に、「含む」、「包含」または他の何らかのそれらの派生表現は、挙げられた要素を含む工程、方法、製造品または装置がその要素のみを含むのではなく、そのような工程、方法、製造品または装置に明瞭に挙げられたり、それらに固有のものではない他の要素を含み得るという形で、非排他的包含を網羅するものである。

【特許請求の範囲】

【請求項1】

第1ウェル領域(104)の下に第1ドープ領域(102)を有した半導体基板(100)に前記第1ウェル領域(104)を形成する工程であって、前記第1ウェル領域(104)および前記第1ドープ領域(102)はp型不純物及びn型不純物からなる群から選択された第1導電型の不純物を含有し、前記第1ウェル領域(104)が前記第1ドープ領域(102)と電気接続され、かつ、フィールド構造(106)が前記第1ウェル領域(104)のいずれかの側に形成されている、第1ウェル領域(104)を形成する工程と、

分離領域(206)を前記第1ウェル領域(104)と第1ドープ領域(102)との間に形成する工程であって、前記分離領域(206)は前記フィールド構造(106)の一部の下方まで伸びている、前記分離領域(206)を形成する工程と、

前記フィールド構造(106)の下方に第2ウェル領域(404)を形成する工程とを備え、

前記分離構造(206)は前記第2ウェル領域(404)に電気接続され、及び、前記分離領域(206)及び前記第2ウェル領域(404)は、前記第1導電型とは反対の第2導電型の不純物を含有している、フィールド構造を有する半導体素子の製造方法。

【請求項2】

前記分離領域(206)のピーク不純物濃度が約1E17〜1E19原子/cm3の範囲にあり、

前記第2ウェル領域(404)のピーク不純物濃度が約1E17〜1E19原子/cm3の範囲にあり、前記方法は、

前記分離領域(206)と第1ドープ領域(102)との間に第2ドープ領域(310)を形成する工程であって、前記第2ドープ領域(310)は前記第1導電型の不純物を含有し、前記第2ドープ領域(310)のピーク濃度が約1E17〜1E19原子/cm3の範囲にある工程と、

前記分離領域(206)の上に第3ドープ領域(312)を形成する工程であって、前記第3ドープ領域(312)は前記第1導電型の不純物を含有し、前記第3ドープ領域(312)のピーク濃度が約1E17〜1E19原子/cm3の範囲にある工程とをさらに備える、請求項1に記載の方法。

【請求項3】

前記半導体基板(100)上にゲート構造(504)を形成する工程と、

前記ゲート構造(504)に隣接したソース/ドレーン領域(604)を形成する工程と、

前記ゲート構造(504)および前記ソース/ドレーン領域(604)の下に保護電荷再結合領域(610)を形成する工程とをさらに備える、請求項1に記載の方法。

【請求項4】

第1ウェル領域(104)の下に第1ドープ領域(102)を有した半導体基板(100)にある第1ウェル領域(104)と、前記第1ウェル領域(104)および前記第1ドープ領域(102)はp型不純物およびn型不純物からなる群から選択される第1導電型の不純物を含有することと、前記第1ウェル領域(104)は前記第1ドープ領域(102)と電気接続されていることと、

前記第1ウェル領域(104)と前記第1ドープ領域(102)との間にあり、前記フィールド構造の一部の下方まで伸びている分離領域(206)と、

フィールド構造(106)の下方の第2ウェル領域(404)とを備え、前記分離領域(206)は前記第2ウェル領域(404)に電気接続され、前記分離領域(206)および前記第2ウェル領域(404)は第2導電型の不純物を含有し、前記第2の型の不純物は前記第1の型の不純物とは反対である、フィールド構造を有した半導体素子。

【請求項1】

第1ウェル領域(104)の下に第1ドープ領域(102)を有した半導体基板(100)に前記第1ウェル領域(104)を形成する工程であって、前記第1ウェル領域(104)および前記第1ドープ領域(102)はp型不純物及びn型不純物からなる群から選択された第1導電型の不純物を含有し、前記第1ウェル領域(104)が前記第1ドープ領域(102)と電気接続され、かつ、フィールド構造(106)が前記第1ウェル領域(104)のいずれかの側に形成されている、第1ウェル領域(104)を形成する工程と、

分離領域(206)を前記第1ウェル領域(104)と第1ドープ領域(102)との間に形成する工程であって、前記分離領域(206)は前記フィールド構造(106)の一部の下方まで伸びている、前記分離領域(206)を形成する工程と、

前記フィールド構造(106)の下方に第2ウェル領域(404)を形成する工程とを備え、

前記分離構造(206)は前記第2ウェル領域(404)に電気接続され、及び、前記分離領域(206)及び前記第2ウェル領域(404)は、前記第1導電型とは反対の第2導電型の不純物を含有している、フィールド構造を有する半導体素子の製造方法。

【請求項2】

前記分離領域(206)のピーク不純物濃度が約1E17〜1E19原子/cm3の範囲にあり、

前記第2ウェル領域(404)のピーク不純物濃度が約1E17〜1E19原子/cm3の範囲にあり、前記方法は、

前記分離領域(206)と第1ドープ領域(102)との間に第2ドープ領域(310)を形成する工程であって、前記第2ドープ領域(310)は前記第1導電型の不純物を含有し、前記第2ドープ領域(310)のピーク濃度が約1E17〜1E19原子/cm3の範囲にある工程と、

前記分離領域(206)の上に第3ドープ領域(312)を形成する工程であって、前記第3ドープ領域(312)は前記第1導電型の不純物を含有し、前記第3ドープ領域(312)のピーク濃度が約1E17〜1E19原子/cm3の範囲にある工程とをさらに備える、請求項1に記載の方法。

【請求項3】

前記半導体基板(100)上にゲート構造(504)を形成する工程と、

前記ゲート構造(504)に隣接したソース/ドレーン領域(604)を形成する工程と、

前記ゲート構造(504)および前記ソース/ドレーン領域(604)の下に保護電荷再結合領域(610)を形成する工程とをさらに備える、請求項1に記載の方法。

【請求項4】

第1ウェル領域(104)の下に第1ドープ領域(102)を有した半導体基板(100)にある第1ウェル領域(104)と、前記第1ウェル領域(104)および前記第1ドープ領域(102)はp型不純物およびn型不純物からなる群から選択される第1導電型の不純物を含有することと、前記第1ウェル領域(104)は前記第1ドープ領域(102)と電気接続されていることと、

前記第1ウェル領域(104)と前記第1ドープ領域(102)との間にあり、前記フィールド構造の一部の下方まで伸びている分離領域(206)と、

フィールド構造(106)の下方の第2ウェル領域(404)とを備え、前記分離領域(206)は前記第2ウェル領域(404)に電気接続され、前記分離領域(206)および前記第2ウェル領域(404)は第2導電型の不純物を含有し、前記第2の型の不純物は前記第1の型の不純物とは反対である、フィールド構造を有した半導体素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−165005(P2012−165005A)

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願番号】特願2012−96796(P2012−96796)

【出願日】平成24年4月20日(2012.4.20)

【分割の表示】特願2001−564389(P2001−564389)の分割

【原出願日】平成13年1月31日(2001.1.31)

【出願人】(504199127)フリースケール セミコンダクター インコーポレイテッド (806)

【Fターム(参考)】

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願日】平成24年4月20日(2012.4.20)

【分割の表示】特願2001−564389(P2001−564389)の分割

【原出願日】平成13年1月31日(2001.1.31)

【出願人】(504199127)フリースケール セミコンダクター インコーポレイテッド (806)

【Fターム(参考)】

[ Back to top ]