半導体素子の実装方法

【課題】薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制することを目的とする。

【解決手段】半導体素子を搭載する毎に加圧状態で加熱して仮接合を行い、全ての半導体素子を仮接合した後、一括して加圧状態で加熱して本接合を行うことにより、薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

【解決手段】半導体素子を搭載する毎に加圧状態で加熱して仮接合を行い、全ての半導体素子を仮接合した後、一括して加圧状態で加熱して本接合を行うことにより、薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

【発明の詳細な説明】

【技術分野】

【0001】

薄型化,端子の狭ピッチ化がされた半導体素子をバンプを介して基板や下段の半導体素子に接合する半導体素子の実装方法に関する。

【背景技術】

【0002】

半導体装置の高機能化,小型化の要請に応じ、半導体素子を複数積層して1パッケージ化するSiP(System in Packate)等の半導体装置が用いられている。また、さらなる小型化を実現するために積層される個々の半導体素子が薄型化され、高機能化のために端子数が増加して端子の狭ピッチ化が進んでいる。例えば、半導体素子厚が50μm、端子間ピッチが50μmの半導体素子が搭載されている。

【0003】

ここで、半導体素子の積層は、バンプを介して電極端子間をはんだ接合することにより行われるが、はんだ溶融の際の加熱により、半導体素子が反り、上段の半導体素子の積層が困難になったり、電極端子間の接続不良等が発生する場合があった。反りの原因は、半導体素子表面に形成される回路に用いられるAlやCuあるいはSiN,ポリミド等の絶縁膜の材料と半導体裏面材料との線膨張係数差によるものである。特に、半導体素子の薄型化により反りの発生が顕著となり、また、端子が狭ピッチ化されるために半導体素子の反りを原因とする電極端子間の接続不良が発生しやすくなっている。

【0004】

そのため、従来の半導体素子の実装方法では、はんだを溶融してからはんだが凝固して電極端子間接合が完了するまでの間、半導体素子の反りを規制するように半導体素子を加圧していた。

【0005】

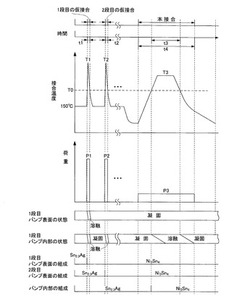

以下、図6を用いて従来の半導体素子の実装方法について説明する。

図6は従来の接合条件に対応する実装状態の推移を説明する相関図である。

まず、バンプを介して互いの電極端子が接続されるように、基板上に半導体素子を載置する。

【0006】

次に、半導体素子上面と平行で半導体素子上面より大きな板状の加圧部材を用いて、半導体素子上から荷重P1を加圧する。

次に、バンプを加熱してバンプを溶融する。加熱は、バンプをはんだ融点T0以上に昇温し、所定の温度T1を一定時間保持する。その後、バンプを冷却する。そして、溶融したバンプが完全に凝固すると加圧を解除し、1段目の半導体素子の実装が終了する。バンプが融点T0以上になっている期間t1にバンプが溶融し、その後凝固することで電極端子間を接合する。また、バンプが溶融する前から凝固するまでの期間t2の間加圧を行うことにより、半導体素子の実装時に半導体素子が反ることを防止している。

【0007】

次に、同様に、半導体素子上に別の半導体素子を搭載し、電極端子間をバンプにより接合する。以後、所定の段数の半導体素子について同様の工程を繰り返す。つまり、1段の半導体素子を実装する時間はt2であり、積層する段数の分だけ実装時間t2を繰り返す。

【0008】

このように、半導体素子を積層する毎に、バンプが凝固するまでの間加圧しながら実装することにより、半導体素子が反ることを防止しながら実装を行っていた。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平9−97791号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、従来の半導体素子の実装方法では、半導体素子を積層する毎に、バンプが凝固するまで加圧を行い実装する必要があったため、接合時間を要し、生産性が低くなるという問題点があった。

【0011】

本発明は、上記問題点を解決するために、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制することを目的とする。

【課題を解決するための手段】

【0012】

上記目的を達成するために、本発明の半導体素子の実装方法は、基板または下段となる第1の半導体素子が備える第1の電極端子と第2の半導体素子が備える第2の電極端子とをバンプをはさんで対向させて前記基板または下段となる第1の半導体素子上に前記第2の半導体素子を搭載する第1の搭載工程と、前記バンプを加熱しながら前記第2の半導体素子の前記第2の電極端子形成面の裏面である上面を加圧する第1の仮接合工程と、前記第2の半導体素子上に前記第1の搭載工程と同様に第3の半導体素子を搭載する第2の搭載工程と、前記第2の搭載工程で搭載した前記第2の半導体素子と前記第3の半導体素子とを前記第1の仮接合工程と同様に仮接合する第2の仮接合工程と、前記第2の搭載工程および第2の仮接合工程と同様の工程を所定の段数の半導体素子を積層するまで繰り返す積層工程と、前記所定の段数の半導体素子の前記第2の仮接合工程が終了した後、最上段の半導体素子上面を加圧しながら前記バンプを加熱する本接合工程とを有し、前記本接合工程の加圧は前記バンプが凝固するまで行われ、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が前記本接合終了後の前記バンプの合金化率よりも低いことを特徴とする。

【0013】

また、本発明の半導体素子の実装方法は、ウェハに形成された第1の半導体素子が備える第1の電極端子と第2の半導体素子が備える第2の電極端子とをバンプをはさんで対向させて前記第1の半導体素子上に前記第2の半導体素子を搭載する第1の搭載工程と、前記バンプを加熱しながら前記第2の半導体素子の前記第2の電極端子形成面の裏面である上面を加圧する第1の仮接合工程と、前記第2の半導体素子上に前記第1の搭載工程と同様に第3の半導体素子を搭載する第2の搭載工程と、前記第2の搭載工程で搭載した前記第2の半導体素子と前記第3の半導体素子とを前記第1の仮接合工程と同様に仮接合する第2の仮接合工程と、前記第2の搭載工程および第2の仮接合工程と同様の工程を所定の段数の半導体素子を積層するまで繰り返す積層工程と、前記所定の段数の半導体素子の前記第2の仮接合工程を前記ウェハ上の全ての前記第1の半導体素子について行った後、前記ウェハについて一括で、最上段の半導体素子上面を加圧しながら前記バンプを加熱する本接合工程とを有し、前記本接合工程の加圧は前記バンプが凝固するまで行われ、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が前記本接合終了後の前記バンプの合金化率よりも低いことを特徴とする。

【0014】

また、前記第1の仮接合工程および第2の仮接合工程にて前記バンプを第1の温度まで加熱し、前記本接合工程にて前記バンプを第2の温度まで加熱し、前記第1の温度が前記第2の温度より高いことが好ましい。

【0015】

また、前記本接合における加圧時間が前記第1の仮接合工程および第2の仮接合工程における加圧時間より長いことが好ましい。

また、前記第1の仮接合工程および第2の仮接合工程における加圧は前記バンプが前記バンプの材料の融点以上の温度に加熱されている期間中にのみ行われることが好ましい。

【0016】

また、前記本接合の加圧における荷重が前記第1の仮接合工程および第2の仮接合工程の加圧における荷重より小さいことが好ましい。

また、前記バンプの材料がSn2.3Agである場合、前記第1の仮接合工程および第2の仮接合工程における加圧時間は0.25〜2.0sec、前記本接合における加圧時間は30〜300secであっても良い。

【0017】

また、前記本接合を還元ガス雰囲気中で行うことが好ましい。

また、前記搭載工程の前に前記バンプの表面に対してArプラズマ洗浄あるいは蟻酸還元または水素還元を行うことが好ましい。

【0018】

また、前記反りが下に凸の場合は前記半導体素子の外周領域に、前記反りが上に凸の場合は前記半導体素子の中央部に、搭載された半導体素子間をつなぐ紫外線硬化接着剤を設け、前記仮接合工程において紫外線を照射しても良い。

【0019】

また、前記第1の搭載工程および前記第2の搭載工程を加熱しながら行うことが好ましい。

また、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が1.0〜10.0%であり、前記本接合終了後の前記バンプの合金化率が25.0〜100%であることが好ましい。

【発明の効果】

【0020】

半導体素子を搭載する毎に加圧状態で加熱して仮接合を行い、全ての半導体素子を仮接合した後、一括して加圧状態で加熱して本接合を行うことにより、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

【図面の簡単な説明】

【0021】

【図1】実施の形態1における半導体素子の実装方法の仮接合工程を順に説明する概略断面図

【図2】実施の形態1における半導体素子の実装方法の本接合工程を順に説明する概略断面図

【図3】接合条件に対応する実装状態の推移を説明する相関図

【図4】実施の形態2における半導体素子の実装方法の仮接合工程を順に説明する概略断面図

【図5】実施の形態3における半導体素子の実装方法を説明する図

【図6】従来の接合条件に対応する実装状態の推移を説明する相関図

【発明を実施するための形態】

【0022】

半導体装置を製造する際や実装基板に半導体素子を実装する際に、下段となる基板や半導体素子の電極端子と上段となる半導体素子の電極端子とを、バンプを介してフリップチップ接合して実装することが行われる。そして、実装した半導体素子上にさらに半導体素子をフリップチップ接合して、複数の半導体素子が積層される。

【0023】

以下、図面を用いて、本発明のバンプを介した半導体素子の実装方法の実施の形態について、基板に複数の半導体素子を積層して実装する場合を例に説明する。

(実施の形態1)

まず、図1,図2を用いて実施の形態1における半導体素子の実装方法について説明する。

【0024】

図1は実施の形態1における半導体素子の実装方法の仮接合工程を順に説明する概略断面図、図2は実施の形態1における半導体素子の実装方法の本接合工程を順に説明する概略断面図である。

【0025】

図1に示すように、実施の形態1では、仮接合として、電極端子7が複数形成された基板2と、電極端子7と対応する位置に複数の電極端子8が形成された半導体素子1を実装する。さらに、半導体素子1上に別の半導体素子を同様に実装し、このような実装を繰り返して半導体素子を積層する。

【0026】

まず、図1(a)に示すように、基板2の電極端子7または半導体素子1の電極端子8のいずれかにバンプ4を形成する。バンプ4の形成方法は任意であるが、例えば、電極端子7または電極端子8にTi,W,Cuでシード層スパッタを行い、電極端子表面をNi電界めっきした後、レジストを形成してはんだめっきを行い、レジスト除去後リフローして形成する。あるいは、Cuピラーバンプの場合、シード層スパッタを行った後、電極端子表面にCu電解めっきを形成し、レジストを形成してはんだめっきを行った後、レジストを除去し、最後にリフローして形成しても良い。

【0027】

次に、図1(b)に示すように、電極端子7,8の位置を合わせて基板2上に半導体素子1を載置し、仮接合として、加熱した状態で、半導体素子1の反りを抑制するように半導体素子1の上面全面と接する平板状の加圧部材5を半導体素子1に当接させて加圧する。加熱の方法として、例えば、基板2を加熱ステージ6上に載置することで基板2側から加熱し、ヒーター9で加圧部材5を加熱することにより半導体素子1側からも加熱する。

【0028】

このような仮接合により、図1(c)に示すように、バンプ4と電極端子7,8との界面領域のみを合金化して基板2と半導体素子1とを仮接合する。このような部分的な合金化は、加圧,加熱時間により制御され、バンプ4の約1.0〜10.0%が合金化するようにする。これにより、例えば、バンプ4の高さが約10μmの場合、バンプ4の電極端子7,8の界面から1.0μm程度の範囲が合金化する。この時、加圧,加熱を解除した瞬間はバンプ4の合金化されていない領域である非合金層4aは溶融状態である。また、加圧を解除することにより、半導体素子1は表裏の線膨張係数差により反りを生じ始める。この状態で、非合金層4aは凝固し始め、半導体素子1が完全に反る前に凝固することにより、半導体素子1の反りを抑制しながら半導体素子1の仮接合を行うことができる。このように、反りによる応力がバンプ4に印加する際に、非合金層4aは合金化せず溶融しているため、反りによりバンプ4が切断されることを防止することができる。ここで、加圧,加熱を解除した後、冷却ガス等でバンプ4を冷却することにより、凝固が促進し、より反りを抑制しながら半導体素子1を仮接合することができる。

【0029】

さらに、バンプ4の接着から仮接合を行って、半導体素子1上に半導体素子3を実装する。このような半導体素子の実装を繰り返し、図1(d)に示すように、基板2上に複数の半導体素子を積層する。このように、半導体素子を実装する毎に仮接合を行うことにより、上段の半導体素子の仮接合時に下段の半導体素子に接合されたバンプ4の非合金層4aが再び溶融し、下段の半導体素子の反りを緩和することができる。また、非合金層4aは合金化せず、合金層4bよりも弾性力の有るはんだであるため、半導体素子の積層時に半導体素子にかかる応力を緩和し、半導体素子の破壊等を抑制することができる。図1(d)では3段の半導体素子を積層する例を示しているが、積層する段数に制限はない。

【0030】

次に、図2に示すように、実施の形態1では、本接合として、仮接合を繰り返して積層した半導体素子のバンプ4の非合金層4aを一括して合金化する。

まず、図2(a)に示すように、バンプ4の電極端子7,8との境界領域のみが合金化して積層された複数の半導体素子に対して、最上段の半導体素子10上に、例えば半導体素子10平面を覆うような加圧部材5を当接させて積層した半導体素子全体を加圧した状態で加熱する。

【0031】

このような加熱により非合金層4aが再溶融し、この状態で加圧されることにより半導体素子の反りが除去される。つまり、加熱,加圧により半導体素子の反りが戻る方向に作用するが、バンプ4が完全に合金化されておらず非合金層4aが溶融するため、半導体素子の戻りを阻害せずに溶融した非合金層4aが反りの戻りを吸収し、はんだの表面張力により反りを抑制して、半導体素子の反りを除去することができる。

【0032】

次に、図2(b)に示すように、加熱を停止し、加圧状態を維持したまま冷却ガス11を導入してバンプを冷却する。このように、加熱後、加圧状態でバンプ全体の約25.0〜100%が凝固して合金層4cとなり、半導体素子が反りのない状態で各半導体素子が下段の半導体素子または基板2に実装固定される。

【0033】

最後に、冷却ガス11の導入および加圧を停止すると、図2(c)に示すように、基板2上への反りのない半導体素子の積層が完成する。

以上のように、複数の半導体素子をバンプを介して積層する際に、半導体素子を1段実装する毎に加熱中のみ加圧する仮接合を繰り返し、全ての半導体素子の仮接合を行った後、一括して加熱から冷却が終了までの間加圧する本接合を行うことにより、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

【0034】

例えば、基板に4段の半導体素子を積層する場合、従来は、反りを防止するために半導体素子を接合する度に加圧を維持しながら約30sec間加熱,冷却を行っており、4段の半導体素子を積層する場合は約120secの接合時間を要していた。これに対して本発明の半導体素子の実装方法によれば、4段の半導体素子の実装毎に約0.25secの仮接合を行った後、一括して約30secの本接合を行うことにより、合計で4段の半導体素子を積層する場合は約31secの接合時間で接合を行うことができ、約89secの時短が可能となり、生産性を向上させることができる。

【0035】

次に、図1〜3を用いて具体的な例における半導体素子の実装方法について詳細に説明する。

図3は接合条件に対応する実装状態の推移を説明する相関図である。

【0036】

ここでは、50μmピッチで22500個のCu製の電極端子8を設けた8mm角、50μm厚の半導体素子をはんだ材料がSn2.3Agのバンプ4を介して、Ni−Al製の電極端子7を設けた基板2上に2段積層する場合を例に説明する。なお、Sn2.3Agは、Snを97.7at%、Agを2.3at%含有する合金である。

【0037】

まず、電極端子7または電極端子8のいずれかにバンプ4を形成する。

次に、ヒーター9を用いて加熱しながら、バンプ4を介して電極端子7と電極端子8接続するように基板2上に半導体素子1を搭載し、例えば、基板2を150℃に加熱された加熱ステージ6上に載置する(図1(a)の状態)。

【0038】

次に、バンプ4の温度がはんだの融点T0より高いT1になるように昇温して加熱を停止する。この時、はんだの融点T0より高い温度となる時間がt1になるように加熱を調節する。これにより、バンプ4と電極端子7,8との界面領域のみに厚さ0.5〜2.0μmで組成がNi3Sn4の合金層4bが形成される。また、加熱を開始してからバンプ4の温度がT0を超えるまでのタイミングから、好ましくはバンプ4の温度がT0を超えると同時に、加圧部材5を用いて半導体素子1の反りを防止するように荷重P1で加圧を開始し、バンプ4の温度がT0を下回ると同時に加圧を解除する。つまり、概ね、バンプ4の温度がT0を超えるt1時間だけ加圧をして仮接合を行う(図1(b)の状態)。

【0039】

このように、T0より高い温度で加熱する期間中に加圧して実装することにより、半導体素子1の反りを防止できる。なお、除圧することにより、半導体素子1は反ろうとするが、温度がT0を下回るためにバンプ4の非合金層4aは凝固を始め、反りの進行中に凝固するので、反りによるバンプ4の破断を防ぎながら反りを抑制することができる。このようにして、合金層4bにより電極端子7,8とバンプ4との仮接合がなされる(図1(c)の状態)。また、凝固を促進して反り量を低減させるために、除圧後N2ガス等の冷却ガスを導入しても良い。

【0040】

そして、同様の方法で、半導体素子1の上面に半導体素子3を仮接合し、さらに、所望の段数まで半導体素子の仮接合を繰り返す(図1(d)の状態)。この時、上段の半導体素子の方がヒーターに近いため高温となり、合金化が下段に比べて促進される。逆に、下段の半導体素子は上段の半導体素子の仮接合時に同時に合金化が進むため、合金化のばらつきは抑制される。

【0041】

ここで、バンプ4がSn2.3Agであるので、融点T0は220℃であり、T1は260〜300℃に設定する。また、t1は0.25〜2.0secとすることにより、バンプ4と電極端子7または電極端子8との界面領域のみ合金化する。また、荷重P1および2段目以降の荷重P2を10〜200Nとすることにより、半導体素子1の反りを抑制することができる。また、加熱ステージ温度は120〜200℃とし、加熱ヘッド温度は280〜340℃とする。

【0042】

続いて、積層する全ての半導体素子の仮接合が終了した段階で、一括して本接合を行う。

まず、例えば260℃に設定された真空加熱炉に仮接合された半導体素子を搬入し、加圧部材5により最上段の半導体素子から0.1〜0.5Nの荷重P3を加える(図2(a)の状態)。

【0043】

次に、バンプ4の温度が融点T0を超えてT3に達するまで昇温を続け、T3になった時点で昇温を停止する。その後、バンプ4の温度は徐々に低下してT0に至る。この、バンプ4の温度が融点T0を超えてからT0に戻るまでに時間t3の間に、非合金層4aが溶融して全体が合金化する。加圧により半導体素子の反りが戻ろうとし、その時点でバンプ4の非合金層4aが溶融しているため半導体素子の反りが解消される。

【0044】

次に、バンプ4の温度がT0に至ると、非合金層4aを迅速に凝固させるためにN2ガス等の冷却ガスを導入する(図2(b)の状態)。

次に、非合金層4aが完全に凝固した後、加圧を解除する。加圧の解除は非合金層4aが完全に凝固したことをモニターして行っても良いが、あらかじめ求めた凝固が完了するタイミングで解除しても良い。加圧の時間t4は加熱開始前から非合金層4aが完全に凝固するまでの時間であり、ここでは30〜300secとなる。これにより、バンプ4の全体、あるいは少なくとも90%以上が組成が(Cu,Ni)6Sn5の合金層4cとなり、電極端子7,8間が合金層4cでつながり接合が強固となる。以上により、基板2上に複数の半導体素子を積層する実装が終了する(図2(c)の状態)。

【0045】

このように、加熱を開始してから冷却が完了するまでの間に加圧を実施することにより、半導体素子の反りを防止しながら積層実装を行うことができる。

ここで、バンプ4がSn2.3Agであるので、融点T0は220℃であり、T3は245〜260℃に設定する。また、T1をT3より高い温度とすることにより、仮接合をより短時間に行うことができる。また、一部が合金化されているので、比較的低い温度T3で本接合することができ、さらに、仮接合よりも長時間加熱するために仮接合より高密度な合金化が可能となり、接合強度を高くすることができる。また、仮接合によりある程度の反りの矯正がなされているので、荷重P3は荷重P1およびP2より小さくしても、本接合にて半導体素子の反りを防止することができる。

【0046】

本接合は全ての半導体素子を一括して行う方法について説明したが、本接合を複数回に分けて、いくつかの仮接合された半導体素子毎の本接合を繰り返すことにより全ての半導体素子を本接合しても良い。これにより、生産効率の向上を図りながら、特に多段積層する場合などに安定的に接合処理を行うことが可能となる。

【0047】

以上のように、半導体素子を実装する毎に仮接合を行い、仮接合のバンプ凝固過程では加圧を行わないことにより、半導体素子の実装毎の実装時間を短縮する。また、上段の半導体素子の接合時に、バンプの非合金層が溶融するため、加圧による反りの抑制を効率化できる。そして、積層された複数の半導体素子について一括で本接合を行う。本接合では、バンプ凝固過程においても加圧を継続することにより、薄型化,端子が狭ピッチ化された半導体素子であっても半導体素子の反りを抑制しながら積層された半導体素子の実装が可能となる。また、長時間を要するバンプ凝固過程での加圧を半導体素子の積層後に一括で行うことにより、半導体素子の実装毎にバンプ凝固過程での加圧を行う場合に比べて実装時間が短縮されるので生産性を向上させることができる。

【0048】

なお、各構成材料は上記例以外に様々な材料を用いることができ、それに応じて仮接合,本接合の条件を決定する。はんだ材料としては、SnAg、SnAgCu、SnZn、SnZnBi、SnPb、SnBi、SnAgBiIn、SnIn、In、Sn等を用いることができる。電極端子としては、例えば、AlCu、AlSiCu、AlSi、Cu、Al等を用いることができる。さらに、バンプ4としてCuを内包したSn等のはんだ、あるいはCuの表面にSn等のはんだを設けたCuピラーバンプや無電解Niめっきバンプ等を用いても良い。

【0049】

また、図1,2の説明では、半導体素子が下に凸の向きに反る場合を例示しているが、反りの向きは半導体素子毎で任意であり、半導体素子によって反りの方向が異なっている場合でも同様の方法で積層実装が可能である。

(実施の形態2)

次に、図4を用いて実施の形態2における半導体素子の実装方法について説明する。

【0050】

図4は実施の形態2における半導体素子の実装方法の仮接合工程を順に説明する概略断面図である。

実施の形態2における半導体素子の実装方法の特徴は、半導体素子の反りが大きくなる領域、つまり、基板と半導体素子、あるいは半導体素子間の距離が大きくなる領域に紫外線硬化および熱硬化を併用する紫外線硬化接着剤を設けることである。例えば、半導体素子が下に凸になる場合、半導体素子の周辺領域である半導体素子のコーナー部や電極端子の外側の半導体素子の外周辺に沿った領域等に、高さがバンプとその上下の電極端子の高さの合計と同程度の1または複数の紫外線硬化接着剤を設ける。逆に、半導体素子が上に凸になる場合は、半導体素子中央部の電極端子が形成されていない領域に高さがバンプとその上下の電極端子の高さの合計と同程度の1または複数の紫外線硬化接着剤を設ける。また、反りの方向が不明の場合は両方に紫外線硬化接着剤を設けても良い。

【0051】

以下、図4を用いて仮接合工程について、半導体素子が下に凸になるように反る場合を例に説明する。なお、本接合工程は実施の形態1と同様であるので説明を省略する。

まず、図4(a)に示すように、電極端子8の外側で半導体素子1の外周部に1または複数の紫外線硬化接着剤12を設ける。紫外線硬化接着剤12の高さは、バンプ4とその上下の電極端子7,8の高さの合計と同程度とする。その後またはその前に、実施の形態1と同様に電極端子7または8にバンプ4を接着する。

【0052】

次に、図4(b)に示すように、電極端子7,8の位置を合わせて基板2上に半導体素子1を載置し、実施の形態1と同様に加熱,加圧を行って仮接合を行う。本実施の形態では、仮接合の際に紫外線を照射する。加圧中の紫外線の照射は紫外線硬化接着剤12が完全に硬化せず、弾性が残る程度の時間に調整して行う。例えば、紫外線硬化接着剤12として、アクリル系材料の一般的な紫外線・熱硬化併用型接着剤を用いる。照射条件は、365nm波長で300〜500mW/cm2の光量を0.1〜1.0sec間照射する。この時点では光硬化成分のみが硬化し、熱硬化成分は未反応のため紫外線硬化接着剤12は半硬化状態である。この状態で、加圧を停止することにより半導体素子1は反り始めるが、紫外線照射の継続により紫外線硬化接着剤12が硬化および収縮するため、反りに対する抗力となり反りを抑制することができる(図4(c))。

【0053】

以上の仮接合を半導体素子を搭載する毎に行い、その後、実施の形態1と同様に一括して本接合を行う。本接合に際し、紫外線硬化接着剤12は半硬化状態であるので、加圧による反りの矯正の妨げにはならず、本接合の際の加熱により硬化し、反りの防止にも貢献する。

【0054】

以上のように、実施の形態1と同様に薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができ、さらに、仮接合時に紫外線硬化接着剤12に紫外線を照射することにより反りの抑制を行うことができるので、反りの大きい半導体素子であっても容易に反りを抑制して積層することができる。

(実施の形態3)

次に、図5を用いて実施の形態3における半導体素子の実装方法について説明する。

【0055】

図5は実施の形態3における半導体素子の実装方法を説明する図であり、図5(a)は半導体素子を積層したウェハの構成を示す斜視図、図5(b)は半導体素子を積層したウェハの構成を示す断面図、図5(c)は積層した半導体素子を個片化する工程を説明する断面図である。

【0056】

以上の各実施の形態では、基板あるいは半導体素子上に複数段の半導体素子を実装する方法について説明したが、実施の形態3における半導体素子の実装方法の特徴は、基板に代わり複数の半導体素子が形成されたウェハの各半導体素子上に複数段の半導体素子を実装することである。

【0057】

図5に示すように、ウェハ13の表面には複数の半導体素子14が互いにスクライブ領域15を介してマトリクス状に形成されている。本実施の形態では、まず、ウェハの状態で半導体素子14上に複数の半導体素子を積層する。積層は実施の形態1または実施の形態2と同様の方法で、各半導体素子14上に所定の段数の半導体素子を仮接合し、全ての半導体素子14の仮接合を行ってから、ウェハ13単位で一括して全ての半導体素子14の本接合を行う(図5(a),図5(b))。

【0058】

このようにして、ウェハ13上の半導体素子14上に複数の半導体素子を積層した状態で、各半導体素子を一括モールドし、その後、スクライブ領域15に沿ってダイシングブレード16等を用いてダイシングすることにより、半導体素子が積層された半導体装置を個片化する(図5(c))。

【0059】

以上のように、ウェハ状態で半導体素子14上に、個々の半導体素子14毎に仮接合を行った後、ウェハ一括で本接合を行うことにより、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。例えば、ウェハ13に1000個の半導体素子14が形成され、半導体素子14上に4段の半導体素子を積層する場合、仮接合時間を0.25sec,本接合時間を30secとすると、実施の形態1および実施の形態2の方法を用いて実装した場合、1つの半導体素子14の実装に、仮接合時間として0.25sec×4段=1.00sec、本接合時間として30secかかり、合計31secが必要となる。さらにこれを1000個に行うため、ウェハ13の全ての半導体素子14に半導体素子を積層するのに31000secが必要となる。実施の形態3では、ウェハ3上の全ての半導体素子14を実装するためには、仮接合時間として0.25sec×4段×1000個=1000sec、本接合時間として30secを要するのみで、合計1030secで積層することが可能となり、実施の形態1,2に比べて生産性向上の効果が顕著となる。従来の方法で実装した場合、30sec×4段×1000個=120000secを要するので、実施の形態3のようにウェハ上の半導体素子に実装する場合には、飛躍的に生産性を向上させることができることとなる。

【0060】

なお、上記各実施の形態において、仮接合または本接合、あるいはその両方をバンプに還元ガスを導入しながら行っても良い。還元ガスを導入することにより、バンプ表面の酸化物を還元することができ、はんだと電極端子との濡れ性が向上し、接合部の空隙の発生を抑制して接合強度を向上させると共に接合を短時間で行うことができる。なお、還元ガスとしては、蟻酸等のカルボン酸等を用いることができる。

【0061】

また、仮接合の前にArプラズマ洗浄あるいは蟻酸還元または水素還元を行うによりバンプ表面のはんだ酸化膜を除去しても良い。バンプ表面の酸化物を除去することにより、接合部の空隙の発生を抑制して接合強度を向上させると共に接合を短時間で行うことができる。さらに、Arプラズマ洗浄後、H2ガス雰囲気中に保持することにより、その後の酸化を抑制することもできる。

【産業上の利用可能性】

【0062】

本発明は、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制することができ、薄型化,端子の狭ピッチ化がされた半導体素子をバンプを介して基板や下段の半導体素子に接合する半導体素子の実装方法等に有用である。

【符号の説明】

【0063】

1 半導体素子

2 基板

3 半導体素子

4 バンプ

4a 合金層

4b 非合金層

5 加圧部材

6 加熱ステージ

7 電極端子

8 電極端子

9 ヒーター

10 半導体素子

11 冷却ガス

12 紫外線硬化接着剤

13 ウェハ

14 半導体素子

15 スクライブ領域

16 ダイシングブレード

【技術分野】

【0001】

薄型化,端子の狭ピッチ化がされた半導体素子をバンプを介して基板や下段の半導体素子に接合する半導体素子の実装方法に関する。

【背景技術】

【0002】

半導体装置の高機能化,小型化の要請に応じ、半導体素子を複数積層して1パッケージ化するSiP(System in Packate)等の半導体装置が用いられている。また、さらなる小型化を実現するために積層される個々の半導体素子が薄型化され、高機能化のために端子数が増加して端子の狭ピッチ化が進んでいる。例えば、半導体素子厚が50μm、端子間ピッチが50μmの半導体素子が搭載されている。

【0003】

ここで、半導体素子の積層は、バンプを介して電極端子間をはんだ接合することにより行われるが、はんだ溶融の際の加熱により、半導体素子が反り、上段の半導体素子の積層が困難になったり、電極端子間の接続不良等が発生する場合があった。反りの原因は、半導体素子表面に形成される回路に用いられるAlやCuあるいはSiN,ポリミド等の絶縁膜の材料と半導体裏面材料との線膨張係数差によるものである。特に、半導体素子の薄型化により反りの発生が顕著となり、また、端子が狭ピッチ化されるために半導体素子の反りを原因とする電極端子間の接続不良が発生しやすくなっている。

【0004】

そのため、従来の半導体素子の実装方法では、はんだを溶融してからはんだが凝固して電極端子間接合が完了するまでの間、半導体素子の反りを規制するように半導体素子を加圧していた。

【0005】

以下、図6を用いて従来の半導体素子の実装方法について説明する。

図6は従来の接合条件に対応する実装状態の推移を説明する相関図である。

まず、バンプを介して互いの電極端子が接続されるように、基板上に半導体素子を載置する。

【0006】

次に、半導体素子上面と平行で半導体素子上面より大きな板状の加圧部材を用いて、半導体素子上から荷重P1を加圧する。

次に、バンプを加熱してバンプを溶融する。加熱は、バンプをはんだ融点T0以上に昇温し、所定の温度T1を一定時間保持する。その後、バンプを冷却する。そして、溶融したバンプが完全に凝固すると加圧を解除し、1段目の半導体素子の実装が終了する。バンプが融点T0以上になっている期間t1にバンプが溶融し、その後凝固することで電極端子間を接合する。また、バンプが溶融する前から凝固するまでの期間t2の間加圧を行うことにより、半導体素子の実装時に半導体素子が反ることを防止している。

【0007】

次に、同様に、半導体素子上に別の半導体素子を搭載し、電極端子間をバンプにより接合する。以後、所定の段数の半導体素子について同様の工程を繰り返す。つまり、1段の半導体素子を実装する時間はt2であり、積層する段数の分だけ実装時間t2を繰り返す。

【0008】

このように、半導体素子を積層する毎に、バンプが凝固するまでの間加圧しながら実装することにより、半導体素子が反ることを防止しながら実装を行っていた。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平9−97791号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、従来の半導体素子の実装方法では、半導体素子を積層する毎に、バンプが凝固するまで加圧を行い実装する必要があったため、接合時間を要し、生産性が低くなるという問題点があった。

【0011】

本発明は、上記問題点を解決するために、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制することを目的とする。

【課題を解決するための手段】

【0012】

上記目的を達成するために、本発明の半導体素子の実装方法は、基板または下段となる第1の半導体素子が備える第1の電極端子と第2の半導体素子が備える第2の電極端子とをバンプをはさんで対向させて前記基板または下段となる第1の半導体素子上に前記第2の半導体素子を搭載する第1の搭載工程と、前記バンプを加熱しながら前記第2の半導体素子の前記第2の電極端子形成面の裏面である上面を加圧する第1の仮接合工程と、前記第2の半導体素子上に前記第1の搭載工程と同様に第3の半導体素子を搭載する第2の搭載工程と、前記第2の搭載工程で搭載した前記第2の半導体素子と前記第3の半導体素子とを前記第1の仮接合工程と同様に仮接合する第2の仮接合工程と、前記第2の搭載工程および第2の仮接合工程と同様の工程を所定の段数の半導体素子を積層するまで繰り返す積層工程と、前記所定の段数の半導体素子の前記第2の仮接合工程が終了した後、最上段の半導体素子上面を加圧しながら前記バンプを加熱する本接合工程とを有し、前記本接合工程の加圧は前記バンプが凝固するまで行われ、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が前記本接合終了後の前記バンプの合金化率よりも低いことを特徴とする。

【0013】

また、本発明の半導体素子の実装方法は、ウェハに形成された第1の半導体素子が備える第1の電極端子と第2の半導体素子が備える第2の電極端子とをバンプをはさんで対向させて前記第1の半導体素子上に前記第2の半導体素子を搭載する第1の搭載工程と、前記バンプを加熱しながら前記第2の半導体素子の前記第2の電極端子形成面の裏面である上面を加圧する第1の仮接合工程と、前記第2の半導体素子上に前記第1の搭載工程と同様に第3の半導体素子を搭載する第2の搭載工程と、前記第2の搭載工程で搭載した前記第2の半導体素子と前記第3の半導体素子とを前記第1の仮接合工程と同様に仮接合する第2の仮接合工程と、前記第2の搭載工程および第2の仮接合工程と同様の工程を所定の段数の半導体素子を積層するまで繰り返す積層工程と、前記所定の段数の半導体素子の前記第2の仮接合工程を前記ウェハ上の全ての前記第1の半導体素子について行った後、前記ウェハについて一括で、最上段の半導体素子上面を加圧しながら前記バンプを加熱する本接合工程とを有し、前記本接合工程の加圧は前記バンプが凝固するまで行われ、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が前記本接合終了後の前記バンプの合金化率よりも低いことを特徴とする。

【0014】

また、前記第1の仮接合工程および第2の仮接合工程にて前記バンプを第1の温度まで加熱し、前記本接合工程にて前記バンプを第2の温度まで加熱し、前記第1の温度が前記第2の温度より高いことが好ましい。

【0015】

また、前記本接合における加圧時間が前記第1の仮接合工程および第2の仮接合工程における加圧時間より長いことが好ましい。

また、前記第1の仮接合工程および第2の仮接合工程における加圧は前記バンプが前記バンプの材料の融点以上の温度に加熱されている期間中にのみ行われることが好ましい。

【0016】

また、前記本接合の加圧における荷重が前記第1の仮接合工程および第2の仮接合工程の加圧における荷重より小さいことが好ましい。

また、前記バンプの材料がSn2.3Agである場合、前記第1の仮接合工程および第2の仮接合工程における加圧時間は0.25〜2.0sec、前記本接合における加圧時間は30〜300secであっても良い。

【0017】

また、前記本接合を還元ガス雰囲気中で行うことが好ましい。

また、前記搭載工程の前に前記バンプの表面に対してArプラズマ洗浄あるいは蟻酸還元または水素還元を行うことが好ましい。

【0018】

また、前記反りが下に凸の場合は前記半導体素子の外周領域に、前記反りが上に凸の場合は前記半導体素子の中央部に、搭載された半導体素子間をつなぐ紫外線硬化接着剤を設け、前記仮接合工程において紫外線を照射しても良い。

【0019】

また、前記第1の搭載工程および前記第2の搭載工程を加熱しながら行うことが好ましい。

また、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が1.0〜10.0%であり、前記本接合終了後の前記バンプの合金化率が25.0〜100%であることが好ましい。

【発明の効果】

【0020】

半導体素子を搭載する毎に加圧状態で加熱して仮接合を行い、全ての半導体素子を仮接合した後、一括して加圧状態で加熱して本接合を行うことにより、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

【図面の簡単な説明】

【0021】

【図1】実施の形態1における半導体素子の実装方法の仮接合工程を順に説明する概略断面図

【図2】実施の形態1における半導体素子の実装方法の本接合工程を順に説明する概略断面図

【図3】接合条件に対応する実装状態の推移を説明する相関図

【図4】実施の形態2における半導体素子の実装方法の仮接合工程を順に説明する概略断面図

【図5】実施の形態3における半導体素子の実装方法を説明する図

【図6】従来の接合条件に対応する実装状態の推移を説明する相関図

【発明を実施するための形態】

【0022】

半導体装置を製造する際や実装基板に半導体素子を実装する際に、下段となる基板や半導体素子の電極端子と上段となる半導体素子の電極端子とを、バンプを介してフリップチップ接合して実装することが行われる。そして、実装した半導体素子上にさらに半導体素子をフリップチップ接合して、複数の半導体素子が積層される。

【0023】

以下、図面を用いて、本発明のバンプを介した半導体素子の実装方法の実施の形態について、基板に複数の半導体素子を積層して実装する場合を例に説明する。

(実施の形態1)

まず、図1,図2を用いて実施の形態1における半導体素子の実装方法について説明する。

【0024】

図1は実施の形態1における半導体素子の実装方法の仮接合工程を順に説明する概略断面図、図2は実施の形態1における半導体素子の実装方法の本接合工程を順に説明する概略断面図である。

【0025】

図1に示すように、実施の形態1では、仮接合として、電極端子7が複数形成された基板2と、電極端子7と対応する位置に複数の電極端子8が形成された半導体素子1を実装する。さらに、半導体素子1上に別の半導体素子を同様に実装し、このような実装を繰り返して半導体素子を積層する。

【0026】

まず、図1(a)に示すように、基板2の電極端子7または半導体素子1の電極端子8のいずれかにバンプ4を形成する。バンプ4の形成方法は任意であるが、例えば、電極端子7または電極端子8にTi,W,Cuでシード層スパッタを行い、電極端子表面をNi電界めっきした後、レジストを形成してはんだめっきを行い、レジスト除去後リフローして形成する。あるいは、Cuピラーバンプの場合、シード層スパッタを行った後、電極端子表面にCu電解めっきを形成し、レジストを形成してはんだめっきを行った後、レジストを除去し、最後にリフローして形成しても良い。

【0027】

次に、図1(b)に示すように、電極端子7,8の位置を合わせて基板2上に半導体素子1を載置し、仮接合として、加熱した状態で、半導体素子1の反りを抑制するように半導体素子1の上面全面と接する平板状の加圧部材5を半導体素子1に当接させて加圧する。加熱の方法として、例えば、基板2を加熱ステージ6上に載置することで基板2側から加熱し、ヒーター9で加圧部材5を加熱することにより半導体素子1側からも加熱する。

【0028】

このような仮接合により、図1(c)に示すように、バンプ4と電極端子7,8との界面領域のみを合金化して基板2と半導体素子1とを仮接合する。このような部分的な合金化は、加圧,加熱時間により制御され、バンプ4の約1.0〜10.0%が合金化するようにする。これにより、例えば、バンプ4の高さが約10μmの場合、バンプ4の電極端子7,8の界面から1.0μm程度の範囲が合金化する。この時、加圧,加熱を解除した瞬間はバンプ4の合金化されていない領域である非合金層4aは溶融状態である。また、加圧を解除することにより、半導体素子1は表裏の線膨張係数差により反りを生じ始める。この状態で、非合金層4aは凝固し始め、半導体素子1が完全に反る前に凝固することにより、半導体素子1の反りを抑制しながら半導体素子1の仮接合を行うことができる。このように、反りによる応力がバンプ4に印加する際に、非合金層4aは合金化せず溶融しているため、反りによりバンプ4が切断されることを防止することができる。ここで、加圧,加熱を解除した後、冷却ガス等でバンプ4を冷却することにより、凝固が促進し、より反りを抑制しながら半導体素子1を仮接合することができる。

【0029】

さらに、バンプ4の接着から仮接合を行って、半導体素子1上に半導体素子3を実装する。このような半導体素子の実装を繰り返し、図1(d)に示すように、基板2上に複数の半導体素子を積層する。このように、半導体素子を実装する毎に仮接合を行うことにより、上段の半導体素子の仮接合時に下段の半導体素子に接合されたバンプ4の非合金層4aが再び溶融し、下段の半導体素子の反りを緩和することができる。また、非合金層4aは合金化せず、合金層4bよりも弾性力の有るはんだであるため、半導体素子の積層時に半導体素子にかかる応力を緩和し、半導体素子の破壊等を抑制することができる。図1(d)では3段の半導体素子を積層する例を示しているが、積層する段数に制限はない。

【0030】

次に、図2に示すように、実施の形態1では、本接合として、仮接合を繰り返して積層した半導体素子のバンプ4の非合金層4aを一括して合金化する。

まず、図2(a)に示すように、バンプ4の電極端子7,8との境界領域のみが合金化して積層された複数の半導体素子に対して、最上段の半導体素子10上に、例えば半導体素子10平面を覆うような加圧部材5を当接させて積層した半導体素子全体を加圧した状態で加熱する。

【0031】

このような加熱により非合金層4aが再溶融し、この状態で加圧されることにより半導体素子の反りが除去される。つまり、加熱,加圧により半導体素子の反りが戻る方向に作用するが、バンプ4が完全に合金化されておらず非合金層4aが溶融するため、半導体素子の戻りを阻害せずに溶融した非合金層4aが反りの戻りを吸収し、はんだの表面張力により反りを抑制して、半導体素子の反りを除去することができる。

【0032】

次に、図2(b)に示すように、加熱を停止し、加圧状態を維持したまま冷却ガス11を導入してバンプを冷却する。このように、加熱後、加圧状態でバンプ全体の約25.0〜100%が凝固して合金層4cとなり、半導体素子が反りのない状態で各半導体素子が下段の半導体素子または基板2に実装固定される。

【0033】

最後に、冷却ガス11の導入および加圧を停止すると、図2(c)に示すように、基板2上への反りのない半導体素子の積層が完成する。

以上のように、複数の半導体素子をバンプを介して積層する際に、半導体素子を1段実装する毎に加熱中のみ加圧する仮接合を繰り返し、全ての半導体素子の仮接合を行った後、一括して加熱から冷却が終了までの間加圧する本接合を行うことにより、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

【0034】

例えば、基板に4段の半導体素子を積層する場合、従来は、反りを防止するために半導体素子を接合する度に加圧を維持しながら約30sec間加熱,冷却を行っており、4段の半導体素子を積層する場合は約120secの接合時間を要していた。これに対して本発明の半導体素子の実装方法によれば、4段の半導体素子の実装毎に約0.25secの仮接合を行った後、一括して約30secの本接合を行うことにより、合計で4段の半導体素子を積層する場合は約31secの接合時間で接合を行うことができ、約89secの時短が可能となり、生産性を向上させることができる。

【0035】

次に、図1〜3を用いて具体的な例における半導体素子の実装方法について詳細に説明する。

図3は接合条件に対応する実装状態の推移を説明する相関図である。

【0036】

ここでは、50μmピッチで22500個のCu製の電極端子8を設けた8mm角、50μm厚の半導体素子をはんだ材料がSn2.3Agのバンプ4を介して、Ni−Al製の電極端子7を設けた基板2上に2段積層する場合を例に説明する。なお、Sn2.3Agは、Snを97.7at%、Agを2.3at%含有する合金である。

【0037】

まず、電極端子7または電極端子8のいずれかにバンプ4を形成する。

次に、ヒーター9を用いて加熱しながら、バンプ4を介して電極端子7と電極端子8接続するように基板2上に半導体素子1を搭載し、例えば、基板2を150℃に加熱された加熱ステージ6上に載置する(図1(a)の状態)。

【0038】

次に、バンプ4の温度がはんだの融点T0より高いT1になるように昇温して加熱を停止する。この時、はんだの融点T0より高い温度となる時間がt1になるように加熱を調節する。これにより、バンプ4と電極端子7,8との界面領域のみに厚さ0.5〜2.0μmで組成がNi3Sn4の合金層4bが形成される。また、加熱を開始してからバンプ4の温度がT0を超えるまでのタイミングから、好ましくはバンプ4の温度がT0を超えると同時に、加圧部材5を用いて半導体素子1の反りを防止するように荷重P1で加圧を開始し、バンプ4の温度がT0を下回ると同時に加圧を解除する。つまり、概ね、バンプ4の温度がT0を超えるt1時間だけ加圧をして仮接合を行う(図1(b)の状態)。

【0039】

このように、T0より高い温度で加熱する期間中に加圧して実装することにより、半導体素子1の反りを防止できる。なお、除圧することにより、半導体素子1は反ろうとするが、温度がT0を下回るためにバンプ4の非合金層4aは凝固を始め、反りの進行中に凝固するので、反りによるバンプ4の破断を防ぎながら反りを抑制することができる。このようにして、合金層4bにより電極端子7,8とバンプ4との仮接合がなされる(図1(c)の状態)。また、凝固を促進して反り量を低減させるために、除圧後N2ガス等の冷却ガスを導入しても良い。

【0040】

そして、同様の方法で、半導体素子1の上面に半導体素子3を仮接合し、さらに、所望の段数まで半導体素子の仮接合を繰り返す(図1(d)の状態)。この時、上段の半導体素子の方がヒーターに近いため高温となり、合金化が下段に比べて促進される。逆に、下段の半導体素子は上段の半導体素子の仮接合時に同時に合金化が進むため、合金化のばらつきは抑制される。

【0041】

ここで、バンプ4がSn2.3Agであるので、融点T0は220℃であり、T1は260〜300℃に設定する。また、t1は0.25〜2.0secとすることにより、バンプ4と電極端子7または電極端子8との界面領域のみ合金化する。また、荷重P1および2段目以降の荷重P2を10〜200Nとすることにより、半導体素子1の反りを抑制することができる。また、加熱ステージ温度は120〜200℃とし、加熱ヘッド温度は280〜340℃とする。

【0042】

続いて、積層する全ての半導体素子の仮接合が終了した段階で、一括して本接合を行う。

まず、例えば260℃に設定された真空加熱炉に仮接合された半導体素子を搬入し、加圧部材5により最上段の半導体素子から0.1〜0.5Nの荷重P3を加える(図2(a)の状態)。

【0043】

次に、バンプ4の温度が融点T0を超えてT3に達するまで昇温を続け、T3になった時点で昇温を停止する。その後、バンプ4の温度は徐々に低下してT0に至る。この、バンプ4の温度が融点T0を超えてからT0に戻るまでに時間t3の間に、非合金層4aが溶融して全体が合金化する。加圧により半導体素子の反りが戻ろうとし、その時点でバンプ4の非合金層4aが溶融しているため半導体素子の反りが解消される。

【0044】

次に、バンプ4の温度がT0に至ると、非合金層4aを迅速に凝固させるためにN2ガス等の冷却ガスを導入する(図2(b)の状態)。

次に、非合金層4aが完全に凝固した後、加圧を解除する。加圧の解除は非合金層4aが完全に凝固したことをモニターして行っても良いが、あらかじめ求めた凝固が完了するタイミングで解除しても良い。加圧の時間t4は加熱開始前から非合金層4aが完全に凝固するまでの時間であり、ここでは30〜300secとなる。これにより、バンプ4の全体、あるいは少なくとも90%以上が組成が(Cu,Ni)6Sn5の合金層4cとなり、電極端子7,8間が合金層4cでつながり接合が強固となる。以上により、基板2上に複数の半導体素子を積層する実装が終了する(図2(c)の状態)。

【0045】

このように、加熱を開始してから冷却が完了するまでの間に加圧を実施することにより、半導体素子の反りを防止しながら積層実装を行うことができる。

ここで、バンプ4がSn2.3Agであるので、融点T0は220℃であり、T3は245〜260℃に設定する。また、T1をT3より高い温度とすることにより、仮接合をより短時間に行うことができる。また、一部が合金化されているので、比較的低い温度T3で本接合することができ、さらに、仮接合よりも長時間加熱するために仮接合より高密度な合金化が可能となり、接合強度を高くすることができる。また、仮接合によりある程度の反りの矯正がなされているので、荷重P3は荷重P1およびP2より小さくしても、本接合にて半導体素子の反りを防止することができる。

【0046】

本接合は全ての半導体素子を一括して行う方法について説明したが、本接合を複数回に分けて、いくつかの仮接合された半導体素子毎の本接合を繰り返すことにより全ての半導体素子を本接合しても良い。これにより、生産効率の向上を図りながら、特に多段積層する場合などに安定的に接合処理を行うことが可能となる。

【0047】

以上のように、半導体素子を実装する毎に仮接合を行い、仮接合のバンプ凝固過程では加圧を行わないことにより、半導体素子の実装毎の実装時間を短縮する。また、上段の半導体素子の接合時に、バンプの非合金層が溶融するため、加圧による反りの抑制を効率化できる。そして、積層された複数の半導体素子について一括で本接合を行う。本接合では、バンプ凝固過程においても加圧を継続することにより、薄型化,端子が狭ピッチ化された半導体素子であっても半導体素子の反りを抑制しながら積層された半導体素子の実装が可能となる。また、長時間を要するバンプ凝固過程での加圧を半導体素子の積層後に一括で行うことにより、半導体素子の実装毎にバンプ凝固過程での加圧を行う場合に比べて実装時間が短縮されるので生産性を向上させることができる。

【0048】

なお、各構成材料は上記例以外に様々な材料を用いることができ、それに応じて仮接合,本接合の条件を決定する。はんだ材料としては、SnAg、SnAgCu、SnZn、SnZnBi、SnPb、SnBi、SnAgBiIn、SnIn、In、Sn等を用いることができる。電極端子としては、例えば、AlCu、AlSiCu、AlSi、Cu、Al等を用いることができる。さらに、バンプ4としてCuを内包したSn等のはんだ、あるいはCuの表面にSn等のはんだを設けたCuピラーバンプや無電解Niめっきバンプ等を用いても良い。

【0049】

また、図1,2の説明では、半導体素子が下に凸の向きに反る場合を例示しているが、反りの向きは半導体素子毎で任意であり、半導体素子によって反りの方向が異なっている場合でも同様の方法で積層実装が可能である。

(実施の形態2)

次に、図4を用いて実施の形態2における半導体素子の実装方法について説明する。

【0050】

図4は実施の形態2における半導体素子の実装方法の仮接合工程を順に説明する概略断面図である。

実施の形態2における半導体素子の実装方法の特徴は、半導体素子の反りが大きくなる領域、つまり、基板と半導体素子、あるいは半導体素子間の距離が大きくなる領域に紫外線硬化および熱硬化を併用する紫外線硬化接着剤を設けることである。例えば、半導体素子が下に凸になる場合、半導体素子の周辺領域である半導体素子のコーナー部や電極端子の外側の半導体素子の外周辺に沿った領域等に、高さがバンプとその上下の電極端子の高さの合計と同程度の1または複数の紫外線硬化接着剤を設ける。逆に、半導体素子が上に凸になる場合は、半導体素子中央部の電極端子が形成されていない領域に高さがバンプとその上下の電極端子の高さの合計と同程度の1または複数の紫外線硬化接着剤を設ける。また、反りの方向が不明の場合は両方に紫外線硬化接着剤を設けても良い。

【0051】

以下、図4を用いて仮接合工程について、半導体素子が下に凸になるように反る場合を例に説明する。なお、本接合工程は実施の形態1と同様であるので説明を省略する。

まず、図4(a)に示すように、電極端子8の外側で半導体素子1の外周部に1または複数の紫外線硬化接着剤12を設ける。紫外線硬化接着剤12の高さは、バンプ4とその上下の電極端子7,8の高さの合計と同程度とする。その後またはその前に、実施の形態1と同様に電極端子7または8にバンプ4を接着する。

【0052】

次に、図4(b)に示すように、電極端子7,8の位置を合わせて基板2上に半導体素子1を載置し、実施の形態1と同様に加熱,加圧を行って仮接合を行う。本実施の形態では、仮接合の際に紫外線を照射する。加圧中の紫外線の照射は紫外線硬化接着剤12が完全に硬化せず、弾性が残る程度の時間に調整して行う。例えば、紫外線硬化接着剤12として、アクリル系材料の一般的な紫外線・熱硬化併用型接着剤を用いる。照射条件は、365nm波長で300〜500mW/cm2の光量を0.1〜1.0sec間照射する。この時点では光硬化成分のみが硬化し、熱硬化成分は未反応のため紫外線硬化接着剤12は半硬化状態である。この状態で、加圧を停止することにより半導体素子1は反り始めるが、紫外線照射の継続により紫外線硬化接着剤12が硬化および収縮するため、反りに対する抗力となり反りを抑制することができる(図4(c))。

【0053】

以上の仮接合を半導体素子を搭載する毎に行い、その後、実施の形態1と同様に一括して本接合を行う。本接合に際し、紫外線硬化接着剤12は半硬化状態であるので、加圧による反りの矯正の妨げにはならず、本接合の際の加熱により硬化し、反りの防止にも貢献する。

【0054】

以上のように、実施の形態1と同様に薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができ、さらに、仮接合時に紫外線硬化接着剤12に紫外線を照射することにより反りの抑制を行うことができるので、反りの大きい半導体素子であっても容易に反りを抑制して積層することができる。

(実施の形態3)

次に、図5を用いて実施の形態3における半導体素子の実装方法について説明する。

【0055】

図5は実施の形態3における半導体素子の実装方法を説明する図であり、図5(a)は半導体素子を積層したウェハの構成を示す斜視図、図5(b)は半導体素子を積層したウェハの構成を示す断面図、図5(c)は積層した半導体素子を個片化する工程を説明する断面図である。

【0056】

以上の各実施の形態では、基板あるいは半導体素子上に複数段の半導体素子を実装する方法について説明したが、実施の形態3における半導体素子の実装方法の特徴は、基板に代わり複数の半導体素子が形成されたウェハの各半導体素子上に複数段の半導体素子を実装することである。

【0057】

図5に示すように、ウェハ13の表面には複数の半導体素子14が互いにスクライブ領域15を介してマトリクス状に形成されている。本実施の形態では、まず、ウェハの状態で半導体素子14上に複数の半導体素子を積層する。積層は実施の形態1または実施の形態2と同様の方法で、各半導体素子14上に所定の段数の半導体素子を仮接合し、全ての半導体素子14の仮接合を行ってから、ウェハ13単位で一括して全ての半導体素子14の本接合を行う(図5(a),図5(b))。

【0058】

このようにして、ウェハ13上の半導体素子14上に複数の半導体素子を積層した状態で、各半導体素子を一括モールドし、その後、スクライブ領域15に沿ってダイシングブレード16等を用いてダイシングすることにより、半導体素子が積層された半導体装置を個片化する(図5(c))。

【0059】

以上のように、ウェハ状態で半導体素子14上に、個々の半導体素子14毎に仮接合を行った後、ウェハ一括で本接合を行うことにより、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。例えば、ウェハ13に1000個の半導体素子14が形成され、半導体素子14上に4段の半導体素子を積層する場合、仮接合時間を0.25sec,本接合時間を30secとすると、実施の形態1および実施の形態2の方法を用いて実装した場合、1つの半導体素子14の実装に、仮接合時間として0.25sec×4段=1.00sec、本接合時間として30secかかり、合計31secが必要となる。さらにこれを1000個に行うため、ウェハ13の全ての半導体素子14に半導体素子を積層するのに31000secが必要となる。実施の形態3では、ウェハ3上の全ての半導体素子14を実装するためには、仮接合時間として0.25sec×4段×1000個=1000sec、本接合時間として30secを要するのみで、合計1030secで積層することが可能となり、実施の形態1,2に比べて生産性向上の効果が顕著となる。従来の方法で実装した場合、30sec×4段×1000個=120000secを要するので、実施の形態3のようにウェハ上の半導体素子に実装する場合には、飛躍的に生産性を向上させることができることとなる。

【0060】

なお、上記各実施の形態において、仮接合または本接合、あるいはその両方をバンプに還元ガスを導入しながら行っても良い。還元ガスを導入することにより、バンプ表面の酸化物を還元することができ、はんだと電極端子との濡れ性が向上し、接合部の空隙の発生を抑制して接合強度を向上させると共に接合を短時間で行うことができる。なお、還元ガスとしては、蟻酸等のカルボン酸等を用いることができる。

【0061】

また、仮接合の前にArプラズマ洗浄あるいは蟻酸還元または水素還元を行うによりバンプ表面のはんだ酸化膜を除去しても良い。バンプ表面の酸化物を除去することにより、接合部の空隙の発生を抑制して接合強度を向上させると共に接合を短時間で行うことができる。さらに、Arプラズマ洗浄後、H2ガス雰囲気中に保持することにより、その後の酸化を抑制することもできる。

【産業上の利用可能性】

【0062】

本発明は、薄型化,端子が狭ピッチ化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制することができ、薄型化,端子の狭ピッチ化がされた半導体素子をバンプを介して基板や下段の半導体素子に接合する半導体素子の実装方法等に有用である。

【符号の説明】

【0063】

1 半導体素子

2 基板

3 半導体素子

4 バンプ

4a 合金層

4b 非合金層

5 加圧部材

6 加熱ステージ

7 電極端子

8 電極端子

9 ヒーター

10 半導体素子

11 冷却ガス

12 紫外線硬化接着剤

13 ウェハ

14 半導体素子

15 スクライブ領域

16 ダイシングブレード

【特許請求の範囲】

【請求項1】

基板または下段となる第1の半導体素子が備える第1の電極端子と第2の半導体素子が備える第2の電極端子とをバンプをはさんで対向させて前記基板または下段となる第1の半導体素子上に前記第2の半導体素子を搭載する第1の搭載工程と、

前記バンプを加熱しながら前記第2の半導体素子の前記第2の電極端子形成面の裏面である上面を加圧する第1の仮接合工程と、

前記第2の半導体素子上に前記第1の搭載工程と同様に第3の半導体素子を搭載する第2の搭載工程と、

前記第2の搭載工程で搭載した前記第2の半導体素子と前記第3の半導体素子とを前記第1の仮接合工程と同様に仮接合する第2の仮接合工程と、

前記第2の搭載工程および第2の仮接合工程と同様の工程を所定の段数の半導体素子を積層するまで繰り返す積層工程と、

前記所定の段数の半導体素子の前記第2の仮接合工程が終了した後、最上段の半導体素子上面を加圧しながら前記バンプを加熱する本接合工程と

を有し、前記本接合工程の加圧は前記バンプが凝固するまで行われ、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が前記本接合終了後の前記バンプの合金化率よりも低いことを特徴とする半導体素子の実装方法。

【請求項2】

ウェハに形成された第1の半導体素子が備える第1の電極端子と第2の半導体素子が備える第2の電極端子とをバンプをはさんで対向させて前記第1の半導体素子上に前記第2の半導体素子を搭載する第1の搭載工程と、

前記バンプを加熱しながら前記第2の半導体素子の前記第2の電極端子形成面の裏面である上面を加圧する第1の仮接合工程と、

前記第2の半導体素子上に前記第1の搭載工程と同様に第3の半導体素子を搭載する第2の搭載工程と、

前記第2の搭載工程で搭載した前記第2の半導体素子と前記第3の半導体素子とを前記第1の仮接合工程と同様に仮接合する第2の仮接合工程と、

前記第2の搭載工程および第2の仮接合工程と同様の工程を所定の段数の半導体素子を積層するまで繰り返す積層工程と、

前記所定の段数の半導体素子の前記第2の仮接合工程を前記ウェハ上の全ての前記第1の半導体素子について行った後、前記ウェハについて一括で、最上段の半導体素子上面を加圧しながら前記バンプを加熱する本接合工程と

を有し、前記本接合工程の加圧は前記バンプが凝固するまで行われ、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が前記本接合終了後の前記バンプの合金化率よりも低いことを特徴とする半導体素子の実装方法。

【請求項3】

前記第1の仮接合工程および第2の仮接合工程にて前記バンプを第1の温度まで加熱し、前記本接合工程にて前記バンプを第2の温度まで加熱し、前記第1の温度が前記第2の温度より高いことを特徴とする請求項1または請求項2のいずれかに記載の半導体素子の実装方法。

【請求項4】

前記本接合における加圧時間が前記第1の仮接合工程および第2の仮接合工程における加圧時間より長いことを特徴とする請求項1〜請求項3のいずれかに記載の半導体素子の実装方法。

【請求項5】

前記第1の仮接合工程および第2の仮接合工程における加圧は前記バンプが前記バンプの材料の融点以上の温度に加熱されている期間中にのみ行われることを特徴とする請求項1〜請求項4のいずれかに記載の半導体素子の実装方法。

【請求項6】

前記本接合の加圧における荷重が前記第1の仮接合工程および第2の仮接合工程の加圧における荷重より小さいことを特徴とする請求項1〜請求項5のいずれかに記載の半導体素子の実装方法。

【請求項7】

前記バンプの材料がSn2.3Agである場合、前記第1の仮接合工程および第2の仮接合工程における加圧時間は0.25〜2.0sec、前記本接合における加圧時間は30〜300secであることを特徴とする請求項1〜請求項6のいずれかに記載の半導体素子の実装方法。

【請求項8】

前記本接合を還元ガス雰囲気中で行うことを特徴とする請求項1〜請求項7のいずれかに記載の半導体素子の実装方法。

【請求項9】

前記搭載工程の前に前記バンプの表面に対してArプラズマ洗浄あるいは蟻酸還元または水素還元を行うことを特徴とする請求項1〜請求項8のいずれかに記載の半導体素子の実装方法。

【請求項10】

前記反りが下に凸の場合は前記半導体素子の外周領域に、前記反りが上に凸の場合は前記半導体素子の中央部に、搭載された半導体素子間をつなぐ紫外線硬化接着剤を設け、前記仮接合工程において紫外線を照射することを特徴とする請求項1〜請求項9のいずれかに記載の半導体素子の実装方法。

【請求項11】

前記第1の搭載工程および前記第2の搭載工程を加熱しながら行うことを特徴とする請求項1〜請求項10のいずれかに記載の半導体素子の実装方法。

【請求項12】

前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が1.0〜10.0%であり、前記本接合終了後の前記バンプの合金化率が25.0〜100%であることを特徴とする請求項1〜請求項11のいずれかに記載の半導体素子の実装方法。

【請求項1】

基板または下段となる第1の半導体素子が備える第1の電極端子と第2の半導体素子が備える第2の電極端子とをバンプをはさんで対向させて前記基板または下段となる第1の半導体素子上に前記第2の半導体素子を搭載する第1の搭載工程と、

前記バンプを加熱しながら前記第2の半導体素子の前記第2の電極端子形成面の裏面である上面を加圧する第1の仮接合工程と、

前記第2の半導体素子上に前記第1の搭載工程と同様に第3の半導体素子を搭載する第2の搭載工程と、

前記第2の搭載工程で搭載した前記第2の半導体素子と前記第3の半導体素子とを前記第1の仮接合工程と同様に仮接合する第2の仮接合工程と、

前記第2の搭載工程および第2の仮接合工程と同様の工程を所定の段数の半導体素子を積層するまで繰り返す積層工程と、

前記所定の段数の半導体素子の前記第2の仮接合工程が終了した後、最上段の半導体素子上面を加圧しながら前記バンプを加熱する本接合工程と

を有し、前記本接合工程の加圧は前記バンプが凝固するまで行われ、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が前記本接合終了後の前記バンプの合金化率よりも低いことを特徴とする半導体素子の実装方法。

【請求項2】

ウェハに形成された第1の半導体素子が備える第1の電極端子と第2の半導体素子が備える第2の電極端子とをバンプをはさんで対向させて前記第1の半導体素子上に前記第2の半導体素子を搭載する第1の搭載工程と、

前記バンプを加熱しながら前記第2の半導体素子の前記第2の電極端子形成面の裏面である上面を加圧する第1の仮接合工程と、

前記第2の半導体素子上に前記第1の搭載工程と同様に第3の半導体素子を搭載する第2の搭載工程と、

前記第2の搭載工程で搭載した前記第2の半導体素子と前記第3の半導体素子とを前記第1の仮接合工程と同様に仮接合する第2の仮接合工程と、

前記第2の搭載工程および第2の仮接合工程と同様の工程を所定の段数の半導体素子を積層するまで繰り返す積層工程と、

前記所定の段数の半導体素子の前記第2の仮接合工程を前記ウェハ上の全ての前記第1の半導体素子について行った後、前記ウェハについて一括で、最上段の半導体素子上面を加圧しながら前記バンプを加熱する本接合工程と

を有し、前記本接合工程の加圧は前記バンプが凝固するまで行われ、前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が前記本接合終了後の前記バンプの合金化率よりも低いことを特徴とする半導体素子の実装方法。

【請求項3】

前記第1の仮接合工程および第2の仮接合工程にて前記バンプを第1の温度まで加熱し、前記本接合工程にて前記バンプを第2の温度まで加熱し、前記第1の温度が前記第2の温度より高いことを特徴とする請求項1または請求項2のいずれかに記載の半導体素子の実装方法。

【請求項4】

前記本接合における加圧時間が前記第1の仮接合工程および第2の仮接合工程における加圧時間より長いことを特徴とする請求項1〜請求項3のいずれかに記載の半導体素子の実装方法。

【請求項5】

前記第1の仮接合工程および第2の仮接合工程における加圧は前記バンプが前記バンプの材料の融点以上の温度に加熱されている期間中にのみ行われることを特徴とする請求項1〜請求項4のいずれかに記載の半導体素子の実装方法。

【請求項6】

前記本接合の加圧における荷重が前記第1の仮接合工程および第2の仮接合工程の加圧における荷重より小さいことを特徴とする請求項1〜請求項5のいずれかに記載の半導体素子の実装方法。

【請求項7】

前記バンプの材料がSn2.3Agである場合、前記第1の仮接合工程および第2の仮接合工程における加圧時間は0.25〜2.0sec、前記本接合における加圧時間は30〜300secであることを特徴とする請求項1〜請求項6のいずれかに記載の半導体素子の実装方法。

【請求項8】

前記本接合を還元ガス雰囲気中で行うことを特徴とする請求項1〜請求項7のいずれかに記載の半導体素子の実装方法。

【請求項9】

前記搭載工程の前に前記バンプの表面に対してArプラズマ洗浄あるいは蟻酸還元または水素還元を行うことを特徴とする請求項1〜請求項8のいずれかに記載の半導体素子の実装方法。

【請求項10】

前記反りが下に凸の場合は前記半導体素子の外周領域に、前記反りが上に凸の場合は前記半導体素子の中央部に、搭載された半導体素子間をつなぐ紫外線硬化接着剤を設け、前記仮接合工程において紫外線を照射することを特徴とする請求項1〜請求項9のいずれかに記載の半導体素子の実装方法。

【請求項11】

前記第1の搭載工程および前記第2の搭載工程を加熱しながら行うことを特徴とする請求項1〜請求項10のいずれかに記載の半導体素子の実装方法。

【請求項12】

前記第1の仮接合工程および前記第2の仮接合工程によって合金化された前記バンプの合金化率が1.0〜10.0%であり、前記本接合終了後の前記バンプの合金化率が25.0〜100%であることを特徴とする請求項1〜請求項11のいずれかに記載の半導体素子の実装方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−80758(P2013−80758A)

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願番号】特願2011−218824(P2011−218824)

【出願日】平成23年10月3日(2011.10.3)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年5月2日(2013.5.2)

【国際特許分類】

【出願日】平成23年10月3日(2011.10.3)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]