半導体素子の製造方法及び半導体素子

【課題】レジストを「焦げ」の発生を防ぎつつ除去し、さらにプラズマ酸化珪素膜を半導体ウェハ内部の不純物の再分布を抑制しながら高速に形成する半導体素子の製造方法及び半導体素子を提供する。

【解決手段】レジスト301の灰化時には低めのRF電力を用いることで、レジスト301の「焦げ」の発生を防いで灰化する。レジスト301の灰化が終了した時点から高めのRF電力に切り替えることで酸化レートの高いプラズマ酸化を行い、ポリシリコンからなるN型配線部103、P型配線部104の表面に不純物の外方拡散防止膜としてのプラズマ酸化珪素膜401を形成する。熱工程を行うことなくポリシリコンをくるむようにプラズマ酸化珪素膜401を形成するため、半導体ウェハ101中の不純物を殆ど再分布させない。

【解決手段】レジスト301の灰化時には低めのRF電力を用いることで、レジスト301の「焦げ」の発生を防いで灰化する。レジスト301の灰化が終了した時点から高めのRF電力に切り替えることで酸化レートの高いプラズマ酸化を行い、ポリシリコンからなるN型配線部103、P型配線部104の表面に不純物の外方拡散防止膜としてのプラズマ酸化珪素膜401を形成する。熱工程を行うことなくポリシリコンをくるむようにプラズマ酸化珪素膜401を形成するため、半導体ウェハ101中の不純物を殆ど再分布させない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体ウェハ上にある半導体素子からの、不純物の外方拡散を抑制する方法を提供することを目的とした半導体素子の製造方法及び半導体素子に関する。

【背景技術】

【0002】

半導体ウェハ上に形成されたポリシリコン領域からの不純物の外方拡散を防止し、ポリシリコンの比抵抗を安定化させる方法が背景技術として知られている。この背景技術について、まず説明する。

【0003】

半導体ウェハ上に酸化珪素膜を形成した後、ポリシリコン膜を形成し、次にフォトリソグラフ工程を用いて、所望のポリシリコン領域を残してポリシリコン膜をエッチングし除去する。

【0004】

続けてサイドウォールを形成した後、CVD(Chemical Vapor Deposition:化学気相成長)法を用いて不純物の外方拡散を防止するための酸化珪素膜を10nm程度形成する。

【0005】

次にN+領域を形成する領域にのみレジストを開口し、燐などのイオン注入を行う。このイオン注入により所望のポリシリコン領域にN型の不純物を導入する。続けて、P+、領域を形成する領域にのみレジストを開口し、硼素等のイオン注入を行うことで所望のポリシリコン領域にP型の不純物をイオン注入により導入する。

【0006】

イオン注入後、CVD法による酸化珪素膜を外方拡散防止膜とし、アニールによる活性化処理を行う。アニールを行うことでポリシリコンからの不純物の外方拡散を防止しながら不純物を活性化し、安定した抵抗値を有するポリシリコン領域を形成する。

【0007】

続けて、特許文献に示されている技術について以下に概略を説明する。

【0008】

特許文献1では、レジストを灰化する時に、レジストがついていない部分に付随的に形成される酸化珪素膜(特許文献中では、酸化膜と記載されている)を外方拡散の防止膜として用い、ポリシリコン領域からの外方拡散を防止している。

【0009】

また、特許文献2では、外方拡散を防止するための酸化珪素膜をCVD法で成膜する。成膜後、酸素と水素の混合ガス中で熱処理を行うことで、熱酸化膜と比べ欠陥の多いCVD膜中の欠陥を修復するようにしている。

【0010】

【特許文献1】特開2001−7220号公報

【特許文献2】特開平5−55482号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、サイドウォールを形成する時には、ポリシリコン領域が露出するまで酸化珪素膜を異方性ドライエッチングし除去する工程が必要となる。ドライエッチングを行った後のポリシリコン領域は、ドライエッチングによりダメージを受けている。

【0012】

この技術では、ダメージに対応する処置を行わずにCVD法により酸化珪素膜を形成しているため、ポリシリコン領域のダメージが修復されていない状態で酸化珪素膜に埋め込まれることとなる。従って、デバイス特性は残留したダメージの影響を受けて不安定なものとなるおそれがあった。

【0013】

また、特許文献1に示された方法では、TEOS(テトラエトキシシラン)を用いてCVD法で製造された酸化珪素膜をレジストマスクでエッチングし所望のパターンを得てイオン注入等の工程を行った後、レジスト除去とプラズマ酸化を同時に灰化工程で行っている。

【0014】

そのため、レジストマスクの下側にあるポリシリコンは、プラズマ酸化を受けることなく、ポリシリコン上に直接CVD膜が形成されることとなる。つまり、エッチング処理で荒れた界面上に、界面のダメージを修復する工程を行うことなく、CVD法により形成された酸化珪素膜が成膜されることとなる。そのため、ポリシリコン領域にはエッチング時のダメージがそのまま残留することとなり、デバイス特性が不安定なものとなるおそれがあった。

【0015】

さらに、レジスト除去とプラズマ酸化を同時に行っていることから後述するレジストの「焦げ」が生じない条件でプラズマ酸化を行う必要が生じ、プラズマ酸化の処理速度を抑える必要があり、生産性が低下する問題も抱えていた。

【0016】

ここで、「焦げ」について説明する。「焦げ」はレジストの灰化速度を上げすぎた時、レジスト上に発生する物質である。「焦げ」の分子構造等は不明であるが、「焦げ」は灰化でも、硫酸を主としたウェットエッチングでも除去することができない物質であることが経験的に知られており、一旦、「焦げ」ができると除去が困難となるため、「焦げ」が発生しない範囲でレジストの灰化を行うことが必要となる。

【0017】

また、特許文献2に示された方法では、CVD法で形成された酸化珪素膜とポリシリコン膜との間に生じる欠陥は修復されるものの、熱処理を行うために起こる半導体ウェハ上の不純物の再分布を防ぐことができないため、特に微細構造を有する半導体素子を製造する方法への展開が困難となる問題があった。

【0018】

そこで、本発明は、ポリシリコン領域の、ドライエッチングによるダメージを修復し、プラズマ酸化の速度を「焦げ」の発生を回避した上で向上させることでスループットを上げ、かつ半導体ウェハ内部の不純物の再分布を抑制した半導体素子の製造方法及び半導体素子を提供することにある。

【課題を解決するための手段】

【0019】

上記目的を達成するために、本発明の半導体素子の製造方法は、半導体ウェハ上の一主面上に配置されたレジストを、前記レジストの存在を示す信号が検出されている期間では、酸化性を有するプラズマを用いて前記レジストを灰化処理し除去する処理を行い、前記レジストの存在を示す信号が略消滅した後は、前記灰化処理の条件と比べ、前記半導体ウェハの前記一主面上にあるポリシリコンの酸化速度を上げた条件で酸化処理を行う。

【0020】

この製造方法によれば、ポリシリコンの酸化時にはレジストの灰化時にはレジストの灰化に適した条件でレジストを灰化するため、レジストの「焦げ」発生を抑えられる。そして、レジストが略消滅した時点から酸化速度を上げるため、レジストの「焦げ」発生を抑えた状態で処理速度の高いプラズマ酸化を実現することができる。さらに、レジストがほぼ消失した後で酸化速度を上げるため、レジストの有無による酸化珪素膜の膜厚分布を小さく抑えることができる。

【0021】

また、本発明の半導体素子の製造方法は、前記信号は一酸化炭素プラズマの発光色を示す発光信号であることを特徴とする。

【0022】

この製造方法によれば、プラズマ中に含まれているレジスト起因の物質による発光輝線をモニタすることで、レジストが半導体ウェハ上に残留しているか否かを知ることができ、適切なタイミングで酸化速度を上げる条件に切り替えることが可能となる。

【0023】

また、本発明の半導体素子の製造方法は、前記灰化処理及び前記酸化処理はプラズマ発生領域とウェハ処理領域が同一反応管の内部にあり、前記プラズマ発生領域より前記ウェハ処理領域へとプラズマを導き前記半導体ウェハをプラズマ処理するダウンフロー型装置を用いて前記半導体ウェハの処理を行なうことを特徴とする。

【0024】

この製造方法によれば、プラズマを、ウェハと離れたところで発生させることができる。そのためプラズマ発生領域で発生プラズマを発生させるプラズマ放電部と灰化処理部とを空間的に離すことができ、ダメージを起こす荷電粒子を放電部に閉じ込めて、活性種(ラジカル)を主とした反応雰囲気を下流に位置した処理部に送り込み、この反応雰囲気でレジストの除去を行わせることで、低ダメージな灰化及びプラズマ酸化が可能となる。

【0025】

また、本発明の半導体素子の製造方法は、前記灰化処理は、前記半導体ウェハの単位平方センチあたりの面積に対してプラズマ励起用のRF電力を1.6W〜4.5Wの範囲で印加し、かつ灰化時の反応圧力を53Pa〜133Paの範囲で灰化が行うことを特徴とする。

【0026】

この製造方法によれば、後述するレジストの「焦げ」発生を防ぐことができ、かつプラズマを安定して立てられるため、安定したプラズマを維持した状態で灰化を行うことが可能となる。

【0027】

また、本発明の半導体素子の製造方法は、前記酸化処理は、前記半導体ウェハの単位平方センチあたりの面積に対してプラズマ励起用のRF電力を4.8W〜9.6Wの範囲で印加し、かつ酸化時の反応圧力を13Pa〜66Paの範囲で酸化が行うことを特徴とする。

【0028】

この製造方法によれば、酸化速度を灰化時に比べ上げることができるため、半導体ウェハの処理速度を実用的な速度に引き上げることが可能となる。

【0029】

また、本発明の半導体素子は上記半導体素子の製造方法で製造されている。

【0030】

この構成によれば、ポリシリコン全面が酸化珪素膜で覆われるため、ポリシリコンからの外方拡散が抑えられ、ポリシリコンの抵抗値が安定する。また、熱処理を行っていないため、半導体ウェハ内部での不純物再分布を生じさせることがない。そのため、微細化に適した半導体素子を得ることが可能となる。

【発明を実施するための最良の形態】

【0031】

本発明を具体化した一実施形態について、図面を参照して説明する。図1〜7は本発明を実施した時の工程断面図である。この工程断面図は本実施形態を説明するためのもので、膜厚などの比率は説明の都合上、実際のものと変えている場合がある。また、図8はレジストの灰化及びプラズマ酸化膜形成に用いられる、灰化装置の概略を示す断面図である。

【0032】

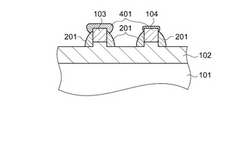

まず、図1について説明する。図1はポリシリコン配線を形成した後の工程断面図である。半導体ウェハ101の第一主面上に形成したSTI(Shallow Trench Isolation:浅溝素子分離)領域102上にポリシリコンからなるN型配線部103、P型配線部104が形成されている。

【0033】

次に、図2について説明する。図2は酸化珪素膜でサイドウォールを形成した後の工程断面図である。酸化珪素膜をCVD(Chemical Vapor Deposition:化学気相成長)法にて成膜し、その後異方性を有するドライエッチングを行うことでサイドウォール201を形成している。このドライエッチングは、N型配線部103、P型配線部104の上部が露出するまで行うため、N型配線部103、P型配線部104はドライエッチングによるダメージを受けている。

【0034】

次に、図3について説明する。図3はN型配線部への不純物導入工程を行った後の工程断面図である。

【0035】

半導体ウェハの第一主面にレジスト301を塗布し、N型配線部103が形成される領域のみ開口し、例えば砒素302を打ち込みエネルギーを30KeV、ドーズ量を3e15cm-2程度でイオン注入する。この工程により、N型配線部103にN型の不純物となる砒素が導入される。

【0036】

ここで、灰化装置800について図面を用いて簡単に説明する。図8は、灰化装置の概略の断面図である。石英で作られたチャンバー801には、MFC(マスフローコントローラ)802を通して酸素が導入される。

【0037】

そして、チャンバー801内部に酸素プラズマ806を立てるため、RF駆動電源803から13.56MHzのRF電力を、インピーダンス整合をとるためのマッチングボックス804を通して、RFコイル813に供給する。チャンバー801中に導入された酸素がRF励起領域805に流れていき、RF電力により励起され、酸素プラズマ806が発生する。

【0038】

酸素プラズマ806はガスフローに従って下流に流れていき、ウェハ処理領域807に導かれていく。ウェハ処理領域807には、金属アルミニウムの周りを酸化アルミニウムでコーティングしたステージ808が備えられている。ステージ808上には、半導体ウェハ101が置かれている。酸素プラズマ806はウェハ処理領域807にあるステージ808に置かれた半導体ウェハ101上に導かれ、半導体ウェハ101上で灰化やプラズマ酸化等の工程が行われる。そして、灰化やプラズマ酸化等の工程を終えた酸素プラズマ806は、さらに下流側に設置されているスロットルバルブ809、排気ポンプ810を通して外部へ排気されていく。

【0039】

スロットルバルブ809は、チャンバー801の下流部に備えられた圧力計811からフィードバックを受けて制御されており、常に所定の圧力を維持するよう制御されている。

【0040】

また、チャンバー801の外側には、プラズマの発光スペクトルをモニタする発光信号検出器812が備えられている。有機物であるレジストを酸素で灰化する際には、一酸化炭素が発生する。そこで、この一酸化炭素の発光信号をモニタすることで半導体ウェハ101上のレジストの有無を判別することができる。

【0041】

上述の灰化装置800を用いてレジスト301を灰化する。アッシングの条件は、直径8インチ(≒20cm)の半導体ウェハ101を用いた場合、例えばRF電力1000W、反応圧力500mTorr(≒67Pa)で行われる。灰化に必要とされるRF電力は半導体ウェハ101の面積で規格化することができ、1000W、8インチの半導体ウェハ101を処理する場合、約3.2W/cm2で灰化を行うこととなる。例えば、ウェハの直径を変えた場合には、3.2W/cm2とウェハの面積を掛ければ、必要となるRF電力を求めることができる。

【0042】

本実施形態では、3.2W/cm2、67Paという条件で灰化を行っているが、これはRF電力として1.6W/cm2〜4.5W/cm2、反応圧力として53Pa〜133Paの範囲で設定可能である。1.6W/cm2未満のRF電力を用いると、プラズマが立たなくなり灰化が行えなくなる。また4.5W/cm2を超えるRF電力を用いると、レジストに「焦げ」が発生してしまう。また、53Pa未満の反応圧力、133Paを超える反応圧力を用いると、プラズマが立たなくなり灰化が行えなくなる。

【0043】

より望ましいプロセス条件範囲としては、RF電力として2.5W/cm2〜3.8W/cm2、反応圧力として66Pa〜110Paがより望ましい範囲となる。この範囲内では、プラズマが安定して立ち、しかもレジストの「焦げ」発生の心配はほぼ無く、適切な灰化レートが得られる。

【0044】

本実施形態で用いた値である3.2W/cm2、67Paという条件で灰化すると、半導体ウェハ101の状態にもよるが、おおよそ1分程度で灰化が完了する。この条件で灰化した場合、レジスト301が無い領域でのプラズマ酸化珪素膜401の膜厚は、4nm程度となる。

【0045】

図4はレジストを灰化した直後の工程断面図である。レジスト301の除去は酸素プラズマによる灰化を用いて行っている。レジスト301に覆われていないN型配線部103上にはプラズマ酸化珪素膜401が形成している。この時点では、レジスト301に覆われていたP型配線部104上にはプラズマ酸化膜401は形成されていない。レジスト301が半導体ウェハ101上から消失すると、灰化装置800についている発光信号検出器812で受ける一酸化炭素の信号強度がほぼ消失する。

【0046】

発光信号検出器812で受ける一酸化炭素の信号強度がほぼ消失した後、続けてプラズマ酸化を行う。プラズマ酸化時には、レジスト301は消失しているのでレジスト301の「焦げ」を心配する必要がなくなる。そこでRF電力を50%上げ1800W(≒6W/cm2)、また反応圧力も清浄性を保ちやすい低圧側に条件をふり、300mTorr(≒40Pa)まで下げてプラズマ酸化を行う。この状態で1分酸化を行うと、レジスト301が存在していた領域でも、5nm程度のプラズマ酸化珪素膜401が形成される。

【0047】

なお、プラズマ酸化の条件としては、本実施形態では、RF電力として6W/cm2、反応圧力として40Paを用いたが、これはRF電力として、4.8W/cm2〜9.6W/cm2、反応圧力として13Pa〜66Paの範囲で設定可能である。4.8W/cm2未満のRF電力で処理すると、形成される酸化珪素膜の膜質が悪くなるため実用的ではない。また、9.6W/cm2を超えるRF電力を加えるのは処理装置のハードウェア的な限界、具体的には異常放電が生じる可能性が出てくるため酸化処理が困難となる。また、反応圧力として13Pa未満では、プラズマが立たないため、処理が行えない。また、66Paを超える反応圧力では、酸化レートが遅くなるため実用的ではない。

【0048】

より望ましいプロセス条件範囲としては、RF電力として4.8W/cm2〜8W/cm2、反応圧力として27Pa〜53Paがより望ましい範囲となる。この範囲内では、プラズマが安定して立ち、しかも形成される酸化珪素膜の膜質も十分優れたものが得られる上、適切な酸化レートが得られる。

【0049】

図5はレジストの灰化に続けて行うプラズマ酸化が終了した直後の工程断面図である。レジスト301に覆われていた領域も、プラズマ酸化工程で酸化される。また、同時にN型配線部103、P型配線部104を形成する際に用いられたドライエッチング工程でのダメージも、プラズマ酸化膜に吸収され回復する。

【0050】

なお、プラズマ酸化時、酸化速度を上げる条件で酸化を行うと、半導体ウェハ101の処理時間はおおよそ2分(灰化1分+プラズマ酸化1分)で済む。

【0051】

一方、プラズマ酸化時、処理条件を灰化の条件をそのまま用いると、同一のプラズマ酸化珪素膜の膜厚を得るためには、2分程度の処理時間が必要となる。従って、一枚の半導体ウェハ101の処理時間はおおよそ3分(アッシング1分+プラズマ酸化2分)を必要とする。単純計算では、スループットを50%向上させることができる。半導体ウェハ101の入れ替え等の時間を考慮しても、処理能力は30%程度向上し、灰化装置400の原価償却に要する期間は30%程度短縮される。

【0052】

次に、P型配線部104への不純物導入工程を以下のように行う。

【0053】

半導体ウェハ101の第一主面にレジスト601を塗布し、P型配線部104が形成される領域のみ開口し、例えば硼素を打ち込みエネルギーを3KeV、ドーズ量を3e15cm-2程度でイオン注入する。この工程により、P型配線部104が必要な領域に不純物が導入される。図6は、レジストをパターニングした直後の工程断面図である。レジスト601は通常のフォトリソグラフ工程を用いて、所望のパターンとなるよう形成される。

【0054】

次にレジスト601を除去し、同時にプラズマ酸化珪素膜401を形成する。レジスト除去及びプラズマ酸化珪素膜401はN型配線部103を処理した条件と同一の条件を用いて処理する。この際、N型配線部103とP型配線部104は相補的に作られるため、N型配線部103の作成時にレジスト301で覆われていた領域は露出され、レジストで覆われていなかった部分はレジスト601で覆われる。従ってN型配線部103上のプラズマ酸化珪素401の膜厚とP型配線部104上のプラズマ酸化珪素401とは平準化され、半導体ウェハ101上でのN型配線部103上のプラズマ酸化珪素401の膜厚とP型配線部104上のプラズマ酸化珪素401の膜厚は、最終的には12nm程度で均一に形成される。

【0055】

図7は、灰化とプラズマ酸化が終了した直後の工程断面図である。N型配線部103とP型配線部104とを覆うプラズマ酸化膜401はN型配線部103とP型配線部104でほぼ同じ値となっており、ばらつきの少ない外方拡散防止膜が形成できている。

【0056】

なお、本実施形態では、STI領域102上のN型配線部103とP型配線部104について説明したが、NMOS、PMOSのトランジスタのゲート領域でも同様に相補的に外方拡散防止膜が形成されており、トランジスタ領域でもばらつきの少ない外方拡散防止膜が形成できている。

【0057】

また、本実施形態では、半導体ウェハ101に熱をかける処理は行われていない。従って、イオン注入等の工程で形成された半導体ウェハ101中の不純物分布はイオン注入終了後の分布をそのまま残しており、熱拡散等による不純物の拡散が生じていない。つまり、急峻な不純物分布を要する微細半導体素子の製造について優れた製造方法を得ることができた。

【0058】

次に、本実施形態の効果について記述する。

(1)レジスト301、601を灰化する期間は低いRF電力で処理しているため、レジストの「焦げ」の発生を効果的に抑えることができた。また、レジスト301、601が灰化されたタイミングでRF電力を50%程度上げることでプラズマ酸化速度を上げるため、レジストの「焦げ」の発生を抑えながら短時間でプラズマ酸化珪素膜が形成できる。

【0059】

また、CMOSを作る際には、レジスト301、601はほぼ相補的な配置を成しているため、NMOS、PMOSともほぼ同じプラズマ酸化膜膜厚を得ることができる。

(2)プラズマから発せられる一酸化炭素の発光スペクトルをモニタした信号に基づき、レジスト301、601の残りを検出するようにしたため、レジスト301、601がエッチングし終わった時から即時にプラズマ酸化に適した条件に切り替えることができ、半導体ウェハ101の一枚あたりの処理時間を短縮することができる。

(3)プラズマ発生領域とウェハ処理領域とが離れた状態で、同一反応管の内部にあり、プラズマ発生領域よりウェハ処理領域へとプラズマを移動させて半導体ウェハ101をプラズマ処理するダウンフロー型装置800を用いて半導体ウェハ101の処理を行ったため、酸素のラジカルを主体とした灰化やプラズマ酸化処理を行うことができ、イオン化した酸素を用いる場合と比べ半導体ウェハ101に与えるダメージが小さい状態で処理することができる。

(4)灰化処理をRF電力を1000W(直径8インチ≒20cmの半導体ウェハ101を使用;3.2W/cm2のRF電力を使用)、反応圧力を500mTorr(≒67Pa)、酸素を用いて灰化したため、レジスト301、601に「焦げ」を作ることなく、1ウェハあたり1分程度でアッシングを行うことができる。

(5)プラズマ酸化時のRF電力1800W(直径8インチ≒20cmの半導体ウェハ101を使用;6W/cm2のRF電力を使用)、反応圧力300mTorr(≒40Pa)、酸素を用いてプラズマ酸化したため、1ウェハあたり1分程度で外方拡散を防止するための酸化珪素膜を得ることができる。また、ドライエッチングにより発生したポリシリコンのダメージ層を酸化珪素膜にしたため、ダメージ残りを抑制することができる。

(6)ポリシリコンを用いた素子に関して、ドライエッチング起因のダメージがある部分をプラズマ酸化により取り除くと同時にプラズマ酸化珪素膜に変換したため、不純物の外方拡散をも抑えることができ、低ダメージ、高再現性を持つ半導体素子を形成することが可能となる。

<変形例>

・前記実施形態では、純酸素を用いて灰化やプラズマ酸化を行った例について述べているが、これはもちろん酸化雰囲気をもつ他のガスを用いても良い。また、灰化とプラズマ酸化との切り替えの際にガス種を変えることがあっても良い。

【0060】

・前記実施形態では、一酸化炭素の発光スペクトルをモニタしてレジストのアッシング終了を検知したが、これはもちろんレジスト由来の発光スペクトルを用いるものであれば良い。

【0061】

・前記実施形態では、発光スペクトル強度をモニタしてレジストのアッシング終了を検知する判別方法として、一酸化炭素の発光スペクトルがほぼ消失した時点としているが、これは、場合により一酸化炭素の発光スペクトルが定常状態より低下した時点や、一酸化炭素の発光スペクトルがほぼ消失してから5秒後など、一酸化炭素の発光スペクトルの変動を基に判定しても良い。

【図面の簡単な説明】

【0062】

【図1】STI領域上にポリシリコン領域を形成した直後の工程断面図。

【図2】サイドウォールを形成した後の工程断面図。

【図3】N型配線部への不純物導入工程を行った後の工程断面図。

【図4】レジストを灰化した直後の工程断面図。

【図5】プラズマ酸化が終了した直後の工程断面図。

【図6】レジストをパターニングした直後の工程断面図。

【図7】灰化とプラズマ酸化が終了した直後の工程断面図。

【図8】灰化装置の概略の断面図。

【符号の説明】

【0063】

101…半導体ウェハ、102…STI領域、103…ポリシリコンとしてのN型配線部、104…ポリシリコンとしてのP型配線部、201…サイドウォール、301…レジスト、302…砒素、401…プラズマ酸化珪素膜、601…レジスト、800…灰化装置、801…チャンバー、802…MFC、803…RF駆動電源、804…マッチングボックス、805…RF励起領域、806…酸素プラズマ、807…ウェハ処理領域、808…ステージ、809…スロットルバルブ、810…排気ポンプ、811…圧力計、812…発光信号検出器、813…RFコイル。

【技術分野】

【0001】

本発明は、半導体ウェハ上にある半導体素子からの、不純物の外方拡散を抑制する方法を提供することを目的とした半導体素子の製造方法及び半導体素子に関する。

【背景技術】

【0002】

半導体ウェハ上に形成されたポリシリコン領域からの不純物の外方拡散を防止し、ポリシリコンの比抵抗を安定化させる方法が背景技術として知られている。この背景技術について、まず説明する。

【0003】

半導体ウェハ上に酸化珪素膜を形成した後、ポリシリコン膜を形成し、次にフォトリソグラフ工程を用いて、所望のポリシリコン領域を残してポリシリコン膜をエッチングし除去する。

【0004】

続けてサイドウォールを形成した後、CVD(Chemical Vapor Deposition:化学気相成長)法を用いて不純物の外方拡散を防止するための酸化珪素膜を10nm程度形成する。

【0005】

次にN+領域を形成する領域にのみレジストを開口し、燐などのイオン注入を行う。このイオン注入により所望のポリシリコン領域にN型の不純物を導入する。続けて、P+、領域を形成する領域にのみレジストを開口し、硼素等のイオン注入を行うことで所望のポリシリコン領域にP型の不純物をイオン注入により導入する。

【0006】

イオン注入後、CVD法による酸化珪素膜を外方拡散防止膜とし、アニールによる活性化処理を行う。アニールを行うことでポリシリコンからの不純物の外方拡散を防止しながら不純物を活性化し、安定した抵抗値を有するポリシリコン領域を形成する。

【0007】

続けて、特許文献に示されている技術について以下に概略を説明する。

【0008】

特許文献1では、レジストを灰化する時に、レジストがついていない部分に付随的に形成される酸化珪素膜(特許文献中では、酸化膜と記載されている)を外方拡散の防止膜として用い、ポリシリコン領域からの外方拡散を防止している。

【0009】

また、特許文献2では、外方拡散を防止するための酸化珪素膜をCVD法で成膜する。成膜後、酸素と水素の混合ガス中で熱処理を行うことで、熱酸化膜と比べ欠陥の多いCVD膜中の欠陥を修復するようにしている。

【0010】

【特許文献1】特開2001−7220号公報

【特許文献2】特開平5−55482号公報

【発明の開示】

【発明が解決しようとする課題】

【0011】

しかしながら、サイドウォールを形成する時には、ポリシリコン領域が露出するまで酸化珪素膜を異方性ドライエッチングし除去する工程が必要となる。ドライエッチングを行った後のポリシリコン領域は、ドライエッチングによりダメージを受けている。

【0012】

この技術では、ダメージに対応する処置を行わずにCVD法により酸化珪素膜を形成しているため、ポリシリコン領域のダメージが修復されていない状態で酸化珪素膜に埋め込まれることとなる。従って、デバイス特性は残留したダメージの影響を受けて不安定なものとなるおそれがあった。

【0013】

また、特許文献1に示された方法では、TEOS(テトラエトキシシラン)を用いてCVD法で製造された酸化珪素膜をレジストマスクでエッチングし所望のパターンを得てイオン注入等の工程を行った後、レジスト除去とプラズマ酸化を同時に灰化工程で行っている。

【0014】

そのため、レジストマスクの下側にあるポリシリコンは、プラズマ酸化を受けることなく、ポリシリコン上に直接CVD膜が形成されることとなる。つまり、エッチング処理で荒れた界面上に、界面のダメージを修復する工程を行うことなく、CVD法により形成された酸化珪素膜が成膜されることとなる。そのため、ポリシリコン領域にはエッチング時のダメージがそのまま残留することとなり、デバイス特性が不安定なものとなるおそれがあった。

【0015】

さらに、レジスト除去とプラズマ酸化を同時に行っていることから後述するレジストの「焦げ」が生じない条件でプラズマ酸化を行う必要が生じ、プラズマ酸化の処理速度を抑える必要があり、生産性が低下する問題も抱えていた。

【0016】

ここで、「焦げ」について説明する。「焦げ」はレジストの灰化速度を上げすぎた時、レジスト上に発生する物質である。「焦げ」の分子構造等は不明であるが、「焦げ」は灰化でも、硫酸を主としたウェットエッチングでも除去することができない物質であることが経験的に知られており、一旦、「焦げ」ができると除去が困難となるため、「焦げ」が発生しない範囲でレジストの灰化を行うことが必要となる。

【0017】

また、特許文献2に示された方法では、CVD法で形成された酸化珪素膜とポリシリコン膜との間に生じる欠陥は修復されるものの、熱処理を行うために起こる半導体ウェハ上の不純物の再分布を防ぐことができないため、特に微細構造を有する半導体素子を製造する方法への展開が困難となる問題があった。

【0018】

そこで、本発明は、ポリシリコン領域の、ドライエッチングによるダメージを修復し、プラズマ酸化の速度を「焦げ」の発生を回避した上で向上させることでスループットを上げ、かつ半導体ウェハ内部の不純物の再分布を抑制した半導体素子の製造方法及び半導体素子を提供することにある。

【課題を解決するための手段】

【0019】

上記目的を達成するために、本発明の半導体素子の製造方法は、半導体ウェハ上の一主面上に配置されたレジストを、前記レジストの存在を示す信号が検出されている期間では、酸化性を有するプラズマを用いて前記レジストを灰化処理し除去する処理を行い、前記レジストの存在を示す信号が略消滅した後は、前記灰化処理の条件と比べ、前記半導体ウェハの前記一主面上にあるポリシリコンの酸化速度を上げた条件で酸化処理を行う。

【0020】

この製造方法によれば、ポリシリコンの酸化時にはレジストの灰化時にはレジストの灰化に適した条件でレジストを灰化するため、レジストの「焦げ」発生を抑えられる。そして、レジストが略消滅した時点から酸化速度を上げるため、レジストの「焦げ」発生を抑えた状態で処理速度の高いプラズマ酸化を実現することができる。さらに、レジストがほぼ消失した後で酸化速度を上げるため、レジストの有無による酸化珪素膜の膜厚分布を小さく抑えることができる。

【0021】

また、本発明の半導体素子の製造方法は、前記信号は一酸化炭素プラズマの発光色を示す発光信号であることを特徴とする。

【0022】

この製造方法によれば、プラズマ中に含まれているレジスト起因の物質による発光輝線をモニタすることで、レジストが半導体ウェハ上に残留しているか否かを知ることができ、適切なタイミングで酸化速度を上げる条件に切り替えることが可能となる。

【0023】

また、本発明の半導体素子の製造方法は、前記灰化処理及び前記酸化処理はプラズマ発生領域とウェハ処理領域が同一反応管の内部にあり、前記プラズマ発生領域より前記ウェハ処理領域へとプラズマを導き前記半導体ウェハをプラズマ処理するダウンフロー型装置を用いて前記半導体ウェハの処理を行なうことを特徴とする。

【0024】

この製造方法によれば、プラズマを、ウェハと離れたところで発生させることができる。そのためプラズマ発生領域で発生プラズマを発生させるプラズマ放電部と灰化処理部とを空間的に離すことができ、ダメージを起こす荷電粒子を放電部に閉じ込めて、活性種(ラジカル)を主とした反応雰囲気を下流に位置した処理部に送り込み、この反応雰囲気でレジストの除去を行わせることで、低ダメージな灰化及びプラズマ酸化が可能となる。

【0025】

また、本発明の半導体素子の製造方法は、前記灰化処理は、前記半導体ウェハの単位平方センチあたりの面積に対してプラズマ励起用のRF電力を1.6W〜4.5Wの範囲で印加し、かつ灰化時の反応圧力を53Pa〜133Paの範囲で灰化が行うことを特徴とする。

【0026】

この製造方法によれば、後述するレジストの「焦げ」発生を防ぐことができ、かつプラズマを安定して立てられるため、安定したプラズマを維持した状態で灰化を行うことが可能となる。

【0027】

また、本発明の半導体素子の製造方法は、前記酸化処理は、前記半導体ウェハの単位平方センチあたりの面積に対してプラズマ励起用のRF電力を4.8W〜9.6Wの範囲で印加し、かつ酸化時の反応圧力を13Pa〜66Paの範囲で酸化が行うことを特徴とする。

【0028】

この製造方法によれば、酸化速度を灰化時に比べ上げることができるため、半導体ウェハの処理速度を実用的な速度に引き上げることが可能となる。

【0029】

また、本発明の半導体素子は上記半導体素子の製造方法で製造されている。

【0030】

この構成によれば、ポリシリコン全面が酸化珪素膜で覆われるため、ポリシリコンからの外方拡散が抑えられ、ポリシリコンの抵抗値が安定する。また、熱処理を行っていないため、半導体ウェハ内部での不純物再分布を生じさせることがない。そのため、微細化に適した半導体素子を得ることが可能となる。

【発明を実施するための最良の形態】

【0031】

本発明を具体化した一実施形態について、図面を参照して説明する。図1〜7は本発明を実施した時の工程断面図である。この工程断面図は本実施形態を説明するためのもので、膜厚などの比率は説明の都合上、実際のものと変えている場合がある。また、図8はレジストの灰化及びプラズマ酸化膜形成に用いられる、灰化装置の概略を示す断面図である。

【0032】

まず、図1について説明する。図1はポリシリコン配線を形成した後の工程断面図である。半導体ウェハ101の第一主面上に形成したSTI(Shallow Trench Isolation:浅溝素子分離)領域102上にポリシリコンからなるN型配線部103、P型配線部104が形成されている。

【0033】

次に、図2について説明する。図2は酸化珪素膜でサイドウォールを形成した後の工程断面図である。酸化珪素膜をCVD(Chemical Vapor Deposition:化学気相成長)法にて成膜し、その後異方性を有するドライエッチングを行うことでサイドウォール201を形成している。このドライエッチングは、N型配線部103、P型配線部104の上部が露出するまで行うため、N型配線部103、P型配線部104はドライエッチングによるダメージを受けている。

【0034】

次に、図3について説明する。図3はN型配線部への不純物導入工程を行った後の工程断面図である。

【0035】

半導体ウェハの第一主面にレジスト301を塗布し、N型配線部103が形成される領域のみ開口し、例えば砒素302を打ち込みエネルギーを30KeV、ドーズ量を3e15cm-2程度でイオン注入する。この工程により、N型配線部103にN型の不純物となる砒素が導入される。

【0036】

ここで、灰化装置800について図面を用いて簡単に説明する。図8は、灰化装置の概略の断面図である。石英で作られたチャンバー801には、MFC(マスフローコントローラ)802を通して酸素が導入される。

【0037】

そして、チャンバー801内部に酸素プラズマ806を立てるため、RF駆動電源803から13.56MHzのRF電力を、インピーダンス整合をとるためのマッチングボックス804を通して、RFコイル813に供給する。チャンバー801中に導入された酸素がRF励起領域805に流れていき、RF電力により励起され、酸素プラズマ806が発生する。

【0038】

酸素プラズマ806はガスフローに従って下流に流れていき、ウェハ処理領域807に導かれていく。ウェハ処理領域807には、金属アルミニウムの周りを酸化アルミニウムでコーティングしたステージ808が備えられている。ステージ808上には、半導体ウェハ101が置かれている。酸素プラズマ806はウェハ処理領域807にあるステージ808に置かれた半導体ウェハ101上に導かれ、半導体ウェハ101上で灰化やプラズマ酸化等の工程が行われる。そして、灰化やプラズマ酸化等の工程を終えた酸素プラズマ806は、さらに下流側に設置されているスロットルバルブ809、排気ポンプ810を通して外部へ排気されていく。

【0039】

スロットルバルブ809は、チャンバー801の下流部に備えられた圧力計811からフィードバックを受けて制御されており、常に所定の圧力を維持するよう制御されている。

【0040】

また、チャンバー801の外側には、プラズマの発光スペクトルをモニタする発光信号検出器812が備えられている。有機物であるレジストを酸素で灰化する際には、一酸化炭素が発生する。そこで、この一酸化炭素の発光信号をモニタすることで半導体ウェハ101上のレジストの有無を判別することができる。

【0041】

上述の灰化装置800を用いてレジスト301を灰化する。アッシングの条件は、直径8インチ(≒20cm)の半導体ウェハ101を用いた場合、例えばRF電力1000W、反応圧力500mTorr(≒67Pa)で行われる。灰化に必要とされるRF電力は半導体ウェハ101の面積で規格化することができ、1000W、8インチの半導体ウェハ101を処理する場合、約3.2W/cm2で灰化を行うこととなる。例えば、ウェハの直径を変えた場合には、3.2W/cm2とウェハの面積を掛ければ、必要となるRF電力を求めることができる。

【0042】

本実施形態では、3.2W/cm2、67Paという条件で灰化を行っているが、これはRF電力として1.6W/cm2〜4.5W/cm2、反応圧力として53Pa〜133Paの範囲で設定可能である。1.6W/cm2未満のRF電力を用いると、プラズマが立たなくなり灰化が行えなくなる。また4.5W/cm2を超えるRF電力を用いると、レジストに「焦げ」が発生してしまう。また、53Pa未満の反応圧力、133Paを超える反応圧力を用いると、プラズマが立たなくなり灰化が行えなくなる。

【0043】

より望ましいプロセス条件範囲としては、RF電力として2.5W/cm2〜3.8W/cm2、反応圧力として66Pa〜110Paがより望ましい範囲となる。この範囲内では、プラズマが安定して立ち、しかもレジストの「焦げ」発生の心配はほぼ無く、適切な灰化レートが得られる。

【0044】

本実施形態で用いた値である3.2W/cm2、67Paという条件で灰化すると、半導体ウェハ101の状態にもよるが、おおよそ1分程度で灰化が完了する。この条件で灰化した場合、レジスト301が無い領域でのプラズマ酸化珪素膜401の膜厚は、4nm程度となる。

【0045】

図4はレジストを灰化した直後の工程断面図である。レジスト301の除去は酸素プラズマによる灰化を用いて行っている。レジスト301に覆われていないN型配線部103上にはプラズマ酸化珪素膜401が形成している。この時点では、レジスト301に覆われていたP型配線部104上にはプラズマ酸化膜401は形成されていない。レジスト301が半導体ウェハ101上から消失すると、灰化装置800についている発光信号検出器812で受ける一酸化炭素の信号強度がほぼ消失する。

【0046】

発光信号検出器812で受ける一酸化炭素の信号強度がほぼ消失した後、続けてプラズマ酸化を行う。プラズマ酸化時には、レジスト301は消失しているのでレジスト301の「焦げ」を心配する必要がなくなる。そこでRF電力を50%上げ1800W(≒6W/cm2)、また反応圧力も清浄性を保ちやすい低圧側に条件をふり、300mTorr(≒40Pa)まで下げてプラズマ酸化を行う。この状態で1分酸化を行うと、レジスト301が存在していた領域でも、5nm程度のプラズマ酸化珪素膜401が形成される。

【0047】

なお、プラズマ酸化の条件としては、本実施形態では、RF電力として6W/cm2、反応圧力として40Paを用いたが、これはRF電力として、4.8W/cm2〜9.6W/cm2、反応圧力として13Pa〜66Paの範囲で設定可能である。4.8W/cm2未満のRF電力で処理すると、形成される酸化珪素膜の膜質が悪くなるため実用的ではない。また、9.6W/cm2を超えるRF電力を加えるのは処理装置のハードウェア的な限界、具体的には異常放電が生じる可能性が出てくるため酸化処理が困難となる。また、反応圧力として13Pa未満では、プラズマが立たないため、処理が行えない。また、66Paを超える反応圧力では、酸化レートが遅くなるため実用的ではない。

【0048】

より望ましいプロセス条件範囲としては、RF電力として4.8W/cm2〜8W/cm2、反応圧力として27Pa〜53Paがより望ましい範囲となる。この範囲内では、プラズマが安定して立ち、しかも形成される酸化珪素膜の膜質も十分優れたものが得られる上、適切な酸化レートが得られる。

【0049】

図5はレジストの灰化に続けて行うプラズマ酸化が終了した直後の工程断面図である。レジスト301に覆われていた領域も、プラズマ酸化工程で酸化される。また、同時にN型配線部103、P型配線部104を形成する際に用いられたドライエッチング工程でのダメージも、プラズマ酸化膜に吸収され回復する。

【0050】

なお、プラズマ酸化時、酸化速度を上げる条件で酸化を行うと、半導体ウェハ101の処理時間はおおよそ2分(灰化1分+プラズマ酸化1分)で済む。

【0051】

一方、プラズマ酸化時、処理条件を灰化の条件をそのまま用いると、同一のプラズマ酸化珪素膜の膜厚を得るためには、2分程度の処理時間が必要となる。従って、一枚の半導体ウェハ101の処理時間はおおよそ3分(アッシング1分+プラズマ酸化2分)を必要とする。単純計算では、スループットを50%向上させることができる。半導体ウェハ101の入れ替え等の時間を考慮しても、処理能力は30%程度向上し、灰化装置400の原価償却に要する期間は30%程度短縮される。

【0052】

次に、P型配線部104への不純物導入工程を以下のように行う。

【0053】

半導体ウェハ101の第一主面にレジスト601を塗布し、P型配線部104が形成される領域のみ開口し、例えば硼素を打ち込みエネルギーを3KeV、ドーズ量を3e15cm-2程度でイオン注入する。この工程により、P型配線部104が必要な領域に不純物が導入される。図6は、レジストをパターニングした直後の工程断面図である。レジスト601は通常のフォトリソグラフ工程を用いて、所望のパターンとなるよう形成される。

【0054】

次にレジスト601を除去し、同時にプラズマ酸化珪素膜401を形成する。レジスト除去及びプラズマ酸化珪素膜401はN型配線部103を処理した条件と同一の条件を用いて処理する。この際、N型配線部103とP型配線部104は相補的に作られるため、N型配線部103の作成時にレジスト301で覆われていた領域は露出され、レジストで覆われていなかった部分はレジスト601で覆われる。従ってN型配線部103上のプラズマ酸化珪素401の膜厚とP型配線部104上のプラズマ酸化珪素401とは平準化され、半導体ウェハ101上でのN型配線部103上のプラズマ酸化珪素401の膜厚とP型配線部104上のプラズマ酸化珪素401の膜厚は、最終的には12nm程度で均一に形成される。

【0055】

図7は、灰化とプラズマ酸化が終了した直後の工程断面図である。N型配線部103とP型配線部104とを覆うプラズマ酸化膜401はN型配線部103とP型配線部104でほぼ同じ値となっており、ばらつきの少ない外方拡散防止膜が形成できている。

【0056】

なお、本実施形態では、STI領域102上のN型配線部103とP型配線部104について説明したが、NMOS、PMOSのトランジスタのゲート領域でも同様に相補的に外方拡散防止膜が形成されており、トランジスタ領域でもばらつきの少ない外方拡散防止膜が形成できている。

【0057】

また、本実施形態では、半導体ウェハ101に熱をかける処理は行われていない。従って、イオン注入等の工程で形成された半導体ウェハ101中の不純物分布はイオン注入終了後の分布をそのまま残しており、熱拡散等による不純物の拡散が生じていない。つまり、急峻な不純物分布を要する微細半導体素子の製造について優れた製造方法を得ることができた。

【0058】

次に、本実施形態の効果について記述する。

(1)レジスト301、601を灰化する期間は低いRF電力で処理しているため、レジストの「焦げ」の発生を効果的に抑えることができた。また、レジスト301、601が灰化されたタイミングでRF電力を50%程度上げることでプラズマ酸化速度を上げるため、レジストの「焦げ」の発生を抑えながら短時間でプラズマ酸化珪素膜が形成できる。

【0059】

また、CMOSを作る際には、レジスト301、601はほぼ相補的な配置を成しているため、NMOS、PMOSともほぼ同じプラズマ酸化膜膜厚を得ることができる。

(2)プラズマから発せられる一酸化炭素の発光スペクトルをモニタした信号に基づき、レジスト301、601の残りを検出するようにしたため、レジスト301、601がエッチングし終わった時から即時にプラズマ酸化に適した条件に切り替えることができ、半導体ウェハ101の一枚あたりの処理時間を短縮することができる。

(3)プラズマ発生領域とウェハ処理領域とが離れた状態で、同一反応管の内部にあり、プラズマ発生領域よりウェハ処理領域へとプラズマを移動させて半導体ウェハ101をプラズマ処理するダウンフロー型装置800を用いて半導体ウェハ101の処理を行ったため、酸素のラジカルを主体とした灰化やプラズマ酸化処理を行うことができ、イオン化した酸素を用いる場合と比べ半導体ウェハ101に与えるダメージが小さい状態で処理することができる。

(4)灰化処理をRF電力を1000W(直径8インチ≒20cmの半導体ウェハ101を使用;3.2W/cm2のRF電力を使用)、反応圧力を500mTorr(≒67Pa)、酸素を用いて灰化したため、レジスト301、601に「焦げ」を作ることなく、1ウェハあたり1分程度でアッシングを行うことができる。

(5)プラズマ酸化時のRF電力1800W(直径8インチ≒20cmの半導体ウェハ101を使用;6W/cm2のRF電力を使用)、反応圧力300mTorr(≒40Pa)、酸素を用いてプラズマ酸化したため、1ウェハあたり1分程度で外方拡散を防止するための酸化珪素膜を得ることができる。また、ドライエッチングにより発生したポリシリコンのダメージ層を酸化珪素膜にしたため、ダメージ残りを抑制することができる。

(6)ポリシリコンを用いた素子に関して、ドライエッチング起因のダメージがある部分をプラズマ酸化により取り除くと同時にプラズマ酸化珪素膜に変換したため、不純物の外方拡散をも抑えることができ、低ダメージ、高再現性を持つ半導体素子を形成することが可能となる。

<変形例>

・前記実施形態では、純酸素を用いて灰化やプラズマ酸化を行った例について述べているが、これはもちろん酸化雰囲気をもつ他のガスを用いても良い。また、灰化とプラズマ酸化との切り替えの際にガス種を変えることがあっても良い。

【0060】

・前記実施形態では、一酸化炭素の発光スペクトルをモニタしてレジストのアッシング終了を検知したが、これはもちろんレジスト由来の発光スペクトルを用いるものであれば良い。

【0061】

・前記実施形態では、発光スペクトル強度をモニタしてレジストのアッシング終了を検知する判別方法として、一酸化炭素の発光スペクトルがほぼ消失した時点としているが、これは、場合により一酸化炭素の発光スペクトルが定常状態より低下した時点や、一酸化炭素の発光スペクトルがほぼ消失してから5秒後など、一酸化炭素の発光スペクトルの変動を基に判定しても良い。

【図面の簡単な説明】

【0062】

【図1】STI領域上にポリシリコン領域を形成した直後の工程断面図。

【図2】サイドウォールを形成した後の工程断面図。

【図3】N型配線部への不純物導入工程を行った後の工程断面図。

【図4】レジストを灰化した直後の工程断面図。

【図5】プラズマ酸化が終了した直後の工程断面図。

【図6】レジストをパターニングした直後の工程断面図。

【図7】灰化とプラズマ酸化が終了した直後の工程断面図。

【図8】灰化装置の概略の断面図。

【符号の説明】

【0063】

101…半導体ウェハ、102…STI領域、103…ポリシリコンとしてのN型配線部、104…ポリシリコンとしてのP型配線部、201…サイドウォール、301…レジスト、302…砒素、401…プラズマ酸化珪素膜、601…レジスト、800…灰化装置、801…チャンバー、802…MFC、803…RF駆動電源、804…マッチングボックス、805…RF励起領域、806…酸素プラズマ、807…ウェハ処理領域、808…ステージ、809…スロットルバルブ、810…排気ポンプ、811…圧力計、812…発光信号検出器、813…RFコイル。

【特許請求の範囲】

【請求項1】

半導体ウェハ上の一主面上に配置されたレジストを、前記レジストの存在を示す信号が検出されている期間では、酸化性を有するプラズマを用いて前記レジストを灰化し除去する処理を行う工程と、前記レジストの存在を示す信号が略消滅した後は、前記灰化の条件と比べ、前記半導体ウェハの前記一主面上にあるポリシリコンの酸化速度が高い条件で、前記灰化の処理に続けて酸化処理を行う工程とを有することを特徴とする半導体素子の製造方法。

【請求項2】

前記信号は一酸化炭素プラズマの発光色を示す発光信号であることを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項3】

前記灰化処理及び前記酸化処理はプラズマ発生領域とウェハ処理領域とが離れた状態で同一反応管の内部にあり、前記プラズマ発生領域より前記ウェハ処理領域へとプラズマを移動させて前記半導体ウェハをプラズマ処理するダウンフロー型装置を用いて前記半導体ウェハの処理を行うことを特徴とする請求項1又は2に記載の半導体素子の製造方法。

【請求項4】

前記灰化処理は、前記半導体ウェハの単位平方センチあたりの面積に対してプラズマ励起用のRF電力を1.6W〜4.5Wの範囲で印加し、かつ灰化時の反応圧力を53Pa〜133Paの範囲で灰化を行うことを特徴とする請求項1〜3のいずれか一項に記載の半導体素子の製造方法。

【請求項5】

前記酸化処理は、前記半導体ウェハの単位平方センチあたりの面積に対してプラスマ励起用のRF電力を4.8W〜9.6Wの範囲で印加し、かつ酸化時の反応圧力を13Pa〜66Paの範囲で酸化を行うことを特徴とする請求項1〜4のいずれか一項に記載の半導体素子の製造方法。

【請求項6】

請求項1から5のいずれか一項に記載の製造方法で製造された半導体素子。

【請求項1】

半導体ウェハ上の一主面上に配置されたレジストを、前記レジストの存在を示す信号が検出されている期間では、酸化性を有するプラズマを用いて前記レジストを灰化し除去する処理を行う工程と、前記レジストの存在を示す信号が略消滅した後は、前記灰化の条件と比べ、前記半導体ウェハの前記一主面上にあるポリシリコンの酸化速度が高い条件で、前記灰化の処理に続けて酸化処理を行う工程とを有することを特徴とする半導体素子の製造方法。

【請求項2】

前記信号は一酸化炭素プラズマの発光色を示す発光信号であることを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項3】

前記灰化処理及び前記酸化処理はプラズマ発生領域とウェハ処理領域とが離れた状態で同一反応管の内部にあり、前記プラズマ発生領域より前記ウェハ処理領域へとプラズマを移動させて前記半導体ウェハをプラズマ処理するダウンフロー型装置を用いて前記半導体ウェハの処理を行うことを特徴とする請求項1又は2に記載の半導体素子の製造方法。

【請求項4】

前記灰化処理は、前記半導体ウェハの単位平方センチあたりの面積に対してプラズマ励起用のRF電力を1.6W〜4.5Wの範囲で印加し、かつ灰化時の反応圧力を53Pa〜133Paの範囲で灰化を行うことを特徴とする請求項1〜3のいずれか一項に記載の半導体素子の製造方法。

【請求項5】

前記酸化処理は、前記半導体ウェハの単位平方センチあたりの面積に対してプラスマ励起用のRF電力を4.8W〜9.6Wの範囲で印加し、かつ酸化時の反応圧力を13Pa〜66Paの範囲で酸化を行うことを特徴とする請求項1〜4のいずれか一項に記載の半導体素子の製造方法。

【請求項6】

請求項1から5のいずれか一項に記載の製造方法で製造された半導体素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2006−41327(P2006−41327A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2004−221379(P2004−221379)

【出願日】平成16年7月29日(2004.7.29)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成16年7月29日(2004.7.29)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]