半導体素子の製造方法

【課題】Siウエハ等の半導体基板上に形成された特に高アスペクト比の穴に、バリア層やAl層等となるターゲット材料を成膜した際に、穴の側壁面及び底面をターゲット材料で完全に覆うことを可能にすることにより、スパイクの発生や導通不良の発生を防止することが可能な、半導体素子の製造方法を提供する。

【解決手段】半導体基板1上の絶縁層2に穴3を形成する。ターゲット5と半導体基板1との距離を第1の値L2とする第1のスパッタリングによってターゲット材料5aを穴3に成膜し、上記距離を第1の値L2よりも小さい第2の値L1とする第2のスパッタリングにより、ターゲット材料5aを穴3に成膜する。第1のスパッタリングは異方性スパッタリングであり、第2のスパッタリングは等方性スパッタリングである。また、第1のスパッタリングはロングスロースパッタである。

【解決手段】半導体基板1上の絶縁層2に穴3を形成する。ターゲット5と半導体基板1との距離を第1の値L2とする第1のスパッタリングによってターゲット材料5aを穴3に成膜し、上記距離を第1の値L2よりも小さい第2の値L1とする第2のスパッタリングにより、ターゲット材料5aを穴3に成膜する。第1のスパッタリングは異方性スパッタリングであり、第2のスパッタリングは等方性スパッタリングである。また、第1のスパッタリングはロングスロースパッタである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子の製造方法に係り、特に、半導体基板上に形成された高アスペクト比の穴に、ターゲット材料をスパッタリングにより成膜する成膜工程を有する半導体素子の製造方法に関する。

【背景技術】

【0002】

半導体素子を製造する過程において、一般的に、Si(シリコン)ウエハ等の半導体基板上に絶縁層を形成し、この絶縁層に穴を形成した後、この穴に例えばTi(チタン)やTiN(窒化チタン)等からなるバリア層及びAl(アルミニウム)層をそれぞれスパッタリングにより成膜する成膜工程がある。成膜された上記穴は半導体基板に導通するビアホールとなる。

【0003】

ところで、半導体素子におけるさらなる高集積化及び高密度配線化により、高アスペクト比のビアホールを安定して形成することが重要になってきている。ここで、高アスペクト比とは、ビアホール(穴)の直径に対する深さの比率が2以上のものを称す。

【0004】

高アスペクト比の穴に、バリア層やAl層等となる所定のターゲット材料を、通常のスパッタリングにより成膜した場合の課題について、図12を用いて説明する。

図12は、高アスペクト比の穴にバリア層やAl層等となるターゲット材料を通常のスパッタリングにより成膜した場合の課題を説明するための模式的断面図であり、同図中の(a)は通常のスパッタリングを説明するためのものであり、(b)は高アスペクト比の穴にターゲット材料が成膜された状態を示すものである。

【0005】

図12(a)に示すように、通常のスパッタリングは、特定の成膜方向性を有さない等方性のスパッタリングである。このため、図12(b)に示すように、半導体基板100の中央部の穴102a及び外周部の穴102bには、ターゲット104を構成するターゲット材料104aが同じような付き回り性を有して成膜されるものの、絶縁層106のエッジ部E106に集中的に成膜されるため、成膜が進むにつれて、穴102a,102bの開口部A102が特に狭くなる。

このため、通常のスパッタリングでは、ターゲット材料104aは、穴102a,102bの側壁面B102を覆って成膜される一方、底面C102が完全に覆われずに成膜される場合がある。

穴102a,102bの底面C102がターゲット材料104aで完全に覆われていないと、Al層からSiウエハ100へのAlの異常成長によるスパイクが発生してリーク電流が増加したり、穴102a,102bへの他のターゲット材料の埋め込み性が悪化して導通不良が発生する場合がある。

【0006】

そこで、上記課題を解決するための手段として、ロングスロースパッタ法を用いてターゲット材料を成膜する成膜方法がある(例えば特許文献1)。

【特許文献1】特開2005−33218号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

ここで、高アスペクト比の穴に、バリア層やAl層等となるターゲット材料を、ロングスロースパッタ法により成膜した場合の課題について、図13を用いて説明する。

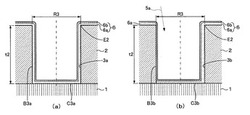

図13は、高アスペクト比の穴にバリア層やAl層等となるターゲット材料をロングスロースパッタ法により成膜した場合の課題を説明するための模式的断面図であり、同図中の(a)はロングスロースパッタ法を説明するためのものであり、(b)は半導体基板200の中央部に形成された高アスペクト比の穴202aを、(c)は外周部に形成された高アスペクト比の穴202bを、それぞれ示すものである。

【0008】

図13(a)に示すように、ロングスロースパッタ法は、ターゲット204と半導体基板200との距離L200が、図12(a)に示す通常のスパッタリングの距離L100よりも長いので、特定の成膜方向性を有する異方性のスパッタリングである。また、ロングスロースパッタ法は、通常のスパッタリングよりも成膜速度が遅い。

このため、ロングスロースパッタ法を用いれば、通常のスパッタリングのようにターゲット材料204aが絶縁層206のエッジ部E206に集中的に成膜されることを防止することができる。

【0009】

しかしながら、ロングスロースパッタ法では、図13(b)に示すように、半導体基板200の中央部では、ターゲット204を構成するターゲット材料204aが、穴202aの側壁面B202a及び底面C202aを覆って良好に成膜されるものの、図13(c)に示すように、半導体基板200の外周部では、ターゲット材料204aが穴202bに対して斜め上方から浅い角度で成膜されるため、穴202bの底面C202bをターゲット材料204aで覆うことは可能であるが、穴202bの側壁面B202bがターゲット材料204aで完全に覆わずに成膜される場合がある。

穴202bの側壁面B202bがターゲット材料204aで完全に覆われていないと、この穴202bへの他のターゲット材料を成膜した際の埋め込み性が悪化して導通不良が発生する場合がある。

【0010】

そこで、本発明が解決しようとする課題は、Siウエハ等の半導体基板上に形成された特に高アスペクト比の穴に、バリア層やAl層等となるターゲット材料を成膜した際に、穴の側壁面及び底面をターゲット材料で完全に覆うことを可能にすることにより、スパイクの発生や導通不良の発生を防止することが可能な、半導体素子の製造方法を提供することにある。

【課題を解決するための手段】

【0011】

上記の課題を解決するために、本願各発明は次の半導体素子の製造方法を提供する。

1)半導体基板(1)上に形成されている絶縁層(2)に穴(3)を形成する穴形成工程と、前記穴形成工程の後に、ターゲット(5)と前記半導体基板との距離を第1の値(L2)とする第1のスパッタリングにより、前記ターゲットを構成するターゲット材料(5a)を前記穴に成膜する第1の成膜工程と、前記第1の成膜工程の後に、前記半導体基板と前記ターゲットとの距離を、前記第1の値よりも小さい第2の値(L1)とする第2のスパッタリングにより、前記ターゲット材料を前記穴に成膜する第2の成膜工程と、を有することを特徴とする半導体素子の製造方法。

2)前記第1のスパッタリングは異方性を有するスパッタリングであり、前記第2のスパッタリングは等方性を有するスパッタリングであることを特徴とする1)記載の半導体素子の製造方法。

3)前記第1のスパッタリングはロングスロースパッタであることを特徴とする1)または2)記載の半導体素子の製造方法。

4)前記穴形成工程は、前記絶縁層上に、開口部を有するレジスト層を形成する第1の形成工程と、前記第1の形成工程の後に、前記レジスト層をマスクとして前記絶縁層に等方性のエッチングを行って、前記絶縁層に所定の開口径を有する凹部を形成する第2の形成工程と、前記第2の形成工程の後に、前記レジスト層をマスクとして、前記凹部が形成されている領域の前記絶縁層に異方性のエッチングを行って、前記凹部に連接し前記開口径よりも小さい穴径を有する穴を形成する第3の形成工程と、前記第3の形成工程の後に、前記レジスト層を除去する除去工程と、を有することを特徴とする1)乃至3)のいずれかに記載の半導体素子の製造方法。

【発明の効果】

【0012】

本発明によれば、Siウエハ等の半導体基板上に形成された特に高アスペクト比の穴に、バリア層やAl層等となるターゲット材料を成膜した際に、穴の側壁面及び底面をターゲット材料で完全に覆うことが可能になるので、スパイクの発生や導通不良の発生を防止することができるという効果を奏する。

【発明を実施するための最良の形態】

【0013】

本発明の実施の形態を、好ましい実施例である第1実施例及び第2実施例により図1〜図11を用いて説明する。

【0014】

<第1実施例>

以下に説明する第1工程〜第6工程は、本発明に係る半導体素子の製造方法における製造過程をそれぞれ示すものである。

[第1工程]

第1工程を、図1を用いて説明する。図1は、本発明に係る半導体素子の製造方法の第1実施例における第1工程を説明するための模式的断面図である。

【0015】

図1に示すように、半導体基板1上に絶縁層2を熱酸化処理や成膜等の周知の半導体プロセスにより形成する。

第1実施例では、半導体基板1として直径が6インチのSi(シリコン)ウエハを用い、絶縁層2の材料としてSiO2(二酸化シリコン)を用いてその厚さt2を0.8μmとした。

【0016】

次に、絶縁層2に、ドライエッチングやウェットエッチング等の周知の半導体プロセスを用いて、半導体基板1の中央部及び外周部を含む全域に亘って、半導体基板1を露出させる高アスペクト比の穴3を複数形成する。

ここで、高アスペクト比とは、穴3の直径R3に対する深さt2の比率t2/R3が2以上のものを称す。

第1実施例では、穴3の直径R3を0.3μmとした。従って穴3のアスペクト比は2.7(小数点以下2桁目を四捨五入)である。

なお、図1では、説明をわかりやすくするために、複数形成された穴3のうち、半導体基板1の中央部に形成された穴3aと、外周部に形成された穴3bの2つの穴3を抜粋して示している。

【0017】

[第2工程]

第2工程を、図2,図12(a),及び図13(a)を用いて説明する。

図2は、本発明に係る半導体素子の製造方法の第1実施例における第2工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第1バリア層6がそれぞれ形成された状態を示すものである。

【0018】

図13(a)に示すように、第1のターゲット5の構成材料である第1のターゲット材料5aを、半導体基板1上に形成された絶縁層2上に、まず異方性のスパッタリングであるロングスロースパッタ法を用いて成膜した後に、さらに、図12(a)に示すように、等方性のスパッタリングである通常のスパッタリングを用いて成膜することにより、所定の厚さの第1のバリア層6を形成する(図2参照)。

ここで、第1のバリア層6において、ロングスロースパッタ法により成膜された膜を6a、その後に通常のスパッタリングにより成膜された膜を6bとそれぞれ末尾に符号を付す。

【0019】

前述したように、ロングスロースパッタ法は、第1のターゲット5と半導体基板1との距離L2が通常のスパッタリングの距離L1よりも長いので、特定の成膜方向性を有する異方性のスパッタリングであり、また、通常のスパッタリングよりも成膜速度が遅いため、第1のターゲット材料5aが絶縁層2のエッジ部E2に集中的に成膜されることを防止することができる。

従って、第1のバリア層6aが成膜された後の穴3a,3bは広い開口部を有しているため、次に行う通常のスパッタリングによる第1のバリア層6bを上記穴3a,3bにそれぞれ付き回りよく成膜することができる。

【0020】

また、前述したように、ロングスロースパッタ法では、図2(b)に示すように、半導体基板1の外周部では、第1のターゲット材料5aが穴3bに対して斜め上方から浅い角度で成膜されるため、穴3bの底面C3bを第1のバリア層6aで覆うことは可能であるが、穴3bの側壁面B3bが第1のバリア層6aで完全に覆われずに成膜される場合がある。

【0021】

このような場合においても、穴3bが広い開口部を有した状態で通常のスパッタリングを行うことができるため、穴3bの側壁面B3b及び底面C3bを、その後に成膜される第1のバリア層6bで完全に覆うことができる。

【0022】

第1実施例では、第1のターゲット5と半導体基板1との距離L1を5cmとし、L2を30cmとした。

また、第1実施例では、第1のターゲット材料5aとしてTi(チタン)を用い、第1のバリア層6aの厚さ(絶縁層2上の厚さ)を16nmとし、第1のバリア層6bの厚さ(絶縁層2上の厚さ)を4nmとした。

【0023】

上述した手順によれば、まず、異方性のスパッタリングであるロングスロースパッタ法により、半導体基板1の中央部及び外周部を含む全域に亘って形成された複数の高アスペクト比の穴3a,3bの各底面C3a,C3bを第1のバリア層6aで完全に覆うことができる。

また、穴3bの側壁面B3bが第1のバリア層6aで完全に覆われていない場合においても、その後に等方性のスパッタリングである通常のスパッタリングにより成膜される第1のバリア層6bでこれら側壁面B3bを完全に覆うことができる。即ち、高アスペクト比の穴3a,3bの側壁面B3a,B3b及び底面C3a,C3bを第1のバリア層6で完全に覆うことができる。

【0024】

[第3工程]

第3工程を、図3,図12(a),及び図13(a)を用いて説明する。

図3は、本発明に係る半導体素子の製造方法の第1実施例における第3工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第2バリア層9がそれぞれ形成された状態を示すものである。

【0025】

図13(a)に示すように、第2のターゲット8の構成材料である第2のターゲット材料8aを、第2工程を経た半導体基板1上に、まず異方性のスパッタリングであるロングスロースパッタ法を用いて成膜した後に、さらに、図12(a)に示すように、等方性のスパッタリングである通常のスパッタリングを用いて成膜することにより、第2のバリア層9を形成する(図3参照)。

その後、アニール処理を行って、第1のバリア層6と第2のバリア層9とを相互拡散により一体化させる。

第2のバリア層9は、後述する第1のAl層15及び第2のAl層17のAl原子が半導体基板1の内部に異常成長することによって発生するスパイクによるリーク電流の増加を防止する機能を有する。

ここで、第2のバリア層9において、ロングスロースパッタ法により成膜された膜を9a、その後に通常のスパッタリングにより成膜された膜を9bとそれぞれ末尾に符号を付す。

【0026】

前述したように、ロングスロースパッタ法は、第2のターゲット8と半導体基板1との距離L4が、通常のスパッタリングの距離L3よりも長いので、特定の成膜方向性を有する異方性のスパッタリングであり、また、通常のスパッタリングよりも成膜速度が遅いため、第2のターゲット材料8aが絶縁層2のエッジ部E2に集中的に成膜されることを防止することができる。

従って、第2のバリア層9aが成膜された後の穴3a,3bは広い開口部を有しているため、次に行う通常のスパッタリングによる第2のバリア層9bを上記穴3a,3bに付き回りよくそれぞれ成膜することができる。

【0027】

また、前述したように、ロングスロースパッタ法では、図3(b)に示すように、半導体基板1の外周部では第2のターゲット材料8aが穴3bに対して斜め上方から浅い角度で成膜されるため、第1のバリア層6で覆われている穴3bの底面C3bを第2のバリア層9aで覆うことは可能であるが、穴3bの側壁面B3bを覆う第1のバリア層6が第2のバリア層9aで完全に覆われない場合がある。

【0028】

このような場合においても、穴3bが広い開口部を有した状態で通常のスパッタリングを行うことができるため、穴3bの側壁面B3b及び底面C3bを覆う第1のバリア層6を、第2のバリア層9bで完全に覆うことができる。

【0029】

第1実施例では、第2のターゲット8と半導体基板1との距離L3を5cmとし、L4を30cmとした。

また、第1実施例では、第2のターゲット材料8aとしてTiN(窒化チタン)を用い、第2のバリア層9aの厚さ(絶縁層2上の厚さ)を80nmとし、第2のバリア層9bの厚さ(絶縁層2上の厚さ)を20nmとした。

【0030】

上述した手順によれば、まず、異方性のスパッタリングであるロングスロースパッタ法により、半導体基板1の中央部及び外周部を含む全域に亘って形成された複数の高アスペクト比の穴3a,3bの各底面C3a,C3bを、第2のバリア層9aで完全に覆うことができる。

また、穴3bの側壁面B3bが第2のバリア層9aで完全に覆われていない場合においても、その後に等方性のスパッタリングである通常のスパッタリングにより成膜される第2のバリア層9bでこの側壁面B3bを完全に覆うことができる。即ち、第2工程を経た高アスペクト比の穴3a,3bの側壁面B3a,B3b及び底面C3a,C3bを第2のバリア層9で完全に覆うことができる。

【0031】

[第4工程]

第4工程を、図4,図12(a),及び図13(a)を用いて説明する。

図4は、本発明に係る半導体素子の製造方法の第1実施例における第4工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第3バリア層12がそれぞれ形成された状態を示すものである。

【0032】

図13(a)に示すように、第3のターゲット11の構成材料である第3のターゲット材料11aを、第3工程を経た半導体基板1上に、まず異方性のスパッタリングであるロングスロースパッタ法を用いて成膜した後に、さらに、図12(a)に示すように、等方性のスパッタリングである通常のスパッタリングを用いて成膜することにより、第3のバリア層12を形成する(図4参照)。

第3のバリア層12は、後述する第1のAl層15及び第2のAl層17との密着性を向上させて、これらAl層15,17の埋め込み性を良好にする機能を有する。

ここで、第3のバリア層12において、ロングスロースパッタ法により成膜された膜を12a、その後に通常のスパッタリングにより成膜された膜を12bとそれぞれ末尾に符号を付す。

【0033】

前述したように、ロングスロースパッタ法は、第3のターゲット11と半導体基板1との距離L6が通常のスパッタリングの距離L5よりも長いので、特定の成膜方向性を有する異方性のスパッタリングであり、また、通常のスパッタリングよりも成膜速度が遅いため、第3のターゲット材料11aが絶縁層2のエッジ部E2に集中的に成膜されることを防止することができる。

従って、第3のバリア層12aが成膜された後の穴3a,3bは広い開口部を有しているため、次に行う通常のスパッタリングによる第3のバリア層12bを上記穴3a,3bに付き回りよくそれぞれ成膜することができる。

【0034】

また、前述したように、ロングスロースパッタ法では、図4(b)に示すように、半導体基板1の外周部では、第3のターゲット材料11aが穴3bに対して斜め上方から浅い角度で成膜されるため、第2のバリア層9で覆われている穴3bの底面C3bを第3のバリア層12aで覆うことは可能であるが、穴3bの側壁面B3bを覆う第2のバリア層9が第3のバリア層12aで完全に覆われない場合がある。

【0035】

このような場合においても、穴3bが広い開口部を有した状態で通常のスパッタリングを行うことができるため、穴3bの側壁面B3b及び底面C3bを覆う第2のバリア層9を第3のバリア層12bで完全に覆うことができる。

【0036】

第1実施例では、第3のターゲット11と半導体基板1との距離L5を5cmとし、L6を30cmとした。

また、第1実施例では、第3のターゲット材料11aとしてTiを用い、第2のバリア層12aの厚さ(絶縁層2上の厚さ)を40nmとし、第3のバリア層12bの厚さ(絶縁層2上の厚さ)を10nmとした。

【0037】

上述した手順によれば、まず、異方性のスパッタリングであるロングスロースパッタ法により、半導体基板1の中央部及び外周部を含む全域に亘って形成された複数の高アスペクト比の穴3a,3bの各底面C3a,C3bを第3のバリア層12aで完全に覆うことができる。

また、穴3bの側壁面B3bが第3のバリア層12aで完全に覆われていない場合においても、その後に等方性のスパッタリングである通常のスパッタリングにより成膜される第3のバリア層12bでこの側壁面B3bを完全に覆うことができる。即ち、第3工程を経た高アスペクト比の穴3a,3bの側壁面B3a,B3b及び底面C3a,C3bを第3のバリア層12で完全に覆うことができる。

【0038】

[第5工程]

第5工程を、図5,図12(a),及び図13(a)を用いて説明する。

図5は、本発明に係る半導体素子の製造方法の第1実施例における第5工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第1のAl層15がそれぞれ形成された状態を示すものである。

【0039】

図13(a)に示すように、第4のターゲット14の構成材料である第4のターゲット材料14aのAl(アルミニウム)を、第4工程を経た半導体基板1上に、まず異方性のスパッタリングであるロングスロースパッタ法を用いて成膜した後に、さらに、図12(a)に示すように、等方性のスパッタリングである通常のスパッタリングを用いて成膜することにより、第1のAl層15を形成する(図5参照)。

ここで、第1のAl層15において、ロングスロースパッタ法により成膜された膜を15a、その後に通常のスパッタリングにより成膜された膜を15bとそれぞれ末尾に符号を付す。

【0040】

前述したように、ロングスロースパッタ法は、第4のターゲット14と半導体基板1との距離L8が、通常のスパッタリングの距離L7よりも長いので、特定の成膜方向性を有する異方性のスパッタリングであり、また、通常のスパッタリングよりも成膜速度が遅いため、第4のターゲット材料14aが絶縁層2のエッジ部E2に集中的に成膜されることを防止することができる。

従って、第1のAl層15aが成膜された後の穴3a,3bは広い開口部を有しているため、次に行う通常のスパッタリングによる第1のAl層15bを上記穴3a,3bにそれぞれ付き回りよく成膜することができる。

【0041】

また、前述したように、ロングスロースパッタ法では、図5(b)に示すように、半導体基板1の外周部では、第4のターゲット材料14aが穴3bに対して斜め上方から浅い角度で成膜されるため、第3のバリア層12で覆われている穴3bの底面C3bを第1のAl層15aで覆うことは可能であるが、穴3bの側壁面B3bを覆う第3のバリア層12が第1のAl層15aで完全に覆われない場合がある。

【0042】

このような場合においても、穴3bが広い開口部を有した状態で通常のスパッタリングを行うことができるため、穴3bの側壁面B3b及び底面C3bを覆う第3のバリア層12を、その後に成膜される第1のAl層15bで完全に覆うことができる。

【0043】

第1実施例では、第4のターゲット14と半導体基板1との距離L7を5cmとし、L8を30cmとした。

また、第1実施例では、第1のAl層15aの厚さ(絶縁層2上の厚さ)を160nmとし、第1のAl層15bの厚さ(絶縁層2上の厚さ)を40nmとした。

【0044】

上述した手順によれば、まず異方性のスパッタリングであるロングスロースパッタ法により、半導体基板1の中央部及び外周部を含む全域に亘って形成された複数の高アスペクト比の穴3a,3bの各底面C3a,C3bを第1のAl層15aで完全に覆うことができる。

また、穴3bの側壁面B3bが第1のAl層15aで完全に覆われていない場合においても、その後に等方性のスパッタリングである通常のスパッタリングにより成膜される第1のAl層15bでこの側壁面B3bを完全に覆うことができる。即ち、第4工程を経た高アスペクト比の穴3a,3bの側壁面B3a,B3b及び底面C3a,C3bを第1のAl層15で完全に覆うことができる。

【0045】

[第6工程]

第6工程について図6を用いて説明する。

図6は、本発明に係る半導体素子の製造方法の第1実施例における第6工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第2のAl層17がそれぞれ形成された状態を示すものである。

【0046】

図6に示すように、フロースパッタにより、第5工程を経た半導体基板1上に、第2のAl層17を形成する。

フロースパッタとは、成膜材料(ここではAl)が流動性を有する程度に加熱しながらスパッタリングを行うものである。

そのため、第2のAl層17は、第5工程を経た穴3a,3bを埋めると共にその表面は略平坦な面になる。

また、第2のAl層17を形成する際に、その下地膜である第1のAl層15も加熱されて流動性を有するようになるため、第1のAl層15と第2のAl層17とは互いに溶け合って一体化される。

【0047】

上述した手順により、穴3a,3bは、半導体基板1と電気的に接続する高アスペクト比のビアホール20a,20bとなる。

【0048】

以降、所定の工程を行うことによって所望の半導体素子を得る。

上記所定の工程の一例として、第2のAl層17の表面に、例えばTiNを主成分とする反射防止膜を形成する工程などがある。

【0049】

ここで、上述した第1実施例の半導体素子、及び、第1実施例と同様の構成であって第1〜第3のバリア層及び第1のAl層をロングスロースパッタ法のみで成膜した比較例の半導体素子について、それぞれのスパイク発生率を調べ、その結果を表1に示す。

【0050】

【表1】

【0051】

表1に示すように、比較例の半導体素子では、半導体基板の外周部(中心から52.5mm離れた位置)に発生率50%とかなり高い確率でスパイクが発生していたのに対し、第1実施例の半導体素子では、半導体基板の中心から外周部に亘ってスパイクが発生していないことを確認した。

【0052】

次に、上述の第1実施例及び比較例の各半導体素子の高アスペクト比の穴について、Al層の埋め込み不良率を調べ、その結果を表2に示す。

【0053】

【表2】

【0054】

表2に示すように、比較例の半導体素子では、半導体基板の外周部(中心から52.5mm離れた位置)に発生率17〜30%とかなり高い確率でAl層の埋め込み不良が発生していたのに対し、第1実施例の半導体素子では、半導体基板の中心から外周部に亘って埋め込み不良が発生していないことを確認した。

【0055】

上述した半導体素子の製造方法によれば、半導体基板上に形成された高アスペクト比(例えば2以上)の穴に、バリア層やAl層等の所定の膜を、ロングスロースパッタ法と通常のスパッタリングとを順次行って成膜することにより、高アスペクト比のビアホールを、半導体基板の中央部及び外周部を含む全域に亘って安定して形成することができる。

【0056】

<第2実施例>

第2実施例は、上述した第1実施例に対して、第1工程が異なり第2工程〜第6工程は同じなので、ここでは特に第1工程について図7〜図11を用いて詳細に説明する。

図7〜図10は、本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部に穴35a(図9及び図10に図示)が、(b)は半導体基板1の外周部に穴35b(図9及び図10に図示)がそれぞれ形成される状態を示すものである。また、図7〜図10における(a),(b)は図2〜図6の(a),(b)にそれぞれ対応するものである。

図11は、本発明に係る半導体素子の製造方法の第2実施例における第1工程以降の工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴35aに、(b)は半導体基板1の外周部の穴35bに所定の膜がそれぞれ形成された状態を示すものである。また、図11における(a),(b)は図2〜図10の(a),(b)にそれぞれ対応するものである。

なお、図7〜図11において、図1〜図6と同じ構成部については説明をわかりやすくするために同じ符号を付す。

【0057】

[第1工程]

図7に示すように、まず、半導体基板1上に絶縁層2を熱酸化処理や成膜等の周知の半導体プロセスにより形成する。半導体基板1及び絶縁層2は第1実施例と同じである。

次に、絶縁層2上に、開口径がR3の開口部30a,30bを有するレジスト層31を形成する。

【0058】

その後、図8に示すように、レジスト層31をマスクとして、絶縁層2に等方性のエッチングを行うことにより、絶縁層2に凹部32a,32bを形成する。

等方性のエッチングにより、絶縁層2はその厚さ方向にエッチングされると共にその面に沿う方向にもエッチングされる。

従って、形成された凹部32a,32bの開口径R13はレジスト層31の開口径R3よりも大きくなる。

第2実施例では、等方性のエッチングを、CF4ガスを用いたドライエッチングとした。

【0059】

さらに、図9に示すように、レジスト層31をマスクとして、絶縁層2の凹部32a,32bが形成された領域に異方性のエッチングを行う。

異方性のエッチングにより、絶縁層2はその厚さ方向にエッチングされる。

これにより、絶縁層2には、直径R3の第1の径部34a,34bと直径R3よりも大きい開口径R13の第1の径部(凹部)32a,32bとが連接された穴35a,35bが形成される。

第2実施例では、異方性のエッチングを、CHF3ガスを用いたドライエッチングとした。

【0060】

次に、図10に示すように、レジスト層31を除去する。

【0061】

以上が第2実施例の第1工程である。

【0062】

その後、第1実施例の第2工程〜第6工程と同様の工程を行うことにより、図11に示すにように、穴35a,35bは、半導体基板1と電気的に接続する高アスペクト比のビアホール40a,40bとなる。

【0063】

以降、所定の工程を行うことによって所望の半導体素子を得る。

上記所定の工程の一例として、第2のAl層17の表面に、例えばTiNを主成分とする反射防止膜を形成する工程などがある。

【0064】

上述した手順によれば、穴35a,35bの開口径R13を第1実施例よりも広くすることができるので、穴35a,35bの内面への各膜6,9,12,15の付き回り性が向上するので、第1実施例よりもさらに高アスペクト比のビアホールを形成することができる。

【0065】

本発明の実施例は、上述した構成及び手順に限定されるものではなく、本発明の要旨を逸脱しない範囲において変形例としてもよいのは言うまでもない。

【0066】

例えば、第1実施例では、ビアホール(穴)のアスペクト比を2.7としたが、これに限定されるものではなく、特にアスペクト比が2以上の高アスペクト比のビアホールに対して好適である。

【図面の簡単な説明】

【0067】

【図1】本発明に係る半導体素子の製造方法の第1実施例における第1工程を説明するための模式的断面図である。

【図2】本発明に係る半導体素子の製造方法の第1実施例における第2工程を説明するための模式的断面図である。

【図3】本発明に係る半導体素子の製造方法の第1実施例における第3工程を説明するための模式的断面図である。

【図4】本発明に係る半導体素子の製造方法の第1実施例における第4工程を説明するための模式的断面図である。

【図5】本発明に係る半導体素子の製造方法の第1実施例における第5工程を説明するための模式的断面図である。

【図6】本発明に係る半導体素子の製造方法の第1実施例における第6工程を説明するための模式的断面図である。

【図7】本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図である。

【図8】本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図である。

【図9】本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図である。

【図10】本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図である。

【図11】本発明に係る半導体素子の製造方法の第2実施例における第1工程以降の工程を説明するための模式的断面図である。

【図12】通常のスパッタリングにより成膜した場合の課題を説明するための模式的断面図である。

【図13】ロングスロースパッタ法により成膜した場合の課題を説明するための模式的断面図である。

【符号の説明】

【0068】

1_半導体基板、 2_絶縁層、 3,3a,3b_穴、 5,8,11,14_ターゲット、 5a,8a,11a,14a_ターゲット材料、 6,6a,6b,9,9a,9b,12,12a,12b_バリア層、 15,15a,15b,17_Al層、 20a,20b_ビアホール、 t2_厚さ、 R3_直径、 L1〜L8_距離、 B3a,B3b_側壁面、 C3a,C3b_底面

【技術分野】

【0001】

本発明は、半導体素子の製造方法に係り、特に、半導体基板上に形成された高アスペクト比の穴に、ターゲット材料をスパッタリングにより成膜する成膜工程を有する半導体素子の製造方法に関する。

【背景技術】

【0002】

半導体素子を製造する過程において、一般的に、Si(シリコン)ウエハ等の半導体基板上に絶縁層を形成し、この絶縁層に穴を形成した後、この穴に例えばTi(チタン)やTiN(窒化チタン)等からなるバリア層及びAl(アルミニウム)層をそれぞれスパッタリングにより成膜する成膜工程がある。成膜された上記穴は半導体基板に導通するビアホールとなる。

【0003】

ところで、半導体素子におけるさらなる高集積化及び高密度配線化により、高アスペクト比のビアホールを安定して形成することが重要になってきている。ここで、高アスペクト比とは、ビアホール(穴)の直径に対する深さの比率が2以上のものを称す。

【0004】

高アスペクト比の穴に、バリア層やAl層等となる所定のターゲット材料を、通常のスパッタリングにより成膜した場合の課題について、図12を用いて説明する。

図12は、高アスペクト比の穴にバリア層やAl層等となるターゲット材料を通常のスパッタリングにより成膜した場合の課題を説明するための模式的断面図であり、同図中の(a)は通常のスパッタリングを説明するためのものであり、(b)は高アスペクト比の穴にターゲット材料が成膜された状態を示すものである。

【0005】

図12(a)に示すように、通常のスパッタリングは、特定の成膜方向性を有さない等方性のスパッタリングである。このため、図12(b)に示すように、半導体基板100の中央部の穴102a及び外周部の穴102bには、ターゲット104を構成するターゲット材料104aが同じような付き回り性を有して成膜されるものの、絶縁層106のエッジ部E106に集中的に成膜されるため、成膜が進むにつれて、穴102a,102bの開口部A102が特に狭くなる。

このため、通常のスパッタリングでは、ターゲット材料104aは、穴102a,102bの側壁面B102を覆って成膜される一方、底面C102が完全に覆われずに成膜される場合がある。

穴102a,102bの底面C102がターゲット材料104aで完全に覆われていないと、Al層からSiウエハ100へのAlの異常成長によるスパイクが発生してリーク電流が増加したり、穴102a,102bへの他のターゲット材料の埋め込み性が悪化して導通不良が発生する場合がある。

【0006】

そこで、上記課題を解決するための手段として、ロングスロースパッタ法を用いてターゲット材料を成膜する成膜方法がある(例えば特許文献1)。

【特許文献1】特開2005−33218号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

ここで、高アスペクト比の穴に、バリア層やAl層等となるターゲット材料を、ロングスロースパッタ法により成膜した場合の課題について、図13を用いて説明する。

図13は、高アスペクト比の穴にバリア層やAl層等となるターゲット材料をロングスロースパッタ法により成膜した場合の課題を説明するための模式的断面図であり、同図中の(a)はロングスロースパッタ法を説明するためのものであり、(b)は半導体基板200の中央部に形成された高アスペクト比の穴202aを、(c)は外周部に形成された高アスペクト比の穴202bを、それぞれ示すものである。

【0008】

図13(a)に示すように、ロングスロースパッタ法は、ターゲット204と半導体基板200との距離L200が、図12(a)に示す通常のスパッタリングの距離L100よりも長いので、特定の成膜方向性を有する異方性のスパッタリングである。また、ロングスロースパッタ法は、通常のスパッタリングよりも成膜速度が遅い。

このため、ロングスロースパッタ法を用いれば、通常のスパッタリングのようにターゲット材料204aが絶縁層206のエッジ部E206に集中的に成膜されることを防止することができる。

【0009】

しかしながら、ロングスロースパッタ法では、図13(b)に示すように、半導体基板200の中央部では、ターゲット204を構成するターゲット材料204aが、穴202aの側壁面B202a及び底面C202aを覆って良好に成膜されるものの、図13(c)に示すように、半導体基板200の外周部では、ターゲット材料204aが穴202bに対して斜め上方から浅い角度で成膜されるため、穴202bの底面C202bをターゲット材料204aで覆うことは可能であるが、穴202bの側壁面B202bがターゲット材料204aで完全に覆わずに成膜される場合がある。

穴202bの側壁面B202bがターゲット材料204aで完全に覆われていないと、この穴202bへの他のターゲット材料を成膜した際の埋め込み性が悪化して導通不良が発生する場合がある。

【0010】

そこで、本発明が解決しようとする課題は、Siウエハ等の半導体基板上に形成された特に高アスペクト比の穴に、バリア層やAl層等となるターゲット材料を成膜した際に、穴の側壁面及び底面をターゲット材料で完全に覆うことを可能にすることにより、スパイクの発生や導通不良の発生を防止することが可能な、半導体素子の製造方法を提供することにある。

【課題を解決するための手段】

【0011】

上記の課題を解決するために、本願各発明は次の半導体素子の製造方法を提供する。

1)半導体基板(1)上に形成されている絶縁層(2)に穴(3)を形成する穴形成工程と、前記穴形成工程の後に、ターゲット(5)と前記半導体基板との距離を第1の値(L2)とする第1のスパッタリングにより、前記ターゲットを構成するターゲット材料(5a)を前記穴に成膜する第1の成膜工程と、前記第1の成膜工程の後に、前記半導体基板と前記ターゲットとの距離を、前記第1の値よりも小さい第2の値(L1)とする第2のスパッタリングにより、前記ターゲット材料を前記穴に成膜する第2の成膜工程と、を有することを特徴とする半導体素子の製造方法。

2)前記第1のスパッタリングは異方性を有するスパッタリングであり、前記第2のスパッタリングは等方性を有するスパッタリングであることを特徴とする1)記載の半導体素子の製造方法。

3)前記第1のスパッタリングはロングスロースパッタであることを特徴とする1)または2)記載の半導体素子の製造方法。

4)前記穴形成工程は、前記絶縁層上に、開口部を有するレジスト層を形成する第1の形成工程と、前記第1の形成工程の後に、前記レジスト層をマスクとして前記絶縁層に等方性のエッチングを行って、前記絶縁層に所定の開口径を有する凹部を形成する第2の形成工程と、前記第2の形成工程の後に、前記レジスト層をマスクとして、前記凹部が形成されている領域の前記絶縁層に異方性のエッチングを行って、前記凹部に連接し前記開口径よりも小さい穴径を有する穴を形成する第3の形成工程と、前記第3の形成工程の後に、前記レジスト層を除去する除去工程と、を有することを特徴とする1)乃至3)のいずれかに記載の半導体素子の製造方法。

【発明の効果】

【0012】

本発明によれば、Siウエハ等の半導体基板上に形成された特に高アスペクト比の穴に、バリア層やAl層等となるターゲット材料を成膜した際に、穴の側壁面及び底面をターゲット材料で完全に覆うことが可能になるので、スパイクの発生や導通不良の発生を防止することができるという効果を奏する。

【発明を実施するための最良の形態】

【0013】

本発明の実施の形態を、好ましい実施例である第1実施例及び第2実施例により図1〜図11を用いて説明する。

【0014】

<第1実施例>

以下に説明する第1工程〜第6工程は、本発明に係る半導体素子の製造方法における製造過程をそれぞれ示すものである。

[第1工程]

第1工程を、図1を用いて説明する。図1は、本発明に係る半導体素子の製造方法の第1実施例における第1工程を説明するための模式的断面図である。

【0015】

図1に示すように、半導体基板1上に絶縁層2を熱酸化処理や成膜等の周知の半導体プロセスにより形成する。

第1実施例では、半導体基板1として直径が6インチのSi(シリコン)ウエハを用い、絶縁層2の材料としてSiO2(二酸化シリコン)を用いてその厚さt2を0.8μmとした。

【0016】

次に、絶縁層2に、ドライエッチングやウェットエッチング等の周知の半導体プロセスを用いて、半導体基板1の中央部及び外周部を含む全域に亘って、半導体基板1を露出させる高アスペクト比の穴3を複数形成する。

ここで、高アスペクト比とは、穴3の直径R3に対する深さt2の比率t2/R3が2以上のものを称す。

第1実施例では、穴3の直径R3を0.3μmとした。従って穴3のアスペクト比は2.7(小数点以下2桁目を四捨五入)である。

なお、図1では、説明をわかりやすくするために、複数形成された穴3のうち、半導体基板1の中央部に形成された穴3aと、外周部に形成された穴3bの2つの穴3を抜粋して示している。

【0017】

[第2工程]

第2工程を、図2,図12(a),及び図13(a)を用いて説明する。

図2は、本発明に係る半導体素子の製造方法の第1実施例における第2工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第1バリア層6がそれぞれ形成された状態を示すものである。

【0018】

図13(a)に示すように、第1のターゲット5の構成材料である第1のターゲット材料5aを、半導体基板1上に形成された絶縁層2上に、まず異方性のスパッタリングであるロングスロースパッタ法を用いて成膜した後に、さらに、図12(a)に示すように、等方性のスパッタリングである通常のスパッタリングを用いて成膜することにより、所定の厚さの第1のバリア層6を形成する(図2参照)。

ここで、第1のバリア層6において、ロングスロースパッタ法により成膜された膜を6a、その後に通常のスパッタリングにより成膜された膜を6bとそれぞれ末尾に符号を付す。

【0019】

前述したように、ロングスロースパッタ法は、第1のターゲット5と半導体基板1との距離L2が通常のスパッタリングの距離L1よりも長いので、特定の成膜方向性を有する異方性のスパッタリングであり、また、通常のスパッタリングよりも成膜速度が遅いため、第1のターゲット材料5aが絶縁層2のエッジ部E2に集中的に成膜されることを防止することができる。

従って、第1のバリア層6aが成膜された後の穴3a,3bは広い開口部を有しているため、次に行う通常のスパッタリングによる第1のバリア層6bを上記穴3a,3bにそれぞれ付き回りよく成膜することができる。

【0020】

また、前述したように、ロングスロースパッタ法では、図2(b)に示すように、半導体基板1の外周部では、第1のターゲット材料5aが穴3bに対して斜め上方から浅い角度で成膜されるため、穴3bの底面C3bを第1のバリア層6aで覆うことは可能であるが、穴3bの側壁面B3bが第1のバリア層6aで完全に覆われずに成膜される場合がある。

【0021】

このような場合においても、穴3bが広い開口部を有した状態で通常のスパッタリングを行うことができるため、穴3bの側壁面B3b及び底面C3bを、その後に成膜される第1のバリア層6bで完全に覆うことができる。

【0022】

第1実施例では、第1のターゲット5と半導体基板1との距離L1を5cmとし、L2を30cmとした。

また、第1実施例では、第1のターゲット材料5aとしてTi(チタン)を用い、第1のバリア層6aの厚さ(絶縁層2上の厚さ)を16nmとし、第1のバリア層6bの厚さ(絶縁層2上の厚さ)を4nmとした。

【0023】

上述した手順によれば、まず、異方性のスパッタリングであるロングスロースパッタ法により、半導体基板1の中央部及び外周部を含む全域に亘って形成された複数の高アスペクト比の穴3a,3bの各底面C3a,C3bを第1のバリア層6aで完全に覆うことができる。

また、穴3bの側壁面B3bが第1のバリア層6aで完全に覆われていない場合においても、その後に等方性のスパッタリングである通常のスパッタリングにより成膜される第1のバリア層6bでこれら側壁面B3bを完全に覆うことができる。即ち、高アスペクト比の穴3a,3bの側壁面B3a,B3b及び底面C3a,C3bを第1のバリア層6で完全に覆うことができる。

【0024】

[第3工程]

第3工程を、図3,図12(a),及び図13(a)を用いて説明する。

図3は、本発明に係る半導体素子の製造方法の第1実施例における第3工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第2バリア層9がそれぞれ形成された状態を示すものである。

【0025】

図13(a)に示すように、第2のターゲット8の構成材料である第2のターゲット材料8aを、第2工程を経た半導体基板1上に、まず異方性のスパッタリングであるロングスロースパッタ法を用いて成膜した後に、さらに、図12(a)に示すように、等方性のスパッタリングである通常のスパッタリングを用いて成膜することにより、第2のバリア層9を形成する(図3参照)。

その後、アニール処理を行って、第1のバリア層6と第2のバリア層9とを相互拡散により一体化させる。

第2のバリア層9は、後述する第1のAl層15及び第2のAl層17のAl原子が半導体基板1の内部に異常成長することによって発生するスパイクによるリーク電流の増加を防止する機能を有する。

ここで、第2のバリア層9において、ロングスロースパッタ法により成膜された膜を9a、その後に通常のスパッタリングにより成膜された膜を9bとそれぞれ末尾に符号を付す。

【0026】

前述したように、ロングスロースパッタ法は、第2のターゲット8と半導体基板1との距離L4が、通常のスパッタリングの距離L3よりも長いので、特定の成膜方向性を有する異方性のスパッタリングであり、また、通常のスパッタリングよりも成膜速度が遅いため、第2のターゲット材料8aが絶縁層2のエッジ部E2に集中的に成膜されることを防止することができる。

従って、第2のバリア層9aが成膜された後の穴3a,3bは広い開口部を有しているため、次に行う通常のスパッタリングによる第2のバリア層9bを上記穴3a,3bに付き回りよくそれぞれ成膜することができる。

【0027】

また、前述したように、ロングスロースパッタ法では、図3(b)に示すように、半導体基板1の外周部では第2のターゲット材料8aが穴3bに対して斜め上方から浅い角度で成膜されるため、第1のバリア層6で覆われている穴3bの底面C3bを第2のバリア層9aで覆うことは可能であるが、穴3bの側壁面B3bを覆う第1のバリア層6が第2のバリア層9aで完全に覆われない場合がある。

【0028】

このような場合においても、穴3bが広い開口部を有した状態で通常のスパッタリングを行うことができるため、穴3bの側壁面B3b及び底面C3bを覆う第1のバリア層6を、第2のバリア層9bで完全に覆うことができる。

【0029】

第1実施例では、第2のターゲット8と半導体基板1との距離L3を5cmとし、L4を30cmとした。

また、第1実施例では、第2のターゲット材料8aとしてTiN(窒化チタン)を用い、第2のバリア層9aの厚さ(絶縁層2上の厚さ)を80nmとし、第2のバリア層9bの厚さ(絶縁層2上の厚さ)を20nmとした。

【0030】

上述した手順によれば、まず、異方性のスパッタリングであるロングスロースパッタ法により、半導体基板1の中央部及び外周部を含む全域に亘って形成された複数の高アスペクト比の穴3a,3bの各底面C3a,C3bを、第2のバリア層9aで完全に覆うことができる。

また、穴3bの側壁面B3bが第2のバリア層9aで完全に覆われていない場合においても、その後に等方性のスパッタリングである通常のスパッタリングにより成膜される第2のバリア層9bでこの側壁面B3bを完全に覆うことができる。即ち、第2工程を経た高アスペクト比の穴3a,3bの側壁面B3a,B3b及び底面C3a,C3bを第2のバリア層9で完全に覆うことができる。

【0031】

[第4工程]

第4工程を、図4,図12(a),及び図13(a)を用いて説明する。

図4は、本発明に係る半導体素子の製造方法の第1実施例における第4工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第3バリア層12がそれぞれ形成された状態を示すものである。

【0032】

図13(a)に示すように、第3のターゲット11の構成材料である第3のターゲット材料11aを、第3工程を経た半導体基板1上に、まず異方性のスパッタリングであるロングスロースパッタ法を用いて成膜した後に、さらに、図12(a)に示すように、等方性のスパッタリングである通常のスパッタリングを用いて成膜することにより、第3のバリア層12を形成する(図4参照)。

第3のバリア層12は、後述する第1のAl層15及び第2のAl層17との密着性を向上させて、これらAl層15,17の埋め込み性を良好にする機能を有する。

ここで、第3のバリア層12において、ロングスロースパッタ法により成膜された膜を12a、その後に通常のスパッタリングにより成膜された膜を12bとそれぞれ末尾に符号を付す。

【0033】

前述したように、ロングスロースパッタ法は、第3のターゲット11と半導体基板1との距離L6が通常のスパッタリングの距離L5よりも長いので、特定の成膜方向性を有する異方性のスパッタリングであり、また、通常のスパッタリングよりも成膜速度が遅いため、第3のターゲット材料11aが絶縁層2のエッジ部E2に集中的に成膜されることを防止することができる。

従って、第3のバリア層12aが成膜された後の穴3a,3bは広い開口部を有しているため、次に行う通常のスパッタリングによる第3のバリア層12bを上記穴3a,3bに付き回りよくそれぞれ成膜することができる。

【0034】

また、前述したように、ロングスロースパッタ法では、図4(b)に示すように、半導体基板1の外周部では、第3のターゲット材料11aが穴3bに対して斜め上方から浅い角度で成膜されるため、第2のバリア層9で覆われている穴3bの底面C3bを第3のバリア層12aで覆うことは可能であるが、穴3bの側壁面B3bを覆う第2のバリア層9が第3のバリア層12aで完全に覆われない場合がある。

【0035】

このような場合においても、穴3bが広い開口部を有した状態で通常のスパッタリングを行うことができるため、穴3bの側壁面B3b及び底面C3bを覆う第2のバリア層9を第3のバリア層12bで完全に覆うことができる。

【0036】

第1実施例では、第3のターゲット11と半導体基板1との距離L5を5cmとし、L6を30cmとした。

また、第1実施例では、第3のターゲット材料11aとしてTiを用い、第2のバリア層12aの厚さ(絶縁層2上の厚さ)を40nmとし、第3のバリア層12bの厚さ(絶縁層2上の厚さ)を10nmとした。

【0037】

上述した手順によれば、まず、異方性のスパッタリングであるロングスロースパッタ法により、半導体基板1の中央部及び外周部を含む全域に亘って形成された複数の高アスペクト比の穴3a,3bの各底面C3a,C3bを第3のバリア層12aで完全に覆うことができる。

また、穴3bの側壁面B3bが第3のバリア層12aで完全に覆われていない場合においても、その後に等方性のスパッタリングである通常のスパッタリングにより成膜される第3のバリア層12bでこの側壁面B3bを完全に覆うことができる。即ち、第3工程を経た高アスペクト比の穴3a,3bの側壁面B3a,B3b及び底面C3a,C3bを第3のバリア層12で完全に覆うことができる。

【0038】

[第5工程]

第5工程を、図5,図12(a),及び図13(a)を用いて説明する。

図5は、本発明に係る半導体素子の製造方法の第1実施例における第5工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第1のAl層15がそれぞれ形成された状態を示すものである。

【0039】

図13(a)に示すように、第4のターゲット14の構成材料である第4のターゲット材料14aのAl(アルミニウム)を、第4工程を経た半導体基板1上に、まず異方性のスパッタリングであるロングスロースパッタ法を用いて成膜した後に、さらに、図12(a)に示すように、等方性のスパッタリングである通常のスパッタリングを用いて成膜することにより、第1のAl層15を形成する(図5参照)。

ここで、第1のAl層15において、ロングスロースパッタ法により成膜された膜を15a、その後に通常のスパッタリングにより成膜された膜を15bとそれぞれ末尾に符号を付す。

【0040】

前述したように、ロングスロースパッタ法は、第4のターゲット14と半導体基板1との距離L8が、通常のスパッタリングの距離L7よりも長いので、特定の成膜方向性を有する異方性のスパッタリングであり、また、通常のスパッタリングよりも成膜速度が遅いため、第4のターゲット材料14aが絶縁層2のエッジ部E2に集中的に成膜されることを防止することができる。

従って、第1のAl層15aが成膜された後の穴3a,3bは広い開口部を有しているため、次に行う通常のスパッタリングによる第1のAl層15bを上記穴3a,3bにそれぞれ付き回りよく成膜することができる。

【0041】

また、前述したように、ロングスロースパッタ法では、図5(b)に示すように、半導体基板1の外周部では、第4のターゲット材料14aが穴3bに対して斜め上方から浅い角度で成膜されるため、第3のバリア層12で覆われている穴3bの底面C3bを第1のAl層15aで覆うことは可能であるが、穴3bの側壁面B3bを覆う第3のバリア層12が第1のAl層15aで完全に覆われない場合がある。

【0042】

このような場合においても、穴3bが広い開口部を有した状態で通常のスパッタリングを行うことができるため、穴3bの側壁面B3b及び底面C3bを覆う第3のバリア層12を、その後に成膜される第1のAl層15bで完全に覆うことができる。

【0043】

第1実施例では、第4のターゲット14と半導体基板1との距離L7を5cmとし、L8を30cmとした。

また、第1実施例では、第1のAl層15aの厚さ(絶縁層2上の厚さ)を160nmとし、第1のAl層15bの厚さ(絶縁層2上の厚さ)を40nmとした。

【0044】

上述した手順によれば、まず異方性のスパッタリングであるロングスロースパッタ法により、半導体基板1の中央部及び外周部を含む全域に亘って形成された複数の高アスペクト比の穴3a,3bの各底面C3a,C3bを第1のAl層15aで完全に覆うことができる。

また、穴3bの側壁面B3bが第1のAl層15aで完全に覆われていない場合においても、その後に等方性のスパッタリングである通常のスパッタリングにより成膜される第1のAl層15bでこの側壁面B3bを完全に覆うことができる。即ち、第4工程を経た高アスペクト比の穴3a,3bの側壁面B3a,B3b及び底面C3a,C3bを第1のAl層15で完全に覆うことができる。

【0045】

[第6工程]

第6工程について図6を用いて説明する。

図6は、本発明に係る半導体素子の製造方法の第1実施例における第6工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴3aに、(b)は半導体基板1の外周部の穴3bに、第2のAl層17がそれぞれ形成された状態を示すものである。

【0046】

図6に示すように、フロースパッタにより、第5工程を経た半導体基板1上に、第2のAl層17を形成する。

フロースパッタとは、成膜材料(ここではAl)が流動性を有する程度に加熱しながらスパッタリングを行うものである。

そのため、第2のAl層17は、第5工程を経た穴3a,3bを埋めると共にその表面は略平坦な面になる。

また、第2のAl層17を形成する際に、その下地膜である第1のAl層15も加熱されて流動性を有するようになるため、第1のAl層15と第2のAl層17とは互いに溶け合って一体化される。

【0047】

上述した手順により、穴3a,3bは、半導体基板1と電気的に接続する高アスペクト比のビアホール20a,20bとなる。

【0048】

以降、所定の工程を行うことによって所望の半導体素子を得る。

上記所定の工程の一例として、第2のAl層17の表面に、例えばTiNを主成分とする反射防止膜を形成する工程などがある。

【0049】

ここで、上述した第1実施例の半導体素子、及び、第1実施例と同様の構成であって第1〜第3のバリア層及び第1のAl層をロングスロースパッタ法のみで成膜した比較例の半導体素子について、それぞれのスパイク発生率を調べ、その結果を表1に示す。

【0050】

【表1】

【0051】

表1に示すように、比較例の半導体素子では、半導体基板の外周部(中心から52.5mm離れた位置)に発生率50%とかなり高い確率でスパイクが発生していたのに対し、第1実施例の半導体素子では、半導体基板の中心から外周部に亘ってスパイクが発生していないことを確認した。

【0052】

次に、上述の第1実施例及び比較例の各半導体素子の高アスペクト比の穴について、Al層の埋め込み不良率を調べ、その結果を表2に示す。

【0053】

【表2】

【0054】

表2に示すように、比較例の半導体素子では、半導体基板の外周部(中心から52.5mm離れた位置)に発生率17〜30%とかなり高い確率でAl層の埋め込み不良が発生していたのに対し、第1実施例の半導体素子では、半導体基板の中心から外周部に亘って埋め込み不良が発生していないことを確認した。

【0055】

上述した半導体素子の製造方法によれば、半導体基板上に形成された高アスペクト比(例えば2以上)の穴に、バリア層やAl層等の所定の膜を、ロングスロースパッタ法と通常のスパッタリングとを順次行って成膜することにより、高アスペクト比のビアホールを、半導体基板の中央部及び外周部を含む全域に亘って安定して形成することができる。

【0056】

<第2実施例>

第2実施例は、上述した第1実施例に対して、第1工程が異なり第2工程〜第6工程は同じなので、ここでは特に第1工程について図7〜図11を用いて詳細に説明する。

図7〜図10は、本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部に穴35a(図9及び図10に図示)が、(b)は半導体基板1の外周部に穴35b(図9及び図10に図示)がそれぞれ形成される状態を示すものである。また、図7〜図10における(a),(b)は図2〜図6の(a),(b)にそれぞれ対応するものである。

図11は、本発明に係る半導体素子の製造方法の第2実施例における第1工程以降の工程を説明するための模式的断面図であり、同図中の(a)は半導体基板1の中央部の穴35aに、(b)は半導体基板1の外周部の穴35bに所定の膜がそれぞれ形成された状態を示すものである。また、図11における(a),(b)は図2〜図10の(a),(b)にそれぞれ対応するものである。

なお、図7〜図11において、図1〜図6と同じ構成部については説明をわかりやすくするために同じ符号を付す。

【0057】

[第1工程]

図7に示すように、まず、半導体基板1上に絶縁層2を熱酸化処理や成膜等の周知の半導体プロセスにより形成する。半導体基板1及び絶縁層2は第1実施例と同じである。

次に、絶縁層2上に、開口径がR3の開口部30a,30bを有するレジスト層31を形成する。

【0058】

その後、図8に示すように、レジスト層31をマスクとして、絶縁層2に等方性のエッチングを行うことにより、絶縁層2に凹部32a,32bを形成する。

等方性のエッチングにより、絶縁層2はその厚さ方向にエッチングされると共にその面に沿う方向にもエッチングされる。

従って、形成された凹部32a,32bの開口径R13はレジスト層31の開口径R3よりも大きくなる。

第2実施例では、等方性のエッチングを、CF4ガスを用いたドライエッチングとした。

【0059】

さらに、図9に示すように、レジスト層31をマスクとして、絶縁層2の凹部32a,32bが形成された領域に異方性のエッチングを行う。

異方性のエッチングにより、絶縁層2はその厚さ方向にエッチングされる。

これにより、絶縁層2には、直径R3の第1の径部34a,34bと直径R3よりも大きい開口径R13の第1の径部(凹部)32a,32bとが連接された穴35a,35bが形成される。

第2実施例では、異方性のエッチングを、CHF3ガスを用いたドライエッチングとした。

【0060】

次に、図10に示すように、レジスト層31を除去する。

【0061】

以上が第2実施例の第1工程である。

【0062】

その後、第1実施例の第2工程〜第6工程と同様の工程を行うことにより、図11に示すにように、穴35a,35bは、半導体基板1と電気的に接続する高アスペクト比のビアホール40a,40bとなる。

【0063】

以降、所定の工程を行うことによって所望の半導体素子を得る。

上記所定の工程の一例として、第2のAl層17の表面に、例えばTiNを主成分とする反射防止膜を形成する工程などがある。

【0064】

上述した手順によれば、穴35a,35bの開口径R13を第1実施例よりも広くすることができるので、穴35a,35bの内面への各膜6,9,12,15の付き回り性が向上するので、第1実施例よりもさらに高アスペクト比のビアホールを形成することができる。

【0065】

本発明の実施例は、上述した構成及び手順に限定されるものではなく、本発明の要旨を逸脱しない範囲において変形例としてもよいのは言うまでもない。

【0066】

例えば、第1実施例では、ビアホール(穴)のアスペクト比を2.7としたが、これに限定されるものではなく、特にアスペクト比が2以上の高アスペクト比のビアホールに対して好適である。

【図面の簡単な説明】

【0067】

【図1】本発明に係る半導体素子の製造方法の第1実施例における第1工程を説明するための模式的断面図である。

【図2】本発明に係る半導体素子の製造方法の第1実施例における第2工程を説明するための模式的断面図である。

【図3】本発明に係る半導体素子の製造方法の第1実施例における第3工程を説明するための模式的断面図である。

【図4】本発明に係る半導体素子の製造方法の第1実施例における第4工程を説明するための模式的断面図である。

【図5】本発明に係る半導体素子の製造方法の第1実施例における第5工程を説明するための模式的断面図である。

【図6】本発明に係る半導体素子の製造方法の第1実施例における第6工程を説明するための模式的断面図である。

【図7】本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図である。

【図8】本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図である。

【図9】本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図である。

【図10】本発明に係る半導体素子の製造方法の第2実施例における第1工程を説明するための模式的断面図である。

【図11】本発明に係る半導体素子の製造方法の第2実施例における第1工程以降の工程を説明するための模式的断面図である。

【図12】通常のスパッタリングにより成膜した場合の課題を説明するための模式的断面図である。

【図13】ロングスロースパッタ法により成膜した場合の課題を説明するための模式的断面図である。

【符号の説明】

【0068】

1_半導体基板、 2_絶縁層、 3,3a,3b_穴、 5,8,11,14_ターゲット、 5a,8a,11a,14a_ターゲット材料、 6,6a,6b,9,9a,9b,12,12a,12b_バリア層、 15,15a,15b,17_Al層、 20a,20b_ビアホール、 t2_厚さ、 R3_直径、 L1〜L8_距離、 B3a,B3b_側壁面、 C3a,C3b_底面

【特許請求の範囲】

【請求項1】

半導体基板上に形成されている絶縁層に穴を形成する穴形成工程と、

前記穴形成工程の後に、ターゲットと前記半導体基板との距離を第1の値とする第1のスパッタリングにより、前記ターゲットを構成するターゲット材料を前記穴に成膜する第1の成膜工程と、

前記第1の成膜工程の後に、前記半導体基板と前記ターゲットとの距離を、前記第1の値よりも小さい第2の値とする第2のスパッタリングにより、前記ターゲット材料を前記穴に成膜する第2の成膜工程と、

を有することを特徴とする半導体素子の製造方法。

【請求項2】

前記第1のスパッタリングは異方性を有するスパッタリングであり、前記第2のスパッタリングは等方性を有するスパッタリングであることを特徴とする請求項1記載の半導体素子の製造方法。

【請求項3】

前記第1のスパッタリングはロングスロースパッタであることを特徴とする請求項1または2記載の半導体素子の製造方法。

【請求項4】

前記穴形成工程は、

前記絶縁層上に、開口部を有するレジスト層を形成する第1の形成工程と、

前記第1の形成工程の後に、前記レジスト層をマスクとして前記絶縁層に等方性のエッチングを行って、前記絶縁層に所定の開口径を有する凹部を形成する第2の形成工程と、

前記第2の形成工程の後に、前記レジスト層をマスクとして、前記凹部が形成されている領域の前記絶縁層に異方性のエッチングを行って、前記凹部に連接し前記開口径よりも小さい穴径を有する穴を形成する第3の形成工程と、

前記第3の形成工程の後に、前記レジスト層を除去する除去工程と、

を有することを特徴とする請求項1乃至3のいずれか1項に記載の半導体素子の製造方法。

【請求項1】

半導体基板上に形成されている絶縁層に穴を形成する穴形成工程と、

前記穴形成工程の後に、ターゲットと前記半導体基板との距離を第1の値とする第1のスパッタリングにより、前記ターゲットを構成するターゲット材料を前記穴に成膜する第1の成膜工程と、

前記第1の成膜工程の後に、前記半導体基板と前記ターゲットとの距離を、前記第1の値よりも小さい第2の値とする第2のスパッタリングにより、前記ターゲット材料を前記穴に成膜する第2の成膜工程と、

を有することを特徴とする半導体素子の製造方法。

【請求項2】

前記第1のスパッタリングは異方性を有するスパッタリングであり、前記第2のスパッタリングは等方性を有するスパッタリングであることを特徴とする請求項1記載の半導体素子の製造方法。

【請求項3】

前記第1のスパッタリングはロングスロースパッタであることを特徴とする請求項1または2記載の半導体素子の製造方法。

【請求項4】

前記穴形成工程は、

前記絶縁層上に、開口部を有するレジスト層を形成する第1の形成工程と、

前記第1の形成工程の後に、前記レジスト層をマスクとして前記絶縁層に等方性のエッチングを行って、前記絶縁層に所定の開口径を有する凹部を形成する第2の形成工程と、

前記第2の形成工程の後に、前記レジスト層をマスクとして、前記凹部が形成されている領域の前記絶縁層に異方性のエッチングを行って、前記凹部に連接し前記開口径よりも小さい穴径を有する穴を形成する第3の形成工程と、

前記第3の形成工程の後に、前記レジスト層を除去する除去工程と、

を有することを特徴とする請求項1乃至3のいずれか1項に記載の半導体素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2009−224756(P2009−224756A)

【公開日】平成21年10月1日(2009.10.1)

【国際特許分類】

【出願番号】特願2008−297794(P2008−297794)

【出願日】平成20年11月21日(2008.11.21)

【出願人】(000004329)日本ビクター株式会社 (3,896)

【Fターム(参考)】

【公開日】平成21年10月1日(2009.10.1)

【国際特許分類】

【出願日】平成20年11月21日(2008.11.21)

【出願人】(000004329)日本ビクター株式会社 (3,896)

【Fターム(参考)】

[ Back to top ]