半導体素子の製造方法

【課題】 成長用基板の上に形成する半導体層が薄くても、再現性よく半導体層から成長用基板を分離する方法が望まれる。

【解決手段】 表面に凹凸が形成された成長用基板の、該表面の凸部の上面に離散的に分布し、化合物半導体からなる複数の支柱を形成する。支柱によって成長用基板の上に支えられ、化合物半導体からなる半導体層を形成する。半導体層の上に、支持基板を接着する。成長用基板を半導体層から分離する。

【解決手段】 表面に凹凸が形成された成長用基板の、該表面の凸部の上面に離散的に分布し、化合物半導体からなる複数の支柱を形成する。支柱によって成長用基板の上に支えられ、化合物半導体からなる半導体層を形成する。半導体層の上に、支持基板を接着する。成長用基板を半導体層から分離する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、成長用基板の上に半導体層を形成した後、半導体層から成長用基板を分離する半導体素子の製造方法に関する。

【背景技術】

【0002】

発光ダイオード等の光半導体素子の従来の製造方法の一例について説明する。まず、成長用基板の上に、n型半導体層、発光層、及びp型半導体層を成長させる。成長用基板が絶縁性である場合には、p型半導体層及び発光層の一部を除去してn型半導体層を露出させる。n型半導体層の露出した領域、及び露出しているp型半導体層に電極を形成する。

【0003】

成長用基板は、その上に成長させる半導体層の結晶品質に大きな影響を与える。また、成長用基板の導電性、熱伝導性、光吸収係数等の物性が、光半導体素子の電気特性、熱特性、及び光学特性に影響する。結晶性のよい半導体層を形成するために適した成長用基板が、導電性、熱伝導性、光吸収係数等の物性の点で好ましいものであるとは限らない。

【0004】

半導体層を成長させた後、成長用基板を半導体層から分離した光半導体素子が提案されている。最終的に成長用基板が分離されるため、成長用基板として、半導体層の結晶成長に最適のものを選択することができる。成長用基板と半導体層との間に配置される層に空孔を生じさせることにより、成長用基板を半導体層から分離することができる(特許文献1、2)。また、成長用基板と半導体層との間に剥離層を配置し、この剥離層をエッチングすることにより、成長用基板を半導体層から分離することができる(特許文献3)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−228539号公報

【特許文献2】特開2002−241192号公報

【特許文献3】特開2004−172351号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

成長用基板の上に形成する半導体層が薄くても、再現性よく半導体層から成長用基板を分離する方法が望まれる。従来の方法では、半導体層から成長用基板を再現性よく分離することが困難であった。

【課題を解決するための手段】

【0007】

本発明の一観点によると、

表面に凹凸が形成された成長用基板の、該表面の凸部の上面に離散的に分布し、化合物半導体からなる複数の支柱を形成する工程と、

前記支柱によって前記成長用基板の上に支えられ、化合物半導体からなる半導体層を形成する工程と、

前記半導体層の上に、支持基板を接着する工程と、

前記成長用基板を前記半導体層から分離する工程と

を有する半導体素子の製造方法が提供される。

【発明の効果】

【0008】

支持基板を接着した後、再現性よく、成長用基板を半導体層から分離することができる。

【図面の簡単な説明】

【0009】

【図1−1】(1A)は、実施例で用いる成長用基板の断面図であり、(1B)はその平面図である。

【図1−2】(1C)〜(1F)は、実施例による方法で製造される半導体素子の製造途中段階における断面図である。

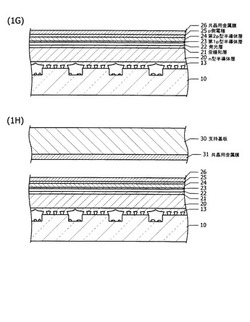

【図1−3】(1G)、(1H)は、実施例による方法で製造される半導体素子の製造途中段階における断面図である。

【図1−4】(1I)、(1J)は、実施例による方法で製造される半導体素子の製造途中段階における断面図である。

【図1−5】(1K)、(1L)は、実施例による方法で製造される半導体素子の製造途中段階における断面図である。

【図2】実施例及び比較例による方法で作製した試料の接続部の割合を示すグラフである。

【図3】成長用基板の凹部の側面の傾斜角を説明する線図である。

【図4】実施例の変形例による方法で用いる成長用基板の平面図である。

【発明を実施するための形態】

【0010】

図1A〜図1Lを参照して、実施例による半導体素子の製造方法について説明する。

【0011】

図1Aに示すように、成長用基板10の表面に複数の凹部11を形成する。実施例では、成長用基板10として、C面サファイア基板を用いる。凹部11の形成には、通常のフォトリソグラフィ技術を用いる。成長用基板10のエッチングには、例えばBCl3、Cl2、及びArの混合ガスの誘導結合プラズマを用いた反応性イオンエッチングが用いられる。凹部11の側面(段差面)は、成長用基板10の元の表面に対して、ほぼ垂直である。凹部11が形成されていない領域(凸部の上面)は平坦である。

【0012】

図1Bに、凹部11が形成された成長用基板10の平面図を示す。図1Bの一点鎖線1A−1Aにおける断面図が図1Aに相当する。凹部11は、正三角形を敷き詰めた三角格子の格子点に配置される。凹部11の各々の平面形状は円形である。凹部11の平面形状の直径をWbとし、最近接の凹部11の間隔をWdとする。また、図1Aに示したように、凹部11の深さをDとする。一例として、凹部11の深さDは1μmであり、直径Wbは6μmであり、間隔Wdは11μmである。

【0013】

図1Cに示すように、成長用基板10を有機金属化学気相成長(MOCVD)装置に搬入し、成長用基板10の凸部の上面及び凹部11の底面に、GaNからなる下地層12を形成する。成長条件は、例えば下記の通りである。

・トリメチルガリウム(TMG)供給量 11μmol/min

・キャリアガス 窒素ガス(13.5SLM)と水素ガス(4.5SLM)

・アンモニアガス(NH3)供給量 3.3SLM

・成長温度 525℃

上述の条件で、V/III比は14000である。ここで、V/III比は、供給される原料中のIII族元素のモル数に対するV族元素のモル数の比と定義される。下地層12の厚さは、凹部11の深さDよりも薄くする。凹部11の深さDが1μmのとき、例えば下地層12の厚さを200nmとする。このように高いV/III比を採用すると、Gaのマイグレーションが促進され、面内で偏りなくGaN膜が成長する。これにより、表面の凹凸の高さ及びピッチが面内に亘ってほぼ揃った下地層12が得られる。凹部11の側面には、下地層12が形成されない。

【0014】

仮に、3000未満の低いV/III比を採用すると、Gaのマイグレーションが促進されず、原料ガスの気流の影響を受けて、GaNが成長し易い領域と、成長し難い領域との差が顕著に現れる。このため、下地層12は離散的に分布する島状構造になってしまう。良好な下地層12を得るために、成長時のV/III比を3000〜25000の範囲内にすることが好ましい。TMGの供給量は、8μmol/min〜23μmol/minの範囲内とすることが好ましく、9μmol/min〜15μmol/minの範囲内とすることがより好ましい。NH3の供給量は、0.5SLM〜5.5SLMの範囲内とすることが好ましい。

【0015】

成長温度は、425℃〜625℃の範囲内とすることが好ましい。成長速度は、5nm/min〜40nm/minの範囲内とすることが好ましい。

【0016】

図1Dから図1Fまでの工程について説明する。下地層12(図1C)を形成した後、TMGの供給を停止させ、基板温度を1000℃まで上昇させる。成長条件の異なる第1工程と第2工程とを交互に繰り返すことにより、GaNからなる半導体層13(図1F)を形成する。繰り返し回数は、例えば4回とする。

【0017】

第1工程の成長条件は、例えば下記の通りである。

・TMG供給量 23μmol/min

・キャリアガス 窒素ガス(6SLM)と水素ガス(7.5SLM)

・NH3供給量 2.2SLM

・成長時間 膜厚20nmになる時間

第2工程の成長条件は、例えば下記の通りである。

・TMG供給量 45μmol/min

・キャリアガス 窒素ガス(6SLM)と水素ガス(7.5SLM)

・NH3供給量 4.4SLM

・成長時間 膜厚80nmになる時間

第1工程では、縦方向の成長が支配的となり、第2工程では、横方向(面内方向)の成長が支配的となる。第1工程と第2工程とを交互に繰り返す過程で、供給されるGa原子及びN原子が基板表面に吸着されて膜が成長する反応と、成長したGaNが分解し脱離する反応とが生じる。

【0018】

ここで、第1工程で「縦方向成長が支配的」とは、横方向成長速度をVs、縦方向成長速度をVnとしたとき、第1工程のVn/Vsが、第2工程のVn/Vsよりも大きいことを意味する。また、第2工程で「横方向成長が支配的」とは、第2工程のVs/Vnが、第1工程のVs/Vnよりも大きいことを意味する。

【0019】

第1工程で、下地層12(図1C)のうち成長核となる部分から結晶が成長すると同時に、結晶性の低い部分においては、熱によってGaNが分解する。分解によって生成された窒素がガスとなって成長用基板10から脱離する。これにより、凹部11の間の領域(凸部の上面)に離散的に分布する支柱13a(図1D)が形成される。なお、GaNが分解することにより生成された金属Gaは成長用基板10の上に残る。凹部11の底面には、成長用がガスが供給されにくいため、GaNの分解が支配的になり、支柱13aは形成されない。

【0020】

結晶成長の核となる部分以外の下地層12の結晶性を低くするために、下地層12の成長温度は、上述のように、半導体層13の成長温度よりも低い425℃〜625℃の範囲内とすることが好ましい。

【0021】

第2工程では、横方向の成長が支配的になり、支柱13aの先端から横方向に張り出した庇部13b(図1E)が形成される。例えば、原料ガスの供給量を増やすことにより、横方向成長を支配的にすることができる。庇部13bの端面には、GaNの(11−22)面が現れる。ここで、「−2」は、2のオーバーバーを意味する。庇部13bが形成されると、次の第1工程で、その下の空洞にNH3が供給され難くなり、GaNの分解及び窒素の脱離が促進される。これにより支柱13aが細くなる。凹部11内にもNH3が供給され難いため、凹部11の底面においては、GaNの分解と窒素の脱離とが促進される。

【0022】

庇部13bの張り出し量が長くなると、相互に隣り合う支柱13aから成長した庇部13b同士が接触する。凹部11の上方においても、庇部13b同士が接触することにより、面内方向に連続し、平滑な表面を有する半導体層13(図1F)が形成される。半導体層13は、複数の支柱13aによって成長用基板10の上方に支持される。支柱13aの間には、空洞13cが残る。空洞13cは、面内方向に連通している。凹部11内には支柱13aが配置されない。横方向に成長した部分(空洞13cの上の部分)には、成長用基板10と支柱13aとの界面から成長する欠陥が導入され難いため、結晶性の高い半導体層13が得られる。

【0023】

成長用基板10の凸部の上面から半導体層13の上面までの高さは、約400nmである。

【0024】

GaN膜の成長と、分解及び脱離とを並行して生じさせるために、第1工程及び第2工程の成長温度は、800℃〜1200℃の範囲内にすることが好ましい。第1工程において、TMGの供給量を10μmol/min〜30μmol/minの範囲内とし、NH3の供給量を1SLM〜3SLMの範囲内とすることが好ましい。第2工程においては、TMG供給量を30μmol/min〜70μmol/minの範囲内とし、NH3の供給量を3SLM〜7SLMの範囲内とすることが好ましい。

【0025】

半導体層13に、n型ドーパントとしてSiをドープしてもよい。Siの濃度が高くなると横方向成長し難くなるため、Si濃度は、5×1017cm−3以下にすることが好ましい。

【0026】

図1Gに示すように、半導体層13の上に、n型GaNからなるn型半導体層20を形成する。n型半導体層20の厚さは、例えば3μm〜10μmの範囲内である。n型不純物としてSiが用いられ、その濃度は例えば約5×1018cm−3である。Si原料として、例えばSiH4が用いられる。

【0027】

成長条件は、例えば下記の通りである。

・成長温度 1000℃

・TMG供給量 45μmol/min

・NH3供給量 4.4SLM

なお、成長温度を980℃〜1020℃の範囲内としてもよい。TMG供給量を10μmol/min〜70μmol/minの範囲内とし、NH3供給量を3.3SLM〜5.5SLMの範囲内としてもよい。V/III比は、2000〜22500の範囲内とすることが好ましく、3000〜8000の範囲内とすることが、平坦性及び結晶性の点でより好ましい。成長速度は、0.5μm/h〜5μm/hの範囲内とすることが好ましい。図1Gでは、半導体層13とn型半導体層20との境界を明示しているが、実際には、両者ともGaNで形成され、同一チャンバ内で連続して成長されるため、両者の境界が明瞭に識別できるわけではない。

【0028】

n型半導体層20の上に歪緩和層21を形成する。歪緩和層21は、例えば交互に積層された厚さ2nmのGaN層と厚さ2nmのIn0.2Ga0.8N層とを含み、合計の厚さは例えば120nmである。なお、各層の厚さ及び積層数を変えることにより、合計の膜厚を50nm〜300nmの範囲内にしてもよい。歪緩和層21の成長条件は、例えば下記の通りである。

・成長温度 730℃〜790℃

・TMG供給量 3.6μmol/min

・トリメチルインジウム(TMI)供給量 3.6μmol/min

・NH3供給量 3.3SLM〜5.5SLM

GaN層の成長時には、TMIの供給が停止される。TMGの供給量及びTMIの供給量を1μmol/min〜10μmol/minの範囲内としてもよい。ただし、TMGの供給量とTMIの供給量との比は、In組成比が0.2になるように調整される。

【0029】

歪緩和層21にSiをドープしてもよい。Si濃度は、例えば5×1017cm−3以下とする。また、InxGa1−xN層(0<x<0.2)と、In0.2Ga0.8N層とが交互に積層された構造としてもよい。

【0030】

歪緩和層21の上に発光層22を形成する。発光層22は、交互に積層されたGaNからなる厚さ14nmの障壁層と、In0.35Ga0.65Nからなる厚さ2.2nmの井戸層とを含む。障壁層及び井戸層の層数は、それぞれ5である。発光層22の成長条件は、例えば下記の通りである。

・成長温度 700℃〜760℃

・TMG供給量 3.6μmol/min

・TMI供給量 10μmol/min

・NH3供給量 3.3SLM〜5.5SLM

GaN層の成長時には、TMIの供給が停止される。TMGの供給量を1μmol/min〜10μmol/minの範囲内としてもよい。このとき、TMIの供給量は、In組成比が0.35になるように調整される。発光層22にSiをドープしてもよい。Si濃度は、例えば5×1017cm−3以下とする。

【0031】

発光層22の上に、Mgがドープされたp型Al0.2Ga0.8Nからなる第1p型半導体層23を形成する。第1p型半導体層23の厚さは、例えば20nm〜60nmの範囲内である。第1p型半導体層23の成長条件は、例えば下記の通りである。

・成長温度 770℃〜970℃

・TMG供給量 8.1μmol/min

・トリメチルアルミニウム(TMA)供給量 7.6μmol/min

・NH3供給量 3.3SLM〜5.5SLM

ドーパントであるMgの原料として、例えばビスシクロペンタジエニルマグネシウム(CP2Mg)を用いることができる。TMGの供給量を4μmol/min〜20μmol/minの範囲内としてもよい。このとき、TMAの供給量は、Al組成比が0.2になるように調整される。Mg濃度は、例えば1×1020cm−3である。

【0032】

第1p型半導体層23の上に、Mgがドープされたp型GaNからなる第2p型半導体層24を形成する。第2p型半導体層24の厚さは、例えば100nm〜300nmの範囲内である。第2p型半導体層24の成長条件は、例えば下記の通りである。

・成長温度 770℃〜970℃

・TMG供給量 18μmol/min

・NH3供給量 3.3SLM〜5.5SLM

TMGの供給量を8μmol/min〜36μmol/minの範囲内としてもよい。Mg濃度は、例えば1×1020cm−3である。

【0033】

第2p型半導体層24の上に、p側電極25を形成する。p側電極25は、例えば、基板側に配置された厚さ1nmの白金(Pt)膜と、その上に配置された厚さ300nmの銀(Ag)膜とを含む。Pt膜及びAg膜の形成には、例えば電子ビーム蒸着が用いられる。Pt膜は、オーミック接触を確保するためのものである。p側電極25と第2p型半導体層24との接触抵抗率は、1×10−3Ω・cm2である。Ag膜は、発光層22からの放射光に対して高い反射率を確保するためのものである。p側電極25の反射率は約80%である。Pt膜の厚さを0.3nm〜100nmの範囲内としてもよい。Ag膜の厚さを50nm〜300nmの範囲内としてもよい。

【0034】

p側電極25として、Pt膜とRh膜との2層構造を採用してもよいし、Ni膜とAg膜との2層構造を採用してもよい。

【0035】

p側電極25の上に、共晶用金属膜26を形成する。共晶用金属膜26は、例えば厚さ100nmのTi膜、その上の厚さ200nmのPt膜、及びその上の厚さ200nmのAu膜で構成される。これらの膜の形成には、例えば電子ビーム蒸着が用いられる。Ti膜は、その上のPt膜の密着性を高める。Pt膜は、AuSn合金との接合時におけるSnの拡散を防止する。Au膜は、AuSn共晶を形成するためのものである。

【0036】

Ti膜の厚さを50nm〜100nmの範囲内としてもよい。Pt膜の厚さを200nm以上にしてもよい。Au膜は、接合されるAuSn膜の厚さ及び組成を考慮し、AuSn共晶点に整合する厚さにすればよい。

【0037】

共晶用金属膜26を、厚さ100nmのTi膜、厚さ100nmのPt膜、厚さ200nmのAu膜、厚さ100nmのPt膜、及び厚さ200nmのAu膜がこの順番に積層された5層構造としてもよい。5層構造を採用することにより、Snの拡散防止機能を高めることができる。

【0038】

図1Hに示すように、支持基板30の片側の表面に共晶用金属膜31を形成する。支持基板30には、例えばシリコン基板が用いられる。共晶用金属膜31は、Pt膜、Ti膜、Ni膜、Au膜、及びAuSn膜がこの順番に積層された積層構造を有する。Pt膜は、支持基板30のSiとシリサイド反応することにより、支持基板30に対してオーミック接触する。Ti膜は、シリサイド化したPt膜と、Ni膜との密着性を高める。Ni膜は、AuSnの濡れ性を高める。Au膜は、Ni膜の酸化を防止する。AuSn膜は、共晶を形成するためのものである。

【0039】

支持基板30と成長用基板10とを、共晶用金属膜26と31とが対向する向きに配置する。

【0040】

図1Iに示すように、共晶用金属膜26と31とを接触させ、真空中で熱圧着を行う。熱圧着時の圧力は、3MPaとし、温度は330℃とする。なお、熱圧着を窒素ガス等の不活性ガス雰囲気中で行ってもよい。また、AuSn共晶の形成に適した温度であれば、330℃以外の温度で熱圧着を行ってもよい。

【0041】

図1Jに示すように、基板温度を室温に戻す過程で、成長用基板10と支持基板30との熱膨張係数の相違に起因して、成長用基板10が半導体層13から自然に分離する。自然分離した半導体層13の表面には、複数の支柱13aが残った状態である。なお、自然分離し難い場合には、ピンセット等で成長用基板10の端部に機械的な衝撃を与えてもよい。また、超音波により衝撃を与えてもよい。成長用基板10と半導体層13との間の空洞に溶剤を浸透させ、加熱してもよい。この場合には、溶剤の蒸気圧によって成長用基板10が半導体層13から分離する。

【0042】

その他に、補助的にレーザを照射したり、酸やアルカリに浸漬させたりして、分離してもよい。また、電界エッチング手法を用いてもよい。

【0043】

図1Kに示すように、半導体層13の表面を塩酸で処理する。塩酸処理により、n型半導体層20が露出し、露出した表面が平坦になる。なお、塩酸に代えて、窒化物半導体をエッチングできる他の薬液、例えばリン酸、硫酸、水酸化カリウム(KOH)、水酸化ナトリウム(NaOH)等を用いてもよい。また、薬液処理に代えて、Arプラズマや塩素系プラズマを用いたドライエッチングを適用してもよい。

【0044】

図1Lに示すように、n型半導体層20の表面の一部の領域に、n側電極35を形成する。n側電極35は、例えばTi膜と、その上に配置されたAl膜との2層で構成される。n側電極35として、Al膜とRh膜との2層構造、Al膜とIr膜との2層構造、Al膜とPt膜との2層構造、またはAl膜とPd膜との2層構造を採用してもよい。これらの積層構造とすることにより、n側電極35とn型半導体層20との接触抵抗率を1×10−4Ω・cm2以下にすることができる。n側電極35の上に、ボンディングし易くするために、Ti膜とAu膜とを順番に積層してもよい。

【0045】

その後、支持基板30からn型半導体層20までの積層構造を、個別のチップに分割する。以下、分割方法について説明する。

【0046】

n型半導体層20の表面から、p側電極25まで達する溝を、反応性イオンエッチング(RIE)により形成する。溝を形成した後、支持基板30をダイシングし、各チップに分割する。なお、レーザスクライブ等の技術を用いてもよい。

【0047】

次に、図2を参照して、図1Aの凹部11を形成した効果について説明する。

【0048】

凹部11を形成した成長用基板10を用いて半導体層を成長させた複数の試料と、凹部11を形成していない成長用基板を用いて半導体層を成長させた複数の試料とを作製した。図1Jに示したように、作製した試料の成長用基板を半導体層から分離させ、支柱13aの剥離面の合計の面積を測定した。成長用基板10の表面の面積に対する支柱13aの剥離面の合計の面積の比を「接続部の割合」ということとする。

【0049】

図2の縦軸は、接続部の割合を単位「%」で表す。白丸は、凹部11を形成した実施例による方法で作製した複数の試料の接続部の割合を示し、黒丸は、凹部を形成していない成長用基板を用いた複数の試料の接続部の割合を示す。なお、実施例による方法で作製する試料においては、図1Cに示した下地層12の厚さを180nmとし、凹部を形成していない成長用基板を用いて作製する試料においては、下地層12の厚さを200nmとした。

【0050】

凹部を形成していない成長用基板を用いる場合には、成長用基板と半導体層との間に十分な大きさの空洞を確保するために、下地層12を200nm程度まで厚くしなければならない。実施例による方法で作製する場合には、成長用基板に凹部が形成されているため、下地層12を180nm程度まで薄くしても、十分な大きさの空洞を確保することができる。

【0051】

すべての試料において、図1Gに示した半導体層13及びn型半導体層20の合計の厚さは6μmとした。凹部11の直径Wbは4μmとし、凹部11の間隔Wdは3μmとし、凹部11の深さDは1μmとした。

【0052】

凹部11を形成した試料の方が、接続部の割合のばらつきが小さいことがわかる。接続部の割合が高すぎると、半導体層から成長用基板を分離させることが困難になる。凹部11を形成すると、凹部11の底面に支柱13a(図1D)が分布しないため、接続部の割合が高くなりすぎることが回避される。

【0053】

逆に、接続部の割合が低すぎると、図1Iに示した支持基板30を接合する前に、成長用基板が自然に分離してしまう。凹部が形成されていない成長用基板を用いる場合には、下地層12を200nm程度まで厚くしなければならない。下地層12が厚いと、支柱13aの分布密度のばらつきが大きくなる。このため、作製した試料の接続部の割合が低くなりすぎる場合もある。凹部11を形成することにより、接続部の割合が低くなりすぎることを回避できる。

【0054】

凹部11を形成することにより、接続部の割合のばらつきを抑制し、支持基板30を接合した後に、再現性よく成長用基板10を分離することができる。

【0055】

次に、凹部11の好ましい断面形状について説明する。上記実施例では、凹部11の側面が、成長用基板10の元の表面(凸部の上面によって画定される仮想平面)に対してほぼ垂直、すなわち傾斜角がほぼ90°であった。このとき、凹部11の断面形状はほぼ長方形である。凹部11の側面の傾斜角が小さくなると、側面にも下地層12(図1C)が成長してしまう。側面に下地層12が形成されると、側面にも半導体層13(図1F)の成長が始まり、凹部11内が半導体層13で埋め込まれてしまう場合がある。または、凹部11の開口面よりも低い位置で半導体層13が連続してしまう場合もある。凹部11を形成する十分な効果を得るために、図3に示すように、凹部11の側面(段差面)の傾斜角θbを、70°〜90°の範囲内にすることが好ましく、80°〜90°の範囲内することがより好ましい。

【0056】

次に、凹部11の好ましい深さについて説明する。凹部11が浅すぎると、凹部11の底面に形成された下地層12(図1C)から支柱13a(図1D)が伸び、半導体層13(図1F)に連続してしまう。凹部11の底面に支柱13aが分布しないようにするために、凹部11の深さを1μm以上にすることが好ましい。逆に、凹部11の加工のし易さの点から、凹部11の深さは3μm以下にすることが好ましい。

【0057】

次に、凹部11の平面形状について説明する。上記実施例では、凹部11の平面形状を円形にしたが、その他の形状にしてもよい。図1Eに示した庇部13bの端面には、GaNの(11−22)面が現れるため、庇部13bの平面形状は正六角形になる。すなわち、横方向への成長は、6方向へ均等に進む。凹部11の縁の各位置から内側に向かって成長した結晶が凹部11のほぼ中心で融合するまでの時間差を短くするために、凹部11の平面形状を六角形以上の正多角形、または円形にすることが好ましい。

【0058】

図4に、凹部11の平面形状を正六角形にした場合の成長用基板10の平面図を示す。相互に隣り合う凹部11の対向する縁同士が平行になるように凹部11が配置されている。このとき、凹部11の寸法Wbは、正六角形の内接円の直径で定義される。凹部11の間隔Wdは、相互に隣り合う凹部11の対向する縁の間隔で定義される。

【0059】

次に、正六角形以上の正多角形または円形の凹部11の寸法Wb及び間隔Wdの好適値について説明する。凹部11の寸法Wbが大きすぎると、横方向に斉唱した庇部13bが凹部11上で接触するまでの時間(半導体層13(図1F)が連続するまでの時間)が長くなる。庇部13bが接触するまでの時間にも、支柱13aの直上には、縦方向の結晶成長が生じている。このため、庇部13bが接触するまでの時間が長くなると、半導体層13の表面の平坦性が悪くなってしまう。凹部11の寸法Wbが10μm程度であれば、縦方向の成長が3μm程度で連続した半導体層13が形成される。この場合、発光素子として十分な平坦性が得られる。従って、凹部11の寸法Wbを10μm以下にすることが好ましい。

【0060】

凹部11の寸法Wbが小さすぎると、凹部11を形成する効果が得られなくなってしまう。凹部11の寸法Wbは1μm以上にすることが好ましく、3μm以上にすることがより好ましい。

【0061】

凹部11の間隔Wdが狭すぎると、凸部の上面に十分な太さの支柱13a(図1D)が形成され難くなり、成長用基板10と半導体層13との接続強度が弱くなってしまう。十分な太さの支柱13aを形成するために、凹部11の間隔Wdを3μm以上にすることが好ましい。凹部11の間隔Wdが広すぎると、凸部の上面に形成される支柱13aの分布のばらつきが大きくなってしまい、凹部11を形成する十分な効果が得られない。従って、凹部11の間隔Wdを20μm以下にすることが好ましく、10μm以下にすることがより好ましい。

【0062】

次に、成長用基板10の表面において、凹部11が占める割合の好ましい範囲について説明する。成長用基板10の凹部形成前の表面の面積に対する凹部11の占める面積の割合(以下、「凹部11の面積比」という。)が高すぎると、支柱13a(図1F)の本数が少なくなり、成長用基板10と半導体層13との十分な接続強度が得られなくなる。十分な接続強度を得るために、凹部11の面積比を50%以下にすることが好ましい。

【0063】

逆に、凹部11の面積比が低すぎると、支柱13a(図1D)の分布のばらつきが大きくなり、凹部11を形成する効果が得られない。支柱13aのばらつきを抑制する十分な効果を得るために、凹部11の面積比を5%以上にすることが好ましい。

【0064】

次に、図1Cに示した下地層12の厚さの好適な範囲について説明する。下地層12が薄すぎると、図1Dから図1Fの工程で、全域でGaNの分解と脱離が生じてしまい、離散的に分布する支柱13aが形成され難くなる。また、下地層12を厚くしすぎると、GaNの分解及び脱離が生じる領域の面内分布のばらつきが大きくなる。このため、支柱13aの分布のばらつきが大きくなってしまう。このため、下地層12の厚さは、150nm〜200nmの範囲内とすることが好ましい。

【0065】

図1Dから図1Fに示した半導体層13を形成するための第1工程と第2工程との好適な条件について説明する。

【0066】

支柱13aの十分な高さを確保するために、第1工程と第2工程との繰り返し回数は、4回以上とすることが好ましい。また、第1工程と第2工程とを切り替える度に、第1工程の成長時間を徐々に短くし、第2工程の成長時間を徐々に長くすることが好ましい。このように時間制御すると、半導体層13形成の初期段階で、GaNの分解と脱離を生じやすくさせ、支柱13aをより高くすることができる。また、半導体層13形成過程の後半では、横方向成長を支配的にすることで、空洞13c(図1F)が形成され易くなる。

【0067】

半導体層13の形成過程の後半で横方向成長を優位にさせることにより、凹部11の上方で半導体層13を、再現性よく連続させることが可能になる。凹部11内の空洞は、凸部の上面よりも高い位置まで達し、凸部の上に形成される空洞とほぼ同一の高さまで達する。このため、凸部の上の空洞、及び凹部11から上方に延びる空洞が、共に、ある高さの仮想平面内に分布することになる。空洞が分布する高さが一定でない場合には、空洞が分布する高さが変化する境界線で、成長用基板10の分離の進行が停止し易くなる。実施例においては、空洞が1枚の仮想平面上に分布するため、成長用基板10の分離の進行が妨げられることがない。

【0068】

上記実施例では、図1Iに示した工程で、Siからなる支持基板を、成長用基板10の上に成長させた半導体層に接合した。その他に、図1Gに示したp側電極25の表面に銅等の金属めっきを施すことにより、十分な機械的支持力を持つ厚さの金属膜を形成してもよい。この構造では、めっきにより形成された金属膜が、支持基板としての役割を持つ。

【0069】

上記実施例では、半導体層13及びn型半導体層20をGaNで形成したが、その他、V族元素として窒素を含むIII−V族化合物半導体で形成してもよい。

【0070】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0071】

10 成長用基板

11 凹部

12 下地層

13 半導体層

13a 支柱

13b 庇部

20 n型半導体層

21 歪緩和層

22 発光層

23 第1p型半導体層

24 第2p型半導体層

25 p側電極

26 接合用金属膜

30 支持基板

31 接合用金属膜

35 n側電極

【技術分野】

【0001】

本発明は、成長用基板の上に半導体層を形成した後、半導体層から成長用基板を分離する半導体素子の製造方法に関する。

【背景技術】

【0002】

発光ダイオード等の光半導体素子の従来の製造方法の一例について説明する。まず、成長用基板の上に、n型半導体層、発光層、及びp型半導体層を成長させる。成長用基板が絶縁性である場合には、p型半導体層及び発光層の一部を除去してn型半導体層を露出させる。n型半導体層の露出した領域、及び露出しているp型半導体層に電極を形成する。

【0003】

成長用基板は、その上に成長させる半導体層の結晶品質に大きな影響を与える。また、成長用基板の導電性、熱伝導性、光吸収係数等の物性が、光半導体素子の電気特性、熱特性、及び光学特性に影響する。結晶性のよい半導体層を形成するために適した成長用基板が、導電性、熱伝導性、光吸収係数等の物性の点で好ましいものであるとは限らない。

【0004】

半導体層を成長させた後、成長用基板を半導体層から分離した光半導体素子が提案されている。最終的に成長用基板が分離されるため、成長用基板として、半導体層の結晶成長に最適のものを選択することができる。成長用基板と半導体層との間に配置される層に空孔を生じさせることにより、成長用基板を半導体層から分離することができる(特許文献1、2)。また、成長用基板と半導体層との間に剥離層を配置し、この剥離層をエッチングすることにより、成長用基板を半導体層から分離することができる(特許文献3)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−228539号公報

【特許文献2】特開2002−241192号公報

【特許文献3】特開2004−172351号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

成長用基板の上に形成する半導体層が薄くても、再現性よく半導体層から成長用基板を分離する方法が望まれる。従来の方法では、半導体層から成長用基板を再現性よく分離することが困難であった。

【課題を解決するための手段】

【0007】

本発明の一観点によると、

表面に凹凸が形成された成長用基板の、該表面の凸部の上面に離散的に分布し、化合物半導体からなる複数の支柱を形成する工程と、

前記支柱によって前記成長用基板の上に支えられ、化合物半導体からなる半導体層を形成する工程と、

前記半導体層の上に、支持基板を接着する工程と、

前記成長用基板を前記半導体層から分離する工程と

を有する半導体素子の製造方法が提供される。

【発明の効果】

【0008】

支持基板を接着した後、再現性よく、成長用基板を半導体層から分離することができる。

【図面の簡単な説明】

【0009】

【図1−1】(1A)は、実施例で用いる成長用基板の断面図であり、(1B)はその平面図である。

【図1−2】(1C)〜(1F)は、実施例による方法で製造される半導体素子の製造途中段階における断面図である。

【図1−3】(1G)、(1H)は、実施例による方法で製造される半導体素子の製造途中段階における断面図である。

【図1−4】(1I)、(1J)は、実施例による方法で製造される半導体素子の製造途中段階における断面図である。

【図1−5】(1K)、(1L)は、実施例による方法で製造される半導体素子の製造途中段階における断面図である。

【図2】実施例及び比較例による方法で作製した試料の接続部の割合を示すグラフである。

【図3】成長用基板の凹部の側面の傾斜角を説明する線図である。

【図4】実施例の変形例による方法で用いる成長用基板の平面図である。

【発明を実施するための形態】

【0010】

図1A〜図1Lを参照して、実施例による半導体素子の製造方法について説明する。

【0011】

図1Aに示すように、成長用基板10の表面に複数の凹部11を形成する。実施例では、成長用基板10として、C面サファイア基板を用いる。凹部11の形成には、通常のフォトリソグラフィ技術を用いる。成長用基板10のエッチングには、例えばBCl3、Cl2、及びArの混合ガスの誘導結合プラズマを用いた反応性イオンエッチングが用いられる。凹部11の側面(段差面)は、成長用基板10の元の表面に対して、ほぼ垂直である。凹部11が形成されていない領域(凸部の上面)は平坦である。

【0012】

図1Bに、凹部11が形成された成長用基板10の平面図を示す。図1Bの一点鎖線1A−1Aにおける断面図が図1Aに相当する。凹部11は、正三角形を敷き詰めた三角格子の格子点に配置される。凹部11の各々の平面形状は円形である。凹部11の平面形状の直径をWbとし、最近接の凹部11の間隔をWdとする。また、図1Aに示したように、凹部11の深さをDとする。一例として、凹部11の深さDは1μmであり、直径Wbは6μmであり、間隔Wdは11μmである。

【0013】

図1Cに示すように、成長用基板10を有機金属化学気相成長(MOCVD)装置に搬入し、成長用基板10の凸部の上面及び凹部11の底面に、GaNからなる下地層12を形成する。成長条件は、例えば下記の通りである。

・トリメチルガリウム(TMG)供給量 11μmol/min

・キャリアガス 窒素ガス(13.5SLM)と水素ガス(4.5SLM)

・アンモニアガス(NH3)供給量 3.3SLM

・成長温度 525℃

上述の条件で、V/III比は14000である。ここで、V/III比は、供給される原料中のIII族元素のモル数に対するV族元素のモル数の比と定義される。下地層12の厚さは、凹部11の深さDよりも薄くする。凹部11の深さDが1μmのとき、例えば下地層12の厚さを200nmとする。このように高いV/III比を採用すると、Gaのマイグレーションが促進され、面内で偏りなくGaN膜が成長する。これにより、表面の凹凸の高さ及びピッチが面内に亘ってほぼ揃った下地層12が得られる。凹部11の側面には、下地層12が形成されない。

【0014】

仮に、3000未満の低いV/III比を採用すると、Gaのマイグレーションが促進されず、原料ガスの気流の影響を受けて、GaNが成長し易い領域と、成長し難い領域との差が顕著に現れる。このため、下地層12は離散的に分布する島状構造になってしまう。良好な下地層12を得るために、成長時のV/III比を3000〜25000の範囲内にすることが好ましい。TMGの供給量は、8μmol/min〜23μmol/minの範囲内とすることが好ましく、9μmol/min〜15μmol/minの範囲内とすることがより好ましい。NH3の供給量は、0.5SLM〜5.5SLMの範囲内とすることが好ましい。

【0015】

成長温度は、425℃〜625℃の範囲内とすることが好ましい。成長速度は、5nm/min〜40nm/minの範囲内とすることが好ましい。

【0016】

図1Dから図1Fまでの工程について説明する。下地層12(図1C)を形成した後、TMGの供給を停止させ、基板温度を1000℃まで上昇させる。成長条件の異なる第1工程と第2工程とを交互に繰り返すことにより、GaNからなる半導体層13(図1F)を形成する。繰り返し回数は、例えば4回とする。

【0017】

第1工程の成長条件は、例えば下記の通りである。

・TMG供給量 23μmol/min

・キャリアガス 窒素ガス(6SLM)と水素ガス(7.5SLM)

・NH3供給量 2.2SLM

・成長時間 膜厚20nmになる時間

第2工程の成長条件は、例えば下記の通りである。

・TMG供給量 45μmol/min

・キャリアガス 窒素ガス(6SLM)と水素ガス(7.5SLM)

・NH3供給量 4.4SLM

・成長時間 膜厚80nmになる時間

第1工程では、縦方向の成長が支配的となり、第2工程では、横方向(面内方向)の成長が支配的となる。第1工程と第2工程とを交互に繰り返す過程で、供給されるGa原子及びN原子が基板表面に吸着されて膜が成長する反応と、成長したGaNが分解し脱離する反応とが生じる。

【0018】

ここで、第1工程で「縦方向成長が支配的」とは、横方向成長速度をVs、縦方向成長速度をVnとしたとき、第1工程のVn/Vsが、第2工程のVn/Vsよりも大きいことを意味する。また、第2工程で「横方向成長が支配的」とは、第2工程のVs/Vnが、第1工程のVs/Vnよりも大きいことを意味する。

【0019】

第1工程で、下地層12(図1C)のうち成長核となる部分から結晶が成長すると同時に、結晶性の低い部分においては、熱によってGaNが分解する。分解によって生成された窒素がガスとなって成長用基板10から脱離する。これにより、凹部11の間の領域(凸部の上面)に離散的に分布する支柱13a(図1D)が形成される。なお、GaNが分解することにより生成された金属Gaは成長用基板10の上に残る。凹部11の底面には、成長用がガスが供給されにくいため、GaNの分解が支配的になり、支柱13aは形成されない。

【0020】

結晶成長の核となる部分以外の下地層12の結晶性を低くするために、下地層12の成長温度は、上述のように、半導体層13の成長温度よりも低い425℃〜625℃の範囲内とすることが好ましい。

【0021】

第2工程では、横方向の成長が支配的になり、支柱13aの先端から横方向に張り出した庇部13b(図1E)が形成される。例えば、原料ガスの供給量を増やすことにより、横方向成長を支配的にすることができる。庇部13bの端面には、GaNの(11−22)面が現れる。ここで、「−2」は、2のオーバーバーを意味する。庇部13bが形成されると、次の第1工程で、その下の空洞にNH3が供給され難くなり、GaNの分解及び窒素の脱離が促進される。これにより支柱13aが細くなる。凹部11内にもNH3が供給され難いため、凹部11の底面においては、GaNの分解と窒素の脱離とが促進される。

【0022】

庇部13bの張り出し量が長くなると、相互に隣り合う支柱13aから成長した庇部13b同士が接触する。凹部11の上方においても、庇部13b同士が接触することにより、面内方向に連続し、平滑な表面を有する半導体層13(図1F)が形成される。半導体層13は、複数の支柱13aによって成長用基板10の上方に支持される。支柱13aの間には、空洞13cが残る。空洞13cは、面内方向に連通している。凹部11内には支柱13aが配置されない。横方向に成長した部分(空洞13cの上の部分)には、成長用基板10と支柱13aとの界面から成長する欠陥が導入され難いため、結晶性の高い半導体層13が得られる。

【0023】

成長用基板10の凸部の上面から半導体層13の上面までの高さは、約400nmである。

【0024】

GaN膜の成長と、分解及び脱離とを並行して生じさせるために、第1工程及び第2工程の成長温度は、800℃〜1200℃の範囲内にすることが好ましい。第1工程において、TMGの供給量を10μmol/min〜30μmol/minの範囲内とし、NH3の供給量を1SLM〜3SLMの範囲内とすることが好ましい。第2工程においては、TMG供給量を30μmol/min〜70μmol/minの範囲内とし、NH3の供給量を3SLM〜7SLMの範囲内とすることが好ましい。

【0025】

半導体層13に、n型ドーパントとしてSiをドープしてもよい。Siの濃度が高くなると横方向成長し難くなるため、Si濃度は、5×1017cm−3以下にすることが好ましい。

【0026】

図1Gに示すように、半導体層13の上に、n型GaNからなるn型半導体層20を形成する。n型半導体層20の厚さは、例えば3μm〜10μmの範囲内である。n型不純物としてSiが用いられ、その濃度は例えば約5×1018cm−3である。Si原料として、例えばSiH4が用いられる。

【0027】

成長条件は、例えば下記の通りである。

・成長温度 1000℃

・TMG供給量 45μmol/min

・NH3供給量 4.4SLM

なお、成長温度を980℃〜1020℃の範囲内としてもよい。TMG供給量を10μmol/min〜70μmol/minの範囲内とし、NH3供給量を3.3SLM〜5.5SLMの範囲内としてもよい。V/III比は、2000〜22500の範囲内とすることが好ましく、3000〜8000の範囲内とすることが、平坦性及び結晶性の点でより好ましい。成長速度は、0.5μm/h〜5μm/hの範囲内とすることが好ましい。図1Gでは、半導体層13とn型半導体層20との境界を明示しているが、実際には、両者ともGaNで形成され、同一チャンバ内で連続して成長されるため、両者の境界が明瞭に識別できるわけではない。

【0028】

n型半導体層20の上に歪緩和層21を形成する。歪緩和層21は、例えば交互に積層された厚さ2nmのGaN層と厚さ2nmのIn0.2Ga0.8N層とを含み、合計の厚さは例えば120nmである。なお、各層の厚さ及び積層数を変えることにより、合計の膜厚を50nm〜300nmの範囲内にしてもよい。歪緩和層21の成長条件は、例えば下記の通りである。

・成長温度 730℃〜790℃

・TMG供給量 3.6μmol/min

・トリメチルインジウム(TMI)供給量 3.6μmol/min

・NH3供給量 3.3SLM〜5.5SLM

GaN層の成長時には、TMIの供給が停止される。TMGの供給量及びTMIの供給量を1μmol/min〜10μmol/minの範囲内としてもよい。ただし、TMGの供給量とTMIの供給量との比は、In組成比が0.2になるように調整される。

【0029】

歪緩和層21にSiをドープしてもよい。Si濃度は、例えば5×1017cm−3以下とする。また、InxGa1−xN層(0<x<0.2)と、In0.2Ga0.8N層とが交互に積層された構造としてもよい。

【0030】

歪緩和層21の上に発光層22を形成する。発光層22は、交互に積層されたGaNからなる厚さ14nmの障壁層と、In0.35Ga0.65Nからなる厚さ2.2nmの井戸層とを含む。障壁層及び井戸層の層数は、それぞれ5である。発光層22の成長条件は、例えば下記の通りである。

・成長温度 700℃〜760℃

・TMG供給量 3.6μmol/min

・TMI供給量 10μmol/min

・NH3供給量 3.3SLM〜5.5SLM

GaN層の成長時には、TMIの供給が停止される。TMGの供給量を1μmol/min〜10μmol/minの範囲内としてもよい。このとき、TMIの供給量は、In組成比が0.35になるように調整される。発光層22にSiをドープしてもよい。Si濃度は、例えば5×1017cm−3以下とする。

【0031】

発光層22の上に、Mgがドープされたp型Al0.2Ga0.8Nからなる第1p型半導体層23を形成する。第1p型半導体層23の厚さは、例えば20nm〜60nmの範囲内である。第1p型半導体層23の成長条件は、例えば下記の通りである。

・成長温度 770℃〜970℃

・TMG供給量 8.1μmol/min

・トリメチルアルミニウム(TMA)供給量 7.6μmol/min

・NH3供給量 3.3SLM〜5.5SLM

ドーパントであるMgの原料として、例えばビスシクロペンタジエニルマグネシウム(CP2Mg)を用いることができる。TMGの供給量を4μmol/min〜20μmol/minの範囲内としてもよい。このとき、TMAの供給量は、Al組成比が0.2になるように調整される。Mg濃度は、例えば1×1020cm−3である。

【0032】

第1p型半導体層23の上に、Mgがドープされたp型GaNからなる第2p型半導体層24を形成する。第2p型半導体層24の厚さは、例えば100nm〜300nmの範囲内である。第2p型半導体層24の成長条件は、例えば下記の通りである。

・成長温度 770℃〜970℃

・TMG供給量 18μmol/min

・NH3供給量 3.3SLM〜5.5SLM

TMGの供給量を8μmol/min〜36μmol/minの範囲内としてもよい。Mg濃度は、例えば1×1020cm−3である。

【0033】

第2p型半導体層24の上に、p側電極25を形成する。p側電極25は、例えば、基板側に配置された厚さ1nmの白金(Pt)膜と、その上に配置された厚さ300nmの銀(Ag)膜とを含む。Pt膜及びAg膜の形成には、例えば電子ビーム蒸着が用いられる。Pt膜は、オーミック接触を確保するためのものである。p側電極25と第2p型半導体層24との接触抵抗率は、1×10−3Ω・cm2である。Ag膜は、発光層22からの放射光に対して高い反射率を確保するためのものである。p側電極25の反射率は約80%である。Pt膜の厚さを0.3nm〜100nmの範囲内としてもよい。Ag膜の厚さを50nm〜300nmの範囲内としてもよい。

【0034】

p側電極25として、Pt膜とRh膜との2層構造を採用してもよいし、Ni膜とAg膜との2層構造を採用してもよい。

【0035】

p側電極25の上に、共晶用金属膜26を形成する。共晶用金属膜26は、例えば厚さ100nmのTi膜、その上の厚さ200nmのPt膜、及びその上の厚さ200nmのAu膜で構成される。これらの膜の形成には、例えば電子ビーム蒸着が用いられる。Ti膜は、その上のPt膜の密着性を高める。Pt膜は、AuSn合金との接合時におけるSnの拡散を防止する。Au膜は、AuSn共晶を形成するためのものである。

【0036】

Ti膜の厚さを50nm〜100nmの範囲内としてもよい。Pt膜の厚さを200nm以上にしてもよい。Au膜は、接合されるAuSn膜の厚さ及び組成を考慮し、AuSn共晶点に整合する厚さにすればよい。

【0037】

共晶用金属膜26を、厚さ100nmのTi膜、厚さ100nmのPt膜、厚さ200nmのAu膜、厚さ100nmのPt膜、及び厚さ200nmのAu膜がこの順番に積層された5層構造としてもよい。5層構造を採用することにより、Snの拡散防止機能を高めることができる。

【0038】

図1Hに示すように、支持基板30の片側の表面に共晶用金属膜31を形成する。支持基板30には、例えばシリコン基板が用いられる。共晶用金属膜31は、Pt膜、Ti膜、Ni膜、Au膜、及びAuSn膜がこの順番に積層された積層構造を有する。Pt膜は、支持基板30のSiとシリサイド反応することにより、支持基板30に対してオーミック接触する。Ti膜は、シリサイド化したPt膜と、Ni膜との密着性を高める。Ni膜は、AuSnの濡れ性を高める。Au膜は、Ni膜の酸化を防止する。AuSn膜は、共晶を形成するためのものである。

【0039】

支持基板30と成長用基板10とを、共晶用金属膜26と31とが対向する向きに配置する。

【0040】

図1Iに示すように、共晶用金属膜26と31とを接触させ、真空中で熱圧着を行う。熱圧着時の圧力は、3MPaとし、温度は330℃とする。なお、熱圧着を窒素ガス等の不活性ガス雰囲気中で行ってもよい。また、AuSn共晶の形成に適した温度であれば、330℃以外の温度で熱圧着を行ってもよい。

【0041】

図1Jに示すように、基板温度を室温に戻す過程で、成長用基板10と支持基板30との熱膨張係数の相違に起因して、成長用基板10が半導体層13から自然に分離する。自然分離した半導体層13の表面には、複数の支柱13aが残った状態である。なお、自然分離し難い場合には、ピンセット等で成長用基板10の端部に機械的な衝撃を与えてもよい。また、超音波により衝撃を与えてもよい。成長用基板10と半導体層13との間の空洞に溶剤を浸透させ、加熱してもよい。この場合には、溶剤の蒸気圧によって成長用基板10が半導体層13から分離する。

【0042】

その他に、補助的にレーザを照射したり、酸やアルカリに浸漬させたりして、分離してもよい。また、電界エッチング手法を用いてもよい。

【0043】

図1Kに示すように、半導体層13の表面を塩酸で処理する。塩酸処理により、n型半導体層20が露出し、露出した表面が平坦になる。なお、塩酸に代えて、窒化物半導体をエッチングできる他の薬液、例えばリン酸、硫酸、水酸化カリウム(KOH)、水酸化ナトリウム(NaOH)等を用いてもよい。また、薬液処理に代えて、Arプラズマや塩素系プラズマを用いたドライエッチングを適用してもよい。

【0044】

図1Lに示すように、n型半導体層20の表面の一部の領域に、n側電極35を形成する。n側電極35は、例えばTi膜と、その上に配置されたAl膜との2層で構成される。n側電極35として、Al膜とRh膜との2層構造、Al膜とIr膜との2層構造、Al膜とPt膜との2層構造、またはAl膜とPd膜との2層構造を採用してもよい。これらの積層構造とすることにより、n側電極35とn型半導体層20との接触抵抗率を1×10−4Ω・cm2以下にすることができる。n側電極35の上に、ボンディングし易くするために、Ti膜とAu膜とを順番に積層してもよい。

【0045】

その後、支持基板30からn型半導体層20までの積層構造を、個別のチップに分割する。以下、分割方法について説明する。

【0046】

n型半導体層20の表面から、p側電極25まで達する溝を、反応性イオンエッチング(RIE)により形成する。溝を形成した後、支持基板30をダイシングし、各チップに分割する。なお、レーザスクライブ等の技術を用いてもよい。

【0047】

次に、図2を参照して、図1Aの凹部11を形成した効果について説明する。

【0048】

凹部11を形成した成長用基板10を用いて半導体層を成長させた複数の試料と、凹部11を形成していない成長用基板を用いて半導体層を成長させた複数の試料とを作製した。図1Jに示したように、作製した試料の成長用基板を半導体層から分離させ、支柱13aの剥離面の合計の面積を測定した。成長用基板10の表面の面積に対する支柱13aの剥離面の合計の面積の比を「接続部の割合」ということとする。

【0049】

図2の縦軸は、接続部の割合を単位「%」で表す。白丸は、凹部11を形成した実施例による方法で作製した複数の試料の接続部の割合を示し、黒丸は、凹部を形成していない成長用基板を用いた複数の試料の接続部の割合を示す。なお、実施例による方法で作製する試料においては、図1Cに示した下地層12の厚さを180nmとし、凹部を形成していない成長用基板を用いて作製する試料においては、下地層12の厚さを200nmとした。

【0050】

凹部を形成していない成長用基板を用いる場合には、成長用基板と半導体層との間に十分な大きさの空洞を確保するために、下地層12を200nm程度まで厚くしなければならない。実施例による方法で作製する場合には、成長用基板に凹部が形成されているため、下地層12を180nm程度まで薄くしても、十分な大きさの空洞を確保することができる。

【0051】

すべての試料において、図1Gに示した半導体層13及びn型半導体層20の合計の厚さは6μmとした。凹部11の直径Wbは4μmとし、凹部11の間隔Wdは3μmとし、凹部11の深さDは1μmとした。

【0052】

凹部11を形成した試料の方が、接続部の割合のばらつきが小さいことがわかる。接続部の割合が高すぎると、半導体層から成長用基板を分離させることが困難になる。凹部11を形成すると、凹部11の底面に支柱13a(図1D)が分布しないため、接続部の割合が高くなりすぎることが回避される。

【0053】

逆に、接続部の割合が低すぎると、図1Iに示した支持基板30を接合する前に、成長用基板が自然に分離してしまう。凹部が形成されていない成長用基板を用いる場合には、下地層12を200nm程度まで厚くしなければならない。下地層12が厚いと、支柱13aの分布密度のばらつきが大きくなる。このため、作製した試料の接続部の割合が低くなりすぎる場合もある。凹部11を形成することにより、接続部の割合が低くなりすぎることを回避できる。

【0054】

凹部11を形成することにより、接続部の割合のばらつきを抑制し、支持基板30を接合した後に、再現性よく成長用基板10を分離することができる。

【0055】

次に、凹部11の好ましい断面形状について説明する。上記実施例では、凹部11の側面が、成長用基板10の元の表面(凸部の上面によって画定される仮想平面)に対してほぼ垂直、すなわち傾斜角がほぼ90°であった。このとき、凹部11の断面形状はほぼ長方形である。凹部11の側面の傾斜角が小さくなると、側面にも下地層12(図1C)が成長してしまう。側面に下地層12が形成されると、側面にも半導体層13(図1F)の成長が始まり、凹部11内が半導体層13で埋め込まれてしまう場合がある。または、凹部11の開口面よりも低い位置で半導体層13が連続してしまう場合もある。凹部11を形成する十分な効果を得るために、図3に示すように、凹部11の側面(段差面)の傾斜角θbを、70°〜90°の範囲内にすることが好ましく、80°〜90°の範囲内することがより好ましい。

【0056】

次に、凹部11の好ましい深さについて説明する。凹部11が浅すぎると、凹部11の底面に形成された下地層12(図1C)から支柱13a(図1D)が伸び、半導体層13(図1F)に連続してしまう。凹部11の底面に支柱13aが分布しないようにするために、凹部11の深さを1μm以上にすることが好ましい。逆に、凹部11の加工のし易さの点から、凹部11の深さは3μm以下にすることが好ましい。

【0057】

次に、凹部11の平面形状について説明する。上記実施例では、凹部11の平面形状を円形にしたが、その他の形状にしてもよい。図1Eに示した庇部13bの端面には、GaNの(11−22)面が現れるため、庇部13bの平面形状は正六角形になる。すなわち、横方向への成長は、6方向へ均等に進む。凹部11の縁の各位置から内側に向かって成長した結晶が凹部11のほぼ中心で融合するまでの時間差を短くするために、凹部11の平面形状を六角形以上の正多角形、または円形にすることが好ましい。

【0058】

図4に、凹部11の平面形状を正六角形にした場合の成長用基板10の平面図を示す。相互に隣り合う凹部11の対向する縁同士が平行になるように凹部11が配置されている。このとき、凹部11の寸法Wbは、正六角形の内接円の直径で定義される。凹部11の間隔Wdは、相互に隣り合う凹部11の対向する縁の間隔で定義される。

【0059】

次に、正六角形以上の正多角形または円形の凹部11の寸法Wb及び間隔Wdの好適値について説明する。凹部11の寸法Wbが大きすぎると、横方向に斉唱した庇部13bが凹部11上で接触するまでの時間(半導体層13(図1F)が連続するまでの時間)が長くなる。庇部13bが接触するまでの時間にも、支柱13aの直上には、縦方向の結晶成長が生じている。このため、庇部13bが接触するまでの時間が長くなると、半導体層13の表面の平坦性が悪くなってしまう。凹部11の寸法Wbが10μm程度であれば、縦方向の成長が3μm程度で連続した半導体層13が形成される。この場合、発光素子として十分な平坦性が得られる。従って、凹部11の寸法Wbを10μm以下にすることが好ましい。

【0060】

凹部11の寸法Wbが小さすぎると、凹部11を形成する効果が得られなくなってしまう。凹部11の寸法Wbは1μm以上にすることが好ましく、3μm以上にすることがより好ましい。

【0061】

凹部11の間隔Wdが狭すぎると、凸部の上面に十分な太さの支柱13a(図1D)が形成され難くなり、成長用基板10と半導体層13との接続強度が弱くなってしまう。十分な太さの支柱13aを形成するために、凹部11の間隔Wdを3μm以上にすることが好ましい。凹部11の間隔Wdが広すぎると、凸部の上面に形成される支柱13aの分布のばらつきが大きくなってしまい、凹部11を形成する十分な効果が得られない。従って、凹部11の間隔Wdを20μm以下にすることが好ましく、10μm以下にすることがより好ましい。

【0062】

次に、成長用基板10の表面において、凹部11が占める割合の好ましい範囲について説明する。成長用基板10の凹部形成前の表面の面積に対する凹部11の占める面積の割合(以下、「凹部11の面積比」という。)が高すぎると、支柱13a(図1F)の本数が少なくなり、成長用基板10と半導体層13との十分な接続強度が得られなくなる。十分な接続強度を得るために、凹部11の面積比を50%以下にすることが好ましい。

【0063】

逆に、凹部11の面積比が低すぎると、支柱13a(図1D)の分布のばらつきが大きくなり、凹部11を形成する効果が得られない。支柱13aのばらつきを抑制する十分な効果を得るために、凹部11の面積比を5%以上にすることが好ましい。

【0064】

次に、図1Cに示した下地層12の厚さの好適な範囲について説明する。下地層12が薄すぎると、図1Dから図1Fの工程で、全域でGaNの分解と脱離が生じてしまい、離散的に分布する支柱13aが形成され難くなる。また、下地層12を厚くしすぎると、GaNの分解及び脱離が生じる領域の面内分布のばらつきが大きくなる。このため、支柱13aの分布のばらつきが大きくなってしまう。このため、下地層12の厚さは、150nm〜200nmの範囲内とすることが好ましい。

【0065】

図1Dから図1Fに示した半導体層13を形成するための第1工程と第2工程との好適な条件について説明する。

【0066】

支柱13aの十分な高さを確保するために、第1工程と第2工程との繰り返し回数は、4回以上とすることが好ましい。また、第1工程と第2工程とを切り替える度に、第1工程の成長時間を徐々に短くし、第2工程の成長時間を徐々に長くすることが好ましい。このように時間制御すると、半導体層13形成の初期段階で、GaNの分解と脱離を生じやすくさせ、支柱13aをより高くすることができる。また、半導体層13形成過程の後半では、横方向成長を支配的にすることで、空洞13c(図1F)が形成され易くなる。

【0067】

半導体層13の形成過程の後半で横方向成長を優位にさせることにより、凹部11の上方で半導体層13を、再現性よく連続させることが可能になる。凹部11内の空洞は、凸部の上面よりも高い位置まで達し、凸部の上に形成される空洞とほぼ同一の高さまで達する。このため、凸部の上の空洞、及び凹部11から上方に延びる空洞が、共に、ある高さの仮想平面内に分布することになる。空洞が分布する高さが一定でない場合には、空洞が分布する高さが変化する境界線で、成長用基板10の分離の進行が停止し易くなる。実施例においては、空洞が1枚の仮想平面上に分布するため、成長用基板10の分離の進行が妨げられることがない。

【0068】

上記実施例では、図1Iに示した工程で、Siからなる支持基板を、成長用基板10の上に成長させた半導体層に接合した。その他に、図1Gに示したp側電極25の表面に銅等の金属めっきを施すことにより、十分な機械的支持力を持つ厚さの金属膜を形成してもよい。この構造では、めっきにより形成された金属膜が、支持基板としての役割を持つ。

【0069】

上記実施例では、半導体層13及びn型半導体層20をGaNで形成したが、その他、V族元素として窒素を含むIII−V族化合物半導体で形成してもよい。

【0070】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0071】

10 成長用基板

11 凹部

12 下地層

13 半導体層

13a 支柱

13b 庇部

20 n型半導体層

21 歪緩和層

22 発光層

23 第1p型半導体層

24 第2p型半導体層

25 p側電極

26 接合用金属膜

30 支持基板

31 接合用金属膜

35 n側電極

【特許請求の範囲】

【請求項1】

表面に凹凸が形成された成長用基板の、該表面の凸部の上面に離散的に分布し、化合物半導体からなる複数の支柱を形成する工程と、

前記支柱によって前記成長用基板の上に支えられ、化合物半導体からなる半導体層を形成する工程と、

前記半導体層の上に、支持基板を接着する工程と、

前記成長用基板を前記半導体層から分離する工程と

を有する半導体素子の製造方法。

【請求項2】

前記成長用基板の表面には、複数の凹部が離散的に分布しており、凸部の上面は平坦である請求項1に記載の半導体素子の製造方法。

【請求項3】

前記支柱を形成する工程において、面内方向よりも縦方向の成長が支配的になる条件で前記支柱を成長させる第1工程と、縦方向よりも面内方向の成長が支配的になる条件で前記支柱を成長させる第2の工程とを交互に繰り返す請求項1または2に記載の半導体素子の製造方法。

【請求項4】

前記成長用基板の上に前記支柱を形成する前に、前記成長用基板の表面に、前記支柱を形成するときの成長温度よりも低い成長温度で、前記成長用基板の表面の凹凸の高低差よりも薄い化合物半導体からなる下地層を形成する工程を含む請求項1乃至3のいずれか1項に記載の半導体素子の製造方法。

【請求項5】

前記成長用基板の表面に形成された凹凸の段差面は、前記凸部の上面で画定される仮想平面に対して70°〜90°の傾斜角を有する請求項1乃至4のいずれか1項に記載の半導体素子の製造方法。

【請求項6】

前記凹部の各々の平面形状は、直径10μm以下の円形、または直径10μm以下の円を内接円とする多角形である請求項1乃至5のいずれか1項に記載の半導体素子の製造方法。

【請求項7】

前記支柱及び前記半導体層は、V族元素として窒素を含むIII−V族化合物半導体であり、

前記第1工程及び前記第2工程では、前記成長用基板を成長用チャンバ内に配置し、該チャンバ内に、III族原料及びV族原料を供給することにより前記支柱を成長させ、前記第1工程におけるIII族原料及びV族原料の供給量が、前記第2工程におけるIII族原料及びV族原料の供給量よりも少ない請求項3に記載の半導体素子の製造方法。

【請求項1】

表面に凹凸が形成された成長用基板の、該表面の凸部の上面に離散的に分布し、化合物半導体からなる複数の支柱を形成する工程と、

前記支柱によって前記成長用基板の上に支えられ、化合物半導体からなる半導体層を形成する工程と、

前記半導体層の上に、支持基板を接着する工程と、

前記成長用基板を前記半導体層から分離する工程と

を有する半導体素子の製造方法。

【請求項2】

前記成長用基板の表面には、複数の凹部が離散的に分布しており、凸部の上面は平坦である請求項1に記載の半導体素子の製造方法。

【請求項3】

前記支柱を形成する工程において、面内方向よりも縦方向の成長が支配的になる条件で前記支柱を成長させる第1工程と、縦方向よりも面内方向の成長が支配的になる条件で前記支柱を成長させる第2の工程とを交互に繰り返す請求項1または2に記載の半導体素子の製造方法。

【請求項4】

前記成長用基板の上に前記支柱を形成する前に、前記成長用基板の表面に、前記支柱を形成するときの成長温度よりも低い成長温度で、前記成長用基板の表面の凹凸の高低差よりも薄い化合物半導体からなる下地層を形成する工程を含む請求項1乃至3のいずれか1項に記載の半導体素子の製造方法。

【請求項5】

前記成長用基板の表面に形成された凹凸の段差面は、前記凸部の上面で画定される仮想平面に対して70°〜90°の傾斜角を有する請求項1乃至4のいずれか1項に記載の半導体素子の製造方法。

【請求項6】

前記凹部の各々の平面形状は、直径10μm以下の円形、または直径10μm以下の円を内接円とする多角形である請求項1乃至5のいずれか1項に記載の半導体素子の製造方法。

【請求項7】

前記支柱及び前記半導体層は、V族元素として窒素を含むIII−V族化合物半導体であり、

前記第1工程及び前記第2工程では、前記成長用基板を成長用チャンバ内に配置し、該チャンバ内に、III族原料及びV族原料を供給することにより前記支柱を成長させ、前記第1工程におけるIII族原料及びV族原料の供給量が、前記第2工程におけるIII族原料及びV族原料の供給量よりも少ない請求項3に記載の半導体素子の製造方法。

【図1−1】

【図1−2】

【図1−3】

【図1−4】

【図1−5】

【図2】

【図3】

【図4】

【図1−2】

【図1−3】

【図1−4】

【図1−5】

【図2】

【図3】

【図4】

【公開番号】特開2011−192752(P2011−192752A)

【公開日】平成23年9月29日(2011.9.29)

【国際特許分類】

【出願番号】特願2010−56480(P2010−56480)

【出願日】平成22年3月12日(2010.3.12)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

【公開日】平成23年9月29日(2011.9.29)

【国際特許分類】

【出願日】平成22年3月12日(2010.3.12)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

[ Back to top ]