半導体素子制御装置

【課題】電源電圧が低下した場合でも、制御対象とする半導体素子を適切に制御することができる半導体素子制御装置を提供する。

【解決手段】電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用電圧Vgsとの差電圧を付与する。

【解決手段】電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用電圧Vgsとの差電圧を付与する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、直流電源と負荷との間に接続される電圧駆動型の半導体素子を制御する半導体素子制御装置に関する。

【背景技術】

【0002】

例えば降圧型のDC/DCコンバータのような電源回路において、電源とグランドとの間にパワーMOSFETのような半導体スイッチング素子を接続し、そのFETを高速でスイッチング制御する場合には、ゲート電圧がゲート−ソース間電圧の耐圧を超えないようにクランプ制御することが行われている。そのような従来技術の一例として、特許文献1に開示されているものがある(図14参照)。

【特許文献1】特開平11−205123号公報(図2)

【発明の開示】

【発明が解決しようとする課題】

【0003】

この回路では、制御対象とするPチャネルMOSFET:M5をオンさせる場合のゲート電圧は、電源電圧に対して常にFET:M8,M6の閾値電圧VT分(2VT)だけ低い電圧となるように制御される。その結果、電源電圧Vddが低下した場合であっても、ゲート電圧は上記の制約を受けるため、FET:M5を十分にオンさせることができないという問題があった。

本発明は上記事情に鑑みてなされたものであり、その目的は、電源電圧が低下した場合でも、制御対象とする半導体素子を適切に制御することができる半導体素子制御装置を提供することにある。

【課題を解決するための手段】

【0004】

請求項1記載の半導体素子制御装置によれば、電圧付与回路は、電源電圧が閾値以下である場合は駆動回路のグランド側端子にグランドレベル近傍の電圧を付与し、電源電圧が閾値を超えている場合は、前記グランド側端子に電源電圧とクランプ制御用電圧との差電圧を付与する。即ち、電源電圧が閾値を超えていれば、制御対象とする半導体素子の電源側端子と導通制御端子との電圧差はクランプ制御用電圧となり、電源電圧が閾値以下であれば、上記電圧差は電源電圧に近い値となる。従って、電源電圧が低下した結果クランプ制御が不要な状態となった場合に、制御対象の半導体素子を十分にオンさせることができる。

【0005】

請求項2記載の半導体素子制御装置によれば、電圧発生回路は、電源電圧と閾値との関係に応じて、グランドレベル近傍の電圧と前記差電圧とを切り換えて出力し、電圧バッファ回路は、電圧発生回路の出力電圧に応じた電圧を、駆動回路のグランド側端子に付与する。したがって、電圧発生回路の出力電圧により、グランド側端子に付与する電圧を切り換えることができる。

【0006】

請求項3記載の半導体素子制御装置によれば、電源電圧が定電流回路の動作開始電圧に達しなければ、抵抗素子との共通接続点の電位はグランドレベル付近の電圧となり、電源電圧が前記動作開始電圧に達すると、共通接続点の電位は、電源電圧より抵抗素子における電圧降下分を減じた値となる。したがって、定電流回路の動作開始電圧に応じて閾値を設定できると共に、抵抗素子の抵抗値と定電流回路の電流値とでクランプ制御電圧を設定することができる。

【0007】

請求項4記載の半導体素子制御装置によれば、電源電圧が定電流回路の動作開始電圧に達すると、ツェナーダイオードとの共通接続点の電位は、電源電圧よりツェナー電圧を減じた値となる。したがって、ツェナー電圧によりクランプ制御電圧を設定することができる。

【0008】

請求項5記載の半導体素子制御装置によれば、電圧バッファ回路を構成するオペアンプが、電圧発生回路の出力電圧に応じて駆動回路のグランド側端子とグランドとの間に接続される半導体素子の導通状態を制御して前記グランド側端子の電位を制御するので、グランド側端子の電位を、電圧発生回路の出力電圧に応じて設定することができる。

【0009】

請求項6記載の半導体素子制御装置によれば、電圧バッファ回路を構成する第2半導体素子は電圧発生回路の出力電圧により導通制御され、その第2半導体素子の導通状態に応じて第1半導体素子の導通が制御される。したがって、グランド側端子の電位を、前記出力電圧に、第2半導体素子が導通することで付与される定電圧を加えた電位に制御することができる。

【0010】

請求項7記載の半導体素子制御装置によれば、導通制御回路は、電源電圧が前記閾値以下のレベルに設定される下限値を下回った場合に、駆動回路のグランド側端子とグランドとの間に接続される半導体素子を導通させる。従って、電圧付与回路が、十分な低電圧を付与することができない構成である場合でも、補助電圧付与回路の作用により十分に低い電圧を駆動回路のグランド側端子に付与できる。

【0011】

請求項8記載の半導体素子制御装置によれば、導通制御回路は、補助電圧付与回路を構成する半導体素子の導通制御にヒステリシス特性を持たせるので、電源電圧が下限値付近で変動する場合に、前記半導体素子が頻繁に断続されることを回避できる。

【発明を実施するための最良の形態】

【0012】

(第1実施例)

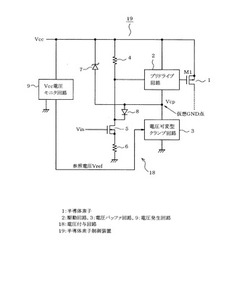

以下、本発明の第1実施例について図1乃至図5を参照して説明する。図1は、半導体素子制御装置の全体構成を概略的に示すものである。電源Vccとグランドとの間には、PチャネルMOSFET(半導体素子,トランジスタ)1と、図示しない負荷との直列回路が接続される。この場合、負荷とは、DCモータやランプ,その他インダクタなどである。FET1のゲート(導通制御端子)には、プリドライブ回路(駆動回路)2によりゲート電圧が与えられて、FET1のON,OFF、すなわち負荷に対する通電が制御される。

【0013】

プリドライブ回路2の電源側端子は電源Vccに接続されており、グランド側端子は、電圧可変型クランプ回路3(以下、単にクランプ回路と称す)を介してグランドに接続されている。このクランプ回路(電圧バッファ回路)3は、プリドライブ回路2のグランド側端子に、仮想グランド電圧Vcpを付与するものである。また、電源Vccとグランドとの間には、抵抗素子4,NチャネルMOSFET5,抵抗素子6の直列回路が接続されており、FET5のドレインは、プリドライブ回路2の入力端子に接続されている。

【0014】

電源Vccとプリドライブ回路2のグランド側端子との間には、過電圧保護用のツェナーダイオード7が接続されており、そのツェナーダイオード7のアノードとFET5のドレインとの間には、クランプ用のダイオード8が接続されている。FET5のゲートには外部より制御信号Vinが与えられるようになっており、制御信号Vinがハイレベルになると、FET5がONしてプリドライブ回路2の入力端子がロウレベルとなり、FET1がONされる。

【0015】

また、電源Vccとグランドとの間には電圧モニタ回路(電圧発生回路)9が接続されている。この電圧モニタ回路9は、電源Vccの電圧レベルに応じて、クランプ回路3に出力する参照電圧Vrefを変化させるようになっており、クランプ回路3は、その参照電圧Vrefに応じてプリドライブ回路2のグランド側端子に与える仮想グランド電圧Vcpを変化させる。

【0016】

図2は、プリドライブ回路2の具体構成例を示すものである。プリドライブ回路2は、P,NチャネルMOSFET10P,10NよりなるCMOSインバータと、P,NチャネルMOSFET11P,11NよりなるCMOSインバータとを直列接続して構成されている。FET10P及び11Pのソースは電源Vccに接続され、FET10N及び11Nのソースには、クランプ回路3により仮想グランド電圧Vcpが与えられる。そして、FET10P,10NのゲートはFET5のドレインに接続され、FET11P,11NのドレインはFET1のゲートに接続される。

【0017】

図3(a),(b)は、電圧モニタ回路9(a,b)の具体構成例を示す。図3(a)は、電源Vccとグランドとの間に、抵抗素子12と定電流回路13との直列回路を接続したものであり、両者の共通接続点がクランプ回路3に与える参照電圧Vrefとなる。また、図3(b)は、(a)の抵抗素子12をツェナーダイオード14に置き換えたものである。これらの電圧モニタ回路9は、例えば電源Vccの最大電圧が16V程度である場合に閾値電圧Vthを8Vに設定し、

Vcc>Vth → Vref=Vcc−Vgs …(1)

Vcc≦Vth → Vref≒0 …(2)

となるように、参照電圧Vrefを変化させる。ここで、電圧Vgsは、プリドライブ回路2がFET1をONさせる場合に、FET1のゲート−ソース間電圧として付与する電圧であり、FET1のゲート−ソース間耐圧Vgs(max)(例えば10V)を超えないようにゲート電圧をクランプする電圧(クランプ制御用電圧)で、例えば8Vに設定されている。

【0018】

すなわち、図3の構成では、Vcc≦Vthの場合、定電流回路13は電流を流さないように構成されており、その結果、参照電圧Vref≒0となる。そして、Vcc>Vthの場合、(a)では、定電流回路13が流す定電流により抵抗素子12に発生する電圧降下が電圧Vgsに相当するように定められ、(b)では、ツェナーダイオード14のツェナー電圧Vz=Vgsに定められる。

【0019】

図4(a),(b)は、クランプ回路3(a,b)の具体構成例を示す。図4(a)は、NチャネルMOSFET15のドレイン,ゲートに、オペアンプ16の非反転入力端子と、出力端子とをそれぞれ接続して構成したもので、オペアンプ16の反転入力端子には、電圧モニタ回路9より参照電圧Vrefが与えられる。また、図4(b)は、(a)のFET15に替えて、NPNトランジスタ17を接続したものである。

尚、以上の構成において、クランプ回路3と電圧モニタ回路9とは、電圧付与回路18を構成している。また、以上の構成よりFET1を除いたものが、半導体素子制御装置19を構成している。

【0020】

次に、本実施例の作用について図5も参照して説明する。図5は、電源電圧Vccが16V〜0Vの範囲で変化する場合に、クランプ回路3によって付与される仮想グランド電圧Vcpの変化を示すものである。電源電圧Vccが、電圧モニタ回路9に設定されている閾値電圧Vthを上回る場合、クランプ回路3に付与される参照電圧Vrefは、上記(1)式で示したようにVref=Vcc−Vgs となり、その参照電圧Vrefは、クランプ回路3のオペアンプ16の作用により仮想グランド電圧Vcpとして出力される。

【0021】

その結果、制御信号Vinがハイレベルとなり、プリドライブ回路2の入力端子がロウレベルになると、内部の出力側FET11P,11NがそれぞれOFF,ONとなるので、FET1(M1)のゲート電圧は、ほぼ仮想グランド電圧Vcpに等しくなる。この時、FET1のゲート−ソース(電源側端子)間電圧は、Vcc−(Vcc−Vgs)=Vgsとなり、FET1は、電圧差8Vでクランプされた状態でONとなる。

上記の状態は、Vcc>Vthが成立する間にFET1がONとなる場合は常に維持されるので、FET1のソース−ゲート間電圧は常にVcp=8Vとなり、電圧クランプ機能が有効となる。

【0022】

そして、電源電圧Vccが閾値電圧Vth以下になると、参照電圧Vrefは、上記(2)式で示したようにVref≒0となるので、仮想グランド電圧Vcpも、Vcp≒0として出力される。この時、FET1がONする場合のソース−ゲート間電圧は、ほぼ電源電圧Vccとなる。

【0023】

以上の結果、電源電圧Vccと仮想グランド電圧Vcpとの関係は、図5に示すようになる。尚、図5において、電源電圧Vccが0V〜1.5V付近の間に仮想グランド電圧Vcpが上昇するように示されているのは、この区間ではオペアンプ16が、図4(a)の場合、FET15をONさせるのに必要な電圧VTを出力できず、仮想グランド電圧Vcpがハイインピーダンス状態になることを示している。したがって、図4(b)の場合、上記ハイインピーダンス状態になる電圧範囲は0V〜0.6V付近となる。

【0024】

以上のように本実施例によれば、電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用の電圧Vgsとの差電圧を付与するようにした。従って、電源電圧Vccが低下することでアクティブなクランプ制御が不要となった状況下でFET1をONさせる場合は、クランプ制御を無効化してゲート−ソース間電圧を電源電圧Vccにほぼ等しくすることができ、FET1を十分にONさせることができる。

【0025】

また、電圧付与回路18を電圧モニタ回路9とクランプ回路3とで構成し、電圧モニタ回路9が出力する電圧に応じて、プリドライブ回路2のグランド側端子に与える仮想グランド電圧Vcpを切り換えるようにした。そして、電圧モニタ回路9aとして、抵抗素子12と定電流回路13との直列回路で構成すれば、定電流回路13の動作開始電圧に応じて閾値電圧Vthを設定すると共に、抵抗素子12の抵抗値と定電流回路13の電流値とでクランプ制御電圧Vgsを設定することができる。また、電圧モニタ回路9bとして、ツェナーダイオード14と定電流回路13との直列回路で構成すれば、ツェナー電圧Vzでクランプ制御電圧Vgsを設定することができる。

【0026】

そして、クランプ制御回路3は、オペアンプ16が、参照電圧Vrefに応じてプリドライブ回路2のグランド側端子とグランドとの間に接続されるFET15又はトランジスタ17の導通状態を制御してグランド側端子の電位を制御するので、グランド側端子の電位を、参照電圧Vrefに応じて設定することができる。

【0027】

(第2実施例)

図6乃至図9は本発明の第2実施例を示すものであり、第1実施例と同一部分には同一符号を付して説明を省略し、以下異なる部分について説明する。図6に示すように、第2実施例の半導体素子制御装置21は、クランプ回路3,電圧モニタ回路9が、クランプ回路(電圧付与回路,電圧バッファ回路)22,電圧モニタ回路(電圧発生回路,補助電圧付与回路)23にそれぞれ置き換わっており、クランプ回路22に対して並列にNチャネルMOSFET(半導体素子,補助電圧付与回路)24が接続されている。また、電圧モニタ回路9は、電圧モニタ回路23に置き換わっており、FET24のON,OFFは、電圧モニタ回路23により制御される。その他の構成ついては第1実施例と同様である。

【0028】

図7(a),(b)は電圧モニタ回路23(a,b)の具体構成を示すが、参照電圧Vrefを生成出力する部分は電圧モニタ回路9と同様に構成されており、FET24(M2)を制御する構成部分が追加されている。図7(a)では、電源Vccとグランドとの間に抵抗素子25,26の直列回路が接続されており、両者の共通接続点はコンパレータ27の反転入力端子に接続されている。コンパレータ27の非反転入力端子には、比較用の基準電圧Vref1が与えられており、コンパレータ27の出力信号によりFET24を制御する。また、図7(b)は、抵抗素子25に替えてツェナーダイオード28を配置している。

【0029】

図8(a),(b)は、クランプ回路22(a,b)の具体構成例を示す。図8(a)は、NチャネルMOSFET29(第1半導体素子)に並列に、PチャネルMOSFET30(第2半導体素子)及び抵抗素子31の並列回路を接続したもので、両者の共通接続点がFET29のゲートに接続されている。そして、FET30のゲートに参照電圧Vrefが与えられる。FET1がプリドライバ回路2によってOFFされた場合、そのゲート電圧は、ほぼ電源電圧Vccとなる。その状態からプリドライバ回路2がFET1をONさせる場合、プリドライバ回路2のグランド側電圧は、FET1のゲート容量によりある程度高電圧を維持する。

【0030】

したがって、クランプ回路22(a)に与えられる参照電圧Vrefが≒0の場合、FET30はONしてFET29もONするが、この時の仮想グランド電圧Vcpは、FET22が存在しないと仮定すれば、ほぼFET30の閾値電圧VTとなる。そして、参照電圧Vrefが(Vcc−Vgs)で与えられる場合も、仮想グランド電圧Vcpは、(Vcc−Vgs+VT)となる。

【0031】

また、図8(b)は、(a)のFET29,30に替えて、NPNトランジスタ32(第1半導体素子),PNPトランジスタ33(第2半導体素子)を接続したものである。この場合、仮想グランド電圧Vcpは、上記の閾値電圧VTをベース−エミッタ間電圧VFに置き換えたものとなる。そして、FET24は、何れの場合も電源電圧Vccが閾値電圧Vth(=下限値)以下でONするように制御される。

【0032】

次に、第2実施例の作用について図9も参照して説明する。例えば、FET1をキャリア周波数が数100kHzのオーダーでPWM制御することを想定すると、第1実施例のようにオペアンプ16を用いて構成されるクランプ回路3では、高速動作に制約があり追従が困難となる場合がある。

そこで、第2実施例では、クランプ回路22にオペアンプを使用せず、FET29,30又はバイポーラトランジスタ32,33を用いて構成し、高速動作に十分に対応することを可能としている。しかしながら、その一方で、プリドライブ回路2に与える仮想グランド電圧Vcpの最低レベルは上述のように電圧VT又はVFとなるため、Vcc≦Vthの電圧範囲でクランプ制御を無効化する場合に、FET1の駆動電圧範囲が狭まることになる。

【0033】

上記の問題を改善するため、クランプ回路22に対して並列にFET24を接続し、Vcc≦Vthの電圧範囲でONさせて、仮想グランド電圧Vcpの最低レベルが第1実施例と同様にグランドレベル付近となるようにしている。その結果、電源電圧Vccと仮想グランド電圧Vcpとの関係は図9に示すようになり、Vcc>Vthの電圧範囲では、FET1をONさせた場合のゲート−ソース間電圧は[Vgs−VT(又はVF)]となる。

【0034】

以上のように第2実施例によれば、クランプ回路22をより高速動作が可能にとなるように構成すると共に、電圧モニタ回路23が、電源電圧Vccが閾値Vth以下となった場合にFET24をONさせるようにした。従って、クランプ回路22の構成が、十分な低電圧を付与するのが困難であっても、FET24の作用によって十分に低い電圧をプリドライブ回路2のグランド側端子に付与することができ、FET1の駆動電圧範囲が狭まることを回避できる。

また、クランプ回路22は、FET30(又はトランジスタ33)を参照電圧Vrefにより導通制御し、そのFET30の導通状態に応じてFET29(又はトランジスタ32)の導通を制御するので、Vcc>Vthの電圧範囲では、グランド側端子の電位を、参照電圧Vrefに、導通時に生じる定電圧VT(又はVF)を加えた電位に制御できる。

【0035】

(第3実施例)

図10は本発明の第3実施例であり、電圧モニタ回路の異なる構成例を示す。電圧モニタ回路(電圧付与回路,電圧発生回路,補助電圧付与回路)41は、第2実施例のようにコンパレータ27を使用せず、参照電圧Vrefを出力する回路部分とFET24のゲート駆動信号を出力する回路部分とが一体に構成されている。電源Vccとグランドとの間には、抵抗素子42,ツェナーダイオード43,定電流回路44の直列回路が接続されており、ツェナーダイオード43と定電流回路44との共通接続点は、NPNトランジスタ45のベースに接続されている。トランジスタ45のコレクタは電源Vccに接続され、エミッタは、定電流回路46を介してグランドに接続されていると共に参照電圧Vrefを出力するようになっている。

【0036】

また、電源Vccとグランドとの間には、PNPトランジスタ47,抵抗素子48及び49の直列回路が接続されており、トランジスタ47のベースは、抵抗素子42とツェナーダイオード43との共通接続点に接続されている。更に、電源Vccとグランドとの間には、定電流回路50及びNPNトランジスタ51の直列回路が接続されており、トランジスタ51のベースは抵抗素子48及び49の共通接続点に接続されている。そして、トランジスタ51のコレクタより、FET24のゲート駆動信号が出力される。

【0037】

次に、第3実施例の作用について説明する。Vcc≦Vthの場合、ツェナーダイオード43がONしないため、トランジスタ45,47,51は何れもOFFとなる。したがって、参照電圧Vrefは≒0となり、FET24のゲート駆動信号はハイレベルとなり、FET24はONされる。一方、Vcc>Vthの場合、ツェナーダイオード43がONするので、トランジスタ45,47,51は何れもONとなる。したがって、参照電圧Vrefは[Vcc−Vgs(抵抗素子42の電圧降下分)]となり、FET24のゲート駆動信号はロウレベルとなってFET24はOFFされる。この場合、クランプ制御電圧Vgsは、抵抗素子42の電圧降下分と、ツェナーダイオード43のツェナー電圧Vzと、トランジスタ45のベース−エミッタ間電圧VFとの和になる。

以上のように構成される第3実施例による場合も、第1,第2実施例と同様の効果が得られる。

【0038】

(第4実施例)

図11及び図12は本発明の第4実施例を示すものであり、第3実施例と異なる部分について説明する。第4実施例の電圧モニタ回路(電圧付与回路,補助電圧付与回路,導通制御回路)52は、第3実施例の電圧モニタ回路41に対し、FET24のゲート駆動信号の出力についてヒステリシス特性を持たせるように構成したものである。

【0039】

抵抗素子48及び49の共通接続点とトランジスタ51のベースとの間には、抵抗素子53が挿入されており、また、前記共通接続点とグランドとの間には、抵抗素子54,NPNトランジスタ55の直列回路が接続されている。電源Vccとグランドとの間には、抵抗素子56,NPNトランジスタ57の直列回路が接続されている。そして、トランジスタ57のベースは、抵抗素子58を介して上記共通接続点に接続されている。

【0040】

次に、第4実施例の作用について図12も参照して説明する。第3実施例の電圧モニタ回路41では、トランジスタ51をONさせるために流す電流I1は、抵抗素子49の抵抗値をR1とすると、[I1=VF/R1]であった。一方、電圧モニタ回路52では、トランジスタ51をONさせるために流す電流I2は、トランジスタ57,55が同時にONするため、抵抗素子54の抵抗値をR2とすると、概略的に示せば[I2=VF/(R1//R2)]に増加する(例えば、数10mA程度)。したがって、その電流が増加する分だけ、トランジスタ51をONしてFET24をターンOFFさせる電圧が上昇するようになる。

その結果、図12に示すように、FET24をONさせる電圧範囲にヒステリシス特性が付与される。斯様な特性を付与することで、閾値Vth付近で電源電圧Vccが変化した場合に、その変動に応じてFET24のON/OFFが頻繁に切り替わることを防止できる。

【0041】

(第5実施例)

図13は本発明の第5実施例を示すものである。第5実施例は、第2実施例の半導体素子制御装置21に使用されるクランプ回路22を、クランプ回路(電圧付与回路,電圧バッファ回路)61に置き換えることを想定する。図13(a),(b)に示すように、クランプ回路61(a,b)は、オペアンプ62とPチャネルMOSFET(半導体素子)63,又はPNPトランジスタ(半導体素子)64との組合せで構成される。

【0042】

第2実施例の半導体素子制御装置21にクランプ回路61を組み合わせると、オペアンプ62が含まれるため、高速動作に対する適応性は若干低下する。しかし、クランプ回路22を使用する場合のように、参照電圧Vrefに対して仮想クランプ電圧Vcpが[+VT(又はVF)]となることがない。したがって、図9では、仮想クランプ電圧Vcpは破線で示す参照電圧Vrefに一致するため、FET1の駆動電圧範囲を拡げることができる。

【0043】

本発明は上記し且つ図面に記載した実施例にのみ限定されるものではなく、以下のような変形または拡張が可能である。

保護用のツェナーダイオード7や、FET5のクランプ用ダイオード8は、必要に応じて設ければ良い。

電源電圧Vccや、制御対象とする半導体素子の耐圧、閾値電圧Vthなどは、個別の設計に応じて適宜変更すれば良い。

閾値電圧Vthとクランプ制御電圧とが同じ電圧に設定される場合は、図3(b)の低電流回路13を抵抗素子に置き換えても良い。

第2実施例において、FET24をターンONさせる下限値は、閾値電圧Vthよりも低くなるように設定しても良い。

【図面の簡単な説明】

【0044】

【図1】本発明の第1実施例であり、半導体素子制御装置の全体構成を概略的に示す図

【図2】プリドライブ回路の具体構成例を示す図

【図3】電圧モニタ回路の具体構成例を示す図

【図4】クランプ回路の具体構成例を示す図

【図5】電源電圧Vccの変化に伴う仮想グランド電圧Vcpの変化を示す図

【図6】本発明の第2実施例を示す図1相当図

【図7】図3相当図

【図8】図4相当図

【図9】図5相当図

【図10】本発明の第3実施例を示す図3相当図

【図11】本発明の第4実施例を示す図10相当図

【図12】図9相当図

【図13】本発明の第5実施例を示す図8相当図

【図14】従来技術を示す図1相当図

【符号の説明】

【0045】

図面中、1はPチャネルMOSFET(半導体素子)、2はプリドライブ回路(駆動回路)、3は電圧可変型クランプ回路(電圧バッファ回路)、9は電圧モニタ回路(電圧発生回路)、12は抵抗素子、13は定電流回路、14はツェナーダイオード、15はNチャネルMOSFET(半導体素子)、16オペアンプ、17はNPNトランジスタ(半導体素子)、18は電圧付与回路、19,21は半導体素子制御装置、22は電圧可変型クランプ回路(電圧付与回路,電圧バッファ回路)、23は電圧モニタ回路(補助電圧付与回路)、24はNチャネルMOSFET(半導体素子,補助電圧付与回路)、29はNチャネルMOSFET(第1半導体素子)、30はPチャネルMOSFET(第2半導体素子)、31は抵抗素子、32はNPNトランジスタ(第1半導体素子)、33はPNPトランジスタ(第2半導体素子)、41は電圧モニタ回路(電圧付与回路,補助電圧付与回路)、52は電圧モニタ回路(電圧付与回路,補助電圧付与回路)、61は電圧可変型クランプ回路(電圧付与回路,電圧バッファ回路)、62はオペアンプ、63はPチャネルMOSFET(半導体素子)、64はPNPトランジスタ(半導体素子)を示す。

【技術分野】

【0001】

本発明は、直流電源と負荷との間に接続される電圧駆動型の半導体素子を制御する半導体素子制御装置に関する。

【背景技術】

【0002】

例えば降圧型のDC/DCコンバータのような電源回路において、電源とグランドとの間にパワーMOSFETのような半導体スイッチング素子を接続し、そのFETを高速でスイッチング制御する場合には、ゲート電圧がゲート−ソース間電圧の耐圧を超えないようにクランプ制御することが行われている。そのような従来技術の一例として、特許文献1に開示されているものがある(図14参照)。

【特許文献1】特開平11−205123号公報(図2)

【発明の開示】

【発明が解決しようとする課題】

【0003】

この回路では、制御対象とするPチャネルMOSFET:M5をオンさせる場合のゲート電圧は、電源電圧に対して常にFET:M8,M6の閾値電圧VT分(2VT)だけ低い電圧となるように制御される。その結果、電源電圧Vddが低下した場合であっても、ゲート電圧は上記の制約を受けるため、FET:M5を十分にオンさせることができないという問題があった。

本発明は上記事情に鑑みてなされたものであり、その目的は、電源電圧が低下した場合でも、制御対象とする半導体素子を適切に制御することができる半導体素子制御装置を提供することにある。

【課題を解決するための手段】

【0004】

請求項1記載の半導体素子制御装置によれば、電圧付与回路は、電源電圧が閾値以下である場合は駆動回路のグランド側端子にグランドレベル近傍の電圧を付与し、電源電圧が閾値を超えている場合は、前記グランド側端子に電源電圧とクランプ制御用電圧との差電圧を付与する。即ち、電源電圧が閾値を超えていれば、制御対象とする半導体素子の電源側端子と導通制御端子との電圧差はクランプ制御用電圧となり、電源電圧が閾値以下であれば、上記電圧差は電源電圧に近い値となる。従って、電源電圧が低下した結果クランプ制御が不要な状態となった場合に、制御対象の半導体素子を十分にオンさせることができる。

【0005】

請求項2記載の半導体素子制御装置によれば、電圧発生回路は、電源電圧と閾値との関係に応じて、グランドレベル近傍の電圧と前記差電圧とを切り換えて出力し、電圧バッファ回路は、電圧発生回路の出力電圧に応じた電圧を、駆動回路のグランド側端子に付与する。したがって、電圧発生回路の出力電圧により、グランド側端子に付与する電圧を切り換えることができる。

【0006】

請求項3記載の半導体素子制御装置によれば、電源電圧が定電流回路の動作開始電圧に達しなければ、抵抗素子との共通接続点の電位はグランドレベル付近の電圧となり、電源電圧が前記動作開始電圧に達すると、共通接続点の電位は、電源電圧より抵抗素子における電圧降下分を減じた値となる。したがって、定電流回路の動作開始電圧に応じて閾値を設定できると共に、抵抗素子の抵抗値と定電流回路の電流値とでクランプ制御電圧を設定することができる。

【0007】

請求項4記載の半導体素子制御装置によれば、電源電圧が定電流回路の動作開始電圧に達すると、ツェナーダイオードとの共通接続点の電位は、電源電圧よりツェナー電圧を減じた値となる。したがって、ツェナー電圧によりクランプ制御電圧を設定することができる。

【0008】

請求項5記載の半導体素子制御装置によれば、電圧バッファ回路を構成するオペアンプが、電圧発生回路の出力電圧に応じて駆動回路のグランド側端子とグランドとの間に接続される半導体素子の導通状態を制御して前記グランド側端子の電位を制御するので、グランド側端子の電位を、電圧発生回路の出力電圧に応じて設定することができる。

【0009】

請求項6記載の半導体素子制御装置によれば、電圧バッファ回路を構成する第2半導体素子は電圧発生回路の出力電圧により導通制御され、その第2半導体素子の導通状態に応じて第1半導体素子の導通が制御される。したがって、グランド側端子の電位を、前記出力電圧に、第2半導体素子が導通することで付与される定電圧を加えた電位に制御することができる。

【0010】

請求項7記載の半導体素子制御装置によれば、導通制御回路は、電源電圧が前記閾値以下のレベルに設定される下限値を下回った場合に、駆動回路のグランド側端子とグランドとの間に接続される半導体素子を導通させる。従って、電圧付与回路が、十分な低電圧を付与することができない構成である場合でも、補助電圧付与回路の作用により十分に低い電圧を駆動回路のグランド側端子に付与できる。

【0011】

請求項8記載の半導体素子制御装置によれば、導通制御回路は、補助電圧付与回路を構成する半導体素子の導通制御にヒステリシス特性を持たせるので、電源電圧が下限値付近で変動する場合に、前記半導体素子が頻繁に断続されることを回避できる。

【発明を実施するための最良の形態】

【0012】

(第1実施例)

以下、本発明の第1実施例について図1乃至図5を参照して説明する。図1は、半導体素子制御装置の全体構成を概略的に示すものである。電源Vccとグランドとの間には、PチャネルMOSFET(半導体素子,トランジスタ)1と、図示しない負荷との直列回路が接続される。この場合、負荷とは、DCモータやランプ,その他インダクタなどである。FET1のゲート(導通制御端子)には、プリドライブ回路(駆動回路)2によりゲート電圧が与えられて、FET1のON,OFF、すなわち負荷に対する通電が制御される。

【0013】

プリドライブ回路2の電源側端子は電源Vccに接続されており、グランド側端子は、電圧可変型クランプ回路3(以下、単にクランプ回路と称す)を介してグランドに接続されている。このクランプ回路(電圧バッファ回路)3は、プリドライブ回路2のグランド側端子に、仮想グランド電圧Vcpを付与するものである。また、電源Vccとグランドとの間には、抵抗素子4,NチャネルMOSFET5,抵抗素子6の直列回路が接続されており、FET5のドレインは、プリドライブ回路2の入力端子に接続されている。

【0014】

電源Vccとプリドライブ回路2のグランド側端子との間には、過電圧保護用のツェナーダイオード7が接続されており、そのツェナーダイオード7のアノードとFET5のドレインとの間には、クランプ用のダイオード8が接続されている。FET5のゲートには外部より制御信号Vinが与えられるようになっており、制御信号Vinがハイレベルになると、FET5がONしてプリドライブ回路2の入力端子がロウレベルとなり、FET1がONされる。

【0015】

また、電源Vccとグランドとの間には電圧モニタ回路(電圧発生回路)9が接続されている。この電圧モニタ回路9は、電源Vccの電圧レベルに応じて、クランプ回路3に出力する参照電圧Vrefを変化させるようになっており、クランプ回路3は、その参照電圧Vrefに応じてプリドライブ回路2のグランド側端子に与える仮想グランド電圧Vcpを変化させる。

【0016】

図2は、プリドライブ回路2の具体構成例を示すものである。プリドライブ回路2は、P,NチャネルMOSFET10P,10NよりなるCMOSインバータと、P,NチャネルMOSFET11P,11NよりなるCMOSインバータとを直列接続して構成されている。FET10P及び11Pのソースは電源Vccに接続され、FET10N及び11Nのソースには、クランプ回路3により仮想グランド電圧Vcpが与えられる。そして、FET10P,10NのゲートはFET5のドレインに接続され、FET11P,11NのドレインはFET1のゲートに接続される。

【0017】

図3(a),(b)は、電圧モニタ回路9(a,b)の具体構成例を示す。図3(a)は、電源Vccとグランドとの間に、抵抗素子12と定電流回路13との直列回路を接続したものであり、両者の共通接続点がクランプ回路3に与える参照電圧Vrefとなる。また、図3(b)は、(a)の抵抗素子12をツェナーダイオード14に置き換えたものである。これらの電圧モニタ回路9は、例えば電源Vccの最大電圧が16V程度である場合に閾値電圧Vthを8Vに設定し、

Vcc>Vth → Vref=Vcc−Vgs …(1)

Vcc≦Vth → Vref≒0 …(2)

となるように、参照電圧Vrefを変化させる。ここで、電圧Vgsは、プリドライブ回路2がFET1をONさせる場合に、FET1のゲート−ソース間電圧として付与する電圧であり、FET1のゲート−ソース間耐圧Vgs(max)(例えば10V)を超えないようにゲート電圧をクランプする電圧(クランプ制御用電圧)で、例えば8Vに設定されている。

【0018】

すなわち、図3の構成では、Vcc≦Vthの場合、定電流回路13は電流を流さないように構成されており、その結果、参照電圧Vref≒0となる。そして、Vcc>Vthの場合、(a)では、定電流回路13が流す定電流により抵抗素子12に発生する電圧降下が電圧Vgsに相当するように定められ、(b)では、ツェナーダイオード14のツェナー電圧Vz=Vgsに定められる。

【0019】

図4(a),(b)は、クランプ回路3(a,b)の具体構成例を示す。図4(a)は、NチャネルMOSFET15のドレイン,ゲートに、オペアンプ16の非反転入力端子と、出力端子とをそれぞれ接続して構成したもので、オペアンプ16の反転入力端子には、電圧モニタ回路9より参照電圧Vrefが与えられる。また、図4(b)は、(a)のFET15に替えて、NPNトランジスタ17を接続したものである。

尚、以上の構成において、クランプ回路3と電圧モニタ回路9とは、電圧付与回路18を構成している。また、以上の構成よりFET1を除いたものが、半導体素子制御装置19を構成している。

【0020】

次に、本実施例の作用について図5も参照して説明する。図5は、電源電圧Vccが16V〜0Vの範囲で変化する場合に、クランプ回路3によって付与される仮想グランド電圧Vcpの変化を示すものである。電源電圧Vccが、電圧モニタ回路9に設定されている閾値電圧Vthを上回る場合、クランプ回路3に付与される参照電圧Vrefは、上記(1)式で示したようにVref=Vcc−Vgs となり、その参照電圧Vrefは、クランプ回路3のオペアンプ16の作用により仮想グランド電圧Vcpとして出力される。

【0021】

その結果、制御信号Vinがハイレベルとなり、プリドライブ回路2の入力端子がロウレベルになると、内部の出力側FET11P,11NがそれぞれOFF,ONとなるので、FET1(M1)のゲート電圧は、ほぼ仮想グランド電圧Vcpに等しくなる。この時、FET1のゲート−ソース(電源側端子)間電圧は、Vcc−(Vcc−Vgs)=Vgsとなり、FET1は、電圧差8Vでクランプされた状態でONとなる。

上記の状態は、Vcc>Vthが成立する間にFET1がONとなる場合は常に維持されるので、FET1のソース−ゲート間電圧は常にVcp=8Vとなり、電圧クランプ機能が有効となる。

【0022】

そして、電源電圧Vccが閾値電圧Vth以下になると、参照電圧Vrefは、上記(2)式で示したようにVref≒0となるので、仮想グランド電圧Vcpも、Vcp≒0として出力される。この時、FET1がONする場合のソース−ゲート間電圧は、ほぼ電源電圧Vccとなる。

【0023】

以上の結果、電源電圧Vccと仮想グランド電圧Vcpとの関係は、図5に示すようになる。尚、図5において、電源電圧Vccが0V〜1.5V付近の間に仮想グランド電圧Vcpが上昇するように示されているのは、この区間ではオペアンプ16が、図4(a)の場合、FET15をONさせるのに必要な電圧VTを出力できず、仮想グランド電圧Vcpがハイインピーダンス状態になることを示している。したがって、図4(b)の場合、上記ハイインピーダンス状態になる電圧範囲は0V〜0.6V付近となる。

【0024】

以上のように本実施例によれば、電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用の電圧Vgsとの差電圧を付与するようにした。従って、電源電圧Vccが低下することでアクティブなクランプ制御が不要となった状況下でFET1をONさせる場合は、クランプ制御を無効化してゲート−ソース間電圧を電源電圧Vccにほぼ等しくすることができ、FET1を十分にONさせることができる。

【0025】

また、電圧付与回路18を電圧モニタ回路9とクランプ回路3とで構成し、電圧モニタ回路9が出力する電圧に応じて、プリドライブ回路2のグランド側端子に与える仮想グランド電圧Vcpを切り換えるようにした。そして、電圧モニタ回路9aとして、抵抗素子12と定電流回路13との直列回路で構成すれば、定電流回路13の動作開始電圧に応じて閾値電圧Vthを設定すると共に、抵抗素子12の抵抗値と定電流回路13の電流値とでクランプ制御電圧Vgsを設定することができる。また、電圧モニタ回路9bとして、ツェナーダイオード14と定電流回路13との直列回路で構成すれば、ツェナー電圧Vzでクランプ制御電圧Vgsを設定することができる。

【0026】

そして、クランプ制御回路3は、オペアンプ16が、参照電圧Vrefに応じてプリドライブ回路2のグランド側端子とグランドとの間に接続されるFET15又はトランジスタ17の導通状態を制御してグランド側端子の電位を制御するので、グランド側端子の電位を、参照電圧Vrefに応じて設定することができる。

【0027】

(第2実施例)

図6乃至図9は本発明の第2実施例を示すものであり、第1実施例と同一部分には同一符号を付して説明を省略し、以下異なる部分について説明する。図6に示すように、第2実施例の半導体素子制御装置21は、クランプ回路3,電圧モニタ回路9が、クランプ回路(電圧付与回路,電圧バッファ回路)22,電圧モニタ回路(電圧発生回路,補助電圧付与回路)23にそれぞれ置き換わっており、クランプ回路22に対して並列にNチャネルMOSFET(半導体素子,補助電圧付与回路)24が接続されている。また、電圧モニタ回路9は、電圧モニタ回路23に置き換わっており、FET24のON,OFFは、電圧モニタ回路23により制御される。その他の構成ついては第1実施例と同様である。

【0028】

図7(a),(b)は電圧モニタ回路23(a,b)の具体構成を示すが、参照電圧Vrefを生成出力する部分は電圧モニタ回路9と同様に構成されており、FET24(M2)を制御する構成部分が追加されている。図7(a)では、電源Vccとグランドとの間に抵抗素子25,26の直列回路が接続されており、両者の共通接続点はコンパレータ27の反転入力端子に接続されている。コンパレータ27の非反転入力端子には、比較用の基準電圧Vref1が与えられており、コンパレータ27の出力信号によりFET24を制御する。また、図7(b)は、抵抗素子25に替えてツェナーダイオード28を配置している。

【0029】

図8(a),(b)は、クランプ回路22(a,b)の具体構成例を示す。図8(a)は、NチャネルMOSFET29(第1半導体素子)に並列に、PチャネルMOSFET30(第2半導体素子)及び抵抗素子31の並列回路を接続したもので、両者の共通接続点がFET29のゲートに接続されている。そして、FET30のゲートに参照電圧Vrefが与えられる。FET1がプリドライバ回路2によってOFFされた場合、そのゲート電圧は、ほぼ電源電圧Vccとなる。その状態からプリドライバ回路2がFET1をONさせる場合、プリドライバ回路2のグランド側電圧は、FET1のゲート容量によりある程度高電圧を維持する。

【0030】

したがって、クランプ回路22(a)に与えられる参照電圧Vrefが≒0の場合、FET30はONしてFET29もONするが、この時の仮想グランド電圧Vcpは、FET22が存在しないと仮定すれば、ほぼFET30の閾値電圧VTとなる。そして、参照電圧Vrefが(Vcc−Vgs)で与えられる場合も、仮想グランド電圧Vcpは、(Vcc−Vgs+VT)となる。

【0031】

また、図8(b)は、(a)のFET29,30に替えて、NPNトランジスタ32(第1半導体素子),PNPトランジスタ33(第2半導体素子)を接続したものである。この場合、仮想グランド電圧Vcpは、上記の閾値電圧VTをベース−エミッタ間電圧VFに置き換えたものとなる。そして、FET24は、何れの場合も電源電圧Vccが閾値電圧Vth(=下限値)以下でONするように制御される。

【0032】

次に、第2実施例の作用について図9も参照して説明する。例えば、FET1をキャリア周波数が数100kHzのオーダーでPWM制御することを想定すると、第1実施例のようにオペアンプ16を用いて構成されるクランプ回路3では、高速動作に制約があり追従が困難となる場合がある。

そこで、第2実施例では、クランプ回路22にオペアンプを使用せず、FET29,30又はバイポーラトランジスタ32,33を用いて構成し、高速動作に十分に対応することを可能としている。しかしながら、その一方で、プリドライブ回路2に与える仮想グランド電圧Vcpの最低レベルは上述のように電圧VT又はVFとなるため、Vcc≦Vthの電圧範囲でクランプ制御を無効化する場合に、FET1の駆動電圧範囲が狭まることになる。

【0033】

上記の問題を改善するため、クランプ回路22に対して並列にFET24を接続し、Vcc≦Vthの電圧範囲でONさせて、仮想グランド電圧Vcpの最低レベルが第1実施例と同様にグランドレベル付近となるようにしている。その結果、電源電圧Vccと仮想グランド電圧Vcpとの関係は図9に示すようになり、Vcc>Vthの電圧範囲では、FET1をONさせた場合のゲート−ソース間電圧は[Vgs−VT(又はVF)]となる。

【0034】

以上のように第2実施例によれば、クランプ回路22をより高速動作が可能にとなるように構成すると共に、電圧モニタ回路23が、電源電圧Vccが閾値Vth以下となった場合にFET24をONさせるようにした。従って、クランプ回路22の構成が、十分な低電圧を付与するのが困難であっても、FET24の作用によって十分に低い電圧をプリドライブ回路2のグランド側端子に付与することができ、FET1の駆動電圧範囲が狭まることを回避できる。

また、クランプ回路22は、FET30(又はトランジスタ33)を参照電圧Vrefにより導通制御し、そのFET30の導通状態に応じてFET29(又はトランジスタ32)の導通を制御するので、Vcc>Vthの電圧範囲では、グランド側端子の電位を、参照電圧Vrefに、導通時に生じる定電圧VT(又はVF)を加えた電位に制御できる。

【0035】

(第3実施例)

図10は本発明の第3実施例であり、電圧モニタ回路の異なる構成例を示す。電圧モニタ回路(電圧付与回路,電圧発生回路,補助電圧付与回路)41は、第2実施例のようにコンパレータ27を使用せず、参照電圧Vrefを出力する回路部分とFET24のゲート駆動信号を出力する回路部分とが一体に構成されている。電源Vccとグランドとの間には、抵抗素子42,ツェナーダイオード43,定電流回路44の直列回路が接続されており、ツェナーダイオード43と定電流回路44との共通接続点は、NPNトランジスタ45のベースに接続されている。トランジスタ45のコレクタは電源Vccに接続され、エミッタは、定電流回路46を介してグランドに接続されていると共に参照電圧Vrefを出力するようになっている。

【0036】

また、電源Vccとグランドとの間には、PNPトランジスタ47,抵抗素子48及び49の直列回路が接続されており、トランジスタ47のベースは、抵抗素子42とツェナーダイオード43との共通接続点に接続されている。更に、電源Vccとグランドとの間には、定電流回路50及びNPNトランジスタ51の直列回路が接続されており、トランジスタ51のベースは抵抗素子48及び49の共通接続点に接続されている。そして、トランジスタ51のコレクタより、FET24のゲート駆動信号が出力される。

【0037】

次に、第3実施例の作用について説明する。Vcc≦Vthの場合、ツェナーダイオード43がONしないため、トランジスタ45,47,51は何れもOFFとなる。したがって、参照電圧Vrefは≒0となり、FET24のゲート駆動信号はハイレベルとなり、FET24はONされる。一方、Vcc>Vthの場合、ツェナーダイオード43がONするので、トランジスタ45,47,51は何れもONとなる。したがって、参照電圧Vrefは[Vcc−Vgs(抵抗素子42の電圧降下分)]となり、FET24のゲート駆動信号はロウレベルとなってFET24はOFFされる。この場合、クランプ制御電圧Vgsは、抵抗素子42の電圧降下分と、ツェナーダイオード43のツェナー電圧Vzと、トランジスタ45のベース−エミッタ間電圧VFとの和になる。

以上のように構成される第3実施例による場合も、第1,第2実施例と同様の効果が得られる。

【0038】

(第4実施例)

図11及び図12は本発明の第4実施例を示すものであり、第3実施例と異なる部分について説明する。第4実施例の電圧モニタ回路(電圧付与回路,補助電圧付与回路,導通制御回路)52は、第3実施例の電圧モニタ回路41に対し、FET24のゲート駆動信号の出力についてヒステリシス特性を持たせるように構成したものである。

【0039】

抵抗素子48及び49の共通接続点とトランジスタ51のベースとの間には、抵抗素子53が挿入されており、また、前記共通接続点とグランドとの間には、抵抗素子54,NPNトランジスタ55の直列回路が接続されている。電源Vccとグランドとの間には、抵抗素子56,NPNトランジスタ57の直列回路が接続されている。そして、トランジスタ57のベースは、抵抗素子58を介して上記共通接続点に接続されている。

【0040】

次に、第4実施例の作用について図12も参照して説明する。第3実施例の電圧モニタ回路41では、トランジスタ51をONさせるために流す電流I1は、抵抗素子49の抵抗値をR1とすると、[I1=VF/R1]であった。一方、電圧モニタ回路52では、トランジスタ51をONさせるために流す電流I2は、トランジスタ57,55が同時にONするため、抵抗素子54の抵抗値をR2とすると、概略的に示せば[I2=VF/(R1//R2)]に増加する(例えば、数10mA程度)。したがって、その電流が増加する分だけ、トランジスタ51をONしてFET24をターンOFFさせる電圧が上昇するようになる。

その結果、図12に示すように、FET24をONさせる電圧範囲にヒステリシス特性が付与される。斯様な特性を付与することで、閾値Vth付近で電源電圧Vccが変化した場合に、その変動に応じてFET24のON/OFFが頻繁に切り替わることを防止できる。

【0041】

(第5実施例)

図13は本発明の第5実施例を示すものである。第5実施例は、第2実施例の半導体素子制御装置21に使用されるクランプ回路22を、クランプ回路(電圧付与回路,電圧バッファ回路)61に置き換えることを想定する。図13(a),(b)に示すように、クランプ回路61(a,b)は、オペアンプ62とPチャネルMOSFET(半導体素子)63,又はPNPトランジスタ(半導体素子)64との組合せで構成される。

【0042】

第2実施例の半導体素子制御装置21にクランプ回路61を組み合わせると、オペアンプ62が含まれるため、高速動作に対する適応性は若干低下する。しかし、クランプ回路22を使用する場合のように、参照電圧Vrefに対して仮想クランプ電圧Vcpが[+VT(又はVF)]となることがない。したがって、図9では、仮想クランプ電圧Vcpは破線で示す参照電圧Vrefに一致するため、FET1の駆動電圧範囲を拡げることができる。

【0043】

本発明は上記し且つ図面に記載した実施例にのみ限定されるものではなく、以下のような変形または拡張が可能である。

保護用のツェナーダイオード7や、FET5のクランプ用ダイオード8は、必要に応じて設ければ良い。

電源電圧Vccや、制御対象とする半導体素子の耐圧、閾値電圧Vthなどは、個別の設計に応じて適宜変更すれば良い。

閾値電圧Vthとクランプ制御電圧とが同じ電圧に設定される場合は、図3(b)の低電流回路13を抵抗素子に置き換えても良い。

第2実施例において、FET24をターンONさせる下限値は、閾値電圧Vthよりも低くなるように設定しても良い。

【図面の簡単な説明】

【0044】

【図1】本発明の第1実施例であり、半導体素子制御装置の全体構成を概略的に示す図

【図2】プリドライブ回路の具体構成例を示す図

【図3】電圧モニタ回路の具体構成例を示す図

【図4】クランプ回路の具体構成例を示す図

【図5】電源電圧Vccの変化に伴う仮想グランド電圧Vcpの変化を示す図

【図6】本発明の第2実施例を示す図1相当図

【図7】図3相当図

【図8】図4相当図

【図9】図5相当図

【図10】本発明の第3実施例を示す図3相当図

【図11】本発明の第4実施例を示す図10相当図

【図12】図9相当図

【図13】本発明の第5実施例を示す図8相当図

【図14】従来技術を示す図1相当図

【符号の説明】

【0045】

図面中、1はPチャネルMOSFET(半導体素子)、2はプリドライブ回路(駆動回路)、3は電圧可変型クランプ回路(電圧バッファ回路)、9は電圧モニタ回路(電圧発生回路)、12は抵抗素子、13は定電流回路、14はツェナーダイオード、15はNチャネルMOSFET(半導体素子)、16オペアンプ、17はNPNトランジスタ(半導体素子)、18は電圧付与回路、19,21は半導体素子制御装置、22は電圧可変型クランプ回路(電圧付与回路,電圧バッファ回路)、23は電圧モニタ回路(補助電圧付与回路)、24はNチャネルMOSFET(半導体素子,補助電圧付与回路)、29はNチャネルMOSFET(第1半導体素子)、30はPチャネルMOSFET(第2半導体素子)、31は抵抗素子、32はNPNトランジスタ(第1半導体素子)、33はPNPトランジスタ(第2半導体素子)、41は電圧モニタ回路(電圧付与回路,補助電圧付与回路)、52は電圧モニタ回路(電圧付与回路,補助電圧付与回路)、61は電圧可変型クランプ回路(電圧付与回路,電圧バッファ回路)、62はオペアンプ、63はPチャネルMOSFET(半導体素子)、64はPNPトランジスタ(半導体素子)を示す。

【特許請求の範囲】

【請求項1】

直流電源と負荷との間に接続される電圧駆動型の半導体素子を制御するもので、前記半導体素子を導通状態とする場合、必要に応じてクランプ制御を行う半導体素子制御装置において、

外部より与えられる制御信号に応じて、前記半導体素子の導通制御端子に駆動電圧を印加する駆動回路と、

前記電源の電圧を所定の閾値と比較して、前記電源電圧が前記閾値以下である場合は前記駆動回路のグランド側端子にグランドレベル近傍の電圧を付与し、前記電源電圧が前記閾値を超えている場合は、前記グランド側端子に前記電源電圧と前記クランプ制御用電圧との差電圧を付与する電圧付与回路とを備えることを特徴とする半導体素子制御装置。

【請求項2】

前記電圧付与回路は、

前記電源電圧と前記閾値との関係に応じて、前記グランドレベル近傍の電圧と前記差電圧とを切り換えて出力する電圧発生回路と、

この電圧発生回路の出力電圧に応じた電圧を、前記駆動回路のグランド側端子に付与する電圧バッファ回路とで構成されることを特徴とする請求項1記載の半導体素子制御装置。

【請求項3】

前記電圧発生回路は、前記電源とグランドとの間に接続される抵抗素子と定電流回路との直列回路で構成されることを特徴とする請求項2記載の半導体素子制御装置。

【請求項4】

前記電圧発生回路は、前記電源とグランドとの間に接続されるツェナーダイオードと定電流回路との直列回路で構成されることを特徴とする請求項2記載の半導体素子制御装置。

【請求項5】

前記電圧バッファ回路は、

前記駆動回路のグランド側端子とグランドとの間に接続される半導体素子と、

前記電圧発生回路の出力電圧に応じて前記半導体素子の導通状態を制御することで、前記グランド側端子の電位を制御するオペアンプとで構成されることを特徴とする請求項2乃至4の何れかに記載の半導体素子制御装置。

【請求項6】

前記電圧バッファ回路は、

前記駆動回路のグランド側端子とグランドとの間に接続される第1半導体素子と、

この第1半導体素子に並列に接続される、前記素子に対して相補型となる第2半導体素子と抵抗素子との直列回路で構成され、

前記直列回路の共通接続点は、前記第1半導体素子の導通制御端子に接続され、前記第2半導体素子の導通制御端子に前記電圧発生回路の出力電圧が与えられることを特徴とする請求項2乃至4の何れかに記載の半導体素子制御装置。

【請求項7】

前記駆動回路のグランド側端子とグランドとの間に接続される半導体素子と、

前記電源電圧が前記閾値以下のレベルに設定される下限値を下回った場合に前記半導体素子を導通させる導通制御回路とで構成される補助電圧付与回路を備えることを特徴とする請求項1乃至6の何れかに記載の半導体素子制御装置。

【請求項8】

前記導通制御回路は、前記半導体素子の導通制御にヒステリシス特性を持たせるように構成されることを特徴とする請求項7記載の半導体素子制御装置。

【請求項1】

直流電源と負荷との間に接続される電圧駆動型の半導体素子を制御するもので、前記半導体素子を導通状態とする場合、必要に応じてクランプ制御を行う半導体素子制御装置において、

外部より与えられる制御信号に応じて、前記半導体素子の導通制御端子に駆動電圧を印加する駆動回路と、

前記電源の電圧を所定の閾値と比較して、前記電源電圧が前記閾値以下である場合は前記駆動回路のグランド側端子にグランドレベル近傍の電圧を付与し、前記電源電圧が前記閾値を超えている場合は、前記グランド側端子に前記電源電圧と前記クランプ制御用電圧との差電圧を付与する電圧付与回路とを備えることを特徴とする半導体素子制御装置。

【請求項2】

前記電圧付与回路は、

前記電源電圧と前記閾値との関係に応じて、前記グランドレベル近傍の電圧と前記差電圧とを切り換えて出力する電圧発生回路と、

この電圧発生回路の出力電圧に応じた電圧を、前記駆動回路のグランド側端子に付与する電圧バッファ回路とで構成されることを特徴とする請求項1記載の半導体素子制御装置。

【請求項3】

前記電圧発生回路は、前記電源とグランドとの間に接続される抵抗素子と定電流回路との直列回路で構成されることを特徴とする請求項2記載の半導体素子制御装置。

【請求項4】

前記電圧発生回路は、前記電源とグランドとの間に接続されるツェナーダイオードと定電流回路との直列回路で構成されることを特徴とする請求項2記載の半導体素子制御装置。

【請求項5】

前記電圧バッファ回路は、

前記駆動回路のグランド側端子とグランドとの間に接続される半導体素子と、

前記電圧発生回路の出力電圧に応じて前記半導体素子の導通状態を制御することで、前記グランド側端子の電位を制御するオペアンプとで構成されることを特徴とする請求項2乃至4の何れかに記載の半導体素子制御装置。

【請求項6】

前記電圧バッファ回路は、

前記駆動回路のグランド側端子とグランドとの間に接続される第1半導体素子と、

この第1半導体素子に並列に接続される、前記素子に対して相補型となる第2半導体素子と抵抗素子との直列回路で構成され、

前記直列回路の共通接続点は、前記第1半導体素子の導通制御端子に接続され、前記第2半導体素子の導通制御端子に前記電圧発生回路の出力電圧が与えられることを特徴とする請求項2乃至4の何れかに記載の半導体素子制御装置。

【請求項7】

前記駆動回路のグランド側端子とグランドとの間に接続される半導体素子と、

前記電源電圧が前記閾値以下のレベルに設定される下限値を下回った場合に前記半導体素子を導通させる導通制御回路とで構成される補助電圧付与回路を備えることを特徴とする請求項1乃至6の何れかに記載の半導体素子制御装置。

【請求項8】

前記導通制御回路は、前記半導体素子の導通制御にヒステリシス特性を持たせるように構成されることを特徴とする請求項7記載の半導体素子制御装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2009−44304(P2009−44304A)

【公開日】平成21年2月26日(2009.2.26)

【国際特許分類】

【出願番号】特願2007−205327(P2007−205327)

【出願日】平成19年8月7日(2007.8.7)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成21年2月26日(2009.2.26)

【国際特許分類】

【出願日】平成19年8月7日(2007.8.7)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]