半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子及びその形成方法に関する。より詳しくは、埋込型ゲートと格納電極コンタクトを含む半導体素子及びその形成方法に関する。

【背景技術】

【0002】

最近、半導体メモリ素子、特にDRAM(Dynamic Random Access Memory)素子の大容量化に対する要求が漸次大きくなるにも拘わらず、チップの大きさの増加の限界によりDRAM素子の容量増加もまた限界を見せる実情である。チップの大きさが増加することになれば、ウエハ当りチップの数が減少し、素子の生産性が減少することになる。したがって、最近はセルレイアウトを変化させてセルの面積を減少させ、それに伴いより多いメモリセルを1つのウエハに集積させようとする努力を傾けている。このような努力により、最近は既存の8F2レイアウトから6F2レイアウトに変化している。

【0003】

一方、半導体記憶装置の全体面積を縮小させると、1つのウエハ当り生産可能な半導体記憶装置の数を増加させることができ生産性が向上する。半導体記憶装置の全体面積を縮小させるため、多様な方法が提案されている。このうち1つが水平チャンネル領域を有していた従来のプラナーゲート(Planar Gate)に代えて、基板にリセスが形成されそのリセスにゲートを形成することにより、リセスの曲面に沿ってチャンネル領域が形成されるリセスゲート(Recess Gate)を用いることであり、このリセスゲートから進んでリセス内にゲート全体を埋め込んで形成する埋込型ゲート(Buried Gate)が研究されている。

【0004】

このような埋込型ゲートは、ゲート全体が半導体基板の表面以下に埋め込まれて形成されるので、チャンネル長と幅を確保することができることは勿論、リセスゲートに比べゲート(ワードラインとビットラインとの間に発生する寄生キャパシタンス(Parasitic Capacitance)を従来に比べ50%程度減少させることのできる効果を提供する。

【0005】

ところが、このように埋込型ゲートが適用された6F2レイアウトにおいても格納電極コンタクトと活性領域が接するコンタクト面積が減少し、コンタクト抵抗が増加するとの問題が発生している実情である。

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、前記のような従来の問題点を解決するためのものであり、素子分離構造の上部に分離パターンを形成し、この分離パターンの両端にコンタクトプラグを形成することにより、格納電極コンタクトと活性領域との間のフルオーバーラップを提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させる半導体素子及びその形成方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る半導体素子は、半導体基板に備えられるメインゲート及び素子分離構造と、前記素子分離構造の上部に備えられる分離パターンと、前記分離パターンの両端に備えられるコンタクトプラグとを含み、素子分離構造の上部に分離パターンを形成し、この分離パターンの両端にコンタクトプラグを形成することにより、格納電極コンタクトと活性領域との間のフルオーバーラップを提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させることを特徴とする。

【0008】

さらに、前記素子分離構造は、前記半導体基板で前記メインゲートに隣接して備えられる分離ゲート、又は前記半導体基板が食刻されたトレンチに埋め込まれた絶縁膜を含む素子分離膜のうち1つ以上を含むことができる。

【0009】

さらに、前記分離パターンは酸化膜と相違する食刻選択比を有する絶縁膜であって、窒化膜、シリコン酸化窒化膜、非晶質炭素を含むことを特徴とする。

【0010】

なお、前記メインゲート及び前記分離ゲートは、半導体基板に所定の深さに形成されたリセスと、前記リセスの下部に埋め込まれたゲート導電層と、前記リセスで前記ゲート導電層の上部に備えられるキャッピング膜とを含む埋込型ゲートであることが好ましい。

【0011】

併せて、前記分離パターンの下部は、前記リセスの上部に埋め込まれ、パターンの崩壊が防止されることを特徴とする。

【0012】

さらに、前記メインゲート及び前記分離ゲートは、2つのメインゲートと1つの分離ゲートとが交互に備えられることが好ましい。

【0013】

さらに、前記2つのメインゲートの間のビットラインコンタクト領域の上部に備えられるビットラインコンタクトと、前記ビットラインコンタクトの上部に備えられるビットラインとをさらに含むことができる。

【0014】

なお、前記コンタクトプラグは、格納電極コンタクトプラグを含むことが好ましい。

【0015】

一方、本発明に係る半導体素子は、半導体基板にラインタイプに形成された活性領域と、前記半導体基板に前記活性領域に対し斜めに延長されたメインゲート及び分離ゲートと、前記分離ゲートの上部に備えられるラインタイプの分離パターンと、前記分離パターンの両端に沿って延長されるコンタクトプラグとを含み、素子分離構造の上部に分離パターンを形成し、この分離パターンの両端にコンタクトプラグを形成することにより、格納電極コンタクトと活性領域との間のフルオーバーラップを提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させることを特徴とする。

【0016】

さらに、前記メインゲート及び前記分離ゲートは、2つのメインゲートと1つの分離ゲートとが交互に備えられることが好ましい。

なお、前記2つのメインゲートの間に備えられるビットラインコンタクトプラグをさらに含むことができる。

【0017】

併せて、前記ビットラインコンタクトプラグの上部に備えられ、前記メインゲートと交差しながら延長されたラインタイプのビットラインをさらに含むことを特徴とする。

【0018】

さらに、前記ビットラインは、前記メインゲートと垂直に交差することが好ましく、前記コンタクトプラグは、格納電極コンタクトプラグを含むことが好ましい。

【0019】

一方、本発明に係る半導体素子の形成方法は、半導体基板にメインゲート及び素子分離構造を形成するステップと、前記素子分離構造の上部に分離パターンを形成するステップと、前記分離パターンの両端にコンタクトプラグを形成するステップとを含み、素子分離構造の上部に分離パターンを形成し、この分離パターンの両端にコンタクトプラグを形成することにより、格納電極コンタクトと活性領域との間のフルオーバーラップを提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させることを特徴とする。

【0020】

さらに、前記素子分離構造を形成するステップは、前記半導体基板で前記メインゲートに隣接して備えられる分離ゲートを形成するステップ、又は前記半導体基板が食刻されたトレンチに埋め込まれた絶縁膜を含む素子分離膜を形成するステップのうち1つ以上を含むことができる。

【0021】

なお、前記分離パターンを形成するステップは、前記半導体基板の上部に層間絶縁膜を形成するステップと、前記分離ゲートを境界に前記層間絶縁膜を食刻するステップと、前記食刻された層間絶縁膜を含む半導体基板の全面に分離パターン層を蒸着するステップと、前記分離パターン層をエッチバックして前記層間絶縁膜の側壁に分離パターンを残留させるステップと、前記層間絶縁膜を除去するステップとを含むことが好ましい。

【0022】

さらに、前記メインゲート及び前記分離ゲートを形成するステップは、半導体基板に所定の深さにリセスを形成するステップと、前記リセスの下部にゲート導電層を埋め込むステップと、前記リセスで前記ゲート導電層の上部にキャッピング膜を埋め込むステップとを含むことを特徴とする。

【0023】

併せて、前記分離パターンの下部を前記リセスの上部に埋め込んで形成することが好ましい。

【0024】

さらに、前記キャッピング膜を所定の深さに食刻するステップと、前記食刻されたキャッピング膜を含む半導体基板の上部に分離パターン層を形成するステップとを含むことができる。

【0025】

なお、前記コンタクトプラグを形成するステップは、前記分離パターンを含む半導体基板に層間絶縁膜を形成するステップと、前記メインゲートを境界に前記層間絶縁膜を食刻してコンタクトホールを形成するステップと、前記コンタクトホールを含む半導体基板の全面に導電物質を蒸着するステップと、前記層間絶縁膜の上部の前記導電物質を平坦化食刻するステップとを含むことが好ましい。

【0026】

さらに、前記分離パターンは酸化膜と相違する食刻選択比を有する絶縁膜であって、窒化膜、シリコン酸化窒化膜、非晶質炭素を含むことができる。

【0027】

併せて、前記メインゲート及び前記分離ゲートを形成するステップは、2つのメインゲートと1つの分離ゲートとが交互に備えられるようにすることが好ましい。

【0028】

なお、前記2つのメインゲートの間のビットラインコンタクト領域の上部にビットラインコンタクトを形成するステップと、前記ビットラインコンタクトの上部にビットラインを形成するステップとをさらに含むことを特徴とする。

【0029】

さらに、前記コンタクトプラグは、格納電極コンタクトプラグを含むことができる。

【0030】

一方、本発明に係る半導体素子の形成方法は、半導体基板にラインタイプの活性領域を形成するステップと、前記半導体基板に前記活性領域に対し斜めに延長されたメインゲート及び分離ゲートをラインタイプに形成するステップと、前記分離ゲートの上部にラインタイプの分離パターンを形成するステップと、前記分離パターンの両端に沿って延長されるコンタクトプラグを形成するステップとを含むことを特徴とする。

【0031】

さらに、前記メインゲート及び前記分離ゲートを形成するステップは、2つのメインゲートと1つの分離ゲートとが交互に備えられるようにすることが好ましい。

【0032】

さらに、前記2つのメインゲートの間にコンタクトプラグを形成するステップをさらに含むことができる。

【0033】

さらに、前記ビットラインコンタクトプラグの上部に備えられ前記ビットラインコンタクトプラグと連結され、前記メインゲートと交差しながら延長されたビットラインをラインタイプに形成するステップをさらに含むことを特徴とする。

【0034】

併せて、前記ビットラインは、前記メインゲートと垂直に交差することが好ましい。

【0035】

さらに、前記コンタクトプラグは、格納電極コンタクトプラグを含むことができる。

【発明の効果】

【0036】

本発明に係る半導体素子及びその形成方法は、格納電極コンタクトと活性領域との間のフルオーバーラップ(full overlap)を提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させる効果を提供する。

【図面の簡単な説明】

【0037】

【図1】本発明の1つの実施形態に係る半導体素子を示す平面図である。

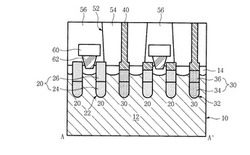

【図2】図1においてA-A'線に沿った断面図である。

【図3】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図4】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図5】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図6】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図7】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図8】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図9】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図10】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図11】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図12】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図13】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図14】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図15】本発明に係る半導体素子の他の実施形態を示した断面図である。

【発明を実施するための形態】

【0038】

以下、図を参照しながら、本発明に係る半導体素子及びその形成方法の1つの実施形態に対し詳しく説明する。

【0039】

図1は、本発明の1つの実施形態に係る半導体素子を示す平面図である。図1に示す通り、本発明の1つの実施形態における活性領域(active region)12は、斜めに傾いた角度で延長されたラインタイプ(line type)に形成される。そして、半導体基板10のうちこの活性領域12が形成されない領域は、ラインタイプの素子分離膜となる。但し、本発明において活性領域12がこのようなラインタイプ構造に制限されるものではなく、これと異なる活性領域の構造に対しては後述する。

【0040】

そして、ビットライン(bit line)60は半導体基板10で左右方向に沿って延長されたラインタイプに形成され、メインゲート(main gate)20もまた半導体基板10で上下方向に沿って延長されたラインタイプに形成される。そして、2つのメインゲート20の間にはメインゲート20と類似の構造の分離ゲート(isolation gate)30が上下方向に沿って延長されたラインタイプにビットライン60と垂直に交差しながら形成される。この多数のメインゲート20と多数の分離ゲート30との組み合わせは、全体の半導体基板10で互いに一定の間隔に、例えば、1:1ラインアンドスペース構造(ラインパターンが1の線幅であれば、その左右の空間が1の線幅に形成される構造)に形成されることが好ましい。

【0041】

そして、分離ゲート30の上部には分離ゲート30と同一のラインタイプの分離パターン(isolation pattern;図2を参照)40が形成され、この分離パターン40の両側にはコンタクトプラグ(contact plug)がそれぞれ形成され、このコンタクトプラグ50は格納電極コンタクトプラグ(storage node contact plug)を含むことができる。

【0042】

図2は、図1においてA-A'線に沿う断面図である。図2に示す通り、半導体基板10には活性領域12が形成されており、活性領域12には2つのメインゲート20と1つの分離ゲート30とが一定の間隔を置いて順次繰り返される構造に形成される。そして、このメインゲート20及び分離ゲート30は、半導体基板10の内部にゲートが埋め込まれた構造の埋込型ゲート(buried gate)に形成され得る。このメイン及び分離ゲート20、30はそれぞれ、半導体基板10に形成された所定深さのリセス(recess)22、32、このリセス22、32の下部に埋め込まれタングステンやチタニウムなどの金属を含むゲート導電層(gate electrode)24、34、そしてリセス22、32内でゲート導電層24、34の上部に埋め込まれ窒化膜や酸化膜のような絶縁物質を含むキャッピング膜(capping film)26、36を含むことが好ましい。

【0043】

ここでメインゲート20は、半導体素子内でワードライン(word line)で動作するゲートであり、分離ゲート30は、メインゲート20と同一の構造の素子であるが、実際のゲートで動作せず各セルを分離する役割を果たすゲートであり、分離ゲート30等は全てバックバイアス電圧(Vbb)と連結される方式で接地(grounding)されることが好ましい。さらに、この分離ゲート30は、後述するところのように、素子分離膜(device isolation film)、或いは素子分離膜にゲートが埋め込まれた構造に取り替えられることも可能である(図15を参照)。

【0044】

一方、活性領域12のうち各ゲート20、30の間の領域には接合領域(junction)が形成されるところ、2つのメインゲート20の間はビットラインコンタクト領域(bit line contact region)が、メインゲート20と分離ゲート30との間は格納電極コンタクト領域(storage node contact region)になることが好ましいが、これに限定されない。この結果、ビットラインコンタクト領域の上部にはビットラインコンタクトプラグ(bit line contact plug)62及びビットライン(bit line)60が形成され、格納電極コンタクト領域の上部には格納電極コンタクトプラグ54及びキャパシタ(図示省略)が形成され得る。このとき、ビットラインコンタクトプラグ62は、図2に示す通り格納電極コンタクトプラグ54より低い高さに形成されてもよく、図14に示す通り格納電極コンタクトプラグ54より高い高さに形成されてもよい。

【0045】

さらに、分離ゲート30の上部には分離パターン(isolation pattern)40が形成される。この分離パターン40は、図1に示されたラインタイプの分離ゲート30の上部に沿って同一のラインタイプに形成されることが好ましく、物質は酸化膜(oxide film)と相違する食刻選択比を有する物質であれば十分であり、窒化膜(nitride)、シリコン酸化窒化膜(SiON)、非晶質炭素(amorphous carbon)のような物質を含むことが好ましい。そして、分離パターン40は2つのコンタクトプラグ54の間に位置することになる。即ち、分離パターン40の両端にはそれぞれコンタクトプラグ54が備えられ、このコンタクトプラグ54は格納電極コンタクトプラグであり得る。

【0046】

なお、この分離パターン40は基板10の上部に形成されるところ、分離パターン40の下部はリセス32の上部に一部埋め込まれて備えられることが好ましく、この結果、分離パターン40が基板10の上部で高い縦横比(aspect ratio)で形成されても崩壊が防止され得る。

【0047】

このような構造を有する本発明の1つの実施形態に係る半導体素子は、分離ゲート30の上部に分離パターン40が形成された構造を介し、2つの格納電極コンタクトプラグ54を1回の食刻工程及び蒸着工程で形成し、このとき予め形成された分離パターン40が2つの格納電極コンタクトプラグ54を分離する役割を果たす。この結果、格納電極コンタクトと活性領域との間のフルオーバーラップ(full overlap)を提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させる効果を提供することができる。

【0048】

図3〜図14は、本発明に係る半導体素子の形成方法を示した断面図であって、図1においてA-A'線に沿う断面図である。以下では、図3〜図14を参照しながら、前述の構造を有する半導体素子の形成方法を説明する。

【0049】

先ず、図3に示す通り、半導体基板10にメインゲート20及び分離ゲート30を埋め込んで形成する。具体的に、半導体基板10に所定深さのリセス22、32を所定の深さに形成し、このリセス22、32を含む半導体基板10にタングステンやチタニウムなどを含む導電物質を蒸着して埋め込んだあとエッチバック(etch back)で食刻し、リセス22、32の下部にのみ導電物質を残留させてゲート導電層24、34を形成する。以後、リセス22、32内でゲート導電層24、34の上部に窒化膜や酸化膜のような絶縁物質を含むキャッピング膜26、36を形成することが好ましい。

【0050】

そして、各ゲート20、30の間の半導体基板10に対するイオン注入を行って接合領域(junction)14を形成し、半導体基板10の上部に酸化膜などを含む層間絶縁膜(interlayer dielectric)57を所定の厚さに蒸着する。

【0051】

一方、図示されてはいないが、図3に示されたゲート20、30形成の工程以前に、図1に示す通り、ラインタイプの活性領域12を画成するラインタイプの素子分離膜をSTI(Shallow Trench Isolation)工程で形成することが好ましい。

【0052】

この素子分離膜を形成するSTI工程を具体的に説明すれば、先ず酸化工程を介しトレンチ内壁に側壁酸化膜(wall oxide)を形成し、この側壁酸化膜はトレンチ形成以後に露出した半導体基板の表面の格子欠陷を緩和させる効果を提供する。以後、トレンチの表面にライナー窒化膜(liner nitride)及びライナー酸化膜(liner oxide)を形成する。ライナー窒化膜はトレンチ内壁の酸化を防止し、後続工程における応力の発生を抑制する効果を提供することができる。そして、ライナー酸化膜は、トレンチ埋込みのための絶縁物質の蒸着時にストレスなどがトレンチ内に直接伝えられることを抑制するか、トレンチにより露出した半導体基板とパッド窒化膜パターンとの物質差による蒸着速度の差による不均一性を解消する効果を提供することができる。

【0053】

次に、ライナー酸化膜が形成されたトレンチを含む半導体基板全体の上部に素子分離用絶縁物質を形成する。素子分離用絶縁物質は酸化膜を含み、例えば、高密度プラズマ(HDP:High Density Plasma)やSOD(Spin On Dielectric)を用いることができる。引続き、パッド窒化膜パターンが露出するまで機械的化学的研磨(Chemical Mechanical Polishing;CMP)工程を進めて素子分離膜を形成することができる。

【0054】

図4に示す通り、層間絶縁膜57の上部にマスクパターン(mask pattern)72を形成する。このマスクパターン72は感光膜(photoresist layer)パターン或いはハードマスク(hard mask)パターンを含むことができ、各マスクパターン72の境界は分離ゲート30の上部に位置することが好ましい。さらに具体的には、マスクパターン72の境界は、2つの隣接した分離ゲート30のうち左側に位置した分離ゲート30の左側端部(left end)と、右側に位置した分離ゲート30の右側端部(right end)とが一致することが最も好ましい。

【0055】

図5に示す通り、マスクパターン72をマスクとして層間絶縁膜57を食刻して半導体基板10を露出させる。このとき、2つのメインゲート20と2つの分離ゲート30の上側が露出することが好ましい。そして、食刻された層間絶縁膜57の境界もまた分離ゲート30の上部に位置することになる。

【0056】

図6に示す通り、キャッピング膜26、36に対する食刻工程を行い、キャッピング膜26、36の上部を一部除去する。この結果、各埋込型ゲート20、30の上側にはキャッピング膜リセス26a、36aが所定の深さに形成される。このキャッピング膜26、36に対する食刻工程は、窒化膜(キャッピング膜)とシリコン(基板)及び酸化膜(層間絶縁膜)の間の食刻選択比を利用することが好ましい。

【0057】

図7に示す通り、キャッピング膜リセス26a、36aを含む半導体基板10の全面に分離パターン層(isolation pattern layer)42を所定の厚さに蒸着する。この分離パターン層42は追って分離パターン40になる構成であって、酸化膜(oxide film)と相違する食刻選択比を有する物質であれば十分であり、窒化膜(nitride)、シリコン酸化窒化膜(SiON)、非晶質炭素(amorphous carbon)のような物質を含むことが好ましい。さらに、この分離パターン層42を蒸着する工程は物理的気相蒸着(PVD)、化学気相蒸着(CVD)又は原子層蒸着(ALD)などの工程が適用され得る。

【0058】

図8に示す通り、分離パターン層42に対する異方性食刻工程を行って層間絶縁膜57の側壁にのみ分離パターン層42が残留するようにすることにより、分離パターン40を形成する。このとき、層間絶縁膜57の境界は分離ゲート30の上部なので、分離パターン40もまた分離ゲート30の上部に形成される。そして、この異方性食刻工程では、前述のキャッピング膜リセス26a、36aにも分離パターン層42が残留することになるので、結果的に、分離パターン40の下部はキャッピング膜リセス36aに埋め込まれた構造となり、追っての工程で分離パターン40の崩壊が防止され得る。

【0059】

図9に示す通り、層間絶縁膜57を除去し、半導体基板10の上部には分離パターン40だけが備えられるようにする。

【0060】

図10に示す通り、分離パターン40が備えられた半導体基板10の上部に再度層間絶縁膜56を蒸着して全体表面を平坦化する。このとき、層間絶縁膜56は酸化膜を含むことが好ましい。次いで、層間絶縁膜56の上部に感光膜やハードマスク材質のマスクパターン74を形成する。このマスクパターン74は、格納電極コンタクト領域(storage node contact region)を画成する形態に形成されることが好ましく、1つの格納電極コンタクトでなく、1つの分離パターン40を含む隣接した2つの格納電極コンタクトを共に画成する形態及び大きさに形成されることが好ましい。

【0061】

図11に示す通り、マスクパターン74をマスクとして層間絶縁膜56を食刻して格納電極コンタクトホール(storage node contact hole)52を形成する。この格納電極コンタクトホール52は分離ゲート30とメインゲート20との間の接合領域14を露出させることが好ましく、格納電極コンタクトホール52の中心には分離パターン40が位置する。この食刻過程で、分離パターン40は酸化膜材質の層間絶縁膜56とは食刻選択比を有する窒化膜(nitride)、シリコン酸化窒化膜(SiON)、非晶質炭素(amorphous carbon)のような物質を含むので、層間絶縁膜56が食刻される工程で共に食刻されず残留することになる。

【0062】

図12に示す通り、格納電極コンタクトホール52を含む半導体基板10の全面にポリシリコンのような導電物質54aを蒸着して格納電極コンタクトホール52を埋め込む。図13に示す通り、導電物質54aの上部をCMP(Chemical Mechanical Polishing)のような工程で平坦化食刻して互いに分離させることにより、各格納電極コンタクトホール52に埋め込まれる格納電極コンタクトプラグ54を形成する。

【0063】

図14に示す通り、格納電極コンタクトプラグ54が形成された層間絶縁膜56を食刻し、導電物質を埋め込んでビットラインコンタクトプラグ62を形成し、その上部にビットライン(図2を参照)60を形成する。そして、格納電極コンタクトプラグ54の上部には下部電極、誘電膜及び上部電極を含むキャパシタを形成する。

【0064】

このような構成を有する本発明の1つの実施形態に係る半導体素子の形成方法は、分離ゲート30の上部に分離パターン40が形成された構造を介し2つの格納電極コンタクトプラグ54を1回の食刻工程及び蒸着工程で形成し、このとき予め形成された分離パターン40が2つの格納電極コンタクトプラグ54を分離する役割を果たす。この結果、格納電極コンタクトプラグと活性領域との間のフルオーバーラップ(full overlap)を提供することができるので食刻工程でのオーバーレイ問題を解消し、コンタクト抵抗を減少させることができ、格納電極の食刻線幅を増加させて工程マージンを向上させる効果を提供することができる。

【0065】

一方、今まで説明した実施形態は、活性領域(図1を参照)12がラインタイプに形成され分離ゲート30を含む構造を説明したが、下記のように活性領域がバータイプ(bar type)に形成され、分離ゲート30を含まない半導体素子にも適用され得る。

【0066】

図15は、本発明に係る半導体素子の他の実施形態を示した図である。図15に示す通り、前述した本発明の実施形態から分離ゲート30は省略され、当該位置に素子分離膜38が形成されてもよい。この素子分離膜38は、STI工程を介しトレンチに絶縁膜が埋め込まれた構造に形成されることが好ましく、この素子分離膜38にもゲート20が埋め込まれて備えられ得る。そして、この素子分離膜38の上部にも分離パターン40が形成され、分離パターン40の左右側に格納電極コンタクトプラグ54が形成される。

【0067】

このような構造を有する半導体素子においても、前述の実施形態と同様に、素子分離膜38の上部に分離パターン40が形成された構造を介し2つの格納電極コンタクトプラグ54を1回の食刻工程及び蒸着工程で形成し、このとき、予め形成された分離パターン40が2つの格納電極コンタクトプラグ54を分離する役割を果たす。この結果、格納電極コンタクトと活性領域との間のフルオーバーラップ(full overlap)を提供することができるので食刻工程でのオーバーレイ問題を解消し、コンタクト抵抗を減少させることができ、格納電極の食刻線幅を増加させて工程マージンを向上させる効果を提供することができる。

【技術分野】

【0001】

本発明は、半導体素子及びその形成方法に関する。より詳しくは、埋込型ゲートと格納電極コンタクトを含む半導体素子及びその形成方法に関する。

【背景技術】

【0002】

最近、半導体メモリ素子、特にDRAM(Dynamic Random Access Memory)素子の大容量化に対する要求が漸次大きくなるにも拘わらず、チップの大きさの増加の限界によりDRAM素子の容量増加もまた限界を見せる実情である。チップの大きさが増加することになれば、ウエハ当りチップの数が減少し、素子の生産性が減少することになる。したがって、最近はセルレイアウトを変化させてセルの面積を減少させ、それに伴いより多いメモリセルを1つのウエハに集積させようとする努力を傾けている。このような努力により、最近は既存の8F2レイアウトから6F2レイアウトに変化している。

【0003】

一方、半導体記憶装置の全体面積を縮小させると、1つのウエハ当り生産可能な半導体記憶装置の数を増加させることができ生産性が向上する。半導体記憶装置の全体面積を縮小させるため、多様な方法が提案されている。このうち1つが水平チャンネル領域を有していた従来のプラナーゲート(Planar Gate)に代えて、基板にリセスが形成されそのリセスにゲートを形成することにより、リセスの曲面に沿ってチャンネル領域が形成されるリセスゲート(Recess Gate)を用いることであり、このリセスゲートから進んでリセス内にゲート全体を埋め込んで形成する埋込型ゲート(Buried Gate)が研究されている。

【0004】

このような埋込型ゲートは、ゲート全体が半導体基板の表面以下に埋め込まれて形成されるので、チャンネル長と幅を確保することができることは勿論、リセスゲートに比べゲート(ワードラインとビットラインとの間に発生する寄生キャパシタンス(Parasitic Capacitance)を従来に比べ50%程度減少させることのできる効果を提供する。

【0005】

ところが、このように埋込型ゲートが適用された6F2レイアウトにおいても格納電極コンタクトと活性領域が接するコンタクト面積が減少し、コンタクト抵抗が増加するとの問題が発生している実情である。

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、前記のような従来の問題点を解決するためのものであり、素子分離構造の上部に分離パターンを形成し、この分離パターンの両端にコンタクトプラグを形成することにより、格納電極コンタクトと活性領域との間のフルオーバーラップを提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させる半導体素子及びその形成方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る半導体素子は、半導体基板に備えられるメインゲート及び素子分離構造と、前記素子分離構造の上部に備えられる分離パターンと、前記分離パターンの両端に備えられるコンタクトプラグとを含み、素子分離構造の上部に分離パターンを形成し、この分離パターンの両端にコンタクトプラグを形成することにより、格納電極コンタクトと活性領域との間のフルオーバーラップを提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させることを特徴とする。

【0008】

さらに、前記素子分離構造は、前記半導体基板で前記メインゲートに隣接して備えられる分離ゲート、又は前記半導体基板が食刻されたトレンチに埋め込まれた絶縁膜を含む素子分離膜のうち1つ以上を含むことができる。

【0009】

さらに、前記分離パターンは酸化膜と相違する食刻選択比を有する絶縁膜であって、窒化膜、シリコン酸化窒化膜、非晶質炭素を含むことを特徴とする。

【0010】

なお、前記メインゲート及び前記分離ゲートは、半導体基板に所定の深さに形成されたリセスと、前記リセスの下部に埋め込まれたゲート導電層と、前記リセスで前記ゲート導電層の上部に備えられるキャッピング膜とを含む埋込型ゲートであることが好ましい。

【0011】

併せて、前記分離パターンの下部は、前記リセスの上部に埋め込まれ、パターンの崩壊が防止されることを特徴とする。

【0012】

さらに、前記メインゲート及び前記分離ゲートは、2つのメインゲートと1つの分離ゲートとが交互に備えられることが好ましい。

【0013】

さらに、前記2つのメインゲートの間のビットラインコンタクト領域の上部に備えられるビットラインコンタクトと、前記ビットラインコンタクトの上部に備えられるビットラインとをさらに含むことができる。

【0014】

なお、前記コンタクトプラグは、格納電極コンタクトプラグを含むことが好ましい。

【0015】

一方、本発明に係る半導体素子は、半導体基板にラインタイプに形成された活性領域と、前記半導体基板に前記活性領域に対し斜めに延長されたメインゲート及び分離ゲートと、前記分離ゲートの上部に備えられるラインタイプの分離パターンと、前記分離パターンの両端に沿って延長されるコンタクトプラグとを含み、素子分離構造の上部に分離パターンを形成し、この分離パターンの両端にコンタクトプラグを形成することにより、格納電極コンタクトと活性領域との間のフルオーバーラップを提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させることを特徴とする。

【0016】

さらに、前記メインゲート及び前記分離ゲートは、2つのメインゲートと1つの分離ゲートとが交互に備えられることが好ましい。

なお、前記2つのメインゲートの間に備えられるビットラインコンタクトプラグをさらに含むことができる。

【0017】

併せて、前記ビットラインコンタクトプラグの上部に備えられ、前記メインゲートと交差しながら延長されたラインタイプのビットラインをさらに含むことを特徴とする。

【0018】

さらに、前記ビットラインは、前記メインゲートと垂直に交差することが好ましく、前記コンタクトプラグは、格納電極コンタクトプラグを含むことが好ましい。

【0019】

一方、本発明に係る半導体素子の形成方法は、半導体基板にメインゲート及び素子分離構造を形成するステップと、前記素子分離構造の上部に分離パターンを形成するステップと、前記分離パターンの両端にコンタクトプラグを形成するステップとを含み、素子分離構造の上部に分離パターンを形成し、この分離パターンの両端にコンタクトプラグを形成することにより、格納電極コンタクトと活性領域との間のフルオーバーラップを提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させることを特徴とする。

【0020】

さらに、前記素子分離構造を形成するステップは、前記半導体基板で前記メインゲートに隣接して備えられる分離ゲートを形成するステップ、又は前記半導体基板が食刻されたトレンチに埋め込まれた絶縁膜を含む素子分離膜を形成するステップのうち1つ以上を含むことができる。

【0021】

なお、前記分離パターンを形成するステップは、前記半導体基板の上部に層間絶縁膜を形成するステップと、前記分離ゲートを境界に前記層間絶縁膜を食刻するステップと、前記食刻された層間絶縁膜を含む半導体基板の全面に分離パターン層を蒸着するステップと、前記分離パターン層をエッチバックして前記層間絶縁膜の側壁に分離パターンを残留させるステップと、前記層間絶縁膜を除去するステップとを含むことが好ましい。

【0022】

さらに、前記メインゲート及び前記分離ゲートを形成するステップは、半導体基板に所定の深さにリセスを形成するステップと、前記リセスの下部にゲート導電層を埋め込むステップと、前記リセスで前記ゲート導電層の上部にキャッピング膜を埋め込むステップとを含むことを特徴とする。

【0023】

併せて、前記分離パターンの下部を前記リセスの上部に埋め込んで形成することが好ましい。

【0024】

さらに、前記キャッピング膜を所定の深さに食刻するステップと、前記食刻されたキャッピング膜を含む半導体基板の上部に分離パターン層を形成するステップとを含むことができる。

【0025】

なお、前記コンタクトプラグを形成するステップは、前記分離パターンを含む半導体基板に層間絶縁膜を形成するステップと、前記メインゲートを境界に前記層間絶縁膜を食刻してコンタクトホールを形成するステップと、前記コンタクトホールを含む半導体基板の全面に導電物質を蒸着するステップと、前記層間絶縁膜の上部の前記導電物質を平坦化食刻するステップとを含むことが好ましい。

【0026】

さらに、前記分離パターンは酸化膜と相違する食刻選択比を有する絶縁膜であって、窒化膜、シリコン酸化窒化膜、非晶質炭素を含むことができる。

【0027】

併せて、前記メインゲート及び前記分離ゲートを形成するステップは、2つのメインゲートと1つの分離ゲートとが交互に備えられるようにすることが好ましい。

【0028】

なお、前記2つのメインゲートの間のビットラインコンタクト領域の上部にビットラインコンタクトを形成するステップと、前記ビットラインコンタクトの上部にビットラインを形成するステップとをさらに含むことを特徴とする。

【0029】

さらに、前記コンタクトプラグは、格納電極コンタクトプラグを含むことができる。

【0030】

一方、本発明に係る半導体素子の形成方法は、半導体基板にラインタイプの活性領域を形成するステップと、前記半導体基板に前記活性領域に対し斜めに延長されたメインゲート及び分離ゲートをラインタイプに形成するステップと、前記分離ゲートの上部にラインタイプの分離パターンを形成するステップと、前記分離パターンの両端に沿って延長されるコンタクトプラグを形成するステップとを含むことを特徴とする。

【0031】

さらに、前記メインゲート及び前記分離ゲートを形成するステップは、2つのメインゲートと1つの分離ゲートとが交互に備えられるようにすることが好ましい。

【0032】

さらに、前記2つのメインゲートの間にコンタクトプラグを形成するステップをさらに含むことができる。

【0033】

さらに、前記ビットラインコンタクトプラグの上部に備えられ前記ビットラインコンタクトプラグと連結され、前記メインゲートと交差しながら延長されたビットラインをラインタイプに形成するステップをさらに含むことを特徴とする。

【0034】

併せて、前記ビットラインは、前記メインゲートと垂直に交差することが好ましい。

【0035】

さらに、前記コンタクトプラグは、格納電極コンタクトプラグを含むことができる。

【発明の効果】

【0036】

本発明に係る半導体素子及びその形成方法は、格納電極コンタクトと活性領域との間のフルオーバーラップ(full overlap)を提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させる効果を提供する。

【図面の簡単な説明】

【0037】

【図1】本発明の1つの実施形態に係る半導体素子を示す平面図である。

【図2】図1においてA-A'線に沿った断面図である。

【図3】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図4】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図5】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図6】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図7】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図8】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図9】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図10】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図11】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図12】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図13】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図14】本発明に係る半導体素子の形成方法を示す断面図であって、図1においてA-A'線に沿う断面図である。

【図15】本発明に係る半導体素子の他の実施形態を示した断面図である。

【発明を実施するための形態】

【0038】

以下、図を参照しながら、本発明に係る半導体素子及びその形成方法の1つの実施形態に対し詳しく説明する。

【0039】

図1は、本発明の1つの実施形態に係る半導体素子を示す平面図である。図1に示す通り、本発明の1つの実施形態における活性領域(active region)12は、斜めに傾いた角度で延長されたラインタイプ(line type)に形成される。そして、半導体基板10のうちこの活性領域12が形成されない領域は、ラインタイプの素子分離膜となる。但し、本発明において活性領域12がこのようなラインタイプ構造に制限されるものではなく、これと異なる活性領域の構造に対しては後述する。

【0040】

そして、ビットライン(bit line)60は半導体基板10で左右方向に沿って延長されたラインタイプに形成され、メインゲート(main gate)20もまた半導体基板10で上下方向に沿って延長されたラインタイプに形成される。そして、2つのメインゲート20の間にはメインゲート20と類似の構造の分離ゲート(isolation gate)30が上下方向に沿って延長されたラインタイプにビットライン60と垂直に交差しながら形成される。この多数のメインゲート20と多数の分離ゲート30との組み合わせは、全体の半導体基板10で互いに一定の間隔に、例えば、1:1ラインアンドスペース構造(ラインパターンが1の線幅であれば、その左右の空間が1の線幅に形成される構造)に形成されることが好ましい。

【0041】

そして、分離ゲート30の上部には分離ゲート30と同一のラインタイプの分離パターン(isolation pattern;図2を参照)40が形成され、この分離パターン40の両側にはコンタクトプラグ(contact plug)がそれぞれ形成され、このコンタクトプラグ50は格納電極コンタクトプラグ(storage node contact plug)を含むことができる。

【0042】

図2は、図1においてA-A'線に沿う断面図である。図2に示す通り、半導体基板10には活性領域12が形成されており、活性領域12には2つのメインゲート20と1つの分離ゲート30とが一定の間隔を置いて順次繰り返される構造に形成される。そして、このメインゲート20及び分離ゲート30は、半導体基板10の内部にゲートが埋め込まれた構造の埋込型ゲート(buried gate)に形成され得る。このメイン及び分離ゲート20、30はそれぞれ、半導体基板10に形成された所定深さのリセス(recess)22、32、このリセス22、32の下部に埋め込まれタングステンやチタニウムなどの金属を含むゲート導電層(gate electrode)24、34、そしてリセス22、32内でゲート導電層24、34の上部に埋め込まれ窒化膜や酸化膜のような絶縁物質を含むキャッピング膜(capping film)26、36を含むことが好ましい。

【0043】

ここでメインゲート20は、半導体素子内でワードライン(word line)で動作するゲートであり、分離ゲート30は、メインゲート20と同一の構造の素子であるが、実際のゲートで動作せず各セルを分離する役割を果たすゲートであり、分離ゲート30等は全てバックバイアス電圧(Vbb)と連結される方式で接地(grounding)されることが好ましい。さらに、この分離ゲート30は、後述するところのように、素子分離膜(device isolation film)、或いは素子分離膜にゲートが埋め込まれた構造に取り替えられることも可能である(図15を参照)。

【0044】

一方、活性領域12のうち各ゲート20、30の間の領域には接合領域(junction)が形成されるところ、2つのメインゲート20の間はビットラインコンタクト領域(bit line contact region)が、メインゲート20と分離ゲート30との間は格納電極コンタクト領域(storage node contact region)になることが好ましいが、これに限定されない。この結果、ビットラインコンタクト領域の上部にはビットラインコンタクトプラグ(bit line contact plug)62及びビットライン(bit line)60が形成され、格納電極コンタクト領域の上部には格納電極コンタクトプラグ54及びキャパシタ(図示省略)が形成され得る。このとき、ビットラインコンタクトプラグ62は、図2に示す通り格納電極コンタクトプラグ54より低い高さに形成されてもよく、図14に示す通り格納電極コンタクトプラグ54より高い高さに形成されてもよい。

【0045】

さらに、分離ゲート30の上部には分離パターン(isolation pattern)40が形成される。この分離パターン40は、図1に示されたラインタイプの分離ゲート30の上部に沿って同一のラインタイプに形成されることが好ましく、物質は酸化膜(oxide film)と相違する食刻選択比を有する物質であれば十分であり、窒化膜(nitride)、シリコン酸化窒化膜(SiON)、非晶質炭素(amorphous carbon)のような物質を含むことが好ましい。そして、分離パターン40は2つのコンタクトプラグ54の間に位置することになる。即ち、分離パターン40の両端にはそれぞれコンタクトプラグ54が備えられ、このコンタクトプラグ54は格納電極コンタクトプラグであり得る。

【0046】

なお、この分離パターン40は基板10の上部に形成されるところ、分離パターン40の下部はリセス32の上部に一部埋め込まれて備えられることが好ましく、この結果、分離パターン40が基板10の上部で高い縦横比(aspect ratio)で形成されても崩壊が防止され得る。

【0047】

このような構造を有する本発明の1つの実施形態に係る半導体素子は、分離ゲート30の上部に分離パターン40が形成された構造を介し、2つの格納電極コンタクトプラグ54を1回の食刻工程及び蒸着工程で形成し、このとき予め形成された分離パターン40が2つの格納電極コンタクトプラグ54を分離する役割を果たす。この結果、格納電極コンタクトと活性領域との間のフルオーバーラップ(full overlap)を提供することができるので食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させて工程マージンを向上させる効果を提供することができる。

【0048】

図3〜図14は、本発明に係る半導体素子の形成方法を示した断面図であって、図1においてA-A'線に沿う断面図である。以下では、図3〜図14を参照しながら、前述の構造を有する半導体素子の形成方法を説明する。

【0049】

先ず、図3に示す通り、半導体基板10にメインゲート20及び分離ゲート30を埋め込んで形成する。具体的に、半導体基板10に所定深さのリセス22、32を所定の深さに形成し、このリセス22、32を含む半導体基板10にタングステンやチタニウムなどを含む導電物質を蒸着して埋め込んだあとエッチバック(etch back)で食刻し、リセス22、32の下部にのみ導電物質を残留させてゲート導電層24、34を形成する。以後、リセス22、32内でゲート導電層24、34の上部に窒化膜や酸化膜のような絶縁物質を含むキャッピング膜26、36を形成することが好ましい。

【0050】

そして、各ゲート20、30の間の半導体基板10に対するイオン注入を行って接合領域(junction)14を形成し、半導体基板10の上部に酸化膜などを含む層間絶縁膜(interlayer dielectric)57を所定の厚さに蒸着する。

【0051】

一方、図示されてはいないが、図3に示されたゲート20、30形成の工程以前に、図1に示す通り、ラインタイプの活性領域12を画成するラインタイプの素子分離膜をSTI(Shallow Trench Isolation)工程で形成することが好ましい。

【0052】

この素子分離膜を形成するSTI工程を具体的に説明すれば、先ず酸化工程を介しトレンチ内壁に側壁酸化膜(wall oxide)を形成し、この側壁酸化膜はトレンチ形成以後に露出した半導体基板の表面の格子欠陷を緩和させる効果を提供する。以後、トレンチの表面にライナー窒化膜(liner nitride)及びライナー酸化膜(liner oxide)を形成する。ライナー窒化膜はトレンチ内壁の酸化を防止し、後続工程における応力の発生を抑制する効果を提供することができる。そして、ライナー酸化膜は、トレンチ埋込みのための絶縁物質の蒸着時にストレスなどがトレンチ内に直接伝えられることを抑制するか、トレンチにより露出した半導体基板とパッド窒化膜パターンとの物質差による蒸着速度の差による不均一性を解消する効果を提供することができる。

【0053】

次に、ライナー酸化膜が形成されたトレンチを含む半導体基板全体の上部に素子分離用絶縁物質を形成する。素子分離用絶縁物質は酸化膜を含み、例えば、高密度プラズマ(HDP:High Density Plasma)やSOD(Spin On Dielectric)を用いることができる。引続き、パッド窒化膜パターンが露出するまで機械的化学的研磨(Chemical Mechanical Polishing;CMP)工程を進めて素子分離膜を形成することができる。

【0054】

図4に示す通り、層間絶縁膜57の上部にマスクパターン(mask pattern)72を形成する。このマスクパターン72は感光膜(photoresist layer)パターン或いはハードマスク(hard mask)パターンを含むことができ、各マスクパターン72の境界は分離ゲート30の上部に位置することが好ましい。さらに具体的には、マスクパターン72の境界は、2つの隣接した分離ゲート30のうち左側に位置した分離ゲート30の左側端部(left end)と、右側に位置した分離ゲート30の右側端部(right end)とが一致することが最も好ましい。

【0055】

図5に示す通り、マスクパターン72をマスクとして層間絶縁膜57を食刻して半導体基板10を露出させる。このとき、2つのメインゲート20と2つの分離ゲート30の上側が露出することが好ましい。そして、食刻された層間絶縁膜57の境界もまた分離ゲート30の上部に位置することになる。

【0056】

図6に示す通り、キャッピング膜26、36に対する食刻工程を行い、キャッピング膜26、36の上部を一部除去する。この結果、各埋込型ゲート20、30の上側にはキャッピング膜リセス26a、36aが所定の深さに形成される。このキャッピング膜26、36に対する食刻工程は、窒化膜(キャッピング膜)とシリコン(基板)及び酸化膜(層間絶縁膜)の間の食刻選択比を利用することが好ましい。

【0057】

図7に示す通り、キャッピング膜リセス26a、36aを含む半導体基板10の全面に分離パターン層(isolation pattern layer)42を所定の厚さに蒸着する。この分離パターン層42は追って分離パターン40になる構成であって、酸化膜(oxide film)と相違する食刻選択比を有する物質であれば十分であり、窒化膜(nitride)、シリコン酸化窒化膜(SiON)、非晶質炭素(amorphous carbon)のような物質を含むことが好ましい。さらに、この分離パターン層42を蒸着する工程は物理的気相蒸着(PVD)、化学気相蒸着(CVD)又は原子層蒸着(ALD)などの工程が適用され得る。

【0058】

図8に示す通り、分離パターン層42に対する異方性食刻工程を行って層間絶縁膜57の側壁にのみ分離パターン層42が残留するようにすることにより、分離パターン40を形成する。このとき、層間絶縁膜57の境界は分離ゲート30の上部なので、分離パターン40もまた分離ゲート30の上部に形成される。そして、この異方性食刻工程では、前述のキャッピング膜リセス26a、36aにも分離パターン層42が残留することになるので、結果的に、分離パターン40の下部はキャッピング膜リセス36aに埋め込まれた構造となり、追っての工程で分離パターン40の崩壊が防止され得る。

【0059】

図9に示す通り、層間絶縁膜57を除去し、半導体基板10の上部には分離パターン40だけが備えられるようにする。

【0060】

図10に示す通り、分離パターン40が備えられた半導体基板10の上部に再度層間絶縁膜56を蒸着して全体表面を平坦化する。このとき、層間絶縁膜56は酸化膜を含むことが好ましい。次いで、層間絶縁膜56の上部に感光膜やハードマスク材質のマスクパターン74を形成する。このマスクパターン74は、格納電極コンタクト領域(storage node contact region)を画成する形態に形成されることが好ましく、1つの格納電極コンタクトでなく、1つの分離パターン40を含む隣接した2つの格納電極コンタクトを共に画成する形態及び大きさに形成されることが好ましい。

【0061】

図11に示す通り、マスクパターン74をマスクとして層間絶縁膜56を食刻して格納電極コンタクトホール(storage node contact hole)52を形成する。この格納電極コンタクトホール52は分離ゲート30とメインゲート20との間の接合領域14を露出させることが好ましく、格納電極コンタクトホール52の中心には分離パターン40が位置する。この食刻過程で、分離パターン40は酸化膜材質の層間絶縁膜56とは食刻選択比を有する窒化膜(nitride)、シリコン酸化窒化膜(SiON)、非晶質炭素(amorphous carbon)のような物質を含むので、層間絶縁膜56が食刻される工程で共に食刻されず残留することになる。

【0062】

図12に示す通り、格納電極コンタクトホール52を含む半導体基板10の全面にポリシリコンのような導電物質54aを蒸着して格納電極コンタクトホール52を埋め込む。図13に示す通り、導電物質54aの上部をCMP(Chemical Mechanical Polishing)のような工程で平坦化食刻して互いに分離させることにより、各格納電極コンタクトホール52に埋め込まれる格納電極コンタクトプラグ54を形成する。

【0063】

図14に示す通り、格納電極コンタクトプラグ54が形成された層間絶縁膜56を食刻し、導電物質を埋め込んでビットラインコンタクトプラグ62を形成し、その上部にビットライン(図2を参照)60を形成する。そして、格納電極コンタクトプラグ54の上部には下部電極、誘電膜及び上部電極を含むキャパシタを形成する。

【0064】

このような構成を有する本発明の1つの実施形態に係る半導体素子の形成方法は、分離ゲート30の上部に分離パターン40が形成された構造を介し2つの格納電極コンタクトプラグ54を1回の食刻工程及び蒸着工程で形成し、このとき予め形成された分離パターン40が2つの格納電極コンタクトプラグ54を分離する役割を果たす。この結果、格納電極コンタクトプラグと活性領域との間のフルオーバーラップ(full overlap)を提供することができるので食刻工程でのオーバーレイ問題を解消し、コンタクト抵抗を減少させることができ、格納電極の食刻線幅を増加させて工程マージンを向上させる効果を提供することができる。

【0065】

一方、今まで説明した実施形態は、活性領域(図1を参照)12がラインタイプに形成され分離ゲート30を含む構造を説明したが、下記のように活性領域がバータイプ(bar type)に形成され、分離ゲート30を含まない半導体素子にも適用され得る。

【0066】

図15は、本発明に係る半導体素子の他の実施形態を示した図である。図15に示す通り、前述した本発明の実施形態から分離ゲート30は省略され、当該位置に素子分離膜38が形成されてもよい。この素子分離膜38は、STI工程を介しトレンチに絶縁膜が埋め込まれた構造に形成されることが好ましく、この素子分離膜38にもゲート20が埋め込まれて備えられ得る。そして、この素子分離膜38の上部にも分離パターン40が形成され、分離パターン40の左右側に格納電極コンタクトプラグ54が形成される。

【0067】

このような構造を有する半導体素子においても、前述の実施形態と同様に、素子分離膜38の上部に分離パターン40が形成された構造を介し2つの格納電極コンタクトプラグ54を1回の食刻工程及び蒸着工程で形成し、このとき、予め形成された分離パターン40が2つの格納電極コンタクトプラグ54を分離する役割を果たす。この結果、格納電極コンタクトと活性領域との間のフルオーバーラップ(full overlap)を提供することができるので食刻工程でのオーバーレイ問題を解消し、コンタクト抵抗を減少させることができ、格納電極の食刻線幅を増加させて工程マージンを向上させる効果を提供することができる。

【特許請求の範囲】

【請求項1】

半導体基板に備えられるメインゲート及び素子分離構造と、

前記素子分離構造の上部に備えられる分離パターンと、

前記分離パターンの両端に備えられるコンタクトプラグと

を含むことを特徴とする半導体素子。

【請求項2】

前記素子分離構造は、

前記半導体基板で前記メインゲートに隣接して備えられる分離ゲート、又は

前記半導体基板が食刻されたトレンチに埋め込まれた絶縁膜を含む素子分離膜のうち1つ以上を含むことを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記分離パターンは酸化膜と相違する食刻選択比を有する絶縁膜であって、窒化膜、シリコン酸化窒化膜、非晶質炭素を含むことを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記メインゲート及び前記分離ゲートは、

半導体基板に所定の深さに形成されたリセスと、

前記リセスの下部に埋め込まれたゲート導電層と、

前記リセスで前記ゲート導電層の上部に備えられるキャッピング膜と

を含むことを特徴とする請求項2に記載の半導体素子。

【請求項5】

前記分離パターンの下部は、前記リセスの上部に埋め込まれていることを特徴とする請求項4に記載の半導体素子。

【請求項6】

前記メインゲート及び前記分離ゲートは、

2つのメインゲートと1つの分離ゲートとが交互に備えられることを特徴とする請求項2に記載の半導体素子。

【請求項7】

前記2つのメインゲートの間のビットラインコンタクト領域の上部に備えられるビットラインコンタクトと、

前記ビットラインコンタクトの上部に備えられるビットラインと

をさらに含むことを特徴とする請求項6に記載の半導体素子。

【請求項8】

前記コンタクトプラグは、格納電極コンタクトプラグを含むことを特徴とする請求項1に記載の半導体素子。

【請求項9】

半導体基板にラインタイプに形成された活性領域と、

前記半導体基板に前記活性領域に対し斜めに延長されたメインゲート及び分離ゲートと、

前記分離ゲートの上部に備えられるラインタイプの分離パターンと、

前記分離パターンの両端に沿って延長されるコンタクトプラグと

を含むことを特徴とする半導体素子。

【請求項10】

前記メインゲート及び前記分離ゲートは、

2つのメインゲートと1つの分離ゲートとが交互に備えられることを特徴とする請求項9に記載の半導体素子。

【請求項11】

前記2つのメインゲートの間に備えられるビットラインコンタクトプラグをさらに含むことを特徴とする請求項10に記載の半導体素子。

【請求項12】

前記ビットラインコンタクトプラグの上部に備えられ、前記メインゲートと交差しながら延長されたラインタイプのビットラインをさらに含むことを特徴とする請求項11に記載の半導体素子。

【請求項13】

前記ビットラインは、前記メインゲートと垂直に交差することを特徴とする請求項12に記載の半導体素子。

【請求項14】

前記コンタクトプラグは、格納電極コンタクトプラグを含むことを特徴とする請求項9に記載の半導体素子。

【請求項15】

半導体基板にメインゲート及び素子分離構造を形成するステップと、

前記素子分離構造の上部に分離パターンを形成するステップと、

前記分離パターンの両端にコンタクトプラグを形成するステップと

を含むことを特徴とする半導体素子の形成方法。

【請求項16】

前記素子分離構造を形成するステップは、

前記半導体基板で前記メインゲートに隣接して備えられる分離ゲートを形成するステップ、又は

前記半導体基板が食刻されたトレンチに埋め込まれた絶縁膜を含む素子分離膜を形成するステップのうち1つ以上を含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項17】

前記分離パターンを形成するステップは、

前記半導体基板の上部に層間絶縁膜を形成するステップと、

前記分離ゲートを境界に前記層間絶縁膜を食刻するステップと、

前記食刻された層間絶縁膜を含む半導体基板の全面に分離パターン層を蒸着するステップと、

前記分離パターン層をエッチバックして前記層間絶縁膜の側壁に分離パターンを残留させるステップと、

前記層間絶縁膜を除去するステップと

を含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項18】

前記メインゲート及び前記分離ゲートを形成するステップは、

半導体基板に所定の深さにリセスを形成するステップと、

前記リセスの下部にゲート導電層を埋め込むステップと、

前記リセスで前記ゲート導電層の上部にキャッピング膜を埋め込むステップと

を含むことを特徴とする請求項16に記載の半導体素子の形成方法。

【請求項19】

前記分離パターンの下部を前記リセスの上部に埋め込んで形成することを特徴とする請求項18に記載の半導体素子の形成方法。

【請求項20】

前記キャッピング膜を所定の深さに食刻するステップと、

前記食刻されたキャッピング膜を含む半導体基板の上部に分離パターン層を形成するステップと

を含むことを特徴とする請求項19に記載の半導体素子の形成方法。

【請求項21】

前記コンタクトプラグを形成するステップは、

前記分離パターンを含む半導体基板に層間絶縁膜を形成するステップと、

前記メインゲートを境界に前記層間絶縁膜を食刻してコンタクトホールを形成するステップと、

前記コンタクトホールを含む半導体基板の全面に導電物質を蒸着するステップと、

前記層間絶縁膜の上部の前記導電物質を平坦化食刻するステップと

を含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項22】

前記分離パターンは酸化膜と相違する食刻選択比を有する絶縁膜であって、窒化膜、シリコン酸化窒化膜、非晶質炭素を含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項23】

前記メインゲート及び前記分離ゲートを形成するステップは、

2つのメインゲートと1つの分離ゲートとが交互に備えられるようにすることを特徴とする請求項16に記載の半導体素子の形成方法。

【請求項24】

前記2つのメインゲートの間のビットラインコンタクト領域の上部にビットラインコンタクトを形成するステップと、

前記ビットラインコンタクトの上部にビットラインを形成するステップと

をさらに含むことを特徴とする請求項23に記載の半導体素子の形成方法。

【請求項25】

前記コンタクトプラグは、格納電極コンタクトプラグを含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項26】

半導体基板にラインタイプの活性領域を形成するステップと、

前記半導体基板に前記活性領域に対し斜めに延長されたメインゲート及び分離ゲートをラインタイプに形成するステップと、

前記分離ゲートの上部にラインタイプの分離パターンを形成するステップと、

前記分離パターンの両端に沿って延長されるコンタクトプラグを形成するステップと

を含むことを特徴とする半導体素子の形成方法。

【請求項27】

前記メインゲート及び前記分離ゲートを形成するステップは、

2つのメインゲートと1つの分離ゲートとが交互に備えられるようにすることを特徴とする請求項26に記載の半導体素子の形成方法。

【請求項28】

前記2つのメインゲートの間にビットラインコンタクトプラグを形成するステップをさらに含むことを特徴とする請求項27に記載の半導体素子の形成方法。

【請求項29】

前記ビットラインコンタクトプラグの上部に備えられ前記ビットラインコンタクトプラグと連結され、前記メインゲートと交差しながら延長されたビットラインをラインタイプに形成するステップをさらに含むことを特徴とする請求項28に記載の半導体素子の形成方法。

【請求項30】

前記ビットラインは、前記メインゲートと垂直に交差することを特徴とする請求項26に記載の半導体素子の形成方法。

【請求項31】

前記コンタクトプラグは、格納電極コンタクトプラグを含むことを特徴とする請求項26に記載の半導体素子の形成方法。

【請求項1】

半導体基板に備えられるメインゲート及び素子分離構造と、

前記素子分離構造の上部に備えられる分離パターンと、

前記分離パターンの両端に備えられるコンタクトプラグと

を含むことを特徴とする半導体素子。

【請求項2】

前記素子分離構造は、

前記半導体基板で前記メインゲートに隣接して備えられる分離ゲート、又は

前記半導体基板が食刻されたトレンチに埋め込まれた絶縁膜を含む素子分離膜のうち1つ以上を含むことを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記分離パターンは酸化膜と相違する食刻選択比を有する絶縁膜であって、窒化膜、シリコン酸化窒化膜、非晶質炭素を含むことを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記メインゲート及び前記分離ゲートは、

半導体基板に所定の深さに形成されたリセスと、

前記リセスの下部に埋め込まれたゲート導電層と、

前記リセスで前記ゲート導電層の上部に備えられるキャッピング膜と

を含むことを特徴とする請求項2に記載の半導体素子。

【請求項5】

前記分離パターンの下部は、前記リセスの上部に埋め込まれていることを特徴とする請求項4に記載の半導体素子。

【請求項6】

前記メインゲート及び前記分離ゲートは、

2つのメインゲートと1つの分離ゲートとが交互に備えられることを特徴とする請求項2に記載の半導体素子。

【請求項7】

前記2つのメインゲートの間のビットラインコンタクト領域の上部に備えられるビットラインコンタクトと、

前記ビットラインコンタクトの上部に備えられるビットラインと

をさらに含むことを特徴とする請求項6に記載の半導体素子。

【請求項8】

前記コンタクトプラグは、格納電極コンタクトプラグを含むことを特徴とする請求項1に記載の半導体素子。

【請求項9】

半導体基板にラインタイプに形成された活性領域と、

前記半導体基板に前記活性領域に対し斜めに延長されたメインゲート及び分離ゲートと、

前記分離ゲートの上部に備えられるラインタイプの分離パターンと、

前記分離パターンの両端に沿って延長されるコンタクトプラグと

を含むことを特徴とする半導体素子。

【請求項10】

前記メインゲート及び前記分離ゲートは、

2つのメインゲートと1つの分離ゲートとが交互に備えられることを特徴とする請求項9に記載の半導体素子。

【請求項11】

前記2つのメインゲートの間に備えられるビットラインコンタクトプラグをさらに含むことを特徴とする請求項10に記載の半導体素子。

【請求項12】

前記ビットラインコンタクトプラグの上部に備えられ、前記メインゲートと交差しながら延長されたラインタイプのビットラインをさらに含むことを特徴とする請求項11に記載の半導体素子。

【請求項13】

前記ビットラインは、前記メインゲートと垂直に交差することを特徴とする請求項12に記載の半導体素子。

【請求項14】

前記コンタクトプラグは、格納電極コンタクトプラグを含むことを特徴とする請求項9に記載の半導体素子。

【請求項15】

半導体基板にメインゲート及び素子分離構造を形成するステップと、

前記素子分離構造の上部に分離パターンを形成するステップと、

前記分離パターンの両端にコンタクトプラグを形成するステップと

を含むことを特徴とする半導体素子の形成方法。

【請求項16】

前記素子分離構造を形成するステップは、

前記半導体基板で前記メインゲートに隣接して備えられる分離ゲートを形成するステップ、又は

前記半導体基板が食刻されたトレンチに埋め込まれた絶縁膜を含む素子分離膜を形成するステップのうち1つ以上を含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項17】

前記分離パターンを形成するステップは、

前記半導体基板の上部に層間絶縁膜を形成するステップと、

前記分離ゲートを境界に前記層間絶縁膜を食刻するステップと、

前記食刻された層間絶縁膜を含む半導体基板の全面に分離パターン層を蒸着するステップと、

前記分離パターン層をエッチバックして前記層間絶縁膜の側壁に分離パターンを残留させるステップと、

前記層間絶縁膜を除去するステップと

を含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項18】

前記メインゲート及び前記分離ゲートを形成するステップは、

半導体基板に所定の深さにリセスを形成するステップと、

前記リセスの下部にゲート導電層を埋め込むステップと、

前記リセスで前記ゲート導電層の上部にキャッピング膜を埋め込むステップと

を含むことを特徴とする請求項16に記載の半導体素子の形成方法。

【請求項19】

前記分離パターンの下部を前記リセスの上部に埋め込んで形成することを特徴とする請求項18に記載の半導体素子の形成方法。

【請求項20】

前記キャッピング膜を所定の深さに食刻するステップと、

前記食刻されたキャッピング膜を含む半導体基板の上部に分離パターン層を形成するステップと

を含むことを特徴とする請求項19に記載の半導体素子の形成方法。

【請求項21】

前記コンタクトプラグを形成するステップは、

前記分離パターンを含む半導体基板に層間絶縁膜を形成するステップと、

前記メインゲートを境界に前記層間絶縁膜を食刻してコンタクトホールを形成するステップと、

前記コンタクトホールを含む半導体基板の全面に導電物質を蒸着するステップと、

前記層間絶縁膜の上部の前記導電物質を平坦化食刻するステップと

を含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項22】

前記分離パターンは酸化膜と相違する食刻選択比を有する絶縁膜であって、窒化膜、シリコン酸化窒化膜、非晶質炭素を含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項23】

前記メインゲート及び前記分離ゲートを形成するステップは、

2つのメインゲートと1つの分離ゲートとが交互に備えられるようにすることを特徴とする請求項16に記載の半導体素子の形成方法。

【請求項24】

前記2つのメインゲートの間のビットラインコンタクト領域の上部にビットラインコンタクトを形成するステップと、

前記ビットラインコンタクトの上部にビットラインを形成するステップと

をさらに含むことを特徴とする請求項23に記載の半導体素子の形成方法。

【請求項25】

前記コンタクトプラグは、格納電極コンタクトプラグを含むことを特徴とする請求項15に記載の半導体素子の形成方法。

【請求項26】

半導体基板にラインタイプの活性領域を形成するステップと、

前記半導体基板に前記活性領域に対し斜めに延長されたメインゲート及び分離ゲートをラインタイプに形成するステップと、

前記分離ゲートの上部にラインタイプの分離パターンを形成するステップと、

前記分離パターンの両端に沿って延長されるコンタクトプラグを形成するステップと

を含むことを特徴とする半導体素子の形成方法。

【請求項27】

前記メインゲート及び前記分離ゲートを形成するステップは、

2つのメインゲートと1つの分離ゲートとが交互に備えられるようにすることを特徴とする請求項26に記載の半導体素子の形成方法。

【請求項28】

前記2つのメインゲートの間にビットラインコンタクトプラグを形成するステップをさらに含むことを特徴とする請求項27に記載の半導体素子の形成方法。

【請求項29】

前記ビットラインコンタクトプラグの上部に備えられ前記ビットラインコンタクトプラグと連結され、前記メインゲートと交差しながら延長されたビットラインをラインタイプに形成するステップをさらに含むことを特徴とする請求項28に記載の半導体素子の形成方法。

【請求項30】

前記ビットラインは、前記メインゲートと垂直に交差することを特徴とする請求項26に記載の半導体素子の形成方法。

【請求項31】

前記コンタクトプラグは、格納電極コンタクトプラグを含むことを特徴とする請求項26に記載の半導体素子の形成方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−175111(P2012−175111A)

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願番号】特願2012−36410(P2012−36410)

【出願日】平成24年2月22日(2012.2.22)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願日】平成24年2月22日(2012.2.22)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

[ Back to top ]