半導体素子及びその製造方法

【課題】 オーミック電極とバリアメタル層の密着強度を向上させる。

【解決手段】 半導体素子の製造方法は、(a1)半導体積層構造を準備する工程と、(b1)前記半導体積層構造上にオーミック電極層を成膜する工程と、(c1)前記オーミック電極層上にAuを含む接着層を成膜する工程と、(d1)前記工程(c1)から大気開放せずにバリアメタル層を成膜する工程とを含む。

【解決手段】 半導体素子の製造方法は、(a1)半導体積層構造を準備する工程と、(b1)前記半導体積層構造上にオーミック電極層を成膜する工程と、(c1)前記オーミック電極層上にAuを含む接着層を成膜する工程と、(d1)前記工程(c1)から大気開放せずにバリアメタル層を成膜する工程とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体基板上にn型層とp型層とを形成した発光ダイオード(LED)においては、n型層、p型層にオーミック電極を形成し、順方向電流を流すことにより発光を生じさせる。p型層から供給される正孔とn型層から供給される電子が発光性再結合を行うことにより、所定波長の発光が生じる。発光はあらゆる方向に向かう。

【0003】

オーミック電極は通常加熱による合金化処理を行なって形成するので、オーミック電極は一般的に反射率が低い。広い面積に均一に電流を供給し、かつオーミック電極による光吸収を抑制するために、光取り出し面側のオーミック電極はパターニングすることが多い。表面側から出力光を取り出す場合、裏面側に向かった発光は、有効に利用できないことが多い。外部発光効率を向上させるために、反射構造を形成することが行われている。

【0004】

図4(A)および4(B)は、特開平7−273368号の従来の技術に開示されている2種類の反射構造を示す。

【0005】

図4(A)においては、LEDを形成した半導体基板102の裏面に酸化シリコン等の透明絶縁膜109を形成し、例えば行列状に分布した領域を残すようにパターニングする。表面側にオーミック電極107を形成し、裏面側に透明絶縁膜109を覆うようにオーミック電極108を形成する。オーミック電極107,108の合金化処理を行なっても、オーミック電極108と透明絶縁膜109の界面および透明絶縁膜109と半導体基板102の界面は乱れず、反射面が形成される。

【0006】

図4(B)においては、表面側にオーミック電極107を形成し、裏面側にオーミック電極108のパターンを形成した状態で、オーミック電極の合金化処理を行なう。その後、オーミック電極108のパターンを覆って、半導体基板裏面上に高反射率のAg等の反射金属層110を形成する。反射金属層110形成後は、反射金属層110と半導体基板102の界面を保護するように、加熱処理は避ける。反射金属層110と半導体基板102の界面は高反射率の反射面を提供する。

【0007】

LEDをパッケージやサブマウントに実装する際、発光層側を下にしてパッケージやサブマウントに実装するジャンクションダウン構造がある。発光層からの発熱の放熱効率を向上することが容易になる。この場合、反射構造を形成しようとすると、発光層側に反射構造、オーミック電極を形成し、その上に半田、共晶合金などの接合層を形成することになる。LEDをパッケージやサブマウントに実装する際、接合層は加熱溶融される。この時、接合層の構成元素が拡散し、LEDの性能を劣化させる問題が生じる。拡散を防止するため、バリアメタル層が用いられる。

【0008】

図5は、特開2007−317771号に開示されたジャンクションダウン型発光ダイオードの構成を示す。半導体基板111の表面(図では下面)上に発光層112が形成される。半導体基板111は、発光層112で発光する光を透過させるように透光性を有する半導体で形成される。発光層112表面(下面)上に発光波長で透明な絶縁膜113が形成され、電極形成を可能にするようにパターニングされる。パターニングされた絶縁膜113を介して、発光層112の上に、p側オーミック電極114が形成される。p側オーミック電極114の上には、バリアメタル層115、密着層115a、接合層117が積層される。また、半導体基板111の裏面(上面)上にn側オーミック電極116が形成される。

【0009】

絶縁膜113は、SiO2 ,Si3 N4 等から構成され、反射率が最大となる厚さ(SiO2 の場合には、例えば約100nm)に形成される。絶縁膜113は、発光層112とp型電極114のオーミック接触を可能にするように、パターニングにより一部が除去される。絶縁膜113の存在する領域では、発光層112から下方に向かう光が、絶縁膜113、合金化されていないp側オーミック電極114で反射され、上方に向かって効率的に取り出される。

【0010】

p側オーミック電極114は、例えば100〜400nmの厚さのAuZn膜で形成され、絶縁膜113が形成されない領域で、発光層112の下面とオーミック接触する。n側オーミック電極116は、Au−Ge−Ni膜で形成される。

【0011】

バリアメタル層115は、例えば、電子ビーム(EB)蒸着,スパッタリング等によりTaN/Taの周期構造を有する複合バリアメタル層で形成される。バリアメタル層115は、p側オーミック電極114と接合層117の間の拡散を防止する障壁を形成する。密着層115aは、バリアメタル層115と接合層117の間の密着性を向上する。

【0012】

p側オーミック電極114は、チップ毎に、チップ分離後のチップ外周部となるべき境界線より内側の領域に成膜される。バリアメタル層115、密着層115a、接合層117は、その形状がp型電極114より僅かに小さくパターニングされる。ダイシングストリートの金属層が除去されていることにより、ダイシングブレードの目詰まりが低減できる。

【0013】

【特許文献1】特開平7−273368号公報

【特許文献2】特開2007−317771号公報

【発明の開示】

【発明が解決しようとする課題】

【0014】

上述したジャンクションダウン構造を有する半導体の製造工程においては、いくつかの問題点がある。

【0015】

例えば、反射絶縁膜パターンを形成し、ダイシングストリートライン上にレジストマスクを形成した半導体基板上に、オーミック電極、バリアメタル層を積層させ、レジストマスク上の金属層をリフトオフした状態でオーミック接触をとるための熱処理を施すと、絶縁層とバリアメタル層の熱膨張係数やヤング率などが大きく異なるため、絶縁層とオーミック電極の界面に浮き(空洞)が生じてしまい、反射率が低下するという問題がある。

【0016】

このような問題を避けるために、オーミック電極層を蒸着させた後に一度炉内からウェハを取り出し、レジストを除去し、オーミック電極の熱処理を行い、必要に応じてさらにレジストマスクを形成した後で、バリアメタル層を蒸着させる方法がある。しかし、この方法だと、オーミック電極層とバリアメタル層との界面の密着強度が弱くなるという別の問題がある。

【0017】

本発明の目的は、オーミック電極とバリアメタル層の密着強度を向上させた半導体素子の製造方法を提供することである。

【0018】

本発明の目的は、オーミック電極とバリアメタル層の密着強度を向上させた半導体素子を提供することである。

【課題を解決するための手段】

【0019】

本発明の一観点によれば、半導体素子の製造方法は、(a1)半導体積層構造を準備する工程と、(b1)前記半導体積層構造上にオーミック電極層を成膜する工程と、(c1)前記オーミック電極層上にAuを含む接着層を成膜する工程と、(d1)前記工程(c1)から大気開放せずにバリアメタル層を成膜する工程とを含む。

【0020】

本発明の他の観点によれば、半導体素子は、半導体積層構造と、前記半導体積層構造上に形成されるオーミック電極と、前記オーミック電極上に形成されるAuを含む接着層と、前記接着層上に形成されるバリアメタル層とを有する。

【発明の効果】

【0021】

本発明によれば、オーミック電極とバリアメタル層の密着強度を向上させることができる。

【発明を実施するための最良の形態】

【0022】

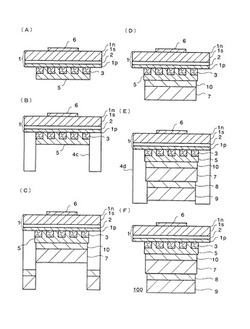

図1(A)〜(G)及び図2(A)〜(F)は、本発明の実施例による半導体素子100の製造工程を示す概略的な断面図である。

【0023】

半導体基板1sは、AlAs混昌比0.2以上のAlGaAs基板であり、該半導体基板1s上には、ダブルヘテロ(DH)構造のAl0.02GaAs活性層を有する発光層2が形成されている。図1(A)に示すように、半導体基板1sと発光層2を含む半導体積層構造1の主表面のうちの発光層2に近い面(本実施例ではp型層側、以下、半導体積層構造1のp型層側表面1pと呼ぶ)に、SiO2からなる絶縁膜3を1000Åの厚さで蒸着する。絶縁膜3を設けることにより、発光層2からの発光を半導体基板1s側へ反射して、半導体基板1s側から効率よく取り出すことができる。

【0024】

次に、絶縁膜3上にレジスト膜を塗布して露光、現像でレジストパターンを形成し、バッファードフッ酸(BHF)に2分間浸すことによりウェットエッチングを行い、図1(B)に示すように、絶縁膜3の一部を取り去り、半導体積層構造1の表面と後に形成するp型オーミック電極5とが導通が取れるようにする。

【0025】

続いて、ダイシングストリートとなる部分へのメタル蒸着を防ぐために、図1(C)に示すように、レジスト膜を塗布して露光、現像を行ってレジストパターン4aを形成する。なお、レジストは、例えば、エレクトロニックマテリアルズ社製のAZ5214を用いることができる。

【0026】

次に、BHFに一瞬浸し、半導体積層構造1表面の酸化膜を除去して、図1(C)に示すように、スパッタリング等によりAuZn(Zn含有量5重量%)を3000Åの厚さで真空蒸着しp型オーミック電極層5を形成する。なお、オーミック電極層5を構成するAnZnのZn含有量は、高い反射率、かつ十分なオーミック接触を形成することができる含有量とする。

【0027】

その後、半導体積層構造1のp型層側表面1pにリフトオフテープを貼り付けて、剥がすことにより大部分のレジストパターン4a及びその上のp型オーミック電極層5を除去する。続いて、アセトン超音波洗浄を3分間ずつ3回行うことにより、図1(D)に示すように、完全にレジストパターン4aを除去する。

【0028】

次に、図1(E)に示すように、ダイシングストリートとなる部分の絶縁膜3をBHFに2分間浸すことによりウェットエッチングを行い、除去する。

【0029】

次に、半導体積層構造1の主表面のうちの発光層2に遠い面(本実施例ではn型層側、以下、半導体積層構造1のn型層側表面1nと呼ぶ)に、レジストパターン膜を塗布して90℃でベークした後、電極用マスクを用いて露光を行い、さらに110℃にて反転ベーク、全面露光、AZデベロッパーを1:1にて純水で希釈させた現像液に70秒間浸してパターニングを行い、図1(F)に示すレジストパターン4bを形成する。なお、レジストは、例えば、エレクトロニックマテリアルズ社製のAZ5214を用いることができる。

【0030】

その後、BHFに30秒間浸すことによりウェットエッチングを行い、半導体積層構造1のn型層側表面1nの酸化膜を除去した後、AuGeNiを半導体積層構造1のn型層側表面1nに蒸着させ、図1(G)に示すように、n型オーミック電極層6を形成する。

【0031】

次に、半導体積層構造1のn型層側表面1nにリフトオフテープを貼り付けて、剥がすことにより大部分のレジストパターン4b及びその上のn型オーミック電極層6を除去する。続いて、アセトン超音波洗浄を3分間ずつ3回行うことにより、完全にレジストパターン4bを除去して、図2(A)に示す状態とする。p型及びn型オーミック電極5、6のオーミック接触を形成するために、熱処理を行う。この熱処理は、図2(A)に示す状態のウェハ(半導体積層構造1)を、窒素雰囲気にした合金炉内において400℃まで昇温させてオーミック電極を下地半導体と合金化し、100℃まで冷却させた後に、合金炉から取り出すことにより行う。

【0032】

次に、半導体積層構造1のp型層側表面1pに、レジスト膜を塗布して100℃でベークした後、電極用マスクを用いて露光を行い、さらに120℃にて反転ベーク、全面露光、現像液(例えば、AZ−300MIF)に150秒間浸してパターニングを行い、図2(B)に示すダイシングストリートとなる部分へのメタル蒸着を防ぐためのレジストパターン4cを形成する。なお、レジストは、例えば、エレクトロニックマテリアルズ社製のAZ5200を用いることができる。

【0033】

図2(C)に示すように、p型オーミック電極5の表面にスパッタリング等によりAuZn(Zn含有量5重量%)を1000Åの厚さで真空蒸着させ、接着層10を形成する。続けて、半導体積層構造1をスパッタリング装置等から取り出すことなく、スパッタリング等により接着層10の表面にTaNを2000Å、Taを1000Å、TaNを2000Åの厚さで順次真空蒸着させ、複合バリアメタル層7を形成する。複合バリアメタル層7を設けることにより、共晶層9の元素のオーミック電極への熱拡散を防止することができる。TaNの窒化率はバリア性を有し、かつAuを含む層と高い密着性を得ることができるように設定する。その後、レジストパターン4cを完全に除去できるまでAZリムーバ超音波洗浄を行い、図2(D)に示す状態とする。

【0034】

図2(E)に示すように、再度レジストパターン4d(エレクトロニックマテリアルズ社製のAZ5200等)を形成する。その後、Al、Ta、Auの積層からなる密着向上層8を蒸着させ、続いて、AuSnからなる共晶材を蒸着し、共晶層9を形成する。共晶層9は、半導体発光素子の配線基板等への実装に好適に用いられる。最後に、レジストパターン4d及びその上の密着向上層8及び共晶層9を完全に除去できるまでAZリムーバ超音波洗浄を行い、図2(F)に示す状態とする。

【0035】

図3は、本発明の実施例による半導体素子100と比較例による半導体素子の歩留まり及びダイシェア強度を比較結果を示す表である。

【0036】

比較例による半導体素子は、本発明の実施例による半導体素子100と異なり、図2(B)に示す状態で、接着層10を形成することなく、厚さ3000ÅのAuZnからなるp型オーミック電極5の表面にTaN(窒化率0.7、ここで窒化率は金属原子数と窒素原子数の比を示す)を2000Å、Taを1000Å、TaN(窒化率0.7)を2000Åの厚さで順次真空蒸着させ、複合バリアメタル層7を形成したものである。それ以外は本発明の実施例による半導体素子100と同様の材料及び条件で作製した。

【0037】

図3(A)は、本発明の実施例による半導体素子100と比較例による半導体素子の歩留まりを測定した結果を示す表である。

【0038】

この表は、ブルーシートに貼り付けたウェハをダイシング工程によりチップ分離させ、分離したチップをブルーシートから剥がした時、ブルーシートにメタルが残っているサンプルを不良とし、歩留まりを測定したものである。

【0039】

比較例による半導体素子では、歩留まりが10%以下なのに対して、本実施例による半導体素子100では歩留まりが100%ととなり、飛躍的に向上していることがわかった。

【0040】

また、電極界面の密着性を評価するために実施例による半導体素子100及び比較例による半導体素子のそれぞれのダイシェア強度を測定した。図3(B)は、その結果を示す表である。

【0041】

なお、ダイシェア強度とは半導体素子をパッケージや配線基板等の実装面に実装させた状態において側面より針を押し当て、接合された半導体素子をはく離させるために必要な強度のことである。多層電極構造の密着性と共晶接合部分の強度が十分にあれば、素子破壊するまでの強度を測定することとなる。

【0042】

比較例による半導体素子では、剥離界面がオーミック電極とバリアメタル界面に限られていたのに対し、実施例による半導体素子100では、素子破壊が起きていることがわかった。これらのことから、実施例による半導体素子100では、オーミック電極(p型オーミック電極5)とバリアメタル電極(複合バリアメタル層7)の界面の密着強度が十分であり、比較例のものに比べて飛躍的に向上したことがわかる。

【0043】

なお、実施例による半導体素子100及び比較例による半導体素子のそれぞれに対して2次イオン質量分析(SIMS)を行ったところ、比較例による半導体素子においてバリアメタル層(実施例の複合バリアメタル層7に相当)とオーミック電極(実施例のp型オーミック電極5に相当)との界面にカーボンをより多く含む層があることがわかった。これに対して、実施例による半導体素子100においては、p型オーミック電極(AuZn層)5と接着層(AuZn層)10との界面にカーボンをより多く含む層があることがわかった。

【0044】

以上、本発明の実施例によれば、オーミック電極膜(p型オーミック電極5)の成膜後のレジスト除去工程後に、オーミック電極膜(p型オーミック電極5)の上に蒸着装置において接着層10を形成して、該蒸着装置から取り出さずに複合バリアメタル層7を形成することにより、オーミック電極5とバリアメタル層7の密着強度を飛躍的に向上させることができる。

【0045】

また、本発明の実施例によれば、オーミック電極膜(p型オーミック電極5)の成膜後の熱処理の後に、オーミック電極膜(p型オーミック電極5)の上に蒸着装置において接着層10を形成して、該蒸着装置から取り出さずに複合バリアメタル層7を形成することにより、オーミック電極5とバリアメタル層7の密着強度を飛躍的に向上させることができるとともに、絶縁膜3とオーミック電極5の界面に浮きが生じることを防止できる。

【0046】

つまり、本発明の実施例によれば、オーミック電極膜5の成膜後に大気開放してフォトリソグラフィ工程や合金化工程を経た場合も、Auを含む金属からなる接着層10を成膜し、その後、大気開放せずにバリアメタル層7を成膜することにより、接着層10を介してオーミック電極5とバリアメタル層7の密着強度を飛躍的に向上させることができる。

【0047】

なお、上述の実施例では、実装面側の導電型をp型とし、p型オーミック電極5をAuZnで形成したが、p型オーミック電極5はAuBeで形成したり、実装面側にp型オーミック電極5の代わりにn型電極として、AuGeやAuSnなどで形成するようにしてもよい。すなわち、実装面側のオーミック電極5はAuを含む材料で形成し、その上に形成する接着層10もAuを含む材料で形成する。オーミック電極5及び接着層10の双方をAuを含む材料で形成することによりなじみがよくなり、密着性が向上する。オーミック電極5及び接着層10の双方をAuを含む材料で構成すれば、同一材料でなくてもよいが、本実施例のように同一材料で形成することにより、密着性はさらに向上する。

【0048】

また、本発明の実施例はオーミック電極とバリアメタルの密着性を向上することを目的としていることから、絶縁膜3はSiO2に限らず、SiNXでもよいし、省略してもよい。絶縁膜3を省略する場合は、図1(A)及び図1(B)を参照して説明した絶縁膜3の形成工程及び図1(E)を参照して説明したダイシングストリート部分の絶縁膜除去工程が不要となる。

【0049】

また、上述の実施例では、複合バリアメタル層7をTaN/Ta/TaNの積層で形成したが、共晶材料の拡散を防止することが可能なTiNやTiWN等の窒化物で形成してもよい。なお、バリアメタル層7は、上記の窒化物の積層でもよいし単層で形成してもよい。

また、接着層10とバリアメタル層7との間に、他の層を挟んでもよいが、その場合においても、接着層10の成膜からバリアメタル層7の成膜までは大気開放せずに行うものとする。

【0050】

また、接着層10とバリアメタル層7は、異なる蒸着装置で成膜されてもよいが、その場合においても、接着層10の成膜からバリアメタル層7の成膜までは大気開放せずに行うものとする。

【0051】

なお、発光層2の材料はAlGaAsに限らず、例えば、AlGaInP、GaN等であってもよいが、AlGaAs系半導体やAlGaInP系半導体は、電極とオーミック接触を形成する際に合金化工程が必要であるため、本発明を好適に用いることができる。また、密着向上層8は省略あるいは他の材料によって構成することができる。さらに、共晶材は、共晶層9として半導体素子100の一部とするのではなく、半導体素子100を取り付ける際に底面に補充するようにしてもよい。

【0052】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【図面の簡単な説明】

【0053】

【図1】本発明の実施例による半導体素子100の製造工程を示す概略的な断面図である。

【図2】本発明の実施例による半導体素子100の製造工程を示す概略的な断面図である。

【図3】本発明の実施例による半導体素子100と比較例による半導体素子の歩留まり及びダイシェア強度を比較結果を示す表である。

【図4】従来の半導体素子の構成を示す概略的な断面図である。

【図5】従来の半導体素子の構成を示す概略的な断面図である。

【符号の説明】

【0054】

1…半導体積層構造、2…発光層、3…絶縁膜(SiO2)、4…レジスト、5…p型オーミック電極(AuZn)、6…n型オーミック電極(AuGeNi)、7…複合バリアメタル層(TaN/Ta/TaN)、8…密着向上層、9…共晶層、10…接着層(AuZn)、100…半導体素子

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体基板上にn型層とp型層とを形成した発光ダイオード(LED)においては、n型層、p型層にオーミック電極を形成し、順方向電流を流すことにより発光を生じさせる。p型層から供給される正孔とn型層から供給される電子が発光性再結合を行うことにより、所定波長の発光が生じる。発光はあらゆる方向に向かう。

【0003】

オーミック電極は通常加熱による合金化処理を行なって形成するので、オーミック電極は一般的に反射率が低い。広い面積に均一に電流を供給し、かつオーミック電極による光吸収を抑制するために、光取り出し面側のオーミック電極はパターニングすることが多い。表面側から出力光を取り出す場合、裏面側に向かった発光は、有効に利用できないことが多い。外部発光効率を向上させるために、反射構造を形成することが行われている。

【0004】

図4(A)および4(B)は、特開平7−273368号の従来の技術に開示されている2種類の反射構造を示す。

【0005】

図4(A)においては、LEDを形成した半導体基板102の裏面に酸化シリコン等の透明絶縁膜109を形成し、例えば行列状に分布した領域を残すようにパターニングする。表面側にオーミック電極107を形成し、裏面側に透明絶縁膜109を覆うようにオーミック電極108を形成する。オーミック電極107,108の合金化処理を行なっても、オーミック電極108と透明絶縁膜109の界面および透明絶縁膜109と半導体基板102の界面は乱れず、反射面が形成される。

【0006】

図4(B)においては、表面側にオーミック電極107を形成し、裏面側にオーミック電極108のパターンを形成した状態で、オーミック電極の合金化処理を行なう。その後、オーミック電極108のパターンを覆って、半導体基板裏面上に高反射率のAg等の反射金属層110を形成する。反射金属層110形成後は、反射金属層110と半導体基板102の界面を保護するように、加熱処理は避ける。反射金属層110と半導体基板102の界面は高反射率の反射面を提供する。

【0007】

LEDをパッケージやサブマウントに実装する際、発光層側を下にしてパッケージやサブマウントに実装するジャンクションダウン構造がある。発光層からの発熱の放熱効率を向上することが容易になる。この場合、反射構造を形成しようとすると、発光層側に反射構造、オーミック電極を形成し、その上に半田、共晶合金などの接合層を形成することになる。LEDをパッケージやサブマウントに実装する際、接合層は加熱溶融される。この時、接合層の構成元素が拡散し、LEDの性能を劣化させる問題が生じる。拡散を防止するため、バリアメタル層が用いられる。

【0008】

図5は、特開2007−317771号に開示されたジャンクションダウン型発光ダイオードの構成を示す。半導体基板111の表面(図では下面)上に発光層112が形成される。半導体基板111は、発光層112で発光する光を透過させるように透光性を有する半導体で形成される。発光層112表面(下面)上に発光波長で透明な絶縁膜113が形成され、電極形成を可能にするようにパターニングされる。パターニングされた絶縁膜113を介して、発光層112の上に、p側オーミック電極114が形成される。p側オーミック電極114の上には、バリアメタル層115、密着層115a、接合層117が積層される。また、半導体基板111の裏面(上面)上にn側オーミック電極116が形成される。

【0009】

絶縁膜113は、SiO2 ,Si3 N4 等から構成され、反射率が最大となる厚さ(SiO2 の場合には、例えば約100nm)に形成される。絶縁膜113は、発光層112とp型電極114のオーミック接触を可能にするように、パターニングにより一部が除去される。絶縁膜113の存在する領域では、発光層112から下方に向かう光が、絶縁膜113、合金化されていないp側オーミック電極114で反射され、上方に向かって効率的に取り出される。

【0010】

p側オーミック電極114は、例えば100〜400nmの厚さのAuZn膜で形成され、絶縁膜113が形成されない領域で、発光層112の下面とオーミック接触する。n側オーミック電極116は、Au−Ge−Ni膜で形成される。

【0011】

バリアメタル層115は、例えば、電子ビーム(EB)蒸着,スパッタリング等によりTaN/Taの周期構造を有する複合バリアメタル層で形成される。バリアメタル層115は、p側オーミック電極114と接合層117の間の拡散を防止する障壁を形成する。密着層115aは、バリアメタル層115と接合層117の間の密着性を向上する。

【0012】

p側オーミック電極114は、チップ毎に、チップ分離後のチップ外周部となるべき境界線より内側の領域に成膜される。バリアメタル層115、密着層115a、接合層117は、その形状がp型電極114より僅かに小さくパターニングされる。ダイシングストリートの金属層が除去されていることにより、ダイシングブレードの目詰まりが低減できる。

【0013】

【特許文献1】特開平7−273368号公報

【特許文献2】特開2007−317771号公報

【発明の開示】

【発明が解決しようとする課題】

【0014】

上述したジャンクションダウン構造を有する半導体の製造工程においては、いくつかの問題点がある。

【0015】

例えば、反射絶縁膜パターンを形成し、ダイシングストリートライン上にレジストマスクを形成した半導体基板上に、オーミック電極、バリアメタル層を積層させ、レジストマスク上の金属層をリフトオフした状態でオーミック接触をとるための熱処理を施すと、絶縁層とバリアメタル層の熱膨張係数やヤング率などが大きく異なるため、絶縁層とオーミック電極の界面に浮き(空洞)が生じてしまい、反射率が低下するという問題がある。

【0016】

このような問題を避けるために、オーミック電極層を蒸着させた後に一度炉内からウェハを取り出し、レジストを除去し、オーミック電極の熱処理を行い、必要に応じてさらにレジストマスクを形成した後で、バリアメタル層を蒸着させる方法がある。しかし、この方法だと、オーミック電極層とバリアメタル層との界面の密着強度が弱くなるという別の問題がある。

【0017】

本発明の目的は、オーミック電極とバリアメタル層の密着強度を向上させた半導体素子の製造方法を提供することである。

【0018】

本発明の目的は、オーミック電極とバリアメタル層の密着強度を向上させた半導体素子を提供することである。

【課題を解決するための手段】

【0019】

本発明の一観点によれば、半導体素子の製造方法は、(a1)半導体積層構造を準備する工程と、(b1)前記半導体積層構造上にオーミック電極層を成膜する工程と、(c1)前記オーミック電極層上にAuを含む接着層を成膜する工程と、(d1)前記工程(c1)から大気開放せずにバリアメタル層を成膜する工程とを含む。

【0020】

本発明の他の観点によれば、半導体素子は、半導体積層構造と、前記半導体積層構造上に形成されるオーミック電極と、前記オーミック電極上に形成されるAuを含む接着層と、前記接着層上に形成されるバリアメタル層とを有する。

【発明の効果】

【0021】

本発明によれば、オーミック電極とバリアメタル層の密着強度を向上させることができる。

【発明を実施するための最良の形態】

【0022】

図1(A)〜(G)及び図2(A)〜(F)は、本発明の実施例による半導体素子100の製造工程を示す概略的な断面図である。

【0023】

半導体基板1sは、AlAs混昌比0.2以上のAlGaAs基板であり、該半導体基板1s上には、ダブルヘテロ(DH)構造のAl0.02GaAs活性層を有する発光層2が形成されている。図1(A)に示すように、半導体基板1sと発光層2を含む半導体積層構造1の主表面のうちの発光層2に近い面(本実施例ではp型層側、以下、半導体積層構造1のp型層側表面1pと呼ぶ)に、SiO2からなる絶縁膜3を1000Åの厚さで蒸着する。絶縁膜3を設けることにより、発光層2からの発光を半導体基板1s側へ反射して、半導体基板1s側から効率よく取り出すことができる。

【0024】

次に、絶縁膜3上にレジスト膜を塗布して露光、現像でレジストパターンを形成し、バッファードフッ酸(BHF)に2分間浸すことによりウェットエッチングを行い、図1(B)に示すように、絶縁膜3の一部を取り去り、半導体積層構造1の表面と後に形成するp型オーミック電極5とが導通が取れるようにする。

【0025】

続いて、ダイシングストリートとなる部分へのメタル蒸着を防ぐために、図1(C)に示すように、レジスト膜を塗布して露光、現像を行ってレジストパターン4aを形成する。なお、レジストは、例えば、エレクトロニックマテリアルズ社製のAZ5214を用いることができる。

【0026】

次に、BHFに一瞬浸し、半導体積層構造1表面の酸化膜を除去して、図1(C)に示すように、スパッタリング等によりAuZn(Zn含有量5重量%)を3000Åの厚さで真空蒸着しp型オーミック電極層5を形成する。なお、オーミック電極層5を構成するAnZnのZn含有量は、高い反射率、かつ十分なオーミック接触を形成することができる含有量とする。

【0027】

その後、半導体積層構造1のp型層側表面1pにリフトオフテープを貼り付けて、剥がすことにより大部分のレジストパターン4a及びその上のp型オーミック電極層5を除去する。続いて、アセトン超音波洗浄を3分間ずつ3回行うことにより、図1(D)に示すように、完全にレジストパターン4aを除去する。

【0028】

次に、図1(E)に示すように、ダイシングストリートとなる部分の絶縁膜3をBHFに2分間浸すことによりウェットエッチングを行い、除去する。

【0029】

次に、半導体積層構造1の主表面のうちの発光層2に遠い面(本実施例ではn型層側、以下、半導体積層構造1のn型層側表面1nと呼ぶ)に、レジストパターン膜を塗布して90℃でベークした後、電極用マスクを用いて露光を行い、さらに110℃にて反転ベーク、全面露光、AZデベロッパーを1:1にて純水で希釈させた現像液に70秒間浸してパターニングを行い、図1(F)に示すレジストパターン4bを形成する。なお、レジストは、例えば、エレクトロニックマテリアルズ社製のAZ5214を用いることができる。

【0030】

その後、BHFに30秒間浸すことによりウェットエッチングを行い、半導体積層構造1のn型層側表面1nの酸化膜を除去した後、AuGeNiを半導体積層構造1のn型層側表面1nに蒸着させ、図1(G)に示すように、n型オーミック電極層6を形成する。

【0031】

次に、半導体積層構造1のn型層側表面1nにリフトオフテープを貼り付けて、剥がすことにより大部分のレジストパターン4b及びその上のn型オーミック電極層6を除去する。続いて、アセトン超音波洗浄を3分間ずつ3回行うことにより、完全にレジストパターン4bを除去して、図2(A)に示す状態とする。p型及びn型オーミック電極5、6のオーミック接触を形成するために、熱処理を行う。この熱処理は、図2(A)に示す状態のウェハ(半導体積層構造1)を、窒素雰囲気にした合金炉内において400℃まで昇温させてオーミック電極を下地半導体と合金化し、100℃まで冷却させた後に、合金炉から取り出すことにより行う。

【0032】

次に、半導体積層構造1のp型層側表面1pに、レジスト膜を塗布して100℃でベークした後、電極用マスクを用いて露光を行い、さらに120℃にて反転ベーク、全面露光、現像液(例えば、AZ−300MIF)に150秒間浸してパターニングを行い、図2(B)に示すダイシングストリートとなる部分へのメタル蒸着を防ぐためのレジストパターン4cを形成する。なお、レジストは、例えば、エレクトロニックマテリアルズ社製のAZ5200を用いることができる。

【0033】

図2(C)に示すように、p型オーミック電極5の表面にスパッタリング等によりAuZn(Zn含有量5重量%)を1000Åの厚さで真空蒸着させ、接着層10を形成する。続けて、半導体積層構造1をスパッタリング装置等から取り出すことなく、スパッタリング等により接着層10の表面にTaNを2000Å、Taを1000Å、TaNを2000Åの厚さで順次真空蒸着させ、複合バリアメタル層7を形成する。複合バリアメタル層7を設けることにより、共晶層9の元素のオーミック電極への熱拡散を防止することができる。TaNの窒化率はバリア性を有し、かつAuを含む層と高い密着性を得ることができるように設定する。その後、レジストパターン4cを完全に除去できるまでAZリムーバ超音波洗浄を行い、図2(D)に示す状態とする。

【0034】

図2(E)に示すように、再度レジストパターン4d(エレクトロニックマテリアルズ社製のAZ5200等)を形成する。その後、Al、Ta、Auの積層からなる密着向上層8を蒸着させ、続いて、AuSnからなる共晶材を蒸着し、共晶層9を形成する。共晶層9は、半導体発光素子の配線基板等への実装に好適に用いられる。最後に、レジストパターン4d及びその上の密着向上層8及び共晶層9を完全に除去できるまでAZリムーバ超音波洗浄を行い、図2(F)に示す状態とする。

【0035】

図3は、本発明の実施例による半導体素子100と比較例による半導体素子の歩留まり及びダイシェア強度を比較結果を示す表である。

【0036】

比較例による半導体素子は、本発明の実施例による半導体素子100と異なり、図2(B)に示す状態で、接着層10を形成することなく、厚さ3000ÅのAuZnからなるp型オーミック電極5の表面にTaN(窒化率0.7、ここで窒化率は金属原子数と窒素原子数の比を示す)を2000Å、Taを1000Å、TaN(窒化率0.7)を2000Åの厚さで順次真空蒸着させ、複合バリアメタル層7を形成したものである。それ以外は本発明の実施例による半導体素子100と同様の材料及び条件で作製した。

【0037】

図3(A)は、本発明の実施例による半導体素子100と比較例による半導体素子の歩留まりを測定した結果を示す表である。

【0038】

この表は、ブルーシートに貼り付けたウェハをダイシング工程によりチップ分離させ、分離したチップをブルーシートから剥がした時、ブルーシートにメタルが残っているサンプルを不良とし、歩留まりを測定したものである。

【0039】

比較例による半導体素子では、歩留まりが10%以下なのに対して、本実施例による半導体素子100では歩留まりが100%ととなり、飛躍的に向上していることがわかった。

【0040】

また、電極界面の密着性を評価するために実施例による半導体素子100及び比較例による半導体素子のそれぞれのダイシェア強度を測定した。図3(B)は、その結果を示す表である。

【0041】

なお、ダイシェア強度とは半導体素子をパッケージや配線基板等の実装面に実装させた状態において側面より針を押し当て、接合された半導体素子をはく離させるために必要な強度のことである。多層電極構造の密着性と共晶接合部分の強度が十分にあれば、素子破壊するまでの強度を測定することとなる。

【0042】

比較例による半導体素子では、剥離界面がオーミック電極とバリアメタル界面に限られていたのに対し、実施例による半導体素子100では、素子破壊が起きていることがわかった。これらのことから、実施例による半導体素子100では、オーミック電極(p型オーミック電極5)とバリアメタル電極(複合バリアメタル層7)の界面の密着強度が十分であり、比較例のものに比べて飛躍的に向上したことがわかる。

【0043】

なお、実施例による半導体素子100及び比較例による半導体素子のそれぞれに対して2次イオン質量分析(SIMS)を行ったところ、比較例による半導体素子においてバリアメタル層(実施例の複合バリアメタル層7に相当)とオーミック電極(実施例のp型オーミック電極5に相当)との界面にカーボンをより多く含む層があることがわかった。これに対して、実施例による半導体素子100においては、p型オーミック電極(AuZn層)5と接着層(AuZn層)10との界面にカーボンをより多く含む層があることがわかった。

【0044】

以上、本発明の実施例によれば、オーミック電極膜(p型オーミック電極5)の成膜後のレジスト除去工程後に、オーミック電極膜(p型オーミック電極5)の上に蒸着装置において接着層10を形成して、該蒸着装置から取り出さずに複合バリアメタル層7を形成することにより、オーミック電極5とバリアメタル層7の密着強度を飛躍的に向上させることができる。

【0045】

また、本発明の実施例によれば、オーミック電極膜(p型オーミック電極5)の成膜後の熱処理の後に、オーミック電極膜(p型オーミック電極5)の上に蒸着装置において接着層10を形成して、該蒸着装置から取り出さずに複合バリアメタル層7を形成することにより、オーミック電極5とバリアメタル層7の密着強度を飛躍的に向上させることができるとともに、絶縁膜3とオーミック電極5の界面に浮きが生じることを防止できる。

【0046】

つまり、本発明の実施例によれば、オーミック電極膜5の成膜後に大気開放してフォトリソグラフィ工程や合金化工程を経た場合も、Auを含む金属からなる接着層10を成膜し、その後、大気開放せずにバリアメタル層7を成膜することにより、接着層10を介してオーミック電極5とバリアメタル層7の密着強度を飛躍的に向上させることができる。

【0047】

なお、上述の実施例では、実装面側の導電型をp型とし、p型オーミック電極5をAuZnで形成したが、p型オーミック電極5はAuBeで形成したり、実装面側にp型オーミック電極5の代わりにn型電極として、AuGeやAuSnなどで形成するようにしてもよい。すなわち、実装面側のオーミック電極5はAuを含む材料で形成し、その上に形成する接着層10もAuを含む材料で形成する。オーミック電極5及び接着層10の双方をAuを含む材料で形成することによりなじみがよくなり、密着性が向上する。オーミック電極5及び接着層10の双方をAuを含む材料で構成すれば、同一材料でなくてもよいが、本実施例のように同一材料で形成することにより、密着性はさらに向上する。

【0048】

また、本発明の実施例はオーミック電極とバリアメタルの密着性を向上することを目的としていることから、絶縁膜3はSiO2に限らず、SiNXでもよいし、省略してもよい。絶縁膜3を省略する場合は、図1(A)及び図1(B)を参照して説明した絶縁膜3の形成工程及び図1(E)を参照して説明したダイシングストリート部分の絶縁膜除去工程が不要となる。

【0049】

また、上述の実施例では、複合バリアメタル層7をTaN/Ta/TaNの積層で形成したが、共晶材料の拡散を防止することが可能なTiNやTiWN等の窒化物で形成してもよい。なお、バリアメタル層7は、上記の窒化物の積層でもよいし単層で形成してもよい。

また、接着層10とバリアメタル層7との間に、他の層を挟んでもよいが、その場合においても、接着層10の成膜からバリアメタル層7の成膜までは大気開放せずに行うものとする。

【0050】

また、接着層10とバリアメタル層7は、異なる蒸着装置で成膜されてもよいが、その場合においても、接着層10の成膜からバリアメタル層7の成膜までは大気開放せずに行うものとする。

【0051】

なお、発光層2の材料はAlGaAsに限らず、例えば、AlGaInP、GaN等であってもよいが、AlGaAs系半導体やAlGaInP系半導体は、電極とオーミック接触を形成する際に合金化工程が必要であるため、本発明を好適に用いることができる。また、密着向上層8は省略あるいは他の材料によって構成することができる。さらに、共晶材は、共晶層9として半導体素子100の一部とするのではなく、半導体素子100を取り付ける際に底面に補充するようにしてもよい。

【0052】

以上実施例に沿って本発明を説明したが、本発明はこれらに制限されるものではない。例えば、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【図面の簡単な説明】

【0053】

【図1】本発明の実施例による半導体素子100の製造工程を示す概略的な断面図である。

【図2】本発明の実施例による半導体素子100の製造工程を示す概略的な断面図である。

【図3】本発明の実施例による半導体素子100と比較例による半導体素子の歩留まり及びダイシェア強度を比較結果を示す表である。

【図4】従来の半導体素子の構成を示す概略的な断面図である。

【図5】従来の半導体素子の構成を示す概略的な断面図である。

【符号の説明】

【0054】

1…半導体積層構造、2…発光層、3…絶縁膜(SiO2)、4…レジスト、5…p型オーミック電極(AuZn)、6…n型オーミック電極(AuGeNi)、7…複合バリアメタル層(TaN/Ta/TaN)、8…密着向上層、9…共晶層、10…接着層(AuZn)、100…半導体素子

【特許請求の範囲】

【請求項1】

(a1)半導体積層構造を準備する工程と、

(b1)前記半導体積層構造上にオーミック電極層を成膜する工程と、

(c1)前記オーミック電極層上にAuを含む接着層を成膜する工程と、

(d1)前記工程(c1)から大気開放せずにバリアメタル層を成膜する工程と

を含む半導体素子の製造方法。

【請求項2】

さらに、(a2)前記工程(a1)の後に、前記半導体積層構造上にレジストパターンを形成する工程と、

(b2)前記工程(b1)と前記工程(c1)との間に、前記レジストパターンをその上のオーミック電極層とともに除去する工程とを含む請求項1記載の半導体素子の製造方法。

【請求項3】

さらに、(b3)前記工程(b1)と前記工程(c1)との間に、前記オーミック電極層と前記半導体積層構造とを熱処理し、オーミック接触を形成する工程とを含む請求項1又は2記載の半導体素子の製造方法。

【請求項4】

前記工程(c1)及び(d1)は、蒸着により行われる請求項1〜3のいずれか1項に記載の半導体素子の製造方法。

【請求項5】

前記オーミック電極層はAuを含む金属からなる請求項1〜4のいずれか1項に記載の半導体素子の製造方法。

【請求項6】

前記バリアメタル層は金属窒化物からなる請求項1〜5のいずれか1項に記載の半導体素子の製造方法。

【請求項7】

半導体積層構造と、

前記半導体積層構造上に形成されるオーミック電極と、

前記オーミック電極上に形成されるAuを含む接着層と、

前記接着層上に形成されるバリアメタル層と

を有する半導体素子。

【請求項8】

前記オーミック電極はAuを含む金属からなり、

前記バリアメタル層は金属窒化物からなる請求項7記載の半導体素子。

【請求項1】

(a1)半導体積層構造を準備する工程と、

(b1)前記半導体積層構造上にオーミック電極層を成膜する工程と、

(c1)前記オーミック電極層上にAuを含む接着層を成膜する工程と、

(d1)前記工程(c1)から大気開放せずにバリアメタル層を成膜する工程と

を含む半導体素子の製造方法。

【請求項2】

さらに、(a2)前記工程(a1)の後に、前記半導体積層構造上にレジストパターンを形成する工程と、

(b2)前記工程(b1)と前記工程(c1)との間に、前記レジストパターンをその上のオーミック電極層とともに除去する工程とを含む請求項1記載の半導体素子の製造方法。

【請求項3】

さらに、(b3)前記工程(b1)と前記工程(c1)との間に、前記オーミック電極層と前記半導体積層構造とを熱処理し、オーミック接触を形成する工程とを含む請求項1又は2記載の半導体素子の製造方法。

【請求項4】

前記工程(c1)及び(d1)は、蒸着により行われる請求項1〜3のいずれか1項に記載の半導体素子の製造方法。

【請求項5】

前記オーミック電極層はAuを含む金属からなる請求項1〜4のいずれか1項に記載の半導体素子の製造方法。

【請求項6】

前記バリアメタル層は金属窒化物からなる請求項1〜5のいずれか1項に記載の半導体素子の製造方法。

【請求項7】

半導体積層構造と、

前記半導体積層構造上に形成されるオーミック電極と、

前記オーミック電極上に形成されるAuを含む接着層と、

前記接着層上に形成されるバリアメタル層と

を有する半導体素子。

【請求項8】

前記オーミック電極はAuを含む金属からなり、

前記バリアメタル層は金属窒化物からなる請求項7記載の半導体素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2009−164228(P2009−164228A)

【公開日】平成21年7月23日(2009.7.23)

【国際特許分類】

【出願番号】特願2007−340148(P2007−340148)

【出願日】平成19年12月28日(2007.12.28)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

【公開日】平成21年7月23日(2009.7.23)

【国際特許分類】

【出願日】平成19年12月28日(2007.12.28)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

[ Back to top ]