半導体素子及びその製造方法

【課題】半導体層の素子分離される部分に溝を形成する際に内在する応力が開放されても、その応力によりフィールドプレート部が絶縁膜から剥離するのを防止でき、高耐圧化を可能にした半導体素子及びその製造方法を提供する。

【解決手段】HFET10は、電子供給層14上に形成されたソース電極16、ドレイン電極17およびゲート電極18と、各電極間を絶縁する絶縁膜19と、半導体層22の素子分離される部分に形成されたメサ構造23を有する。ゲート電極18は、ショットキー電極の機能を有する第1の電極層20と、絶縁膜19との接触部が絶縁膜19に密着する金属材料で構成されたフィールドプレート部21aを有する第2の電極層21と、を有する。メサ構造23を形成する際に内在する応力が開放されても、その応力によりゲート電極18のフィールドプレート部21aが絶縁膜19から剥離するのを防止でき、高耐圧化が可能になる。

【解決手段】HFET10は、電子供給層14上に形成されたソース電極16、ドレイン電極17およびゲート電極18と、各電極間を絶縁する絶縁膜19と、半導体層22の素子分離される部分に形成されたメサ構造23を有する。ゲート電極18は、ショットキー電極の機能を有する第1の電極層20と、絶縁膜19との接触部が絶縁膜19に密着する金属材料で構成されたフィールドプレート部21aを有する第2の電極層21と、を有する。メサ構造23を形成する際に内在する応力が開放されても、その応力によりゲート電極18のフィールドプレート部21aが絶縁膜19から剥離するのを防止でき、高耐圧化が可能になる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、GaN系ヘテロ接合電界効果トランジスタなどの半導体素子及びその製造方法に関する。

【背景技術】

【0002】

GaN、AlGaNなどの窒化物系半導体は、従来のSi、GaAsなどの半導体に比べてそのエネルギーバンドギャップが広いため、高温、高耐圧デバイス用半導体として優れている。特にこれらの窒化物系半導体(GaN系半導体)材料では、同様に広バンドギャップ半導体であるSiCなどと異なり、AlGaN/GaN等のヘテロ接合構造の形成が可能であるので、窒化物系半導体ヘテロ接合電界効果トランジスタ(Hetero-junction FET: HFET)の開発が盛んに行われている(例えば、特許文献1および2を参照)。

【0003】

化合物半導体を用いた半導体素子には一層の高耐圧性が求められており、このため、例えばHFET等のFETでは、ゲート耐圧の改善が必要とされている。ゲート耐圧の改善には、ゲート電極端部における電界集中の緩和が必要であり、この電界集中の緩和には、フィールドプレート構造が有効なことが知られている(例えば、特許文献3を参照)。

【0004】

このようなフィールドプレート構造を有する半導体素子として、例えば、特許文献3に開示されたものが知られている。この半導体素子は、半導体層上に絶縁膜を挟み込んで配設された複数電極の一つは、半導体層とショットキー接合したショットキー電極層と、ショットキー電極層上に積層され、絶縁膜上に張り出すとともに絶縁膜に密着する張出部を有するフィールドプレート電極層と、を備える。この半導体素子によれば、フィールドプレート電極層の張出部が絶縁膜から剥離するのを防止でき、一層の高耐圧化を図れる。

【特許文献1】特開2005−129856号公報

【特許文献2】特開2003−179082号公報

【特許文献3】特開2005−93864号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、上記フィールドプレート構造を有するGaN系FETなどの半導体素子では、ダイサーによって素子分離する際に素子が受けるダメージを低減するために、素子周辺の半導体層を除去して溝を形成し、その溝部分にダイサーカットを施すことが検討されている。

【0006】

例えば、Si基板などの基板を用いたAlGaN/GaN系HFETの場合、ゲート電極には、AlGaNからなる電子供給層とのショットキー障壁高さの高いNiと、電極の金属抵抗を低減することを目的としたAuの積層構造(Ni/Au)が用いられることが多い。また、AlGaNからなる電子供給層上のパッシベイション膜(絶縁膜)には、SiO2が用いられることが多い。

【0007】

このような半導体素子では、Si基板上にエピタキシャル成長されたGaN等からなる半導体層には、Siとの格子定数の違いなどから応力が内在し、素子周辺の半導体層にエッチングにより溝を形成する際に、その応力が開放される。

このようなAlGaN/GaN系HFETなどの半導体素子を上記フィールドプレート構造とし、ゲート電極のフィールドプレート部の金属にNiなどを用いた場合、上記応力の開放と、NiとSiO2の密着性の不良により、フィールドプレート部が絶縁膜から剥離してしまう。

【0008】

本発明は、このような従来の問題点に鑑みて為されたもので、その目的は、半導体層の素子分離される部分に溝を形成する際に内在する応力が開放されても、その応力によりフィールドプレート部が絶縁膜から剥離するのを防止でき、高耐圧化を可能にした半導体素子及びその製造方法を提供することにある。

【課題を解決するための手段】

【0009】

上記課題を解決するために、請求項1に記載の発明に係る半導体素子は、基板上に形成された化合物半導体からなる半導体層と、前記半導体層上の一部に形成された、開口部を有する絶縁膜と、前記半導体層上に形成された複数の電極と、前記半導体層の素子分離される部分に形成されたメサ構造と、を備え、前記複数の電極の一つの電極は、前記開口部に形成され、ショットキー電極の機能を有する第1の電極層と、該第1の電極層上に積層され、前記絶縁膜上で前記複数の電極のうちの他の電極側へ張り出しかつ前記絶縁膜との接触部が前記絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層と、を有することを特徴とする。

【0010】

この構成によれば、上記一つの電極の第2の電極層は絶縁膜との接触部が絶縁膜に密着する金属材料で構成されたフィールドプレート部を有している。このため、半導体層の素子分離される部分に溝をエッチングにより形成する際に半導体層に内在する応力が開放されても、その応力によりフィールドプレート部が絶縁膜から剥離するのを防止でき、高耐圧化が可能になる。また、半導体層のダイサーでカットされる部分に溝が形成されているので、ダイサーでカットする際に、半導体素子自体が受けるダメージが少ない。

請求項2に記載の発明に係る半導体素子は、前記メサ構造は前記基板に達する深さの溝を有することを特徴とする。この構成によれば、メサ構造の溝内にダイサーを挿入して素子分離する際に、ダイサーで基板をカットするだけでよいので、半導体素子自体が受けるダメージが更に少なくなる。

【0011】

請求項3に記載の発明に係る半導体素子は、前記第1の電極層は、Ni,Pd,Ir,Ptのいずれか一つと、Auとの積層構造を有し、前記第2の電極層は、前記絶縁膜との接触部側に、Ti或いはCrからなる層を備えていることを特徴とする。

請求項4に記載の発明に係る半導体素子は、前記第2の電極層は、前記第1の電極層の端部および前記絶縁膜と接触する側から順に、Ti,PtおよびAuを積層した構造或いはCr,PtおよびAuを積層した構造を有することを特徴とする。

請求項5に記載の発明に係る半導体素子は、前記化合物半導体は、窒化物系半導体であることを特徴とする。

【0012】

請求項6に記載の発明に係る半導体素子の製造方法は、基板上に化合物半導体からなる半導体層を形成する工程と、前記半導体層上に絶縁膜により電気的に分離された複数の電極を形成する工程と、前記半導体層の素子分離される部分に溝を形成する工程と、を備え、前記複数の電極の一つの電極は、電極としての機能を有する第1の電極層と、該第1の電極層上に積層され、前記絶縁膜上で前記複数の電極のうちの他の電極側へ張り出しかつ前記絶縁膜との接触部側が前記絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層とを有することを特徴とする。

【発明の効果】

【0013】

本発明によれば、複数の電極の一つの電極の第2の電極層は絶縁膜との接触部が絶縁膜に密着する金属材料で構成されたフィールドプレート部を有している。このため、半導体層の素子分離される部分に溝をエッチングにより形成する際に半導体層に内在する応力が開放されても、その応力によりフィールドプレート部が絶縁膜から剥離するのを防止でき、高耐圧化が可能になる。

【発明を実施するための最良の形態】

【0014】

次に、本発明を具体化した実施形態を図面に基づいて説明する。

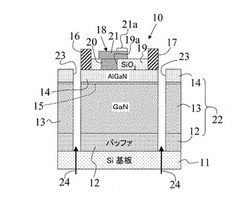

図1は、本発明の一実施形態に係る半導体素子としてのAlGaN/GaN系ヘテロ接合電界効果トランジスタ(Hetero-junction FET: HFET)10の概略構成を示す断面図である。図2は、図1に示すHFET10のゲート電極部分を拡大して示す部分断面図である。

【0015】

HFET10は、図1に示すように、シリコン(Si)基板11上に、AlGaNからなるバッファ層12と、GaNからなる電子走行層13と、電子走行層13に比べて薄いAl0.25Ga0.75Nからなる電子供給層14と、をこの順に積層して形成された半導体層22を有する。このHFET10では、バンドギャップの広いAlGaNからなる電子供給層14とAlGaNよりバンドギャップの狭いGaNからなる電子走行層13とでヘテロ接合界面が形成されている。

【0016】

このAlGaN/GaNヘテロ接合界面には、自発分極、および圧電効果(ピエゾ効果)によって、高濃度の二次元電子ガス層15を形成し、チャンネルの抵抗、即ちHFET10のオン抵抗を小さくする効果がある。

【0017】

また、HFET10は、電子供給層14上に形成されたソース電極16、ドレイン電極17およびゲート電極18の複数の電極と、SiO2などからなる絶縁膜19とを有する。絶縁膜19は、電子供給層14上における、ソース電極16とゲート電極18との間、およびゲート電極18とドレイン電極17との間にそれぞれ形成されている。これにより、ソース電極16とゲート電極18、およびゲート電極18とドレイン電極17がそれぞれ電気的に絶縁されている。なお、ソース電極16またはドレイン電極17と、電子供給層14との間には、各層間のコンタクト抵抗を低減するための図示しないコンタクト層が形成されている。このコンタクト層は、n型不純物が高濃度にドーピングされた窒化物系化合物半導体を用いて形成されている。

【0018】

また、HFET10は、半導体層22の素子分離される部分に形成されたメサ構造23を有する。このメサ構造23は、シリコン基板11に達する深さまでエッチングされた溝を有する深メサである。

複数の電極の一つの電極であるゲート電極18は、ショットキー電極の機能を有する第1の電極層20と、第1の電極層20上に積層され、絶縁膜19上で複数の電極のうちの他の電極であるドレイン電極17側へ張り出しかつ絶縁膜19との接触部が絶縁膜19に密着する金属材料で構成されたフィールドプレート部21aを有する第2の電極層21と、を有する。

【0019】

図1および図2に示すように、ゲート電極18の第1の電極層20は、絶縁膜19の開口部19aに形成されており、半導体層22とショットキー接合する金属材料である第1の層20aと、金属抵抗を低減する金属材料である第2の層20bとの積層構造を有する。第1の層20aは、Ni,Pd,Ir,Ptのいずれか一つから選択される。本実施形態では、第1の電極層20は、Niからなる第1の層20aとAuからなる第2の層20bとの積層構造、つまりNi/Auの積層構造を有する。

【0020】

また、ゲート電極18の第2の電極層21は、図1および図2に示すように、第1の電極層20の第2の層20bおよび絶縁膜19と接触する側から順に、絶縁膜19に密着する金属材料、つまり絶縁膜19との密着性の良い金属からなる第1の層21bと、第2の層21cと、金属抵抗を低減する金属材料からなる第3の層21dとを有する。第1の層21bは、Ti或いはCrのいずれかの金属材料が用いられる。本実施形態では、第1の層21bにTiを用いた。

【0021】

Ni/Auの積層構造を有する第1の電極層20は、良好なショットキー特性を得るために400℃〜600℃ほどで熱処理する必要がある。そのため、第2の層21cには、その熱処理を実施する際に、第3の層21dであるAuの第1の層21bであるTiへの拡散を防止するためにバリアとなる金属材料、たとえばPtを用いた。このように、本実施形態では、ゲート電極21の第2の電極層21に、Ti,PtおよびAuの積層構造を用いた。なお、第1の電極層20と第2の電極層21とは、これらの接合面において電気的に接続される。

【0022】

このような構造を有するHFET10では、ソース電極16とドレイン電極17とを作動させた場合、電子走行層13に供給された電子が2次元電子ガス層15中を高速走行してドレイン電極17まで移動する。このとき、ゲート電極18に加える電圧を制御してゲート電極18直下の空乏層の厚さを変化させることによって、ソース電極16からドレイン電極17へ移動する電子、すなわちドレイン電流を制御することができる。

【0023】

このように第2の電極層21に用いられる密着材料としてのTi、Cr等は、ショットキー接合材料としてのNi、Pd、Ir、Pt等に比べて絶縁膜19との密着度が高い。このため、HFET10におけるフィールドプレート部21aと絶縁膜19との密着度が高い。これによって、HFET10では、ゲート電極18の一層の高耐圧化が実現されている。

【0024】

つぎに、HFET10の製造方法について説明する。

まず、シリコン基板11を設置して真空度を10hPaとしたMOCVD(Metal Organic Chemical Vapor Deposition)装置内に、窒化物系化合物半導体の原料となるトリメチルガリウム(TMGa)とトリメチルアルミニウム(TMAl)とアンモニア(NH3)とを、それぞれ10cm3/min、50cm3/min、12lcm3/minの流量で導入し、成長温度110℃で、層厚50nmのAlGaNからなるバッファ層12をシリコン基板11上に成膜する。

【0025】

次に、TMGaとNH3とを、それぞれ10cm3/min、12lcm3/minの流量で導入し、成長温度1050℃で、層厚400nmのGaNからなる電子走行層13をバッファ層12上に成膜する。

【0026】

次に、TMAlとTMGaとNH3とを、それぞれ50cm3/min、10cm3/min、12lcm3/minの流量で導入し、成長温度1050℃で、層厚30nmのアンドープAl0.25Ga0.75Nからなる電子供給層14を電子走行層13上に成膜する。この電子供給層14のキャリア濃度は1×1016/cm3である。

【0027】

次に、フォトリソグラフィを利用したパターンニングによって、電子供給層14上にSiO2膜からなるマスクを形成するとともに、ソース電極16およびドレイン電極17を形成すべき領域に各電極形状に対応した開口部を形成する。そして、この開口部に例えばTi、AlおよびAuを、それぞれ膜厚50nm、50nmおよび10nmとして順次蒸着して、ソース電極16およびドレイン電極17を形成する。

【0028】

次に、電子供給層14上のマスクを除去し、ソース電極16およびドレイン電極17の間の電子供給層14上に絶縁膜19としてのSiO2膜を蒸着し、ゲート電極18を形成すべき領域の絶縁膜19をエッチングして、第1の電極層20の形状に対応した開口部を形成する。そして、この開口部にNiおよびAuを、それぞれ膜厚10nmおよび200nmとして順次蒸着して、第1の電極層20を形成する。なお、ここで、Niの代わりに、例えばPt、Pd、Irのいずれかを蒸着するようにしてもよい。

【0029】

次に、電子供給層14、ソース電極16、ドレイン電極17、第1の電極層20および絶縁膜19上にフォトレジストからなるマスクを形成するとともに、第2の電極層21を形成すべき領域のマスクをエッチングして、第2の電極層21の形状に対応した開口部を形成する。そして、この開口部にTi、PtおよびAuを、それぞれ膜厚50nm、200nmおよび200nmとして順次蒸着して、第2の電極層21を形成する。その後、フォトレジストからなるマスクを除去する。

【0030】

最後に、電子供給層14、ソース電極16、ドレイン電極17、第2の電極層21および絶縁膜19上にSiO2膜を形成し、このSiO2膜のパターニングを行ってメサ構造23の溝を形成すべき箇所を開口する。この後、その開口において、半導体層22を、その表面側からシリコン基板11に達する深さまでエッチングにより除去して、壁面が略垂直の溝を有するメサ構造23を形成する。これにより、図1に示すHFET10が完成する。なお、図1で符号24は、ダイサーによるカットラインである。

以上のように構成された一実施形態によれば、以下の作用効果を奏する。

【0031】

○第1の電極層20と第2の電極層21とを積層して形成されたフィールドプレート構造を有するゲート電極18によって、このゲート電極18の端部における電界集中は緩和される。また、ゲート電極18の第2の電極層21はSiO2からなる絶縁膜19との接触部が絶縁膜19に密着する金属材料で構成されたフィールドプレート部21aを有している。このため、半導体層22の素子分離される部分にメサ構造23の溝をエッチングにより形成する際に半導体層22に内在する応力が開放されても、その応力によりゲート電極18のフィールドプレート部21aが絶縁膜19から剥離するのを防止でき、高耐圧化が可能になる。

【0032】

○第1の電極層20をNiからなる第1の層20aとAuからなる第2の層20bとの積層構造(Ni/Auの積層構造)としているので、AlGaNからなる電子供給層14との障壁高さの高いNi/Auは良好なショットキー特性を示す。これにより、障壁高さの高いゲート電極が得られ、ゲートリーク電流の低減と、フィールドプレート部21aの剥離防止との両立を図れる。ゲートリーク電流が低減されることで、オフ耐圧が向上する。

【0033】

○半導体層22のダイサーでカットされる(ダイサーで素子分離される)部分に、メサ構造23の溝が形成されているので、ダイサーでカットする際に、半導体素子自体が受けるダメージが少ない。

なお、この発明は以下のように変更して具体化することもできる。

【0034】

・上記実施形態では、一例としてHFETについて説明したが、本発明は、HFETに限らず、MISFET(Metal Insulator Semiconductor FET)、MOSFET(Metal Oxide Semiconductor FET)、MESFET(Metal Semiconductor FET)等、種々のFETに適用可能である。

【0035】

・上記実施形態では、シリコン基板11に達する深さまでエッチングされた溝を有する深メサのメサ構造23を有するHFET10について説明したが、本発明は、深メサのメサ構造23に限らず、そのメサ構造23とは異なる形状の溝、異なる深さの溝、その溝よりも数の多い溝を有するメサ構造が形成された半導体素子にも適用可能である。

【0036】

・上記実施形態では、シリコン基板11を用いているが、シリコン基板に限らず、他の基板を用いた半導体素子にも本発明は適用可能である。

【0037】

・また、本発明は、FET以外にも、ショットキーダイオード等、各種ダイオードにも適用可能である。例えば、半導体層上に形成され、絶縁膜で互いに電気的に絶縁されたカソード電極およびアノード電極を有し、半導体層とショットキー接合するアノード電極に、フィールドプレート構造を持たせたショットキーダイオードにも本発明は適用可能である。つまり、本発明を適用したショットキーダイオードでは、アノード電極は、上記ゲート電極18と同様に、ショットキー電極の機能を有する第1の電極層と、該第1の電極層上に積層され、絶縁膜上でカソード電極側へ張り出しかつ絶縁膜との接触部が絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層と、を有する。

【図面の簡単な説明】

【0038】

【図1】本発明の一実施形態に係るHFETの概略構成を示す断面図。

【図2】図1に示すHFETのゲート電極部分を拡大して示す部分断面図で。

【符号の説明】

【0039】

10:HFET

11:シリコン基板

12:バッファ層

13:電子走行層

14:電子供給層

15:二次元電子ガス層

16:ソース電極

17:ドレイン電極

18:ゲート電極

19:絶縁膜

19a:開口部

20:第1の電極層

20a:第1の層

20b:第2の層

21:第2の電極層

21a:フィールドプレート部

22:半導体層

23:メサ構造

【技術分野】

【0001】

本発明は、GaN系ヘテロ接合電界効果トランジスタなどの半導体素子及びその製造方法に関する。

【背景技術】

【0002】

GaN、AlGaNなどの窒化物系半導体は、従来のSi、GaAsなどの半導体に比べてそのエネルギーバンドギャップが広いため、高温、高耐圧デバイス用半導体として優れている。特にこれらの窒化物系半導体(GaN系半導体)材料では、同様に広バンドギャップ半導体であるSiCなどと異なり、AlGaN/GaN等のヘテロ接合構造の形成が可能であるので、窒化物系半導体ヘテロ接合電界効果トランジスタ(Hetero-junction FET: HFET)の開発が盛んに行われている(例えば、特許文献1および2を参照)。

【0003】

化合物半導体を用いた半導体素子には一層の高耐圧性が求められており、このため、例えばHFET等のFETでは、ゲート耐圧の改善が必要とされている。ゲート耐圧の改善には、ゲート電極端部における電界集中の緩和が必要であり、この電界集中の緩和には、フィールドプレート構造が有効なことが知られている(例えば、特許文献3を参照)。

【0004】

このようなフィールドプレート構造を有する半導体素子として、例えば、特許文献3に開示されたものが知られている。この半導体素子は、半導体層上に絶縁膜を挟み込んで配設された複数電極の一つは、半導体層とショットキー接合したショットキー電極層と、ショットキー電極層上に積層され、絶縁膜上に張り出すとともに絶縁膜に密着する張出部を有するフィールドプレート電極層と、を備える。この半導体素子によれば、フィールドプレート電極層の張出部が絶縁膜から剥離するのを防止でき、一層の高耐圧化を図れる。

【特許文献1】特開2005−129856号公報

【特許文献2】特開2003−179082号公報

【特許文献3】特開2005−93864号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、上記フィールドプレート構造を有するGaN系FETなどの半導体素子では、ダイサーによって素子分離する際に素子が受けるダメージを低減するために、素子周辺の半導体層を除去して溝を形成し、その溝部分にダイサーカットを施すことが検討されている。

【0006】

例えば、Si基板などの基板を用いたAlGaN/GaN系HFETの場合、ゲート電極には、AlGaNからなる電子供給層とのショットキー障壁高さの高いNiと、電極の金属抵抗を低減することを目的としたAuの積層構造(Ni/Au)が用いられることが多い。また、AlGaNからなる電子供給層上のパッシベイション膜(絶縁膜)には、SiO2が用いられることが多い。

【0007】

このような半導体素子では、Si基板上にエピタキシャル成長されたGaN等からなる半導体層には、Siとの格子定数の違いなどから応力が内在し、素子周辺の半導体層にエッチングにより溝を形成する際に、その応力が開放される。

このようなAlGaN/GaN系HFETなどの半導体素子を上記フィールドプレート構造とし、ゲート電極のフィールドプレート部の金属にNiなどを用いた場合、上記応力の開放と、NiとSiO2の密着性の不良により、フィールドプレート部が絶縁膜から剥離してしまう。

【0008】

本発明は、このような従来の問題点に鑑みて為されたもので、その目的は、半導体層の素子分離される部分に溝を形成する際に内在する応力が開放されても、その応力によりフィールドプレート部が絶縁膜から剥離するのを防止でき、高耐圧化を可能にした半導体素子及びその製造方法を提供することにある。

【課題を解決するための手段】

【0009】

上記課題を解決するために、請求項1に記載の発明に係る半導体素子は、基板上に形成された化合物半導体からなる半導体層と、前記半導体層上の一部に形成された、開口部を有する絶縁膜と、前記半導体層上に形成された複数の電極と、前記半導体層の素子分離される部分に形成されたメサ構造と、を備え、前記複数の電極の一つの電極は、前記開口部に形成され、ショットキー電極の機能を有する第1の電極層と、該第1の電極層上に積層され、前記絶縁膜上で前記複数の電極のうちの他の電極側へ張り出しかつ前記絶縁膜との接触部が前記絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層と、を有することを特徴とする。

【0010】

この構成によれば、上記一つの電極の第2の電極層は絶縁膜との接触部が絶縁膜に密着する金属材料で構成されたフィールドプレート部を有している。このため、半導体層の素子分離される部分に溝をエッチングにより形成する際に半導体層に内在する応力が開放されても、その応力によりフィールドプレート部が絶縁膜から剥離するのを防止でき、高耐圧化が可能になる。また、半導体層のダイサーでカットされる部分に溝が形成されているので、ダイサーでカットする際に、半導体素子自体が受けるダメージが少ない。

請求項2に記載の発明に係る半導体素子は、前記メサ構造は前記基板に達する深さの溝を有することを特徴とする。この構成によれば、メサ構造の溝内にダイサーを挿入して素子分離する際に、ダイサーで基板をカットするだけでよいので、半導体素子自体が受けるダメージが更に少なくなる。

【0011】

請求項3に記載の発明に係る半導体素子は、前記第1の電極層は、Ni,Pd,Ir,Ptのいずれか一つと、Auとの積層構造を有し、前記第2の電極層は、前記絶縁膜との接触部側に、Ti或いはCrからなる層を備えていることを特徴とする。

請求項4に記載の発明に係る半導体素子は、前記第2の電極層は、前記第1の電極層の端部および前記絶縁膜と接触する側から順に、Ti,PtおよびAuを積層した構造或いはCr,PtおよびAuを積層した構造を有することを特徴とする。

請求項5に記載の発明に係る半導体素子は、前記化合物半導体は、窒化物系半導体であることを特徴とする。

【0012】

請求項6に記載の発明に係る半導体素子の製造方法は、基板上に化合物半導体からなる半導体層を形成する工程と、前記半導体層上に絶縁膜により電気的に分離された複数の電極を形成する工程と、前記半導体層の素子分離される部分に溝を形成する工程と、を備え、前記複数の電極の一つの電極は、電極としての機能を有する第1の電極層と、該第1の電極層上に積層され、前記絶縁膜上で前記複数の電極のうちの他の電極側へ張り出しかつ前記絶縁膜との接触部側が前記絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層とを有することを特徴とする。

【発明の効果】

【0013】

本発明によれば、複数の電極の一つの電極の第2の電極層は絶縁膜との接触部が絶縁膜に密着する金属材料で構成されたフィールドプレート部を有している。このため、半導体層の素子分離される部分に溝をエッチングにより形成する際に半導体層に内在する応力が開放されても、その応力によりフィールドプレート部が絶縁膜から剥離するのを防止でき、高耐圧化が可能になる。

【発明を実施するための最良の形態】

【0014】

次に、本発明を具体化した実施形態を図面に基づいて説明する。

図1は、本発明の一実施形態に係る半導体素子としてのAlGaN/GaN系ヘテロ接合電界効果トランジスタ(Hetero-junction FET: HFET)10の概略構成を示す断面図である。図2は、図1に示すHFET10のゲート電極部分を拡大して示す部分断面図である。

【0015】

HFET10は、図1に示すように、シリコン(Si)基板11上に、AlGaNからなるバッファ層12と、GaNからなる電子走行層13と、電子走行層13に比べて薄いAl0.25Ga0.75Nからなる電子供給層14と、をこの順に積層して形成された半導体層22を有する。このHFET10では、バンドギャップの広いAlGaNからなる電子供給層14とAlGaNよりバンドギャップの狭いGaNからなる電子走行層13とでヘテロ接合界面が形成されている。

【0016】

このAlGaN/GaNヘテロ接合界面には、自発分極、および圧電効果(ピエゾ効果)によって、高濃度の二次元電子ガス層15を形成し、チャンネルの抵抗、即ちHFET10のオン抵抗を小さくする効果がある。

【0017】

また、HFET10は、電子供給層14上に形成されたソース電極16、ドレイン電極17およびゲート電極18の複数の電極と、SiO2などからなる絶縁膜19とを有する。絶縁膜19は、電子供給層14上における、ソース電極16とゲート電極18との間、およびゲート電極18とドレイン電極17との間にそれぞれ形成されている。これにより、ソース電極16とゲート電極18、およびゲート電極18とドレイン電極17がそれぞれ電気的に絶縁されている。なお、ソース電極16またはドレイン電極17と、電子供給層14との間には、各層間のコンタクト抵抗を低減するための図示しないコンタクト層が形成されている。このコンタクト層は、n型不純物が高濃度にドーピングされた窒化物系化合物半導体を用いて形成されている。

【0018】

また、HFET10は、半導体層22の素子分離される部分に形成されたメサ構造23を有する。このメサ構造23は、シリコン基板11に達する深さまでエッチングされた溝を有する深メサである。

複数の電極の一つの電極であるゲート電極18は、ショットキー電極の機能を有する第1の電極層20と、第1の電極層20上に積層され、絶縁膜19上で複数の電極のうちの他の電極であるドレイン電極17側へ張り出しかつ絶縁膜19との接触部が絶縁膜19に密着する金属材料で構成されたフィールドプレート部21aを有する第2の電極層21と、を有する。

【0019】

図1および図2に示すように、ゲート電極18の第1の電極層20は、絶縁膜19の開口部19aに形成されており、半導体層22とショットキー接合する金属材料である第1の層20aと、金属抵抗を低減する金属材料である第2の層20bとの積層構造を有する。第1の層20aは、Ni,Pd,Ir,Ptのいずれか一つから選択される。本実施形態では、第1の電極層20は、Niからなる第1の層20aとAuからなる第2の層20bとの積層構造、つまりNi/Auの積層構造を有する。

【0020】

また、ゲート電極18の第2の電極層21は、図1および図2に示すように、第1の電極層20の第2の層20bおよび絶縁膜19と接触する側から順に、絶縁膜19に密着する金属材料、つまり絶縁膜19との密着性の良い金属からなる第1の層21bと、第2の層21cと、金属抵抗を低減する金属材料からなる第3の層21dとを有する。第1の層21bは、Ti或いはCrのいずれかの金属材料が用いられる。本実施形態では、第1の層21bにTiを用いた。

【0021】

Ni/Auの積層構造を有する第1の電極層20は、良好なショットキー特性を得るために400℃〜600℃ほどで熱処理する必要がある。そのため、第2の層21cには、その熱処理を実施する際に、第3の層21dであるAuの第1の層21bであるTiへの拡散を防止するためにバリアとなる金属材料、たとえばPtを用いた。このように、本実施形態では、ゲート電極21の第2の電極層21に、Ti,PtおよびAuの積層構造を用いた。なお、第1の電極層20と第2の電極層21とは、これらの接合面において電気的に接続される。

【0022】

このような構造を有するHFET10では、ソース電極16とドレイン電極17とを作動させた場合、電子走行層13に供給された電子が2次元電子ガス層15中を高速走行してドレイン電極17まで移動する。このとき、ゲート電極18に加える電圧を制御してゲート電極18直下の空乏層の厚さを変化させることによって、ソース電極16からドレイン電極17へ移動する電子、すなわちドレイン電流を制御することができる。

【0023】

このように第2の電極層21に用いられる密着材料としてのTi、Cr等は、ショットキー接合材料としてのNi、Pd、Ir、Pt等に比べて絶縁膜19との密着度が高い。このため、HFET10におけるフィールドプレート部21aと絶縁膜19との密着度が高い。これによって、HFET10では、ゲート電極18の一層の高耐圧化が実現されている。

【0024】

つぎに、HFET10の製造方法について説明する。

まず、シリコン基板11を設置して真空度を10hPaとしたMOCVD(Metal Organic Chemical Vapor Deposition)装置内に、窒化物系化合物半導体の原料となるトリメチルガリウム(TMGa)とトリメチルアルミニウム(TMAl)とアンモニア(NH3)とを、それぞれ10cm3/min、50cm3/min、12lcm3/minの流量で導入し、成長温度110℃で、層厚50nmのAlGaNからなるバッファ層12をシリコン基板11上に成膜する。

【0025】

次に、TMGaとNH3とを、それぞれ10cm3/min、12lcm3/minの流量で導入し、成長温度1050℃で、層厚400nmのGaNからなる電子走行層13をバッファ層12上に成膜する。

【0026】

次に、TMAlとTMGaとNH3とを、それぞれ50cm3/min、10cm3/min、12lcm3/minの流量で導入し、成長温度1050℃で、層厚30nmのアンドープAl0.25Ga0.75Nからなる電子供給層14を電子走行層13上に成膜する。この電子供給層14のキャリア濃度は1×1016/cm3である。

【0027】

次に、フォトリソグラフィを利用したパターンニングによって、電子供給層14上にSiO2膜からなるマスクを形成するとともに、ソース電極16およびドレイン電極17を形成すべき領域に各電極形状に対応した開口部を形成する。そして、この開口部に例えばTi、AlおよびAuを、それぞれ膜厚50nm、50nmおよび10nmとして順次蒸着して、ソース電極16およびドレイン電極17を形成する。

【0028】

次に、電子供給層14上のマスクを除去し、ソース電極16およびドレイン電極17の間の電子供給層14上に絶縁膜19としてのSiO2膜を蒸着し、ゲート電極18を形成すべき領域の絶縁膜19をエッチングして、第1の電極層20の形状に対応した開口部を形成する。そして、この開口部にNiおよびAuを、それぞれ膜厚10nmおよび200nmとして順次蒸着して、第1の電極層20を形成する。なお、ここで、Niの代わりに、例えばPt、Pd、Irのいずれかを蒸着するようにしてもよい。

【0029】

次に、電子供給層14、ソース電極16、ドレイン電極17、第1の電極層20および絶縁膜19上にフォトレジストからなるマスクを形成するとともに、第2の電極層21を形成すべき領域のマスクをエッチングして、第2の電極層21の形状に対応した開口部を形成する。そして、この開口部にTi、PtおよびAuを、それぞれ膜厚50nm、200nmおよび200nmとして順次蒸着して、第2の電極層21を形成する。その後、フォトレジストからなるマスクを除去する。

【0030】

最後に、電子供給層14、ソース電極16、ドレイン電極17、第2の電極層21および絶縁膜19上にSiO2膜を形成し、このSiO2膜のパターニングを行ってメサ構造23の溝を形成すべき箇所を開口する。この後、その開口において、半導体層22を、その表面側からシリコン基板11に達する深さまでエッチングにより除去して、壁面が略垂直の溝を有するメサ構造23を形成する。これにより、図1に示すHFET10が完成する。なお、図1で符号24は、ダイサーによるカットラインである。

以上のように構成された一実施形態によれば、以下の作用効果を奏する。

【0031】

○第1の電極層20と第2の電極層21とを積層して形成されたフィールドプレート構造を有するゲート電極18によって、このゲート電極18の端部における電界集中は緩和される。また、ゲート電極18の第2の電極層21はSiO2からなる絶縁膜19との接触部が絶縁膜19に密着する金属材料で構成されたフィールドプレート部21aを有している。このため、半導体層22の素子分離される部分にメサ構造23の溝をエッチングにより形成する際に半導体層22に内在する応力が開放されても、その応力によりゲート電極18のフィールドプレート部21aが絶縁膜19から剥離するのを防止でき、高耐圧化が可能になる。

【0032】

○第1の電極層20をNiからなる第1の層20aとAuからなる第2の層20bとの積層構造(Ni/Auの積層構造)としているので、AlGaNからなる電子供給層14との障壁高さの高いNi/Auは良好なショットキー特性を示す。これにより、障壁高さの高いゲート電極が得られ、ゲートリーク電流の低減と、フィールドプレート部21aの剥離防止との両立を図れる。ゲートリーク電流が低減されることで、オフ耐圧が向上する。

【0033】

○半導体層22のダイサーでカットされる(ダイサーで素子分離される)部分に、メサ構造23の溝が形成されているので、ダイサーでカットする際に、半導体素子自体が受けるダメージが少ない。

なお、この発明は以下のように変更して具体化することもできる。

【0034】

・上記実施形態では、一例としてHFETについて説明したが、本発明は、HFETに限らず、MISFET(Metal Insulator Semiconductor FET)、MOSFET(Metal Oxide Semiconductor FET)、MESFET(Metal Semiconductor FET)等、種々のFETに適用可能である。

【0035】

・上記実施形態では、シリコン基板11に達する深さまでエッチングされた溝を有する深メサのメサ構造23を有するHFET10について説明したが、本発明は、深メサのメサ構造23に限らず、そのメサ構造23とは異なる形状の溝、異なる深さの溝、その溝よりも数の多い溝を有するメサ構造が形成された半導体素子にも適用可能である。

【0036】

・上記実施形態では、シリコン基板11を用いているが、シリコン基板に限らず、他の基板を用いた半導体素子にも本発明は適用可能である。

【0037】

・また、本発明は、FET以外にも、ショットキーダイオード等、各種ダイオードにも適用可能である。例えば、半導体層上に形成され、絶縁膜で互いに電気的に絶縁されたカソード電極およびアノード電極を有し、半導体層とショットキー接合するアノード電極に、フィールドプレート構造を持たせたショットキーダイオードにも本発明は適用可能である。つまり、本発明を適用したショットキーダイオードでは、アノード電極は、上記ゲート電極18と同様に、ショットキー電極の機能を有する第1の電極層と、該第1の電極層上に積層され、絶縁膜上でカソード電極側へ張り出しかつ絶縁膜との接触部が絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層と、を有する。

【図面の簡単な説明】

【0038】

【図1】本発明の一実施形態に係るHFETの概略構成を示す断面図。

【図2】図1に示すHFETのゲート電極部分を拡大して示す部分断面図で。

【符号の説明】

【0039】

10:HFET

11:シリコン基板

12:バッファ層

13:電子走行層

14:電子供給層

15:二次元電子ガス層

16:ソース電極

17:ドレイン電極

18:ゲート電極

19:絶縁膜

19a:開口部

20:第1の電極層

20a:第1の層

20b:第2の層

21:第2の電極層

21a:フィールドプレート部

22:半導体層

23:メサ構造

【特許請求の範囲】

【請求項1】

基板上に形成された化合物半導体からなる半導体層と、

前記半導体層上の一部に形成された、開口部を有する絶縁膜と、

前記半導体層上に形成された複数の電極と、

前記半導体層の素子分離される部分に形成されたメサ構造と、を備え、

前記複数の電極の一つの電極は、前記開口部に形成され、ショットキー電極の機能を有する第1の電極層と、該第1の電極層上に積層され、前記絶縁膜上で前記複数の電極のうちの他の電極側へ張り出しかつ前記絶縁膜との接触部が前記絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層と、を有することを特徴とする半導体素子。

【請求項2】

前記メサ構造は前記基板に達する深さの溝を有することを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記第1の電極層は、Ni,Pd,Ir,Ptのいずれか一つと、Auとの積層構造を有し、前記第2の電極層は、前記絶縁膜との接触部側に、Ti或いはCrからなる層を備えていることを特徴とする請求項1又は2に記載の半導体素子。

【請求項4】

前記第2の電極層は、前記第1の電極層の端部および前記絶縁膜と接触する側から順に、Ti,PtおよびAuを積層した構造或いはCr,PtおよびAuを積層した構造を有することを特徴とする請求項1又は2に記載の半導体素子。

【請求項5】

前記化合物半導体は、窒化物系半導体であることを特徴とする請求項1乃至4のいずれか一つに記載の半導体素子。

【請求項6】

基板上に化合物半導体からなる半導体層を形成する工程と、

前記半導体層上に絶縁膜により電気的に分離された複数の電極を形成する工程と、

前記半導体層の素子分離される部分に溝を形成する工程と、を備え、

前記複数の電極の一つの電極は、電極としての機能を有する第1の電極層と、該第1の電極層上に積層され、前記絶縁膜上で前記複数の電極のうちの他の電極側へ張り出しかつ前記絶縁膜との接触部側が前記絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層とを有することを特徴とする半導体素子の製造方法。

【請求項1】

基板上に形成された化合物半導体からなる半導体層と、

前記半導体層上の一部に形成された、開口部を有する絶縁膜と、

前記半導体層上に形成された複数の電極と、

前記半導体層の素子分離される部分に形成されたメサ構造と、を備え、

前記複数の電極の一つの電極は、前記開口部に形成され、ショットキー電極の機能を有する第1の電極層と、該第1の電極層上に積層され、前記絶縁膜上で前記複数の電極のうちの他の電極側へ張り出しかつ前記絶縁膜との接触部が前記絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層と、を有することを特徴とする半導体素子。

【請求項2】

前記メサ構造は前記基板に達する深さの溝を有することを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記第1の電極層は、Ni,Pd,Ir,Ptのいずれか一つと、Auとの積層構造を有し、前記第2の電極層は、前記絶縁膜との接触部側に、Ti或いはCrからなる層を備えていることを特徴とする請求項1又は2に記載の半導体素子。

【請求項4】

前記第2の電極層は、前記第1の電極層の端部および前記絶縁膜と接触する側から順に、Ti,PtおよびAuを積層した構造或いはCr,PtおよびAuを積層した構造を有することを特徴とする請求項1又は2に記載の半導体素子。

【請求項5】

前記化合物半導体は、窒化物系半導体であることを特徴とする請求項1乃至4のいずれか一つに記載の半導体素子。

【請求項6】

基板上に化合物半導体からなる半導体層を形成する工程と、

前記半導体層上に絶縁膜により電気的に分離された複数の電極を形成する工程と、

前記半導体層の素子分離される部分に溝を形成する工程と、を備え、

前記複数の電極の一つの電極は、電極としての機能を有する第1の電極層と、該第1の電極層上に積層され、前記絶縁膜上で前記複数の電極のうちの他の電極側へ張り出しかつ前記絶縁膜との接触部側が前記絶縁膜に密着する金属材料で構成されたフィールドプレート部を有する第2の電極層とを有することを特徴とする半導体素子の製造方法。

【図1】

【図2】

【図2】

【公開番号】特開2010−10412(P2010−10412A)

【公開日】平成22年1月14日(2010.1.14)

【国際特許分類】

【出願番号】特願2008−168224(P2008−168224)

【出願日】平成20年6月27日(2008.6.27)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

【公開日】平成22年1月14日(2010.1.14)

【国際特許分類】

【出願日】平成20年6月27日(2008.6.27)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

[ Back to top ]