半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に関し、特に、絶縁膜を貫通するコンタクトプラグを介して絶縁膜の上部および下部にそれぞれ形成された構造を電気的に連結させる半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体素子は、半導体基板上に積層された複数の導電性パターンと絶縁膜を含む。また、半導体素子は、絶縁膜を挟んで絶縁膜の下部に形成された導電性の下部構造と絶縁膜の上部に形成された導電性の上部構造を電気的に連結させるために絶縁膜を貫通して形成されたコンタクトプラグをさらに含む。

【0003】

以下、NAND型フラッシュメモリ素子のドレイン領域とビットラインを電気的に連結させるコンタクトプラグを例として、下部構造と上部構造とを電気的に連結させるコンタクトプラグについてより具体的に説明する。

【0004】

図1は、NAND型フラッシュメモリ素子のドレイン領域とビットラインを電気的に連結させるドレインコンタクトプラグを示す断面図である。図1を参照すると、NAND型フラッシュメモリ素子は、ドレインセレクトトランジスタ、ソースセレクトトランジスタ、ドレインセレクトトランジスタとソースセレクトトランジスタとの間に直列に連結された複数のメモリセルを含むメモリストリングを複数含んでいる。

【0005】

一方、メモリストリングは、ビットライン19を介してメモリセルのデータを格納するのに必要な電圧を印加するページバッファ部に電気的に連結される。ビットライン19は、ドレインコンタクトプラグ11を経由してメモリストリングのドレイン領域5に電気的に連結される。すなわち、第1層間絶縁膜7の上部に形成されたビットライン19と上部構造は、第1層間絶縁膜7を貫通するドレインコンタクトプラグ11を介して第1層間絶縁膜7の下部に形成されたドレイン領域5という下部構造に電気的に連結されうる。

【0006】

ドレイン領域5は、素子分離膜3によって区画された半導体基板1の活性領域に不純物を注入して形成されたのである。ドレインコンタクトプラグ11は、ドレイン領域5を含む半導体基板1上部に、少なくとも一層の第1層間絶縁膜7を形成する工程、ドレイン領域5が露出するように、第1層間絶縁膜7の一部をエッチングして第1層間絶縁膜7を貫通するドレインコンタクトホール9を形成する工程、およびドレインコンタクトホール9の内部を導電性物質で埋め込む工程を通じて形成される。

【0007】

ビットライン19は、ダマシンスキーム(Damascene Scheme)を用いて形成することができる。ダマシンスキームを利用する場合、ビットライン19は、ドレインコンタクトプラグ11が形成された第1層間絶縁膜7の上部にエッチング停止膜13および第2層間絶縁膜15を積層する工程、エッチング停止膜13が露出するように第2層間絶縁膜15の一部をエッチングした後、露出したエッチング停止膜13をエッチングしてドレインコンタクトプラグ11を露出させるトレンチ17を形成する工程、およびトレンチ17の内部を導電性物質で埋め込む工程を経て形成する。

【0008】

ところが、半導体素子の高集積化のために半導体素子のパターンが30nm以下に狭くなるにつれて、隣接したドレインコンタクトプラグ11間の間隔が狭くなっている。これにより、ドレインコンタクトプラグ11とビットライン19とのオーバーレイマージン(Overlay Margin)が不足し、ドレインコンタクトプラグ11とビットライン19との間の最短距離L1が、設定された値より近く形成されうる。その結果、互いに絶縁されなければならないドレインコンタクトプラグ11とビットライン19間のショートにより、漏れ電流(Leakage)が発生し、半導体素子が誤動作することになる。

【0009】

図2は、図1において、上述したショート問題を改善できるNAND型フラッシュメモリ素子の断面図である。図2に示されたNAND型フラッシュメモリ素子のドレインコンタクトプラグ21と、スペーサ20以外の他の構成は、図1に図示しているものと同様である。図2の構成要素のうち、図1に示された構成要素と同一の構成要素は、図1に示された構成要素と同一の符号であり、図1で上述した方法と同じ方法によって形成される。

【0010】

図2を参照すると、互いに絶縁されなければならないドレインコンタクトプラグ21とビットライン19間のショートを改善するために、ドレインコンタクトホール9を形成した後、ドレインコンタクトホール9の側壁全面に絶縁膜でスペーサ20を形成する。この後、スペーサ20が形成されたドレインコンタクトホール9の内部を導電性物質で埋め込み、ドレインコンタクトプラグ21を形成する。これにより、ドレインコンタクトプラグ21とビットライン19との間の最短距離L2をスペーサ20の幅ほど増加させることができる。これにより、ドレインコンタクトプラグ21とビットライン19のオーバーレイーマージンが改善され、互いに絶縁されなければならないドレインコンタクトプラグ21とビットライン19間のショートの発生を改善することができる。しかし、ドレインコンタクトホール10の側壁にスペーサ20をさらに形成する場合、スペーサ20を形成するための工程を追加しなければならにため、工程が複雑になるという短所がある。そして、スペーサ20の幅によりドレインコンタクトプラグ21の下部の幅が狭くなり、ドレインコンタクトプラグ21のコンタクト抵抗が減少するという問題がある。

【発明の概要】

【発明が解決しようとする課題】

【0011】

したがって、本発明は、上記問題を解決するために案出された発明であり、その目的は絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供することである。

【課題を解決するための手段】

【0012】

前記目的を達成するために本発明の第1実施例による半導体素子は、半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグ、及び前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサを含む。

【0013】

また、本発明の第2実施例による半導体素子は、半導体基板の上部に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成された導電膜と、前記コンタクトホール内で前記導電膜の下部側壁の縁と前記導電膜の底面を取り囲むバリアメタル膜、および前記コンタクトホール内で前記導電膜の上部側壁を部分的に覆うスペーサを含む。

【0014】

さらに、本発明の実施例による半導体素子の製造方法は、半導体基板の上部に第1層間絶縁膜を形成する段階と、前記第1層間絶縁膜を貫通するコンタクトホールを形成する段階と、前記コンタクトホールの内部の上部側壁の縁にリセスされたコンタクトプラグを形成する段階、及び前記コンタクトプラグの前記上部側壁を部分的に覆うスペーサを形成する段階と、を含む。

【発明の効果】

【0015】

以上のように、本発明によれば、スペーサをコンタクトプラグの側壁全面に形成することなく、コンタクトプラグの上部(Top Portion)の側壁に限って形成することで、コンタクトプラグの下部の幅を確保できるので、コンタクトプラグの抵抗を改善することができる。

【0016】

また、本発明によれば、コンタクトプラグの上部側壁にスペーサを形成することで、互いに絶縁されるように形成されるべきコンタクトプラグとコンタクトプラグの上部に形成される導電性パターンのオーバーレイマージンをスペーサの幅ほど確保することができる。

【0017】

そして、本発明によれば、スペーサとエッチング停止膜を同じ工程を通じて同じ物質膜で形成することで、スペーサを形成するための別の工程を施す必要がないため、工数を低減し、半導体素子の製造に要求されるコストを削減することができる。

【図面の簡単な説明】

【0018】

【図1】NAND型フラッシュメモリ素子のドレイン領域とビットラインを電気的に連結させるドレインコンタクトプラグを示す断面図である。

【図2】図1に示したNAND型フラッシュメモリ素子のショートの問題を改善するための他のNAND型フラッシュメモリ素子の断面図である。

【図3】本発明の実施例による半導体素子の平面図である。

【図4】本発明の実施例による半導体素子の製造方法を説明するために、図3に示した線I−Iの方向に沿って切り取った断面図である。

【図5】本発明の実施例による半導体素子の製造方法を説明するために、図3に示した線I−Iの方向に沿って切り取った断面図である。

【図6】本発明の実施例による半導体素子の製造方法を説明するために、図3に示した線I−Iの方向に沿って切り取った断面図である。

【図7】本発明の実施例による半導体素子の製造方法を説明するために、図3に示した線I−Iの方向に沿って切り取った断面図である。

【発明を実施するための最良の形態】

【0019】

以下、添付図面を参照して本発明の好ましい実施例を説明する。ただし、本発明は、以下開示される実施例に限定されるものではなく、異なる様々な形態具現することができ、本発明の範囲は、後述する実施例に限定されるものではない。本実施例は本発明の開示が完全になるようにして通常の知識を有する者に発明の範疇を完全に知らせるために提供されるものであり、本発明の範囲は、本願の特許請求の範囲によって理解されるべきである。

【0020】

一方、ある膜が他の膜または半導体基板の"上"にあると記載されている場合、前記ある膜とは、前記他の膜または半導体基板に直接接触して存在することができ、またはその間に第3の膜が介在される場合がある。また、図面では、それぞれの層の厚さや大きさは、説明の便宜と明確性のために誇張された。図面において同じ符号は同じ要素を指す。

【0021】

図3は、本発明の実施例による半導体素子の平面図である。特に、図3は、NAND型フラッシュメモリ素子を例として示した。図3を参照すると、本発明の実施例によるNAND型フラッシュメモリ素子のセルアレイは、トレンチまたは素子分離膜が形成される素子分離領域Bと素子分離領域Bによって区分される活性領域Aを含む。

【0022】

素子分離領域Bと活性領域Aは、互いに平行に交互に定義される。そして、素子分離領域Bと、活性領域Aに交差するように、半導体基板の上部にドレインセレクトラインDSL、ソースセレクトラインSSL、およびワードラインWLを形成する。互いに隣り合うドレインセレクトラインDSLとソースセレクトラインSSLとの間には、複数のワードラインWLが形成される。

【0023】

一般に、ドレインセレクトラインDSL同士が互いに隣り合うように配置され、かつ、ソースセレクトラインSSL同士が隣り合うように配置される。セレクトライン(DSL、およびSSL)とワードラインWLとの間の活性領域Aには不純物が注入され、接合領域が形成される。ここで、ドレインセレクトラインDSLの間に形成される接合領域は、メモリストリングSTのドレイン領域となり、ソースセレクトラインSSLの間に形成される接合領域は、メモリストリングSTのソース領域となる。

【0024】

ドレインセレクトラインDSLと活性領域Aとの交差部に形成されたドレインセレクトトランジスタ、ソースセレクトラインSSLと活性領域Aとの交差部に形成されたソースセレクトトランジスタ、互いに隣り合うドレインセレクトトランジスタとソースセレクトトランジスタとの間のワードラインWLと活性領域Aとの交差部に形成された複数のメモリセルが直列に連結されて、一つのメモリストリングSTを構成する。それぞれのメモリストリングSTは、ドレインコンタクトプラグ120を介して、それに対応するビットラインBL(133)に電気的に連結され、ソースコンタクトライン150を介して共通ソース電圧が印加される金属配線(図示せず)に電気的に連結される。

【0025】

ビットラインBL(133)は、活性領域Aの上部に形成され、活性領域Aに平行に形成される。そして、ビットラインBL(133)は、メモリセルのデータを格納するのに必要な電圧を印加するページバッファ部(図示せず)とメモリストリングSTと、を連結する。

【0026】

前記ドレインコンタクトプラグ120は、ドレインセレクトラインDSLの間の活性領域Aのそれぞれの上部に形成される。そして、ドレインコンタクトプラグ120は、ドレインセレクトラインDSL、ソースセレクトラインSSL、ワードラインWL、素子分離領域B、活性領域A、およびソースコンタクトプラグ150などの下部構造を覆う少なくとも一層の第1層間絶縁膜を貫通して、活性領域Aの表面に形成されたドレイン領域に連結される。そして、ドレインコンタクトプラグ120は、第1層間絶縁膜をエッチングしてドレイン領域を露出させるコンタクトホールの内部に形成されるが、コンタクトホールを形成するためのエッチング工程の際、エッチングマージンを確保するために、ドレインセレクトラインDSLの間のコンタクトホールをジグザグに配列する。これにより、ドレインセレクトラインDSLに沿って一列に配列されたドレイン領域に連結されたドレインコンタクトプラグ120も同様にジグザグに配列される。その結果、互いに隣接するドレインコンタクトプラグたち120との間の最短距離が増加され、互いに隣接するドレインコンタクトプラグ120同士で連結されるような不良を改善することができる。

【0027】

ビットラインBL(133)は、活性領域Aのそれぞれの上部に形成される。また、ビットラインBL(133)は、ドレインコンタクトプラグ120を覆うエッチング停止膜及び第2層間絶縁膜を貫通してドレインコンタクトプラグ120の上部面を露出させ、活性領域Aと同じ方向に沿って形成されたトレンチ132(図6参照)の内部に形成される。

【0028】

一方、ソースコンタクトライン150は、ソースセレクトラインSSLの間の素子分離領域B、およびソース領域を露出させるトレンチの内部に形成される。ここで、トレンチは、ソースセレクトラインSSLと同じ方向に沿って形成される。このようなトレンチの内部に形成されたソースコンタクトライン150は、ソースセレクトラインSSLの間のソース領域に共通に連結される。

【0029】

図4ないし図7は、本発明の実施例による半導体素子の製造方法を説明するために、図3に示された線I−Iの方向に沿って切り取った断面図である。図4(a)を参照すると、ドレイン領域105のような接合領域が形成された半導体基板101を提供する。 NAND型フラッシュメモリ素子の接合領域を形成するための具体的な工程の一例を説明すると以下の通りである。

【0030】

まず、半導体基板101の上部にトンネル絶縁膜とフローティングゲート用導電膜を蒸着して、フローティングゲート用導電膜の上部に複数の素子分離マスクパターンを形成する。この後、素子分離マスクパターンの間に露出されたフローティングゲート用導電膜、トンネル絶縁膜を除去して半導体基板101の素子分離領域Bを露出させる。

【0031】

次に、素子分離領域Bをエッチングして半導体基板101にトレンチを形成し、トレンチの内部を絶縁物で埋め込む。化学的機械的研磨(CMP:Chemical Mechanical Polishing)などの平坦化工程で素子分離マスクパターンが露出されるように絶縁物を平坦化させる。次に、素子分離マスクパターンを除去し、絶縁物の高さをエッチング工程で制御してターゲットとする高さを有する素子分離膜103を形成する。半導体基板101の活性領域Aは、素子分離膜103を挟んで分離される。この後、誘電体膜、コントロールゲート用導電膜を蒸着する。コントロールゲート用導電膜蒸着の前に、セレクトライン(DSLおよびSSL)が形成されるべき領域の誘電体膜には、フローティングゲート用導電膜を露出させるコンタクトホールが形成される。その後、コントロールゲート用導電膜上にゲートハードマスクパターンを形成し、ゲートハードマスクパターンの間のコントロールゲート用導電膜、誘電体膜、フローティングゲート用導電膜を除去して複数のワードラインWL、セレクトライン(DSLおよびSSL)を形成する。この後、ワードラインWLとセレクトライン(DSLおよびSSL)の間の活性領域Aに不純物を注入し、セル結合領域、ソース領域、ドレイン領域105を形成する。

【0032】

ドレイン領域105の上部には、少なくとも一層の第1層間絶縁膜107を形成する。第1層間絶縁膜107は、下部構造(105、DSL、SSL、WL、105)を覆うように形成される。通常、第1層間絶縁膜107は酸化膜である。この後、第1層間絶縁膜107の上部に第1ハードマスク膜HM1を形成する。第1ハードマスク膜HM1は、第1層間絶縁膜107のエッチング選択比が他の物質で形成されることが好ましく、ACL(Amorphous Carbon Layer109)およびSiON111の積層構造で形成することがてきる。次に、第1ハードマスク膜HM1の上部に第1フォトレジストパターン113を形成する。第1フォトレジストパターン113は、後続工程でコンタクトホール115が形成されるべき領域を露出させる。

【0033】

図4(b)を参照すると、第1フォトレジストパターン113の間で露出された第1ハードマスク膜HM1を除去して第1層間絶縁膜107を露出させ、露出した第1層間絶縁膜107を除去し、ドレイン領域105を露出させ、第1層間絶縁膜107を貫通するコンタクトホール115を形成する。ドレイン領域105を露出させるコンタクトホール115は、ドレインコンタクトホールとなる。この後、残留する第1フォトレジストパターン113及び第1ハードマスク膜HM1を除去する。

【0034】

図5(a)を参照すると、コンタクトホール115の表面および第1層間絶縁膜107の表面に沿って第1導電膜117を形成する。この後、第1導電膜117の上部に第2導電膜119を形成し、コンタクトホール115の内部を第2導電膜119で埋め込む。

【0035】

第1導電膜117と第2導電膜119は、互いに異なる導電性物質であり、特に、リセス領域を形成するためにコンタクトホール115の側壁と第2導電膜119との間に形成された第1導電膜117の一部を除去する後続のエッチング工程で利用されるエッチング物質に対してエッチング選択比の高い物質で形成されることが好ましい。また、第2導電膜119が金属を含む場合、第1導電膜117は、第2導電膜119からの金属が、第1層間絶縁膜107の内部に拡散しないように防止する役割をするバリアメタル膜になりうる。たとえば、第2導電膜119がタングステンで形成された場合、第1導電膜117は、タングステンの拡散を防止するためのチタン、チタン窒化膜の積層構造で形成されうる。第1導電膜117は、後続のビットライン形成時のコンタクトプラグ120とビットラインのオーバーレイのマージンを十分に確保でき、次に形成されるべきドレインコンタクトプラグ120の抵抗確保のために、100Åないし250Åの厚さで形成されることが好ましい。

【0036】

第1および第2導電膜117、119を形成した後、化学的機械的研磨などの平坦化工程で、第1層間絶縁膜107が露出されるように、第1層間絶縁膜107の上部面上の第1および第2導電膜117、119を除去する。これにより、第1および第2導電膜117、119は、コンタクトホール115の内部のみに残留する。

【0037】

図5(b)を参照すると、第1層間絶縁膜107及び第2導電膜119に比べて第1導電膜117をより速くエッチングするエッチング物質でコンタクトホール115の側壁と第2導電膜119との間に形成された第1導電膜117の一部を除去する。たとえば、第1層間絶縁膜107が酸化膜で、第2導電膜119がタングステンで、第1導電膜117がチタンおよびチタン窒化膜の積層構造である場合、第1導電膜117 は、タングステンおよび酸化膜に比べて、エッチング選択比の高いBCl3とCl2の混合エッチングガスでエッチングされたり、Cl2エッチングガスによってエッチングされる。これにより、第2導電膜119及び第1層間絶縁膜107は、第1導電膜117をエッチングする間に除去されず、第1導電膜117より突出されるように残留する。そして、第1導電膜117が一部除去された領域にリセス領域Rが形成される。第1導電膜117のエッチング程度は、半導体素子のデザインルールに応じて多様に変更することができる。

【0038】

上述した第1導電膜117のエッチング工程を通じてリセス領域R下部のコンタクトホール115の側壁とコンタクトホール115の底面に沿って形成されたキャッピング部117aと、リセス領域Rを除くコンタクトホール115の内部を埋め込み、キャッピング部117aより突出されるように形成された突出部119aを含むドレインコンタクトプラグ120が形成される。ドレインコンタクトプラグ120は、ドレイン領域105に連結されるようにドレイン領域105の上部に形成される。一方、コンタクトホール115の下部側壁と第2導電膜119との間にリセス領域Rが形成されないようにしてドレインコンタクトプラグ120の下部幅を確保する。

【0039】

図6(a)を参照すると、リセス領域Rが埋め込まれるようドレインコンタクトプラグ120及び第1層間絶縁膜107の上部に物質膜121を形成する。物質膜121は、第1層間絶縁膜107および後続工程で形成される第2層間絶縁膜123のエッチング選択比が異なる物質で形成されることが好ましく、窒化膜も可能である。リセス領域Rを埋め込む物質膜121の一部は、スペーサ121aになり、第1層間絶縁膜107及び突出部119a上部に形成された物質膜121の一部は、後続エッチング工程の際、第1層間絶縁膜107が過度にエッチングされる不良を防止するエッチング停止膜121bとなる。

【0040】

この後、物質膜121の上部に第2層間絶縁膜123を形成する。第2層間絶縁膜123は、酸化膜になりうる。次に、第2層間絶縁膜123の上部に第2ハードマスク膜HM2を形成する。第2ハードマスク膜HM2は、第2層間絶縁膜123とエッチング選択比の異なる物質で形成されることが好ましく、ポリシリコン膜125、ACL127およびSiON129の積層構造で形成することができる。次に、第2ハードマスク膜HM2の上部に第2フォトレジストパターン131を形成する。第2フォトレジストパターン131は、後続工程でトレンチ132が形成されるべき領域を開口させる。

【0041】

図6(b)を参照すると、第2フォトレジストパターン131の間で露出された第2ハードマスク膜HM2を除去し、第2層間絶縁膜123を露出させ、露出された第2層間絶縁膜123をエッチング工程によって除去する。第2層間絶縁膜123を除去するためのエッチング工程を物質膜121の露出時に停止する。次に、露出物質膜121のエッチング工程で除去し、ドレインコンタクトプラグ120を露出させる。これにより、第2層間絶縁膜123と物質膜121を貫通してドレインコンタクトプラグ120を露出させるトレンチ132が形成される。残留する物質膜121は、リセス領域Rを埋め込むスペーサ121a、及び第2層間絶縁膜123と第1層間絶縁膜107との間のエッチング停止膜121bに区分される。トレンチ132の形成の際、トレンチ132と非重畳されたスペーサ121aは、エッチング停止膜121bと連結されて残留することができる。

【0042】

上述のように、本発明は、エッチング停止膜121bを形成するための物質膜121でスペーサ121aを形成するため、スペーサ121aを形成するための別途の工程を行う必要がないため、半導体素子の製造工程を単純化することができる。

【0043】

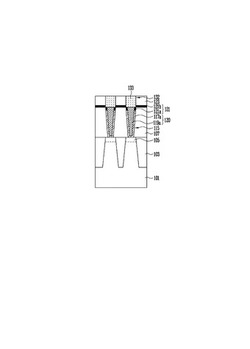

図7を参照すると、残留する第2のハードマスク膜125を除去した後、トレンチ132の内部を導電性物質で埋め込む。導電性物質は、低抵抗導電性物質である銅の場合もある。次に、化学的機械的研磨CMPなどの平坦化工程で第2層間絶縁膜123が露出されるように第2層間絶縁膜123の上部面上の導電性物質を除去する。これにより、導電性物質は、トレンチ132の内部のみに残留して導電性パターンメタルライン133となる。メタルライン133は、第2層間絶縁膜123と物質膜121を貫通してドレインコンタクトプラグ120に連結される。ドレインコンタクトプラグ120を経由してドレイン領域105に連結されたメタルライン133は、NAND型フラッシュメモリ素子のビットラインとなる。

【0044】

本発明に係るスペーサ部121aは、コンタクトホール115の側壁全面に形成されず、キャッピング部117aより突出された突出部119aの上部側壁の縁、すなわちコンタクトホール115の上部側壁のみに形成される。そして、コンタクトホール115の下部全体がドレインコンタクトプラグ120で埋め込まれる。その結果、ドレインコンタクトプラグ120の上部幅の一部をスペーサ部121aの幅だけ減らしても、ドレインコンタクトプラグ120の下部幅を確保することができるため、ドレインコンタクトプラグ120のコンタクト抵抗を改善することができる。そして、ドレインコンタクトプラグ120の上部側壁に沿ってスペーサ121aが形成されるため、互いに絶縁されるように形成されなければならないドレインコンタクトプラグ120とビットライン133との最短距離をスペーサ121aの幅ほど増やすことができる。したがって、ドレインコンタクトプラグ120とビットライン133のオーバーレイマージンをスペーサ121aの幅ほど確保することができる。

【0045】

以上、ドレインコンタクトプラグ120を介してビットライン133及びドレイン領域105を電気的に連結する構造に限って説明したが、コンタクトプラグ下部の導電性配線とコンタクトプラグ上部の導電性配線をコンタクトプラグを介して電気的に連結する場合にも適用することができる。また、コンタクトプラグがライン状に形成される場合にも適用することができる。

【0046】

以上説明したように、本発明の最も好ましい実施の形態について説明したが、本発明は、上記記載に限定されるものではなく、特許請求の範囲に記載され、又は明細書に開示された発明の要旨に基づき、当業者において様々な変形や変更が可能なのはもちろんであり、斯かる変形や変更が、本発明の範囲に含まれることは言うまでもない。

【符号の説明】

【0047】

101 半導体基板、

105 ドレイン領域、

120 コンタクトプラグ、

119a 突出部、

117a キャッピング部、

121 物質膜、

121a スペーサ、

121b エッチング停止膜、

133 ビットライン、

107 第1層間絶縁膜、

123 第2層間絶縁膜、

133 メタルライン

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に関し、特に、絶縁膜を貫通するコンタクトプラグを介して絶縁膜の上部および下部にそれぞれ形成された構造を電気的に連結させる半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体素子は、半導体基板上に積層された複数の導電性パターンと絶縁膜を含む。また、半導体素子は、絶縁膜を挟んで絶縁膜の下部に形成された導電性の下部構造と絶縁膜の上部に形成された導電性の上部構造を電気的に連結させるために絶縁膜を貫通して形成されたコンタクトプラグをさらに含む。

【0003】

以下、NAND型フラッシュメモリ素子のドレイン領域とビットラインを電気的に連結させるコンタクトプラグを例として、下部構造と上部構造とを電気的に連結させるコンタクトプラグについてより具体的に説明する。

【0004】

図1は、NAND型フラッシュメモリ素子のドレイン領域とビットラインを電気的に連結させるドレインコンタクトプラグを示す断面図である。図1を参照すると、NAND型フラッシュメモリ素子は、ドレインセレクトトランジスタ、ソースセレクトトランジスタ、ドレインセレクトトランジスタとソースセレクトトランジスタとの間に直列に連結された複数のメモリセルを含むメモリストリングを複数含んでいる。

【0005】

一方、メモリストリングは、ビットライン19を介してメモリセルのデータを格納するのに必要な電圧を印加するページバッファ部に電気的に連結される。ビットライン19は、ドレインコンタクトプラグ11を経由してメモリストリングのドレイン領域5に電気的に連結される。すなわち、第1層間絶縁膜7の上部に形成されたビットライン19と上部構造は、第1層間絶縁膜7を貫通するドレインコンタクトプラグ11を介して第1層間絶縁膜7の下部に形成されたドレイン領域5という下部構造に電気的に連結されうる。

【0006】

ドレイン領域5は、素子分離膜3によって区画された半導体基板1の活性領域に不純物を注入して形成されたのである。ドレインコンタクトプラグ11は、ドレイン領域5を含む半導体基板1上部に、少なくとも一層の第1層間絶縁膜7を形成する工程、ドレイン領域5が露出するように、第1層間絶縁膜7の一部をエッチングして第1層間絶縁膜7を貫通するドレインコンタクトホール9を形成する工程、およびドレインコンタクトホール9の内部を導電性物質で埋め込む工程を通じて形成される。

【0007】

ビットライン19は、ダマシンスキーム(Damascene Scheme)を用いて形成することができる。ダマシンスキームを利用する場合、ビットライン19は、ドレインコンタクトプラグ11が形成された第1層間絶縁膜7の上部にエッチング停止膜13および第2層間絶縁膜15を積層する工程、エッチング停止膜13が露出するように第2層間絶縁膜15の一部をエッチングした後、露出したエッチング停止膜13をエッチングしてドレインコンタクトプラグ11を露出させるトレンチ17を形成する工程、およびトレンチ17の内部を導電性物質で埋め込む工程を経て形成する。

【0008】

ところが、半導体素子の高集積化のために半導体素子のパターンが30nm以下に狭くなるにつれて、隣接したドレインコンタクトプラグ11間の間隔が狭くなっている。これにより、ドレインコンタクトプラグ11とビットライン19とのオーバーレイマージン(Overlay Margin)が不足し、ドレインコンタクトプラグ11とビットライン19との間の最短距離L1が、設定された値より近く形成されうる。その結果、互いに絶縁されなければならないドレインコンタクトプラグ11とビットライン19間のショートにより、漏れ電流(Leakage)が発生し、半導体素子が誤動作することになる。

【0009】

図2は、図1において、上述したショート問題を改善できるNAND型フラッシュメモリ素子の断面図である。図2に示されたNAND型フラッシュメモリ素子のドレインコンタクトプラグ21と、スペーサ20以外の他の構成は、図1に図示しているものと同様である。図2の構成要素のうち、図1に示された構成要素と同一の構成要素は、図1に示された構成要素と同一の符号であり、図1で上述した方法と同じ方法によって形成される。

【0010】

図2を参照すると、互いに絶縁されなければならないドレインコンタクトプラグ21とビットライン19間のショートを改善するために、ドレインコンタクトホール9を形成した後、ドレインコンタクトホール9の側壁全面に絶縁膜でスペーサ20を形成する。この後、スペーサ20が形成されたドレインコンタクトホール9の内部を導電性物質で埋め込み、ドレインコンタクトプラグ21を形成する。これにより、ドレインコンタクトプラグ21とビットライン19との間の最短距離L2をスペーサ20の幅ほど増加させることができる。これにより、ドレインコンタクトプラグ21とビットライン19のオーバーレイーマージンが改善され、互いに絶縁されなければならないドレインコンタクトプラグ21とビットライン19間のショートの発生を改善することができる。しかし、ドレインコンタクトホール10の側壁にスペーサ20をさらに形成する場合、スペーサ20を形成するための工程を追加しなければならにため、工程が複雑になるという短所がある。そして、スペーサ20の幅によりドレインコンタクトプラグ21の下部の幅が狭くなり、ドレインコンタクトプラグ21のコンタクト抵抗が減少するという問題がある。

【発明の概要】

【発明が解決しようとする課題】

【0011】

したがって、本発明は、上記問題を解決するために案出された発明であり、その目的は絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供することである。

【課題を解決するための手段】

【0012】

前記目的を達成するために本発明の第1実施例による半導体素子は、半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグ、及び前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサを含む。

【0013】

また、本発明の第2実施例による半導体素子は、半導体基板の上部に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成された導電膜と、前記コンタクトホール内で前記導電膜の下部側壁の縁と前記導電膜の底面を取り囲むバリアメタル膜、および前記コンタクトホール内で前記導電膜の上部側壁を部分的に覆うスペーサを含む。

【0014】

さらに、本発明の実施例による半導体素子の製造方法は、半導体基板の上部に第1層間絶縁膜を形成する段階と、前記第1層間絶縁膜を貫通するコンタクトホールを形成する段階と、前記コンタクトホールの内部の上部側壁の縁にリセスされたコンタクトプラグを形成する段階、及び前記コンタクトプラグの前記上部側壁を部分的に覆うスペーサを形成する段階と、を含む。

【発明の効果】

【0015】

以上のように、本発明によれば、スペーサをコンタクトプラグの側壁全面に形成することなく、コンタクトプラグの上部(Top Portion)の側壁に限って形成することで、コンタクトプラグの下部の幅を確保できるので、コンタクトプラグの抵抗を改善することができる。

【0016】

また、本発明によれば、コンタクトプラグの上部側壁にスペーサを形成することで、互いに絶縁されるように形成されるべきコンタクトプラグとコンタクトプラグの上部に形成される導電性パターンのオーバーレイマージンをスペーサの幅ほど確保することができる。

【0017】

そして、本発明によれば、スペーサとエッチング停止膜を同じ工程を通じて同じ物質膜で形成することで、スペーサを形成するための別の工程を施す必要がないため、工数を低減し、半導体素子の製造に要求されるコストを削減することができる。

【図面の簡単な説明】

【0018】

【図1】NAND型フラッシュメモリ素子のドレイン領域とビットラインを電気的に連結させるドレインコンタクトプラグを示す断面図である。

【図2】図1に示したNAND型フラッシュメモリ素子のショートの問題を改善するための他のNAND型フラッシュメモリ素子の断面図である。

【図3】本発明の実施例による半導体素子の平面図である。

【図4】本発明の実施例による半導体素子の製造方法を説明するために、図3に示した線I−Iの方向に沿って切り取った断面図である。

【図5】本発明の実施例による半導体素子の製造方法を説明するために、図3に示した線I−Iの方向に沿って切り取った断面図である。

【図6】本発明の実施例による半導体素子の製造方法を説明するために、図3に示した線I−Iの方向に沿って切り取った断面図である。

【図7】本発明の実施例による半導体素子の製造方法を説明するために、図3に示した線I−Iの方向に沿って切り取った断面図である。

【発明を実施するための最良の形態】

【0019】

以下、添付図面を参照して本発明の好ましい実施例を説明する。ただし、本発明は、以下開示される実施例に限定されるものではなく、異なる様々な形態具現することができ、本発明の範囲は、後述する実施例に限定されるものではない。本実施例は本発明の開示が完全になるようにして通常の知識を有する者に発明の範疇を完全に知らせるために提供されるものであり、本発明の範囲は、本願の特許請求の範囲によって理解されるべきである。

【0020】

一方、ある膜が他の膜または半導体基板の"上"にあると記載されている場合、前記ある膜とは、前記他の膜または半導体基板に直接接触して存在することができ、またはその間に第3の膜が介在される場合がある。また、図面では、それぞれの層の厚さや大きさは、説明の便宜と明確性のために誇張された。図面において同じ符号は同じ要素を指す。

【0021】

図3は、本発明の実施例による半導体素子の平面図である。特に、図3は、NAND型フラッシュメモリ素子を例として示した。図3を参照すると、本発明の実施例によるNAND型フラッシュメモリ素子のセルアレイは、トレンチまたは素子分離膜が形成される素子分離領域Bと素子分離領域Bによって区分される活性領域Aを含む。

【0022】

素子分離領域Bと活性領域Aは、互いに平行に交互に定義される。そして、素子分離領域Bと、活性領域Aに交差するように、半導体基板の上部にドレインセレクトラインDSL、ソースセレクトラインSSL、およびワードラインWLを形成する。互いに隣り合うドレインセレクトラインDSLとソースセレクトラインSSLとの間には、複数のワードラインWLが形成される。

【0023】

一般に、ドレインセレクトラインDSL同士が互いに隣り合うように配置され、かつ、ソースセレクトラインSSL同士が隣り合うように配置される。セレクトライン(DSL、およびSSL)とワードラインWLとの間の活性領域Aには不純物が注入され、接合領域が形成される。ここで、ドレインセレクトラインDSLの間に形成される接合領域は、メモリストリングSTのドレイン領域となり、ソースセレクトラインSSLの間に形成される接合領域は、メモリストリングSTのソース領域となる。

【0024】

ドレインセレクトラインDSLと活性領域Aとの交差部に形成されたドレインセレクトトランジスタ、ソースセレクトラインSSLと活性領域Aとの交差部に形成されたソースセレクトトランジスタ、互いに隣り合うドレインセレクトトランジスタとソースセレクトトランジスタとの間のワードラインWLと活性領域Aとの交差部に形成された複数のメモリセルが直列に連結されて、一つのメモリストリングSTを構成する。それぞれのメモリストリングSTは、ドレインコンタクトプラグ120を介して、それに対応するビットラインBL(133)に電気的に連結され、ソースコンタクトライン150を介して共通ソース電圧が印加される金属配線(図示せず)に電気的に連結される。

【0025】

ビットラインBL(133)は、活性領域Aの上部に形成され、活性領域Aに平行に形成される。そして、ビットラインBL(133)は、メモリセルのデータを格納するのに必要な電圧を印加するページバッファ部(図示せず)とメモリストリングSTと、を連結する。

【0026】

前記ドレインコンタクトプラグ120は、ドレインセレクトラインDSLの間の活性領域Aのそれぞれの上部に形成される。そして、ドレインコンタクトプラグ120は、ドレインセレクトラインDSL、ソースセレクトラインSSL、ワードラインWL、素子分離領域B、活性領域A、およびソースコンタクトプラグ150などの下部構造を覆う少なくとも一層の第1層間絶縁膜を貫通して、活性領域Aの表面に形成されたドレイン領域に連結される。そして、ドレインコンタクトプラグ120は、第1層間絶縁膜をエッチングしてドレイン領域を露出させるコンタクトホールの内部に形成されるが、コンタクトホールを形成するためのエッチング工程の際、エッチングマージンを確保するために、ドレインセレクトラインDSLの間のコンタクトホールをジグザグに配列する。これにより、ドレインセレクトラインDSLに沿って一列に配列されたドレイン領域に連結されたドレインコンタクトプラグ120も同様にジグザグに配列される。その結果、互いに隣接するドレインコンタクトプラグたち120との間の最短距離が増加され、互いに隣接するドレインコンタクトプラグ120同士で連結されるような不良を改善することができる。

【0027】

ビットラインBL(133)は、活性領域Aのそれぞれの上部に形成される。また、ビットラインBL(133)は、ドレインコンタクトプラグ120を覆うエッチング停止膜及び第2層間絶縁膜を貫通してドレインコンタクトプラグ120の上部面を露出させ、活性領域Aと同じ方向に沿って形成されたトレンチ132(図6参照)の内部に形成される。

【0028】

一方、ソースコンタクトライン150は、ソースセレクトラインSSLの間の素子分離領域B、およびソース領域を露出させるトレンチの内部に形成される。ここで、トレンチは、ソースセレクトラインSSLと同じ方向に沿って形成される。このようなトレンチの内部に形成されたソースコンタクトライン150は、ソースセレクトラインSSLの間のソース領域に共通に連結される。

【0029】

図4ないし図7は、本発明の実施例による半導体素子の製造方法を説明するために、図3に示された線I−Iの方向に沿って切り取った断面図である。図4(a)を参照すると、ドレイン領域105のような接合領域が形成された半導体基板101を提供する。 NAND型フラッシュメモリ素子の接合領域を形成するための具体的な工程の一例を説明すると以下の通りである。

【0030】

まず、半導体基板101の上部にトンネル絶縁膜とフローティングゲート用導電膜を蒸着して、フローティングゲート用導電膜の上部に複数の素子分離マスクパターンを形成する。この後、素子分離マスクパターンの間に露出されたフローティングゲート用導電膜、トンネル絶縁膜を除去して半導体基板101の素子分離領域Bを露出させる。

【0031】

次に、素子分離領域Bをエッチングして半導体基板101にトレンチを形成し、トレンチの内部を絶縁物で埋め込む。化学的機械的研磨(CMP:Chemical Mechanical Polishing)などの平坦化工程で素子分離マスクパターンが露出されるように絶縁物を平坦化させる。次に、素子分離マスクパターンを除去し、絶縁物の高さをエッチング工程で制御してターゲットとする高さを有する素子分離膜103を形成する。半導体基板101の活性領域Aは、素子分離膜103を挟んで分離される。この後、誘電体膜、コントロールゲート用導電膜を蒸着する。コントロールゲート用導電膜蒸着の前に、セレクトライン(DSLおよびSSL)が形成されるべき領域の誘電体膜には、フローティングゲート用導電膜を露出させるコンタクトホールが形成される。その後、コントロールゲート用導電膜上にゲートハードマスクパターンを形成し、ゲートハードマスクパターンの間のコントロールゲート用導電膜、誘電体膜、フローティングゲート用導電膜を除去して複数のワードラインWL、セレクトライン(DSLおよびSSL)を形成する。この後、ワードラインWLとセレクトライン(DSLおよびSSL)の間の活性領域Aに不純物を注入し、セル結合領域、ソース領域、ドレイン領域105を形成する。

【0032】

ドレイン領域105の上部には、少なくとも一層の第1層間絶縁膜107を形成する。第1層間絶縁膜107は、下部構造(105、DSL、SSL、WL、105)を覆うように形成される。通常、第1層間絶縁膜107は酸化膜である。この後、第1層間絶縁膜107の上部に第1ハードマスク膜HM1を形成する。第1ハードマスク膜HM1は、第1層間絶縁膜107のエッチング選択比が他の物質で形成されることが好ましく、ACL(Amorphous Carbon Layer109)およびSiON111の積層構造で形成することがてきる。次に、第1ハードマスク膜HM1の上部に第1フォトレジストパターン113を形成する。第1フォトレジストパターン113は、後続工程でコンタクトホール115が形成されるべき領域を露出させる。

【0033】

図4(b)を参照すると、第1フォトレジストパターン113の間で露出された第1ハードマスク膜HM1を除去して第1層間絶縁膜107を露出させ、露出した第1層間絶縁膜107を除去し、ドレイン領域105を露出させ、第1層間絶縁膜107を貫通するコンタクトホール115を形成する。ドレイン領域105を露出させるコンタクトホール115は、ドレインコンタクトホールとなる。この後、残留する第1フォトレジストパターン113及び第1ハードマスク膜HM1を除去する。

【0034】

図5(a)を参照すると、コンタクトホール115の表面および第1層間絶縁膜107の表面に沿って第1導電膜117を形成する。この後、第1導電膜117の上部に第2導電膜119を形成し、コンタクトホール115の内部を第2導電膜119で埋め込む。

【0035】

第1導電膜117と第2導電膜119は、互いに異なる導電性物質であり、特に、リセス領域を形成するためにコンタクトホール115の側壁と第2導電膜119との間に形成された第1導電膜117の一部を除去する後続のエッチング工程で利用されるエッチング物質に対してエッチング選択比の高い物質で形成されることが好ましい。また、第2導電膜119が金属を含む場合、第1導電膜117は、第2導電膜119からの金属が、第1層間絶縁膜107の内部に拡散しないように防止する役割をするバリアメタル膜になりうる。たとえば、第2導電膜119がタングステンで形成された場合、第1導電膜117は、タングステンの拡散を防止するためのチタン、チタン窒化膜の積層構造で形成されうる。第1導電膜117は、後続のビットライン形成時のコンタクトプラグ120とビットラインのオーバーレイのマージンを十分に確保でき、次に形成されるべきドレインコンタクトプラグ120の抵抗確保のために、100Åないし250Åの厚さで形成されることが好ましい。

【0036】

第1および第2導電膜117、119を形成した後、化学的機械的研磨などの平坦化工程で、第1層間絶縁膜107が露出されるように、第1層間絶縁膜107の上部面上の第1および第2導電膜117、119を除去する。これにより、第1および第2導電膜117、119は、コンタクトホール115の内部のみに残留する。

【0037】

図5(b)を参照すると、第1層間絶縁膜107及び第2導電膜119に比べて第1導電膜117をより速くエッチングするエッチング物質でコンタクトホール115の側壁と第2導電膜119との間に形成された第1導電膜117の一部を除去する。たとえば、第1層間絶縁膜107が酸化膜で、第2導電膜119がタングステンで、第1導電膜117がチタンおよびチタン窒化膜の積層構造である場合、第1導電膜117 は、タングステンおよび酸化膜に比べて、エッチング選択比の高いBCl3とCl2の混合エッチングガスでエッチングされたり、Cl2エッチングガスによってエッチングされる。これにより、第2導電膜119及び第1層間絶縁膜107は、第1導電膜117をエッチングする間に除去されず、第1導電膜117より突出されるように残留する。そして、第1導電膜117が一部除去された領域にリセス領域Rが形成される。第1導電膜117のエッチング程度は、半導体素子のデザインルールに応じて多様に変更することができる。

【0038】

上述した第1導電膜117のエッチング工程を通じてリセス領域R下部のコンタクトホール115の側壁とコンタクトホール115の底面に沿って形成されたキャッピング部117aと、リセス領域Rを除くコンタクトホール115の内部を埋め込み、キャッピング部117aより突出されるように形成された突出部119aを含むドレインコンタクトプラグ120が形成される。ドレインコンタクトプラグ120は、ドレイン領域105に連結されるようにドレイン領域105の上部に形成される。一方、コンタクトホール115の下部側壁と第2導電膜119との間にリセス領域Rが形成されないようにしてドレインコンタクトプラグ120の下部幅を確保する。

【0039】

図6(a)を参照すると、リセス領域Rが埋め込まれるようドレインコンタクトプラグ120及び第1層間絶縁膜107の上部に物質膜121を形成する。物質膜121は、第1層間絶縁膜107および後続工程で形成される第2層間絶縁膜123のエッチング選択比が異なる物質で形成されることが好ましく、窒化膜も可能である。リセス領域Rを埋め込む物質膜121の一部は、スペーサ121aになり、第1層間絶縁膜107及び突出部119a上部に形成された物質膜121の一部は、後続エッチング工程の際、第1層間絶縁膜107が過度にエッチングされる不良を防止するエッチング停止膜121bとなる。

【0040】

この後、物質膜121の上部に第2層間絶縁膜123を形成する。第2層間絶縁膜123は、酸化膜になりうる。次に、第2層間絶縁膜123の上部に第2ハードマスク膜HM2を形成する。第2ハードマスク膜HM2は、第2層間絶縁膜123とエッチング選択比の異なる物質で形成されることが好ましく、ポリシリコン膜125、ACL127およびSiON129の積層構造で形成することができる。次に、第2ハードマスク膜HM2の上部に第2フォトレジストパターン131を形成する。第2フォトレジストパターン131は、後続工程でトレンチ132が形成されるべき領域を開口させる。

【0041】

図6(b)を参照すると、第2フォトレジストパターン131の間で露出された第2ハードマスク膜HM2を除去し、第2層間絶縁膜123を露出させ、露出された第2層間絶縁膜123をエッチング工程によって除去する。第2層間絶縁膜123を除去するためのエッチング工程を物質膜121の露出時に停止する。次に、露出物質膜121のエッチング工程で除去し、ドレインコンタクトプラグ120を露出させる。これにより、第2層間絶縁膜123と物質膜121を貫通してドレインコンタクトプラグ120を露出させるトレンチ132が形成される。残留する物質膜121は、リセス領域Rを埋め込むスペーサ121a、及び第2層間絶縁膜123と第1層間絶縁膜107との間のエッチング停止膜121bに区分される。トレンチ132の形成の際、トレンチ132と非重畳されたスペーサ121aは、エッチング停止膜121bと連結されて残留することができる。

【0042】

上述のように、本発明は、エッチング停止膜121bを形成するための物質膜121でスペーサ121aを形成するため、スペーサ121aを形成するための別途の工程を行う必要がないため、半導体素子の製造工程を単純化することができる。

【0043】

図7を参照すると、残留する第2のハードマスク膜125を除去した後、トレンチ132の内部を導電性物質で埋め込む。導電性物質は、低抵抗導電性物質である銅の場合もある。次に、化学的機械的研磨CMPなどの平坦化工程で第2層間絶縁膜123が露出されるように第2層間絶縁膜123の上部面上の導電性物質を除去する。これにより、導電性物質は、トレンチ132の内部のみに残留して導電性パターンメタルライン133となる。メタルライン133は、第2層間絶縁膜123と物質膜121を貫通してドレインコンタクトプラグ120に連結される。ドレインコンタクトプラグ120を経由してドレイン領域105に連結されたメタルライン133は、NAND型フラッシュメモリ素子のビットラインとなる。

【0044】

本発明に係るスペーサ部121aは、コンタクトホール115の側壁全面に形成されず、キャッピング部117aより突出された突出部119aの上部側壁の縁、すなわちコンタクトホール115の上部側壁のみに形成される。そして、コンタクトホール115の下部全体がドレインコンタクトプラグ120で埋め込まれる。その結果、ドレインコンタクトプラグ120の上部幅の一部をスペーサ部121aの幅だけ減らしても、ドレインコンタクトプラグ120の下部幅を確保することができるため、ドレインコンタクトプラグ120のコンタクト抵抗を改善することができる。そして、ドレインコンタクトプラグ120の上部側壁に沿ってスペーサ121aが形成されるため、互いに絶縁されるように形成されなければならないドレインコンタクトプラグ120とビットライン133との最短距離をスペーサ121aの幅ほど増やすことができる。したがって、ドレインコンタクトプラグ120とビットライン133のオーバーレイマージンをスペーサ121aの幅ほど確保することができる。

【0045】

以上、ドレインコンタクトプラグ120を介してビットライン133及びドレイン領域105を電気的に連結する構造に限って説明したが、コンタクトプラグ下部の導電性配線とコンタクトプラグ上部の導電性配線をコンタクトプラグを介して電気的に連結する場合にも適用することができる。また、コンタクトプラグがライン状に形成される場合にも適用することができる。

【0046】

以上説明したように、本発明の最も好ましい実施の形態について説明したが、本発明は、上記記載に限定されるものではなく、特許請求の範囲に記載され、又は明細書に開示された発明の要旨に基づき、当業者において様々な変形や変更が可能なのはもちろんであり、斯かる変形や変更が、本発明の範囲に含まれることは言うまでもない。

【符号の説明】

【0047】

101 半導体基板、

105 ドレイン領域、

120 コンタクトプラグ、

119a 突出部、

117a キャッピング部、

121 物質膜、

121a スペーサ、

121b エッチング停止膜、

133 ビットライン、

107 第1層間絶縁膜、

123 第2層間絶縁膜、

133 メタルライン

【特許請求の範囲】

【請求項1】

半導体基板上に形成された第1層間絶縁膜と、

前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、

前記コンタクトホールの内部に形成されたコンタクトプラグと、

前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、

を含むことを特徴とする半導体素子。

【請求項2】

半導体基板の上部に形成された第1層間絶縁膜と、

前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、

前記コンタクトホールの内部に形成された導電膜と、

前記コンタクトホール内で前記導電膜の下部側壁の縁と前記導電膜の底面を覆うバリアメタル膜と、

前記コンタクトホール内で前記導電膜の上部側壁を部分的に覆うスペーサと、

を含むことを特徴とする半導体素子。

【請求項3】

前記第1層間絶縁膜の上部に形成され、前記スペーサと同一の物質膜で形成されたエッチング停止膜と、

前記エッチング停止膜上部に形成された第2層間絶縁膜と、

前記第2層間絶縁膜および前記エッチング停止膜を貫通するメタルラインと、

をさらに含むことを特徴とする請求項1または2に記載の半導体素子。

【請求項4】

前記スペーサと前記エッチング停止膜は、

前記第1および第2層間絶縁膜とエッチング選択比が異なる物質膜で形成されたことを特徴とする請求項3に記載の半導体素子。

【請求項5】

前記半導体基板は、不純物が注入されたNAND型フラッシュメモリ素子のドレイン領域を含み、

前記メタルラインは、NAND型フラッシュメモリ素子のビットラインであることを特徴とする請求項3に記載の半導体素子。

【請求項6】

前記スペーサと前記エッチング停止膜は、窒化膜で形成され、前記第2層間絶縁膜は酸化膜で形成されたことを特徴とする請求項3に記載の半導体素子。

【請求項7】

前記バリアメタル膜は、チタンおよびチタン窒化膜の積層構造で形成され、前記導電膜は金属膜で形成されたことを特徴とする請求項2に記載の半導体素子。

【請求項8】

前記金属膜は、タングステンを含むことを特徴とする請求項7に記載の半導体素子。

【請求項9】

半導体基板の上部に第1層間絶縁膜を形成する段階と、

前記第1層間絶縁膜を貫通するコンタクトホールを形成する段階と、

前記コンタクトホールの内部に上部側壁縁がリセスされたコンタクトプラグを形成する段階と、

前記コンタクトプラグの前記上部側壁を部分的に覆うスペーサを形成する段階と、

を含むことを特徴とする半導体素子の製造方法。

【請求項10】

前記コンタクトプラグを形成する段階は、

前記第1層間絶縁膜と前記コンタクトホールの表面に沿ってバリアメタル膜を形成する段階と、

前記バリアメタル膜の上部に導電膜を形成し、前記のコンタクトホールの内部を、前記導電膜で埋め込む段階と、

前記第1層間絶縁膜が露出されるように前記バリアメタル膜と前記導電膜を平坦化する段階と、

前記バリアメタル膜の一部をエッチングしてリセス領域を形成する段階と、

を含むことを特徴とする請求項9に記載の半導体素子の製造方法。

【請求項11】

前記バリアメタル膜は、チタンおよびチタン窒化膜の積層構造を含み、

前記導電膜は、タングステンを含むことを特徴とする請求項10に記載の半導体素子の製造方法。

【請求項12】

前記リセス領域を形成する段階は、

BCl3とCl2の混合エッチングガスまたはCl2エッチングガスを介して前記バリアメタル膜をエッチングする段階を含むことを特徴とする請求項10に記載の半導体素子の製造方法。

【請求項13】

前記スペーサを形成する段階は、

前記コンタクトプラグがリセスされた領域が埋め込まれるように前記第1層間絶縁膜上に前記第1層間絶縁膜とエッチング選択比が異なる物質膜を形成し、前記第1層間絶縁膜の上部にエッチング停止膜を形成する段階を含むことを特徴とする請求項9に記載の半導体素子の製造方法。

【請求項14】

前記エッチング停止膜を形成する段階以後、前記エッチング停止膜の上部に第2層間絶縁膜を形成する段階と、

前記第2層間絶縁膜および前記エッチング停止膜を貫通して前記コンタクトプラグと連結されるメタルラインを形成する段階と、

をさらに含むことを特徴とする請求項13に記載の半導体素子の製造方法。

【請求項15】

前記物質膜は窒化膜で形成し、前記第1および第2層間絶縁膜は酸化膜で形成することを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項16】

前記メタルラインを形成する段階は、前記エッチング停止膜が露出するまで前記第2層間絶縁膜をエッチングする段階と、

前記エッチング停止膜の露出領域をエッチングして前記コンタクトプラグを露出させる段階と、

前記第2層間絶縁膜および前記エッチング停止膜がエッチングされた領域を導電性物質で埋め込む段階と、

を含むことを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項17】

前記エッチング停止膜の露出領域をエッチングする段階は、前記コンタクトプラグの前記上部側壁の縁を覆うような前記物質膜が残留されるように実施されることを特徴とする請求項16に記載の半導体素子の製造方法。

【請求項18】

前記第1層間絶縁膜を形成する段階以前に、前記半導体基板の上部にセレクトラインおよびワードラインを形成する段階と、

隣接する前記セレクトラインの間の前記半導体基板内に不純物を注入し、接合領域を形成する段階と、

を含むことを特徴とする請求項9に記載の半導体素子の製造方法。

【請求項1】

半導体基板上に形成された第1層間絶縁膜と、

前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、

前記コンタクトホールの内部に形成されたコンタクトプラグと、

前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、

を含むことを特徴とする半導体素子。

【請求項2】

半導体基板の上部に形成された第1層間絶縁膜と、

前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、

前記コンタクトホールの内部に形成された導電膜と、

前記コンタクトホール内で前記導電膜の下部側壁の縁と前記導電膜の底面を覆うバリアメタル膜と、

前記コンタクトホール内で前記導電膜の上部側壁を部分的に覆うスペーサと、

を含むことを特徴とする半導体素子。

【請求項3】

前記第1層間絶縁膜の上部に形成され、前記スペーサと同一の物質膜で形成されたエッチング停止膜と、

前記エッチング停止膜上部に形成された第2層間絶縁膜と、

前記第2層間絶縁膜および前記エッチング停止膜を貫通するメタルラインと、

をさらに含むことを特徴とする請求項1または2に記載の半導体素子。

【請求項4】

前記スペーサと前記エッチング停止膜は、

前記第1および第2層間絶縁膜とエッチング選択比が異なる物質膜で形成されたことを特徴とする請求項3に記載の半導体素子。

【請求項5】

前記半導体基板は、不純物が注入されたNAND型フラッシュメモリ素子のドレイン領域を含み、

前記メタルラインは、NAND型フラッシュメモリ素子のビットラインであることを特徴とする請求項3に記載の半導体素子。

【請求項6】

前記スペーサと前記エッチング停止膜は、窒化膜で形成され、前記第2層間絶縁膜は酸化膜で形成されたことを特徴とする請求項3に記載の半導体素子。

【請求項7】

前記バリアメタル膜は、チタンおよびチタン窒化膜の積層構造で形成され、前記導電膜は金属膜で形成されたことを特徴とする請求項2に記載の半導体素子。

【請求項8】

前記金属膜は、タングステンを含むことを特徴とする請求項7に記載の半導体素子。

【請求項9】

半導体基板の上部に第1層間絶縁膜を形成する段階と、

前記第1層間絶縁膜を貫通するコンタクトホールを形成する段階と、

前記コンタクトホールの内部に上部側壁縁がリセスされたコンタクトプラグを形成する段階と、

前記コンタクトプラグの前記上部側壁を部分的に覆うスペーサを形成する段階と、

を含むことを特徴とする半導体素子の製造方法。

【請求項10】

前記コンタクトプラグを形成する段階は、

前記第1層間絶縁膜と前記コンタクトホールの表面に沿ってバリアメタル膜を形成する段階と、

前記バリアメタル膜の上部に導電膜を形成し、前記のコンタクトホールの内部を、前記導電膜で埋め込む段階と、

前記第1層間絶縁膜が露出されるように前記バリアメタル膜と前記導電膜を平坦化する段階と、

前記バリアメタル膜の一部をエッチングしてリセス領域を形成する段階と、

を含むことを特徴とする請求項9に記載の半導体素子の製造方法。

【請求項11】

前記バリアメタル膜は、チタンおよびチタン窒化膜の積層構造を含み、

前記導電膜は、タングステンを含むことを特徴とする請求項10に記載の半導体素子の製造方法。

【請求項12】

前記リセス領域を形成する段階は、

BCl3とCl2の混合エッチングガスまたはCl2エッチングガスを介して前記バリアメタル膜をエッチングする段階を含むことを特徴とする請求項10に記載の半導体素子の製造方法。

【請求項13】

前記スペーサを形成する段階は、

前記コンタクトプラグがリセスされた領域が埋め込まれるように前記第1層間絶縁膜上に前記第1層間絶縁膜とエッチング選択比が異なる物質膜を形成し、前記第1層間絶縁膜の上部にエッチング停止膜を形成する段階を含むことを特徴とする請求項9に記載の半導体素子の製造方法。

【請求項14】

前記エッチング停止膜を形成する段階以後、前記エッチング停止膜の上部に第2層間絶縁膜を形成する段階と、

前記第2層間絶縁膜および前記エッチング停止膜を貫通して前記コンタクトプラグと連結されるメタルラインを形成する段階と、

をさらに含むことを特徴とする請求項13に記載の半導体素子の製造方法。

【請求項15】

前記物質膜は窒化膜で形成し、前記第1および第2層間絶縁膜は酸化膜で形成することを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項16】

前記メタルラインを形成する段階は、前記エッチング停止膜が露出するまで前記第2層間絶縁膜をエッチングする段階と、

前記エッチング停止膜の露出領域をエッチングして前記コンタクトプラグを露出させる段階と、

前記第2層間絶縁膜および前記エッチング停止膜がエッチングされた領域を導電性物質で埋め込む段階と、

を含むことを特徴とする請求項14に記載の半導体素子の製造方法。

【請求項17】

前記エッチング停止膜の露出領域をエッチングする段階は、前記コンタクトプラグの前記上部側壁の縁を覆うような前記物質膜が残留されるように実施されることを特徴とする請求項16に記載の半導体素子の製造方法。

【請求項18】

前記第1層間絶縁膜を形成する段階以前に、前記半導体基板の上部にセレクトラインおよびワードラインを形成する段階と、

隣接する前記セレクトラインの間の前記半導体基板内に不純物を注入し、接合領域を形成する段階と、

を含むことを特徴とする請求項9に記載の半導体素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−169630(P2012−169630A)

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願番号】特願2012−31228(P2012−31228)

【出願日】平成24年2月16日(2012.2.16)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願日】平成24年2月16日(2012.2.16)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

[ Back to top ]