半導体素子及びその製造方法

【課題】干渉現象を減らしてゲートラインの抵抗を減らすことができる半導体素子の製造方法を提供する。

【解決手段】最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、最上部層が金属シリサイド層からなり、前記第1間隔より広い第2間隔で前記半導体基板上に配列される第2ゲートラインと、前記第1ゲートラインの間の前記半導体基板上に形成されてエアギャップを含む第1絶縁膜と、前記第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、前記第2絶縁膜の側壁に形成されたエッチング停止膜と、前記第1ゲートラインの間の空間と前記第2ゲートラインとの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、前記第3絶縁膜の上部に形成されたキャッピング膜と、前記キャッピング膜及び前記第3絶縁膜を貫通して前記第2ゲートラインの間の前記半導体基板に形成された接合領域と繋がれるコンタクトプラグと、を含む。

【解決手段】最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、最上部層が金属シリサイド層からなり、前記第1間隔より広い第2間隔で前記半導体基板上に配列される第2ゲートラインと、前記第1ゲートラインの間の前記半導体基板上に形成されてエアギャップを含む第1絶縁膜と、前記第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、前記第2絶縁膜の側壁に形成されたエッチング停止膜と、前記第1ゲートラインの間の空間と前記第2ゲートラインとの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、前記第3絶縁膜の上部に形成されたキャッピング膜と、前記キャッピング膜及び前記第3絶縁膜を貫通して前記第2ゲートラインの間の前記半導体基板に形成された接合領域と繋がれるコンタクトプラグと、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に関し、特にゲートラインを含む半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体素子は、数多くのトランジスタによって製造される。特に、半導体メモリ素子では数多くのセルトランジスタが稠密で規則的な配列で形成され、メモリの種類によってトランジスタのゲート構造が異なる。例えば、DRAMでセルトランジスタのゲートは、ゲート酸化膜とゲート用導電膜の積層構造で形成され、フラッシュメモリでセルトランジスタのゲートはトンネル酸化膜、フローティングゲート、誘電体膜及びコントロールゲートの積層構造で形成される。メモリセルの配列によって縦方向や列方向にトランジスタのゲートが互いに繋がれて、これにより縦方向や列方向にゲートライン(またはワードライン)が形成される。

【0003】

ゲートラインの間は絶縁膜で満たされて、互いに隣接したゲートラインとゲートラインの間に形成された絶縁膜によって寄生キャパシタが形成される。これにより、ゲートラインに電圧が印加されれば、寄生キャパシタ構造とキャパシタカップリング現象によって隣接したゲートラインの電圧が変動される干渉現象が発生される。このような干渉現象は、集積度向上のためにゲートラインの間の間隔が細くなることによってさらにひどく発生される。

【0004】

また、集積度を高めるためにゲートラインの幅が細くなるため、ゲートラインの抵抗が増加する。これにより、ゲートラインの抵抗を低めるためのさまざまな方案が提示されているが、工程の難易度が増加して再現性を確保しにくいという短所がある。

【発明の概要】

【発明が解決しようとする課題】

【0005】

したがって、本発明は上記問題を解決するために案出されたもので、その目的は、干渉現象を減らしてゲートラインの抵抗を減らすことができる半導体素子の製造方法を提供することである。

【課題を解決するための手段】

【0006】

上記目的を達成するために本発明の実施例による半導体素子は、最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、最上部層が金属シリサイド層からなり、第1間隔より広い第2間隔で半導体基板上に配列される第2ゲートラインと、第1ゲートラインの間の半導体基板上に形成されてエアギャップを含む第1絶縁膜と、第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、第2絶縁膜の側壁に形成されたエッチング停止膜と、第1ゲートラインの間の空間と第2ゲートラインの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、第3絶縁膜上部に形成されたキャッピング膜、及びキャッピング膜及び第3絶縁膜を貫通して第2ゲートラインの間の半導体基板に形成された接合領域と繋がれるコンタクトプラグと、を含む。

【0007】

また、金属シリサイド層はタングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成されることができる。

【0008】

また、エッチング停止膜とコンタクトプラグとの間で形成される第4絶縁膜をさらに含むことができる。

【0009】

また、キャッピング膜が窒化膜からなることができる。

【0010】

また、第1絶縁膜が第1ゲートラインより低い高さで形成されることができる。

【0011】

また、第3絶縁膜が第1及び第2ゲートラインの金属シリサイド層と接触することができる。

【0012】

本発明の実施例による半導体素子の製造方法は、最上部層がシリコン膜からなるゲートラインを半導体基板上に形成する段階と、シリコン膜が露出するようにゲートラインの間に反応防止膜を形成する段階と、シリコン膜の露出した部分をシリサイド層で形成する段階と、反応防止膜を除去する段階、及びシリサイド層を含むゲートラインの間に絶縁膜を形成する段階と、を含む。

【0013】

また、反応防止膜はゲートラインの間でゲートラインの高さより低い高さで形成されることができる。

【0014】

また、反応防止膜は、保護膜及び反応防止絶縁膜の積層構造で形成され、シリサイド層を形成する前に反応防止絶縁膜が除去されることができる。

【0015】

また、反応防止膜を形成する段階は、ゲートラインの表面及び半導体基板の表面に保護膜を形成する段階と、ゲートラインの間の空間が満たされるように保護膜を含む全体構造上に反応防止絶縁膜を形成する段階、及び保護膜及び反応防止絶縁膜がゲートラインの間のみに残るように保護膜及び反応防止絶縁膜をエッチングする段階と、を含む。

【0016】

また、保護膜は酸化膜で形成されることができる。

【0017】

反応防止絶縁膜は、SOC膜またはフォトレジストで形成されることができる。

【0018】

また、保護膜及び反応防止絶縁膜をエッチングする段階は、保護膜及び反応防止絶縁膜がゲートラインの間のみに残るように化学的機械的研磨工程を実施する段階、及び保護膜及び反応防止膜がゲートラインの間でゲートラインの高さより低い高さで残留されるようにエッチバック工程で保護膜及び反応防止膜をエッチングする段階を含む。

【0019】

また、シリサイド層はタングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成されることができる。

【0020】

また、ゲートラインはソースセレクトライン、ワードライン及びドレインセレクトラインを含み、ワードラインの間、ソースセレクトライン及びこれに隣接したワードラインの間、ドレインセレクトライン及びこれに隣接したワードラインの間の絶縁膜内にエアギャップが形成され、ソースセレクトラインの対向する側壁とドレインセレクトラインの対向する側壁には、絶縁膜がスペーサの形態で形成されることができる。

【0021】

また、絶縁膜を形成した後、絶縁膜上にエッチング停止膜を形成する段階、エッチング停止膜上に階間絶縁膜を形成する段階、階間絶縁膜及びエッチング停止膜をエッチングしてコンタクトホールを形成する段階、及びコンタクトホール内にコンタクトプラグを形成する段階をさらに含むことができる。

【0022】

絶縁膜はPE-CVD法を利用してUSG膜で形成されることができ、USG膜はソースガスとしてSiH4ガスを使用し、反応ガスとしてN2Oガスを使用して形成されることができる。SiH4ガスの供給流量を350sccmないし550sccmに設定されることができる。

【発明の効果】

【0023】

以上のように、本発明の実施例によれば、工程を単純化しながらゲートラインに印加される電圧によって隣接したゲートラインの電圧が変動される干渉現象を最小化し、ゲートラインの抵抗を低減することができる。また、ゲートラインを窒化膜で安全に保護することができる。

【図面の簡単な説明】

【0024】

【図1】本発明の実施例による半導体素子の製造方法を説明するための断面図である。

【図2】本発明の実施例による半導体素子の製造方法を説明するための断面図である。

【図3】本発明の他の実施例による半導体素子の製造方法を説明するための断面図である。

【図4】本発明の他の実施例による半導体素子の製造方法を説明するための断面図である。

【発明を実施するための形態】

【0025】

以下、添付された図面を参照して本発明の好ましい実施例について説明する。しかし、本発明は以下開示される実施例に限定されるのではなく、互いに異なる多様な形態に具現されることができ、本発明の範囲が次に述べる実施例に限定されるのではない。ただし、本実施例は本発明の開示を完全にさせて通常の知識を有する者に発明の範疇を完全に知らせるために提供されるものであり、本発明の範囲は本願特許請求の範囲によって理解されなければならない。

【0026】

図1(a)ないし図2(d)は、本発明の実施例による半導体素子の製造方法を説明するための断面図である。図1(a)を参照すれば、最上部層がシリコン膜109からなるゲートラインSSL、WL0〜WLn、DSLが半導体基板101上に形成される。より具体的に説明すれば次のようである。

【0027】

NANDフラッシュメモリの場合、ドレインセレクトラインDSL、ワードラインWL0〜WLn及びソースセレクトラインSSLを含むゲートラインが形成される。

【0028】

前記ゲートラインは、セル領域に形成され、周辺回路領域には高電圧トランジスタ及び低電圧トランジスタのゲートライン(図示せず)が形成されることができる。ゲートラインを形成するために次の工程が進行されることができる。

【0029】

まず、半導体基板101内にウェル(図示せず)が形成されて、半導体基板101の全体表面にトンネル絶縁膜103が形成される。この時、周辺回路領域には高電圧トランジスタや低電圧トランジスタのためのゲート絶縁膜が形成される。トンネル絶縁膜103上に第1シリコン層105を形成する。第1シリコン層105は非晶質シリコン層、ポリシリコン層またはこれらの積層構造で形成されることができる。また、第1シリコン層105には3価不純物や5価不純物が添加されることができる。

【0030】

次に、素子分離領域を定義する素子分離マスクをエッチングマスクとして使用するエッチング工程で第1シリコン層105をエッチングする。これにより、第1シリコン層105は平行な多数のシリコンラインにパターニングされる。

【0031】

次に、トンネル絶縁膜103及び半導体基板101をエッチングして素子分離領域に平行なライン形態のトレンチ(図示せず)を形成する。トレンチが満たされるように絶縁膜が形成され、絶縁膜がトレンチ上のみに残留されるように絶縁膜がエッチングされる。これにより、素子分離膜(図示せず)が形成される。

【0032】

全体構造上に誘電体膜107が形成される。誘電体膜107は酸化膜/窒化膜/酸化膜の積層構造で形成され、酸化膜や窒化膜がこれらより高い誘電常数値を持つ絶縁膜で取り替えられる。セレクトラインDSL、SSLが形成される領域で誘電体膜107の一部がエッチングされる。これにより、セレクトラインDSL、SSLが形成される領域で第1シリコン層105の一部が露出される。

【0033】

誘電体膜107の上部に第2シリコン層109及びハードマスク膜111が形成される。第2シリコン層109は、ドープトポリシリコン層で形成することが好ましい。

【0034】

次に、第1シリコン層105がパターニングされた一方向と交差する方向にハードマスク膜111、第2シリコン層109及び誘電体膜107をパターニングする。これにより、平行な多数のコントロールゲートが形成される。引き続いて、第1シリコン層105をエッチングする。その結果、半導体基板101上には多数のゲートラインSSL、WL0〜WLn、DSLが形成される。ハードマスク膜111は後続工程で除去されるのでゲートラインの一部になれない。したがって、ゲートラインSSL、WL0〜WLn、DSLの最上部層は第2シリコン層109になる。

【0035】

一方、誘電体膜107の一部がエッチングされた状態で第2シリコン層109が形成されるから、セレクトラインDSL、SSLの第1シリコン層105と第2シリコン層109は、誘電体膜107のエッチングされた部分を通じて互いに繋がれる。

【0036】

ゲートラインSSL、WL0〜WLn、DSLの間の半導体基板101にはイオン注入工程によって接合領域113が形成される。接合領域113は5価不純物を注入して形成することができる。

【0037】

上記において、セレクトラインDSL、SSLは、ワードラインWL0〜WLnより広い幅で形成されて、セレクトラインDSL、SSLの間隔はワードラインWL0〜WLnの間隔より広い。ここで、間隔によってワードラインWL0〜WLは第1間隔に配列された第1ゲートライングループに定義され、セレクトラインDSL、SSLは第1間隔より広い第2間隔に配列された第2ゲートライングループに定義されることができる。一対の第1ゲートライングループの間には一対のドレインセレクトラインDSLやソースセレクトラインSSLを含む第2ゲートライングループが配置される。

【0038】

図1(b)を参照すれば、ゲートラインSSL、WL0〜WLn、DSLを含む全体構造上にスペーサ用絶縁膜を形成した後、エッチバック工程を施す。これにより、セレクトラインDSL、SSLの対向する側壁には絶縁膜スペーサ115aが形成される。そして、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間と、ワードラインWL0〜WLnの間は間隔が狭いため、スペーサ用絶縁膜115bが残留される。これにより、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間とワードラインWL0〜WLnの間はスペーサ用絶縁膜115bで満たされる。

【0039】

一方、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間と、ワードラインWL0〜WLnの間は間隔が狭くて、絶縁膜を形成する過程でゲートラインDSL、SSL、WL0〜WLnの上部縁に絶縁膜のオーバーハング(Overhang)が形成されるため、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間とワードラインWL0〜WLnの間はスペーサ用絶縁膜115bで完全に満たされず、エアギャップのようなエアギャップ117が形成される。エアギャップ117が形成されることによってワードラインWL0〜WLnの間の寄生キャパシタンス値が低くなるため、ワードラインWL0〜WLnの間の干渉現象を最小化することができる。

【0040】

スペーサ用絶縁膜115a、115bが形成されることによって、セレクトラインDSL、SSLの間の接合領域113の一部が露出され、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間とワードラインWL0〜WLnの間の接合領域はスペーサ用絶縁膜115bによって覆われる。

【0041】

図1(c)を参照すれば、スペーサ用絶縁膜115a、115bを含む全体構造上に第1エッチング停止膜119及び第1階間絶縁膜121を順次形成する。ここで、第1エッチング停止膜119は窒化膜で形成することができ、ゲートラインDSL、SSL、WL0〜WLnによる段差が維持されることができるほどの厚さで全体構造の表面に形成される。

【0042】

図2(a)を参照すれば、ゲートラインSSL、WL0〜WLn、DSLの最上部層であるシリコン層109の上部全体表面と側壁の一部を露出させるために、第1階間絶縁膜121及び第1エッチング停止膜119ゲートラインSSL、WL0〜WLn、DSLの間のみに残留されるようにエッチングされてハードマスク膜111が除去される。特に、ゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層にあたるコントロールゲート用シリコン層109の側壁が露出されて誘電体膜107は露出されないようにスペーサ用絶縁膜115a、115b、第1階間絶縁膜(121及び第1エッチング停止膜119)をエッチングすることが好ましい。

【0043】

ゲートラインSSL、WL0〜WLn、DSLが形成された領域と形成されていない領域で、第1階間絶縁膜121の表面高さが異なることができる。このため、第1階間絶縁膜121をエッチングした後、ゲートラインSSL、WL0〜WLn、DSLの間に残留する第1絶縁膜121が残留する高さが変わることができる。したがって、化学的機械的研磨工程とエッチバック工程を並行して第1階間絶縁膜121及び第1エッチング停止膜119をエッチングすることが好ましい。

【0044】

まず、ゲートラインSSL、WL0〜WLn、DSLのハードマスク膜111が露出するまで化学的機械的研磨工程を実施すれば、ゲートラインSSL、WL0〜WLn、DSLの間に残留する第1階間絶縁膜121の高さを均一に平坦化することができる。次に、エッチバック工程でスペーサ用絶縁膜115a、115b、第1階間絶縁膜121と第1エッチング停止膜119をエッチングすれば、ゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層109の側壁を均一に露出させることができる。

【0045】

これにより、ゲートラインSSL、WL0〜WLn、DSLの間にスペーサ用絶縁膜115a、115b、第1階間絶縁膜121及び第1エッチング停止膜119がゲートラインSSL、WL0〜WLn、DSLより低い高さで残留される。一方、ワードラインWL0〜WLnの間のスペーサ用絶縁膜115bがエッチバック工程によってエッチングされることによって、スペーサ用絶縁膜115b内に形成されたエアギャップ117が露出されることができる。

【0046】

図2(b)を参照すれば、シリサイド工程を施してコントロールゲート用シリコン層109の露出された部分をシリサイド層123で形成する。具体的に、例を挙げて説明すれば、コントロールゲート用シリコン層109の露出された部分が覆われるように全体構造上に金属物質(例えば、タングステン、コバルトまたはニッケル)を蒸着して金属層を形成する。次に、熱処理を実施すれば、金属層と接触するシリコン層109のシリコンと金属層の金属が反応して金属シリサイド層123が形成される。

【0047】

金属層がタングステンで形成された場合、タングステンシリサイド層が形成されて、金属層がコバルトで形成された場合、コバルトシリサイド層が形成されて、金属層がニッケルで形成された場合、ニッケルシリサイド層が形成される。引き続いて、シリコン層109と反応せず残留する金属層を除去する。

【0048】

スペーサ用絶縁膜115a、115b、第1エッチング停止膜119及び第1階間絶縁膜121によってシリコン層109の上部のみが露出された状態でシリサイド層123が形成されるから、シリサイド層123はゲートラインSSL、WL0〜WLn、DSLの上部のみに自動整列されて形成される。

【0049】

図2(c)を参照すれば、シリサイド層123を含む全体構造上に第2階間絶縁膜125、キャッピング膜127及び第3階間絶縁膜129を順次形成する。第2階間絶縁膜125を形成する時露出されたエアギャップ117の入口が第2階間絶縁膜125のオーバーハングによって再度詰まりつつエアギャップ117が維持される。

【0050】

上記において、キャッピング膜127は後続工程で発生される水素イオンのようなモバイルイオンがゲートラインSSL、WL0〜WLn、DSLへ侵透することを防止するための機能を遂行するために形成される。また、キャッピング膜127は第2エッチング停止膜の機能を遂行することもできる。このようなキャッピング膜127は絶縁膜121、125、129と異なる物質で形成されることができ、具体的に窒化膜で形成されることができる。

【0051】

一方、第2階間絶縁膜125は金属シリサイド層123が露出された状態で金属シリサイド層123を含む全体構造の上部に形成されるので、第2階間絶縁膜125と金属シリサイド層123が直接接触する。すなわち、金属シリサイド層123と第2階間絶縁膜125との間にはハードマスクや他の膜が存在しない。そして、金属シリサイド層123が露出された状態で第2階間絶縁膜125が形成された後、キャッピング膜127が形成されることによって、後続工程で発生される水素イオンのようなモバイルイオンがゲートラインSSL、WL0〜WLn、DSLへ浸透されることをキャッピング膜127で防止することができる。

【0052】

図2(d)を参照すれば、セレクトラインSSL、DSLの間の接合領域113が露出するように、第3階間絶縁膜129、第2エッチング停止膜127、第2階間絶縁膜125、第1階間絶縁膜121及び第1エッチング停止膜119を順次エッチングしてコンタクトホールを形成する。引き続き、コンタクトホールの内部を導電性物質で満たしてコンタクトプラグ131を形成する。

【0053】

上記実施例によって形成された半導体素子を構造的側面からよく見ると、第1ゲートライングループに含まれた第1ゲートラインWL0〜WLnは、最上部層が金属シリサイド層123からなり、半導体基板101上に第1間隔に配列される。第2ゲートライングループに含まれた第2ゲートライン(DSLまたはSSL)は、最上部層が金属シリサイド層123からなり、第1間隔より広い第2間隔で半導体基板101上に配列される。

【0054】

第1ゲートラインWL0〜WLnの間の半導体基板101上には、エアギャップ117を含む第1絶縁膜115bが形成される。第2ゲートライン(DSLまたはSSL)の対向する側壁上には第2絶縁膜115aが形成されて、第2絶縁膜115aの側壁にはエッチング停止膜119が形成される。

【0055】

第1ゲートラインWL0〜WLnの間の空間と第2ゲートラインDSL、SSLの間の空間が満たされるように全体構造上に第3絶縁膜125が形成されて、第3絶縁膜125の上部にキャッピング膜127が形成される。キャッピング膜127は窒化膜で形成されることができ、第1及び第2ゲートラインSSL、WL0〜WLn、SSLの全体上部に形成される。

【0056】

第2ゲートラインDSL、SSLの間の半導体基板101に形成された接合領域とキャッピング膜127及び第3絶縁膜125を貫通して繋がれるコンタクトプラグ131が形成される。エッチング停止膜119とコンタクトプラグ121との間には第4絶縁膜121がさらに形成されることができる。

【0057】

第1及び第2ゲートラインSSL、WL0〜WLn、SSLの最上部層は、金属シリサイド層123からなり、金属シリサイド層123上にはハードマスクが存在しないから金属シリサイド層123が第2絶縁膜125と接触する。

【0058】

上記製造方法と構造により、ゲートラインSSL、WL0〜WLn、DSLの幅が狭くなっても抵抗の低いシリサイド層123を形成することで、ゲートラインSSL、WL0〜WLn、DSLの抵抗を下げることができる。また、第2階間絶縁膜125を形成する時、ワードラインWL0〜WLnの間にエアギャップ117を残留させることができるので、ワードラインWL0〜WLnの間の寄生キャパシタンスを下げてワードラインWL0〜WLnの間の干渉現象を最小化することができる。

【0059】

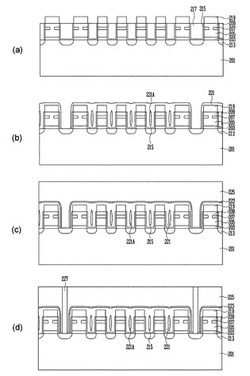

これと異なる方法で干渉現象を最小化してゲートラインの抵抗を下げることができる本発明の他の実施例を説明する。図3(a)ないし図4(d)は、本発明の他の実施例による半導体素子の製造方法を説明するための断面図である。

【0060】

図3(a)を参照すれば、最上部層がシリコン膜209からなるゲートラインSSL、WL0〜WLn、DSLが半導体基板201上に形成される。そして、ゲートラインSSL、WL0〜WLn、DSLの間の半導体基板201には接合領域213を形成する。

【0061】

NANDフラッシュメモリの場合、ゲートラインSSL、WL0〜WLn、DSLは、ソースセレクトラインSSL、ワードラインWL0〜WLn及びドレインセレクトラインDSLを含み、トンネル絶縁膜203、フローティングゲート用シリコン層205、誘電体膜207及びコントロールゲート用シリコン層209の積層構造で形成されることができる。ゲートラインSSL、WL0〜WLn、DSLの上部にはハードマスク膜211が形成されて、ハードマスク膜211は酸化膜で形成することができる。このようなゲートラインSSL、WL0〜WLn、DSL及び接合領域213は図1(a)で説明した方法と同一の方法で形成されることができる。

【0062】

次に、シリサイド工程で金属層がゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層にあたるコントロールゲート用シリコン層209と反応じて、残りのシリコン構造物(例えば、フローティングゲート用シリコン層、半導体基板等)と反応することを防止するための反応防止膜をゲートラインSSL、WL0〜WLn、DSLの間で形成する。より具体的に例を挙げて説明する。

【0063】

図3(b)を参照すれば、ゲートラインSSL、WL0〜WLn、DSLを含む全体構造の表面に保護膜215を形成する。保護膜215は、酸化膜をCVD方式で蒸着して形成することができる。次に、ゲートラインSSL、WL0〜WLn、DSLの間の空間が満たされるように保護膜215を含む全体構造上に反応防止絶縁膜217を形成する。

【0064】

反応防止絶縁膜217は、流動性の良い絶縁膜やSOC(Spin On Carbon)膜やフォトレジストで形成することができる。反応防止絶縁膜217は流動性の良い物質で形成されるから、ゲートラインSSL、WL0〜WLn、DSLの間は反応防止絶縁膜217で完全に満たされてエアギャップは形成されない。

【0065】

保護膜215と反応防止絶縁膜217は、反応防止膜のために形成される。ここで、保護膜215は反応防止絶縁膜217に含まれた不純物がゲートラインSSL、WL0〜WLn、DSLの内部へ侵透することを防止するために形成される。しかし、反応防止膜217の物質によって保護膜215は省略されることができる。

【0066】

図3(c)を参照すれば、ゲートラインSSL、WL0〜WLn、DSL上部のハードマスク膜211が除去されて、コントロールゲート用シリコン層209が露出されるまで化学的機械的研磨工程を施す。これにより、保護膜215と反応防止絶縁膜217はゲートラインSSL、WL0〜WLn、DSLの間のみに残留される。化学的機械的研磨工程によって全体構造の上部表面は平坦になって、ゲートラインSSL、WL0〜WLn、DSLの間に残留する反応防止絶縁膜217の高さが均一になる。

【0067】

図3(d)を参照すれば、ゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層209の側壁を露出させるためにエッチバック工程で保護膜215及び反応防止絶縁膜217をエッチングする。保護膜215及び反応防止絶縁膜217はシリコン層209の側壁全体が露出されるようにエッチングされることが好ましい。しかし、誘電体膜207の側壁が露出されつつともにエッチングされることができるので、シリコン層209の上部側壁のみ露出されるように保護膜215及び反応防止絶縁膜217がエッチングされることもできる。一方、エッチバック工程は保護膜215と反応防止絶縁膜217を同一の割合でエッチングすることができるエッチング剤を使用して実施することが好ましい。

【0068】

反応防止絶縁膜217が均一の高さを維持している状態でエッチバック工程が実施されるから反応防止絶縁膜217のエッチング厚さも均一になる。これにより、ゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層209の側壁をも均一に露出される。

【0069】

上記方法によって保護膜215及び反応防止絶縁膜217を含む反応防止膜がゲートラインSSL、WL0〜WLn、DSLの間でゲートラインSSL、WL0〜WLn、DSLより低い高さで形成される。

【0070】

エッチバック工程が実施された後には洗浄工程が実施されるが、エアギャップのない状態で洗浄工程が実施されるので、エッチング副産物を完全に除去することができ、エッチング副産物がエアギャップ内に残留されるような問題を解決することができる。

【0071】

図4(a)を参照すれば、シリサイド工程を施してコントロールゲート用シリコン層209の露出された部分をシリサイド層219で形成する。シリサイド層219はタングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成することが好ましく、図2(b)で説明した方法と同一の方法で形成されることができる。

【0072】

反応防止膜215、217によってシリコン層209の上部のみ露出された状態でシリサイド層219が形成されるから、シリサイド層219はゲートラインSSL、WL0〜WLn、DSLの上部のみに自動整列されて形成される。

【0073】

ゲートラインSSL、WL0〜WLn、DSLの間の反応防止膜215、217にエアギャップが形成されていない状態でシリサイド層219が形成されるから、シリサイド層219形成後金属層除去の際に金属層の一部がエアギャップ内に残留されるような問題を解決することができる。

【0074】

図4(b)を参照すれば、反応防止絶縁膜217を除去する。一方、図4(a)で反応防止膜215、217のうち反応防止絶縁膜217を先に除去して保護膜215のみを残留させた状態で、シリサイド工程を施してシリサイド層219を形成することもできる。

【0075】

保護膜215は、反応防止絶縁膜217が除去される時ゲートラインSSL、WL0〜WLn、DSLの側壁を保護する。また、保護膜215は後続工程で形成される階間絶縁膜に含まれた不純物がゲートラインSSL、WL0〜WLn、DSLへ侵透することを防止するために残留されることができる。

【0076】

次に、スペーサ用絶縁膜221を形成した後エッチバック工程を施す。これにより、セレクトラインDSL、SSLの対向する側壁には絶縁膜スペーサが形成される。そして、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)の間とワードラインWL0〜WLnの間は間隔が狭いため、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間とワードラインWL0〜WLnの間はスペーサ用絶縁膜221で満たされる。したがって、セレクトラインDSL、SSLの間の接合領域213は一部が露出され、ワードラインWL0〜WLnの間の接合領域はスペーサ用絶縁膜221によって完全に覆われる。

【0077】

スペーサ用絶縁膜221は、PE-CVD法を利用してUSG(Undoped Silicate Glass)膜で形成することが好ましい。USG膜はSiH4ガスをソースガスとして使用してN2Oガスを反応ガスとして使用し、窒素ガスを運送ガスとして使用して形成することができる。USG膜は350℃ないし450℃の温度で800Wないし1200WのRFパワーを印加して形成することができる。特に、USG膜はSiH4ガスの流量によってゲートラインSSL、WL0〜WLn、DSLの平面に蒸着される量と側壁に蒸着される量が異なる。例として、350sccmのSiH4ガスを基準としてもっと多い量(例えば、350sccmないし550sccmのSiH4ガス)が供給されれば、垂直面より水平面でUSG膜がさらに厚く蒸着されるからゲートラインSSL、WL0〜WLn、DSLの上部縁でオーバーハングが発生される程度が増加する。したがって、SiH4ガスの供給量を増加させるとワードラインWL0〜WLnの間の空間が完全に満たされず、エアギャップが発生されるようにスペーサ用絶縁膜221を形成することができる。

【0078】

このように、絶縁膜221を形成するためのソースガスの流量を調節すれば、ゲートラインSSL、WL0〜WLn、DSLの上部縁で蒸着される絶縁膜の量を調節することができ、上部縁でオーバーハングの厚さが異なることになる。絶縁膜221のオーバーハングを増加させればワードラインWL0〜WLnの間が絶縁膜221で満たされる前に互いに隣接したワードラインの縁で絶縁膜221が触れ合いながらワードラインWL0〜WLnの間が絶縁膜219によって完全に満たされずにエアギャップ221Aが均一で形成される。

【0079】

図4(c)を参照すれば、スペーサ用絶縁膜221を含む全体構造上にエッチング停止膜223を形成する。エッチング停止膜223は窒化膜で形成することができる。エッチング停止膜223上には階間絶縁膜225が形成される。

【0080】

図4(d)を参照すれば、セレクトラインSSL、DSLの間の接合領域213が露出されるように、階間絶縁膜225及びエッチング停止膜223を順次エッチングしてコンタクトホールを形成する。次に、コンタクトホール内部を導電性物質で満たしてコンタクトプラグ227を形成する。

【0081】

上記実施例をよく見ると、ゲートラインSSL、WL0〜WLn、DSLの幅が狭くなっても抵抗の低いシリサイド層219を形成することで、ゲートラインSSL、WL0〜WLn、DSLの抵抗を下げることができる。また、ワードラインWL0〜WLnの間にエアギャップ117を形成することで、ワードラインWL0〜WLnの間の寄生キャパシタンスを下げてワードラインWL0〜WLnの間の干渉現象を最小化することができる。

【0082】

前述の実施例に比べて見ると、エアギャップ221Aが形成された後、エアギャップ221Aが露出されないため、エアギャップ221A内にエッチング副産物が残留される可能性がなく、シリサイド工程後にも金属物質が残留される可能性がない。

【0083】

また、エアギャップ221Aが後続工程で損傷されることを防止することができる。したがって、ワードラインWL0〜WLnの間にエアギャップ221Aを均一で形成することができ、ワードラインWL0〜WLnの間の寄生キャパシタンスを均一に制御及び減少させることができる。特に、一つのエッチング停止膜のみを使用してもコンタクトホール形成の際、ゲートラインSSL、WL0〜WLn、DSLの全体を保護することでゲートラインSSL、WL0〜WLn、DSLが露出されてコンタクトプラグ227と繋がれることを防止することができる。それだけでなく、一つのエッチング防止膜を使用して階間絶縁膜の形成回数が減って全体的な工数を減少させることができる。

【0084】

さらに、前述の実施例をよく見ると、ゲートラインSSL、WL0〜WLn、DSLの最上部層にあたるシリコン層109、209を露出させた状態で、シリコン層を金属シリサイド層で形成することで、金属シリサイド層123、219がシリコン層109、209上のみに自己整列されて形成され、金属シリサイド層123、219をゲートライン別に区分するためのエッチング工程が不要であるという単一性を有する。

【0085】

以上説明したように、本発明の最も好ましい実施形態について説明したが、本発明は、上記記載に限定されるものではなく、特許請求の範囲に記載され、又は明細書に開示された発明の要旨に基づき、当業者において様々な変形や変更が可能なのはもちろんであり、斯かる変形や変更が、本発明の範囲に含まれることは言うまでもない。

【符号の説明】

【0086】

101、201 半導体基板、

103、203 トンネル絶縁膜、

105、205 フローティングゲート、

107、207 誘電体膜、

109、209 シリコン層、

111、211 ハードマスク、

113、213 接合領域、

115a 絶縁膜、

115b スペーサ、

121、125、129、225 絶縁膜、

117、221A エアギャップ、

119、223 エッチング停止膜、

123、219 シリサイド層、

131、227 コンタクトプラグ、

215 保護膜、

217 反応防止絶縁膜、

127 キャッピング膜

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に関し、特にゲートラインを含む半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体素子は、数多くのトランジスタによって製造される。特に、半導体メモリ素子では数多くのセルトランジスタが稠密で規則的な配列で形成され、メモリの種類によってトランジスタのゲート構造が異なる。例えば、DRAMでセルトランジスタのゲートは、ゲート酸化膜とゲート用導電膜の積層構造で形成され、フラッシュメモリでセルトランジスタのゲートはトンネル酸化膜、フローティングゲート、誘電体膜及びコントロールゲートの積層構造で形成される。メモリセルの配列によって縦方向や列方向にトランジスタのゲートが互いに繋がれて、これにより縦方向や列方向にゲートライン(またはワードライン)が形成される。

【0003】

ゲートラインの間は絶縁膜で満たされて、互いに隣接したゲートラインとゲートラインの間に形成された絶縁膜によって寄生キャパシタが形成される。これにより、ゲートラインに電圧が印加されれば、寄生キャパシタ構造とキャパシタカップリング現象によって隣接したゲートラインの電圧が変動される干渉現象が発生される。このような干渉現象は、集積度向上のためにゲートラインの間の間隔が細くなることによってさらにひどく発生される。

【0004】

また、集積度を高めるためにゲートラインの幅が細くなるため、ゲートラインの抵抗が増加する。これにより、ゲートラインの抵抗を低めるためのさまざまな方案が提示されているが、工程の難易度が増加して再現性を確保しにくいという短所がある。

【発明の概要】

【発明が解決しようとする課題】

【0005】

したがって、本発明は上記問題を解決するために案出されたもので、その目的は、干渉現象を減らしてゲートラインの抵抗を減らすことができる半導体素子の製造方法を提供することである。

【課題を解決するための手段】

【0006】

上記目的を達成するために本発明の実施例による半導体素子は、最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、最上部層が金属シリサイド層からなり、第1間隔より広い第2間隔で半導体基板上に配列される第2ゲートラインと、第1ゲートラインの間の半導体基板上に形成されてエアギャップを含む第1絶縁膜と、第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、第2絶縁膜の側壁に形成されたエッチング停止膜と、第1ゲートラインの間の空間と第2ゲートラインの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、第3絶縁膜上部に形成されたキャッピング膜、及びキャッピング膜及び第3絶縁膜を貫通して第2ゲートラインの間の半導体基板に形成された接合領域と繋がれるコンタクトプラグと、を含む。

【0007】

また、金属シリサイド層はタングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成されることができる。

【0008】

また、エッチング停止膜とコンタクトプラグとの間で形成される第4絶縁膜をさらに含むことができる。

【0009】

また、キャッピング膜が窒化膜からなることができる。

【0010】

また、第1絶縁膜が第1ゲートラインより低い高さで形成されることができる。

【0011】

また、第3絶縁膜が第1及び第2ゲートラインの金属シリサイド層と接触することができる。

【0012】

本発明の実施例による半導体素子の製造方法は、最上部層がシリコン膜からなるゲートラインを半導体基板上に形成する段階と、シリコン膜が露出するようにゲートラインの間に反応防止膜を形成する段階と、シリコン膜の露出した部分をシリサイド層で形成する段階と、反応防止膜を除去する段階、及びシリサイド層を含むゲートラインの間に絶縁膜を形成する段階と、を含む。

【0013】

また、反応防止膜はゲートラインの間でゲートラインの高さより低い高さで形成されることができる。

【0014】

また、反応防止膜は、保護膜及び反応防止絶縁膜の積層構造で形成され、シリサイド層を形成する前に反応防止絶縁膜が除去されることができる。

【0015】

また、反応防止膜を形成する段階は、ゲートラインの表面及び半導体基板の表面に保護膜を形成する段階と、ゲートラインの間の空間が満たされるように保護膜を含む全体構造上に反応防止絶縁膜を形成する段階、及び保護膜及び反応防止絶縁膜がゲートラインの間のみに残るように保護膜及び反応防止絶縁膜をエッチングする段階と、を含む。

【0016】

また、保護膜は酸化膜で形成されることができる。

【0017】

反応防止絶縁膜は、SOC膜またはフォトレジストで形成されることができる。

【0018】

また、保護膜及び反応防止絶縁膜をエッチングする段階は、保護膜及び反応防止絶縁膜がゲートラインの間のみに残るように化学的機械的研磨工程を実施する段階、及び保護膜及び反応防止膜がゲートラインの間でゲートラインの高さより低い高さで残留されるようにエッチバック工程で保護膜及び反応防止膜をエッチングする段階を含む。

【0019】

また、シリサイド層はタングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成されることができる。

【0020】

また、ゲートラインはソースセレクトライン、ワードライン及びドレインセレクトラインを含み、ワードラインの間、ソースセレクトライン及びこれに隣接したワードラインの間、ドレインセレクトライン及びこれに隣接したワードラインの間の絶縁膜内にエアギャップが形成され、ソースセレクトラインの対向する側壁とドレインセレクトラインの対向する側壁には、絶縁膜がスペーサの形態で形成されることができる。

【0021】

また、絶縁膜を形成した後、絶縁膜上にエッチング停止膜を形成する段階、エッチング停止膜上に階間絶縁膜を形成する段階、階間絶縁膜及びエッチング停止膜をエッチングしてコンタクトホールを形成する段階、及びコンタクトホール内にコンタクトプラグを形成する段階をさらに含むことができる。

【0022】

絶縁膜はPE-CVD法を利用してUSG膜で形成されることができ、USG膜はソースガスとしてSiH4ガスを使用し、反応ガスとしてN2Oガスを使用して形成されることができる。SiH4ガスの供給流量を350sccmないし550sccmに設定されることができる。

【発明の効果】

【0023】

以上のように、本発明の実施例によれば、工程を単純化しながらゲートラインに印加される電圧によって隣接したゲートラインの電圧が変動される干渉現象を最小化し、ゲートラインの抵抗を低減することができる。また、ゲートラインを窒化膜で安全に保護することができる。

【図面の簡単な説明】

【0024】

【図1】本発明の実施例による半導体素子の製造方法を説明するための断面図である。

【図2】本発明の実施例による半導体素子の製造方法を説明するための断面図である。

【図3】本発明の他の実施例による半導体素子の製造方法を説明するための断面図である。

【図4】本発明の他の実施例による半導体素子の製造方法を説明するための断面図である。

【発明を実施するための形態】

【0025】

以下、添付された図面を参照して本発明の好ましい実施例について説明する。しかし、本発明は以下開示される実施例に限定されるのではなく、互いに異なる多様な形態に具現されることができ、本発明の範囲が次に述べる実施例に限定されるのではない。ただし、本実施例は本発明の開示を完全にさせて通常の知識を有する者に発明の範疇を完全に知らせるために提供されるものであり、本発明の範囲は本願特許請求の範囲によって理解されなければならない。

【0026】

図1(a)ないし図2(d)は、本発明の実施例による半導体素子の製造方法を説明するための断面図である。図1(a)を参照すれば、最上部層がシリコン膜109からなるゲートラインSSL、WL0〜WLn、DSLが半導体基板101上に形成される。より具体的に説明すれば次のようである。

【0027】

NANDフラッシュメモリの場合、ドレインセレクトラインDSL、ワードラインWL0〜WLn及びソースセレクトラインSSLを含むゲートラインが形成される。

【0028】

前記ゲートラインは、セル領域に形成され、周辺回路領域には高電圧トランジスタ及び低電圧トランジスタのゲートライン(図示せず)が形成されることができる。ゲートラインを形成するために次の工程が進行されることができる。

【0029】

まず、半導体基板101内にウェル(図示せず)が形成されて、半導体基板101の全体表面にトンネル絶縁膜103が形成される。この時、周辺回路領域には高電圧トランジスタや低電圧トランジスタのためのゲート絶縁膜が形成される。トンネル絶縁膜103上に第1シリコン層105を形成する。第1シリコン層105は非晶質シリコン層、ポリシリコン層またはこれらの積層構造で形成されることができる。また、第1シリコン層105には3価不純物や5価不純物が添加されることができる。

【0030】

次に、素子分離領域を定義する素子分離マスクをエッチングマスクとして使用するエッチング工程で第1シリコン層105をエッチングする。これにより、第1シリコン層105は平行な多数のシリコンラインにパターニングされる。

【0031】

次に、トンネル絶縁膜103及び半導体基板101をエッチングして素子分離領域に平行なライン形態のトレンチ(図示せず)を形成する。トレンチが満たされるように絶縁膜が形成され、絶縁膜がトレンチ上のみに残留されるように絶縁膜がエッチングされる。これにより、素子分離膜(図示せず)が形成される。

【0032】

全体構造上に誘電体膜107が形成される。誘電体膜107は酸化膜/窒化膜/酸化膜の積層構造で形成され、酸化膜や窒化膜がこれらより高い誘電常数値を持つ絶縁膜で取り替えられる。セレクトラインDSL、SSLが形成される領域で誘電体膜107の一部がエッチングされる。これにより、セレクトラインDSL、SSLが形成される領域で第1シリコン層105の一部が露出される。

【0033】

誘電体膜107の上部に第2シリコン層109及びハードマスク膜111が形成される。第2シリコン層109は、ドープトポリシリコン層で形成することが好ましい。

【0034】

次に、第1シリコン層105がパターニングされた一方向と交差する方向にハードマスク膜111、第2シリコン層109及び誘電体膜107をパターニングする。これにより、平行な多数のコントロールゲートが形成される。引き続いて、第1シリコン層105をエッチングする。その結果、半導体基板101上には多数のゲートラインSSL、WL0〜WLn、DSLが形成される。ハードマスク膜111は後続工程で除去されるのでゲートラインの一部になれない。したがって、ゲートラインSSL、WL0〜WLn、DSLの最上部層は第2シリコン層109になる。

【0035】

一方、誘電体膜107の一部がエッチングされた状態で第2シリコン層109が形成されるから、セレクトラインDSL、SSLの第1シリコン層105と第2シリコン層109は、誘電体膜107のエッチングされた部分を通じて互いに繋がれる。

【0036】

ゲートラインSSL、WL0〜WLn、DSLの間の半導体基板101にはイオン注入工程によって接合領域113が形成される。接合領域113は5価不純物を注入して形成することができる。

【0037】

上記において、セレクトラインDSL、SSLは、ワードラインWL0〜WLnより広い幅で形成されて、セレクトラインDSL、SSLの間隔はワードラインWL0〜WLnの間隔より広い。ここで、間隔によってワードラインWL0〜WLは第1間隔に配列された第1ゲートライングループに定義され、セレクトラインDSL、SSLは第1間隔より広い第2間隔に配列された第2ゲートライングループに定義されることができる。一対の第1ゲートライングループの間には一対のドレインセレクトラインDSLやソースセレクトラインSSLを含む第2ゲートライングループが配置される。

【0038】

図1(b)を参照すれば、ゲートラインSSL、WL0〜WLn、DSLを含む全体構造上にスペーサ用絶縁膜を形成した後、エッチバック工程を施す。これにより、セレクトラインDSL、SSLの対向する側壁には絶縁膜スペーサ115aが形成される。そして、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間と、ワードラインWL0〜WLnの間は間隔が狭いため、スペーサ用絶縁膜115bが残留される。これにより、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間とワードラインWL0〜WLnの間はスペーサ用絶縁膜115bで満たされる。

【0039】

一方、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間と、ワードラインWL0〜WLnの間は間隔が狭くて、絶縁膜を形成する過程でゲートラインDSL、SSL、WL0〜WLnの上部縁に絶縁膜のオーバーハング(Overhang)が形成されるため、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間とワードラインWL0〜WLnの間はスペーサ用絶縁膜115bで完全に満たされず、エアギャップのようなエアギャップ117が形成される。エアギャップ117が形成されることによってワードラインWL0〜WLnの間の寄生キャパシタンス値が低くなるため、ワードラインWL0〜WLnの間の干渉現象を最小化することができる。

【0040】

スペーサ用絶縁膜115a、115bが形成されることによって、セレクトラインDSL、SSLの間の接合領域113の一部が露出され、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間とワードラインWL0〜WLnの間の接合領域はスペーサ用絶縁膜115bによって覆われる。

【0041】

図1(c)を参照すれば、スペーサ用絶縁膜115a、115bを含む全体構造上に第1エッチング停止膜119及び第1階間絶縁膜121を順次形成する。ここで、第1エッチング停止膜119は窒化膜で形成することができ、ゲートラインDSL、SSL、WL0〜WLnによる段差が維持されることができるほどの厚さで全体構造の表面に形成される。

【0042】

図2(a)を参照すれば、ゲートラインSSL、WL0〜WLn、DSLの最上部層であるシリコン層109の上部全体表面と側壁の一部を露出させるために、第1階間絶縁膜121及び第1エッチング停止膜119ゲートラインSSL、WL0〜WLn、DSLの間のみに残留されるようにエッチングされてハードマスク膜111が除去される。特に、ゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層にあたるコントロールゲート用シリコン層109の側壁が露出されて誘電体膜107は露出されないようにスペーサ用絶縁膜115a、115b、第1階間絶縁膜(121及び第1エッチング停止膜119)をエッチングすることが好ましい。

【0043】

ゲートラインSSL、WL0〜WLn、DSLが形成された領域と形成されていない領域で、第1階間絶縁膜121の表面高さが異なることができる。このため、第1階間絶縁膜121をエッチングした後、ゲートラインSSL、WL0〜WLn、DSLの間に残留する第1絶縁膜121が残留する高さが変わることができる。したがって、化学的機械的研磨工程とエッチバック工程を並行して第1階間絶縁膜121及び第1エッチング停止膜119をエッチングすることが好ましい。

【0044】

まず、ゲートラインSSL、WL0〜WLn、DSLのハードマスク膜111が露出するまで化学的機械的研磨工程を実施すれば、ゲートラインSSL、WL0〜WLn、DSLの間に残留する第1階間絶縁膜121の高さを均一に平坦化することができる。次に、エッチバック工程でスペーサ用絶縁膜115a、115b、第1階間絶縁膜121と第1エッチング停止膜119をエッチングすれば、ゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層109の側壁を均一に露出させることができる。

【0045】

これにより、ゲートラインSSL、WL0〜WLn、DSLの間にスペーサ用絶縁膜115a、115b、第1階間絶縁膜121及び第1エッチング停止膜119がゲートラインSSL、WL0〜WLn、DSLより低い高さで残留される。一方、ワードラインWL0〜WLnの間のスペーサ用絶縁膜115bがエッチバック工程によってエッチングされることによって、スペーサ用絶縁膜115b内に形成されたエアギャップ117が露出されることができる。

【0046】

図2(b)を参照すれば、シリサイド工程を施してコントロールゲート用シリコン層109の露出された部分をシリサイド層123で形成する。具体的に、例を挙げて説明すれば、コントロールゲート用シリコン層109の露出された部分が覆われるように全体構造上に金属物質(例えば、タングステン、コバルトまたはニッケル)を蒸着して金属層を形成する。次に、熱処理を実施すれば、金属層と接触するシリコン層109のシリコンと金属層の金属が反応して金属シリサイド層123が形成される。

【0047】

金属層がタングステンで形成された場合、タングステンシリサイド層が形成されて、金属層がコバルトで形成された場合、コバルトシリサイド層が形成されて、金属層がニッケルで形成された場合、ニッケルシリサイド層が形成される。引き続いて、シリコン層109と反応せず残留する金属層を除去する。

【0048】

スペーサ用絶縁膜115a、115b、第1エッチング停止膜119及び第1階間絶縁膜121によってシリコン層109の上部のみが露出された状態でシリサイド層123が形成されるから、シリサイド層123はゲートラインSSL、WL0〜WLn、DSLの上部のみに自動整列されて形成される。

【0049】

図2(c)を参照すれば、シリサイド層123を含む全体構造上に第2階間絶縁膜125、キャッピング膜127及び第3階間絶縁膜129を順次形成する。第2階間絶縁膜125を形成する時露出されたエアギャップ117の入口が第2階間絶縁膜125のオーバーハングによって再度詰まりつつエアギャップ117が維持される。

【0050】

上記において、キャッピング膜127は後続工程で発生される水素イオンのようなモバイルイオンがゲートラインSSL、WL0〜WLn、DSLへ侵透することを防止するための機能を遂行するために形成される。また、キャッピング膜127は第2エッチング停止膜の機能を遂行することもできる。このようなキャッピング膜127は絶縁膜121、125、129と異なる物質で形成されることができ、具体的に窒化膜で形成されることができる。

【0051】

一方、第2階間絶縁膜125は金属シリサイド層123が露出された状態で金属シリサイド層123を含む全体構造の上部に形成されるので、第2階間絶縁膜125と金属シリサイド層123が直接接触する。すなわち、金属シリサイド層123と第2階間絶縁膜125との間にはハードマスクや他の膜が存在しない。そして、金属シリサイド層123が露出された状態で第2階間絶縁膜125が形成された後、キャッピング膜127が形成されることによって、後続工程で発生される水素イオンのようなモバイルイオンがゲートラインSSL、WL0〜WLn、DSLへ浸透されることをキャッピング膜127で防止することができる。

【0052】

図2(d)を参照すれば、セレクトラインSSL、DSLの間の接合領域113が露出するように、第3階間絶縁膜129、第2エッチング停止膜127、第2階間絶縁膜125、第1階間絶縁膜121及び第1エッチング停止膜119を順次エッチングしてコンタクトホールを形成する。引き続き、コンタクトホールの内部を導電性物質で満たしてコンタクトプラグ131を形成する。

【0053】

上記実施例によって形成された半導体素子を構造的側面からよく見ると、第1ゲートライングループに含まれた第1ゲートラインWL0〜WLnは、最上部層が金属シリサイド層123からなり、半導体基板101上に第1間隔に配列される。第2ゲートライングループに含まれた第2ゲートライン(DSLまたはSSL)は、最上部層が金属シリサイド層123からなり、第1間隔より広い第2間隔で半導体基板101上に配列される。

【0054】

第1ゲートラインWL0〜WLnの間の半導体基板101上には、エアギャップ117を含む第1絶縁膜115bが形成される。第2ゲートライン(DSLまたはSSL)の対向する側壁上には第2絶縁膜115aが形成されて、第2絶縁膜115aの側壁にはエッチング停止膜119が形成される。

【0055】

第1ゲートラインWL0〜WLnの間の空間と第2ゲートラインDSL、SSLの間の空間が満たされるように全体構造上に第3絶縁膜125が形成されて、第3絶縁膜125の上部にキャッピング膜127が形成される。キャッピング膜127は窒化膜で形成されることができ、第1及び第2ゲートラインSSL、WL0〜WLn、SSLの全体上部に形成される。

【0056】

第2ゲートラインDSL、SSLの間の半導体基板101に形成された接合領域とキャッピング膜127及び第3絶縁膜125を貫通して繋がれるコンタクトプラグ131が形成される。エッチング停止膜119とコンタクトプラグ121との間には第4絶縁膜121がさらに形成されることができる。

【0057】

第1及び第2ゲートラインSSL、WL0〜WLn、SSLの最上部層は、金属シリサイド層123からなり、金属シリサイド層123上にはハードマスクが存在しないから金属シリサイド層123が第2絶縁膜125と接触する。

【0058】

上記製造方法と構造により、ゲートラインSSL、WL0〜WLn、DSLの幅が狭くなっても抵抗の低いシリサイド層123を形成することで、ゲートラインSSL、WL0〜WLn、DSLの抵抗を下げることができる。また、第2階間絶縁膜125を形成する時、ワードラインWL0〜WLnの間にエアギャップ117を残留させることができるので、ワードラインWL0〜WLnの間の寄生キャパシタンスを下げてワードラインWL0〜WLnの間の干渉現象を最小化することができる。

【0059】

これと異なる方法で干渉現象を最小化してゲートラインの抵抗を下げることができる本発明の他の実施例を説明する。図3(a)ないし図4(d)は、本発明の他の実施例による半導体素子の製造方法を説明するための断面図である。

【0060】

図3(a)を参照すれば、最上部層がシリコン膜209からなるゲートラインSSL、WL0〜WLn、DSLが半導体基板201上に形成される。そして、ゲートラインSSL、WL0〜WLn、DSLの間の半導体基板201には接合領域213を形成する。

【0061】

NANDフラッシュメモリの場合、ゲートラインSSL、WL0〜WLn、DSLは、ソースセレクトラインSSL、ワードラインWL0〜WLn及びドレインセレクトラインDSLを含み、トンネル絶縁膜203、フローティングゲート用シリコン層205、誘電体膜207及びコントロールゲート用シリコン層209の積層構造で形成されることができる。ゲートラインSSL、WL0〜WLn、DSLの上部にはハードマスク膜211が形成されて、ハードマスク膜211は酸化膜で形成することができる。このようなゲートラインSSL、WL0〜WLn、DSL及び接合領域213は図1(a)で説明した方法と同一の方法で形成されることができる。

【0062】

次に、シリサイド工程で金属層がゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層にあたるコントロールゲート用シリコン層209と反応じて、残りのシリコン構造物(例えば、フローティングゲート用シリコン層、半導体基板等)と反応することを防止するための反応防止膜をゲートラインSSL、WL0〜WLn、DSLの間で形成する。より具体的に例を挙げて説明する。

【0063】

図3(b)を参照すれば、ゲートラインSSL、WL0〜WLn、DSLを含む全体構造の表面に保護膜215を形成する。保護膜215は、酸化膜をCVD方式で蒸着して形成することができる。次に、ゲートラインSSL、WL0〜WLn、DSLの間の空間が満たされるように保護膜215を含む全体構造上に反応防止絶縁膜217を形成する。

【0064】

反応防止絶縁膜217は、流動性の良い絶縁膜やSOC(Spin On Carbon)膜やフォトレジストで形成することができる。反応防止絶縁膜217は流動性の良い物質で形成されるから、ゲートラインSSL、WL0〜WLn、DSLの間は反応防止絶縁膜217で完全に満たされてエアギャップは形成されない。

【0065】

保護膜215と反応防止絶縁膜217は、反応防止膜のために形成される。ここで、保護膜215は反応防止絶縁膜217に含まれた不純物がゲートラインSSL、WL0〜WLn、DSLの内部へ侵透することを防止するために形成される。しかし、反応防止膜217の物質によって保護膜215は省略されることができる。

【0066】

図3(c)を参照すれば、ゲートラインSSL、WL0〜WLn、DSL上部のハードマスク膜211が除去されて、コントロールゲート用シリコン層209が露出されるまで化学的機械的研磨工程を施す。これにより、保護膜215と反応防止絶縁膜217はゲートラインSSL、WL0〜WLn、DSLの間のみに残留される。化学的機械的研磨工程によって全体構造の上部表面は平坦になって、ゲートラインSSL、WL0〜WLn、DSLの間に残留する反応防止絶縁膜217の高さが均一になる。

【0067】

図3(d)を参照すれば、ゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層209の側壁を露出させるためにエッチバック工程で保護膜215及び反応防止絶縁膜217をエッチングする。保護膜215及び反応防止絶縁膜217はシリコン層209の側壁全体が露出されるようにエッチングされることが好ましい。しかし、誘電体膜207の側壁が露出されつつともにエッチングされることができるので、シリコン層209の上部側壁のみ露出されるように保護膜215及び反応防止絶縁膜217がエッチングされることもできる。一方、エッチバック工程は保護膜215と反応防止絶縁膜217を同一の割合でエッチングすることができるエッチング剤を使用して実施することが好ましい。

【0068】

反応防止絶縁膜217が均一の高さを維持している状態でエッチバック工程が実施されるから反応防止絶縁膜217のエッチング厚さも均一になる。これにより、ゲートラインSSL、WL0〜WLn、DSLの最上部シリコン層209の側壁をも均一に露出される。

【0069】

上記方法によって保護膜215及び反応防止絶縁膜217を含む反応防止膜がゲートラインSSL、WL0〜WLn、DSLの間でゲートラインSSL、WL0〜WLn、DSLより低い高さで形成される。

【0070】

エッチバック工程が実施された後には洗浄工程が実施されるが、エアギャップのない状態で洗浄工程が実施されるので、エッチング副産物を完全に除去することができ、エッチング副産物がエアギャップ内に残留されるような問題を解決することができる。

【0071】

図4(a)を参照すれば、シリサイド工程を施してコントロールゲート用シリコン層209の露出された部分をシリサイド層219で形成する。シリサイド層219はタングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成することが好ましく、図2(b)で説明した方法と同一の方法で形成されることができる。

【0072】

反応防止膜215、217によってシリコン層209の上部のみ露出された状態でシリサイド層219が形成されるから、シリサイド層219はゲートラインSSL、WL0〜WLn、DSLの上部のみに自動整列されて形成される。

【0073】

ゲートラインSSL、WL0〜WLn、DSLの間の反応防止膜215、217にエアギャップが形成されていない状態でシリサイド層219が形成されるから、シリサイド層219形成後金属層除去の際に金属層の一部がエアギャップ内に残留されるような問題を解決することができる。

【0074】

図4(b)を参照すれば、反応防止絶縁膜217を除去する。一方、図4(a)で反応防止膜215、217のうち反応防止絶縁膜217を先に除去して保護膜215のみを残留させた状態で、シリサイド工程を施してシリサイド層219を形成することもできる。

【0075】

保護膜215は、反応防止絶縁膜217が除去される時ゲートラインSSL、WL0〜WLn、DSLの側壁を保護する。また、保護膜215は後続工程で形成される階間絶縁膜に含まれた不純物がゲートラインSSL、WL0〜WLn、DSLへ侵透することを防止するために残留されることができる。

【0076】

次に、スペーサ用絶縁膜221を形成した後エッチバック工程を施す。これにより、セレクトラインDSL、SSLの対向する側壁には絶縁膜スペーサが形成される。そして、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)の間とワードラインWL0〜WLnの間は間隔が狭いため、セレクトライン(SSLまたはDSL)とワードライン(WL0またはWLn)との間とワードラインWL0〜WLnの間はスペーサ用絶縁膜221で満たされる。したがって、セレクトラインDSL、SSLの間の接合領域213は一部が露出され、ワードラインWL0〜WLnの間の接合領域はスペーサ用絶縁膜221によって完全に覆われる。

【0077】

スペーサ用絶縁膜221は、PE-CVD法を利用してUSG(Undoped Silicate Glass)膜で形成することが好ましい。USG膜はSiH4ガスをソースガスとして使用してN2Oガスを反応ガスとして使用し、窒素ガスを運送ガスとして使用して形成することができる。USG膜は350℃ないし450℃の温度で800Wないし1200WのRFパワーを印加して形成することができる。特に、USG膜はSiH4ガスの流量によってゲートラインSSL、WL0〜WLn、DSLの平面に蒸着される量と側壁に蒸着される量が異なる。例として、350sccmのSiH4ガスを基準としてもっと多い量(例えば、350sccmないし550sccmのSiH4ガス)が供給されれば、垂直面より水平面でUSG膜がさらに厚く蒸着されるからゲートラインSSL、WL0〜WLn、DSLの上部縁でオーバーハングが発生される程度が増加する。したがって、SiH4ガスの供給量を増加させるとワードラインWL0〜WLnの間の空間が完全に満たされず、エアギャップが発生されるようにスペーサ用絶縁膜221を形成することができる。

【0078】

このように、絶縁膜221を形成するためのソースガスの流量を調節すれば、ゲートラインSSL、WL0〜WLn、DSLの上部縁で蒸着される絶縁膜の量を調節することができ、上部縁でオーバーハングの厚さが異なることになる。絶縁膜221のオーバーハングを増加させればワードラインWL0〜WLnの間が絶縁膜221で満たされる前に互いに隣接したワードラインの縁で絶縁膜221が触れ合いながらワードラインWL0〜WLnの間が絶縁膜219によって完全に満たされずにエアギャップ221Aが均一で形成される。

【0079】

図4(c)を参照すれば、スペーサ用絶縁膜221を含む全体構造上にエッチング停止膜223を形成する。エッチング停止膜223は窒化膜で形成することができる。エッチング停止膜223上には階間絶縁膜225が形成される。

【0080】

図4(d)を参照すれば、セレクトラインSSL、DSLの間の接合領域213が露出されるように、階間絶縁膜225及びエッチング停止膜223を順次エッチングしてコンタクトホールを形成する。次に、コンタクトホール内部を導電性物質で満たしてコンタクトプラグ227を形成する。

【0081】

上記実施例をよく見ると、ゲートラインSSL、WL0〜WLn、DSLの幅が狭くなっても抵抗の低いシリサイド層219を形成することで、ゲートラインSSL、WL0〜WLn、DSLの抵抗を下げることができる。また、ワードラインWL0〜WLnの間にエアギャップ117を形成することで、ワードラインWL0〜WLnの間の寄生キャパシタンスを下げてワードラインWL0〜WLnの間の干渉現象を最小化することができる。

【0082】

前述の実施例に比べて見ると、エアギャップ221Aが形成された後、エアギャップ221Aが露出されないため、エアギャップ221A内にエッチング副産物が残留される可能性がなく、シリサイド工程後にも金属物質が残留される可能性がない。

【0083】

また、エアギャップ221Aが後続工程で損傷されることを防止することができる。したがって、ワードラインWL0〜WLnの間にエアギャップ221Aを均一で形成することができ、ワードラインWL0〜WLnの間の寄生キャパシタンスを均一に制御及び減少させることができる。特に、一つのエッチング停止膜のみを使用してもコンタクトホール形成の際、ゲートラインSSL、WL0〜WLn、DSLの全体を保護することでゲートラインSSL、WL0〜WLn、DSLが露出されてコンタクトプラグ227と繋がれることを防止することができる。それだけでなく、一つのエッチング防止膜を使用して階間絶縁膜の形成回数が減って全体的な工数を減少させることができる。

【0084】

さらに、前述の実施例をよく見ると、ゲートラインSSL、WL0〜WLn、DSLの最上部層にあたるシリコン層109、209を露出させた状態で、シリコン層を金属シリサイド層で形成することで、金属シリサイド層123、219がシリコン層109、209上のみに自己整列されて形成され、金属シリサイド層123、219をゲートライン別に区分するためのエッチング工程が不要であるという単一性を有する。

【0085】

以上説明したように、本発明の最も好ましい実施形態について説明したが、本発明は、上記記載に限定されるものではなく、特許請求の範囲に記載され、又は明細書に開示された発明の要旨に基づき、当業者において様々な変形や変更が可能なのはもちろんであり、斯かる変形や変更が、本発明の範囲に含まれることは言うまでもない。

【符号の説明】

【0086】

101、201 半導体基板、

103、203 トンネル絶縁膜、

105、205 フローティングゲート、

107、207 誘電体膜、

109、209 シリコン層、

111、211 ハードマスク、

113、213 接合領域、

115a 絶縁膜、

115b スペーサ、

121、125、129、225 絶縁膜、

117、221A エアギャップ、

119、223 エッチング停止膜、

123、219 シリサイド層、

131、227 コンタクトプラグ、

215 保護膜、

217 反応防止絶縁膜、

127 キャッピング膜

【特許請求の範囲】

【請求項1】

最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、

最上部層が金属シリサイド層からなり、前記第1間隔より広い第2間隔で前記半導体基板上に配列される第2ゲートラインと、

前記第1ゲートラインの間の前記半導体基板上に形成されてエアギャップを含む第1絶縁膜と、

前記第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、

前記第2絶縁膜の側壁に形成されたエッチング停止膜と、

前記第1ゲートラインの間の空間と前記第2ゲートラインとの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、

前記第3絶縁膜の上部に形成されたキャッピング膜と、

前記キャッピング膜及び前記第3絶縁膜を貫通して前記第2ゲートラインの間の前記半導体基板に形成された接合領域と繋がれるコンタクトプラグと、

を含むことを特徴とする半導体素子。

【請求項2】

前記金属シリサイド層は、タングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成されることを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記エッチング停止膜とコンタクトプラグとの間で形成される第4絶縁膜をさらに含むことを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記キャッピング膜が窒化膜からなることを特徴とする請求項1に記載の半導体素子。

【請求項5】

前記第1絶縁膜が第1ゲートラインより低い高さで形成されることを特徴とする請求項1に記載の半導体素子。

【請求項6】

前記第3絶縁膜が第1及び第2ゲートラインの金属シリサイド層と接触することを特徴とする請求項1に記載の半導体素子。

【請求項7】

最上部層がシリコン膜からなるゲートラインを半導体基板上に形成する段階と、

前記シリコン膜が露出されるようにゲートラインの間に反応防止膜を形成する段階と、

前記シリコン膜の露出された部分をシリサイド層に形成する段階と、

前記反応防止膜を除去する段階と、

前記シリサイド層を含むゲートラインの間に絶縁膜を形成する段階と、

を含むことを特徴とする半導体素子の製造方法。

【請求項8】

前記反応防止膜は、前記ゲートラインの間で前記ゲートラインの高さより低い高さで形成されることを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項9】

前記反応防止膜は、保護膜及び反応防止絶縁膜の積層構造で形成され、前記シリサイド層を形成する前に前記反応防止絶縁膜が除去されることを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項10】

前記反応防止膜を形成する段階は、

前記ゲートラインの表面及び前記半導体基板の表面に保護膜を形成する段階と、

前記ゲートラインの間の空間が満たされるように前記保護膜を含む全体構造上に反応防止絶縁膜を形成する段階と、

前記保護膜及び前記反応防止絶縁膜が前記ゲートラインの間のみに残留するように前記保護膜及び前記反応防止絶縁膜をエッチングする段階と、

を含むことを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項11】

前記保護膜は、酸化膜で形成されることを特徴とする請求項9または10に記載の半導体素子の製造方法。

【請求項12】

前記反応防止絶縁膜は、SOC膜またはフォトレジストで形成されることを特徴とする請求項9または10に記載の半導体素子の製造方法。

【請求項13】

前記保護膜及び前記反応防止絶縁膜をエッチングする段階は、

前記保護膜及び前記反応防止絶縁膜が前記ゲートラインの間のみに残留するように化学的機械的研磨工程を実施する段階と、

前記保護膜及び前記反応防止膜が前記ゲートラインの間で前記ゲートラインの高さより低い高さで残留されるようにエッチバック工程で前記保護膜及び前記反応防止膜をエッチングする段階と、

を含むことを特徴とする請求項10に記載の半導体素子の製造方法。

【請求項14】

前記シリサイド層は、タングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成されることを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項15】

前記ゲートラインは、ソースセレクトライン、ワードライン及びドレインセレクトラインを含み、ワードラインの間、前記ソースセレクトライン及びこれに隣接したワードラインの間、前記ドレインセレクトライン及びこれに隣接したワードラインの間の絶縁膜内にエアギャップが形成され、

前記ソースセレクトラインの対向する側壁と前記ドレインセレクトラインの対向する側壁には、前記絶縁膜がスペーサの形態で形成されることを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項16】

前記絶縁膜を形成した後、前記絶縁膜上にエッチング停止膜を形成する段階と、

前記エッチング停止膜上に階間絶縁膜を形成する段階と、

前記階間絶縁膜及び前記エッチング停止膜をエッチングしてコンタクトホールを形成する段階と、

前記コンタクトホール内にコンタクトプラグを形成する段階と、

をさらに含むことを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項17】

前記絶縁膜は、PE-CVD法を利用してUSG膜で形成することを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項18】

前記USG膜は、ソースガスとしてSiH4ガスを使用し、反応ガスとしてN2Oガスを使用して形成することを特徴とする請求項17に記載の半導体素子の製造方法。

【請求項19】

前記SiH4ガスの供給流量を350sccmないし550sccmに設定することを特徴とする請求項18に記載の半導体素子の製造方法。

【請求項1】

最上部層が金属シリサイド層からなり、第1間隔で半導体基板上に配列される第1ゲートラインと、

最上部層が金属シリサイド層からなり、前記第1間隔より広い第2間隔で前記半導体基板上に配列される第2ゲートラインと、

前記第1ゲートラインの間の前記半導体基板上に形成されてエアギャップを含む第1絶縁膜と、

前記第2ゲートラインの対向する側壁上に形成された第2絶縁膜と、

前記第2絶縁膜の側壁に形成されたエッチング停止膜と、

前記第1ゲートラインの間の空間と前記第2ゲートラインとの間の空間が満たされるように全体構造上に形成された第3絶縁膜と、

前記第3絶縁膜の上部に形成されたキャッピング膜と、

前記キャッピング膜及び前記第3絶縁膜を貫通して前記第2ゲートラインの間の前記半導体基板に形成された接合領域と繋がれるコンタクトプラグと、

を含むことを特徴とする半導体素子。

【請求項2】

前記金属シリサイド層は、タングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成されることを特徴とする請求項1に記載の半導体素子。

【請求項3】

前記エッチング停止膜とコンタクトプラグとの間で形成される第4絶縁膜をさらに含むことを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記キャッピング膜が窒化膜からなることを特徴とする請求項1に記載の半導体素子。

【請求項5】

前記第1絶縁膜が第1ゲートラインより低い高さで形成されることを特徴とする請求項1に記載の半導体素子。

【請求項6】

前記第3絶縁膜が第1及び第2ゲートラインの金属シリサイド層と接触することを特徴とする請求項1に記載の半導体素子。

【請求項7】

最上部層がシリコン膜からなるゲートラインを半導体基板上に形成する段階と、

前記シリコン膜が露出されるようにゲートラインの間に反応防止膜を形成する段階と、

前記シリコン膜の露出された部分をシリサイド層に形成する段階と、

前記反応防止膜を除去する段階と、

前記シリサイド層を含むゲートラインの間に絶縁膜を形成する段階と、

を含むことを特徴とする半導体素子の製造方法。

【請求項8】

前記反応防止膜は、前記ゲートラインの間で前記ゲートラインの高さより低い高さで形成されることを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項9】

前記反応防止膜は、保護膜及び反応防止絶縁膜の積層構造で形成され、前記シリサイド層を形成する前に前記反応防止絶縁膜が除去されることを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項10】

前記反応防止膜を形成する段階は、

前記ゲートラインの表面及び前記半導体基板の表面に保護膜を形成する段階と、

前記ゲートラインの間の空間が満たされるように前記保護膜を含む全体構造上に反応防止絶縁膜を形成する段階と、

前記保護膜及び前記反応防止絶縁膜が前記ゲートラインの間のみに残留するように前記保護膜及び前記反応防止絶縁膜をエッチングする段階と、

を含むことを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項11】

前記保護膜は、酸化膜で形成されることを特徴とする請求項9または10に記載の半導体素子の製造方法。

【請求項12】

前記反応防止絶縁膜は、SOC膜またはフォトレジストで形成されることを特徴とする請求項9または10に記載の半導体素子の製造方法。

【請求項13】

前記保護膜及び前記反応防止絶縁膜をエッチングする段階は、

前記保護膜及び前記反応防止絶縁膜が前記ゲートラインの間のみに残留するように化学的機械的研磨工程を実施する段階と、

前記保護膜及び前記反応防止膜が前記ゲートラインの間で前記ゲートラインの高さより低い高さで残留されるようにエッチバック工程で前記保護膜及び前記反応防止膜をエッチングする段階と、

を含むことを特徴とする請求項10に記載の半導体素子の製造方法。

【請求項14】

前記シリサイド層は、タングステンシリサイド層、コバルトシリサイド層及びニッケルシリサイド層のうちいずれか一つで形成されることを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項15】

前記ゲートラインは、ソースセレクトライン、ワードライン及びドレインセレクトラインを含み、ワードラインの間、前記ソースセレクトライン及びこれに隣接したワードラインの間、前記ドレインセレクトライン及びこれに隣接したワードラインの間の絶縁膜内にエアギャップが形成され、

前記ソースセレクトラインの対向する側壁と前記ドレインセレクトラインの対向する側壁には、前記絶縁膜がスペーサの形態で形成されることを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項16】

前記絶縁膜を形成した後、前記絶縁膜上にエッチング停止膜を形成する段階と、

前記エッチング停止膜上に階間絶縁膜を形成する段階と、

前記階間絶縁膜及び前記エッチング停止膜をエッチングしてコンタクトホールを形成する段階と、

前記コンタクトホール内にコンタクトプラグを形成する段階と、

をさらに含むことを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項17】

前記絶縁膜は、PE-CVD法を利用してUSG膜で形成することを特徴とする請求項7に記載の半導体素子の製造方法。

【請求項18】

前記USG膜は、ソースガスとしてSiH4ガスを使用し、反応ガスとしてN2Oガスを使用して形成することを特徴とする請求項17に記載の半導体素子の製造方法。

【請求項19】

前記SiH4ガスの供給流量を350sccmないし550sccmに設定することを特徴とする請求項18に記載の半導体素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−235123(P2012−235123A)

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願番号】特願2012−102919(P2012−102919)

【出願日】平成24年4月27日(2012.4.27)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

【公開日】平成24年11月29日(2012.11.29)

【国際特許分類】

【出願日】平成24年4月27日(2012.4.27)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

[ Back to top ]