半導体素子及び結晶成長基板

【課題】ピエゾ電界の悪影響を派生問題なく効果的に緩和若しくは最小化する。

【解決手段】各非縦方向成長部4の上面では、xy平面に平行にr面が結晶成長し、これらの個々のr面は、側壁面1bの近傍に若干のボイド5を形成しつつも、ストライプ溝Sを完全に覆い隠すまで結晶成長して、最終的には略一連の平坦面が形成される。この時以下の結晶成長条件下で50分間、非縦方向成長部4のファセット成長を継続する。このファセット成長の条件設定は、継続的かつ順調なファセット成長を促進する上で重要である。また、下記の結晶成長速度は、r面に垂直な方向の結晶成長速度である。

結晶成長温度 : 990〔℃〕

結晶成長速度 : 0.8〔μm/min〕

供給ガス流量比(V/III 比): 5000

【解決手段】各非縦方向成長部4の上面では、xy平面に平行にr面が結晶成長し、これらの個々のr面は、側壁面1bの近傍に若干のボイド5を形成しつつも、ストライプ溝Sを完全に覆い隠すまで結晶成長して、最終的には略一連の平坦面が形成される。この時以下の結晶成長条件下で50分間、非縦方向成長部4のファセット成長を継続する。このファセット成長の条件設定は、継続的かつ順調なファセット成長を促進する上で重要である。また、下記の結晶成長速度は、r面に垂直な方向の結晶成長速度である。

結晶成長温度 : 990〔℃〕

結晶成長速度 : 0.8〔μm/min〕

供給ガス流量比(V/III 比): 5000

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子及び結晶成長基板に関する。

この結晶成長方法は、半導体発光素子や半導体受光素子(以下、纏めて光半導体素子と言う。)の製造に大いに有用なものである。

【背景技術】

【0002】

活性層の二軸性歪みによって誘起されるピエゾ電界は、半導体発光素子の内部量子効率の低下をもたらすことが一般に知られている。この様なピエゾ電界の緩和や最小化を考慮して提案された光半導体素子としては、例えば下記の特許文献1に掲載されているものが広く知られている。本願図11、図12は、この特許文献1から抜粋したもので、窒化ガリウム系の半導体でのピエゾ電界の角度依存性を示すグラフと、これらの半導体を使用した発光素子の断面図をそれぞれ示している。このグラフの横軸は、c軸の正の向き[0001]からの角度θに対するピエゾ電界の変化を示しており、このグラフから、c面を界面とする活性層においてはピエゾ電界の大きさ(絶対値)が最大となり、r面、a面、またはm面を界面とする活性層においてはピエゾ電界の大きさ(絶対値)は最小(0MV/cm)となることが判る。

【0003】

そして、この特許文献1(第2の実施例)には、「まず、従来技術によりSiC、GaN等の基板51上にn型GaNコンタクト層53、n型AlGaNクラッド層54を{0001}面方向に成長させ、その後、選択成長あるいは選択エッチングにより{2−1−14}面や{01−12}面を形成する。その後再結晶成長により今形成された面方位を持つGaInN/GaNあるいはGaInN/GaInN多重歪量子井戸層55を形成する。」などの記載があり、この様に本特許文献1では、上記の図12を用いて、ピエゾ電界の緩和作用を有する活性層の構成形態とその形成方法を開示している。

【0004】

また、下記の特許文献2には、c面から62°傾斜した斜面((1−101)面)を結晶成長面として用いた結晶成長方法に関する記載がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−112029

【特許文献2】特開2003−347585

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記の特許文献2においては、上記の結晶成長面に関して特に62°と言う傾斜角が選択されるので、この従来技術を採用する限り、前述のグラフ(図11)からも判る通り、ピエゾ電界を略零にすることはできず、よって、依然としてピエゾ電界効果を十分には払拭することができない。

また、この特許文献2においては、ピエゾ電界を積極的に略零にしようとする思想は全く見当たらない。

【0007】

また、上記の特許文献1においては、上記の選択成長あるいは選択エッチングを実施する場合、以下の問題を回避することが困難である。

(1)選択成長を行う場合の問題点

図12に図示される様な理想的な波板形状の多重歪量子井戸層55を選択成長によって形成することは、現在の結晶成長に関する技術水準に照らして、必ずしも容易ではない。また、その様な選択成長が仮に可能であったとしても、我々はその方法を少なくとも上記の特許文献1からは、何ら具体的に知ることができない。

【0008】

例えば、図12のn型AlGaNクラッド層54の中にストライプ状の多数のSiO2 マスク等を成膜して上記の選択成長を実施する場合には、そのマスク形成工程の前後で製造中の光半導体素子を大幅に降温したり昇温したりしなければならないので、この場合には各部の熱膨張係数差に基づく応力が素子内に発生する。したがって、この場合、その後に積層される井戸層の結晶品質は劣化する。

【0009】

また、基板材料等の選択により基板等の熱膨張係数をたとえ最適に選んだとしても、上記の様な大幅な昇降温を行っている間に、n型クラッド層の上方露出面における結晶性が、その露出面近傍における活発な原子脱離現象(:特定元素の昇華)などによって劣化する。この様な結晶性の劣化は、キャリアガスなどによるエッチング作用に基づく所が大きい。これらの事情については、例えば次の文献等からも容易に理解することができる。

(1)公開特許公報:特開平11−068159

(2)公開特許公報:特開平9−139543

(3)公開特許公報:特開平8−88432

【0010】

また、更に、上記の様なストライプ状の多数のSiO2 マスクなどは、活性層の近傍に配置、残留させざるを得ないが、このため、素子内部の電流密度に偏り(ムラ)が生じて、内部量子効率が低下してしまうなどの派生問題も回避し難い。また、この様なマスクを活性層の近傍に配置、残留させれば、光半導体素子の光取り出し効率、光取り込み効率、或いは共振効率等が低下するなどの不都合も生じる。

【0011】

(2)選択エッチングを行う場合の問題点

選択エッチングを行う場合にも、マスク形成工程が不可欠となるため、上記の大幅な昇降温の問題は回避し難い。また、選択エッチングを行えば、その侵食面には、エッチング処理に伴うダメージ(表面荒れ)が顕著に残るので、その上に直接多重歪量子井戸層を良好に結晶成長させることは困難となる。

【0012】

また、特にレーザの共振器を形成する際には、上記の(1)、(2)の何れの場合でも、光導波路上に波板形状の活性層を形成すると、その斜面で共振光が散乱され易いなどの派生問題が生じる。

【0013】

この様に、目的の光半導体素子において所望の発光効率を確保することは、上記の特許文献1から具体的に知り得る技術範囲内では非常に困難である。また、実際に上記の特許文献1(図12)の様な具体的な素子構造によって、実際に半導体発光素子の発光効率が従来よりも向上したと言う報告は、今のところ光半導体素子関連分野において全く見当たらない。これは、それらの半導体発光素子の素子構造や製造工程を具現化するに当たって、実際には上記の様な問題が回避し難いためだと考えられる。

【0014】

以上の様に、活性層などの半導体層の内部に生じるピエゾ電界を効果的に緩和したり、或いはそれらの技術に基づいて、実際に特段の派生問題を生むことなく光半導体素子の動作効率を改善したりすることは、現在の一般的な技術水準に照らして、必ずしも容易とは言えない。

【0015】

本発明は、上記の課題を解決するために成されたものであり、その目的は、広大なr面を有する III族窒化物系化合物半導体から成る半導体結晶の製造方法を開示することである。

また、本発明の更なる目的は、特段の派生問題を生むことなくピエゾ電界の悪影響を効果的に緩和若しくは最小化することができる光半導体素子の構造や製造方法を開示することである。

ただし、上記の個々の目的は、本発明の個々の手段の内の少なくとも何れか1つによって、個々に達成されれば十分であって、本願の個々の発明(下記の個々の手段)は、上記の全ての課題を同時に解決する具体的実施形態が存在することを必ずしも保証するものではない。

【課題を解決するための手段】

【0016】

上記の課題を解決するためには、以下の手段が有効である。

即ち、本発明の第1の手段は、 III族窒化物系化合物半導体から成る半導体層を有する半導体素子であって、サファイア基板と、サファイア基板が有する平面状の主面において形成され、主面に平行ではない平面で構成された二つの側壁面を有する複数の平行なストライプ溝と、複数のストライプ溝において、 III族窒化物系化合物半導体を成長させる側壁面を主内壁面とし、この主内壁面に形成されたバッファ層と、複数のストライプ溝の各主内壁面に対して垂直に、バッファ層の上にc軸方向に成長し、主面の面内方向において合体し、サファイア基板の主面を覆う、 III族窒化物系化合物半導体から成る第1半導体層と、第1半導体層のサファイア基板の主面に平行な面を結晶成長核として、主面に対して垂直な方向に成長した、 III族窒化物系化合物半導体から成る第2半導体層と、第2半導体層の上部に形成された活性層とを有し、ストライプ溝の主内壁面とサファイア基板の主面とが成す第1の角θ1 を、 III族窒化物系化合物半導体のc軸と、 III族窒化物系化合物半導体のピエゾ電界が零となる結晶方位であるr軸、a軸、又は、m軸の方位との成す第2の角θ0 に対して、θ0 −10°≦θ1 ≦θ0 +10°を満たす角度とし、第1半導体層、第2半導体層及び活性層における、サファイア基板の主面に垂直な方向の結晶軸は、 III族窒化物系化合物半導体のr軸、a軸、又は、m軸に対して、±10°以下となる結晶軸であることを特徴とする半導体素子である。

【0017】

また、本発明の第2の手段は、 III族窒化物系化合物半導体から成る半導体層を有する III族窒化物系化合物半導体基板であって、サファイア基板と、サファイア基板が有する平面状の主面において形成され、主面に平行ではない平面で構成された二つの側壁面を有する複数の平行なストライプ溝と、複数のストライプ溝において、 III族窒化物系化合物半導体を成長させる側壁面を主内壁面とし、この主内壁面に形成されたバッファ層と、複数のストライプ溝の各主内壁面に対して垂直に、バッファ層の上にc軸方向に成長し、主面の面内方向において合体し、サファイア基板の主面を覆う、 III族窒化物系化合物半導体から成る第1半導体層と、第1半導体層のサファイア基板の主面に平行な面を結晶成長核として、主面に対して垂直な方向に成長した、 III族窒化物系化合物半導体から成る第2半導体層とを有し、ストライプ溝の主内壁面とサファイア基板の主面とが成す第1の角θ1 は、 III族窒化物系化合物半導体のc軸と、 III族窒化物系化合物半導体のピエゾ電界が零となる結晶方位であるr軸、a軸、又は、m軸の方位との成す第2の角θ0 に対して、θ0 −10°≦θ1 ≦θ0 +10°を満たす角度であり、第1半導体層及び第2半導体層における、サファイア基板の主面に垂直な方向の結晶軸は、 III族窒化物系化合物半導体のr軸、a軸、又は、m軸に対して、±10°以下となる結晶軸であることを特徴とする III族窒化物系化合物半導体基板である。

【0018】

また、本発明の第3の手段は、第1の手段において、ストライプ溝の二つの側壁面のうちバッファ層が形成されていない側壁面は、 III族窒化物系化合物半導体のサファイア基板からの成長を阻害するマスクが形成されておらずサファイア基板が露出していることを特徴とする。

【0019】

また、本発明の第4の手段は、第2の手段において、ストライプ溝の二つの側壁面のうちバッファ層が形成されていない側壁面は、 III族窒化物系化合物半導体のサファイア基板からの成長を阻害するマスクが形成されておらずサファイア基板が露出していることを特徴とする。

【0020】

また、本発明の第5の手段は、第1、第3の手段において、サファイア基板の主内壁面の法線ベクトルは、サファイア基板におけるc軸又はa軸であることを特徴とする。

【0021】

また、本発明の第6の手段は、第2、第4の手段において、サファイア基板の主内壁面の法線ベクトルは、サファイア基板におけるc軸又はa軸であることを特徴とする。

【0022】

また、本発明の第7の手段は、第1、第3、又は、第5の手段において、ピエゾ電界が零となる結晶方位はr軸の方位であり、第2の角θ0 は、43.2°であることを特徴とする。

【0023】

また、本発明の第8の手段は、第2、第4、又は、第6の手段において、ピエゾ電界が零となる結晶方位はr軸の方位であり、第2の角θ0 は、43.2°であることを特徴とする。

【0024】

また、本発明の第9の手段は、第1、第3、第5、又は、第7の手段において、サファイア基板の主内壁面の法線ベクトルは、サファイア基板におけるc軸であり、ピエゾ電界が零となる結晶方位はa軸又はm軸であり、第2の角θ0 は、90°であることを特徴とする。

【0025】

また、本発明の第10の手段は、第2、第4、第6、又は、第8の手段において、サファイア基板の主内壁面の法線ベクトルは、サファイア基板におけるc軸であり、ピエゾ電零となる結晶方位はa軸又はm軸であり、第2の角θ0 は、90°であることを特徴とする。

【0026】

ただし、より望ましくは、「θ0 −3°≦θ1 ≦θ0 +3°」を満たす様に設定すると良い。また、更には、「θ0 −1°<θ1 <θ0 +1°」を満たす様に設定することがより望ましい。

【0027】

なお、上記のc軸の向きは、それをミラー指数を用いて書けば[0001]と表される向きである。各結晶面のミラー指数を以下に例示する。

c面:(0001)

a面:(11−20)

m面:(10−10)

r面:(10−12)

ただし、これらはあくまでも例示であり、所望の半導体結晶の結晶構造が六方晶系であるので、例えばそれらのa面やm面については、他にも当然ながら対称なその他の5つの向きの面がある。

【0028】

なお、上記の本成長工程においては、主面に対して垂直に半導体結晶を縦方向成長させても良いし、或いは主面上に形成されたマスク上方において、主面に対して略平行に半導体結晶を横方向成長させても良い。また、その様な半導体結晶の横方向成長後に、更に縦方向成長を実施しても良い。これらの成長方向に係わる結晶成長の形態や、各形態の組み合わせは任意で良い。

【0029】

また、上記の主面は、結晶成長面に広い1平面を用いる通常の結晶成長における主面と言われる部位(その広い1平面)に相当するが、しかし、本発明では、上記の様に溝形成工程を導入してこの主面を加工し、そのストライプ溝内にバッファ層を積層するので、上記の主面は、バッファ層を介して所望の結晶成長が開始される面とは一致しない。

【0030】

また、ストライプ溝の断面形状を矩形とする場合、上記の主面に対して垂直な側壁面(:ストライプ溝の内壁面)がストライプ溝内で互いに向かい合うことになるが、この様な場合、ストライプ溝内の一方の内壁面だけにバッファ層を形成し、かつ、そのバッファ層が積層される全ての内壁面の法線の向きを1つの向きに揃える様に制限しても良いし、或いはまた、向かい合う双方何れの面にもバッファ層を形成する様にしても良い。

【0031】

また、ストライプ溝が埋まる際には、c面とは異なる局所的な個々の結晶成長面が相互に繋がって略一連の結晶成長面が形成されるが、この時、個々のストライプ溝の中にボイド(:結晶が成長せずにできる空洞部)が形成されて残留していても特段の支障を来すことはない。

【0032】

また、本発明において、ピエゾ電界が零となる上記の結晶方位としてr軸の方位を選択し、六方晶系の結晶構造を有する結晶成長基板を用い、主面の法線ベクトル<σ|の向きを、結晶成長基板のc軸の正の向きからm軸の正の向きに向って第1の角θ1 だけ回転させ、ストライプ溝の長手方向をa軸の方向に取っても良い。

【0033】

また、本発明において、ピエゾ電界が零となる上記の結晶方位としてr軸の方位を選択し、六方晶系の結晶構造を有する結晶成長基板を用い、主面の法線ベクトル<σ|の向きを、結晶成長基板のa軸の正の向きからm軸の正の向きに向って第1の角θ1 だけ回転させ、ストライプ溝の長手方向をc軸の方向に取っても良い。

【0034】

また、本発明において、ピエゾ電界が零となる上記の結晶方位としてr軸の方位を選択し、六方晶系の結晶構造を有する結晶成長基板を用い、主面の法線ベクトル<σ|の向きを、結晶成長基板のa軸の正の向きからc軸の正の向きに向って第1の角θ1 だけ回転させ、ストライプ溝の長手方向をm軸の方向に取っても良い。

【0035】

また、本発明において、ピエゾ電界が零となる上記の結晶方位をa軸又はm軸の方位にしても良い。この時、第2の角θ0 は90°となる。したがって、前述の本発明の第1の手段又は第2の手段に基づき、第1の角θ1 は、80°以上100°以下の範囲であればピエゾ電界を抑制する効果が大きく得られ、かつ、この第1の角θ1 は、直角に近いほどより望ましい。また、この時用いる結晶成長基板は、a面を主面とするa面基板か、又はm面を主面とするm面基板を用いることが望ましい。また、上記の主面上に形成するストライプ溝の長手方向は、結晶成長基板のc軸の方向に対して略垂直な方向に取ることが望ましい。また、ストライプ溝の長手方向は、m軸又はa軸の方向とすることが望ましい。

【0036】

また、ストライプ溝の内側の側壁(内壁面)を主面に略垂直な側壁面から形成する場合、所望の半導体結晶を横方向成長させる場合には、ストライプ溝の両側の内側壁にバッファ層を形成してから横方向成長させて溝の中央部で合体させても良い。この様な場合には、ストライプ溝の内側で対峙する上記の2面の側壁(内壁面)の双方にバッファ層を積層しておくことが望ましい。

【0037】

なお、以上の本発明の第3乃至第10の各手段は、それぞれ何れも、本発明の第1の手段及び第2の手段を実施するにあたっての、より望ましい若しくはより具体的な個別の実施形態を例示するものである。したがって、これらの例示は、本発明の第1の手段及び第2の手段を実施するにあたって、必ずしも何れか1つの手段を選択して採用しなければならないことを意味するものではない。即ち、上記の本発明の第1の手段又は第2の手段により、本発明の第1の手段又は第2の手段の作用・効果を含め、少なくとも上記の何れか1つの作用・効果を得ることができる。

【0038】

なお、本発明において、主面と略同じ向きにr面を形成してその結晶成長面を更に成長させる場合には、第1半導体層の成長工程(非縦方向成長工程)では、所望の半導体結晶は少なくともファセット成長する。

また、本発明において、主面と略同じ向きにa面又はm面を形成してその結晶成長面を更に成長させる場合には、第1半導体層は、所望の半導体結晶は少なくとも横方向成長する。

【0039】

また、本発明において、ストライプ溝を構成する主内壁面以外の内壁面上に半導体結晶の選択成長を促すマスクを結晶成長基板上に形成しても良い。

【0040】

また、本発明において、隣接する他のストライプ溝との間に上記の主面の平坦部が残される様に各ストライプ溝を形成し、この平坦部にもマスクを形成し、更に、ストライプ溝上に成長した半導体結晶を核として、上記の平坦部に半導体結晶を横方向成長させてもよい。なお、この横方向成長のあとに、所望の半導体結晶を縦方向成長をさせても良い。

【0041】

また、本発明において、上記の複数のストライプ溝を、その幅方向に間隔を置かずに隙間なく、主面上に連続して形成してもよい。この時、上記の主面を構成していた平坦面は全面的に消滅する。

【0042】

また、本発明において、ストライプ溝を構成する主内壁面以外の内壁面を上記の主面に対して垂直に形成してもよい。

【0043】

また、本発明において、第1半導体層の結晶成長温度を900℃以上1150℃以下にしても良い。

【0044】

以上の本発明の手段により、前記の課題を効果的、或いは合理的に解決することができる。

【発明の効果】

【0045】

以上の本発明の手段によって得られる効果は以下の通りである。

即ち、本発明によれば、略一連の広大な1つのr面、a面、m面、若しくはこれらの何れか一つの面に概ね近似できる面を、略一連の広大な層界面として有する半導体結晶とすることができる。

【0046】

バッファ層が供する結晶成長面上では、通常、目的の半導体結晶はc面成長するので、本発明によれば、ファセット成長又は横方向成長によって、第1半導体層の主面をr面、a面、m面、又はこれらの何れか一つの結晶面から10°以内のオフ角を有する面とすることができる。

【0047】

また、θ0 ≒θ1 なる関係に基づいて、各部で成長する個々の結晶成長面は、何れも結晶成長基板が最初に有していた上記の主面と略同方向を向きつつ結晶成長する。以下、これと同じ向きの結晶成長面を総称してΛ面と言うことがある。このΛ面は、r面、a面、又はm面の何れかと一致していることがより望ましいが、それらと若干(10°以内)のオフ角を持つ面であっても特段差し支えない。

【0048】

これにより、上記の第1半導体層の成長完了時(非縦方向成長工程の完了時)には、各部の個々のΛ面がそれぞれ互いに略一連に繋がって、広大で略平坦な1つの面を形成する。

また、各部の個々のΛ面の間に若干の段差などの凹凸部が生じても、その後の本発明の第2半導体層の成長工程において、Λ面に垂直な方向に進む各部の縦方向成長によって、それらの凹凸部は良好に是正されて、十分に平坦化される。

【0049】

ただし、上記の角度θ1 は、極力上記の角θ0 に近いことが望ましく、上記の角θ0 に一致する時に最良の結果をもたらす。例えば、目的の半導体結晶が III族窒化物系化合物結晶の場合、一連の広大な1つのr面を得るためには、θ1 =43.2°(=θ0 )とすると最良の結果が得られる。

【0050】

また、この広大な層界面(上記のΛ面)は、ファセット成長又は横方向成長に基づいて形成される面であるので、その転位密度は必然的に低く抑制される。

更に、目的の半導体結晶と結晶成長基板との間の接合面は、例えば矩形波や三角波や鋸歯形状などの波板状に形成されるので、格子定数差や熱膨張係数差などに伴って発生し得る目的の半導体結晶と結晶成長基板との間の応力を効果的に緩和する効果をも同時に得ることができる。

【0051】

また、上記の応力緩和作用は、ストライプ溝の中にボイドが大きく形成されていた方がより効果的に発現する。ただし、ストライプ溝中のボイドの形成は必ずしも必要なものではなく、また、外部量子効率の観点から言えば、ボイドは極力小さい又は極力少ない方が良い場合も多い。したがって、上記のストライプ溝中のボイドの有無やその大小などに付いては、これらの応力緩和作用や外部量子効率などの諸条件や、或いは所望の光半導体素子の性能などまでをも総合的に考慮して、個々に具体的に設計することが望ましい。

【0052】

以上の様な各作用をもたらす本発明によれば、従来より問題であった前述の温度の昇降過程に生じる原子脱離の発生が回避でき、或いは半導体結晶の界面の転位密度が低減するなどするため、上記の目的の半導体結晶における結晶品質は、十分良好に確保することができる。

【0053】

また、本発明によれば、特に広大なr面を形成する場合に、上記のストライプ溝を、上記の主面上に比較的容易または綺麗に形成することができるか、上記のバッファ層を容易、綺麗又は確実に積層することができるか、或いは、周知のファセット成長の作用に基づいて目的の半導体結晶の転位密度を比較的低く抑制することができる。

【0054】

ただし、ストライプ溝を形成する向きを決定づける基準としては、上記の様な作用・効果の観点以外にも、半導体ウェハを所望の光半導体素子などに分割する時の分割の容易性の観点なども有り得る。したがって、上記のストライプ溝を形成する向きは、例えば所望の光半導体素子の平面形状などにも留意して、より総合的に判断することがより望ましい。

【0055】

また、本発明によれば、広大なa面又はm面を形成することができる。

従来のa面又はm面上に活性層を形成した半導体発光素子としては、例えば「特開2000−21789」の図18に記載されているものなどが公知である。この光素子を製造する場合、少なくとも活性層とその周辺の半導体層は、「ラテラル方向のみに成長する成長条件」で結晶成長させなければならない。しかしながら、この様に完全に横方向の結晶成長の条件設定は、実際には極めて困難である。また、獲得し得る活性層の面積が十分には大きくなり難い点や、獲得された半導体ウェハの加工容易性などにも大きな問題が残っているので、この様な光素子を実際に量産することは、現在の一般的な工業的技術水準に照らして非常に困難であると言わざるを得ない。

【0056】

しかしながら、本発明によれば、広大なa面又はm面を形成することができ、かつ、その後の所望の半導体層の結晶成長は、従来の「ラテラル方向のみに成長する成長条件」で実施する必要もない。したがって、本発明によれば、所望の高い発光効率と大きな光出力を有する発光素子や受光素子を量産することができる。

【0057】

この時、上方に何れの結晶面が現れるかは、結晶成長基板の向きに依存する。即ち、a面を主面とする基板を用いれば、目的の半導体結晶についても広大なa面を得ることができ、m面基板を用いれば、目的の半導体結晶についても広大なm面を得ることができる。ただし、この時、主面上に形成するストライプ溝の長手方向は、結晶成長基板のc軸の方向に対して略垂直な方向に取ると良い。より望ましくは、m軸方向またはa軸方向に取ると更に良い。

【0058】

また、本発明によれば、選択成長を促すマスクによって、バッファ層の向きを1通りに統一することが可能又は容易となる。例えば、バッファ層を結晶成長によって形成する場合には、バッファ層を形成すべきある一定の向きの面だけを残しておき、その他の面をマスクすれば良い。

また、これらのマスクは、縦方向成長工程におけるELOマスクとしても作用し得る。したがって、この場合には、上記の本発明の縦方向成長工程で得られる半導体結晶の転位密度を効果的に低減することも可能となる。

【0059】

また、本発明によれば、上記の平坦部に形成されるマスクがELOマスクとして作用する。即ち、このマスクの上では、所望の半導体結晶が横方向に成長するため、その横方向成長部分には転位が伝播しない。このため、転位密度が低い半導体結晶を得ることができる。

【0060】

また、本発明によれば、上記の主面上に平坦部が残らないので、例えば斜めスパッタや或いは斜め露光などの様な単純で簡単な準備工程だけで、バッファ層または基板が供する、所定の向きの所望の結晶成長面だけを形成または露出させることができる場合がある。(例えば、図3−Aや、図10−Bなどの例は、この様な場合を典型的かつ具体的に例示するものである。)

【0061】

また、本発明によれば、方向性を有するドライエッチングなどによって、ストライプ溝の内壁面を容易に形成することができる。

また、本発明によれば、ストライプ溝の主内壁面を含むストライプ溝の各内壁面を良好に形成することができる。

【0062】

なお、ストライプ溝の断面形状を矩形とする場合、上記の主面に対して垂直な側壁面(:ストライプ溝の内壁面)がストライプ溝内で互いに向かい合うことになるが、この様な場合、ストライプ溝内の一方の内壁面だけにバッファ層を形成し、かつ、そのバッファ層が積層される全ての内壁面の法線の向きを1つの向きに揃える様に制限しても良いし、或いはまた、向かい合う双方何れの面にもバッファ層を形成する様にしても良い。向かい合う双方何れの面にもバッファ層を形成すれば、双方から成長してきた半導体結晶をストライプ溝の略中央で合体させることができる。そして、この様な場合にも、本発明を具体的に実施することができる。

【0063】

また、本発明によれば、ファセット成長を良好に促す結晶成長条件を設定することができるので、上記の第1半導体層の成長においてより確実に上記のΛ面のファセット成長を継続することができる。したがって、本発明によれば、上記の一連化や平坦化が比較的容易かつ良好に達成できる。このファセット成長の結晶成長温度の好適値は、キャリアガスや結晶材料ガスの流量や分圧や或いは結晶成長速度等にも依存するものの、通常、より望ましいこの結晶成長温度は、950℃〜1100℃の範囲内にある。

【0064】

また、本発明によれば、上記の従来技術の課題においてみられた様な、従来のエッチング工程や或いは従来のマスク形成工程などを介在させるべき必要性を完全に排除することができるので、これらの介在工程に伴う上記の昇降温に起因する問題も必然的に払拭することができる。また、各ストライプ溝を構成する上記の各内壁面上には、それぞれバッファ層が成膜されるので、これにより、内壁面上にダメージ層が形成されていたとしてもその悪影響は効果的に緩和、抑制することができる。

【0065】

また、素子構造として必要とされる例えばn型層などの各半導体結晶層のΛ面の結晶成長は、活性層を形成するよりも遥かに前の段階より開始することができる。例えば、n型コンタクト層の結晶成長を実施するなどの早期の段階から開始することができる。更に、Λ面の結晶成長によって、光半導体素子の活性層を略一連の略平坦な板状(平面状)に形成することが可能または容易となる。

【0066】

したがって、本発明によれば、非常に良好な結晶成長を促すこれらの作用によって、Λ面を界面とする極めて高品質の活性層を形成することが可能または容易となる。したがって、本発明によれば、目的の光半導体素子において、特段の派生問題を生むことなくピエゾ電界の悪影響を効果的に緩和若しくは最小化することができ、よって、その光半導体素子の動作効率を大幅に向上させることができる。

【0067】

このため、本発明のIII 族窒化物系化合物半導体基板によれば、半導体素子を、容易に製造することができる。言い換えれば、本発明のIII 族窒化物系化合物半導体基板結晶成長基板は、工業的に極めて有用となり得るので、上記の本発明の結晶成長基板は単独でも一般市場において高い商品価値を持ち得る。

【0068】

なお、この様な結晶成長基板においては、上記のΛ面上に、そのΛ面に対して平行な界面を有する平板状の半導体結晶層を更に積層しておくことがより望ましい。即ち、本発明によれば、結晶成長面の平坦性が向上するなどして、結晶成長面の品質が向上する。

【0069】

また、更には、この様な半導体結晶層を十分に厚く積層することによって、下地基板(最初の結晶成長基板)を除去することも可能又は容易となる。また、下地基板が除去されれば、その半導体結晶層を、自立したバルク結晶から成る結晶成長基板として用いることができる。異種基板を有しない自立したバルク結晶から成る結晶成長基板は、熱膨張係数差や格子定数差などに起因する応力の問題から解放される点で、非常に有利である。

【図面の簡単な説明】

【0070】

【図1−A】主面Σを主面とする実施例1の結晶成長基板1(下地基板)の側面図

【図1−B】主面Σにレジストマスク2が形成された結晶成長基板1の側面図

【図1−C】レジストマスク2が形状加工された結晶成長基板1の側面図

【図2】ドライエッチングにより主面Σが形状加工された結晶成長基板1の斜視図

【図3−A】実施例1のバッファ層積層工程を示す結晶成長基板1の部分的断面図

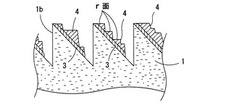

【図3−B】非縦方向成長工程(前半)を示す結晶成長基板1の部分的断面図

【図3−C】非縦方向成長工程(後半)を示す結晶成長基板1の部分的断面図

【図4】目的の半導体結晶層6を有するテンプレート10の断面図

【図5】テンプレート10を有するLED100の断面図(実施例2)

【図6】テンプレート10′を有する半導体レーザ200の断面図(実施例3)

【図7】テンプレート10′の部分的な断面図(実施例3)

【図8−A】バッファ層を結晶成長させる実施例(実施例4)の基板の断面図

【図8−B】バッファ層を結晶成長させる実施例(実施例4)の基板の断面図

【図8−C】バッファ層を結晶成長させる実施例(実施例4)の基板の断面図

【図8−D】バッファ層を結晶成長させる実施例(実施例4)の基板の断面図

【図9−A】バッファ層を結晶成長させる実施例(実施例5)の基板の断面図

【図9−B】バッファ層を結晶成長させる実施例(実施例5)の基板の断面図

【図9−C】バッファ層を結晶成長させる実施例(実施例5)の基板の断面図

【図10−A】バッファ層を結晶成長させる実施例(実施例6)の基板の断面図

【図10−B】バッファ層を結晶成長させる実施例(実施例6)の基板の断面図

【図11】窒化ガリウム系の半導体でのピエゾ電界の角度依存性を示すグラフ

【図12】活性層のピエゾ電界の緩和を試みた従来の光半導体素子の断面図

【発明を実施するための形態】

【0071】

上記の下地基板(または最初の結晶成長基板)としては、例えば、サファイア、シリコン(Si)、炭化珪素(SiC)、酸化亜鉛(ZnO)、2元、3元、又は4元のAlx Iny Ga1-x-y N(0≦x≦1,0≦y≦1,0≦x+y≦1)、或いはその他の公知の結晶成長用の基板材料を使用することができる。即ち、これらの基板は、立方晶系の結晶でも良く、必ずしも六方晶系の結晶に限定されるものではない。

また、例えば、熱膨張係数差や格子定数差などに起因して半導体層に加わる応力を排除するために、所望の半導体結晶に対するそれらの差値が小さい基板材料等を用いると良い場合もある。

【0072】

また、本発明は、2元、3元、或いは4元の「Al1-x-y Gay Inx N;0≦x≦1,0≦y≦1,0≦1−x−y≦1」から成る、より一般の III族窒化物系化合物半導体を目的の半導体結晶とする場合にも有効である。更に、前記の目的の半導体結晶は、2元、3元、又は4元の「Al1-x-y Gay Inx N;0≦x≦1,0≦y≦1,0≦1−x−y≦1」中の III族元素(Al,In,Ga)の内の一部をボロン(B)やタリウム(Tl)等で置換したり、或いは、上記の組成式中の窒素(N)の一部をリン(P)、砒素(As)、アンチモン(Sb)、ビスマス(Bi)等で置換したりした半導体等を上記の目的の半導体結晶としても良い。本発明の作用・効果は、これらの若干の変形や置換などに対しても一定の普遍性を示すものである。

【0073】

また、前記の目的の半導体結晶は、n型またはp型の周知の適当な不純物が添加されたものであっても良い。p型の不純物としては、例えば、マグネシウム(Mg)や、或いはカルシウム(Ca)等を添加することができる。また、n型の不純物としては、例えば、シリコン(Si)や、硫黄(S)、セレン(Se)、テルル(Te)、或いはゲルマニウム(Ge)などを添加することができる。また、これらの不純物は、同時に2元素以上を添加しても良いし、同時に両型(p型とn型)を添加しても良い。

【0074】

また、縦方向成長工程の後に、又は、その縦方向成長工程に並行して、目的とする上記の半導体結晶から結晶成長基板を除去する基板除去工程を設けても良い。この様な基板除去工程の導入によれば、下地基板(最初の結晶成長基板)が除去されるため、目的の半導体結晶を厚く結晶成長させた場合には、自立した半導体バルク結晶を得ることも十分に可能となる。この様な自立した半導体バルク結晶は、勿論光半導体素子の結晶成長基板などに有用となる。

【0075】

また、光半導体素子を製造する場合には、結晶成長基板の格子定数、熱膨張係数、屈折率、或いは透光性などが厳しく問われる場合が多いが、上記の最初の結晶成長基板(以下、下地基板と言うことがある。)を除去できれば、その様な制約から必然的に解放されるので、下地基板の材料選択の任意性も向上する。

【0076】

また、ストライプ溝の形状や大小などによっては、ストライプ溝の底部などにボイドができ易くなる。そして、この様なボイドは、光半導体素子の光取り出し効率や光取り込み効率などを低下させることがあるが、たとえその様な場合であっても、上記の様に下地基板を除去すれば、それらの不具合も同時に回避することができる。

【0077】

なお、自立した半導体バルク結晶に対するハンドリングに伴うその結晶の破損の確率を低減して、十分な歩留りを確保するために、上記の基板除去工程を実施する場合には、目的の半導体結晶(:自立した半導体バルク結晶)は、少なくとも400μm以上に積層することが望ましい。また、バッファ層や非縦方向成長部は相対的に十分に小さいので、これらの部位を残留させて上記の下地基板のみを除去する様にしても、勿論、略同等の作用・効果を得ることができる。或いは、上記の半導体結晶層(:自立した半導体バルク結晶)の下方の一部をも除去してしまっても、特段の支障を来すものではない。

【0078】

また、上記の基板除去工程は、上記の縦方向成長工程と並行して実施することも可能である。その様な並行処理を可能とする製造方法や製造装置としては、例えば「特開2003−7619: III族窒化物系化合物半導体の製造方法及び製造装置」に開示されている技法などが公知である。この公知文献には、結晶成長基板の表裏両面から結晶成長やエッチング等を同時に実施することができる装置等が開示されているが、例えばこの様な技法を利用すれば、目的の半導体結晶を厚く成長させる際に、目的の半導体結晶に作用する応力を極力排除することができる。

【0079】

また、目的とする半導体結晶の組成を結晶成長基板の組成に略一致させると良い場合がある。これにより、目的の半導体結晶と結晶成長基板との熱膨張係数差を小さくすることができるので、上記の様な両面同時処理を可能にする様な特殊な装置を用意できない場合にも、応力の発生を防いで目的の半導体結晶を十分に厚く形成することが可能又は容易となる。

【0080】

また、上記のストライプ溝の深さは、1μm以上30μm以下にすることが望ましい。この範囲は、1μm以上15μm以下とすると更に望ましい。この様な寸法設定によれば、各ストライプ溝内で結晶成長するΛ面が良好に繋がって、一連の略平坦で広大なΛ面を良好に形成することができる。

また、この深さを浅くしすぎるとストライプ溝が細くなり過ぎて、所望の適当な形状にこのストライプ溝を形成することが、現在の周知の基板加工技術の加工精度に照らして困難となる。或いは、各ストライプ溝内で各々綺麗なΛ面が形成される前に、それらの個々のΛ面が相互に不規則に繋がってしまう恐れが生じる。

【0081】

また、この深さを深くし過ぎると、各ストライプ溝内で結晶成長するΛ面が、それぞれ互いに一連に良好に繋がるまでに掛かる時間(即ち、本発明の非縦方向成長工程に掛かる時間)が長くなり過ぎて、必ずしも高い生産性を確保できるとは言えない。また、この深さを深くし過ぎると、局所的な成長速度のムラに伴って発生し得る、上記の個々のΛ面間の段差が大きくなってしまう恐れも十分には払拭できない。また、この深さを深くし過ぎると、特にストライプ溝が急峻な側壁面を有する場合、深い部位には材料ガスが到達し難くなるので、バッファ層の積層状況などによってはストライプ溝の底部などにボイドが形成され易くなるので、前にも言及した様に、場合によっては必ずしも望ましい結晶成長形態になるとは言い切れない。

これらの観点より、各ストライプ溝の深さは、約1μm以上15μm以下がより望ましい。更に望ましくは、ストライプ溝の深さは約2μm以上5μm以下が良い。

【0082】

また、特に広大なr面を獲得したい場合、上記の主面に対して略垂直な側壁面を用いて、上記のストライプ溝の1つの内壁面を形成すると良い場合がある。この設定によれば、主面に略垂直な上記の側壁面をドライエッチングなどによって容易に形成することができると同時に、特に広大なr面を得たい場合には、この構成によって、ストライプ溝が上記の非縦方向成長工程で、成長した半導体結晶によって略過不足なく埋まる様な結晶成長条件が成立し易くなる場合も少なくない。このため、結晶成長基板と目的の半導体結晶との間には、非常にボイドの少ない界面を形成することも可能又は容易となる。したがって、上記の結晶成長基板をそのまま光半導体素子の基板とする場合には、光取り出し効率または光取り込み効率の高い素子を製造できる場合もある。

【0083】

以下、本発明を具体的な実施例に基づいて説明する。

ただし、本発明の実施形態は、以下に示す個々の実施例に限定されるものではない。

【実施例1】

【0084】

(結晶成長基板の構造とその製造工程)

図1−Aに、主面Σを主面とする本実施例1の結晶成長基板1(下地基板)の側面図を示す。この結晶成長基板1はサファイアから形成されている。図中の単位ベクトル<σ|は、結晶成長基板1の上方の略平坦な主面Σの法線ベクトルであり、以下、この法線ベクトル<σ|の向きを3次元直交座標系のz軸の正の向きとする。

【0085】

また、本明細書では、結晶の各面は4つの軸を使った六方晶系におけるミラー指数(hkil)を用いて、上記の3次元直交座標系(x,y,z)と区別する。したがって、例えば上記の法線ベクトル<σ|は、この3次元直交座標を用いて、次式(1)の様に書くことができる。

(法線ベクトル<σ|の直交座標表示)

<σ|=(0,0,1) …(1)

【0086】

図1−Aの結晶成長基板1は、次式(2)を満たす板状の直方体として成形されている。ただし、ここでは、図1−Aの結晶成長基板1を形成するサファイア結晶のc軸の正の向きを向く単位ベクトルを以下<c|で表す。また、このサファイア結晶の1つのa軸の正の向きを向く単位ベクトルを以下<a|で表す。なお、下記の角θ0 は、六方晶系のGaN単結晶(即ち、後述の目的の半導体結晶層6)においてc軸とr軸とが成す角度であり、常温では43.2°である。

【0087】

(単位ベクトル<c|,<a|の直交座標表示)

<c|=(0,sinθ0 ′,cosθ0 ′),

<a|=(0,cosθ0 ′,−sinθ0 ′),

θ0 ′≒θ0 …(2)

ここで、上記の角θ0 ′はこの角θ0 の近傍値でよく、例えば45°程度でも良い。以下、本実施例では、この式(2)においてθ0 ′=θ0 =43.2°が満たされているものとする。

【0088】

また、ここで注意すべき点は、上記の主面Σは、サファイア基板以外の場合でも、一般にはr面とはならないが、それにも関わらず、最終的にはこの主面Σに対して略平行な広大なr面を有する半導体結晶層(即ち、後述の目的の半導体結晶層6)が得られる点である。そして、この理想的とも言える帰結は、後述の傾斜角θ1 の角度設定に依る所が大きい。そして、これらの点が本発明の最も大きな特徴の一つとなっている。

【0089】

図1−Bに、塗布及びベーキングによって上記の主面Σにレジストマスク2が形成された結晶成長基板1の側面図を示す。また、図1−Cには、レジストマスク2が形状加工された結晶成長基板1の側面図を示す。レジストマスク2に対する露光方法としては、例えば次の何れかの方法を採用しても良い。これらの露光方法については周知の適当な任意の方法を用いることができる。

(1)ストライプ形状の濃淡パターンを有するネガを作成して用いる方法

(2)目的の形状に適合する様に焦点制御されたレーザ光を走査制御して照射する方法

【0090】

また、このレジストマスク2の厚さΔ1は、ドライエッチング実行時のレジストマスク2の深さ方向への侵食進行速度Rと、結晶成長基板1の侵食進行速度rと、フォトリソグラフィーなどによってレジストマスク2に形成すべき傾斜面2aの傾斜角φと、その後のドライエッチングによって結晶成長基板1に形成すべき傾斜面1aの傾斜角θ1 (図2)などに基づいて決定することができる。これらの変数R,r,φ,θ1 ,Δ1などが満たすべき関係式に付いては既に公知である。この具体的な関係については、例えば、特開2001−160657に開示されている関係式などを参考にすれば良い。

【0091】

上記のドライエッチングによって上記の主面Σが所望の形状に形状加工された結晶成長基板1の斜視図を図2に示す。ストライプ溝Sは、主面Σに形成された図中の傾斜面1aと側壁面1bから構成されている。また、符号Δ2はストライプ溝Sの深さを表しており、符号θ1 (=90°−α)は下地基板1の主面Σと傾斜面1aとが成す角度を表している。この様に、ストライプ溝Sの長手方向をy軸方向と略一致させた時、上記のa軸の方向(単位ベクトル<a|)と上記のストライプ溝Sの長手方向≡<s|=(0,1,0)との成す角ρは極小(最小)となる(本発明の第6の手段)。この時、式(2)から判る様に、ρ=θ0 ′である。

【0092】

本実施例1では、次式(3)の様に結晶成長基板1を形成する。

(下地基板(結晶成長基板1)の寸法)

α ≡ 90°−θ1 ≒ 47°,

Δ2 ≒ 3μm,

D ≒ 400μm …(3)

なお、水平方向(xy方向)の面積や縦横比などは任意で良い。

【0093】

図3−Aは、本実施例1のバッファ層積層工程を示す結晶成長基板1の部分的断面図である。バッファ層3は、AlGaN(またはAlNまたはGaN)からなる半導体層で、スパッタリングによって成膜する。使用するスパッタリング装置としては、例えば、高周波スパッタ装置や或いはプラズマスパッタ装置などが有用である。このスパッタリングにおいては、成膜領域を制限するために若干角度を付けて結晶成長基板1に対して斜めに材料を吹き付ける(斜めスパッタ)。図中の符号Aはその時の投射方向を表している。この傾け角δは、0°〜60°位で良い。本実施例におけるより望ましい範囲としては、3°〜10°程度である。この角度が大きいと後に形成されるボイドも大きくなる。また、この角度が小さ過ぎると、結晶成長基板1の側壁面1bにも材料が付着してしまい、後の非縦方向成長工程における所望のr面成長が順調に進展しない恐れが生じる。

【0094】

なお、上記のスパッタリングを実施する際の条件は以下の通りに設定する。

(スパッタリング条件)

積層するAlNの膜厚 : 640〔Å〕

スパッタガス : Ar(8sccm)/N2 (10sccm)

基板温度 : 430〔℃〕

DCパワー : 0.5〔W〕

電極面積 : 8000〔cm2 〕

【0095】

図3−B,−Cは、その後の本実施例1の非縦方向成長工程を示す結晶成長基板1の部分的断面図である。この非縦方向成長工程では、最初、上記のバッファ層3の上にはGaNのc面が結晶成長する。このc面成長は、下記の非縦方向成長工程の結晶成長条件に従えば、所謂ファセット成長として進行し、その非縦方向成長部4の片側の上向きのr面の法線ベクトルが、最初の主面Σの法線ベクトル<σ|と一致する様に結晶が成長する(図3−B)。

【0096】

ここでは、MOCVD法によって、上記の各ストライプ溝S中の大部分をGaN結晶で埋め込む。また、キャリアガスにH2 (またはN2 )を使用し、アンモニアとトリメチルガリウム(TMG)を下記の割合で供給する。これにより、各非縦方向成長部4の上面では、図3−Bに示す様にxy平面に平行にr面が結晶成長し、これらの個々のr面は、側壁面1bの近傍に若干のボイド5を形成しつつも、ストライプ溝Sを完全に覆い隠すまで結晶成長して、最終的には略一連の平坦面4aが形成される(図3−C)。

なお、この時(図3−B,−Cの時)の具体的な結晶成長条件は以下の通りにする。この条件設定は、継続的かつ順調なファセット成長を促進する上で重要である。また、下記の結晶成長速度は、r面に垂直な方向の結晶成長速度である。なお、下記のV/III 比は勿論モル比である。

【0097】

(非縦方向成長部4の結晶成長条件)

結晶成長温度 : 990〔℃〕

結晶成長速度 : 0.8〔μm/min〕

結晶成長時間 : 50〔min〕

供給ガス流量比(V/III 比): 5000

【0098】

図4は、GaN結晶から成る目的の半導体結晶層6を有するテンプレート10(新たな結晶成長基板)の断面図である。ここで、この半導体結晶層6の結晶成長条件は、次の通りとする。

(半導体結晶層6の結晶成長条件)

結晶成長温度 : 1050〔℃〕

結晶成長速度 : 0.6〔μm/min〕

結晶成長時間 : 100〔min〕

供給ガス流量比(V/III 比): 50000

【0099】

例えばこの様に、前述のMOCVD法において若干結晶成長条件を変えることで、半導体結晶層6のr面(上面6a)の転位密度が抑制されると共に、半導体結晶層6の上面6aの更なる平坦化を効果的に促進することができる。

したがって、以上の様にして得られるテンプレート10は、r面を界面とする広大かつ平坦な活性層の結晶成長を安定かつ確実に促進するので、内部量子効率の高い光半導体素子を製造する際の結晶成長基板として非常に有用なものとなる。

なお、後述の各実施例では、この様なテンプレートを用いて製造される内部量子効率の高い光半導体素子に付いて具体的に例示する。

【0100】

(r面成長を促進する結晶成長条件)

これらのr面成長には、MOCVD法が適している。また、安定したファセット成長(r面成長)を確実に誘起、促進するための結晶成長条件には、通常の一般的なc面成長の場合に対して、以下の特徴がある。

(1)結晶成長温度

結晶成長温度は、通常の一般的なc面成長の場合よりも低くした方が良い。

【0101】

(2)結晶成長速度

結晶成長速度は、通常の一般的なc面成長の場合よりも高くした方が良い。

(3)V/III 比

V/III 比は、通常の一般的なc面成長の場合よりも小さくした方が良い。

(4)アンモニアガス供給量

NH3 分圧は、通常の一般的なc面成長の場合よりも高くした方が良い。

【0102】

これらの具体的な適正範囲に付いては、既に概ね公知であり、ファセット成長に関わるこれらの一般的な諸傾向などについては、例えば以下の公開特許公報などからも、より詳しく具体的に知ることができる。

【0103】

ただし、これらの従来技術の目的は、所望の半導体結晶層の結晶品質を向上させることであって、これらの従来技術の思想や技法は、一連の平坦かつ広大なr面から成る積層界面を有する半導体結晶層を形成する様な目的や具体的アプローチを含んだものではない。また、これらの従来技術においては、c面成長によって活性層を形成する事例は多数見られるが、r面成長によって活性層を形成する事例は見当たらない。

【0104】

(参考例1)公開特許公報「特開平10−312971」

(参考例2)公開特許公報「特開平11−130597」

(参考例3)公開特許公報「特開平11−251631」

(参考例4)公開特許公報「特開2001−102307」

(参考例5)公開特許公報「特開2002−280609」

(参考例6)澤木宣彦、「選択成長法によるGaN微細構造の作製−集積形量子効果デバイスの実現に向けて−」名城大学ハイテクセンターシンポジウム(窒化物半導体研究センター成果発表シンポジウム)発表論文集、2000年6月23日

(参考例7)"Transmission Electron Microscopy Investigation of Dislocations in GaN Layer Grown by Facet-Controlled Epitaxial Lateral Overgrowth" , JAPANESE

JOURNAL OF APPLIED PHYSICS,Vol.40(2001)pp.L309-L312,Part2,No.4A,1 April 2001

(参考例8)水谷広光、外6名、「FACELO(ファセット制御ELO)によるGaNの低転位化」,信学技報,社団法人電子情報通信学会,ED2000-22,CPM2000-7,SDM2000-22(2000-05),pp.35-40

【実施例2】

【0105】

(LEDの構成例)

図5は、上記の実施例1のテンプレート10を有して成る本実施例2のLED100の断面図である。このテンプレート10では、図4、図5に法線ベクトル<σ|を用いて図示する通り、ノンドープのGaN結晶から成る前述の半導体結晶層6の上方の界面6aがr面となっている。このテンプレート10の上には、シリコン(Si)ドープのGaN から成る膜厚約4.0 μmの高キャリア濃度n+ 層103が形成されている。そして、この高キャリア濃度n+ 層103の上には、Siドープのn型GaN から成る膜厚約0.5 μmのクラッド層104が形成されている。

【0106】

更に、クラッド層104の上にGaNとGa0.8 In0.2 Nから成る多重量子井戸構造(MQW)の膜厚約500Åの発光層105が形成されている。発光層105の上にはp型Al0.15Ga0.85N から成る膜厚約600Åのクラッド層106が形成されている。さらに、クラッド層106の上にはp型GaN から成る膜厚約1500Åのコンタクト層107が形成されている。

【0107】

又、コンタクト層107の上には金属蒸着による薄膜正電極110が、n+ 層103上には負電極140が形成されている。薄膜正電極110は、コンタクト層107に接合する膜厚約15Åのニッケル(Ni)より成る薄膜正電極第1層111と、このNiに接合する膜厚約60Åの金(Au)より成る薄膜正電極第2層112とで構成されている。

【0108】

厚膜正電極120は、膜厚約175Åのバナジウム(V)より成る厚膜正電極第1層121と、膜厚約15000Åの金(Au)より成る厚膜正電極第2層122と、膜厚約100Åのアルミニウム(Al)より成る厚膜正電極第3層123とを薄膜正電極110の上から順次積層させることにより構成されている。負電極140は、膜厚約175Åのバナジウム(V) 層141と、膜厚約1000Åのアルミニウム(Al)層142と、膜厚約500Åのバナジウム(V) 層143と、膜厚約5000Åのニッケル(Ni)層144と、膜厚8000Åの金(Au)層145とを高キャリア濃度n+ 層103の一部露出された部分の上から順次積層させることにより構成されている。また最上部には、SiO2 膜より成る保護膜層130が形成されている。

【0109】

この様にして、形成されたLED100では、活性層(発光層105)の上下の各界面がr面から形成されており、この配向に基づいてピエゾ電界が略0に設定されているので、このLED100は、従来よりも高い発光効率を示す。

【実施例3】

【0110】

(半導体レーザの構成例)

図6に、本実施例3の半導体レーザ200の断面図を示す。この半導体レーザ200は、405nmのピーク波長で青紫色発光するものであり、上記の実施例1の下地基板1をベースに構成されたテンプレート10と略同様にして製造された他のテンプレート10′を有する。

【0111】

図7にこのテンプレート10′の部分的な断面図を示す。このテンプレート10′の先のテンプレート10に対する差異は、ストライプ溝Sの断面形状と斜めスパッタの投射角にある。即ち、本実施例3で使用するテンプレート10′では、傾斜面1a、1bから成る、断面形状が左右略対称形のV字形のストライプ溝S′が採用されている。また、バッファ層3はストライプ溝の一方の傾斜面1aにしか形成しない点では、図3−Aと同じだが、図3−Aのスパッタリングの投射の際の傾け角δに相当する角度は大幅に広く取られている。

【0112】

この様な設定によれば、テンプレート中にボイドを比較的大きく形成することができるので、下地基板と半導体結晶層との間の応力緩和作用が効果的に得られる点で非常に有利となる。

前述の実施例1では、ストライプ溝の片方の面を最初の主面Σに対して略垂直な側壁面(1b)で構成しているが、必ずしもその様な必要性があるわけではなく、例えば、本図7に例示する様に、断面形状が略対称形のV字溝や、或いはU字溝等を形成するなどしても良い。特に、所望の半導体結晶層を厚く結晶成長させたい場合には、基板と成長層との間には十分に歪み緩和作用がある方が望ましいが、その様な場合にはむしろボイドは大きく形成されている方が望ましい。この意味では、ストライプ溝の断面形状はむしろ、本図7に例示される様なV字形や、或いはU字形などの方が望ましい場合も少なくない。

【0113】

また、このテンプレート10′(図7)は、後述の通り共振器の下方部がエッチング処理によって大きくえぐられてしまうため、上記のボイドが外部量子効率などに悪影響を与える様な恐れは、少なくとも共振器の周辺においては全面的に排除される。また、このエッチング(:共振器直下のえぐり)によってもテンプレート10′が大きく二分されるため大きな歪み緩和作用が得られる。

【0114】

図6のテンプレート10′の上には、シリコン(Si)ドープのGaN から成る高キャリア濃度のn型コンタクト層202と、GaN から成るn型クラッド層203とが順次積層されている。更にその上には、活性層とその上下両側に位置する各型の光ガイド層から成る発光出力部204が形成されている。より具体的には、この発光出力部204は、Al0.01Ga0.99Nより成るn型の光ガイド層と、公知の端面発光型レーザダイオードに見られる一般的な多重量子井戸(MQW)構造の活性層と、マグネシウム(Mg)ドープのAl0.01Ga0.99Nから成るp型の光ガイド層とを順次積層することにより形成されたものである。

【0115】

この発光出力部204の上には、p型のAl0.12Ga0.88N から成るp型クラッド層と、Mgドープのp型のGaNから成るp型コンタクト層の計2層が順次積層されて形成されてできたp型半導体層205が配置されている。n型コンタクト層202は、上方(p型半導体層205側)からのエッチングによりその大部分が露出され、本エッチングにより、テンプレート10′に対して略垂直に立脚した平頂な共振器部分が形成される。また、この共振器の両脇には、SiO2 より成る絶縁性保護膜210がスパッタリングにより形成されている。

【0116】

また、テンプレート10′の裏面の凹部Dはエッチング処理により形成したものであり、符号εはこの凹部Dの形成後におけるn型コンタクト層202の残存膜厚を表している。この様に共振器の直下におけるn型コンタクト層202の厚さεを例えば0.3μm程度と非常に薄くする構造は、共振器内への光閉じ込め作用を良好に得るためのものであり、この構造によって、共振器の出射端面に現れるn型コンタクト層の干渉縞(FFPの乱れ)の発現を極めて効果的に抑制することができる。

【0117】

共振器の真下に位置するn型コンタクト層を全部削ってしまうと電流密度分布に偏りが生じて、共振器に効率よく電流を供給することができなくなるが、本実施例の様に共振器の真下に位置するn型コンタクト層の一部分をある程度(例:ε=0.3μm)残しておけば、共振器直下においても負電極と共振器とのコンタクトが良好に確保できるので、共振器内及び共振器周辺の電流の密度分布が理想的な状態に維持でき、同時に、上記の光の閉じ込め作用をも良好に確保することができる。更に、勿論、テンプレート10′の導入によって、発光出力部204の活性層ではr面成長に基づいてピエゾ電界が略0に改善されるため、本実施例3の半導体レーザ200においては、効果的に閾値電流を抑制することも可能となる。

このため、本実施例3の半導体レーザ200は、極めて良好に安定発振する。

【0118】

また、この様な半導体レーザの構造は、上下方向のFFPが乱れないため、レーザビームの照射位置(照射領域)を正確に制御するのに都合が良く、収斂性の良好なスポットサイズの小さな半導体レーザを実現する上で非常に有用である。

【実施例4】

【0119】

上記の実施例1では、前述の斜めスパッタを実施しているが、スパッタリングによるバッファ層の積層は、マスクを用いてその積層領域を制限しても良い。

また、上記の実施例1では、スパッタリングによってバッファ層を形成しているが、その他にも例えば結晶成長などの工程によってもバッファ層を形成することができる。この場合、バッファ層を積層しない部位にマスクを形成しておくマスキング工程などが必要となってしまうが、しかしながら、マスクを用いて自在に制御される結晶成長によってバッファ層を形成すれば、バッファ層を所望の領域に略一様の厚さで薄くムラなく形成することが可能または容易になる。また、バッファ層をその様に綺麗に成膜することは、非縦方向成長工程で形成される非縦方向成長部の平坦性などの品質をより高く確保する上でより望ましい。

以下の本実施例4では、その様な、結晶成長によってバッファ層を形成する場合について例示する。

【0120】

図8−A〜Dは、バッファ層を結晶成長させる実施例(実施例4)の基板の断面図である。基板21には、サファイア基板を用いており、この基板21の向き(配向)は、実施例1(図1−A)と同じである。また、レジストマスク22には図1−Bのレジストマスク2と同じ材料のものを用いているので、記号α、Δ1、φの各変数値についても、前述の実施例1と一致する。

【0121】

本実施例4の大きな特徴の一つは、図8−Aに示される基板21の主面Σ上にSiO2 より成るマスク23が積層されている点にある。ここで、レジストマスク22は、このマスク23の上に形成されている。この様な方法に従えば、図8−Bに示す様に、ストライプ溝Sを形成する両脇のリッジRgの平頂面に選択成長を促すELOマスク(マスク23)を形成することができる。

【0122】

フォトレジスト24は、スパッタまたは塗布によって、上記の基板上に成膜されたものである。このフォトレジスト24に対して、図示する右上の方向Aから露光すると、マスク23上、及び傾斜面21a上のフォトレジスト24は取り除くことができるが、垂直な内壁面21b上のフォトレジスト24は、そのまま残る。したがって、基板21では、傾斜面21aの大部分だけが、上方に露出することになる。

【0123】

図8−Dは、この傾斜面21aの露出面上に、AlNまたはAlGaNから成る低温バッファ層25を積層したものである。この様な方法によっても、図3−Aと同様の所望の方位にバッファ層25を積層することができる。

また、この方法に従えば、低温バッファ層25を成長核として、その後に成長する半導体結晶でストライプ溝Sが全て埋まった後には、マスク23上では、半導体結晶の横方向の成長が促進されるため、所望の半導体結晶を更に上方に成長させれば、目的の半導体結晶の転位密度が効果的に抑制できる。

【実施例5】

【0124】

図9−A,−B,−Cは何れも、バッファ層を結晶成長させる本実施例5の基板の断面図である。a面を主面とするサファイア基板31には、その主面である上面に、c軸に対して垂直な方向に、ストライプ溝Sの長手方向が取られている。SiO2 から形成されるマスク33は、図示する左上の方向からの斜めスパッタリングによって、主面及びストライプ溝Sの内壁面や底面の一部に積層されたものである。この斜めスパッタリングによって、略垂直な内壁面31a上と断面形状が縦長矩形のストライプ溝Sの底部の一部の双方を除く部分に、マスク33が形成されている。内壁面31aは、上記の配向により、サファイアc面となっている。

【0125】

この様な基板に対して、AlNまたはAlGaNから成る低温バッファ層34を積層し、更に、GaNから成る非縦方向成長部35をファセット成長させた状態を図9−Bに示す。この図9−Bは、非縦方向成長部35を形成するGaN結晶によって、上記のストライプ溝Sに蓋がされて、ストライプ溝Sの底部などにボイドが形成された状態を示している。その後a面成長が促進される結晶成長条件で、GaN結晶の成長を続けることにより、図9−Cに図示する様に、一連かつ広大なa面を結晶成長面とする所望のGaN結晶36を得ることができる。

【実施例6】

【0126】

図10−A,−Bは何れも、バッファ層を結晶成長させる本実施例6の基板の断面図である。本図のサファイア基板41の配向は、垂直上向きがm軸の向きと一致し、水平右向きがc軸の向きと一致している。したがって、ストライプ溝Sの垂直な内壁面41aは、サファイアc面になっている。この様な深い略V字型のストライプ溝Sを有するサファイア基板41の上方から、塗布またはスパッタによって、フォトレジスト42を成膜した(図10−A)。

【0127】

図10−Aに図示する矢印の向きは、このフォトレジスト42に対する露光条件を示している。即ち、内壁面41aの上位の部分だけが露出される様に、右上の方向から露光する。この様な構成によっても、サファイアc面だけを露出させることができるので、この場合にも、図9−B,図9−Cと略同様の結晶成長過程に従って、一連の広大なm面を結晶成長面とする、GaNから成る所望の半導体結晶を得ることができる。

【0128】

〔その他の変形例〕

本発明の実施形態は、上記の形態に限定されるものではなく、その他にも以下に例示される様な変形を行っても良い。この様な変形や応用によっても、本発明の作用に基づいて本発明の効果を得ることができる。

【0129】

(変形例1)

例えば、ボイドを大きく形成すると熱膨張係数差や或いは格子定数差などに伴って、基板と成長層との間に発生する上記の応力が、非縦方向成長部又は下地基板の突起部に対する剪断応力として作用するため、下地基板を綺麗に分離できる場合がある。即ち、この様な剪断作用を利用すると良い場合もある。この様な分離工程や分離作用に付いては、例えば公開特許公報「特開2002−293698:半導体基板の製造方法及び半導体素子」にも関連する類似の例示があり、この様な分離処理を本発明の結晶成長方法に導入することは、極めて有用な技法となる場合がある。

【0130】

(変形例2)

また、上記の実施例2や実施例3では、下地基板(結晶成長基板1)を除去せずに半導体発光素子(100,200)の中に残したが、例えば図4の半導体結晶層6の厚さを例えば400μm以上に積層すれば、その半導体結晶層6は自立した単独のバルク結晶として安定するので、その様なバルク結晶を新たな結晶成長基板として、所望の光半導体素子を製造しても良い。この様な場合には、例えば図4の非縦方向成長部4と下地基板(結晶成長基板1)との間に形成されるボイド5は、後の工程(前述の基板除去工程)で完全に排除することができるので、この様なボイドが光半導体素子の外部量子効率を低下させると言った前述の問題が必然的に解決できる。

【0131】

また、この様に後で下地基板を分離または除去する場合には、製造工程の途中で形成されるボイドは、大きい方が応力緩和作用をもたらすのでより望ましい。また、その様な自立した単独のバルク結晶を製造する場合には、前にも言及した様に、前述の縦方向成長工程の後に、又は、その縦方向成長工程に並行して、目的とする上記の半導体結晶から結晶成長基板を除去する基板除去工程を設けても良い。

逆に、この様な技法を用いなかったり、或いは、多数のストライプ溝の形成に基づいて、結晶成長基板(下地基板)と半導体結晶との間に形成される凹凸構造やボイドによる応力緩和作用が乏しかったりすると、所望の半導体結晶層を10μm程度しか積層できないことがあるので注意を要する。

【0132】

(変形例3)

また、上記の実施例1では、ストライプ溝の深さや形成周期は略一定に統一したが、必ずしもこれらを統一した形式でストライプ溝を形成する必要はない。ここで最も重要なことは、尾根状の頂点ラインを略同一平面(Σ)上に略平行に配列することと、各傾斜面(1a)の傾斜角θ1 をそれぞれ何れも前述の角θ0 に略一致させることである。

また、ストライプ溝の幅は、必ずしも図2の様に、一定である必要はない。このことは、図2のx軸方向についてもy軸方向についても、更にはz軸方向についても言えることである。

【0133】

また、上記の実施例1では、最初の結晶成長基板(下地基板)の主面Σは殆ど全面的に取り除かれているが、下地基板には上方の主面(Σ)を部分的かつ離散的に一部残しても良い。

例えば、シリコン(Si)を下地基板とする場合、GaNはバッファ層が供する結晶成長面には結晶成長するが、下地基板(Si)に対して直接には非常に結晶成長し難いので、下地基板にストライプ溝を形成した後に、元来の上方の主面が部分的かつ離散的に一部残っていても、その幅が数μm程度以内と細ければ各結晶成長面を1つの略平坦な面に特段の不都合なく繋げることは十分に可能であり、特に他の派生問題が生じることはない。この意味で、シリコン(Si)を下地基板とすることは有効であると考えられる。

【0134】

(変形例4)

また、上記の公開特許公報「特開2002−293698:半導体基板の製造方法及び半導体素子」にも記載されている様に、シリコン(Si)を下地基板とする場合には、炭化シリコン(SiC)などから成る周知の反応防止層を形成しておくと、積層工程が増えてしまうものの、結晶品質などに関してより効果的となることがある。

また、シリコン(Si)は比較的柔らかい材料であるので、歪み緩和作用やエッチング容易性などの観点からも有利である。また、上記の実施例1では、ドライエッチングによってストライプ溝を形成しているが、例えば基板材料などの個々の実施条件によってはウェットエッチングを実施しても良い。

【産業上の利用可能性】

【0135】

本発明の結晶成長方法、並びに本発明の結晶成長基板は、LEDや半導体レーザなどの半導体発光素子や半導体受光素子の製造に大いに有用なものである。また、それらの結晶成長方法、並びに本発明の結晶成長基板を用いて製造される光半導体素子も本発明の範疇にある。

【符号の説明】

【0136】

1 : 結晶成長基板(下地基板)

1a: 下地基板(結晶成長基板1)の傾斜面

1b: 下地基板(結晶成長基板1)の側壁面

S : ストライプ溝(傾斜面1aと側壁面1bから構成される)

2 : レジストマスク

3 : バッファ層

4 : 非縦方向成長部

5 : ボイド

6 : 目的の半導体結晶層

10 : テンプレート(実施例1で得られる新たな結晶成長基板)

10′: テンプレート(実施例3)

100: 実施例2のLED

200: 実施例3の半導体レーザ

θ0 : 目的の半導体結晶(半導体結晶層6)のc面とr面とが成す角

θ1 : 下地基板1の主面Σと傾斜面1aとが成す角

φ : レジストマスク2の傾斜角

Σ : 下地基板(結晶成長基板1)の上方の主面(主面)

<σ|: 主面Σの法線ベクトル

<c|: c軸の方向ベクトル

<a|: a軸の方向ベクトル

【技術分野】

【0001】

本発明は、半導体素子及び結晶成長基板に関する。

この結晶成長方法は、半導体発光素子や半導体受光素子(以下、纏めて光半導体素子と言う。)の製造に大いに有用なものである。

【背景技術】

【0002】

活性層の二軸性歪みによって誘起されるピエゾ電界は、半導体発光素子の内部量子効率の低下をもたらすことが一般に知られている。この様なピエゾ電界の緩和や最小化を考慮して提案された光半導体素子としては、例えば下記の特許文献1に掲載されているものが広く知られている。本願図11、図12は、この特許文献1から抜粋したもので、窒化ガリウム系の半導体でのピエゾ電界の角度依存性を示すグラフと、これらの半導体を使用した発光素子の断面図をそれぞれ示している。このグラフの横軸は、c軸の正の向き[0001]からの角度θに対するピエゾ電界の変化を示しており、このグラフから、c面を界面とする活性層においてはピエゾ電界の大きさ(絶対値)が最大となり、r面、a面、またはm面を界面とする活性層においてはピエゾ電界の大きさ(絶対値)は最小(0MV/cm)となることが判る。

【0003】

そして、この特許文献1(第2の実施例)には、「まず、従来技術によりSiC、GaN等の基板51上にn型GaNコンタクト層53、n型AlGaNクラッド層54を{0001}面方向に成長させ、その後、選択成長あるいは選択エッチングにより{2−1−14}面や{01−12}面を形成する。その後再結晶成長により今形成された面方位を持つGaInN/GaNあるいはGaInN/GaInN多重歪量子井戸層55を形成する。」などの記載があり、この様に本特許文献1では、上記の図12を用いて、ピエゾ電界の緩和作用を有する活性層の構成形態とその形成方法を開示している。

【0004】

また、下記の特許文献2には、c面から62°傾斜した斜面((1−101)面)を結晶成長面として用いた結晶成長方法に関する記載がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平11−112029

【特許文献2】特開2003−347585

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記の特許文献2においては、上記の結晶成長面に関して特に62°と言う傾斜角が選択されるので、この従来技術を採用する限り、前述のグラフ(図11)からも判る通り、ピエゾ電界を略零にすることはできず、よって、依然としてピエゾ電界効果を十分には払拭することができない。

また、この特許文献2においては、ピエゾ電界を積極的に略零にしようとする思想は全く見当たらない。

【0007】

また、上記の特許文献1においては、上記の選択成長あるいは選択エッチングを実施する場合、以下の問題を回避することが困難である。

(1)選択成長を行う場合の問題点

図12に図示される様な理想的な波板形状の多重歪量子井戸層55を選択成長によって形成することは、現在の結晶成長に関する技術水準に照らして、必ずしも容易ではない。また、その様な選択成長が仮に可能であったとしても、我々はその方法を少なくとも上記の特許文献1からは、何ら具体的に知ることができない。

【0008】

例えば、図12のn型AlGaNクラッド層54の中にストライプ状の多数のSiO2 マスク等を成膜して上記の選択成長を実施する場合には、そのマスク形成工程の前後で製造中の光半導体素子を大幅に降温したり昇温したりしなければならないので、この場合には各部の熱膨張係数差に基づく応力が素子内に発生する。したがって、この場合、その後に積層される井戸層の結晶品質は劣化する。

【0009】

また、基板材料等の選択により基板等の熱膨張係数をたとえ最適に選んだとしても、上記の様な大幅な昇降温を行っている間に、n型クラッド層の上方露出面における結晶性が、その露出面近傍における活発な原子脱離現象(:特定元素の昇華)などによって劣化する。この様な結晶性の劣化は、キャリアガスなどによるエッチング作用に基づく所が大きい。これらの事情については、例えば次の文献等からも容易に理解することができる。

(1)公開特許公報:特開平11−068159

(2)公開特許公報:特開平9−139543

(3)公開特許公報:特開平8−88432

【0010】

また、更に、上記の様なストライプ状の多数のSiO2 マスクなどは、活性層の近傍に配置、残留させざるを得ないが、このため、素子内部の電流密度に偏り(ムラ)が生じて、内部量子効率が低下してしまうなどの派生問題も回避し難い。また、この様なマスクを活性層の近傍に配置、残留させれば、光半導体素子の光取り出し効率、光取り込み効率、或いは共振効率等が低下するなどの不都合も生じる。

【0011】

(2)選択エッチングを行う場合の問題点

選択エッチングを行う場合にも、マスク形成工程が不可欠となるため、上記の大幅な昇降温の問題は回避し難い。また、選択エッチングを行えば、その侵食面には、エッチング処理に伴うダメージ(表面荒れ)が顕著に残るので、その上に直接多重歪量子井戸層を良好に結晶成長させることは困難となる。

【0012】

また、特にレーザの共振器を形成する際には、上記の(1)、(2)の何れの場合でも、光導波路上に波板形状の活性層を形成すると、その斜面で共振光が散乱され易いなどの派生問題が生じる。

【0013】

この様に、目的の光半導体素子において所望の発光効率を確保することは、上記の特許文献1から具体的に知り得る技術範囲内では非常に困難である。また、実際に上記の特許文献1(図12)の様な具体的な素子構造によって、実際に半導体発光素子の発光効率が従来よりも向上したと言う報告は、今のところ光半導体素子関連分野において全く見当たらない。これは、それらの半導体発光素子の素子構造や製造工程を具現化するに当たって、実際には上記の様な問題が回避し難いためだと考えられる。

【0014】

以上の様に、活性層などの半導体層の内部に生じるピエゾ電界を効果的に緩和したり、或いはそれらの技術に基づいて、実際に特段の派生問題を生むことなく光半導体素子の動作効率を改善したりすることは、現在の一般的な技術水準に照らして、必ずしも容易とは言えない。

【0015】

本発明は、上記の課題を解決するために成されたものであり、その目的は、広大なr面を有する III族窒化物系化合物半導体から成る半導体結晶の製造方法を開示することである。

また、本発明の更なる目的は、特段の派生問題を生むことなくピエゾ電界の悪影響を効果的に緩和若しくは最小化することができる光半導体素子の構造や製造方法を開示することである。

ただし、上記の個々の目的は、本発明の個々の手段の内の少なくとも何れか1つによって、個々に達成されれば十分であって、本願の個々の発明(下記の個々の手段)は、上記の全ての課題を同時に解決する具体的実施形態が存在することを必ずしも保証するものではない。

【課題を解決するための手段】

【0016】

上記の課題を解決するためには、以下の手段が有効である。

即ち、本発明の第1の手段は、 III族窒化物系化合物半導体から成る半導体層を有する半導体素子であって、サファイア基板と、サファイア基板が有する平面状の主面において形成され、主面に平行ではない平面で構成された二つの側壁面を有する複数の平行なストライプ溝と、複数のストライプ溝において、 III族窒化物系化合物半導体を成長させる側壁面を主内壁面とし、この主内壁面に形成されたバッファ層と、複数のストライプ溝の各主内壁面に対して垂直に、バッファ層の上にc軸方向に成長し、主面の面内方向において合体し、サファイア基板の主面を覆う、 III族窒化物系化合物半導体から成る第1半導体層と、第1半導体層のサファイア基板の主面に平行な面を結晶成長核として、主面に対して垂直な方向に成長した、 III族窒化物系化合物半導体から成る第2半導体層と、第2半導体層の上部に形成された活性層とを有し、ストライプ溝の主内壁面とサファイア基板の主面とが成す第1の角θ1 を、 III族窒化物系化合物半導体のc軸と、 III族窒化物系化合物半導体のピエゾ電界が零となる結晶方位であるr軸、a軸、又は、m軸の方位との成す第2の角θ0 に対して、θ0 −10°≦θ1 ≦θ0 +10°を満たす角度とし、第1半導体層、第2半導体層及び活性層における、サファイア基板の主面に垂直な方向の結晶軸は、 III族窒化物系化合物半導体のr軸、a軸、又は、m軸に対して、±10°以下となる結晶軸であることを特徴とする半導体素子である。

【0017】

また、本発明の第2の手段は、 III族窒化物系化合物半導体から成る半導体層を有する III族窒化物系化合物半導体基板であって、サファイア基板と、サファイア基板が有する平面状の主面において形成され、主面に平行ではない平面で構成された二つの側壁面を有する複数の平行なストライプ溝と、複数のストライプ溝において、 III族窒化物系化合物半導体を成長させる側壁面を主内壁面とし、この主内壁面に形成されたバッファ層と、複数のストライプ溝の各主内壁面に対して垂直に、バッファ層の上にc軸方向に成長し、主面の面内方向において合体し、サファイア基板の主面を覆う、 III族窒化物系化合物半導体から成る第1半導体層と、第1半導体層のサファイア基板の主面に平行な面を結晶成長核として、主面に対して垂直な方向に成長した、 III族窒化物系化合物半導体から成る第2半導体層とを有し、ストライプ溝の主内壁面とサファイア基板の主面とが成す第1の角θ1 は、 III族窒化物系化合物半導体のc軸と、 III族窒化物系化合物半導体のピエゾ電界が零となる結晶方位であるr軸、a軸、又は、m軸の方位との成す第2の角θ0 に対して、θ0 −10°≦θ1 ≦θ0 +10°を満たす角度であり、第1半導体層及び第2半導体層における、サファイア基板の主面に垂直な方向の結晶軸は、 III族窒化物系化合物半導体のr軸、a軸、又は、m軸に対して、±10°以下となる結晶軸であることを特徴とする III族窒化物系化合物半導体基板である。

【0018】

また、本発明の第3の手段は、第1の手段において、ストライプ溝の二つの側壁面のうちバッファ層が形成されていない側壁面は、 III族窒化物系化合物半導体のサファイア基板からの成長を阻害するマスクが形成されておらずサファイア基板が露出していることを特徴とする。

【0019】

また、本発明の第4の手段は、第2の手段において、ストライプ溝の二つの側壁面のうちバッファ層が形成されていない側壁面は、 III族窒化物系化合物半導体のサファイア基板からの成長を阻害するマスクが形成されておらずサファイア基板が露出していることを特徴とする。

【0020】

また、本発明の第5の手段は、第1、第3の手段において、サファイア基板の主内壁面の法線ベクトルは、サファイア基板におけるc軸又はa軸であることを特徴とする。

【0021】

また、本発明の第6の手段は、第2、第4の手段において、サファイア基板の主内壁面の法線ベクトルは、サファイア基板におけるc軸又はa軸であることを特徴とする。

【0022】

また、本発明の第7の手段は、第1、第3、又は、第5の手段において、ピエゾ電界が零となる結晶方位はr軸の方位であり、第2の角θ0 は、43.2°であることを特徴とする。

【0023】

また、本発明の第8の手段は、第2、第4、又は、第6の手段において、ピエゾ電界が零となる結晶方位はr軸の方位であり、第2の角θ0 は、43.2°であることを特徴とする。

【0024】

また、本発明の第9の手段は、第1、第3、第5、又は、第7の手段において、サファイア基板の主内壁面の法線ベクトルは、サファイア基板におけるc軸であり、ピエゾ電界が零となる結晶方位はa軸又はm軸であり、第2の角θ0 は、90°であることを特徴とする。

【0025】

また、本発明の第10の手段は、第2、第4、第6、又は、第8の手段において、サファイア基板の主内壁面の法線ベクトルは、サファイア基板におけるc軸であり、ピエゾ電零となる結晶方位はa軸又はm軸であり、第2の角θ0 は、90°であることを特徴とする。

【0026】

ただし、より望ましくは、「θ0 −3°≦θ1 ≦θ0 +3°」を満たす様に設定すると良い。また、更には、「θ0 −1°<θ1 <θ0 +1°」を満たす様に設定することがより望ましい。

【0027】

なお、上記のc軸の向きは、それをミラー指数を用いて書けば[0001]と表される向きである。各結晶面のミラー指数を以下に例示する。

c面:(0001)

a面:(11−20)

m面:(10−10)

r面:(10−12)

ただし、これらはあくまでも例示であり、所望の半導体結晶の結晶構造が六方晶系であるので、例えばそれらのa面やm面については、他にも当然ながら対称なその他の5つの向きの面がある。

【0028】

なお、上記の本成長工程においては、主面に対して垂直に半導体結晶を縦方向成長させても良いし、或いは主面上に形成されたマスク上方において、主面に対して略平行に半導体結晶を横方向成長させても良い。また、その様な半導体結晶の横方向成長後に、更に縦方向成長を実施しても良い。これらの成長方向に係わる結晶成長の形態や、各形態の組み合わせは任意で良い。

【0029】

また、上記の主面は、結晶成長面に広い1平面を用いる通常の結晶成長における主面と言われる部位(その広い1平面)に相当するが、しかし、本発明では、上記の様に溝形成工程を導入してこの主面を加工し、そのストライプ溝内にバッファ層を積層するので、上記の主面は、バッファ層を介して所望の結晶成長が開始される面とは一致しない。

【0030】

また、ストライプ溝の断面形状を矩形とする場合、上記の主面に対して垂直な側壁面(:ストライプ溝の内壁面)がストライプ溝内で互いに向かい合うことになるが、この様な場合、ストライプ溝内の一方の内壁面だけにバッファ層を形成し、かつ、そのバッファ層が積層される全ての内壁面の法線の向きを1つの向きに揃える様に制限しても良いし、或いはまた、向かい合う双方何れの面にもバッファ層を形成する様にしても良い。

【0031】

また、ストライプ溝が埋まる際には、c面とは異なる局所的な個々の結晶成長面が相互に繋がって略一連の結晶成長面が形成されるが、この時、個々のストライプ溝の中にボイド(:結晶が成長せずにできる空洞部)が形成されて残留していても特段の支障を来すことはない。

【0032】

また、本発明において、ピエゾ電界が零となる上記の結晶方位としてr軸の方位を選択し、六方晶系の結晶構造を有する結晶成長基板を用い、主面の法線ベクトル<σ|の向きを、結晶成長基板のc軸の正の向きからm軸の正の向きに向って第1の角θ1 だけ回転させ、ストライプ溝の長手方向をa軸の方向に取っても良い。

【0033】

また、本発明において、ピエゾ電界が零となる上記の結晶方位としてr軸の方位を選択し、六方晶系の結晶構造を有する結晶成長基板を用い、主面の法線ベクトル<σ|の向きを、結晶成長基板のa軸の正の向きからm軸の正の向きに向って第1の角θ1 だけ回転させ、ストライプ溝の長手方向をc軸の方向に取っても良い。

【0034】

また、本発明において、ピエゾ電界が零となる上記の結晶方位としてr軸の方位を選択し、六方晶系の結晶構造を有する結晶成長基板を用い、主面の法線ベクトル<σ|の向きを、結晶成長基板のa軸の正の向きからc軸の正の向きに向って第1の角θ1 だけ回転させ、ストライプ溝の長手方向をm軸の方向に取っても良い。

【0035】

また、本発明において、ピエゾ電界が零となる上記の結晶方位をa軸又はm軸の方位にしても良い。この時、第2の角θ0 は90°となる。したがって、前述の本発明の第1の手段又は第2の手段に基づき、第1の角θ1 は、80°以上100°以下の範囲であればピエゾ電界を抑制する効果が大きく得られ、かつ、この第1の角θ1 は、直角に近いほどより望ましい。また、この時用いる結晶成長基板は、a面を主面とするa面基板か、又はm面を主面とするm面基板を用いることが望ましい。また、上記の主面上に形成するストライプ溝の長手方向は、結晶成長基板のc軸の方向に対して略垂直な方向に取ることが望ましい。また、ストライプ溝の長手方向は、m軸又はa軸の方向とすることが望ましい。

【0036】

また、ストライプ溝の内側の側壁(内壁面)を主面に略垂直な側壁面から形成する場合、所望の半導体結晶を横方向成長させる場合には、ストライプ溝の両側の内側壁にバッファ層を形成してから横方向成長させて溝の中央部で合体させても良い。この様な場合には、ストライプ溝の内側で対峙する上記の2面の側壁(内壁面)の双方にバッファ層を積層しておくことが望ましい。

【0037】

なお、以上の本発明の第3乃至第10の各手段は、それぞれ何れも、本発明の第1の手段及び第2の手段を実施するにあたっての、より望ましい若しくはより具体的な個別の実施形態を例示するものである。したがって、これらの例示は、本発明の第1の手段及び第2の手段を実施するにあたって、必ずしも何れか1つの手段を選択して採用しなければならないことを意味するものではない。即ち、上記の本発明の第1の手段又は第2の手段により、本発明の第1の手段又は第2の手段の作用・効果を含め、少なくとも上記の何れか1つの作用・効果を得ることができる。

【0038】

なお、本発明において、主面と略同じ向きにr面を形成してその結晶成長面を更に成長させる場合には、第1半導体層の成長工程(非縦方向成長工程)では、所望の半導体結晶は少なくともファセット成長する。

また、本発明において、主面と略同じ向きにa面又はm面を形成してその結晶成長面を更に成長させる場合には、第1半導体層は、所望の半導体結晶は少なくとも横方向成長する。

【0039】

また、本発明において、ストライプ溝を構成する主内壁面以外の内壁面上に半導体結晶の選択成長を促すマスクを結晶成長基板上に形成しても良い。

【0040】

また、本発明において、隣接する他のストライプ溝との間に上記の主面の平坦部が残される様に各ストライプ溝を形成し、この平坦部にもマスクを形成し、更に、ストライプ溝上に成長した半導体結晶を核として、上記の平坦部に半導体結晶を横方向成長させてもよい。なお、この横方向成長のあとに、所望の半導体結晶を縦方向成長をさせても良い。

【0041】

また、本発明において、上記の複数のストライプ溝を、その幅方向に間隔を置かずに隙間なく、主面上に連続して形成してもよい。この時、上記の主面を構成していた平坦面は全面的に消滅する。

【0042】

また、本発明において、ストライプ溝を構成する主内壁面以外の内壁面を上記の主面に対して垂直に形成してもよい。

【0043】

また、本発明において、第1半導体層の結晶成長温度を900℃以上1150℃以下にしても良い。

【0044】

以上の本発明の手段により、前記の課題を効果的、或いは合理的に解決することができる。

【発明の効果】

【0045】

以上の本発明の手段によって得られる効果は以下の通りである。

即ち、本発明によれば、略一連の広大な1つのr面、a面、m面、若しくはこれらの何れか一つの面に概ね近似できる面を、略一連の広大な層界面として有する半導体結晶とすることができる。

【0046】

バッファ層が供する結晶成長面上では、通常、目的の半導体結晶はc面成長するので、本発明によれば、ファセット成長又は横方向成長によって、第1半導体層の主面をr面、a面、m面、又はこれらの何れか一つの結晶面から10°以内のオフ角を有する面とすることができる。

【0047】

また、θ0 ≒θ1 なる関係に基づいて、各部で成長する個々の結晶成長面は、何れも結晶成長基板が最初に有していた上記の主面と略同方向を向きつつ結晶成長する。以下、これと同じ向きの結晶成長面を総称してΛ面と言うことがある。このΛ面は、r面、a面、又はm面の何れかと一致していることがより望ましいが、それらと若干(10°以内)のオフ角を持つ面であっても特段差し支えない。

【0048】

これにより、上記の第1半導体層の成長完了時(非縦方向成長工程の完了時)には、各部の個々のΛ面がそれぞれ互いに略一連に繋がって、広大で略平坦な1つの面を形成する。

また、各部の個々のΛ面の間に若干の段差などの凹凸部が生じても、その後の本発明の第2半導体層の成長工程において、Λ面に垂直な方向に進む各部の縦方向成長によって、それらの凹凸部は良好に是正されて、十分に平坦化される。

【0049】

ただし、上記の角度θ1 は、極力上記の角θ0 に近いことが望ましく、上記の角θ0 に一致する時に最良の結果をもたらす。例えば、目的の半導体結晶が III族窒化物系化合物結晶の場合、一連の広大な1つのr面を得るためには、θ1 =43.2°(=θ0 )とすると最良の結果が得られる。

【0050】

また、この広大な層界面(上記のΛ面)は、ファセット成長又は横方向成長に基づいて形成される面であるので、その転位密度は必然的に低く抑制される。

更に、目的の半導体結晶と結晶成長基板との間の接合面は、例えば矩形波や三角波や鋸歯形状などの波板状に形成されるので、格子定数差や熱膨張係数差などに伴って発生し得る目的の半導体結晶と結晶成長基板との間の応力を効果的に緩和する効果をも同時に得ることができる。

【0051】

また、上記の応力緩和作用は、ストライプ溝の中にボイドが大きく形成されていた方がより効果的に発現する。ただし、ストライプ溝中のボイドの形成は必ずしも必要なものではなく、また、外部量子効率の観点から言えば、ボイドは極力小さい又は極力少ない方が良い場合も多い。したがって、上記のストライプ溝中のボイドの有無やその大小などに付いては、これらの応力緩和作用や外部量子効率などの諸条件や、或いは所望の光半導体素子の性能などまでをも総合的に考慮して、個々に具体的に設計することが望ましい。

【0052】

以上の様な各作用をもたらす本発明によれば、従来より問題であった前述の温度の昇降過程に生じる原子脱離の発生が回避でき、或いは半導体結晶の界面の転位密度が低減するなどするため、上記の目的の半導体結晶における結晶品質は、十分良好に確保することができる。

【0053】

また、本発明によれば、特に広大なr面を形成する場合に、上記のストライプ溝を、上記の主面上に比較的容易または綺麗に形成することができるか、上記のバッファ層を容易、綺麗又は確実に積層することができるか、或いは、周知のファセット成長の作用に基づいて目的の半導体結晶の転位密度を比較的低く抑制することができる。

【0054】

ただし、ストライプ溝を形成する向きを決定づける基準としては、上記の様な作用・効果の観点以外にも、半導体ウェハを所望の光半導体素子などに分割する時の分割の容易性の観点なども有り得る。したがって、上記のストライプ溝を形成する向きは、例えば所望の光半導体素子の平面形状などにも留意して、より総合的に判断することがより望ましい。

【0055】

また、本発明によれば、広大なa面又はm面を形成することができる。

従来のa面又はm面上に活性層を形成した半導体発光素子としては、例えば「特開2000−21789」の図18に記載されているものなどが公知である。この光素子を製造する場合、少なくとも活性層とその周辺の半導体層は、「ラテラル方向のみに成長する成長条件」で結晶成長させなければならない。しかしながら、この様に完全に横方向の結晶成長の条件設定は、実際には極めて困難である。また、獲得し得る活性層の面積が十分には大きくなり難い点や、獲得された半導体ウェハの加工容易性などにも大きな問題が残っているので、この様な光素子を実際に量産することは、現在の一般的な工業的技術水準に照らして非常に困難であると言わざるを得ない。

【0056】

しかしながら、本発明によれば、広大なa面又はm面を形成することができ、かつ、その後の所望の半導体層の結晶成長は、従来の「ラテラル方向のみに成長する成長条件」で実施する必要もない。したがって、本発明によれば、所望の高い発光効率と大きな光出力を有する発光素子や受光素子を量産することができる。

【0057】

この時、上方に何れの結晶面が現れるかは、結晶成長基板の向きに依存する。即ち、a面を主面とする基板を用いれば、目的の半導体結晶についても広大なa面を得ることができ、m面基板を用いれば、目的の半導体結晶についても広大なm面を得ることができる。ただし、この時、主面上に形成するストライプ溝の長手方向は、結晶成長基板のc軸の方向に対して略垂直な方向に取ると良い。より望ましくは、m軸方向またはa軸方向に取ると更に良い。

【0058】

また、本発明によれば、選択成長を促すマスクによって、バッファ層の向きを1通りに統一することが可能又は容易となる。例えば、バッファ層を結晶成長によって形成する場合には、バッファ層を形成すべきある一定の向きの面だけを残しておき、その他の面をマスクすれば良い。

また、これらのマスクは、縦方向成長工程におけるELOマスクとしても作用し得る。したがって、この場合には、上記の本発明の縦方向成長工程で得られる半導体結晶の転位密度を効果的に低減することも可能となる。

【0059】

また、本発明によれば、上記の平坦部に形成されるマスクがELOマスクとして作用する。即ち、このマスクの上では、所望の半導体結晶が横方向に成長するため、その横方向成長部分には転位が伝播しない。このため、転位密度が低い半導体結晶を得ることができる。

【0060】

また、本発明によれば、上記の主面上に平坦部が残らないので、例えば斜めスパッタや或いは斜め露光などの様な単純で簡単な準備工程だけで、バッファ層または基板が供する、所定の向きの所望の結晶成長面だけを形成または露出させることができる場合がある。(例えば、図3−Aや、図10−Bなどの例は、この様な場合を典型的かつ具体的に例示するものである。)

【0061】

また、本発明によれば、方向性を有するドライエッチングなどによって、ストライプ溝の内壁面を容易に形成することができる。

また、本発明によれば、ストライプ溝の主内壁面を含むストライプ溝の各内壁面を良好に形成することができる。

【0062】

なお、ストライプ溝の断面形状を矩形とする場合、上記の主面に対して垂直な側壁面(:ストライプ溝の内壁面)がストライプ溝内で互いに向かい合うことになるが、この様な場合、ストライプ溝内の一方の内壁面だけにバッファ層を形成し、かつ、そのバッファ層が積層される全ての内壁面の法線の向きを1つの向きに揃える様に制限しても良いし、或いはまた、向かい合う双方何れの面にもバッファ層を形成する様にしても良い。向かい合う双方何れの面にもバッファ層を形成すれば、双方から成長してきた半導体結晶をストライプ溝の略中央で合体させることができる。そして、この様な場合にも、本発明を具体的に実施することができる。

【0063】

また、本発明によれば、ファセット成長を良好に促す結晶成長条件を設定することができるので、上記の第1半導体層の成長においてより確実に上記のΛ面のファセット成長を継続することができる。したがって、本発明によれば、上記の一連化や平坦化が比較的容易かつ良好に達成できる。このファセット成長の結晶成長温度の好適値は、キャリアガスや結晶材料ガスの流量や分圧や或いは結晶成長速度等にも依存するものの、通常、より望ましいこの結晶成長温度は、950℃〜1100℃の範囲内にある。

【0064】

また、本発明によれば、上記の従来技術の課題においてみられた様な、従来のエッチング工程や或いは従来のマスク形成工程などを介在させるべき必要性を完全に排除することができるので、これらの介在工程に伴う上記の昇降温に起因する問題も必然的に払拭することができる。また、各ストライプ溝を構成する上記の各内壁面上には、それぞれバッファ層が成膜されるので、これにより、内壁面上にダメージ層が形成されていたとしてもその悪影響は効果的に緩和、抑制することができる。

【0065】

また、素子構造として必要とされる例えばn型層などの各半導体結晶層のΛ面の結晶成長は、活性層を形成するよりも遥かに前の段階より開始することができる。例えば、n型コンタクト層の結晶成長を実施するなどの早期の段階から開始することができる。更に、Λ面の結晶成長によって、光半導体素子の活性層を略一連の略平坦な板状(平面状)に形成することが可能または容易となる。

【0066】

したがって、本発明によれば、非常に良好な結晶成長を促すこれらの作用によって、Λ面を界面とする極めて高品質の活性層を形成することが可能または容易となる。したがって、本発明によれば、目的の光半導体素子において、特段の派生問題を生むことなくピエゾ電界の悪影響を効果的に緩和若しくは最小化することができ、よって、その光半導体素子の動作効率を大幅に向上させることができる。

【0067】

このため、本発明のIII 族窒化物系化合物半導体基板によれば、半導体素子を、容易に製造することができる。言い換えれば、本発明のIII 族窒化物系化合物半導体基板結晶成長基板は、工業的に極めて有用となり得るので、上記の本発明の結晶成長基板は単独でも一般市場において高い商品価値を持ち得る。

【0068】

なお、この様な結晶成長基板においては、上記のΛ面上に、そのΛ面に対して平行な界面を有する平板状の半導体結晶層を更に積層しておくことがより望ましい。即ち、本発明によれば、結晶成長面の平坦性が向上するなどして、結晶成長面の品質が向上する。

【0069】

また、更には、この様な半導体結晶層を十分に厚く積層することによって、下地基板(最初の結晶成長基板)を除去することも可能又は容易となる。また、下地基板が除去されれば、その半導体結晶層を、自立したバルク結晶から成る結晶成長基板として用いることができる。異種基板を有しない自立したバルク結晶から成る結晶成長基板は、熱膨張係数差や格子定数差などに起因する応力の問題から解放される点で、非常に有利である。

【図面の簡単な説明】

【0070】

【図1−A】主面Σを主面とする実施例1の結晶成長基板1(下地基板)の側面図

【図1−B】主面Σにレジストマスク2が形成された結晶成長基板1の側面図

【図1−C】レジストマスク2が形状加工された結晶成長基板1の側面図

【図2】ドライエッチングにより主面Σが形状加工された結晶成長基板1の斜視図

【図3−A】実施例1のバッファ層積層工程を示す結晶成長基板1の部分的断面図

【図3−B】非縦方向成長工程(前半)を示す結晶成長基板1の部分的断面図

【図3−C】非縦方向成長工程(後半)を示す結晶成長基板1の部分的断面図

【図4】目的の半導体結晶層6を有するテンプレート10の断面図

【図5】テンプレート10を有するLED100の断面図(実施例2)

【図6】テンプレート10′を有する半導体レーザ200の断面図(実施例3)

【図7】テンプレート10′の部分的な断面図(実施例3)

【図8−A】バッファ層を結晶成長させる実施例(実施例4)の基板の断面図

【図8−B】バッファ層を結晶成長させる実施例(実施例4)の基板の断面図

【図8−C】バッファ層を結晶成長させる実施例(実施例4)の基板の断面図

【図8−D】バッファ層を結晶成長させる実施例(実施例4)の基板の断面図

【図9−A】バッファ層を結晶成長させる実施例(実施例5)の基板の断面図

【図9−B】バッファ層を結晶成長させる実施例(実施例5)の基板の断面図

【図9−C】バッファ層を結晶成長させる実施例(実施例5)の基板の断面図

【図10−A】バッファ層を結晶成長させる実施例(実施例6)の基板の断面図

【図10−B】バッファ層を結晶成長させる実施例(実施例6)の基板の断面図

【図11】窒化ガリウム系の半導体でのピエゾ電界の角度依存性を示すグラフ

【図12】活性層のピエゾ電界の緩和を試みた従来の光半導体素子の断面図

【発明を実施するための形態】

【0071】

上記の下地基板(または最初の結晶成長基板)としては、例えば、サファイア、シリコン(Si)、炭化珪素(SiC)、酸化亜鉛(ZnO)、2元、3元、又は4元のAlx Iny Ga1-x-y N(0≦x≦1,0≦y≦1,0≦x+y≦1)、或いはその他の公知の結晶成長用の基板材料を使用することができる。即ち、これらの基板は、立方晶系の結晶でも良く、必ずしも六方晶系の結晶に限定されるものではない。

また、例えば、熱膨張係数差や格子定数差などに起因して半導体層に加わる応力を排除するために、所望の半導体結晶に対するそれらの差値が小さい基板材料等を用いると良い場合もある。

【0072】

また、本発明は、2元、3元、或いは4元の「Al1-x-y Gay Inx N;0≦x≦1,0≦y≦1,0≦1−x−y≦1」から成る、より一般の III族窒化物系化合物半導体を目的の半導体結晶とする場合にも有効である。更に、前記の目的の半導体結晶は、2元、3元、又は4元の「Al1-x-y Gay Inx N;0≦x≦1,0≦y≦1,0≦1−x−y≦1」中の III族元素(Al,In,Ga)の内の一部をボロン(B)やタリウム(Tl)等で置換したり、或いは、上記の組成式中の窒素(N)の一部をリン(P)、砒素(As)、アンチモン(Sb)、ビスマス(Bi)等で置換したりした半導体等を上記の目的の半導体結晶としても良い。本発明の作用・効果は、これらの若干の変形や置換などに対しても一定の普遍性を示すものである。

【0073】

また、前記の目的の半導体結晶は、n型またはp型の周知の適当な不純物が添加されたものであっても良い。p型の不純物としては、例えば、マグネシウム(Mg)や、或いはカルシウム(Ca)等を添加することができる。また、n型の不純物としては、例えば、シリコン(Si)や、硫黄(S)、セレン(Se)、テルル(Te)、或いはゲルマニウム(Ge)などを添加することができる。また、これらの不純物は、同時に2元素以上を添加しても良いし、同時に両型(p型とn型)を添加しても良い。

【0074】

また、縦方向成長工程の後に、又は、その縦方向成長工程に並行して、目的とする上記の半導体結晶から結晶成長基板を除去する基板除去工程を設けても良い。この様な基板除去工程の導入によれば、下地基板(最初の結晶成長基板)が除去されるため、目的の半導体結晶を厚く結晶成長させた場合には、自立した半導体バルク結晶を得ることも十分に可能となる。この様な自立した半導体バルク結晶は、勿論光半導体素子の結晶成長基板などに有用となる。

【0075】

また、光半導体素子を製造する場合には、結晶成長基板の格子定数、熱膨張係数、屈折率、或いは透光性などが厳しく問われる場合が多いが、上記の最初の結晶成長基板(以下、下地基板と言うことがある。)を除去できれば、その様な制約から必然的に解放されるので、下地基板の材料選択の任意性も向上する。

【0076】

また、ストライプ溝の形状や大小などによっては、ストライプ溝の底部などにボイドができ易くなる。そして、この様なボイドは、光半導体素子の光取り出し効率や光取り込み効率などを低下させることがあるが、たとえその様な場合であっても、上記の様に下地基板を除去すれば、それらの不具合も同時に回避することができる。

【0077】

なお、自立した半導体バルク結晶に対するハンドリングに伴うその結晶の破損の確率を低減して、十分な歩留りを確保するために、上記の基板除去工程を実施する場合には、目的の半導体結晶(:自立した半導体バルク結晶)は、少なくとも400μm以上に積層することが望ましい。また、バッファ層や非縦方向成長部は相対的に十分に小さいので、これらの部位を残留させて上記の下地基板のみを除去する様にしても、勿論、略同等の作用・効果を得ることができる。或いは、上記の半導体結晶層(:自立した半導体バルク結晶)の下方の一部をも除去してしまっても、特段の支障を来すものではない。

【0078】

また、上記の基板除去工程は、上記の縦方向成長工程と並行して実施することも可能である。その様な並行処理を可能とする製造方法や製造装置としては、例えば「特開2003−7619: III族窒化物系化合物半導体の製造方法及び製造装置」に開示されている技法などが公知である。この公知文献には、結晶成長基板の表裏両面から結晶成長やエッチング等を同時に実施することができる装置等が開示されているが、例えばこの様な技法を利用すれば、目的の半導体結晶を厚く成長させる際に、目的の半導体結晶に作用する応力を極力排除することができる。

【0079】

また、目的とする半導体結晶の組成を結晶成長基板の組成に略一致させると良い場合がある。これにより、目的の半導体結晶と結晶成長基板との熱膨張係数差を小さくすることができるので、上記の様な両面同時処理を可能にする様な特殊な装置を用意できない場合にも、応力の発生を防いで目的の半導体結晶を十分に厚く形成することが可能又は容易となる。

【0080】

また、上記のストライプ溝の深さは、1μm以上30μm以下にすることが望ましい。この範囲は、1μm以上15μm以下とすると更に望ましい。この様な寸法設定によれば、各ストライプ溝内で結晶成長するΛ面が良好に繋がって、一連の略平坦で広大なΛ面を良好に形成することができる。

また、この深さを浅くしすぎるとストライプ溝が細くなり過ぎて、所望の適当な形状にこのストライプ溝を形成することが、現在の周知の基板加工技術の加工精度に照らして困難となる。或いは、各ストライプ溝内で各々綺麗なΛ面が形成される前に、それらの個々のΛ面が相互に不規則に繋がってしまう恐れが生じる。

【0081】

また、この深さを深くし過ぎると、各ストライプ溝内で結晶成長するΛ面が、それぞれ互いに一連に良好に繋がるまでに掛かる時間(即ち、本発明の非縦方向成長工程に掛かる時間)が長くなり過ぎて、必ずしも高い生産性を確保できるとは言えない。また、この深さを深くし過ぎると、局所的な成長速度のムラに伴って発生し得る、上記の個々のΛ面間の段差が大きくなってしまう恐れも十分には払拭できない。また、この深さを深くし過ぎると、特にストライプ溝が急峻な側壁面を有する場合、深い部位には材料ガスが到達し難くなるので、バッファ層の積層状況などによってはストライプ溝の底部などにボイドが形成され易くなるので、前にも言及した様に、場合によっては必ずしも望ましい結晶成長形態になるとは言い切れない。

これらの観点より、各ストライプ溝の深さは、約1μm以上15μm以下がより望ましい。更に望ましくは、ストライプ溝の深さは約2μm以上5μm以下が良い。

【0082】

また、特に広大なr面を獲得したい場合、上記の主面に対して略垂直な側壁面を用いて、上記のストライプ溝の1つの内壁面を形成すると良い場合がある。この設定によれば、主面に略垂直な上記の側壁面をドライエッチングなどによって容易に形成することができると同時に、特に広大なr面を得たい場合には、この構成によって、ストライプ溝が上記の非縦方向成長工程で、成長した半導体結晶によって略過不足なく埋まる様な結晶成長条件が成立し易くなる場合も少なくない。このため、結晶成長基板と目的の半導体結晶との間には、非常にボイドの少ない界面を形成することも可能又は容易となる。したがって、上記の結晶成長基板をそのまま光半導体素子の基板とする場合には、光取り出し効率または光取り込み効率の高い素子を製造できる場合もある。

【0083】

以下、本発明を具体的な実施例に基づいて説明する。

ただし、本発明の実施形態は、以下に示す個々の実施例に限定されるものではない。

【実施例1】

【0084】

(結晶成長基板の構造とその製造工程)

図1−Aに、主面Σを主面とする本実施例1の結晶成長基板1(下地基板)の側面図を示す。この結晶成長基板1はサファイアから形成されている。図中の単位ベクトル<σ|は、結晶成長基板1の上方の略平坦な主面Σの法線ベクトルであり、以下、この法線ベクトル<σ|の向きを3次元直交座標系のz軸の正の向きとする。

【0085】

また、本明細書では、結晶の各面は4つの軸を使った六方晶系におけるミラー指数(hkil)を用いて、上記の3次元直交座標系(x,y,z)と区別する。したがって、例えば上記の法線ベクトル<σ|は、この3次元直交座標を用いて、次式(1)の様に書くことができる。

(法線ベクトル<σ|の直交座標表示)

<σ|=(0,0,1) …(1)

【0086】

図1−Aの結晶成長基板1は、次式(2)を満たす板状の直方体として成形されている。ただし、ここでは、図1−Aの結晶成長基板1を形成するサファイア結晶のc軸の正の向きを向く単位ベクトルを以下<c|で表す。また、このサファイア結晶の1つのa軸の正の向きを向く単位ベクトルを以下<a|で表す。なお、下記の角θ0 は、六方晶系のGaN単結晶(即ち、後述の目的の半導体結晶層6)においてc軸とr軸とが成す角度であり、常温では43.2°である。

【0087】

(単位ベクトル<c|,<a|の直交座標表示)

<c|=(0,sinθ0 ′,cosθ0 ′),

<a|=(0,cosθ0 ′,−sinθ0 ′),

θ0 ′≒θ0 …(2)

ここで、上記の角θ0 ′はこの角θ0 の近傍値でよく、例えば45°程度でも良い。以下、本実施例では、この式(2)においてθ0 ′=θ0 =43.2°が満たされているものとする。

【0088】

また、ここで注意すべき点は、上記の主面Σは、サファイア基板以外の場合でも、一般にはr面とはならないが、それにも関わらず、最終的にはこの主面Σに対して略平行な広大なr面を有する半導体結晶層(即ち、後述の目的の半導体結晶層6)が得られる点である。そして、この理想的とも言える帰結は、後述の傾斜角θ1 の角度設定に依る所が大きい。そして、これらの点が本発明の最も大きな特徴の一つとなっている。

【0089】

図1−Bに、塗布及びベーキングによって上記の主面Σにレジストマスク2が形成された結晶成長基板1の側面図を示す。また、図1−Cには、レジストマスク2が形状加工された結晶成長基板1の側面図を示す。レジストマスク2に対する露光方法としては、例えば次の何れかの方法を採用しても良い。これらの露光方法については周知の適当な任意の方法を用いることができる。

(1)ストライプ形状の濃淡パターンを有するネガを作成して用いる方法

(2)目的の形状に適合する様に焦点制御されたレーザ光を走査制御して照射する方法

【0090】

また、このレジストマスク2の厚さΔ1は、ドライエッチング実行時のレジストマスク2の深さ方向への侵食進行速度Rと、結晶成長基板1の侵食進行速度rと、フォトリソグラフィーなどによってレジストマスク2に形成すべき傾斜面2aの傾斜角φと、その後のドライエッチングによって結晶成長基板1に形成すべき傾斜面1aの傾斜角θ1 (図2)などに基づいて決定することができる。これらの変数R,r,φ,θ1 ,Δ1などが満たすべき関係式に付いては既に公知である。この具体的な関係については、例えば、特開2001−160657に開示されている関係式などを参考にすれば良い。

【0091】

上記のドライエッチングによって上記の主面Σが所望の形状に形状加工された結晶成長基板1の斜視図を図2に示す。ストライプ溝Sは、主面Σに形成された図中の傾斜面1aと側壁面1bから構成されている。また、符号Δ2はストライプ溝Sの深さを表しており、符号θ1 (=90°−α)は下地基板1の主面Σと傾斜面1aとが成す角度を表している。この様に、ストライプ溝Sの長手方向をy軸方向と略一致させた時、上記のa軸の方向(単位ベクトル<a|)と上記のストライプ溝Sの長手方向≡<s|=(0,1,0)との成す角ρは極小(最小)となる(本発明の第6の手段)。この時、式(2)から判る様に、ρ=θ0 ′である。

【0092】

本実施例1では、次式(3)の様に結晶成長基板1を形成する。

(下地基板(結晶成長基板1)の寸法)

α ≡ 90°−θ1 ≒ 47°,

Δ2 ≒ 3μm,

D ≒ 400μm …(3)

なお、水平方向(xy方向)の面積や縦横比などは任意で良い。

【0093】

図3−Aは、本実施例1のバッファ層積層工程を示す結晶成長基板1の部分的断面図である。バッファ層3は、AlGaN(またはAlNまたはGaN)からなる半導体層で、スパッタリングによって成膜する。使用するスパッタリング装置としては、例えば、高周波スパッタ装置や或いはプラズマスパッタ装置などが有用である。このスパッタリングにおいては、成膜領域を制限するために若干角度を付けて結晶成長基板1に対して斜めに材料を吹き付ける(斜めスパッタ)。図中の符号Aはその時の投射方向を表している。この傾け角δは、0°〜60°位で良い。本実施例におけるより望ましい範囲としては、3°〜10°程度である。この角度が大きいと後に形成されるボイドも大きくなる。また、この角度が小さ過ぎると、結晶成長基板1の側壁面1bにも材料が付着してしまい、後の非縦方向成長工程における所望のr面成長が順調に進展しない恐れが生じる。

【0094】

なお、上記のスパッタリングを実施する際の条件は以下の通りに設定する。

(スパッタリング条件)

積層するAlNの膜厚 : 640〔Å〕

スパッタガス : Ar(8sccm)/N2 (10sccm)

基板温度 : 430〔℃〕

DCパワー : 0.5〔W〕

電極面積 : 8000〔cm2 〕

【0095】

図3−B,−Cは、その後の本実施例1の非縦方向成長工程を示す結晶成長基板1の部分的断面図である。この非縦方向成長工程では、最初、上記のバッファ層3の上にはGaNのc面が結晶成長する。このc面成長は、下記の非縦方向成長工程の結晶成長条件に従えば、所謂ファセット成長として進行し、その非縦方向成長部4の片側の上向きのr面の法線ベクトルが、最初の主面Σの法線ベクトル<σ|と一致する様に結晶が成長する(図3−B)。

【0096】

ここでは、MOCVD法によって、上記の各ストライプ溝S中の大部分をGaN結晶で埋め込む。また、キャリアガスにH2 (またはN2 )を使用し、アンモニアとトリメチルガリウム(TMG)を下記の割合で供給する。これにより、各非縦方向成長部4の上面では、図3−Bに示す様にxy平面に平行にr面が結晶成長し、これらの個々のr面は、側壁面1bの近傍に若干のボイド5を形成しつつも、ストライプ溝Sを完全に覆い隠すまで結晶成長して、最終的には略一連の平坦面4aが形成される(図3−C)。

なお、この時(図3−B,−Cの時)の具体的な結晶成長条件は以下の通りにする。この条件設定は、継続的かつ順調なファセット成長を促進する上で重要である。また、下記の結晶成長速度は、r面に垂直な方向の結晶成長速度である。なお、下記のV/III 比は勿論モル比である。

【0097】

(非縦方向成長部4の結晶成長条件)

結晶成長温度 : 990〔℃〕

結晶成長速度 : 0.8〔μm/min〕

結晶成長時間 : 50〔min〕

供給ガス流量比(V/III 比): 5000

【0098】

図4は、GaN結晶から成る目的の半導体結晶層6を有するテンプレート10(新たな結晶成長基板)の断面図である。ここで、この半導体結晶層6の結晶成長条件は、次の通りとする。

(半導体結晶層6の結晶成長条件)

結晶成長温度 : 1050〔℃〕

結晶成長速度 : 0.6〔μm/min〕

結晶成長時間 : 100〔min〕

供給ガス流量比(V/III 比): 50000

【0099】

例えばこの様に、前述のMOCVD法において若干結晶成長条件を変えることで、半導体結晶層6のr面(上面6a)の転位密度が抑制されると共に、半導体結晶層6の上面6aの更なる平坦化を効果的に促進することができる。

したがって、以上の様にして得られるテンプレート10は、r面を界面とする広大かつ平坦な活性層の結晶成長を安定かつ確実に促進するので、内部量子効率の高い光半導体素子を製造する際の結晶成長基板として非常に有用なものとなる。

なお、後述の各実施例では、この様なテンプレートを用いて製造される内部量子効率の高い光半導体素子に付いて具体的に例示する。

【0100】

(r面成長を促進する結晶成長条件)

これらのr面成長には、MOCVD法が適している。また、安定したファセット成長(r面成長)を確実に誘起、促進するための結晶成長条件には、通常の一般的なc面成長の場合に対して、以下の特徴がある。

(1)結晶成長温度

結晶成長温度は、通常の一般的なc面成長の場合よりも低くした方が良い。

【0101】

(2)結晶成長速度

結晶成長速度は、通常の一般的なc面成長の場合よりも高くした方が良い。

(3)V/III 比

V/III 比は、通常の一般的なc面成長の場合よりも小さくした方が良い。

(4)アンモニアガス供給量

NH3 分圧は、通常の一般的なc面成長の場合よりも高くした方が良い。

【0102】

これらの具体的な適正範囲に付いては、既に概ね公知であり、ファセット成長に関わるこれらの一般的な諸傾向などについては、例えば以下の公開特許公報などからも、より詳しく具体的に知ることができる。

【0103】

ただし、これらの従来技術の目的は、所望の半導体結晶層の結晶品質を向上させることであって、これらの従来技術の思想や技法は、一連の平坦かつ広大なr面から成る積層界面を有する半導体結晶層を形成する様な目的や具体的アプローチを含んだものではない。また、これらの従来技術においては、c面成長によって活性層を形成する事例は多数見られるが、r面成長によって活性層を形成する事例は見当たらない。

【0104】

(参考例1)公開特許公報「特開平10−312971」

(参考例2)公開特許公報「特開平11−130597」

(参考例3)公開特許公報「特開平11−251631」

(参考例4)公開特許公報「特開2001−102307」

(参考例5)公開特許公報「特開2002−280609」

(参考例6)澤木宣彦、「選択成長法によるGaN微細構造の作製−集積形量子効果デバイスの実現に向けて−」名城大学ハイテクセンターシンポジウム(窒化物半導体研究センター成果発表シンポジウム)発表論文集、2000年6月23日

(参考例7)"Transmission Electron Microscopy Investigation of Dislocations in GaN Layer Grown by Facet-Controlled Epitaxial Lateral Overgrowth" , JAPANESE

JOURNAL OF APPLIED PHYSICS,Vol.40(2001)pp.L309-L312,Part2,No.4A,1 April 2001

(参考例8)水谷広光、外6名、「FACELO(ファセット制御ELO)によるGaNの低転位化」,信学技報,社団法人電子情報通信学会,ED2000-22,CPM2000-7,SDM2000-22(2000-05),pp.35-40

【実施例2】

【0105】

(LEDの構成例)

図5は、上記の実施例1のテンプレート10を有して成る本実施例2のLED100の断面図である。このテンプレート10では、図4、図5に法線ベクトル<σ|を用いて図示する通り、ノンドープのGaN結晶から成る前述の半導体結晶層6の上方の界面6aがr面となっている。このテンプレート10の上には、シリコン(Si)ドープのGaN から成る膜厚約4.0 μmの高キャリア濃度n+ 層103が形成されている。そして、この高キャリア濃度n+ 層103の上には、Siドープのn型GaN から成る膜厚約0.5 μmのクラッド層104が形成されている。

【0106】

更に、クラッド層104の上にGaNとGa0.8 In0.2 Nから成る多重量子井戸構造(MQW)の膜厚約500Åの発光層105が形成されている。発光層105の上にはp型Al0.15Ga0.85N から成る膜厚約600Åのクラッド層106が形成されている。さらに、クラッド層106の上にはp型GaN から成る膜厚約1500Åのコンタクト層107が形成されている。

【0107】

又、コンタクト層107の上には金属蒸着による薄膜正電極110が、n+ 層103上には負電極140が形成されている。薄膜正電極110は、コンタクト層107に接合する膜厚約15Åのニッケル(Ni)より成る薄膜正電極第1層111と、このNiに接合する膜厚約60Åの金(Au)より成る薄膜正電極第2層112とで構成されている。

【0108】

厚膜正電極120は、膜厚約175Åのバナジウム(V)より成る厚膜正電極第1層121と、膜厚約15000Åの金(Au)より成る厚膜正電極第2層122と、膜厚約100Åのアルミニウム(Al)より成る厚膜正電極第3層123とを薄膜正電極110の上から順次積層させることにより構成されている。負電極140は、膜厚約175Åのバナジウム(V) 層141と、膜厚約1000Åのアルミニウム(Al)層142と、膜厚約500Åのバナジウム(V) 層143と、膜厚約5000Åのニッケル(Ni)層144と、膜厚8000Åの金(Au)層145とを高キャリア濃度n+ 層103の一部露出された部分の上から順次積層させることにより構成されている。また最上部には、SiO2 膜より成る保護膜層130が形成されている。

【0109】

この様にして、形成されたLED100では、活性層(発光層105)の上下の各界面がr面から形成されており、この配向に基づいてピエゾ電界が略0に設定されているので、このLED100は、従来よりも高い発光効率を示す。

【実施例3】

【0110】

(半導体レーザの構成例)

図6に、本実施例3の半導体レーザ200の断面図を示す。この半導体レーザ200は、405nmのピーク波長で青紫色発光するものであり、上記の実施例1の下地基板1をベースに構成されたテンプレート10と略同様にして製造された他のテンプレート10′を有する。

【0111】

図7にこのテンプレート10′の部分的な断面図を示す。このテンプレート10′の先のテンプレート10に対する差異は、ストライプ溝Sの断面形状と斜めスパッタの投射角にある。即ち、本実施例3で使用するテンプレート10′では、傾斜面1a、1bから成る、断面形状が左右略対称形のV字形のストライプ溝S′が採用されている。また、バッファ層3はストライプ溝の一方の傾斜面1aにしか形成しない点では、図3−Aと同じだが、図3−Aのスパッタリングの投射の際の傾け角δに相当する角度は大幅に広く取られている。

【0112】

この様な設定によれば、テンプレート中にボイドを比較的大きく形成することができるので、下地基板と半導体結晶層との間の応力緩和作用が効果的に得られる点で非常に有利となる。

前述の実施例1では、ストライプ溝の片方の面を最初の主面Σに対して略垂直な側壁面(1b)で構成しているが、必ずしもその様な必要性があるわけではなく、例えば、本図7に例示する様に、断面形状が略対称形のV字溝や、或いはU字溝等を形成するなどしても良い。特に、所望の半導体結晶層を厚く結晶成長させたい場合には、基板と成長層との間には十分に歪み緩和作用がある方が望ましいが、その様な場合にはむしろボイドは大きく形成されている方が望ましい。この意味では、ストライプ溝の断面形状はむしろ、本図7に例示される様なV字形や、或いはU字形などの方が望ましい場合も少なくない。

【0113】

また、このテンプレート10′(図7)は、後述の通り共振器の下方部がエッチング処理によって大きくえぐられてしまうため、上記のボイドが外部量子効率などに悪影響を与える様な恐れは、少なくとも共振器の周辺においては全面的に排除される。また、このエッチング(:共振器直下のえぐり)によってもテンプレート10′が大きく二分されるため大きな歪み緩和作用が得られる。

【0114】

図6のテンプレート10′の上には、シリコン(Si)ドープのGaN から成る高キャリア濃度のn型コンタクト層202と、GaN から成るn型クラッド層203とが順次積層されている。更にその上には、活性層とその上下両側に位置する各型の光ガイド層から成る発光出力部204が形成されている。より具体的には、この発光出力部204は、Al0.01Ga0.99Nより成るn型の光ガイド層と、公知の端面発光型レーザダイオードに見られる一般的な多重量子井戸(MQW)構造の活性層と、マグネシウム(Mg)ドープのAl0.01Ga0.99Nから成るp型の光ガイド層とを順次積層することにより形成されたものである。

【0115】

この発光出力部204の上には、p型のAl0.12Ga0.88N から成るp型クラッド層と、Mgドープのp型のGaNから成るp型コンタクト層の計2層が順次積層されて形成されてできたp型半導体層205が配置されている。n型コンタクト層202は、上方(p型半導体層205側)からのエッチングによりその大部分が露出され、本エッチングにより、テンプレート10′に対して略垂直に立脚した平頂な共振器部分が形成される。また、この共振器の両脇には、SiO2 より成る絶縁性保護膜210がスパッタリングにより形成されている。

【0116】

また、テンプレート10′の裏面の凹部Dはエッチング処理により形成したものであり、符号εはこの凹部Dの形成後におけるn型コンタクト層202の残存膜厚を表している。この様に共振器の直下におけるn型コンタクト層202の厚さεを例えば0.3μm程度と非常に薄くする構造は、共振器内への光閉じ込め作用を良好に得るためのものであり、この構造によって、共振器の出射端面に現れるn型コンタクト層の干渉縞(FFPの乱れ)の発現を極めて効果的に抑制することができる。

【0117】

共振器の真下に位置するn型コンタクト層を全部削ってしまうと電流密度分布に偏りが生じて、共振器に効率よく電流を供給することができなくなるが、本実施例の様に共振器の真下に位置するn型コンタクト層の一部分をある程度(例:ε=0.3μm)残しておけば、共振器直下においても負電極と共振器とのコンタクトが良好に確保できるので、共振器内及び共振器周辺の電流の密度分布が理想的な状態に維持でき、同時に、上記の光の閉じ込め作用をも良好に確保することができる。更に、勿論、テンプレート10′の導入によって、発光出力部204の活性層ではr面成長に基づいてピエゾ電界が略0に改善されるため、本実施例3の半導体レーザ200においては、効果的に閾値電流を抑制することも可能となる。

このため、本実施例3の半導体レーザ200は、極めて良好に安定発振する。

【0118】

また、この様な半導体レーザの構造は、上下方向のFFPが乱れないため、レーザビームの照射位置(照射領域)を正確に制御するのに都合が良く、収斂性の良好なスポットサイズの小さな半導体レーザを実現する上で非常に有用である。

【実施例4】

【0119】

上記の実施例1では、前述の斜めスパッタを実施しているが、スパッタリングによるバッファ層の積層は、マスクを用いてその積層領域を制限しても良い。

また、上記の実施例1では、スパッタリングによってバッファ層を形成しているが、その他にも例えば結晶成長などの工程によってもバッファ層を形成することができる。この場合、バッファ層を積層しない部位にマスクを形成しておくマスキング工程などが必要となってしまうが、しかしながら、マスクを用いて自在に制御される結晶成長によってバッファ層を形成すれば、バッファ層を所望の領域に略一様の厚さで薄くムラなく形成することが可能または容易になる。また、バッファ層をその様に綺麗に成膜することは、非縦方向成長工程で形成される非縦方向成長部の平坦性などの品質をより高く確保する上でより望ましい。

以下の本実施例4では、その様な、結晶成長によってバッファ層を形成する場合について例示する。

【0120】

図8−A〜Dは、バッファ層を結晶成長させる実施例(実施例4)の基板の断面図である。基板21には、サファイア基板を用いており、この基板21の向き(配向)は、実施例1(図1−A)と同じである。また、レジストマスク22には図1−Bのレジストマスク2と同じ材料のものを用いているので、記号α、Δ1、φの各変数値についても、前述の実施例1と一致する。

【0121】

本実施例4の大きな特徴の一つは、図8−Aに示される基板21の主面Σ上にSiO2 より成るマスク23が積層されている点にある。ここで、レジストマスク22は、このマスク23の上に形成されている。この様な方法に従えば、図8−Bに示す様に、ストライプ溝Sを形成する両脇のリッジRgの平頂面に選択成長を促すELOマスク(マスク23)を形成することができる。

【0122】

フォトレジスト24は、スパッタまたは塗布によって、上記の基板上に成膜されたものである。このフォトレジスト24に対して、図示する右上の方向Aから露光すると、マスク23上、及び傾斜面21a上のフォトレジスト24は取り除くことができるが、垂直な内壁面21b上のフォトレジスト24は、そのまま残る。したがって、基板21では、傾斜面21aの大部分だけが、上方に露出することになる。

【0123】

図8−Dは、この傾斜面21aの露出面上に、AlNまたはAlGaNから成る低温バッファ層25を積層したものである。この様な方法によっても、図3−Aと同様の所望の方位にバッファ層25を積層することができる。

また、この方法に従えば、低温バッファ層25を成長核として、その後に成長する半導体結晶でストライプ溝Sが全て埋まった後には、マスク23上では、半導体結晶の横方向の成長が促進されるため、所望の半導体結晶を更に上方に成長させれば、目的の半導体結晶の転位密度が効果的に抑制できる。

【実施例5】

【0124】

図9−A,−B,−Cは何れも、バッファ層を結晶成長させる本実施例5の基板の断面図である。a面を主面とするサファイア基板31には、その主面である上面に、c軸に対して垂直な方向に、ストライプ溝Sの長手方向が取られている。SiO2 から形成されるマスク33は、図示する左上の方向からの斜めスパッタリングによって、主面及びストライプ溝Sの内壁面や底面の一部に積層されたものである。この斜めスパッタリングによって、略垂直な内壁面31a上と断面形状が縦長矩形のストライプ溝Sの底部の一部の双方を除く部分に、マスク33が形成されている。内壁面31aは、上記の配向により、サファイアc面となっている。

【0125】

この様な基板に対して、AlNまたはAlGaNから成る低温バッファ層34を積層し、更に、GaNから成る非縦方向成長部35をファセット成長させた状態を図9−Bに示す。この図9−Bは、非縦方向成長部35を形成するGaN結晶によって、上記のストライプ溝Sに蓋がされて、ストライプ溝Sの底部などにボイドが形成された状態を示している。その後a面成長が促進される結晶成長条件で、GaN結晶の成長を続けることにより、図9−Cに図示する様に、一連かつ広大なa面を結晶成長面とする所望のGaN結晶36を得ることができる。

【実施例6】

【0126】

図10−A,−Bは何れも、バッファ層を結晶成長させる本実施例6の基板の断面図である。本図のサファイア基板41の配向は、垂直上向きがm軸の向きと一致し、水平右向きがc軸の向きと一致している。したがって、ストライプ溝Sの垂直な内壁面41aは、サファイアc面になっている。この様な深い略V字型のストライプ溝Sを有するサファイア基板41の上方から、塗布またはスパッタによって、フォトレジスト42を成膜した(図10−A)。

【0127】

図10−Aに図示する矢印の向きは、このフォトレジスト42に対する露光条件を示している。即ち、内壁面41aの上位の部分だけが露出される様に、右上の方向から露光する。この様な構成によっても、サファイアc面だけを露出させることができるので、この場合にも、図9−B,図9−Cと略同様の結晶成長過程に従って、一連の広大なm面を結晶成長面とする、GaNから成る所望の半導体結晶を得ることができる。

【0128】

〔その他の変形例〕

本発明の実施形態は、上記の形態に限定されるものではなく、その他にも以下に例示される様な変形を行っても良い。この様な変形や応用によっても、本発明の作用に基づいて本発明の効果を得ることができる。

【0129】

(変形例1)

例えば、ボイドを大きく形成すると熱膨張係数差や或いは格子定数差などに伴って、基板と成長層との間に発生する上記の応力が、非縦方向成長部又は下地基板の突起部に対する剪断応力として作用するため、下地基板を綺麗に分離できる場合がある。即ち、この様な剪断作用を利用すると良い場合もある。この様な分離工程や分離作用に付いては、例えば公開特許公報「特開2002−293698:半導体基板の製造方法及び半導体素子」にも関連する類似の例示があり、この様な分離処理を本発明の結晶成長方法に導入することは、極めて有用な技法となる場合がある。

【0130】

(変形例2)

また、上記の実施例2や実施例3では、下地基板(結晶成長基板1)を除去せずに半導体発光素子(100,200)の中に残したが、例えば図4の半導体結晶層6の厚さを例えば400μm以上に積層すれば、その半導体結晶層6は自立した単独のバルク結晶として安定するので、その様なバルク結晶を新たな結晶成長基板として、所望の光半導体素子を製造しても良い。この様な場合には、例えば図4の非縦方向成長部4と下地基板(結晶成長基板1)との間に形成されるボイド5は、後の工程(前述の基板除去工程)で完全に排除することができるので、この様なボイドが光半導体素子の外部量子効率を低下させると言った前述の問題が必然的に解決できる。

【0131】

また、この様に後で下地基板を分離または除去する場合には、製造工程の途中で形成されるボイドは、大きい方が応力緩和作用をもたらすのでより望ましい。また、その様な自立した単独のバルク結晶を製造する場合には、前にも言及した様に、前述の縦方向成長工程の後に、又は、その縦方向成長工程に並行して、目的とする上記の半導体結晶から結晶成長基板を除去する基板除去工程を設けても良い。

逆に、この様な技法を用いなかったり、或いは、多数のストライプ溝の形成に基づいて、結晶成長基板(下地基板)と半導体結晶との間に形成される凹凸構造やボイドによる応力緩和作用が乏しかったりすると、所望の半導体結晶層を10μm程度しか積層できないことがあるので注意を要する。

【0132】

(変形例3)

また、上記の実施例1では、ストライプ溝の深さや形成周期は略一定に統一したが、必ずしもこれらを統一した形式でストライプ溝を形成する必要はない。ここで最も重要なことは、尾根状の頂点ラインを略同一平面(Σ)上に略平行に配列することと、各傾斜面(1a)の傾斜角θ1 をそれぞれ何れも前述の角θ0 に略一致させることである。

また、ストライプ溝の幅は、必ずしも図2の様に、一定である必要はない。このことは、図2のx軸方向についてもy軸方向についても、更にはz軸方向についても言えることである。

【0133】

また、上記の実施例1では、最初の結晶成長基板(下地基板)の主面Σは殆ど全面的に取り除かれているが、下地基板には上方の主面(Σ)を部分的かつ離散的に一部残しても良い。

例えば、シリコン(Si)を下地基板とする場合、GaNはバッファ層が供する結晶成長面には結晶成長するが、下地基板(Si)に対して直接には非常に結晶成長し難いので、下地基板にストライプ溝を形成した後に、元来の上方の主面が部分的かつ離散的に一部残っていても、その幅が数μm程度以内と細ければ各結晶成長面を1つの略平坦な面に特段の不都合なく繋げることは十分に可能であり、特に他の派生問題が生じることはない。この意味で、シリコン(Si)を下地基板とすることは有効であると考えられる。

【0134】

(変形例4)

また、上記の公開特許公報「特開2002−293698:半導体基板の製造方法及び半導体素子」にも記載されている様に、シリコン(Si)を下地基板とする場合には、炭化シリコン(SiC)などから成る周知の反応防止層を形成しておくと、積層工程が増えてしまうものの、結晶品質などに関してより効果的となることがある。

また、シリコン(Si)は比較的柔らかい材料であるので、歪み緩和作用やエッチング容易性などの観点からも有利である。また、上記の実施例1では、ドライエッチングによってストライプ溝を形成しているが、例えば基板材料などの個々の実施条件によってはウェットエッチングを実施しても良い。

【産業上の利用可能性】

【0135】

本発明の結晶成長方法、並びに本発明の結晶成長基板は、LEDや半導体レーザなどの半導体発光素子や半導体受光素子の製造に大いに有用なものである。また、それらの結晶成長方法、並びに本発明の結晶成長基板を用いて製造される光半導体素子も本発明の範疇にある。

【符号の説明】

【0136】

1 : 結晶成長基板(下地基板)

1a: 下地基板(結晶成長基板1)の傾斜面

1b: 下地基板(結晶成長基板1)の側壁面

S : ストライプ溝(傾斜面1aと側壁面1bから構成される)

2 : レジストマスク

3 : バッファ層

4 : 非縦方向成長部

5 : ボイド

6 : 目的の半導体結晶層

10 : テンプレート(実施例1で得られる新たな結晶成長基板)

10′: テンプレート(実施例3)

100: 実施例2のLED

200: 実施例3の半導体レーザ

θ0 : 目的の半導体結晶(半導体結晶層6)のc面とr面とが成す角

θ1 : 下地基板1の主面Σと傾斜面1aとが成す角

φ : レジストマスク2の傾斜角

Σ : 下地基板(結晶成長基板1)の上方の主面(主面)

<σ|: 主面Σの法線ベクトル

<c|: c軸の方向ベクトル

<a|: a軸の方向ベクトル

【特許請求の範囲】

【請求項1】

III族窒化物系化合物半導体から成る半導体層を有する半導体素子であって、

サファイア基板と、

前記サファイア基板が有する平面状の主面において形成され、前記主面に平行ではない平面で構成された二つの側壁面を有する複数の平行なストライプ溝と、

前記複数のストライプ溝において、前記 III族窒化物系化合物半導体を成長させる側壁面を主内壁面とし、この主内壁面に形成されたバッファ層と、

複数の前記ストライプ溝の前記各主内壁面に対して垂直に、前記バッファ層の上にc軸方向に成長し、前記主面の面内方向において合体し、前記サファイア基板の前記主面を覆う、 III族窒化物系化合物半導体から成る第1半導体層と、

前記第1半導体層の前記サファイア基板の前記主面に平行な面を結晶成長核として、前記主面に対して垂直な方向に成長した、 III族窒化物系化合物半導体から成る第2半導体層と、

前記第2半導体層の上部に形成された活性層と

を有し、

前記ストライプ溝の前記主内壁面と前記サファイア基板の前記主面とが成す第1の角θ1 を、前記 III族窒化物系化合物半導体のc軸と、前記 III族窒化物系化合物半導体のピエゾ電界が零となる結晶方位であるr軸、a軸、又は、m軸の方位との成す第2の角θ0 に対して、θ0 −10°≦θ1 ≦θ0 +10°を満たす角度とし、

前記第1半導体層、前記第2半導体層及び前記活性層における、前記サファイア基板の前記主面に垂直な方向の結晶軸は、前記 III族窒化物系化合物半導体のr軸、a軸、又は、m軸に対して、±10°以下となる結晶軸である

ことを特徴とする半導体素子。

【請求項2】

III族窒化物系化合物半導体から成る半導体層を有する III族窒化物系化合物半導体基板であって、

サファイア基板と、

前記サファイア基板が有する平面状の主面において形成され、前記主面に平行ではない平面で構成された二つの側壁面を有する複数の平行なストライプ溝と、

前記複数のストライプ溝において、前記 III族窒化物系化合物半導体を成長させる側壁面を主内壁面とし、この主内壁面に形成されたバッファ層と、

複数の前記ストライプ溝の前記各主内壁面に対して垂直に、前記バッファ層の上にc軸方向に成長し、前記主面の面内方向において合体し、前記サファイア基板の前記主面を覆う、 III族窒化物系化合物半導体から成る第1半導体層と、

前記第1半導体層の前記サファイア基板の前記主面に平行な面を結晶成長核として、前記主面に対して垂直な方向に成長した、 III族窒化物系化合物半導体から成る第2半導体層と、

を有し、

前記ストライプ溝の前記主内壁面と前記サファイア基板の前記主面とが成す第1の角θ1 は、前記 III族窒化物系化合物半導体のc軸と、前記 III族窒化物系化合物半導体のピエゾ電界が零となる結晶方位であるr軸、a軸、又は、m軸の方位との成す第2の角θ0 に対して、θ0 −10°≦θ1 ≦θ0 +10°を満たす角度であり、

前記第1半導体層及び第2半導体層における、前記サファイア基板の前記主面に垂直な方向の結晶軸は、前記 III族窒化物系化合物半導体のr軸、a軸、又は、m軸に対して、±10°以下となる結晶軸である

ことを特徴とする III族窒化物系化合物半導体基板。

【請求項3】

前記ストライプ溝の前記二つの側壁面のうち前記バッファ層を形成しない側壁面は、前記 III族窒化物系化合物半導体の前記サファイア基板からの成長を阻害するマスクが形成されておらず前記サファイア基板が露出していることを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記ストライプ溝の前記二つの側壁面のうち前記バッファ層を形成しない側壁面は、前記 III族窒化物系化合物半導体の前記サファイア基板からの成長を阻害するマスクが形成されておらず前記サファイア基板が露出していることを特徴とする請求項2に記載の III族窒化物系化合物半導体基板。

【請求項5】

前記サファイア基板の前記主内壁面の法線ベクトルは、前記サファイア基板におけるc軸又はa軸であることを特徴とする請求項1又は請求項3に記載の半導体素子。

【請求項6】

前記サファイア基板の前記主内壁面の法線ベクトルは、前記サファイア基板におけるc軸又はa軸であることを特徴とする請求項2又は請求項4に記載の III族窒化物系化合物半導体基板。

【請求項7】

前記ピエゾ電界が零となる前記結晶方位はr軸の方位であり、前記第2の角θ0 は、43.2°であることを特徴とする請求項1、請求項3、又は、請求項5に記載の半導体素子。

【請求項8】

前記ピエゾ電界が零となる前記結晶方位はr軸の方位であり、前記第2の角θ0 は、43.2°であることを特徴とする請求項2、請求項4、又は、請求項6に記載の III族窒化物系化合物半導体基板。

【請求項9】

前記サファイア基板の前記主内壁面の法線ベクトルは、前記サファイア基板におけるc軸であり、

前記ピエゾ電界が零となる前記結晶方位はa軸又はm軸であり、

前記第2の角θ0 は、90°である

ことを特徴とする請求項1、請求項3、請求項5、又は、請求項7に記載の半導体素子。

【請求項10】

前記サファイア基板の前記主内壁面の法線ベクトルは、前記サファイア基板におけるc軸であり、

前記ピエゾ電界が零となる前記結晶方位はa軸又はm軸であり、

前記第2の角θ0 は、90°である

ことを特徴とする請求項2、請求項4、請求項6、又は、請求項8に記載の III族窒化物系化合物半導体基板。

【請求項1】

III族窒化物系化合物半導体から成る半導体層を有する半導体素子であって、

サファイア基板と、

前記サファイア基板が有する平面状の主面において形成され、前記主面に平行ではない平面で構成された二つの側壁面を有する複数の平行なストライプ溝と、

前記複数のストライプ溝において、前記 III族窒化物系化合物半導体を成長させる側壁面を主内壁面とし、この主内壁面に形成されたバッファ層と、

複数の前記ストライプ溝の前記各主内壁面に対して垂直に、前記バッファ層の上にc軸方向に成長し、前記主面の面内方向において合体し、前記サファイア基板の前記主面を覆う、 III族窒化物系化合物半導体から成る第1半導体層と、

前記第1半導体層の前記サファイア基板の前記主面に平行な面を結晶成長核として、前記主面に対して垂直な方向に成長した、 III族窒化物系化合物半導体から成る第2半導体層と、

前記第2半導体層の上部に形成された活性層と

を有し、

前記ストライプ溝の前記主内壁面と前記サファイア基板の前記主面とが成す第1の角θ1 を、前記 III族窒化物系化合物半導体のc軸と、前記 III族窒化物系化合物半導体のピエゾ電界が零となる結晶方位であるr軸、a軸、又は、m軸の方位との成す第2の角θ0 に対して、θ0 −10°≦θ1 ≦θ0 +10°を満たす角度とし、

前記第1半導体層、前記第2半導体層及び前記活性層における、前記サファイア基板の前記主面に垂直な方向の結晶軸は、前記 III族窒化物系化合物半導体のr軸、a軸、又は、m軸に対して、±10°以下となる結晶軸である

ことを特徴とする半導体素子。

【請求項2】

III族窒化物系化合物半導体から成る半導体層を有する III族窒化物系化合物半導体基板であって、

サファイア基板と、

前記サファイア基板が有する平面状の主面において形成され、前記主面に平行ではない平面で構成された二つの側壁面を有する複数の平行なストライプ溝と、

前記複数のストライプ溝において、前記 III族窒化物系化合物半導体を成長させる側壁面を主内壁面とし、この主内壁面に形成されたバッファ層と、

複数の前記ストライプ溝の前記各主内壁面に対して垂直に、前記バッファ層の上にc軸方向に成長し、前記主面の面内方向において合体し、前記サファイア基板の前記主面を覆う、 III族窒化物系化合物半導体から成る第1半導体層と、

前記第1半導体層の前記サファイア基板の前記主面に平行な面を結晶成長核として、前記主面に対して垂直な方向に成長した、 III族窒化物系化合物半導体から成る第2半導体層と、

を有し、

前記ストライプ溝の前記主内壁面と前記サファイア基板の前記主面とが成す第1の角θ1 は、前記 III族窒化物系化合物半導体のc軸と、前記 III族窒化物系化合物半導体のピエゾ電界が零となる結晶方位であるr軸、a軸、又は、m軸の方位との成す第2の角θ0 に対して、θ0 −10°≦θ1 ≦θ0 +10°を満たす角度であり、

前記第1半導体層及び第2半導体層における、前記サファイア基板の前記主面に垂直な方向の結晶軸は、前記 III族窒化物系化合物半導体のr軸、a軸、又は、m軸に対して、±10°以下となる結晶軸である

ことを特徴とする III族窒化物系化合物半導体基板。

【請求項3】

前記ストライプ溝の前記二つの側壁面のうち前記バッファ層を形成しない側壁面は、前記 III族窒化物系化合物半導体の前記サファイア基板からの成長を阻害するマスクが形成されておらず前記サファイア基板が露出していることを特徴とする請求項1に記載の半導体素子。

【請求項4】

前記ストライプ溝の前記二つの側壁面のうち前記バッファ層を形成しない側壁面は、前記 III族窒化物系化合物半導体の前記サファイア基板からの成長を阻害するマスクが形成されておらず前記サファイア基板が露出していることを特徴とする請求項2に記載の III族窒化物系化合物半導体基板。

【請求項5】

前記サファイア基板の前記主内壁面の法線ベクトルは、前記サファイア基板におけるc軸又はa軸であることを特徴とする請求項1又は請求項3に記載の半導体素子。

【請求項6】

前記サファイア基板の前記主内壁面の法線ベクトルは、前記サファイア基板におけるc軸又はa軸であることを特徴とする請求項2又は請求項4に記載の III族窒化物系化合物半導体基板。

【請求項7】

前記ピエゾ電界が零となる前記結晶方位はr軸の方位であり、前記第2の角θ0 は、43.2°であることを特徴とする請求項1、請求項3、又は、請求項5に記載の半導体素子。

【請求項8】

前記ピエゾ電界が零となる前記結晶方位はr軸の方位であり、前記第2の角θ0 は、43.2°であることを特徴とする請求項2、請求項4、又は、請求項6に記載の III族窒化物系化合物半導体基板。

【請求項9】

前記サファイア基板の前記主内壁面の法線ベクトルは、前記サファイア基板におけるc軸であり、

前記ピエゾ電界が零となる前記結晶方位はa軸又はm軸であり、

前記第2の角θ0 は、90°である

ことを特徴とする請求項1、請求項3、請求項5、又は、請求項7に記載の半導体素子。

【請求項10】

前記サファイア基板の前記主内壁面の法線ベクトルは、前記サファイア基板におけるc軸であり、

前記ピエゾ電界が零となる前記結晶方位はa軸又はm軸であり、

前記第2の角θ0 は、90°である

ことを特徴とする請求項2、請求項4、請求項6、又は、請求項8に記載の III族窒化物系化合物半導体基板。

【図1−A】

【図1−B】

【図1−C】

【図2】

【図3−A】

【図3−B】

【図3−C】

【図4】

【図5】

【図6】

【図7】

【図8−A】

【図8−B】

【図8−C】

【図8−D】

【図9−A】

【図9−B】

【図9−C】

【図10−A】

【図10−B】

【図11】

【図12】

【図1−B】

【図1−C】

【図2】

【図3−A】

【図3−B】

【図3−C】

【図4】

【図5】

【図6】

【図7】

【図8−A】

【図8−B】

【図8−C】

【図8−D】

【図9−A】

【図9−B】

【図9−C】

【図10−A】

【図10−B】

【図11】

【図12】

【公開番号】特開2009−182340(P2009−182340A)

【公開日】平成21年8月13日(2009.8.13)

【国際特許分類】

【出願番号】特願2009−112544(P2009−112544)

【出願日】平成21年5月7日(2009.5.7)

【分割の表示】特願2004−215462(P2004−215462)の分割

【原出願日】平成16年7月23日(2004.7.23)

【出願人】(000241463)豊田合成株式会社 (3,467)

【Fターム(参考)】

【公開日】平成21年8月13日(2009.8.13)

【国際特許分類】

【出願日】平成21年5月7日(2009.5.7)

【分割の表示】特願2004−215462(P2004−215462)の分割

【原出願日】平成16年7月23日(2004.7.23)

【出願人】(000241463)豊田合成株式会社 (3,467)

【Fターム(参考)】

[ Back to top ]