半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子基板の製造方法および半導体素子基板並びに表示装置に関し、特に例えば、薄膜トランジスタを含み、アクティブマトリクス駆動方式の表示装置に用いられる半導体素子基板の製造方法および半導体素子基板並びに表示装置に関する。

【背景技術】

【0002】

近年、ガラス基板等の絶縁基板上に成膜した非晶質半導体膜を結晶化して、多結晶シリコン膜等の結晶構造を有する結晶性半導体膜を形成する技術が研究されている。結晶性半導体膜は、非晶質半導体膜に比べて非常に大きなキャリア移動度を有する。このため、例えば表示領域を構成する複数の画素回路と、画素回路を駆動するための周辺回路が同一の基板上に作り込まれたフルモノリシック型の液晶表示装置において、結晶性半導体膜を用いて形成した薄膜トランジスタ(Thin Film Transistor;以下、「TFT」という)は、各画素回路のスイッチング素子として機能するTFT(画素TFT)や、周辺回路を構成するTFT(周辺回路TFT)等として利用され、表示装置の高精細化および高速化を可能にしている。

【0003】

しかし、画素TFTと周辺回路TFTとでは、要求される動作速度や閾値電圧等の電気的特性が異なる。このため、これらのTFTを、一種類の結晶性半導体膜を用いて形成することは困難である。そこで、電気的特性に応じた異なる膜質の結晶性半導体膜を同一の絶縁基板上に形成することが求められている。

【0004】

また、結晶性半導体膜を安価な絶縁基板であるガラス基板やプラスチック基板に形成するためにレーザニール法が開発された。レーザニール法は、輻射加熱または伝導加熱を利用する高温熱処理法に比べて処理時間を大幅に短縮できるだけでなく、非晶質半導体膜を選択的、局所的に加熱することによりガラス基板に熱的損傷を与えない等の特徴がある。そこで、レーザアニール法を用いて、同一の絶縁基板上に膜質の異なる結晶性半導体膜を形成する各種の方法が提案されている。

【0005】

特許文献1には、連続発振レーザビームの走査中に走査速度を調整して単位時間当たりの照射量を領域ごとに連続的に変えることにより、結晶の異方性が異なる複数の領域からなる多結晶半導体膜を1回の走査で形成することが記載されている。

【0006】

また、特許文献2には、画素TFTを、電流経路の方向がレーザビームの照射によって結晶性半導体膜の結晶の成長方向と略垂直になるように配置し、駆動回路用TFTを、電流経路の方向が結晶の成長方向と略平行になるように配置することが記載されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−141040号公報

【特許文献2】国際公開2010/038511号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1に記載された方法によれば、レーザビームを1回だけ走査することによって、同一のガラス基板上に結晶の異方性が異なる複数の領域からなる多結晶半導体膜を形成することができる。しかし、レーザビームの走査中に走査速度を細かく調整することは難しいので、結晶の異方性が異なる領域を用いる必要があるTFTを近接して形成しなければならない場合、それぞれの領域を近接して形成することは難しい。このため、結晶の異方性が異なる領域を用いたTFTを集積化することは困難になる。

【0009】

また、特許文献2に記載されたTFTの配置方法によれば、結晶の成長方向を考慮して、画素TFTと周辺回路TFTを配置しなければならない。このため、特に周辺回路の設計の自由度が小さくなり、TFTを集積化することが困難になる。

【0010】

そこで、本発明は、結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供することを目的とする。

【課題を解決するための手段】

【0011】

第1の発明は、絶縁基板上に半導体素子が形成された半導体素子基板の製造方法であって、

前記絶縁基板上に高融点金属膜を用いて加熱促進層を形成する加熱促進層形成工程と、

前記加熱促進層を覆うように絶縁膜を成膜する絶縁膜形成工程と、

前記絶縁膜上に非晶質半導体膜を成膜する非晶質半導体膜形成工程と、

前記非晶質半導体膜の表面側からレーザビームを照射して前記非晶質半導体膜を溶融固化することにより、結晶異方性を有する第1の結晶性半導体膜と、結晶異方性を有さない第2の結晶性半導体膜とを形成する結晶化工程とを備え、

前記第1の結晶性半導体膜は、前記非晶質半導体膜を透過した前記レーザビームが前記加熱促進層に照射されて、前記非晶質半導体膜の裏面側からも結晶化を促進することにより形成されることを特徴とする。

【0012】

第2の発明は、第1の発明において、

前記非晶質半導体膜の裏面側からの結晶化の促進は、前記加熱促進層の表面で反射された前記レーザビームが前記非晶質半導体膜の裏面に照射されることによって行なわれることを特徴とする。

【0013】

第3の発明は、第2の発明において、

前記高融点金属膜は少なくともモリブデン膜を含む金属膜であることを特徴とする。

【0014】

第4の発明は、第1の発明において、

前記非晶質半導体膜の裏面側からの結晶化の促進は、前記加熱促進層が前記レーザビームを吸収して発生した熱が前記非晶質半導体膜の裏面に与えられることによって行なわれることを特徴とする。

【0015】

第5の発明は、第4の発明において、

前記高融点金属膜は少なくともタングステン膜を含む金属膜であることを特徴とする。

【0016】

第6の発明は、第1の発明において、

前記加熱促進層の膜厚は50nm以上かつ500nm以下であることを特徴とする。

【0017】

第7の発明は、第1の発明において、

前記レーザビームは、連続発振レーザビームまたは擬似連続発振レーザビームであることを特徴とする。

【0018】

第8の発明は、第7の発明において、

前記レーザビームは、イットリウム・アルミニウム・ガーネットレーザの第2高調波のビームであることを特徴とする。

【0019】

第9の発明は、第7の発明において、

前記レーザビームの走査速度は5cm/sec以上かつ3m/sec以下であることを特徴とする。

【0020】

第10の発明は、第7の発明において、

前記レーザビームの走査回数は1回であることを特徴とする。

【0021】

第11の発明は、第1の発明において、

前記絶縁膜は、少なくとも酸化シリコン、窒化シリコン、酸窒化シリコンのいずれかを含むことを特徴とする

【0022】

第12の発明は、第11の発明において、

前記絶縁膜の膜厚は30nm以上かつ500nm以下であることを特徴とする。

【0023】

第13の発明は、第1の発明において、

前記非晶質半導体膜は非晶質シリコン膜であることを特徴とする。

【0024】

第14の発明は、第13の発明において、

前記レーザビームの波長は370nm以上かつ650nm以下であることを特徴とする。

【0025】

第15の発明は、第14の発明において、

前記半導体素子は薄膜トランジスタであり、

前記第1および第2の結晶性半導体膜をパターニングすることによって前記薄膜トランジスタの半導体層を形成する半導体層形成工程をさらに備えることを特徴とする。

【0026】

第16の発明は、半導体素子基板であって、

第1から第15のいずれかの発明に係る半導体素子基板の製造方法によって製造されたことを特徴とする。

【0027】

第17の発明は、第16の発明において、

前記半導体素子基板は、

前記第1の結晶性半導体膜から形成された第1の半導体層を有する第1薄膜トランジスタと、

前記第2の結晶性半導体膜から形成された第2の半導体層を有する第2薄膜トランジスタとを備えることを特徴とする。

【0028】

第18の発明は、第17の発明において、

前記第1の薄膜トランジスタは、前記第1の半導体層の上方に形成された第1のゲート電極を有する薄膜トランジスタであり、

前記第2の薄膜トランジスタは、前記第2の半導体層の上方に形成された第2のゲート電極を有する薄膜トランジスタであることを特徴とする。

【0029】

第19の発明は、第18の発明において、

前記第1の薄膜トランジスタはダブルゲート構造の薄膜トランジスタをさらに含み、

前記ダブルゲート構造の薄膜トランジスタのボトムゲート電極は、前記第1のゲート電極と電気的に接続された前記加熱促進層であることを特徴とする。

【0030】

第20の発明は、第17の発明において、

前記第1の薄膜トランジスタはボトムゲート構造の薄膜トランジスタであり、

前記ボトムゲート構造の薄膜トランジスタのボトムゲート電極は、前記加熱促進層であり、

前記第2の薄膜トランジスタは、前記第2の半導体層の上方に形成された第2のゲート電極を有することを特徴とする。

【0031】

第21の発明は、表示装置であって、

第17から第20のいずれかの発明に係る半導体素子基板を備える表示装置であって、前記第1の薄膜トランジスタのチャネル領域は、前記第2の薄膜トランジスタのチャネル領域よりも大きいことを特徴とする。

【0032】

第22の発明は、第21の発明において、

複数の画素回路をマトリクス状に配列した表示領域と、前記絶縁基板上の額縁領域に形成された前記複数の画素回路を駆動するための周辺回路とをさらに備え、

前記周辺回路は前記第1の薄膜トランジスタによって構成され、

前記複数の画素回路のスイッチング素子は前記第2の薄膜トランジスタによって構成されていることを特徴とする。

【発明の効果】

【0033】

上記第1の発明によれば、レーザビームを反射または吸収して非晶質半導体膜の裏面側からの加熱を促進させるための加熱促進層を形成し、非晶質半導体膜にレーザビームを照射する。加熱促進層は、非晶質半導体膜を透過したレーザビームを反射または吸収して、加熱促進層の上方およびその近傍の非晶質半導体膜を加熱する。これにより、加熱促進層がレーザビームを反射または吸収して、加熱促進層の上方およびその近傍の非晶質半導体膜は、加熱促進層から離れた位置にある非晶質半導体膜よりも加熱されて高温になる。その結果、下方に加熱促進層が形成された非晶質半導体膜およびその近傍に照射されるレーザビームの照射量が実効的に大きくなるので、結晶の配向が揃った第1の結晶性半導体膜になる。このように加熱促進層が形成される位置を精度よく制御して、第1の結晶性半導体膜が形成される位置を高い精度で制御することができる。また、第1の結晶性半導体膜の位置が決まると、結晶の配向がランダムな第2の結晶性半導体膜が形成される位置も決まる。その結果、第1および第2の結晶性半導体膜からなる半導体素子を近接させて形成することができるので、半導体素子を高集積化した半導体素子基板を製造することができる。このとき、加熱促進層は、高融点金属膜からなるので、レーザビームを吸収して高温になっても溶融しにくい。

【0034】

上記第2の発明によれば、加熱促進層は、非晶質半導体膜に照射されたレーザビームをその表面で反射する。反射されたレーザビームは非晶質半導体膜の裏面に照射される。これにより、非晶質半導体膜の裏面側からも非晶質半導体膜の結晶化を促進する。

【0035】

上記第3の発明によれば、モリブデン膜を含む加熱促進層は、レーザビームを反射することによって、非晶質半導体膜の結晶化を裏面側から促進する。

【0036】

上記第4の発明によれば、加熱促進層は、非晶質半導体膜に照射されたレーザビームを吸収して発熱し、非晶質半導体膜の結晶化を裏面側から促進する。

【0037】

上記第5の発明によれば、タングステン膜を含む加熱促進層は、レーザビームを吸収して発熱し、非晶質半導体膜の裏面側を加熱して結晶化を促進する。

【0038】

上記第6の発明によれば、加熱促進層の膜厚を50nm以上にすることによって、非晶質半導体膜にレーザビームを照射したときに、加熱促進層におけるレーザビームの反射または吸収が不十分になることを抑制できる。これにより、加熱促進層の上方およびその近傍の非晶質半導体膜を、溶融固化することができる。一方、加熱促進層の膜厚を500nm以下にすることにより、加熱促進層が設けられた領域の上方の絶縁膜の表面と加熱促進層が設けられていない領域の上方の絶縁膜の表面との間の段差を小さくし、電極や配線が段差によって段切れしにくくする。このため、加熱促進層の膜厚を50nm以上かつ500nm以下にすることが好ましい。

【0039】

上記第7の発明によれば、連続発振レーザビームまたは擬似連続発振レーザビームを出力するレーザ発振器は単純な構造であるので、メンテナンスが長期間不要になる。これにより、レーザ発振器の稼働時間を長くして、ランニングコストを安価にすることができる。

【0040】

上記第8の発明によれば、イットリウム・アルミニウム・ガーネットレーザの第2高調波(波長532nm)を非晶質半導体膜に照射する。これにより、加熱促進層の上方およびその近傍の非晶質半導体膜のみに、実効的に大きな照射量のレーザビームを照射し、部分的に第1の結晶性半導体膜を形成することができる。

【0041】

上記第9の発明によれば、レーザビームの走査速度を5cm/sec以上にすることによって、非晶質半導体膜が過剰なエネルギーを受けて蒸発することを抑制できる。また、レーザビームの走査速度を3m/sec以下にすることによって、非晶質半導体膜を確実に溶融固化することができる。

【0042】

上記第10の発明によれば、レーザビームを1回だけ走査すればよいので、結晶化工程の処理時間を短縮することができる。

【0043】

上記第11の発明によれば、加熱促進層を覆う絶縁膜は、少なくとも酸化シリコン膜、窒化シリコン膜、酸窒化シリコン膜のいずれかを含むので、不純物が絶縁基板から非晶質半導体膜に拡散することを抑制することができる。

【0044】

上記第12の発明によれば、絶縁膜の膜厚を30nm以上にすることにより、第1および第2の結晶性半導体膜をパターニングする際のオーバーエッチングによって絶縁膜がエッチングされ、加熱促進層の一部が露出することを防止できる。これにより、加熱促進層がその後の工程で形成される配線層と短絡しないようにすることができる。一方、絶縁膜の膜厚を500nm以下にすることにより、非晶質半導体膜にレーザビームを照射したときに、加熱促進層によるレーザビームの反射または吸収が十分行なわれ、非晶質半導体膜の裏面側からの結晶化を十分に促進することができる。

【0045】

上記第13の発明によれば、非晶質半導体膜として非晶質シリコン膜を用いることにより、第1および第2の結晶性半導体膜はキャリア移動度の高い多結晶シリコンになる。これにより、優れた電気的特性を有する半導体素子を備えた半導体素子基板を製造することができる。

【0046】

上記第14の発明によれば、波長が370〜650nmのレーザビームに対する非晶質シリコン膜の吸収係数が小さいので、非晶質シリコン膜に照射されたレーザビームはその内部でほとんど吸収されることなく非晶質シリコン膜を透過する。このため、加熱促進層によって吸収または反射されるレーザビームのエネルギーは大きくなり、下方に加熱促進層が設けられた非晶質シリコン膜は、その裏面側から結晶化が促進されて第1の結晶性シリコン膜になる。これに対して、下方に加熱促進層が設けられていない非晶質シリコン膜は、下方に加熱促進層が設けられた非晶質シリコン膜よりもレーザビームによって与えられるエネルギーが実効的に小さくなり、第2の結晶性シリコン膜になる。このように、波長が370〜650nmのレーザビームを非晶質シリコン膜に照射することによって、第1の結晶性シリコン膜と第2の結晶性シリコン膜を分けて形成することができる。これにより、レーザ発振器のパワーやレーザビームの走査速度等の設定条件のマージンを大きくできるので、安定したレーザビームを非晶質シリコン膜に照射することができる。

【0047】

上記第15の発明によれば、第1および第2の半導体膜をパターニングすることによって、電気的特性が異なる第1および第2の薄膜トランジスタを製造することができる。

【0048】

上記第16の発明によれば、第1の発明から第15の発明のいずれかに係る製造方法によって製造された半導体素子基板には、結晶の配向が異なる第1の結晶性半導体膜を用いた半導体素子と第2の結晶性半導体膜を用いた半導体素子とが形成されている。これにより、電気的特性が異なる半導体素子を備えた半導体素子基板を得ることができる。

【0049】

上記第17の発明によれば、結晶の配向が異なる第1の結晶性半導体膜を用いた第1の薄膜トランジスタと、第2の結晶性半導体膜を用いた第2の薄膜トランジスタとが形成されている。これにより、電気的特性が異なる薄膜トランジスタを備えた半導体素子基板を得ることができる。

【0050】

上記第18の発明によれば、電気的特性が異なるトップゲート構造の第1および第2の薄膜トランジスタによって所望の電気的特性を実現可能な半導体素子基板を得ることができる。

【0051】

上記第19の発明によれば、第1の薄膜トランジスタはさらにダブルゲート構造の薄膜トランジスタを含むため、シングルゲート構造の薄膜トランジスタに比べてオン電流を大きくすることができる。また、加熱促進層をボトムゲート電極として用いるので、加熱促進層とは別に、ボトムゲート電極を形成する必要がない。これにより、ダブルゲート構造の薄膜トランジスタの構造を簡略化することができる。

【0052】

上記第20の発明によれば、電気的特性が異なる、ボトムゲート構造の第1の薄膜トランジスタと、トップゲート構造の第2の薄膜トランジスタとによって所望の電気的特性を実現可能な半導体素子基板を得ることができる。また、ボトムゲート構造の薄膜トランジスタでは、加熱促進層をボトムゲート電極として用いるので、加熱促進層とは別に、ボトムゲート電極を形成する必要がない。これにより、ダブルゲート構造の薄膜トランジスタの構造を簡略化することができる。

【0053】

上記第21の発明によれば、大きなチャネル領域を有する第1の薄膜トランジスタではキャリア移動度が大きくなる。また、小さなチャネル領域を有する第2の薄膜トランジスタでは、薄膜トランジスタ間の閾値電圧のばらつきが抑制される。このように電気的特性が異なる第1および第2の薄膜トランジスタが形成された半導体素子基板を用いて表示装置を構成することにより、所望の特性を有する表示装置を構成することができる。

【0054】

上記第22の発明によれば、周辺回路は、キャリア移動度の高い第1の薄膜トランジスタによって構成されており、画素回路は、薄膜トランジスタ間の閾値電圧のばらつきを抑制された第2の薄膜トランジスタによって構成されている。このように、周辺回路および画素回路は、最適な薄膜トランジスタによってそれぞれ構成されるので、輝度や色のばらつきが少なく、安定した表示が可能な表示装置を得ることができる。

【図面の簡単な説明】

【0055】

【図1】本発明の第1の実施形態に係る液晶表示装置の構成を示す平面図である。

【図2】上記実施形態に係る液晶表示装置のA−A線に沿った断面図である。

【図3】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板のブロック図である。

【図4】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成された周辺回路TFTと画素TFTの構成を示す断面図である。

【図5】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成された周辺回路TFTの構成を示す平面図である。

【図6】(a)〜(d)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図7】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図8】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

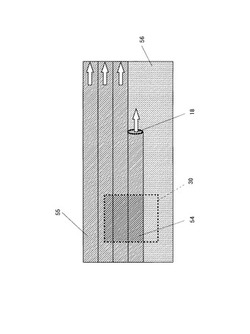

【図9】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の結晶化工程において、YAGレーザのレーザビームを照射して非晶質シリコン膜を結晶化する方法を示す図である。

【図10】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されるべき周辺回路TFTおよび画素TFTの領域における、第1の結晶性シリコン膜および第2の結晶性シリコン膜の形状を示す平面図である。

【図11】本発明の第2の実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成された周辺回路TFT、ダブルゲート周辺回路TFTおよび画素TFTの構成を示す断面図である。

【図12】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されるべき周辺回路TFT、ダブルゲート周辺回路TFT、および画素TFTの領域における第1の結晶性シリコン膜および第2の結晶性シリコン膜の形状を示す平面図である。

【図13】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されたダブルゲート周辺回路TFTの構成を示す平面図である。

【図14】(a)〜(d)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図15】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図16】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図17】本発明の第3の実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されたボトムゲート周辺回路TFTおよび画素TFTの構成を示す断面図である。

【図18】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されたボトムゲート周辺回路TFTの構成を示す平面図である。

【図19】(a)〜(d)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図20】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図21】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図22】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されるべきボトムゲート周辺回路TFTおよび画素TFTの領域における、第1の結晶性シリコン膜および第2の結晶性シリコン膜の形状を示す平面図である。

【発明を実施するための形態】

【0056】

以下、本発明の各実施形態を図面に基づいて詳細に説明する。なお、本明細書の実施形態では、半導体素子基板として液晶表示装置を構成するアクティブマトリクス基板を説明し、半導体素子基板に含まれる半導体素子としてTFTを説明する。なお、本発明は、以下の各実施形態に限定されるものではない。

【0057】

<1.第1の実施形態>

図1は、本発明の第1の実施形態に係る液晶表示装置1の構成を示す平面図であり、図2は、液晶表示装置1のA−A線に沿った断面図である。図3は、液晶表示装置1を構成するアクティブマトリクス基板100の構成を示すブロック図である。

【0058】

<1.1 液晶表示装置の構成>

図1および図2に示すように、液晶表示装置1は、矩形状のアクティブマトリクス基板100、アクティブマトリクス基板100と対向するように配置された矩形状の対向基板105、アクティブマトリクス基板100と対向基板105とを接着するために矩形枠状に形成されたシール材9、および、アクティブマトリクス基板100と対向基板105とシール材9とによって囲まれた空間に封入された液晶層12を備えている。

【0059】

アクティブマトリクス基板100と対向基板105の液晶層12側の各表面に配向膜11がそれぞれ形成され、液晶層12と反対側の各表面に偏光板10がそれぞれ貼り付けられている。液晶層12は、電気光学特性を有するネマチックの液晶材料等により構成されている。

【0060】

また、アクティブマトリクス基板100の液晶層12側の表面には、画像を表示するための表示領域6が設けられている。表示領域6は、画像を表示するために、その最小単位である画素回路をマトリクス状に複数個配列された領域である。なお、図1および図2では、画素回路の図示は省略されている。

【0061】

アクティブマトリクス基板100の表示領域6の周囲には額縁領域7が設けられ、対向基板105と重ならないアクティブマトリクス基板100の領域(図1の下端の領域)には、フレキシブルプリント配線基板(Flexible Printed Circuit、以下、「FPC」という)13を接続するための端子が配置された端子領域8が設けられている。画像を表示するための画像信号等は、外部からFPC13を介して液晶表示装置1に入力される。なお、図1では偏光板10および配向膜11の図示が省略されている。

【0062】

<1.2 アクティブマトリクス基板>

図3に示すように、アクティブマトリクス基板100の表示領域6には、互いに並行に延びるように配置されたn(nは1以上の整数)本のゲート配線GL1〜GLnと、層間絶縁膜を介して、各ゲート配線GL1〜GLnと交差する方向に互いに並行に延びるように配置されたm(mは1以上の整数)本のソース配線SL1〜SLmとが形成されている。ゲート配線GL1〜GLn(nは1以上の整数)とソース配線SL1〜SLmの各交点には、画素回路15が1個ずつ配置されている。

【0063】

画素回路15は、スイッチング素子として機能する画素TFT111と、画素TFT111のドレインに接続された画素電極(図示しない)とを有し、画素電極は共通電極Ecと共に画素容量Cpを形成する。画素TFT111のゲート電極はゲート配線GLi(iは1≦i≦nの整数)に接続され、ソース電極はソース配線SLj(jは1≦j≦mの整数)に接続されている。

【0064】

図1に示すように、アクティブマトリクス基板100の額縁領域7には、画素回路15を駆動するためのゲートドライバ4とソースドライバ5とが配置されている。ゲートドライバ4およびソースドライバ5は絶縁基板上に作り込まれたモノリシック回路であり、周辺回路に含まれる。なお、ゲートドライバ4およびソースドライバ5は、周辺回路TFTによって構成されているが、図3では、周辺回路TFTの図示が省略されている。また図2では、ゲートドライバ4およびソースドライバ5の図示が省略されている。

【0065】

対向基板105のガラス基板またはプラスチック基板等の絶縁基板上には、ゲート配線GL1〜GLnおよびソース配線SL1〜SLmに対応する位置に設けられたブラックマトリクスと、ブラックマトリクスによって囲まれた領域に、例えば赤色層、緑色層および青色層を含む複数色のカラーフィルタと、ブラックマトリクスおよびカラーフィルタを覆うように設けられた共通電極Ecと、アクティブマトリクス基板100と対向基板105との距離を一定に保つために共通電極Ec上に配置された柱状のフォトスペーサとが配置されている。なお、ブラックマトリクス、カラーフィルタ、およびフォトスペーサはいずれも図示されていない。

【0066】

<1.3 液晶表示装置の製造方法>

液晶表示装置1の製造方法について説明する。まず、アクティブマトリクス基板100および対向基板105をそれぞれ製造し、アクティブマトリクス基板100および対向基板105の表面に配向膜11をそれぞれ形成する。

【0067】

次に、これらの配向膜11が対向するように、アクティブマトリクス基板100と対向基板105とをシール材9によって貼り合わせる。シール材9の開口部から、アクティブマトリクス基板100と対向基板105とシール材9とによって囲まれた空間に液晶を注入し、液晶層12を形成する。次に、アクティブマトリクス基板100および対向基板105の配向膜11を形成した表面と反対側の表面に偏光板10をそれぞれ貼り付ける。アクティブマトリクス基板100に設けられた端子領域8の接続端子に、FPC13の接続端子を接続する。これにより、液晶表示装置1が製造される。

【0068】

なお、対向基板105の製造、配向膜11の形成、アクティブマトリクス基板100と対向基板105との貼り合せ、偏光板10の貼り付け、およびFPC13の接続は、公知の方法によって行なうので、本明細書では、それらの説明を省略する。

【0069】

<1.4 液晶表示装置の動作>

液晶表示装置1の動作について説明する。各画素回路15において、ゲートドライバ4からハイレベルのゲート電圧を、ゲート配線GLiを介して画素TFT111のゲート電極に与えて、画素TFT111をオン状態にする。このとき、ソースドライバ5から画像信号DVに応じた信号電圧がソース配線SLjに与えられ、信号電圧は画素TFT111を介して画素電極に書き込まれる。これにより、アクティブマトリクス基板100の各画素電極と対向基板105の共通電極Ecの間に電位差が生じ、液晶層12に信号電圧が印加される。液晶層12に印加された信号電圧によって液晶分子の配向状態が変わり、液晶層12の光透過率が変わる。このようにして、画像信号DVに応じた画像が液晶表示装置1の表示領域6に表示される。なお、ゲートドライバ4は制御信号CS1によって制御され、ソースドライバ5は制御信号CS2によって制御される。

【0070】

<1.5 周辺回路TFTおよび画素TFT>

図4は、アクティブマトリクス基板100に形成された周辺回路TFT110と画素TFT111の構成を示す断面図である。周辺回路TFT110は、アクティブマトリクス基板100の額縁領域7に形成されるゲートドライバ4やソースドライバ5を構成するためのTFTであり、画素TFT111は画素回路15のスイッチング素子として機能するTFTである。

【0071】

図4を参照して、まず周辺回路TFT110の構成を説明する。周辺回路TFT110は、絶縁基板20上に成膜されたベースコート膜40上に形成されている。ベースコート膜40は、絶縁基板20から周辺回路TFT110内に不純物が拡散しないようにするための絶縁膜である。また、絶縁基板20とベースコート膜40との間には、島状の加熱促進層30が設けられている。加熱促進層30が設けられている理由は後述する。

【0072】

加熱促進層30と対向するベースコート膜40上の位置に、島状の半導体層50が形成されている。半導体層50は、結晶異方性を有する結晶性シリコン層(以下、「第1の結晶性シリコン層」という)からなる。半導体層50の中央にチャネル領域50cが形成され、チャネル領域50cの両側にソース領域50sおよびドレイン領域50dがそれぞれ形成されている。チャネル領域50cは真性領域からなり、ソース領域50sおよびドレイン領域50dは、リン(P)等のn型不純物元素をイオン注入されたn型不純物領域からなる。ここで、結晶異方性を有する結晶性シリコン層とは、多結晶シリコンからなり、結晶の配向が特定の方向(具体的には、後述するレーザビームの走査方向)に揃っているシリコン層をいう。

【0073】

半導体層50を含む絶縁基板20を覆うようにゲート絶縁膜60が形成されている。半導体層50のチャネル領域50cと対向するゲート絶縁膜60上の位置に、ゲート電極70が形成されている。さらに、ゲート電極70を含む絶縁基板20を覆うように層間絶縁膜80が形成され、層間絶縁膜80上に引き出し電極90s,90dが形成されている。ゲート絶縁膜60および層間絶縁膜80には、半導体層50のソース領域50sおよびドレイン領域50dにそれぞれ達する2つのコンタクトホールが開孔されている。引き出し電極90s,90dは、これらのコンタクトホールを介して、ソース領域50sおよびドレイン領域50dにそれぞれオーミック接続されている。さらに、それらはパッシバーション膜(図示しない)によって覆われている。

【0074】

このような周辺回路TFT110のチャネル領域50cのサイズは大きく、例えば20×20μmである。

【0075】

次に、画素TFT111の構成について説明する。画素TFT111の構成要素のうち、周辺回路TFT110の構成要素と同じ構成要素には、同じ参照符号を付して、その説明を省略する。画素TFT111には、周辺回路TFT110に設けられていた加熱促進層は設けられていない。このため、ベースコート膜40は絶縁基板20上に形成されている。ベースコート膜40上に、島状の半導体層51が形成されている。半導体層51は、結晶異方性を有さない結晶性シリコン層(以下、「第2の結晶性シリコン層」という)からなる。半導体層51の中央にチャネル領域51cが形成され、チャネル領域51cの両側にソース領域51sおよびドレイン領域51dがそれぞれ形成されている。チャネル領域51cは真性領域からなり、ソース領域51sおよびドレイン領域51dはn型不純物領域からなる。ここで、結晶異方性を有さない結晶性シリコン層とは、平均結晶粒径が例えば約0.3μmΦの比較的小さな多結晶シリコンからなり、結晶の配向がランダムであるシリコン層をいう。このような画素TFT111のチャネル領域51cのサイズは小さく、例えば4×4μmである。

【0076】

画素TFT111は、周辺回路TFT110と同様に、半導体層51を覆うように形成されたゲート絶縁膜60と、ゲート絶縁膜60上に形成されたゲート電極70と、ゲート電極70を覆うように形成された層間絶縁膜80と、層間絶縁膜80上に形成された引き出し電極90s,90dとをさらに備えている。引き出し電極90s,90dは、コンタクトホールを介してソース領域51sおよびドレイン領域51dとそれぞれオーミック接続されている。さらに、それらはパッシバーション膜(図示しない)によって覆われている。

【0077】

なお、画素TFT111のゲート電極70はゲート配線に接続され、引き出し電極90sはソース配線に接続され、引き出し電極90dは画素電極に接続されている。これらのゲート配線、ソース配線および画素電極は、図4には示されていない。

【0078】

図5は、アクティブマトリクス基板100に形成された周辺回路TFT110の構成を示す平面図である。図5に示すように、半導体層50の下方に、半導体層50よりも大きな加熱促進層30が形成されている。このため、半導体層50は第1の結晶性シリコン層52のみからなる。また、ゲート電極70の下方の半導体層50にはチャネル領域(図示しない)が形成されている。また、チャネル領域の両側にはソース領域50sおよびドレイン領域50dが形成されており、引き出し電極90s,90dとそれぞれオーミック接続されている。なお、画素TFT111も、加熱促進層が形成されていないことを除いて、周辺回路TFT110と同様に構成されている。

【0079】

<1.6 レーザアニール法>

周辺回路TFT110および画素TFT111において、非晶質シリコン膜を結晶化して結晶性シリコン膜を形成する際に使用されるレーザアニール法について説明する。

【0080】

レーザアニール法に使用されるレーザビームは、発振方法の違いにより、パルス発振レーザと連続発振レーザとに大別される。パルス発振レーザは出力エネルギーが比較的高いので、ビームスポットの幅を広くして量産性を上げることができる。特に、ビームスポットの形状を、光学部材を用いて加工して長さ10cm以上の線状にすることにより、レーザビームの照射を効率的に行うことができるので、量産性を向上させることができる。

【0081】

また、パルス発振レーザの一種である擬似連続発振レーザも非晶質シリコン膜の結晶化に用いられる。この擬似連続発振レーザとは、レーザビームの走査方向(またはステージの移動方向)に結晶が連続的に成長するように、10MHz以上の高周波パルスを使用したレーザである。

【0082】

一方、連続発振レーザは、パルス発振レーザに比べて最大出力エネルギーが小さいので、ビームスポットのサイズが小さく、幅は数10μm程度から数mm程度である。このため、非晶質シリコン膜の結晶化には、ビームスポットの走査を複数回行なわなければならない。このことから、非晶質シリコン膜の結晶化には、パルス発振レーザが広く用いられていた。

【0083】

しかし、近年、非晶質シリコン膜の結晶化にCW(Continuous Wave)固体レーザ等の連続発振レーザを用いることにより、結晶性シリコン膜内の結晶粒径を大きくできることがわかった。

【0084】

このような連続発振レーザまたはパルス発振レーザの一種である擬似連続発振レーザのレーザビームの単位時間当たりの照射量を大きくすれば、非晶質シリコン膜を完全に溶融させ、レーザビームの走査方向に結晶を成長させることができる。レーザビームの走査方向に結晶が成長した結晶性シリコン膜では、キャリア移動度が大きくなるので、TFTの動作速度を向上させることができる。このように、連続発振レーザまたは擬似連続発振レーザを用いて非晶質シリコン膜を結晶化させれば、結晶はレーザビームを走査する方向(絶縁基板に対して横方向)に成長するので、レーザビームの走査方向に結晶の配向が揃った結晶性シリコン膜になる。そこで、本明細書では、このような結晶異方性を有する結晶性シリコン膜を第1の結晶性シリコン膜といい、第1の結晶性シリコン膜をパターニングしたシリコン層を、第1の結晶性シリコン層という。これに対して、結晶の配向がランダムで、結晶異方性を有さない結晶性シリコン膜を第2の結晶性シリコン膜といい、第2の結晶性シリコン膜をパターニングしたシリコン層を、第2の結晶性シリコン層という。

【0085】

チャネル長方向が第1の結晶性シリコン層の結晶成長方向と同じ方向になるように配置されたTFTでは、オン電流が大きくなるので、第1の結晶性シリコン層は周辺回路TFT110の半導体層50に適している。一方、画素TFT111のように、チャネル領域51cのサイズが小さなTFTでは、チャネル領域内の結晶粒界数または結晶粒界長のTFT間のばらつきが大きくなるので、TFT間の閾値電圧のばらつきも大きくなる。画素TFT111としては、キャリア移動度が多少小さくなっても、TFT間の閾値電圧のばらつきが小さなTFTが好ましい。このため、第2の結晶性シリコン層は画素TFT111の半導体層51に適している。

【0086】

<1.7 アクティブマトリクス基板の製造方法>

本実施形態のアクティブマトリクス基板100の製造方法を説明する。図6(a)〜図6(d)、図7(a)〜図7(c)、図8(a)〜図8(c)は、アクティブマトリクス基板100の各製造工程をそれぞれ示す断面図である。

【0087】

アクティブマトリクス基板100の製造工程には、加熱促進層形成工程と、絶縁膜形成工程と、非晶質半導体膜成膜工程と、結晶化工程とが含まれる。これらの工程により、周辺回路TFT110と画素TFT111の各半導体層50,51が結晶化される。

【0088】

<1.7.1 加熱促進層形成工程>

図6(a)に示すように、ガラス基板またはプラスチック基板等の絶縁基板20上に、スパッタリング法を用いて、例えば厚さが150nmのモリブデン(Mo)膜31を成膜する。次に、図5(b)に示すように、フォトリソグラフィ法を用いてモリブデン膜31をパターニングし、周辺回路TFT110を形成すべき領域に加熱促進層30を形成する。一方、画素TFT111を形成すべき領域には加熱促進層を形成しないので、モリブデン膜31を除去する。

【0089】

モリブデン膜からなる加熱促進層30は、後述する結晶化工程において、非晶質シリコン膜56に照射されたレーザビームを反射する。加熱促進層30によって反射されたレーザビームは、非晶質シリコン膜56の裏面に照射され、非晶質シリコン膜56を裏面側から結晶化する。なお、モリブデン膜31からなる加熱促進層30に代えて、レーザビームを吸収して発熱するタングステン(W)膜からなる加熱促進層を形成してもよい。また、加熱促進層30を、高融点金属であるモリブデン膜31またはタングステン膜を用いて形成することにより、結晶化工程において高温になっても加熱促進層30は溶融しにくくなる。

【0090】

このように、加熱促進層30は、非晶質シリコン膜56を透過したレーザビームを反射または吸収することにより、非晶質シリコン膜56の結晶化を促進させる機能を有する。すなわち、加熱促進層30を設けることにより、第1の結晶性シリコン膜54を形成すべき領域の非晶質シリコン膜56に照射されるレーザビームの照射量を、第2の結晶性シリコン膜55を形成すべき領域に照射されるレーザビームの照射量よりも実効的に大きくすることができる。

【0091】

ここで、加熱促進層30の膜厚が50nmよりも薄い場合には、後述する結晶化工程において非晶質シリコン膜56にレーザビームを照射したときに、加熱促進層30によるレーザビームの反射または吸収が不十分になる。この場合、レーザビームの実効的な照射量が十分大きくならないので、加熱促進層30およびその近傍の非晶質シリコン膜56は十分に溶融固化されず、結晶の配向はランダムになる。

【0092】

一方、加熱促進層30の膜厚が500nmよりも厚い場合には、レーザビームを照射したときに、加熱促進層30が設けられた領域と加熱促進層30が設けられていない領域との境界において、後述する層間絶縁膜80の表面に大きな段差が生じる。この段差によって、層間絶縁膜80の表面に形成される引き出し電極90s,90dは段切れする。そこで、加熱促進層30の膜厚は、50nm以上かつ500nm以下であることが好ましい。なお、引き出し電極90s,90dの段切れをさらに抑制するために、加熱促進層30の膜厚を50nm以上かつ300nm以下にすることがより好ましい。

【0093】

<1.7.2 絶縁膜形成工程>

図6(c)に示すように、加熱促進層30が形成された絶縁基板20上に、原料ガスとしてTEOS(Tetraethyl orthosilicate:Si(OC2H5)4)を用いたCVD(Chemical Vapor Deposition)法等により、例えば厚さが100nmの二酸化シリコン膜(SiO2)からなるベースコート膜40を成膜する。なお、ベースコート膜40は、二酸化シリコン膜の他に、窒化シリコン膜(SiN)、酸窒化シリコン膜(SiON)等であってもよく、またはこれらの膜を積層した積層絶縁膜であってもよい。

【0094】

ここで、ベースコート膜40の膜厚が30nmよりも薄い場合には、後述する第1および第2の結晶性シリコン膜54,55を、ドライエッチング法を用いて形成する際に、ベースコート膜40の一部がオーバーエッチングによって除去され、加熱促進層30の一部が露出する場合がある。この場合、その後の工程で形成される配線層が、露出した加熱促進層30と接触して不具合を生じさせる。一方、ベースコート膜40の膜厚が500nmよりも厚い場合には、後述する結晶化工程において非晶質シリコン膜56にレーザビームを照射したときに、加熱促進層30によるレーザビームの反射または吸収が不十分になる。この場合、加熱促進層30およびその近傍の非晶質シリコン膜56に照射されるレーザビームの照射量を実効的に大きくできないので、非晶質シリコン膜56は十分に溶融固化されず、結晶の配向はランダムになる。そこで、ベースコート膜40の膜厚は、30nm以上かつ500nm以下であることが好ましい。

【0095】

<1.7.3 非晶質半導体膜成膜工程>

図6(d)に示すように、ベースコート膜40を含む絶縁基板20を覆うように、例えば厚さが50nmの非晶質シリコン膜56を成膜する。非晶質シリコン膜56は、原料ガスとしてシランガス(SiH4)を用いたLPCVD(Low Pressure CVD)法等を用いて成膜される。

【0096】

<1.7.4 結晶化工程>

連続発振レーザであるYAGレーザ(イットリウム・アルミニウム・ガーネット(Yttrium Aluminum Garnet)レーザ(以下、「YAGレーザ」という)のレーザビームのビーム形状を、その長さ2mm、幅50μm程度の楕円状になるように成形し、レーザビームを非晶質シリコン膜56の表面に照射する。図9は、YAGレーザのレーザビーム18を照射して非晶質シリコン膜56を結晶化する方法を示す図である。図9に示すように、レーザビーム18を矢印で示す方向に速度20cm/secで走査しながら、非晶質シリコン膜56にYAGレーザの第2高調波(波長532nm)を照射する。このとき、レーザ発振器のパワーを1.2Wに設定する。第2高調波を照射することにより、加熱促進層30およびその近傍の上方に位置する非晶質シリコン膜56は第1の結晶性シリコン膜54になり、それ以外の領域の非晶質シリコン膜56は第2の結晶性シリコン膜55になる。このとき、第2の結晶性シリコン膜55の平均結晶粒径は約0.3μmΦである。

【0097】

結晶化工程において、非晶質シリコン膜56のYAGレーザの第2高調波に対する吸収係数は9.31×104cm-1程度と小さいので、照射された第2高調波の大部分は非晶質シリコン膜56を透過して、モリブデン膜からなる加熱促進層30に到達する。加熱促進層30に到達した第2高調波は加熱促進層30によって反射され、非晶質シリコン膜56を裏面側から照射する。一方、加熱促進層が設けられていない領域では、非晶質シリコン膜56を透過した第2高調波は、さらに絶縁基板20も透過して外部に逃げるので、非晶質シリコン膜56を裏面側から照射することはない。

【0098】

その結果、図7(a)に示すように、加熱促進層30およびその近傍の上方に位置する非晶質シリコン膜56に照射されるレーザビームの実効的な照射量が大きくなる。これにより、加熱促進層30およびその近傍の上方に位置する非晶質シリコン膜56は十分に溶融固化し、第1の結晶性シリコン膜54になる。一方、下方に加熱促進層が設けられていない非晶質シリコン膜56に照射されるレーザビームの実効的な照射量は大きくならないので、非晶質シリコン膜56は十分に溶融固化することができず、第2の結晶性シリコン膜55になる。

【0099】

なお、加熱促進層30がタングステン膜からなる場合には、非晶質シリコン膜56を透過したYAGレーザの第2高調波は、加熱促進層30に吸収されて熱エネルギーに変換される。これにより、非晶質シリコン膜56はその裏面側から加熱され、第1の結晶性シリコン膜54になる。

【0100】

また、加熱促進層30を設けることによって、YAGレーザの設定条件のマージンを大きくできるので、非晶質シリコン膜56に安定な第2高調波を照射することができる。また、YAGレーザ発振器は単純な構造であるので、メンテナンスが長期間不要になる。これにより、YAGレーザ発振器の稼働時間を長くして、ランニングコストを安価にすることができる。

【0101】

また、波長が370〜650nmのレーザビーム18を非晶質シリコン膜56に照射してもよい。波長が370〜650nmのレーザビーム18に対する非晶質シリコン膜の吸収係数は、YAGレーザの第2高調波(波長532nm)の場合と同様に小さい。このため、波長が370〜650nmのレーザビーム18を照射した場合にも、YAGレーザの第2高調波を照射した場合と同様の効果が得られる。

【0102】

また、レーザビーム18の走査速度を5cm/secよりも遅くすれば、非晶質シリコン膜56が過剰なエネルギーを受けて蒸発するため、良好な結晶性シリコン膜を形成することができない。一方、レーザビーム18の走査速度を3m/secよりも速くすれば、走査速度が速すぎて、非晶質シリコン膜56を確実に溶融固化することができない。そこで、レーザビーム18の走査速度は、5cm/sec以上かつ3m/sec以下であることが好ましい。

【0103】

このようにして、同一の絶縁基板20上に、結晶の配向および平均結晶粒径が異なる第1の結晶性シリコン膜54および第2の結晶性シリコン膜55が形成される。図10は、アクティブマトリクス基板100に形成されるべき周辺回路TFT110および画素TFT111の領域における、第1の結晶性シリコン膜54および第2の結晶性シリコン膜55の形状を示す平面図である。図10に示すように、周辺回路TFT110の半導体層50が形成されるべき領域の非晶質シリコン膜56はすべて第1の結晶性シリコン膜54になり、画素TFT111の半導体層51が形成されるべき領域の非晶質シリコン膜56はすべて第2の結晶性シリコン膜55になっている。次に、これらの第1の結晶性シリコン膜54および第2の結晶性シリコン膜55を用いて周辺回路TFT110および画素TFT111を形成する方法を説明する。

【0104】

図7(b)に示すように、第1の結晶性シリコン膜54および第2の結晶性シリコン膜55を、フォトリソグラフィ法を用いてパターニングする。これにより、第1の結晶性シリコン層52および第2の結晶性シリコン層53が形成される。次に、第1の結晶性シリコン層52と第2の結晶性シリコン層53を含む絶縁基板20を覆うように、例えば厚さが100nmの二酸化シリコン膜からなるゲート絶縁膜60を成膜する。ゲート絶縁膜60は、原料ガスとしてTEOS等を使用するAPCVD(Atmospheric Pressure CVD)法によって成膜される。なお、ゲート絶縁膜60は、二酸化シリコン膜の他に、窒化シリコン膜、酸窒化シリコン膜等であってもよく、またこれらの膜を適宜選択して積層した積層絶縁膜であってもよい。

【0105】

図7(c)に示すように、ゲート絶縁膜60上に、スパッタリング法を用いて、例えば厚さが300nmのアルミニウム(Al)膜71を成膜する。次に、図8(a)に示すように、フォトリソグラフィ法を用いてアルミニウム膜71をパターニングして、ゲート絶縁膜60上にゲート電極70を形成する。なお、ゲート電極70は、アルミニウム膜71の他に、例えば、タングステン膜、モリブデン膜、タンタル(Ta)膜、およびチタン(Ti)膜等の高融点金属膜や、これら高融点金属の窒化物膜等から形成してもよく、またこれらの膜から適宜選択して積層した積層金属膜から形成してもよい。また、ゲート電極70を形成する際に、ゲート配線(図示しない)も同時に形成する。

【0106】

図8(b)に示すように、ゲート電極70をマスクとして、第1の結晶性シリコン層52と第2の結晶性シリコン層53に、例えばリン(P)等のn型不純物元素をイオン注入し、電気炉で活性化アニールを行う。

【0107】

図8(c)に示すように、活性化アニールを行なうことにより、第1の結晶性シリコン層52のゲート電極70で覆われた領域には、真性領域であるチャネル領域50cが形成され、チャネル領域50cの両側にはn型不純物領域であるソース領域50sおよびドレイン領域50dがそれぞれ形成される。同様にして、第2の結晶性シリコン層53にも、チャネル領域51c、ソース領域51sおよびドレイン領域51dが形成される。次に、ゲート電極70を含む絶縁基板20を覆うように、APCVD法を用いて、例えば厚さが500nmの窒化シリコン膜からなる層間絶縁膜80を成膜する。次に、層間絶縁膜80およびゲート絶縁膜60に、第1の結晶性シリコン層52からなる半導体層50のソース領域50sおよびドレイン領域50dに達するコンタクトホール85と、第2の結晶性シリコン層53からなる半導体層51のソース領域51sおよびドレイン領域51dに達するコンタクトホール85とをそれぞれ開孔する。

【0108】

次に、層間絶縁膜80を含む絶縁基板20を覆うように、スパッタリング法を用いて、チタン膜、アルミニウム膜およびチタン膜を順に成膜した積層金属膜(図示しない)を形成する。図4に示すように、フォトリソグラフィ法を用いて積層金属膜をパターニングすることにより、層間絶縁膜80上に延びる引き出し電極90s,90dを形成する。これにより、引き出し電極90sは、コンタクトホール85を介して、ソース領域50s,51sと接続され、引き出し電極90dは、コンタクトホール85を介して、ドレイン領域50d,51dと接続される。さらにその後の熱処理によってそれらはオーミック接続される。なお、引き出し電極90s,90dを形成する際に、ソース配線(図示しない)も同時に形成する。

【0109】

これにより、図4に示す周辺回路TFT110および画素TFT111が形成される。なお、引き出し電極90s,90dは、チタン膜、アルミニウム膜およびチタン膜を順に積層した積層金属膜の他に、例えばタングステン膜、チタン膜、またはアルミニウム膜等の単層金属膜から形成してもよく、またはこれらの膜から適宜選択して積層した積層金属膜から形成してもよい。

【0110】

次に、引き出し電極90s,90dを含む絶縁基板20を覆うように、プラズマCVD法によって窒化シリコン膜からなるパッシベーション膜(図示しない)を成膜する。なお、画素TFT111では、さらに平坦化膜、透明導電膜、画素電極等が形成されるが、それらの図示および説明を省略する。

【0111】

このようにして、周辺回路TFT110および画素TFT111を含むアクティブマトリクス基板100が製造される。

【0112】

<1.8 効果>

本実施形態によれば、下方に加熱促進層30が設けられた非晶質シリコン膜56にレーザビームを照射するので、非晶質シリコン膜56に照射されるレーザビームの実効的な照射量は設定値よりも大きくなり、非晶質シリコン膜56は結晶の配向がレーザビームの走査方向に揃った第1の結晶性シリコン膜54になる。一方、下方に加熱促進層30が設けられていない非晶質シリコン膜56に、同じ照射量のレーザビームを照射しても、照射量は実効的に大きくならないので、非晶質シリコン膜56は結晶の配向がランダムな第2の結晶性シリコン膜55になる。

【0113】

また、レーザビームを反射または吸収して非晶質シリコン膜56の裏面側からの加熱を促進させるための加熱促進層30を形成し、非晶質シリコン膜56にレーザビームを照射する。加熱促進層30はレーザビームを反射または吸収して、加熱促進層30の上方およびその近傍の非晶質シリコン膜56を加熱する。これにより、下方に加熱促進層30が形成された非晶質シリコン膜56およびその近傍に照射されるレーザビームの照射量が実効的に大きくなるので、結晶の配向が揃った第1の結晶性シリコン膜54になる。このように加熱促進層30が形成される位置を精度よく制御して、第1の結晶性シリコン膜54が形成される位置を高い精度で制御することができる。また、第1の結晶性シリコン膜54の位置が決まると、結晶の配向がランダムな第2の結晶性シリコン膜55が形成される位置も決まる。その結果、第1および第2の結晶性シリコン膜54,55からなる周辺回路TFT110と画素TFT111とを例えば3μm程度の距離まで近接させて配置することができるので、これらを高集積化したアクティブマトリクス基板100を製造することができる。

【0114】

また、後述する実施例の評価結果から、第1の結晶性シリコン層52を用いて周辺回路TFT110を形成し、第2の結晶性シリコン層53を用いて画素TFT111を形成すれば、周辺回路TFT110のキャリア移動度の低下を抑制することができると共に、画素TFT111間の閾値電圧のばらつきを低減することができる。これにより、アクティブマトリクス基板100の電気的特性を所望の特性にすることができる。また、このようなアクティブマトリクス基板100を用いて構成された液晶表示装置1は、輝度や色のばらつきが少なく、安定した画像を表示することができる。

【0115】

<1.9 実施例>

本実施形態の製造方法により、以下に説明する作製方法で第1の結晶性シリコン層52と第2の結晶性シリコン層53を形成し、第1の結晶性シリコン層52を用いて周辺回路TFT110を、第2の結晶性シリコン層53を用いて画素TFT111をそれぞれ50個ずつ作製した。なお、画素TFT111のチャネル領域51cのサイズは4×4μmであり、周辺回路TFT110のチャネル領域50cのサイズは20×20μmである。

【0116】

<1.9.1 作製方法>

まず、ガラス基板上の周辺回路TFT110を形成すべき領域上に、厚さが150nmの加熱促進層30を形成した。次に、加熱促進層30を含むガラス基板を覆うように、ベースコート膜40を成膜した。このベースコート膜40は、厚さが100nmの二酸化シリコン膜からなる。ベースコート膜40上に、さらに厚さ50nmの非晶質シリコン膜56を成膜した。

【0117】

次に、ビーム形状を、長さ2mm、幅50μmの楕円状になるように成形したYAGレーザのレーザビームを図9の矢印で示す方向に20cm/secの速度で走査しながら、非晶質シリコン膜56にYAGレーザの第2高調波を照射した。このとき、YAGレーザの第2高調波を出力するレーザ発振器のパワーを1.2Wに設定した。これにより、図10に示すように、加熱促進層30およびその近傍の上方に位置する非晶質シリコン膜56は第1の結晶性シリコン膜54になり、それ以外の領域の非晶質シリコン膜56は第2の結晶性シリコン膜55になった。なお、第2の結晶性シリコン膜55の平均結晶粒径は約0.3μmφであった。

【0118】

次に、第1の結晶性シリコン膜54および第2の結晶性シリコン膜55をパターニングすることによって第1および第2の結晶性シリコン層52,53をそれぞれ形成した。次に、第1および第2の結晶性シリコン層52,53を覆うように、厚さが100nmの二酸化シリコン膜からなるゲート絶縁膜60を成膜した。ゲート絶縁膜60上に、厚さが100nmのアルミニウム膜71からなるゲート電極70を形成した。ゲート電極70をマスクにして、第1および第2の結晶性シリコン層52,53にリンをイオン注入した。これにより、第1の結晶性シリコン層52からなる半導体層50のゲート電極70で覆われた領域には、真性領域であるチャネル領域50cが形成され、チャネル領域50cの両側にはn型不純物領域であるソース領域50sおよびドレイン領域50dがそれぞれ形成された。同様にして、第2の結晶性シリコン層53からなる半導体層51にも、チャネル領域51c、ソース領域51sおよびドレイン領域51dが形成された。

【0119】

次に、厚さが500nmの二酸化シリコン膜からなる層間絶縁膜80を成膜した。層間絶縁膜80およびゲート絶縁膜60に、コンタクトホール85を開孔した。次に、これらのコンタクトホール85を介して、ソース領域50s,51sに電気的に接続された引き出し電極90sと、ドレイン領域50d,51dに電気的に接続された引き出し電極90dとを形成した。引き出し電極90s,90dは、厚さが100nmのチタン膜、厚さが300nmのアルミニウム膜、および厚さが100nmのチタン膜を順に積層した積層金属膜を用いて形成された。

【0120】

<1.9.2 評価>

上記作製方法によって作成したTFTの観察および各種の測定から、次のことがわかった。

【0121】

まず、第1および第2の結晶性シリコン膜54,55の結晶粒を後方拡散電子回折像法(Electron Backscatter Diffraction Patterns法、以下、「EBSP法」という)によって分析した。その結果、下方に加熱促進層30が設けられた非晶質シリコン膜56およびその近傍の非晶質シリコン膜56では、結晶の配向がレーザビームの走査方向に揃った結晶粒が観察された。また、下方に加熱促進層が設けられていない非晶質シリコン膜56では、結晶の配向がランダムな結晶粒が観察され、その平均粒径は約0.3μmφであった。このことから、結晶化工程により、下方に加熱促進層30が設けられた非晶質シリコン膜56およびその近傍の非晶質シリコン膜56は第1の結晶性シリコン膜54になり、下方に加熱促進層が設けられていない非晶質シリコン膜56は、第2の結晶性シリコン膜55になることがわかる。

【0122】

また、第1および第2の結晶性シリコン膜54,55をパターニングした半導体層50,51をそれぞれ有する周辺回路TFT110および画素TFT111について、キャリア移動度およびTFT間の閾値電圧のばらつきを測定した。その結果、周辺回路TFT110については、キャリア移動度は370cm2/V・secであり、50個分の閾値電圧のばらつきは0.15Vと大きくなった。一方、画素TFT111については、キャリア移動度は180cm2/V・secであり、50個分の閾値電圧のばらつきは0.05Vと、周辺回路TFT110の場合に比べて小さくなった。

【0123】

<2.第2の実施形態>

本発明の第2の実施形態に係る液晶表示装置の構成、製造方法、および動作は、第1の実施形態の係る液晶表示装置1の構成、製造方法、および動作とそれぞれ同じであるので、それらの図および説明を省略する。

【0124】

<2.1 ダブルゲート周辺回路TFT>

本実施形態に係るアクティブマトリクス基板200は、第1の実施形態に係るアクティブマトリクス基板100に設けられていた周辺回路TFT110および画素TFT111に加えて、さらにダブルゲート構造の周辺回路TFT210を備えている。ダブルゲート構造の周辺回路TFT210は、シングルゲート構造の周辺回路TFT110に設けられた加熱促進層30と同じ構造の加熱促進層130をボトムゲート電極としても使用するTFTであって、周辺回路TFT110と共に周辺回路を構成する。そこで、以下での説明では、ダブルゲート構造の周辺回路TFT210をダブルゲート周辺回路TFT210という。

【0125】

図11は、アクティブマトリクス基板200に形成された周辺回路TFT110、ダブルゲート周辺回路TFT210および画素TFT111の構成を示す断面図である。図11に示す周辺回路TFT110および画素TFT111の構成は、図4に示す第1の実施形態の周辺回路TFT110および画素TFT111とそれぞれ同じ構成である。そこで、周辺回路TFT110および画素TFT111の各構成要素には、図4に示す周辺回路TFT110および画素TFT111の各構成要素に付した参照符号と同じ参照符号を付して説明を省略する。また、ダブルゲート周辺回路TFT210の構成要素は、周辺回路TFT110の構成要素と一部異なっている。そこで、ダブルゲート周辺回路TFT210の構成要素のうち、周辺回路TFT110の構成要素と同じ構成要素には同じ参照符号を付し、異なる構成要素を中心に説明する。

【0126】

ダブルゲート周辺回路TFT210は、図4に示す周辺回路TFT110と異なり、周辺回路TFT110のチャネル領域50cを挟むように、チャネル領域50cの上方にゲート電極70が設けられ、下方にボトムゲート電極として機能する加熱促進層130が設けられている。

【0127】

ダブルゲート周辺回路TFT210が形成されるべき領域の絶縁基板20上に加熱促進層130が形成されている。加熱促進層130の大きさは、周辺回路TFT110が形成されるべき領域に形成された加熱促進層30よりも小さく、後述する半導体層150のチャネル領域150cよりも少し大きい程度である。この加熱促進層130は、完成後のダブルゲート周辺回路TFT210においては、後述するようにボトムゲート電極として機能する。加熱促進層130を含む絶縁基板20を覆うようにベースコート膜40が形成されている。ベースコート膜40は、ダブルゲート周辺回路TFT210の完成後にボトムゲート電極のゲート絶縁膜として機能する。

【0128】

ベースコート膜40上に島状の半導体層150が形成されている。半導体層150は、第1の結晶性シリコン層とその両側に形成された第2の結晶性シリコン層とからなり、第1の結晶性シリコン層の中央にチャネル領域150cが形成されている。チャネル領域150cの両側には、それぞれソース領域150sおよびドレイン領域150dが形成されている。チャネル領域150cは不純物元素を含まない真性領域からなり、ソース領域150sおよびドレイン領域150dはリン等のn型不純物元素をイオン注入されたn型不純物領域からなる。

【0129】

ダブルゲート周辺回路TFT210のソース領域150sおよびドレイン領域150dは、周辺回路TFT110のソース領域50sおよびドレイン領域50dと異なり、第1の結晶性シリコン層だけでなく、第2の結晶性シリコン層も含む。具体的には、ソース領域150sおよびドレイン領域150dのチャネル領域150cに隣接する一部は、第1の結晶性シリコン層からなり、残りの大部分は第2の結晶性シリコン層からなる。このようになる理由について説明する。

【0130】

図12は、アクティブマトリクス基板200に形成されるべき周辺回路TFT110、ダブルゲート周辺回路TFT210、および画素TFT111の領域における第1の結晶性シリコン膜54および第2の結晶性シリコン膜55の形状を示す平面図である。図12に示すように、周辺回路TFT110の第1の結晶性半導体層となるべき非晶質シリコン膜の全体が加熱促進層30の上方に形成されている。このため、照射されるレーザビームだけでなく、加熱促進層30による反射または加熱により、加熱促進層30上の非晶質シリコン膜は溶融固化して結晶の配向が揃った第1の結晶性シリコン膜54になる。

【0131】

一方、ダブルゲート周辺回路TFT210では、非晶質シリコン膜のうち、チャネル領域およびその近傍のみが加熱促進層130の上方に形成され、ソース領域およびドレイン領域の下方には加熱促進層が設けられていない。このような非晶質シリコン膜にレーザビームを照射すれば、溶融固化して第1の結晶性シリコン膜54になるのはチャネル領域になるべき領域と、チャネル領域に隣接するソース領域およびドレイン領域になるべき領域の一部であり、ソース領域およびドレイン領域になるべき領域の大部分は、第2の結晶性シリコン膜55になる。その結果、ソース領域150sおよびドレイン領域150dのチャネル領域150cに隣接する一部は、第1の結晶性シリコン膜54からなり、残りの大部分は第2の結晶性シリコン膜55からなる。なお、画素TFT111が形成されるべき領域の下方には、加熱促進層が形成されていないので、非晶質シリコン膜は第2の結晶性シリコン膜55になる。

【0132】

図11に示すように、半導体層150を含む絶縁基板20を覆うようにゲート絶縁膜60が形成されている。さらに、半導体層150のチャネル領域150cと対向するゲート絶縁膜60上の位置にゲート電極70が形成されている。ゲート電極70は後述するコンタクトホール75を介して加熱促進層130と電気的に接続されている。これにより、加熱促進層130もゲート電極(ボトムゲート電極)として機能し、ゲート電圧がゲート電極70および加熱促進層130によってチャネル領域150cに印加される。

【0133】

層間絶縁膜80、引き出し電極90s,90dの構成は、周辺回路TFT110の場合と同じであるため、それらの説明を省略する。ダブルゲート周辺回路TFT210のチャネル領域150cのサイズは、周辺回路TFT110のサイズと同じく、例えば20×20μmである。

【0134】

図13は、アクティブマトリクス基板200に形成されたダブルゲート周辺回路TFT210の構成を示す平面図である。図13に示すように、半導体層150のチャネル領域150cを上下から挟むように加熱促進層130とゲート電極70が形成されている。また半導体層150のソース領域150sおよびドレイン領域150dには、引き出し電極90s,90dがそれぞれオーミック接続されている。

【0135】

このようなダブルゲート周辺回路TFT210において、加熱促進層130とゲート電極70とは、チャネル領域150cとなるべき領域の外側(図13の上方)に形成されたコンタクトホール75によって接続されている。これにより、ゲート電極70にゲート電圧を印加すれば、コンタクトホール75を介して加熱促進層130にも同じゲート電圧が印加され、加熱促進層130がボトムゲート電極として機能する。また、加熱促進層130の上方に形成されたチャネル領域150cおよびその近傍は第1の結晶性シリコン層52によって構成され、ソース領域150sおよびドレイン領域150dは第1の結晶性シリコン層52と第2の結晶性シリコン層53とによって構成されている。

【0136】

<2.2 アクティブマトリクス基板の製造方法>

次に、アクティブマトリクス基板200の製造方法を説明する。図14(a)〜図14(d)、図15(a)〜図15(c)、図16(a)〜図16(c)は、アクティブマトリクス基板200の各製造工程をそれぞれ示す断面図である。アクティブマトリクス基板200の製造工程には、第1の実施形態の場合と同様に、加熱促進層形成工程と、絶縁膜形成工程と、非晶質半導体膜成膜工程と、結晶化工程とが含まれる。これらの工程により、周辺回路TFT110と、ダブルゲート周辺回路TFT210と、画素TFT111の各半導体層50,150,51が結晶化される。なお、周辺回路TFT110および画素TFT111については第1の実施形態の場合と同じ参照符号を付してその説明を簡略に行ない、ダブルゲート周辺回路TFT210の製造工程を中心に第1の実施形態の各製造工程と比較しつつ説明する。

【0137】

<2.2.1 加熱促進層形成工程>

図14(a)に示す工程は、図6(a)に示す第1の実施形態の工程に対応する工程である。絶縁基板20上に、例えば厚さが150nmのモリブデン膜31を成膜する。次に、図14(b)に示すように、モリブデン膜31を、フォトリソグラフィ法を用いてパターニングし、ダブルゲート周辺回路TFT210が形成されるべき領域に加熱促進層130を形成する。この加熱促進層130は、周辺回路TFT110が形成されるべき領域に形成される加熱促進層30よりも小さい。この加熱促進層130は、ダブルゲート周辺回路TFT210の完成後には、そのボトムゲート電極として機能する。

【0138】

<2.2.2 絶縁膜形成工程>

図14(c)に示す工程は、図6(c)に示す第1の実施形態の工程に対応する工程である。加熱促進層130を含む絶縁基板20を覆うように、例えば厚さが100nmの二酸化シリコン膜からなるベースコート膜40を成膜する。ベースコート膜40は、プラズマCVD法等を用いて成膜される。

【0139】

<2.2.3 非晶質半導体膜成膜工程>

図14(d)に示す工程は、図6(d)に示す第1の実施形態の工程に対応する工程である。ベースコート膜40上に、例えば厚さ50nmの非晶質シリコン膜56を成膜する。非晶質シリコン膜56は、原料ガスとしてシランガス(SiH4)を用いたLPCVD(Low Pressure CVD)法等を用いて成膜される。

【0140】

<2.2.4 結晶化工程>

図15(a)に示す工程は、図7(a)に示す第1の実施形態の工程に対応する工程である。YAGレーザの第2高調波を非晶質シリコン膜56に照射し、非晶質シリコン膜56を溶融固化して結晶化する。なお、YAGレーザのビーム形状および走査速度は第1の実施形態の場合と同じである。これにより、加熱促進層130の上方およびその近傍の領域の非晶質シリコン膜56は第1の結晶性シリコン膜54になり、それ以外の領域の非晶質シリコン膜56は、第2の結晶性シリコン膜55になる。

【0141】

ダブルゲート周辺回路TFT210の加熱促進層130は、周辺回路TFT110の加熱促進層30よりも小さい。このため、図12に示すように、ダブルゲート周辺回路TFT210が形成されるべき領域の第1の結晶性シリコン膜54は、周辺回路TFT110が形成されるべき領域の第1の結晶性シリコン膜54よりも小さくなる。また、画素TFT111が形成されるべき領域には、加熱促進層が形成されていない。このため、非晶質シリコン膜56はすべて第2の結晶性シリコン膜55になる。このようにして、同一の絶縁基板20上に、結晶の配向および平均結晶粒径が異なる第1の結晶性シリコン膜54および第2の結晶性シリコン膜55が形成される。

【0142】

図15(b)に示す工程は、図7(b)に示す第1の実施形態の工程に対応する工程である。図15(b)に示すように、第1の結晶性シリコン膜54および第2の結晶性シリコン膜55を、フォトリソグラフィ法を用いてパターニングすることにより、ダブルゲート周辺回路TFT210の第1および第2の結晶性シリコン層152,153を形成する。このとき、同時に周辺回路TFT110の第1の結晶性シリコン層52、および画素TFT111の第2の結晶性シリコン層53も形成される。次に、ダブルゲート周辺回路TFT210の第1および第2の結晶性シリコン層152,153を含む絶縁基板20を覆うように、例えば厚さが100nmのゲート絶縁膜60を成膜する。

【0143】

さらに、フォトリソグラフィを用いて、ダブルゲート周辺回路TFT210についてのみ、ベースコート膜40とゲート絶縁膜60にコンタクトホール75を開孔する。コンタクトホール75を開孔する位置は、加熱促進層130と後述するゲート電極70とがベースコート膜40およびゲート絶縁膜60を挟んで重なる領域であり、例えば第1の結晶性シリコン層152の外側(図13の上側)の加熱促進層130の上方の位置である。なお、図15(b)にはコンタクトホールは示されていない。

【0144】

図15(c)に示す工程は、図7(c)に示す第1の実施形態の工程に対応する工程である。図15(c)に示すように、ゲート絶縁膜60を含む絶縁基板20を覆うように、スパッタリング法を用いて、例えば厚さが300nmのアルミニウム膜71を成膜する。このとき、コンタクトホール75内にアルミニウム膜71が充填される。

【0145】

図16(a)に示す工程は、図8(a)に示す第1の実施形態の工程に対応する工程である。図16(a)に示すように、フォトリソグラフィ法を用いてアルミニウム膜71をパターニングすることにより、ゲート絶縁膜60上にゲート電極70を形成する。これにより、ダブルゲート周辺回路TFT210にもトップゲート電極として機能するゲート電極70が形成される。また、加熱促進層130はコンタクトホール75を介してゲート電極70と電気的に接続される。

【0146】

図16(b)に示す工程は、図8(b)に示す第1の実施形態の工程に対応する工程である。図16(b)に示すように、ダブルゲート周辺回路TFT210の第1および第2の結晶性シリコン層152,153に、ゲート電極70をマスクとして、n型不純物元素をイオン注入し、電気炉で活性化アニールを行う。

【0147】

図16(c)に示す工程は、図8(c)に示す第1の実施形態の工程に対応する工程である。活性化アニールを行うことにより、ダブルゲート周辺回路TFT210の半導体層150にも、ソース領域150sおよびドレイン領域150dが形成されると共に、ゲート電極70で覆われた領域にチャネル領域150cが形成される。また、チャネル領域150cの全体およびソース領域150sとドレイン領域150dの一部は第1の結晶性シリコン層52からなり、ソース領域150sとドレイン領域150dの大部分は第2の結晶性シリコン層53からなる。次に、ゲート電極70を含む絶縁基板20を覆うように、厚さ500nmの層間絶縁膜80を成膜する。層間絶縁膜80およびゲート絶縁膜60をエッチングする。これにより、ダブルゲート周辺回路TFT210にも、層間絶縁膜80およびゲート絶縁膜60にソース領域150sおよびドレイン領域150dに達するコンタクトホール85がそれぞれ形成される。

【0148】

次に、層間絶縁膜80を含む絶縁基板20を覆うように、スパッタリング法を用いて、チタン膜、アルミニウム膜およびチタン膜を順に成膜した積層金属膜(図示しない)を形成する。図11に示すように、フォトリソグラフィ法を用いて積層金属膜をパターニングすることにより、層間絶縁膜上に延びる引き出し電極90s,90dを形成する。これにより、ダブルゲート周辺回路TFT210においても、引き出し電極90sは、コンタクトホール85を介して、ソース領域150sと接続され、引き出し電極90dは、コンタクトホール85を介して、ドレイン領域150dと接続される。さらにその後の熱処理によってそれらはオーミック接続される。なお、引き出し電極90s,90dを形成する際に、ソース配線(図示しない)も同時に形成する。

【0149】

これにより、図11に示す周辺回路TFT110、ダブルゲート周辺回路TFT210および画素TFT111が形成される。なお、引き出し電極90s,90dは、チタン膜、アルミニウム膜およびチタン膜を順に積層した積層金属膜の他に、例えばタングステン膜、チタン膜、またはアルミニウム膜等の単層金属膜から形成してもよく、またはこれらの膜から適宜選択して積層した積層金属膜から形成してもよい。

【0150】

次に、引き出し電極90s,90dを含む絶縁基板20を覆うように、プラズマCVD法によって窒化シリコン膜からなるパッシベーション膜(図示しない)を成膜する。なお、画素TFT111では、さらに平坦化膜、透明導電膜、画素電極等が形成されるが、それらの図示および説明を省略する。

【0151】

このようにして、周辺回路TFT110、ダブルゲート周辺回路TFT210および画素TFT111を含むアクティブマトリクス基板200が製造される。

【0152】

<2.3 効果>

本実施形態によれば、ダブルゲート周辺回路TFT210においても、周辺回路TFT110および画素TFT111の場合と同様に、下方に加熱促進層130が設けられた領域およびその近傍の非晶質シリコン膜56にレーザビームを照射すれば、非晶質シリコン膜56に照射されるレーザビームの実効的な照射量は設定値よりも大きくなる。これにより、非晶質シリコン膜56は結晶の配向が揃った第1の結晶性シリコン膜154になる。一方、下方に加熱促進層が設けられていない領域の非晶質シリコン膜56に、同じ設定値のレーザビームを照射しても、照射量は実効的に大きくならないので、非晶質シリコン膜56は結晶の配向がランダムな第2の結晶性シリコン膜155になる。

【0153】

また、第1の実施形態の場合と同様に、ダブルゲート周辺回路TFT210においても、加熱促進層130の位置を制御することにより、第1の結晶性シリコン膜154の位置を精度よく制御することができる。これにより、周辺回路TFT110またはダブルゲート周辺回路TFT210と、画素TFT111とを例えば3μm程度の距離まで近接させて配置することができる。その結果、周辺回路TFT110、ダブルゲート周辺回路TFT210および画素TFT111を高集積化したアクティブマトリクス基板200を製造することができる。

【0154】

また、ダブルゲート周辺回路TFT210のチャネル領域150cの形状およびサイズは、シングルゲート構造である周辺回路TFT110の形状およびサイズと同じである。しかし、そのオン電流値は周辺回路TFT110の約1.4倍になるため、ダブルゲート周辺回路TFT210を高い駆動能力が必要とされる回路に配置することができる。

【0155】

また、完成後のダブルゲート周辺回路TFT210では、加熱促進層130はボトムゲート電極として機能し、トップゲート電極として機能するゲート電極70と共に、ダブルゲート構造になる。このように、ダブルゲート周辺回路TFT210を形成する場合、加熱促進層130とは別に、ボトムゲート電極を形成する必要がない。この場合、ダブルゲート周辺回路TFT210の製造工程において、加熱促進層130とゲート電極70とを電気的に接続するために必要なコンタクトホール75を開孔する工程を追加するだけでよい。その結果、ダブルゲート周辺回路TFT210の製造工程を簡略化することができる。

【0156】

また、後述する実施例の評価結果から、周辺回路TFT110の場合と同様に、ダブルゲート周辺回路TFT210も第1の結晶性シリコン層52を用いて形成されるので、キャリア移動度が高くなる。また、第1の実施形態の場合と同様に、画素TFT111においてもTFT間の閾値電圧のばらつきを低減することができる。これにより、アクティブマトリクス基板200の電気的特性を所望の特性にすることができる。また、このようなアクティブマトリクス基板200を用いて構成された液晶表示装置は、輝度や色のばらつきが少なく、安定した画像を表示することができる。

【0157】

<2.4 実施例>

本実施形態の製造方法を用いて、以下に説明する作成方法でダブルゲート周辺回路TFT210、周辺回路TFT110、および画素TFT111をそれぞれ50個ずつ作製した。なお、ダブルゲート周辺回路TFT210および周辺回路TFT110のチャネル領域150c,50cのサイズはいずれも20×20μmであり、画素TFT111のチャネル領域51cのサイズは4×4μmである。

【0158】

<2.4.1 作製方法>

周辺回路TFT110および画素TFT111の作製方法は第1の実施形態の実施例において説明した作成方法と同じである。また、ダブルゲート周辺回路TFT210の作製方法は、一部の工程を除いて周辺回路TFT110と同じである。そこで、ダブルゲート周辺回路TFT210の作製方法について、周辺回路TFT110の場合と異なる工程を中心に説明する。なお、各膜の膜厚は第1の実施形態の実施例の場合と同じであるので、以下の説明では省略する。

【0159】

まず、ガラス基板上の周辺回路TFT110を形成すべき領域上に、加熱促進層30を形成した。ダブルゲート周辺回路TFT210が形成されるべき領域に形成された加熱促進層130のサイズは、周辺回路TFT110が形成されるべき領域に形成された加熱促進層30よりも小さい。次に、加熱促進層30,130を含むガラス基板を覆うように、ベースコート膜40を成膜した。ベースコート膜40上に、さらに非晶質シリコン膜56を成膜した。

【0160】

次に、非晶質シリコン膜56にYAGレーザを照射した。これにより、非晶質シリコン膜56は溶融固化して結晶化する。図12に示すように、ダブルゲート周辺回路TFT210では、加熱促進層130およびその近傍の上方に位置する非晶質シリコン膜56は第1の結晶性シリコン膜54になり、それ以外の領域の非晶質シリコン膜56は第2の結晶性シリコン膜55になった。このとき、加熱促進層130は、加熱促進層30に比べて小さいので、ダブルゲート周辺回路TFT210の第1の結晶性シリコン膜54は、周辺回路TFT110の第1の結晶性シリコン膜54よりも小さくなる。

【0161】

次に、ダブルゲート周辺回路TFT210でも、第1および第2の結晶性シリコン膜54,55をパターニングして第1および第2の結晶性シリコン層152,153を形成し、それらを覆うようにゲート絶縁膜60を成膜した。次に、ダブルゲート周辺回路TFT210についてのみ、第1の結晶性シリコン層152の外側のゲート絶縁膜60およびベースコート膜40に、加熱促進層130に達するコンタクトホール75を開孔し、アルミニウム膜71を成膜した。次に、アルミニウム膜71をパターニングして、ゲート絶縁膜60上にゲート電極70を形成した。このとき、ダブルゲート周辺回路TFT210では、ゲート電極70がコンタクトホール75を介して加熱促進層130と電気的に接続された。

【0162】

次に、ゲート電極70をマスクにしてイオン注入を行なうことにより、ダブルゲート周辺回路TFT210にも、チャネル領域150c、ソース領域150s、およびドレイン領域150dを形成した。さらに層間絶縁膜80を成膜し、層間絶縁膜80に開孔したコンタクトホール85を介して、ソース領域150sおよびドレイン領域150dと電気的に接続された引き出し電極90s,90dを形成した。

【0163】

<2.4.2 評価>

上記作製方法によって作成したTFTの観察および各種の測定から、次のことがわかった。

【0164】

まず、第1の実施形態の場合と同様に、ダブルゲート周辺回路TFT210でも、下方に加熱促進層130が設けられた領域およびその近傍では、レーザビームの走査方向に結晶の配向が揃った結晶粒が観察された。また、下方に加熱促進層が設けられていない領域では、結晶の配向がランダムな結晶粒が観察され、その平均粒径は約0.3μmφであった。このことから、結晶化工程により、下方に加熱促進層130が設けられた領域およびその近傍では、第1の結晶性シリコン膜54が形成され、加熱促進層が設けられていない領域では、第2の結晶性シリコン膜55が形成されたことがわかる。

【0165】

また、ダブルゲート周辺回路TFT210および周辺回路TFT110について、キャリア移動度およびTFT間の閾値電圧のばらつきを測定した。その結果、周辺回路TFT110のキャリア移動度は370cm2/V・secであり、またオン電流値は1.0×10-5Aであった。これに対し、ダブルゲート周辺回路TFT210のオン電流値は1.4×10-5Aであり、この値は周辺回路TFT110のオン電流値の1.4倍であった。また、画素TFT111については、キャリア移動度は180cm2/V・secであり、50個分の閾値電圧のばらつきは0.05Vと比較的小さくなった。

【0166】

<3.第3の実施形態>

本発明の第3の実施形態に係る液晶表示装置の構成、製造方法、および動作は、第1の実施形態の係る液晶表示装置1の構成、製造方法、および動作とそれぞれ同じであるので、それらの図および説明を省略する。

【0167】

<3.1 ボトムゲート周辺回路TFT>

本実施形態に係るアクティブマトリクス基板300には、第1の実施形態に係るアクティブマトリクス基板100に形成されていたトップゲート構造の周辺回路TFT110に代えて、ボトムゲート構造の周辺回路TFT310(以下、「ボトムゲート周辺回路TFT310」という)が形成されている。これにより、アクティブマトリクス基板300は、ボトムゲート周辺回路TFT310と画素TFT111を備えている。ボトムゲート周辺回路TFT310は、加熱促進層230をボトムゲート電極としても使用するTFTであって、周辺回路を構成するために使用される。

【0168】

図17は、アクティブマトリクス基板300に形成されたボトムゲート周辺回路TFT310および画素TFT111の構成を示す断面図である。図17に示す画素TFT111の構成は、図4に示す第1の実施形態の画素TFT111と同じ構成である。そこで、画素TFT111の各構成要素には、図4に示す画素TFT111の各構成要素に付した参照符号と同じ参照符号を付して説明を省略する。また、ボトムゲート周辺回路TFT310の構成要素は、周辺回路TFT110またはダブルゲート周辺回路TFT210の構成要素と一部異なっている。そこで、ボトムゲート周辺回路TFT310の構成要素のうち、周辺回路TFT110またはダブルゲート周辺回路TFT210の構成要素と同じ構成要素にはそれらと同じ参照符号を付し、異なる構成要素を中心に説明する。

【0169】

ボトムゲート周辺回路TFT310は、図4に示す周辺回路TFT110と異なり、半導体層250の上方にゲート電極は設けられていない。その代わりに、半導体層250の下方に設けられた加熱促進層230がボトムゲート電極として機能するボトムゲート構造の周辺回路TFT310である。

【0170】

ボトムゲート周辺回路TFT310が形成されるべき領域の絶縁基板20上に加熱促進層230が形成されている。加熱促進層230は、第2の実施形態のボトムゲート周辺回路TFT310の加熱促進層130と同じ大きさである。この加熱促進層230は、ボトムゲート周辺回路TFT310の完成後には、後述するようにゲート電極(ボトムゲート電極)として機能する。加熱促進層230を含む絶縁基板20を覆うようにベースコート膜40が形成されている。ベースコート膜40は、ボトムゲート周辺回路TFT310の完成後にゲート絶縁膜として機能する。

【0171】

加熱促進層230と対向するベースコート膜40上の位置に島状の半導体層250が形成されている。半導体層250は、第1の結晶性シリコン層と第2の結晶性シリコン層とからなり、第1の結晶性シリコン層の中央にチャネル領域250cが形成されている。チャネル領域250cの両側には、それぞれソース領域250sおよびドレイン領域250dが形成されている。チャネル領域250cは不純物元素を含まない真性領域からなり、ソース領域250sおよびドレイン領域250dはリン等のn型不純物元素をイオン注入されたn型不純物領域からなる。

【0172】

ソース領域250sおよびドレイン領域250dは、ダブルゲート周辺回路TFT210のソース領域150sおよびドレイン領域150dと同様に、第1の結晶性シリコン層だけでなく、第2の結晶性シリコン層も含む。具体的には、ソース領域250sおよびドレイン領域250dのチャネル領域250cに隣接する一部は、第1の結晶性シリコン層からなり、残りの大部分は第2の結晶性シリコン層からなる。

【0173】

ボトムゲート周辺回路TFT310でも、半導体層250を含む絶縁基板20を覆うように、画素TFT111のゲート絶縁膜60と同じ膜厚の絶縁膜65が形成されている。しかし、周辺回路TFT110の場合と異なり、絶縁膜65上にゲート電極は形成されていない。

【0174】

層間絶縁膜80、引き出し電極90s,90dの構成は、周辺回路TFT110の場合と同じであるため、それらの説明を省略する。ボトムゲート周辺回路TFT310のチャネル領域250cのサイズは、周辺回路TFT110と同じ、例えば20×20μmである。

【0175】

図18は、アクティブマトリクス基板300に形成されたボトムゲート周辺回路TFT310の構成を示す平面図である。図18に示すように、加熱促進層230上に半導体層250のチャネル領域250cが形成され、チャネル領域250cの外側(図18の上側)の加熱促進層230に、ゲート電極にゲート電圧を与えるための配線層276が形成されている。また半導体層250のソース領域250sおよびドレイン領域250dには、それぞれ引き出し電極90s,90dがオーミック接続されている。加熱促進層230の上方に形成されたチャネル領域250cおよびその近傍は第1の結晶性シリコン層からなるが、ソース領域250sおよびドレイン領域250dの大部分は第2の結晶性シリコン層からなり、一部は第1の結晶性シリコン層からなる。

【0176】

このようなボトムゲート周辺回路TFT310は、配線層276を介して加熱促進層230にゲート電圧を印加することにより、オン状態とオフ状態を切り替えることができる。

【0177】

<3.2 アクティブマトリクス基板の製造方法>

次に、アクティブマトリクス基板300の製造方法を説明する。図19(a)〜図19(d)、図20(a)〜図20(c)、図21(a)〜図21(c)は、アクティブマトリクス基板300の各製造工程をそれぞれ示す断面図である。なお、画素TFT111の構成要素には、第1の実施形態の画素TFT111の構成要素と同じ参照符号を付してその説明を簡単に行ない、ボトムゲート周辺回路TFT310の製造工程を中心に、第1または第2の実施形態の各製造工程と比較しつつ説明する。

【0178】

アクティブマトリクス基板300の製造工程には、第2の実施形態の場合と同様に、加熱促進層形成工程と、絶縁膜形成工程と、非晶質半導体膜成膜工程と、結晶化工程とが含まれる。図19(a)〜図19(d)および図20(a)に示すように、これらの工程によって、ボトムゲート周辺回路TFT310および画素TFT111が形成されるべき領域に第1および第2の結晶性シリコン膜54,55が形成される。

【0179】

図22は、アクティブマトリクス基板300に形成されるべきボトムゲート周辺回路TFT310および画素TFT111の領域における、第1の結晶性シリコン膜54および第2の結晶性シリコン膜55の形状を示す平面図である。図22に示すように、ボトムゲート周辺回路TFT310では、チャネル領域になるべき非晶質シリコン膜56の下方にのみ加熱促進層230が設けられ、ソース領域およびドレイン領域になるべき非晶質シリコン膜の下方には加熱促進層が設けられていない。このような非晶質シリコン膜にレーザビームを照射すれば、溶融固化して第1の結晶性シリコン膜54になるのは、加熱促進層230の上方のチャネル領域になるべき領域と、ソース領域およびドレイン領域になるべき領域の一部であり、ソース領域およびドレイン領域になるべき領域の大部分は第2の結晶性シリコン膜55になる。これにより、半導体層250は、第1の結晶性シリコン膜54と第2の結晶性シリコン膜55とからなる。なお、画素TFT111が形成されるべき領域の下方には、加熱促進層が形成されていないので、非晶質シリコン膜はすべて第2の結晶性シリコン膜55になる。このため、半導体層51も第2の結晶性シリコン膜55だけからなる。

【0180】

図20(b)は、図7(b)に示す第1の実施形態の工程に対応する工程である。図20(b)に示すように、第1および第2の結晶性シリコン膜54,55を、フォトリソグラフィ法を用いてエッチングする。これにより、ボトムゲート周辺回路TFT310では、加熱促進層230の上方およびその近傍に第1の結晶性シリコン層252が形成され、第1の結晶性シリコン層252の両側に第2の結晶性シリコン層253が形成される。また、画素TFT111では第2の結晶性シリコン層53が形成される。次に、ボトムゲート周辺回路TFT310にも、第1および第2の結晶性シリコン層252,253を含む絶縁基板20を覆うように絶縁膜65(画素TFT111のゲート絶縁膜60と同じ膜厚の二酸化シリコン膜)を成膜する。

【0181】

図20(c)は、図7(c)に示す第1の実施形態の工程に対応する工程である。図20(c)に示すように、ボトムゲート周辺回路TFT310でも、絶縁膜65上にアルミニウム膜71を成膜する。

【0182】

図21(a)は、図8(a)に示す第1の実施形態の工程に対応する工程である。図21(a)に示すように、フォトリソグラフィ法を用いて、アルミニウム膜71をパターニングする。これにより、画素TFT111のゲート絶縁膜60上にゲート電極70が形成される。しかし、ボトムゲート周辺回路TFT310の絶縁膜65上のアルミニウム膜71は除去されるので、ゲート電極は形成されない。

【0183】

図21(b)は、図8(b)に示す第1の実施形態の工程に対応する工程である。図21(b)に示すように、フォトリソグラフィ法を用いて、ボトムゲート周辺回路TFT310の第1の結晶性シリコン層252の上方にレジストパターン277を形成する。次に、画素TFT11にn型不純物元素をイオン注入する際に、ボトムゲート周辺回路TFT310にも、レジストパターン277をマスクにしてn型不純物元素をイオン注入する。

【0184】

図21(c)は、図8(c)に示す第1の実施形態の工程に対応する工程である。図21(c)に示すように、ボトムゲート周辺回路TFT310では、レジストパターン277で覆われていた第1の結晶性シリコン層252にチャネル領域250cが形成され、チャネル領域250cの両側のn型不純物元素がイオン注入された領域にそれぞれソース領域250sおよびドレイン領域250dが形成される。ソース領域250sおよびドレイン領域250dは第1および第2の結晶性シリコン層252,253に形成される。これらのチャネル領域250c、ソース領域250sおよびドレイン領域250dによって半導体層250が構成される。画素TFT111では、チャネル領域51c、ソース領域51sおよびドレイン領域51dによって半導体層51が構成される。半導体層250,51を含む絶縁基板20を覆うように層間絶縁膜80を成膜する。次に、ボトムゲート周辺回路TFT310でも、ソース領域250sおよびドレイン領域250dに達するコンタクトホール85を開孔し、ソース領域250sおよびドレイン領域250dとオーミック接続された電極90s,90dをそれぞれ形成する。

【0185】

これにより、図17に示すボトムゲート周辺回路TFT310および画素TFT111が形成される。なお、引き出し電極90s,90dは、チタン膜、アルミニウム膜およびチタン膜を順に積層した積層金属膜の他に、例えばタングステン膜、チタン膜、またはアルミニウム膜等の単層金属膜から形成してもよく、またはこれらの膜から適宜選択して積層した積層金属膜から形成してもよい。

【0186】

次に、引き出し電極90s,90dを含む絶縁基板20を覆うように、プラズマCVD法によって窒化シリコン膜からなるパッシベーション膜(図示しない)を成膜する。なお、画素TFT111では、さらに平坦化膜、透明導電膜、画素電極等が形成されるが、それらの図示および説明を省略する。

【0187】

このようにして、ボトムゲート周辺回路TFT310および画素TFT111を含むアクティブマトリクス基板300が製造される。

【0188】

<3.3 効果>

本実施形態によれば、ボトムゲート周辺回路TFT310においても、第1の実施形態の場合と同様に、下方に加熱促進層230が設けられた非晶質シリコン膜56にレーザビームを照射すれば、非晶質シリコン膜56に照射されるレーザビームの実効的な照射量は設定値よりも大きくなる。これにより、非晶質シリコン膜56は結晶の配向が揃った第1の結晶性シリコン膜254になる。一方、下方に加熱促進層が設けられていない領域の非晶質シリコン膜56に、同じ設定値のレーザビームを照射しても、照射量は実効的に大きくならないので、非晶質シリコン膜56は結晶の配向がランダムな第2の結晶性シリコン膜255になる。

【0189】

また、第1の実施形態の場合と同様に、ボトムゲート周辺回路TFT310においても、加熱促進層230の位置を制御することにより、第1の結晶性シリコン膜254の位置を精度よく制御することができる。これにより、画素TFT111と、ボトムゲート周辺回路TFT310とを例えば3μm程度の距離まで近接させて配置することができる。その結果、アクティブマトリクス基板300に、画素TFT111と共に、ボトムゲート周辺回路TFT310を高い集積度で集積化することができる。

【0190】

加熱促進層230をボトムゲート電極として用いるので、加熱促進層230とは別に、ボトムゲート電極を形成する必要がない。これにより、ボトムゲート周辺回路TFT310の構造および製造工程を簡略化することができる。

【0191】

<4.各実施形態の変形例>

上記各実施形態の各TFTには、ソース領域およびドレイン領域とチャネル領域との間の各領域に、n型不純物元素がソース領域等よりも低濃度にイオン注入されたLDD(Lightly Doped Drain)領域が形成されていてもよい。

【0192】

上記各実施形態では、各TFTはnチャネル型のTFTであるとした。しかし、各TFTはpチャネル型のTFTであってもよい。この場合、ソース領域およびドレイン領域は、ホウ素(B)等のp型不純物元素をイオン注入することによって形成される。

【0193】

また、上記各実施形態では、半導体素子基板に形成される半導体素子として、薄膜トランジスタを例に説明した。しかし、薄膜トランジスタだけでなく、例えば光センサ等の半導体の電気特性を利用した能動素子であってもよい。

【0194】

上記各実施形態では、半導体素子基板として、アクティブマトリクス駆動方式の液晶表示装置のアクティブマトリクス基板を例に説明した。しかし、半導体素子基板は、アクティブマトリクス駆動方式の有機エレクトロルミネッセンス表示装置のアクティブマトリクス基板であってもよい。また、例えばオーディオ機器、通信機器、または家電製品に用いられ、半導体の電気特性を利用した能動素子を有する電気回路を備えた基板であってもよい。

【符号の説明】

【0195】

1…液晶表示装置

4…ゲートドライバ(周辺回路)

5…ソースドライバ(周辺回路)

6…表示領域

7…額縁領域

15…画素回路

20…絶縁基板

30,130,230…加熱促進層

31…モリブデン膜(高融点金属膜)

40…ベースコート膜(絶縁膜)

50,51,150,250…半導体層

52,152,252…結晶異方性を有する結晶性半導体層(第1の結晶性半導体層)

53,153,253…結晶異方性を有しない結晶性半導体層(第2の結晶性半導体層)

54…結晶異方性を有する結晶性半導体膜(第1の結晶性半導体膜)

55…結晶異方性を有しない結晶性半導体膜(第2の結晶性半導体膜)

56…非晶質シリコン膜(非晶質半導体膜)

60…ゲート絶縁膜

65…絶縁膜

70…ゲート電極

75…コンタクトホール

90s,90d…引き出し電極

100,200,300…アクティブマトリクス基板

110…周辺回路TFT(第1の薄膜トランジスタ)

111…画素TFT(第2の薄膜トランジスタ)

210…ダブルゲート周辺回路TFT(第1の薄膜トランジスタ)

310…ボトムゲート周辺回路TFT(第1の薄膜トランジスタ)

【技術分野】

【0001】

本発明は、半導体素子基板の製造方法および半導体素子基板並びに表示装置に関し、特に例えば、薄膜トランジスタを含み、アクティブマトリクス駆動方式の表示装置に用いられる半導体素子基板の製造方法および半導体素子基板並びに表示装置に関する。

【背景技術】

【0002】

近年、ガラス基板等の絶縁基板上に成膜した非晶質半導体膜を結晶化して、多結晶シリコン膜等の結晶構造を有する結晶性半導体膜を形成する技術が研究されている。結晶性半導体膜は、非晶質半導体膜に比べて非常に大きなキャリア移動度を有する。このため、例えば表示領域を構成する複数の画素回路と、画素回路を駆動するための周辺回路が同一の基板上に作り込まれたフルモノリシック型の液晶表示装置において、結晶性半導体膜を用いて形成した薄膜トランジスタ(Thin Film Transistor;以下、「TFT」という)は、各画素回路のスイッチング素子として機能するTFT(画素TFT)や、周辺回路を構成するTFT(周辺回路TFT)等として利用され、表示装置の高精細化および高速化を可能にしている。

【0003】

しかし、画素TFTと周辺回路TFTとでは、要求される動作速度や閾値電圧等の電気的特性が異なる。このため、これらのTFTを、一種類の結晶性半導体膜を用いて形成することは困難である。そこで、電気的特性に応じた異なる膜質の結晶性半導体膜を同一の絶縁基板上に形成することが求められている。

【0004】

また、結晶性半導体膜を安価な絶縁基板であるガラス基板やプラスチック基板に形成するためにレーザニール法が開発された。レーザニール法は、輻射加熱または伝導加熱を利用する高温熱処理法に比べて処理時間を大幅に短縮できるだけでなく、非晶質半導体膜を選択的、局所的に加熱することによりガラス基板に熱的損傷を与えない等の特徴がある。そこで、レーザアニール法を用いて、同一の絶縁基板上に膜質の異なる結晶性半導体膜を形成する各種の方法が提案されている。

【0005】

特許文献1には、連続発振レーザビームの走査中に走査速度を調整して単位時間当たりの照射量を領域ごとに連続的に変えることにより、結晶の異方性が異なる複数の領域からなる多結晶半導体膜を1回の走査で形成することが記載されている。

【0006】

また、特許文献2には、画素TFTを、電流経路の方向がレーザビームの照射によって結晶性半導体膜の結晶の成長方向と略垂直になるように配置し、駆動回路用TFTを、電流経路の方向が結晶の成長方向と略平行になるように配置することが記載されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2010−141040号公報

【特許文献2】国際公開2010/038511号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1に記載された方法によれば、レーザビームを1回だけ走査することによって、同一のガラス基板上に結晶の異方性が異なる複数の領域からなる多結晶半導体膜を形成することができる。しかし、レーザビームの走査中に走査速度を細かく調整することは難しいので、結晶の異方性が異なる領域を用いる必要があるTFTを近接して形成しなければならない場合、それぞれの領域を近接して形成することは難しい。このため、結晶の異方性が異なる領域を用いたTFTを集積化することは困難になる。

【0009】

また、特許文献2に記載されたTFTの配置方法によれば、結晶の成長方向を考慮して、画素TFTと周辺回路TFTを配置しなければならない。このため、特に周辺回路の設計の自由度が小さくなり、TFTを集積化することが困難になる。

【0010】

そこで、本発明は、結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供することを目的とする。

【課題を解決するための手段】

【0011】

第1の発明は、絶縁基板上に半導体素子が形成された半導体素子基板の製造方法であって、

前記絶縁基板上に高融点金属膜を用いて加熱促進層を形成する加熱促進層形成工程と、

前記加熱促進層を覆うように絶縁膜を成膜する絶縁膜形成工程と、

前記絶縁膜上に非晶質半導体膜を成膜する非晶質半導体膜形成工程と、

前記非晶質半導体膜の表面側からレーザビームを照射して前記非晶質半導体膜を溶融固化することにより、結晶異方性を有する第1の結晶性半導体膜と、結晶異方性を有さない第2の結晶性半導体膜とを形成する結晶化工程とを備え、

前記第1の結晶性半導体膜は、前記非晶質半導体膜を透過した前記レーザビームが前記加熱促進層に照射されて、前記非晶質半導体膜の裏面側からも結晶化を促進することにより形成されることを特徴とする。

【0012】

第2の発明は、第1の発明において、

前記非晶質半導体膜の裏面側からの結晶化の促進は、前記加熱促進層の表面で反射された前記レーザビームが前記非晶質半導体膜の裏面に照射されることによって行なわれることを特徴とする。

【0013】

第3の発明は、第2の発明において、

前記高融点金属膜は少なくともモリブデン膜を含む金属膜であることを特徴とする。

【0014】

第4の発明は、第1の発明において、

前記非晶質半導体膜の裏面側からの結晶化の促進は、前記加熱促進層が前記レーザビームを吸収して発生した熱が前記非晶質半導体膜の裏面に与えられることによって行なわれることを特徴とする。

【0015】

第5の発明は、第4の発明において、

前記高融点金属膜は少なくともタングステン膜を含む金属膜であることを特徴とする。

【0016】

第6の発明は、第1の発明において、

前記加熱促進層の膜厚は50nm以上かつ500nm以下であることを特徴とする。

【0017】

第7の発明は、第1の発明において、

前記レーザビームは、連続発振レーザビームまたは擬似連続発振レーザビームであることを特徴とする。

【0018】

第8の発明は、第7の発明において、

前記レーザビームは、イットリウム・アルミニウム・ガーネットレーザの第2高調波のビームであることを特徴とする。

【0019】

第9の発明は、第7の発明において、

前記レーザビームの走査速度は5cm/sec以上かつ3m/sec以下であることを特徴とする。

【0020】

第10の発明は、第7の発明において、

前記レーザビームの走査回数は1回であることを特徴とする。

【0021】

第11の発明は、第1の発明において、

前記絶縁膜は、少なくとも酸化シリコン、窒化シリコン、酸窒化シリコンのいずれかを含むことを特徴とする

【0022】

第12の発明は、第11の発明において、

前記絶縁膜の膜厚は30nm以上かつ500nm以下であることを特徴とする。

【0023】

第13の発明は、第1の発明において、

前記非晶質半導体膜は非晶質シリコン膜であることを特徴とする。

【0024】

第14の発明は、第13の発明において、

前記レーザビームの波長は370nm以上かつ650nm以下であることを特徴とする。

【0025】

第15の発明は、第14の発明において、

前記半導体素子は薄膜トランジスタであり、

前記第1および第2の結晶性半導体膜をパターニングすることによって前記薄膜トランジスタの半導体層を形成する半導体層形成工程をさらに備えることを特徴とする。

【0026】

第16の発明は、半導体素子基板であって、

第1から第15のいずれかの発明に係る半導体素子基板の製造方法によって製造されたことを特徴とする。

【0027】

第17の発明は、第16の発明において、

前記半導体素子基板は、

前記第1の結晶性半導体膜から形成された第1の半導体層を有する第1薄膜トランジスタと、

前記第2の結晶性半導体膜から形成された第2の半導体層を有する第2薄膜トランジスタとを備えることを特徴とする。

【0028】

第18の発明は、第17の発明において、

前記第1の薄膜トランジスタは、前記第1の半導体層の上方に形成された第1のゲート電極を有する薄膜トランジスタであり、

前記第2の薄膜トランジスタは、前記第2の半導体層の上方に形成された第2のゲート電極を有する薄膜トランジスタであることを特徴とする。

【0029】

第19の発明は、第18の発明において、

前記第1の薄膜トランジスタはダブルゲート構造の薄膜トランジスタをさらに含み、

前記ダブルゲート構造の薄膜トランジスタのボトムゲート電極は、前記第1のゲート電極と電気的に接続された前記加熱促進層であることを特徴とする。

【0030】

第20の発明は、第17の発明において、

前記第1の薄膜トランジスタはボトムゲート構造の薄膜トランジスタであり、

前記ボトムゲート構造の薄膜トランジスタのボトムゲート電極は、前記加熱促進層であり、

前記第2の薄膜トランジスタは、前記第2の半導体層の上方に形成された第2のゲート電極を有することを特徴とする。

【0031】

第21の発明は、表示装置であって、

第17から第20のいずれかの発明に係る半導体素子基板を備える表示装置であって、前記第1の薄膜トランジスタのチャネル領域は、前記第2の薄膜トランジスタのチャネル領域よりも大きいことを特徴とする。

【0032】

第22の発明は、第21の発明において、

複数の画素回路をマトリクス状に配列した表示領域と、前記絶縁基板上の額縁領域に形成された前記複数の画素回路を駆動するための周辺回路とをさらに備え、

前記周辺回路は前記第1の薄膜トランジスタによって構成され、

前記複数の画素回路のスイッチング素子は前記第2の薄膜トランジスタによって構成されていることを特徴とする。

【発明の効果】

【0033】

上記第1の発明によれば、レーザビームを反射または吸収して非晶質半導体膜の裏面側からの加熱を促進させるための加熱促進層を形成し、非晶質半導体膜にレーザビームを照射する。加熱促進層は、非晶質半導体膜を透過したレーザビームを反射または吸収して、加熱促進層の上方およびその近傍の非晶質半導体膜を加熱する。これにより、加熱促進層がレーザビームを反射または吸収して、加熱促進層の上方およびその近傍の非晶質半導体膜は、加熱促進層から離れた位置にある非晶質半導体膜よりも加熱されて高温になる。その結果、下方に加熱促進層が形成された非晶質半導体膜およびその近傍に照射されるレーザビームの照射量が実効的に大きくなるので、結晶の配向が揃った第1の結晶性半導体膜になる。このように加熱促進層が形成される位置を精度よく制御して、第1の結晶性半導体膜が形成される位置を高い精度で制御することができる。また、第1の結晶性半導体膜の位置が決まると、結晶の配向がランダムな第2の結晶性半導体膜が形成される位置も決まる。その結果、第1および第2の結晶性半導体膜からなる半導体素子を近接させて形成することができるので、半導体素子を高集積化した半導体素子基板を製造することができる。このとき、加熱促進層は、高融点金属膜からなるので、レーザビームを吸収して高温になっても溶融しにくい。

【0034】

上記第2の発明によれば、加熱促進層は、非晶質半導体膜に照射されたレーザビームをその表面で反射する。反射されたレーザビームは非晶質半導体膜の裏面に照射される。これにより、非晶質半導体膜の裏面側からも非晶質半導体膜の結晶化を促進する。

【0035】

上記第3の発明によれば、モリブデン膜を含む加熱促進層は、レーザビームを反射することによって、非晶質半導体膜の結晶化を裏面側から促進する。

【0036】

上記第4の発明によれば、加熱促進層は、非晶質半導体膜に照射されたレーザビームを吸収して発熱し、非晶質半導体膜の結晶化を裏面側から促進する。

【0037】

上記第5の発明によれば、タングステン膜を含む加熱促進層は、レーザビームを吸収して発熱し、非晶質半導体膜の裏面側を加熱して結晶化を促進する。

【0038】

上記第6の発明によれば、加熱促進層の膜厚を50nm以上にすることによって、非晶質半導体膜にレーザビームを照射したときに、加熱促進層におけるレーザビームの反射または吸収が不十分になることを抑制できる。これにより、加熱促進層の上方およびその近傍の非晶質半導体膜を、溶融固化することができる。一方、加熱促進層の膜厚を500nm以下にすることにより、加熱促進層が設けられた領域の上方の絶縁膜の表面と加熱促進層が設けられていない領域の上方の絶縁膜の表面との間の段差を小さくし、電極や配線が段差によって段切れしにくくする。このため、加熱促進層の膜厚を50nm以上かつ500nm以下にすることが好ましい。

【0039】

上記第7の発明によれば、連続発振レーザビームまたは擬似連続発振レーザビームを出力するレーザ発振器は単純な構造であるので、メンテナンスが長期間不要になる。これにより、レーザ発振器の稼働時間を長くして、ランニングコストを安価にすることができる。

【0040】

上記第8の発明によれば、イットリウム・アルミニウム・ガーネットレーザの第2高調波(波長532nm)を非晶質半導体膜に照射する。これにより、加熱促進層の上方およびその近傍の非晶質半導体膜のみに、実効的に大きな照射量のレーザビームを照射し、部分的に第1の結晶性半導体膜を形成することができる。

【0041】

上記第9の発明によれば、レーザビームの走査速度を5cm/sec以上にすることによって、非晶質半導体膜が過剰なエネルギーを受けて蒸発することを抑制できる。また、レーザビームの走査速度を3m/sec以下にすることによって、非晶質半導体膜を確実に溶融固化することができる。

【0042】

上記第10の発明によれば、レーザビームを1回だけ走査すればよいので、結晶化工程の処理時間を短縮することができる。

【0043】

上記第11の発明によれば、加熱促進層を覆う絶縁膜は、少なくとも酸化シリコン膜、窒化シリコン膜、酸窒化シリコン膜のいずれかを含むので、不純物が絶縁基板から非晶質半導体膜に拡散することを抑制することができる。

【0044】

上記第12の発明によれば、絶縁膜の膜厚を30nm以上にすることにより、第1および第2の結晶性半導体膜をパターニングする際のオーバーエッチングによって絶縁膜がエッチングされ、加熱促進層の一部が露出することを防止できる。これにより、加熱促進層がその後の工程で形成される配線層と短絡しないようにすることができる。一方、絶縁膜の膜厚を500nm以下にすることにより、非晶質半導体膜にレーザビームを照射したときに、加熱促進層によるレーザビームの反射または吸収が十分行なわれ、非晶質半導体膜の裏面側からの結晶化を十分に促進することができる。

【0045】

上記第13の発明によれば、非晶質半導体膜として非晶質シリコン膜を用いることにより、第1および第2の結晶性半導体膜はキャリア移動度の高い多結晶シリコンになる。これにより、優れた電気的特性を有する半導体素子を備えた半導体素子基板を製造することができる。

【0046】

上記第14の発明によれば、波長が370〜650nmのレーザビームに対する非晶質シリコン膜の吸収係数が小さいので、非晶質シリコン膜に照射されたレーザビームはその内部でほとんど吸収されることなく非晶質シリコン膜を透過する。このため、加熱促進層によって吸収または反射されるレーザビームのエネルギーは大きくなり、下方に加熱促進層が設けられた非晶質シリコン膜は、その裏面側から結晶化が促進されて第1の結晶性シリコン膜になる。これに対して、下方に加熱促進層が設けられていない非晶質シリコン膜は、下方に加熱促進層が設けられた非晶質シリコン膜よりもレーザビームによって与えられるエネルギーが実効的に小さくなり、第2の結晶性シリコン膜になる。このように、波長が370〜650nmのレーザビームを非晶質シリコン膜に照射することによって、第1の結晶性シリコン膜と第2の結晶性シリコン膜を分けて形成することができる。これにより、レーザ発振器のパワーやレーザビームの走査速度等の設定条件のマージンを大きくできるので、安定したレーザビームを非晶質シリコン膜に照射することができる。

【0047】

上記第15の発明によれば、第1および第2の半導体膜をパターニングすることによって、電気的特性が異なる第1および第2の薄膜トランジスタを製造することができる。

【0048】

上記第16の発明によれば、第1の発明から第15の発明のいずれかに係る製造方法によって製造された半導体素子基板には、結晶の配向が異なる第1の結晶性半導体膜を用いた半導体素子と第2の結晶性半導体膜を用いた半導体素子とが形成されている。これにより、電気的特性が異なる半導体素子を備えた半導体素子基板を得ることができる。

【0049】

上記第17の発明によれば、結晶の配向が異なる第1の結晶性半導体膜を用いた第1の薄膜トランジスタと、第2の結晶性半導体膜を用いた第2の薄膜トランジスタとが形成されている。これにより、電気的特性が異なる薄膜トランジスタを備えた半導体素子基板を得ることができる。

【0050】

上記第18の発明によれば、電気的特性が異なるトップゲート構造の第1および第2の薄膜トランジスタによって所望の電気的特性を実現可能な半導体素子基板を得ることができる。

【0051】

上記第19の発明によれば、第1の薄膜トランジスタはさらにダブルゲート構造の薄膜トランジスタを含むため、シングルゲート構造の薄膜トランジスタに比べてオン電流を大きくすることができる。また、加熱促進層をボトムゲート電極として用いるので、加熱促進層とは別に、ボトムゲート電極を形成する必要がない。これにより、ダブルゲート構造の薄膜トランジスタの構造を簡略化することができる。

【0052】

上記第20の発明によれば、電気的特性が異なる、ボトムゲート構造の第1の薄膜トランジスタと、トップゲート構造の第2の薄膜トランジスタとによって所望の電気的特性を実現可能な半導体素子基板を得ることができる。また、ボトムゲート構造の薄膜トランジスタでは、加熱促進層をボトムゲート電極として用いるので、加熱促進層とは別に、ボトムゲート電極を形成する必要がない。これにより、ダブルゲート構造の薄膜トランジスタの構造を簡略化することができる。

【0053】

上記第21の発明によれば、大きなチャネル領域を有する第1の薄膜トランジスタではキャリア移動度が大きくなる。また、小さなチャネル領域を有する第2の薄膜トランジスタでは、薄膜トランジスタ間の閾値電圧のばらつきが抑制される。このように電気的特性が異なる第1および第2の薄膜トランジスタが形成された半導体素子基板を用いて表示装置を構成することにより、所望の特性を有する表示装置を構成することができる。

【0054】

上記第22の発明によれば、周辺回路は、キャリア移動度の高い第1の薄膜トランジスタによって構成されており、画素回路は、薄膜トランジスタ間の閾値電圧のばらつきを抑制された第2の薄膜トランジスタによって構成されている。このように、周辺回路および画素回路は、最適な薄膜トランジスタによってそれぞれ構成されるので、輝度や色のばらつきが少なく、安定した表示が可能な表示装置を得ることができる。

【図面の簡単な説明】

【0055】

【図1】本発明の第1の実施形態に係る液晶表示装置の構成を示す平面図である。

【図2】上記実施形態に係る液晶表示装置のA−A線に沿った断面図である。

【図3】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板のブロック図である。

【図4】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成された周辺回路TFTと画素TFTの構成を示す断面図である。

【図5】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成された周辺回路TFTの構成を示す平面図である。

【図6】(a)〜(d)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図7】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図8】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図9】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の結晶化工程において、YAGレーザのレーザビームを照射して非晶質シリコン膜を結晶化する方法を示す図である。

【図10】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されるべき周辺回路TFTおよび画素TFTの領域における、第1の結晶性シリコン膜および第2の結晶性シリコン膜の形状を示す平面図である。

【図11】本発明の第2の実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成された周辺回路TFT、ダブルゲート周辺回路TFTおよび画素TFTの構成を示す断面図である。

【図12】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されるべき周辺回路TFT、ダブルゲート周辺回路TFT、および画素TFTの領域における第1の結晶性シリコン膜および第2の結晶性シリコン膜の形状を示す平面図である。

【図13】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されたダブルゲート周辺回路TFTの構成を示す平面図である。

【図14】(a)〜(d)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図15】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図16】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図17】本発明の第3の実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されたボトムゲート周辺回路TFTおよび画素TFTの構成を示す断面図である。

【図18】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されたボトムゲート周辺回路TFTの構成を示す平面図である。

【図19】(a)〜(d)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図20】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図21】(a)〜(c)は、上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板の各製造工程をそれぞれ示す断面図である。

【図22】上記実施形態に係る液晶表示装置を構成するアクティブマトリクス基板に形成されるべきボトムゲート周辺回路TFTおよび画素TFTの領域における、第1の結晶性シリコン膜および第2の結晶性シリコン膜の形状を示す平面図である。

【発明を実施するための形態】

【0056】

以下、本発明の各実施形態を図面に基づいて詳細に説明する。なお、本明細書の実施形態では、半導体素子基板として液晶表示装置を構成するアクティブマトリクス基板を説明し、半導体素子基板に含まれる半導体素子としてTFTを説明する。なお、本発明は、以下の各実施形態に限定されるものではない。

【0057】

<1.第1の実施形態>

図1は、本発明の第1の実施形態に係る液晶表示装置1の構成を示す平面図であり、図2は、液晶表示装置1のA−A線に沿った断面図である。図3は、液晶表示装置1を構成するアクティブマトリクス基板100の構成を示すブロック図である。

【0058】

<1.1 液晶表示装置の構成>

図1および図2に示すように、液晶表示装置1は、矩形状のアクティブマトリクス基板100、アクティブマトリクス基板100と対向するように配置された矩形状の対向基板105、アクティブマトリクス基板100と対向基板105とを接着するために矩形枠状に形成されたシール材9、および、アクティブマトリクス基板100と対向基板105とシール材9とによって囲まれた空間に封入された液晶層12を備えている。

【0059】

アクティブマトリクス基板100と対向基板105の液晶層12側の各表面に配向膜11がそれぞれ形成され、液晶層12と反対側の各表面に偏光板10がそれぞれ貼り付けられている。液晶層12は、電気光学特性を有するネマチックの液晶材料等により構成されている。

【0060】

また、アクティブマトリクス基板100の液晶層12側の表面には、画像を表示するための表示領域6が設けられている。表示領域6は、画像を表示するために、その最小単位である画素回路をマトリクス状に複数個配列された領域である。なお、図1および図2では、画素回路の図示は省略されている。

【0061】

アクティブマトリクス基板100の表示領域6の周囲には額縁領域7が設けられ、対向基板105と重ならないアクティブマトリクス基板100の領域(図1の下端の領域)には、フレキシブルプリント配線基板(Flexible Printed Circuit、以下、「FPC」という)13を接続するための端子が配置された端子領域8が設けられている。画像を表示するための画像信号等は、外部からFPC13を介して液晶表示装置1に入力される。なお、図1では偏光板10および配向膜11の図示が省略されている。

【0062】

<1.2 アクティブマトリクス基板>

図3に示すように、アクティブマトリクス基板100の表示領域6には、互いに並行に延びるように配置されたn(nは1以上の整数)本のゲート配線GL1〜GLnと、層間絶縁膜を介して、各ゲート配線GL1〜GLnと交差する方向に互いに並行に延びるように配置されたm(mは1以上の整数)本のソース配線SL1〜SLmとが形成されている。ゲート配線GL1〜GLn(nは1以上の整数)とソース配線SL1〜SLmの各交点には、画素回路15が1個ずつ配置されている。

【0063】

画素回路15は、スイッチング素子として機能する画素TFT111と、画素TFT111のドレインに接続された画素電極(図示しない)とを有し、画素電極は共通電極Ecと共に画素容量Cpを形成する。画素TFT111のゲート電極はゲート配線GLi(iは1≦i≦nの整数)に接続され、ソース電極はソース配線SLj(jは1≦j≦mの整数)に接続されている。

【0064】

図1に示すように、アクティブマトリクス基板100の額縁領域7には、画素回路15を駆動するためのゲートドライバ4とソースドライバ5とが配置されている。ゲートドライバ4およびソースドライバ5は絶縁基板上に作り込まれたモノリシック回路であり、周辺回路に含まれる。なお、ゲートドライバ4およびソースドライバ5は、周辺回路TFTによって構成されているが、図3では、周辺回路TFTの図示が省略されている。また図2では、ゲートドライバ4およびソースドライバ5の図示が省略されている。

【0065】

対向基板105のガラス基板またはプラスチック基板等の絶縁基板上には、ゲート配線GL1〜GLnおよびソース配線SL1〜SLmに対応する位置に設けられたブラックマトリクスと、ブラックマトリクスによって囲まれた領域に、例えば赤色層、緑色層および青色層を含む複数色のカラーフィルタと、ブラックマトリクスおよびカラーフィルタを覆うように設けられた共通電極Ecと、アクティブマトリクス基板100と対向基板105との距離を一定に保つために共通電極Ec上に配置された柱状のフォトスペーサとが配置されている。なお、ブラックマトリクス、カラーフィルタ、およびフォトスペーサはいずれも図示されていない。

【0066】

<1.3 液晶表示装置の製造方法>

液晶表示装置1の製造方法について説明する。まず、アクティブマトリクス基板100および対向基板105をそれぞれ製造し、アクティブマトリクス基板100および対向基板105の表面に配向膜11をそれぞれ形成する。

【0067】

次に、これらの配向膜11が対向するように、アクティブマトリクス基板100と対向基板105とをシール材9によって貼り合わせる。シール材9の開口部から、アクティブマトリクス基板100と対向基板105とシール材9とによって囲まれた空間に液晶を注入し、液晶層12を形成する。次に、アクティブマトリクス基板100および対向基板105の配向膜11を形成した表面と反対側の表面に偏光板10をそれぞれ貼り付ける。アクティブマトリクス基板100に設けられた端子領域8の接続端子に、FPC13の接続端子を接続する。これにより、液晶表示装置1が製造される。

【0068】

なお、対向基板105の製造、配向膜11の形成、アクティブマトリクス基板100と対向基板105との貼り合せ、偏光板10の貼り付け、およびFPC13の接続は、公知の方法によって行なうので、本明細書では、それらの説明を省略する。

【0069】

<1.4 液晶表示装置の動作>

液晶表示装置1の動作について説明する。各画素回路15において、ゲートドライバ4からハイレベルのゲート電圧を、ゲート配線GLiを介して画素TFT111のゲート電極に与えて、画素TFT111をオン状態にする。このとき、ソースドライバ5から画像信号DVに応じた信号電圧がソース配線SLjに与えられ、信号電圧は画素TFT111を介して画素電極に書き込まれる。これにより、アクティブマトリクス基板100の各画素電極と対向基板105の共通電極Ecの間に電位差が生じ、液晶層12に信号電圧が印加される。液晶層12に印加された信号電圧によって液晶分子の配向状態が変わり、液晶層12の光透過率が変わる。このようにして、画像信号DVに応じた画像が液晶表示装置1の表示領域6に表示される。なお、ゲートドライバ4は制御信号CS1によって制御され、ソースドライバ5は制御信号CS2によって制御される。

【0070】

<1.5 周辺回路TFTおよび画素TFT>

図4は、アクティブマトリクス基板100に形成された周辺回路TFT110と画素TFT111の構成を示す断面図である。周辺回路TFT110は、アクティブマトリクス基板100の額縁領域7に形成されるゲートドライバ4やソースドライバ5を構成するためのTFTであり、画素TFT111は画素回路15のスイッチング素子として機能するTFTである。

【0071】

図4を参照して、まず周辺回路TFT110の構成を説明する。周辺回路TFT110は、絶縁基板20上に成膜されたベースコート膜40上に形成されている。ベースコート膜40は、絶縁基板20から周辺回路TFT110内に不純物が拡散しないようにするための絶縁膜である。また、絶縁基板20とベースコート膜40との間には、島状の加熱促進層30が設けられている。加熱促進層30が設けられている理由は後述する。

【0072】

加熱促進層30と対向するベースコート膜40上の位置に、島状の半導体層50が形成されている。半導体層50は、結晶異方性を有する結晶性シリコン層(以下、「第1の結晶性シリコン層」という)からなる。半導体層50の中央にチャネル領域50cが形成され、チャネル領域50cの両側にソース領域50sおよびドレイン領域50dがそれぞれ形成されている。チャネル領域50cは真性領域からなり、ソース領域50sおよびドレイン領域50dは、リン(P)等のn型不純物元素をイオン注入されたn型不純物領域からなる。ここで、結晶異方性を有する結晶性シリコン層とは、多結晶シリコンからなり、結晶の配向が特定の方向(具体的には、後述するレーザビームの走査方向)に揃っているシリコン層をいう。

【0073】

半導体層50を含む絶縁基板20を覆うようにゲート絶縁膜60が形成されている。半導体層50のチャネル領域50cと対向するゲート絶縁膜60上の位置に、ゲート電極70が形成されている。さらに、ゲート電極70を含む絶縁基板20を覆うように層間絶縁膜80が形成され、層間絶縁膜80上に引き出し電極90s,90dが形成されている。ゲート絶縁膜60および層間絶縁膜80には、半導体層50のソース領域50sおよびドレイン領域50dにそれぞれ達する2つのコンタクトホールが開孔されている。引き出し電極90s,90dは、これらのコンタクトホールを介して、ソース領域50sおよびドレイン領域50dにそれぞれオーミック接続されている。さらに、それらはパッシバーション膜(図示しない)によって覆われている。

【0074】

このような周辺回路TFT110のチャネル領域50cのサイズは大きく、例えば20×20μmである。

【0075】

次に、画素TFT111の構成について説明する。画素TFT111の構成要素のうち、周辺回路TFT110の構成要素と同じ構成要素には、同じ参照符号を付して、その説明を省略する。画素TFT111には、周辺回路TFT110に設けられていた加熱促進層は設けられていない。このため、ベースコート膜40は絶縁基板20上に形成されている。ベースコート膜40上に、島状の半導体層51が形成されている。半導体層51は、結晶異方性を有さない結晶性シリコン層(以下、「第2の結晶性シリコン層」という)からなる。半導体層51の中央にチャネル領域51cが形成され、チャネル領域51cの両側にソース領域51sおよびドレイン領域51dがそれぞれ形成されている。チャネル領域51cは真性領域からなり、ソース領域51sおよびドレイン領域51dはn型不純物領域からなる。ここで、結晶異方性を有さない結晶性シリコン層とは、平均結晶粒径が例えば約0.3μmΦの比較的小さな多結晶シリコンからなり、結晶の配向がランダムであるシリコン層をいう。このような画素TFT111のチャネル領域51cのサイズは小さく、例えば4×4μmである。

【0076】

画素TFT111は、周辺回路TFT110と同様に、半導体層51を覆うように形成されたゲート絶縁膜60と、ゲート絶縁膜60上に形成されたゲート電極70と、ゲート電極70を覆うように形成された層間絶縁膜80と、層間絶縁膜80上に形成された引き出し電極90s,90dとをさらに備えている。引き出し電極90s,90dは、コンタクトホールを介してソース領域51sおよびドレイン領域51dとそれぞれオーミック接続されている。さらに、それらはパッシバーション膜(図示しない)によって覆われている。

【0077】

なお、画素TFT111のゲート電極70はゲート配線に接続され、引き出し電極90sはソース配線に接続され、引き出し電極90dは画素電極に接続されている。これらのゲート配線、ソース配線および画素電極は、図4には示されていない。

【0078】

図5は、アクティブマトリクス基板100に形成された周辺回路TFT110の構成を示す平面図である。図5に示すように、半導体層50の下方に、半導体層50よりも大きな加熱促進層30が形成されている。このため、半導体層50は第1の結晶性シリコン層52のみからなる。また、ゲート電極70の下方の半導体層50にはチャネル領域(図示しない)が形成されている。また、チャネル領域の両側にはソース領域50sおよびドレイン領域50dが形成されており、引き出し電極90s,90dとそれぞれオーミック接続されている。なお、画素TFT111も、加熱促進層が形成されていないことを除いて、周辺回路TFT110と同様に構成されている。

【0079】

<1.6 レーザアニール法>

周辺回路TFT110および画素TFT111において、非晶質シリコン膜を結晶化して結晶性シリコン膜を形成する際に使用されるレーザアニール法について説明する。

【0080】

レーザアニール法に使用されるレーザビームは、発振方法の違いにより、パルス発振レーザと連続発振レーザとに大別される。パルス発振レーザは出力エネルギーが比較的高いので、ビームスポットの幅を広くして量産性を上げることができる。特に、ビームスポットの形状を、光学部材を用いて加工して長さ10cm以上の線状にすることにより、レーザビームの照射を効率的に行うことができるので、量産性を向上させることができる。

【0081】

また、パルス発振レーザの一種である擬似連続発振レーザも非晶質シリコン膜の結晶化に用いられる。この擬似連続発振レーザとは、レーザビームの走査方向(またはステージの移動方向)に結晶が連続的に成長するように、10MHz以上の高周波パルスを使用したレーザである。

【0082】

一方、連続発振レーザは、パルス発振レーザに比べて最大出力エネルギーが小さいので、ビームスポットのサイズが小さく、幅は数10μm程度から数mm程度である。このため、非晶質シリコン膜の結晶化には、ビームスポットの走査を複数回行なわなければならない。このことから、非晶質シリコン膜の結晶化には、パルス発振レーザが広く用いられていた。

【0083】

しかし、近年、非晶質シリコン膜の結晶化にCW(Continuous Wave)固体レーザ等の連続発振レーザを用いることにより、結晶性シリコン膜内の結晶粒径を大きくできることがわかった。

【0084】

このような連続発振レーザまたはパルス発振レーザの一種である擬似連続発振レーザのレーザビームの単位時間当たりの照射量を大きくすれば、非晶質シリコン膜を完全に溶融させ、レーザビームの走査方向に結晶を成長させることができる。レーザビームの走査方向に結晶が成長した結晶性シリコン膜では、キャリア移動度が大きくなるので、TFTの動作速度を向上させることができる。このように、連続発振レーザまたは擬似連続発振レーザを用いて非晶質シリコン膜を結晶化させれば、結晶はレーザビームを走査する方向(絶縁基板に対して横方向)に成長するので、レーザビームの走査方向に結晶の配向が揃った結晶性シリコン膜になる。そこで、本明細書では、このような結晶異方性を有する結晶性シリコン膜を第1の結晶性シリコン膜といい、第1の結晶性シリコン膜をパターニングしたシリコン層を、第1の結晶性シリコン層という。これに対して、結晶の配向がランダムで、結晶異方性を有さない結晶性シリコン膜を第2の結晶性シリコン膜といい、第2の結晶性シリコン膜をパターニングしたシリコン層を、第2の結晶性シリコン層という。

【0085】

チャネル長方向が第1の結晶性シリコン層の結晶成長方向と同じ方向になるように配置されたTFTでは、オン電流が大きくなるので、第1の結晶性シリコン層は周辺回路TFT110の半導体層50に適している。一方、画素TFT111のように、チャネル領域51cのサイズが小さなTFTでは、チャネル領域内の結晶粒界数または結晶粒界長のTFT間のばらつきが大きくなるので、TFT間の閾値電圧のばらつきも大きくなる。画素TFT111としては、キャリア移動度が多少小さくなっても、TFT間の閾値電圧のばらつきが小さなTFTが好ましい。このため、第2の結晶性シリコン層は画素TFT111の半導体層51に適している。

【0086】

<1.7 アクティブマトリクス基板の製造方法>

本実施形態のアクティブマトリクス基板100の製造方法を説明する。図6(a)〜図6(d)、図7(a)〜図7(c)、図8(a)〜図8(c)は、アクティブマトリクス基板100の各製造工程をそれぞれ示す断面図である。

【0087】

アクティブマトリクス基板100の製造工程には、加熱促進層形成工程と、絶縁膜形成工程と、非晶質半導体膜成膜工程と、結晶化工程とが含まれる。これらの工程により、周辺回路TFT110と画素TFT111の各半導体層50,51が結晶化される。

【0088】

<1.7.1 加熱促進層形成工程>

図6(a)に示すように、ガラス基板またはプラスチック基板等の絶縁基板20上に、スパッタリング法を用いて、例えば厚さが150nmのモリブデン(Mo)膜31を成膜する。次に、図5(b)に示すように、フォトリソグラフィ法を用いてモリブデン膜31をパターニングし、周辺回路TFT110を形成すべき領域に加熱促進層30を形成する。一方、画素TFT111を形成すべき領域には加熱促進層を形成しないので、モリブデン膜31を除去する。

【0089】

モリブデン膜からなる加熱促進層30は、後述する結晶化工程において、非晶質シリコン膜56に照射されたレーザビームを反射する。加熱促進層30によって反射されたレーザビームは、非晶質シリコン膜56の裏面に照射され、非晶質シリコン膜56を裏面側から結晶化する。なお、モリブデン膜31からなる加熱促進層30に代えて、レーザビームを吸収して発熱するタングステン(W)膜からなる加熱促進層を形成してもよい。また、加熱促進層30を、高融点金属であるモリブデン膜31またはタングステン膜を用いて形成することにより、結晶化工程において高温になっても加熱促進層30は溶融しにくくなる。

【0090】

このように、加熱促進層30は、非晶質シリコン膜56を透過したレーザビームを反射または吸収することにより、非晶質シリコン膜56の結晶化を促進させる機能を有する。すなわち、加熱促進層30を設けることにより、第1の結晶性シリコン膜54を形成すべき領域の非晶質シリコン膜56に照射されるレーザビームの照射量を、第2の結晶性シリコン膜55を形成すべき領域に照射されるレーザビームの照射量よりも実効的に大きくすることができる。

【0091】

ここで、加熱促進層30の膜厚が50nmよりも薄い場合には、後述する結晶化工程において非晶質シリコン膜56にレーザビームを照射したときに、加熱促進層30によるレーザビームの反射または吸収が不十分になる。この場合、レーザビームの実効的な照射量が十分大きくならないので、加熱促進層30およびその近傍の非晶質シリコン膜56は十分に溶融固化されず、結晶の配向はランダムになる。

【0092】

一方、加熱促進層30の膜厚が500nmよりも厚い場合には、レーザビームを照射したときに、加熱促進層30が設けられた領域と加熱促進層30が設けられていない領域との境界において、後述する層間絶縁膜80の表面に大きな段差が生じる。この段差によって、層間絶縁膜80の表面に形成される引き出し電極90s,90dは段切れする。そこで、加熱促進層30の膜厚は、50nm以上かつ500nm以下であることが好ましい。なお、引き出し電極90s,90dの段切れをさらに抑制するために、加熱促進層30の膜厚を50nm以上かつ300nm以下にすることがより好ましい。

【0093】

<1.7.2 絶縁膜形成工程>

図6(c)に示すように、加熱促進層30が形成された絶縁基板20上に、原料ガスとしてTEOS(Tetraethyl orthosilicate:Si(OC2H5)4)を用いたCVD(Chemical Vapor Deposition)法等により、例えば厚さが100nmの二酸化シリコン膜(SiO2)からなるベースコート膜40を成膜する。なお、ベースコート膜40は、二酸化シリコン膜の他に、窒化シリコン膜(SiN)、酸窒化シリコン膜(SiON)等であってもよく、またはこれらの膜を積層した積層絶縁膜であってもよい。

【0094】

ここで、ベースコート膜40の膜厚が30nmよりも薄い場合には、後述する第1および第2の結晶性シリコン膜54,55を、ドライエッチング法を用いて形成する際に、ベースコート膜40の一部がオーバーエッチングによって除去され、加熱促進層30の一部が露出する場合がある。この場合、その後の工程で形成される配線層が、露出した加熱促進層30と接触して不具合を生じさせる。一方、ベースコート膜40の膜厚が500nmよりも厚い場合には、後述する結晶化工程において非晶質シリコン膜56にレーザビームを照射したときに、加熱促進層30によるレーザビームの反射または吸収が不十分になる。この場合、加熱促進層30およびその近傍の非晶質シリコン膜56に照射されるレーザビームの照射量を実効的に大きくできないので、非晶質シリコン膜56は十分に溶融固化されず、結晶の配向はランダムになる。そこで、ベースコート膜40の膜厚は、30nm以上かつ500nm以下であることが好ましい。

【0095】

<1.7.3 非晶質半導体膜成膜工程>

図6(d)に示すように、ベースコート膜40を含む絶縁基板20を覆うように、例えば厚さが50nmの非晶質シリコン膜56を成膜する。非晶質シリコン膜56は、原料ガスとしてシランガス(SiH4)を用いたLPCVD(Low Pressure CVD)法等を用いて成膜される。

【0096】

<1.7.4 結晶化工程>

連続発振レーザであるYAGレーザ(イットリウム・アルミニウム・ガーネット(Yttrium Aluminum Garnet)レーザ(以下、「YAGレーザ」という)のレーザビームのビーム形状を、その長さ2mm、幅50μm程度の楕円状になるように成形し、レーザビームを非晶質シリコン膜56の表面に照射する。図9は、YAGレーザのレーザビーム18を照射して非晶質シリコン膜56を結晶化する方法を示す図である。図9に示すように、レーザビーム18を矢印で示す方向に速度20cm/secで走査しながら、非晶質シリコン膜56にYAGレーザの第2高調波(波長532nm)を照射する。このとき、レーザ発振器のパワーを1.2Wに設定する。第2高調波を照射することにより、加熱促進層30およびその近傍の上方に位置する非晶質シリコン膜56は第1の結晶性シリコン膜54になり、それ以外の領域の非晶質シリコン膜56は第2の結晶性シリコン膜55になる。このとき、第2の結晶性シリコン膜55の平均結晶粒径は約0.3μmΦである。

【0097】

結晶化工程において、非晶質シリコン膜56のYAGレーザの第2高調波に対する吸収係数は9.31×104cm-1程度と小さいので、照射された第2高調波の大部分は非晶質シリコン膜56を透過して、モリブデン膜からなる加熱促進層30に到達する。加熱促進層30に到達した第2高調波は加熱促進層30によって反射され、非晶質シリコン膜56を裏面側から照射する。一方、加熱促進層が設けられていない領域では、非晶質シリコン膜56を透過した第2高調波は、さらに絶縁基板20も透過して外部に逃げるので、非晶質シリコン膜56を裏面側から照射することはない。

【0098】

その結果、図7(a)に示すように、加熱促進層30およびその近傍の上方に位置する非晶質シリコン膜56に照射されるレーザビームの実効的な照射量が大きくなる。これにより、加熱促進層30およびその近傍の上方に位置する非晶質シリコン膜56は十分に溶融固化し、第1の結晶性シリコン膜54になる。一方、下方に加熱促進層が設けられていない非晶質シリコン膜56に照射されるレーザビームの実効的な照射量は大きくならないので、非晶質シリコン膜56は十分に溶融固化することができず、第2の結晶性シリコン膜55になる。

【0099】

なお、加熱促進層30がタングステン膜からなる場合には、非晶質シリコン膜56を透過したYAGレーザの第2高調波は、加熱促進層30に吸収されて熱エネルギーに変換される。これにより、非晶質シリコン膜56はその裏面側から加熱され、第1の結晶性シリコン膜54になる。

【0100】

また、加熱促進層30を設けることによって、YAGレーザの設定条件のマージンを大きくできるので、非晶質シリコン膜56に安定な第2高調波を照射することができる。また、YAGレーザ発振器は単純な構造であるので、メンテナンスが長期間不要になる。これにより、YAGレーザ発振器の稼働時間を長くして、ランニングコストを安価にすることができる。

【0101】

また、波長が370〜650nmのレーザビーム18を非晶質シリコン膜56に照射してもよい。波長が370〜650nmのレーザビーム18に対する非晶質シリコン膜の吸収係数は、YAGレーザの第2高調波(波長532nm)の場合と同様に小さい。このため、波長が370〜650nmのレーザビーム18を照射した場合にも、YAGレーザの第2高調波を照射した場合と同様の効果が得られる。

【0102】

また、レーザビーム18の走査速度を5cm/secよりも遅くすれば、非晶質シリコン膜56が過剰なエネルギーを受けて蒸発するため、良好な結晶性シリコン膜を形成することができない。一方、レーザビーム18の走査速度を3m/secよりも速くすれば、走査速度が速すぎて、非晶質シリコン膜56を確実に溶融固化することができない。そこで、レーザビーム18の走査速度は、5cm/sec以上かつ3m/sec以下であることが好ましい。

【0103】

このようにして、同一の絶縁基板20上に、結晶の配向および平均結晶粒径が異なる第1の結晶性シリコン膜54および第2の結晶性シリコン膜55が形成される。図10は、アクティブマトリクス基板100に形成されるべき周辺回路TFT110および画素TFT111の領域における、第1の結晶性シリコン膜54および第2の結晶性シリコン膜55の形状を示す平面図である。図10に示すように、周辺回路TFT110の半導体層50が形成されるべき領域の非晶質シリコン膜56はすべて第1の結晶性シリコン膜54になり、画素TFT111の半導体層51が形成されるべき領域の非晶質シリコン膜56はすべて第2の結晶性シリコン膜55になっている。次に、これらの第1の結晶性シリコン膜54および第2の結晶性シリコン膜55を用いて周辺回路TFT110および画素TFT111を形成する方法を説明する。

【0104】

図7(b)に示すように、第1の結晶性シリコン膜54および第2の結晶性シリコン膜55を、フォトリソグラフィ法を用いてパターニングする。これにより、第1の結晶性シリコン層52および第2の結晶性シリコン層53が形成される。次に、第1の結晶性シリコン層52と第2の結晶性シリコン層53を含む絶縁基板20を覆うように、例えば厚さが100nmの二酸化シリコン膜からなるゲート絶縁膜60を成膜する。ゲート絶縁膜60は、原料ガスとしてTEOS等を使用するAPCVD(Atmospheric Pressure CVD)法によって成膜される。なお、ゲート絶縁膜60は、二酸化シリコン膜の他に、窒化シリコン膜、酸窒化シリコン膜等であってもよく、またこれらの膜を適宜選択して積層した積層絶縁膜であってもよい。

【0105】

図7(c)に示すように、ゲート絶縁膜60上に、スパッタリング法を用いて、例えば厚さが300nmのアルミニウム(Al)膜71を成膜する。次に、図8(a)に示すように、フォトリソグラフィ法を用いてアルミニウム膜71をパターニングして、ゲート絶縁膜60上にゲート電極70を形成する。なお、ゲート電極70は、アルミニウム膜71の他に、例えば、タングステン膜、モリブデン膜、タンタル(Ta)膜、およびチタン(Ti)膜等の高融点金属膜や、これら高融点金属の窒化物膜等から形成してもよく、またこれらの膜から適宜選択して積層した積層金属膜から形成してもよい。また、ゲート電極70を形成する際に、ゲート配線(図示しない)も同時に形成する。

【0106】

図8(b)に示すように、ゲート電極70をマスクとして、第1の結晶性シリコン層52と第2の結晶性シリコン層53に、例えばリン(P)等のn型不純物元素をイオン注入し、電気炉で活性化アニールを行う。

【0107】

図8(c)に示すように、活性化アニールを行なうことにより、第1の結晶性シリコン層52のゲート電極70で覆われた領域には、真性領域であるチャネル領域50cが形成され、チャネル領域50cの両側にはn型不純物領域であるソース領域50sおよびドレイン領域50dがそれぞれ形成される。同様にして、第2の結晶性シリコン層53にも、チャネル領域51c、ソース領域51sおよびドレイン領域51dが形成される。次に、ゲート電極70を含む絶縁基板20を覆うように、APCVD法を用いて、例えば厚さが500nmの窒化シリコン膜からなる層間絶縁膜80を成膜する。次に、層間絶縁膜80およびゲート絶縁膜60に、第1の結晶性シリコン層52からなる半導体層50のソース領域50sおよびドレイン領域50dに達するコンタクトホール85と、第2の結晶性シリコン層53からなる半導体層51のソース領域51sおよびドレイン領域51dに達するコンタクトホール85とをそれぞれ開孔する。

【0108】

次に、層間絶縁膜80を含む絶縁基板20を覆うように、スパッタリング法を用いて、チタン膜、アルミニウム膜およびチタン膜を順に成膜した積層金属膜(図示しない)を形成する。図4に示すように、フォトリソグラフィ法を用いて積層金属膜をパターニングすることにより、層間絶縁膜80上に延びる引き出し電極90s,90dを形成する。これにより、引き出し電極90sは、コンタクトホール85を介して、ソース領域50s,51sと接続され、引き出し電極90dは、コンタクトホール85を介して、ドレイン領域50d,51dと接続される。さらにその後の熱処理によってそれらはオーミック接続される。なお、引き出し電極90s,90dを形成する際に、ソース配線(図示しない)も同時に形成する。

【0109】

これにより、図4に示す周辺回路TFT110および画素TFT111が形成される。なお、引き出し電極90s,90dは、チタン膜、アルミニウム膜およびチタン膜を順に積層した積層金属膜の他に、例えばタングステン膜、チタン膜、またはアルミニウム膜等の単層金属膜から形成してもよく、またはこれらの膜から適宜選択して積層した積層金属膜から形成してもよい。

【0110】

次に、引き出し電極90s,90dを含む絶縁基板20を覆うように、プラズマCVD法によって窒化シリコン膜からなるパッシベーション膜(図示しない)を成膜する。なお、画素TFT111では、さらに平坦化膜、透明導電膜、画素電極等が形成されるが、それらの図示および説明を省略する。

【0111】

このようにして、周辺回路TFT110および画素TFT111を含むアクティブマトリクス基板100が製造される。

【0112】

<1.8 効果>

本実施形態によれば、下方に加熱促進層30が設けられた非晶質シリコン膜56にレーザビームを照射するので、非晶質シリコン膜56に照射されるレーザビームの実効的な照射量は設定値よりも大きくなり、非晶質シリコン膜56は結晶の配向がレーザビームの走査方向に揃った第1の結晶性シリコン膜54になる。一方、下方に加熱促進層30が設けられていない非晶質シリコン膜56に、同じ照射量のレーザビームを照射しても、照射量は実効的に大きくならないので、非晶質シリコン膜56は結晶の配向がランダムな第2の結晶性シリコン膜55になる。

【0113】

また、レーザビームを反射または吸収して非晶質シリコン膜56の裏面側からの加熱を促進させるための加熱促進層30を形成し、非晶質シリコン膜56にレーザビームを照射する。加熱促進層30はレーザビームを反射または吸収して、加熱促進層30の上方およびその近傍の非晶質シリコン膜56を加熱する。これにより、下方に加熱促進層30が形成された非晶質シリコン膜56およびその近傍に照射されるレーザビームの照射量が実効的に大きくなるので、結晶の配向が揃った第1の結晶性シリコン膜54になる。このように加熱促進層30が形成される位置を精度よく制御して、第1の結晶性シリコン膜54が形成される位置を高い精度で制御することができる。また、第1の結晶性シリコン膜54の位置が決まると、結晶の配向がランダムな第2の結晶性シリコン膜55が形成される位置も決まる。その結果、第1および第2の結晶性シリコン膜54,55からなる周辺回路TFT110と画素TFT111とを例えば3μm程度の距離まで近接させて配置することができるので、これらを高集積化したアクティブマトリクス基板100を製造することができる。

【0114】

また、後述する実施例の評価結果から、第1の結晶性シリコン層52を用いて周辺回路TFT110を形成し、第2の結晶性シリコン層53を用いて画素TFT111を形成すれば、周辺回路TFT110のキャリア移動度の低下を抑制することができると共に、画素TFT111間の閾値電圧のばらつきを低減することができる。これにより、アクティブマトリクス基板100の電気的特性を所望の特性にすることができる。また、このようなアクティブマトリクス基板100を用いて構成された液晶表示装置1は、輝度や色のばらつきが少なく、安定した画像を表示することができる。

【0115】

<1.9 実施例>

本実施形態の製造方法により、以下に説明する作製方法で第1の結晶性シリコン層52と第2の結晶性シリコン層53を形成し、第1の結晶性シリコン層52を用いて周辺回路TFT110を、第2の結晶性シリコン層53を用いて画素TFT111をそれぞれ50個ずつ作製した。なお、画素TFT111のチャネル領域51cのサイズは4×4μmであり、周辺回路TFT110のチャネル領域50cのサイズは20×20μmである。

【0116】

<1.9.1 作製方法>

まず、ガラス基板上の周辺回路TFT110を形成すべき領域上に、厚さが150nmの加熱促進層30を形成した。次に、加熱促進層30を含むガラス基板を覆うように、ベースコート膜40を成膜した。このベースコート膜40は、厚さが100nmの二酸化シリコン膜からなる。ベースコート膜40上に、さらに厚さ50nmの非晶質シリコン膜56を成膜した。

【0117】

次に、ビーム形状を、長さ2mm、幅50μmの楕円状になるように成形したYAGレーザのレーザビームを図9の矢印で示す方向に20cm/secの速度で走査しながら、非晶質シリコン膜56にYAGレーザの第2高調波を照射した。このとき、YAGレーザの第2高調波を出力するレーザ発振器のパワーを1.2Wに設定した。これにより、図10に示すように、加熱促進層30およびその近傍の上方に位置する非晶質シリコン膜56は第1の結晶性シリコン膜54になり、それ以外の領域の非晶質シリコン膜56は第2の結晶性シリコン膜55になった。なお、第2の結晶性シリコン膜55の平均結晶粒径は約0.3μmφであった。

【0118】

次に、第1の結晶性シリコン膜54および第2の結晶性シリコン膜55をパターニングすることによって第1および第2の結晶性シリコン層52,53をそれぞれ形成した。次に、第1および第2の結晶性シリコン層52,53を覆うように、厚さが100nmの二酸化シリコン膜からなるゲート絶縁膜60を成膜した。ゲート絶縁膜60上に、厚さが100nmのアルミニウム膜71からなるゲート電極70を形成した。ゲート電極70をマスクにして、第1および第2の結晶性シリコン層52,53にリンをイオン注入した。これにより、第1の結晶性シリコン層52からなる半導体層50のゲート電極70で覆われた領域には、真性領域であるチャネル領域50cが形成され、チャネル領域50cの両側にはn型不純物領域であるソース領域50sおよびドレイン領域50dがそれぞれ形成された。同様にして、第2の結晶性シリコン層53からなる半導体層51にも、チャネル領域51c、ソース領域51sおよびドレイン領域51dが形成された。

【0119】

次に、厚さが500nmの二酸化シリコン膜からなる層間絶縁膜80を成膜した。層間絶縁膜80およびゲート絶縁膜60に、コンタクトホール85を開孔した。次に、これらのコンタクトホール85を介して、ソース領域50s,51sに電気的に接続された引き出し電極90sと、ドレイン領域50d,51dに電気的に接続された引き出し電極90dとを形成した。引き出し電極90s,90dは、厚さが100nmのチタン膜、厚さが300nmのアルミニウム膜、および厚さが100nmのチタン膜を順に積層した積層金属膜を用いて形成された。

【0120】

<1.9.2 評価>

上記作製方法によって作成したTFTの観察および各種の測定から、次のことがわかった。

【0121】

まず、第1および第2の結晶性シリコン膜54,55の結晶粒を後方拡散電子回折像法(Electron Backscatter Diffraction Patterns法、以下、「EBSP法」という)によって分析した。その結果、下方に加熱促進層30が設けられた非晶質シリコン膜56およびその近傍の非晶質シリコン膜56では、結晶の配向がレーザビームの走査方向に揃った結晶粒が観察された。また、下方に加熱促進層が設けられていない非晶質シリコン膜56では、結晶の配向がランダムな結晶粒が観察され、その平均粒径は約0.3μmφであった。このことから、結晶化工程により、下方に加熱促進層30が設けられた非晶質シリコン膜56およびその近傍の非晶質シリコン膜56は第1の結晶性シリコン膜54になり、下方に加熱促進層が設けられていない非晶質シリコン膜56は、第2の結晶性シリコン膜55になることがわかる。

【0122】

また、第1および第2の結晶性シリコン膜54,55をパターニングした半導体層50,51をそれぞれ有する周辺回路TFT110および画素TFT111について、キャリア移動度およびTFT間の閾値電圧のばらつきを測定した。その結果、周辺回路TFT110については、キャリア移動度は370cm2/V・secであり、50個分の閾値電圧のばらつきは0.15Vと大きくなった。一方、画素TFT111については、キャリア移動度は180cm2/V・secであり、50個分の閾値電圧のばらつきは0.05Vと、周辺回路TFT110の場合に比べて小さくなった。

【0123】

<2.第2の実施形態>

本発明の第2の実施形態に係る液晶表示装置の構成、製造方法、および動作は、第1の実施形態の係る液晶表示装置1の構成、製造方法、および動作とそれぞれ同じであるので、それらの図および説明を省略する。

【0124】

<2.1 ダブルゲート周辺回路TFT>

本実施形態に係るアクティブマトリクス基板200は、第1の実施形態に係るアクティブマトリクス基板100に設けられていた周辺回路TFT110および画素TFT111に加えて、さらにダブルゲート構造の周辺回路TFT210を備えている。ダブルゲート構造の周辺回路TFT210は、シングルゲート構造の周辺回路TFT110に設けられた加熱促進層30と同じ構造の加熱促進層130をボトムゲート電極としても使用するTFTであって、周辺回路TFT110と共に周辺回路を構成する。そこで、以下での説明では、ダブルゲート構造の周辺回路TFT210をダブルゲート周辺回路TFT210という。

【0125】

図11は、アクティブマトリクス基板200に形成された周辺回路TFT110、ダブルゲート周辺回路TFT210および画素TFT111の構成を示す断面図である。図11に示す周辺回路TFT110および画素TFT111の構成は、図4に示す第1の実施形態の周辺回路TFT110および画素TFT111とそれぞれ同じ構成である。そこで、周辺回路TFT110および画素TFT111の各構成要素には、図4に示す周辺回路TFT110および画素TFT111の各構成要素に付した参照符号と同じ参照符号を付して説明を省略する。また、ダブルゲート周辺回路TFT210の構成要素は、周辺回路TFT110の構成要素と一部異なっている。そこで、ダブルゲート周辺回路TFT210の構成要素のうち、周辺回路TFT110の構成要素と同じ構成要素には同じ参照符号を付し、異なる構成要素を中心に説明する。

【0126】

ダブルゲート周辺回路TFT210は、図4に示す周辺回路TFT110と異なり、周辺回路TFT110のチャネル領域50cを挟むように、チャネル領域50cの上方にゲート電極70が設けられ、下方にボトムゲート電極として機能する加熱促進層130が設けられている。

【0127】

ダブルゲート周辺回路TFT210が形成されるべき領域の絶縁基板20上に加熱促進層130が形成されている。加熱促進層130の大きさは、周辺回路TFT110が形成されるべき領域に形成された加熱促進層30よりも小さく、後述する半導体層150のチャネル領域150cよりも少し大きい程度である。この加熱促進層130は、完成後のダブルゲート周辺回路TFT210においては、後述するようにボトムゲート電極として機能する。加熱促進層130を含む絶縁基板20を覆うようにベースコート膜40が形成されている。ベースコート膜40は、ダブルゲート周辺回路TFT210の完成後にボトムゲート電極のゲート絶縁膜として機能する。

【0128】

ベースコート膜40上に島状の半導体層150が形成されている。半導体層150は、第1の結晶性シリコン層とその両側に形成された第2の結晶性シリコン層とからなり、第1の結晶性シリコン層の中央にチャネル領域150cが形成されている。チャネル領域150cの両側には、それぞれソース領域150sおよびドレイン領域150dが形成されている。チャネル領域150cは不純物元素を含まない真性領域からなり、ソース領域150sおよびドレイン領域150dはリン等のn型不純物元素をイオン注入されたn型不純物領域からなる。

【0129】

ダブルゲート周辺回路TFT210のソース領域150sおよびドレイン領域150dは、周辺回路TFT110のソース領域50sおよびドレイン領域50dと異なり、第1の結晶性シリコン層だけでなく、第2の結晶性シリコン層も含む。具体的には、ソース領域150sおよびドレイン領域150dのチャネル領域150cに隣接する一部は、第1の結晶性シリコン層からなり、残りの大部分は第2の結晶性シリコン層からなる。このようになる理由について説明する。

【0130】

図12は、アクティブマトリクス基板200に形成されるべき周辺回路TFT110、ダブルゲート周辺回路TFT210、および画素TFT111の領域における第1の結晶性シリコン膜54および第2の結晶性シリコン膜55の形状を示す平面図である。図12に示すように、周辺回路TFT110の第1の結晶性半導体層となるべき非晶質シリコン膜の全体が加熱促進層30の上方に形成されている。このため、照射されるレーザビームだけでなく、加熱促進層30による反射または加熱により、加熱促進層30上の非晶質シリコン膜は溶融固化して結晶の配向が揃った第1の結晶性シリコン膜54になる。

【0131】

一方、ダブルゲート周辺回路TFT210では、非晶質シリコン膜のうち、チャネル領域およびその近傍のみが加熱促進層130の上方に形成され、ソース領域およびドレイン領域の下方には加熱促進層が設けられていない。このような非晶質シリコン膜にレーザビームを照射すれば、溶融固化して第1の結晶性シリコン膜54になるのはチャネル領域になるべき領域と、チャネル領域に隣接するソース領域およびドレイン領域になるべき領域の一部であり、ソース領域およびドレイン領域になるべき領域の大部分は、第2の結晶性シリコン膜55になる。その結果、ソース領域150sおよびドレイン領域150dのチャネル領域150cに隣接する一部は、第1の結晶性シリコン膜54からなり、残りの大部分は第2の結晶性シリコン膜55からなる。なお、画素TFT111が形成されるべき領域の下方には、加熱促進層が形成されていないので、非晶質シリコン膜は第2の結晶性シリコン膜55になる。

【0132】

図11に示すように、半導体層150を含む絶縁基板20を覆うようにゲート絶縁膜60が形成されている。さらに、半導体層150のチャネル領域150cと対向するゲート絶縁膜60上の位置にゲート電極70が形成されている。ゲート電極70は後述するコンタクトホール75を介して加熱促進層130と電気的に接続されている。これにより、加熱促進層130もゲート電極(ボトムゲート電極)として機能し、ゲート電圧がゲート電極70および加熱促進層130によってチャネル領域150cに印加される。

【0133】

層間絶縁膜80、引き出し電極90s,90dの構成は、周辺回路TFT110の場合と同じであるため、それらの説明を省略する。ダブルゲート周辺回路TFT210のチャネル領域150cのサイズは、周辺回路TFT110のサイズと同じく、例えば20×20μmである。

【0134】

図13は、アクティブマトリクス基板200に形成されたダブルゲート周辺回路TFT210の構成を示す平面図である。図13に示すように、半導体層150のチャネル領域150cを上下から挟むように加熱促進層130とゲート電極70が形成されている。また半導体層150のソース領域150sおよびドレイン領域150dには、引き出し電極90s,90dがそれぞれオーミック接続されている。

【0135】

このようなダブルゲート周辺回路TFT210において、加熱促進層130とゲート電極70とは、チャネル領域150cとなるべき領域の外側(図13の上方)に形成されたコンタクトホール75によって接続されている。これにより、ゲート電極70にゲート電圧を印加すれば、コンタクトホール75を介して加熱促進層130にも同じゲート電圧が印加され、加熱促進層130がボトムゲート電極として機能する。また、加熱促進層130の上方に形成されたチャネル領域150cおよびその近傍は第1の結晶性シリコン層52によって構成され、ソース領域150sおよびドレイン領域150dは第1の結晶性シリコン層52と第2の結晶性シリコン層53とによって構成されている。

【0136】

<2.2 アクティブマトリクス基板の製造方法>

次に、アクティブマトリクス基板200の製造方法を説明する。図14(a)〜図14(d)、図15(a)〜図15(c)、図16(a)〜図16(c)は、アクティブマトリクス基板200の各製造工程をそれぞれ示す断面図である。アクティブマトリクス基板200の製造工程には、第1の実施形態の場合と同様に、加熱促進層形成工程と、絶縁膜形成工程と、非晶質半導体膜成膜工程と、結晶化工程とが含まれる。これらの工程により、周辺回路TFT110と、ダブルゲート周辺回路TFT210と、画素TFT111の各半導体層50,150,51が結晶化される。なお、周辺回路TFT110および画素TFT111については第1の実施形態の場合と同じ参照符号を付してその説明を簡略に行ない、ダブルゲート周辺回路TFT210の製造工程を中心に第1の実施形態の各製造工程と比較しつつ説明する。

【0137】

<2.2.1 加熱促進層形成工程>

図14(a)に示す工程は、図6(a)に示す第1の実施形態の工程に対応する工程である。絶縁基板20上に、例えば厚さが150nmのモリブデン膜31を成膜する。次に、図14(b)に示すように、モリブデン膜31を、フォトリソグラフィ法を用いてパターニングし、ダブルゲート周辺回路TFT210が形成されるべき領域に加熱促進層130を形成する。この加熱促進層130は、周辺回路TFT110が形成されるべき領域に形成される加熱促進層30よりも小さい。この加熱促進層130は、ダブルゲート周辺回路TFT210の完成後には、そのボトムゲート電極として機能する。

【0138】

<2.2.2 絶縁膜形成工程>

図14(c)に示す工程は、図6(c)に示す第1の実施形態の工程に対応する工程である。加熱促進層130を含む絶縁基板20を覆うように、例えば厚さが100nmの二酸化シリコン膜からなるベースコート膜40を成膜する。ベースコート膜40は、プラズマCVD法等を用いて成膜される。

【0139】

<2.2.3 非晶質半導体膜成膜工程>

図14(d)に示す工程は、図6(d)に示す第1の実施形態の工程に対応する工程である。ベースコート膜40上に、例えば厚さ50nmの非晶質シリコン膜56を成膜する。非晶質シリコン膜56は、原料ガスとしてシランガス(SiH4)を用いたLPCVD(Low Pressure CVD)法等を用いて成膜される。

【0140】

<2.2.4 結晶化工程>

図15(a)に示す工程は、図7(a)に示す第1の実施形態の工程に対応する工程である。YAGレーザの第2高調波を非晶質シリコン膜56に照射し、非晶質シリコン膜56を溶融固化して結晶化する。なお、YAGレーザのビーム形状および走査速度は第1の実施形態の場合と同じである。これにより、加熱促進層130の上方およびその近傍の領域の非晶質シリコン膜56は第1の結晶性シリコン膜54になり、それ以外の領域の非晶質シリコン膜56は、第2の結晶性シリコン膜55になる。

【0141】