半導体素子

【課題】 珪素単結晶を基板としてIII族窒化物半導体層を設けるのに際し、そのIII族窒化物半導体層を良質な結晶層とすることができ、素子特性を優れたものとすることができるようにする。

【解決手段】 本発明は、珪素単結晶からなる基板101上にIII族窒化物半導体からなる層を備えた半導体素子10において、上記基板101の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜102が設けられ、そのIV族元素膜102に接合させて上記III族窒化物半導体からなる接合層103が設けられているものである。

【解決手段】 本発明は、珪素単結晶からなる基板101上にIII族窒化物半導体からなる層を備えた半導体素子10において、上記基板101の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜102が設けられ、そのIV族元素膜102に接合させて上記III族窒化物半導体からなる接合層103が設けられているものである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子に関する。

【背景技術】

【0002】

従来から、珪素単結晶(シリコン)を基板とし成長させたIII−V族化合物半導体層を活性層として利用して半導体素子を作製する技術が開示されている(下記の特許文献1参照)。特に、短波長の可視光を出射する発光ダイオード(英略称:LED)やレーザダイオード(英略称:LD)にあっては、シリコン基板上にIII族窒化物半導体層を活性層(発光層)として備えた積層構造体から構成されている(下記の特許文献2参照)。また、シリコン基板上に形成した窒化ガリウム(GaN)層を活性層(チャネル(channel)層)としてショットキー(Schottky)接合型電界効果トランジスタ(英略称:MESFET)を作製する技術が開示されている(下記の特許文献3参照)。

【特許文献1】米国特許 US−6,069,021号

【特許文献2】特開平7−288231号公報

【特許文献3】特開平10−287497号公報

【0003】

III族窒化物半導体層は、格子不整合を緩和するためにシリコン基板の表面上に炭化珪素(SiC)から成る緩衝膜を設けた後、形成するのが一般的である(下記の非特許文献1参照)。立方晶のSiC(所謂、3C型SiC)から成る緩衝膜を設けるために、予め、シリコン基板の表面をアセチレン(分子式:C2H2)を使用して炭化する手段が採られている(下記の非特許文献2参照)。

【非特許文献1】古川 清二郎、雨宮 好仁編著、「シリコン系ヘテロデバイス」、平成3年7月30日、丸善(株)発行、第5章、92頁。

【非特許文献2】S. Motoyama and S. Kaneda, “Low-Temperature Growth of 3C-SiC by Gas Source Molecular Beam Epitaxial Method”,アプライド フィジクス レターズ(Appl. Phys. Lett.), 第54巻、1989年(米国)、242頁。

【0004】

立方晶の3C型SiCの格子定数は、0.436ナノメーター(nm)である。これに対し、例えば、立方晶のGaNの格子定数は0.451nmある。従って、3C型SiCと立方晶のGaNとは良好な格子整合の関係にあるとは言えない。一方、六方晶のウルツ鉱(Wurtzite)型GaNのa軸は0.319nmである。従って、3C型SiCは、六方晶のGaNとも格子整合する関係にない。この格子のミスマッチ(mismatch)に起因して、従来の3C型炭化珪素層上に形成するIII族窒化物半導体層内には、ミスフィット(misfit)転位等の結晶欠陥が導入されてしまう。

【0005】

従って、転位等の結晶欠陥密度が充分に低い良質の珪素単結晶(シリコン)を基板とした場合でも、結晶欠陥が少なく、素子(デバイス)特性を充分に顕現するための良質のIII族窒化物半導体結晶層は、従来の炭化珪素層を利用する限り、充分に安定して形成できていない。このため、良好な電気伝導性、熱伝導性、及び明瞭な劈開性を呈する珪素単結晶の優位性を利用した発光素子、例えば順方向電圧(Vf)の低いLEDや劈開結晶面を共振面とするLD、また放熱性に優れるが故に低損失の電力(パワー)トランジスタを作製するのに支障を来している。

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、上記の従来技術の問題点を克服すべくなされたもので、珪素単結晶を基板としてIII族窒化物半導体層を設けるのに際し、そのIII族窒化物半導体層を良質な結晶層とすることができ、素子特性を優れたものとすることができる半導体素子を提供することを目的とする。

【課題を解決するための手段】

【0007】

1)上記目的を達成するために、第1の発明は、珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子において、上記基板の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜が設けられ、そのIV族元素膜に接合させて上記III族窒化物半導体からなる接合層が設けられているものである。

【0008】

2)第2の発明は、上記した1)項に記載の発明の構成において、上記基板は導電性を有し、上記IV族元素膜はその基板と同一の伝導形の導電性を有しているものである。

【0009】

3)第3の発明は、上記した2)項に記載の発明の構成において、上記接合層は、上記IV族元素膜と同一の伝導形の導電性を有しているものである。

【0010】

4)第4の発明は、上記した1)項に記載の発明の構成において、上記基板、IV族元素膜および接合層を高抵抗とするものである。

【0011】

5)第5の発明は、上記した4)項に記載の発明の構成において、上記接合層を上記基板よりさらに高抵抗とするものである。

【0012】

6)第6の発明は、上記した1)項から5)項の何れか1項に記載の発明の構成において、上記IV族元素膜は上記基板の一表面と同一の面方位を有するものである。

【0013】

第7の発明は、上記した6)項に記載の発明の構成において、上記基板の{001}表面上に上記IV族元素膜が設けられ、そのIV族元素膜の表面は{001}結晶面から構成され、上記接合層はそのIV族元素膜の{001}結晶面に形成されて立方晶の結晶層から構成されているものである。

【0014】

第8の発明は、上記した6)項に記載の発明の構成において、上記基板の{111}表面上に上記IV族元素膜が設けられ、そのIV族元素膜の表面は{111}結晶面から構成され、上記接合層はそのIV族元素膜の{111}結晶面に形成されて六方晶の結晶層から構成されているものである。

【0015】

第9の発明は、上記した1)項から8)項の何れか1項に記載の発明の構成において、上記IV族元素膜は、ゲルマニウムの組成比(=X)を0.10以上で0.85以下とする炭化珪素ゲルマニウム(組成式Si1-XGeXC:0.10≦X≦0.85)からなるものである。

【発明の効果】

【0016】

本発明によれば、珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子において、上記基板の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜を設け、そのIV族元素膜に接合させてIII族窒化物半導体からなる接合層を設ける構成としたので、Si1-XGeXCからなるIV族元素膜と、III族窒化物半導体からなる接合層との間での良好な格子マッチングにより、結晶性に優れるIII族窒化物半導体層が得られ、従って、そのIII族窒化物半導体層の良好な結晶性から素子特性に優れる半導体素子を提供できる。

【0017】

特に、本発明によれば、導電性の珪素単結晶を基板とし、炭化珪素ゲルマニウム(Si1-XGeXC)膜(IV族元素膜)を、その珪素単結晶基板と同一の伝導形の導電性の結晶層から構成することとしたので、珪素単結晶基板側から供給される素子駆動電流を、基板の表面に垂直な方向(縦方向)に流通させて動作させる半導体素子、例えば、受光素子(フォトダイオード)を好都合に構成できる。

【0018】

特に、本発明によれば、導電性珪素単結晶基板と、炭化珪素ゲルマニウム(Si1-XGeXC)膜と、その膜に接合させて設けるIII族窒化物半導体層とを、同一の伝導形としたので、珪素単結晶基板側から供給される素子を駆動させるための電流を、基板の表面に垂直な方向(縦方向)に流通させて動作させる半導体素子、例えばLEDやLDといった発光素子を好都合に構成できる。

【0019】

特に、本発明によれば、高抵抗の珪素単結晶基板上に、高抵抗の炭化珪素ゲルマニウム(Si1-XGeXC)膜を介して高抵抗のIII族窒化物半導体接合層を設ける構成としたので、例えば、高抵抗のIII族窒化物半導体層を緩衝層或いは電子走行層とする電界効果型トランジスタを好適に構成できる。

【0020】

特に、本発明によれば、III族窒化物半導体接合層を、基板を成す珪素単結晶を超える高抵抗の結晶層から構成したので、素子駆動電流のIII族窒化物半導体接合層を介しての漏洩(leak)を低減でき、従って、高周波帯域で動作する高性能の電界効果型トランジスタを構成するのに効果を上げられる。

【0021】

特に、本発明によれば、炭化珪素ゲルマニウム(Si1-XGeXC)膜を、それを設ける珪素単結晶基板と同一の表面の面方位を有する結晶層から構成したので、炭化珪素ゲルマニウム(Si1-XGeXC)膜に接合させて設けるIII族窒化物半導体接合層の結晶系を画一的に制御するのに効果を上げられる。

【0022】

特に、本発明によれば、珪素単結晶基板の{001}表面上に設けた、表面の面方位を{001}とする炭化珪素ゲルマニウム(Si1-XGeXC)膜を用いてIII族窒化物半導体接合層を設ける構成としたので、それに接合させて設けるIII族窒化物半導体接合層を立方晶の結晶層とするのに効果を上げられ、これにより、例えば、立方晶結晶の明瞭な劈開性を利用する端面共振型のIII族窒化物半導体LDを好適に構成できる。

【0023】

また、本発明によれば、珪素単結晶基板の{111}表面上に設けた、表面の面方位を{111}とする炭化珪素ゲルマニウム(組成式Si1-XGeXC)膜を用いてIII族窒化物半導体接合層を設けることとしたので、それに接合させて設けるIII族窒化物半導体接合層を六方晶の結晶層から構成するのに効果を上げられ、これにより、例えば、ピエゾ(piezo)効果の大きな六方晶のIII族窒化物半導体層を利用する2次元電子型電界効果トランジスタを好適に構成できる。

【0024】

特に、本発明によれば、ゲルマニウム(Ge)の組成比(=X)を0.10以上で0.85以下とする炭化珪素ゲルマニウム(Si1-XGeXC:0.10≦X≦0.85)膜を介してIII族窒化物半導体接合層を設ける構成としたので、III族窒化物半導体接合層を、それと格子マッチングに優れるSi1-XGeXC(0.10≦X≦0.85)層を下地層として形成でき、その結果、結晶性に優れるIII族窒化物半導体接合層を構成できるため、性能に優れるIII族窒化物半導体発光デバイスや電子デバイスを提供できる。

【発明を実施するための最良の形態】

【0025】

本発明は、珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子において、その基板の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜を設け、そのIV族元素膜に接合させてIII族窒化物半導体からなる接合層を設けるようにしている。

【0026】

本発明に係るIV族元素膜としての炭化珪素ゲルマニウム(Si1-XGeXC:0<X<1)膜は、{001}や{111}結晶面等を表面とするシリコン基板上に、常圧(略大気圧)或いは減圧化学的気相堆積(英略称:CVD)法や高真空中で成膜する分子線エピタキシャル(英略称:MBE)法等の気相エピタキシャル手段等で形成する。特に、MBE法を利用して、アセチレン(分子式C2H2)等の炭化水素ガス、珪素(元素記号:Si)、及びゲルマニウム(元素記号:Ge)を含むビーム(beam)を高真空中でシリコン基板の表面に吹き付けて、Si1-XGeXCを形成する手法が簡便であり、また、好適である。

【0027】

MBE法によりSi1-XGeXC膜を高真空中で形成するのに際し、高真空の成長環境を利用して、予め表面に珪素原子の再配列構造を出現させる様にシリコン基板を加熱処理すると、結晶欠陥が少なく結晶性に優れるSi1-XGeXC膜を得るのに好適となる。例えば、{001}結晶面を表面とする{001}−シリコン基板にあっては、高真空中で850℃〜1100℃に加熱して、その表面に(2×1)の再配列構造を出現させる処理を施しておくのが好ましい。また、{111}結晶面を表面とする{111}−シリコン基板にあっては、700℃〜900℃で真空加熱処理を施し、(7×7)の再配列構造を出現させた後、Si1-XGeXC膜を形成するのが好ましい。

【0028】

シリコン基板上に形成するSi1-XGeXC膜は、その上に、表面が平坦であり、且つ連続したIII族窒化物半導体層を帰結するのに充分な膜厚を有するのが望ましい。Si1-XGeXC膜は、また、シリコン基板の表面の全面を略一様に被覆する様に設けられているのが好ましいため、2ナノメーター(単位:nm)以上の層厚を有するのが望ましい。また、極端に厚いSi1-XGeXC膜では、表面の平坦性が損なわれてしまうため、上層として平坦性のあるIII族窒化物半導体層を充分に安定して得るに至らない。従って、Si1-XGeXC膜の層厚は、2nm以上で200nm以下とするのが好適である。

【0029】

Si1-XGeXC膜の伝導形を、基板として用いるシリコン単結晶の伝導形と合致させると、シリコン基板の表面に対し垂直方向に素子を駆動させるための電流(素子駆動電流)を流通させる半導体素子を構成する上で好適である。例えば、n形のシリコン基板上に、n形のSi1-XGeXC膜を設ける。n形のSi1-XGeXC膜を形成する際の不純物(ドーパント)としては、n形SiGe混晶層を得る場合と同様に例えば、アンチモン(元素記号:Sb)を用いることができる。p形Si1-XGeXC膜を得るには、例えば、硼素(元素記号:B)をp形のドーパントとして利用できる。

【0030】

更に、Si1-XGeXCから成るIV族元素膜に接合させて設けるIII族窒化物半導体からなる接合層を、基板およびSi1-XGeXC膜と同一の伝導形を有する導電性の結晶層から構成すると、シリコン基板の表面に対し垂直方向に素子駆動電流を流通させる半導体素子を構成する上で更に好適である。例えば、n形シリコン基板上にn形のSi1-XGeXC膜を設け、その上にn形のIII族窒化物半導体層を設ける構成とする。そのn形III族窒化物半導体層上に、例えば、III族窒化物半導体層からなるpn接合型ヘテロ(hetero)構造の発光部を設けてIII族窒化物半導体LEDを構成する。また、例えば、III族窒化物半導体LDを構成する。

【0031】

一方で、シリコン基板の表面に設けるSi1-XGeXC膜を高抵抗層とし、また、それに接合させて設けるIII族窒化物半導体から成る接合層を、高抵抗の結晶層から構成すると、例えば、MESFETを作製するのに利便となる。MESFETを作製するに際し、用いるシリコン基板は、抵抗率にして1キロオーム・センチメートル(KΩ・cm)を超える高抵抗であるのが好ましい。また、MESFETを作製する場合、シリコン基板上に設けるSi1-XGeXC膜及びIII族窒化物半導体接合層は、それを超えて大とする抵抗率を有する高抵抗層であるのが好ましい。MESFETのドレイン(drain)電流の基板への不必要な漏洩を抑止するためである。また、例えば、シリコン基板の同一の表面側上に設けた半導体層に陰極及び陽極の双方を設けてなるLEDを作製するのにも利用できる。高抵抗のSi1-XGeXC膜は不純物を故意に添加しないアンドープ(undope)で形成するのが得策である。

【0032】

接合層を形成するIII族窒化物半導体は、III族元素と、V族元素としての窒素(元素記号:N)とを必須の構成元素として含むIII−V族化合物半導体である。例えば、窒化アルミニウム・ガリウム(AlXGaYN:0≦X,Y≦1、X+Y=1)であり、窒化ガリウム・インジウム(GaXInYN:0≦X,Y≦1、X+Y=1)である。また、窒素と窒素とは別の砒素(元素記号:As)や燐(元素記号:P)等のV族元素を含む窒化燐化ガリウム(GaN1-ZPZ:0≦Z<1)、窒化燐化硼素(BN1-ZPZ:0≦Z<1)、窒化燐化アルミニウム・硼素(BXAlYGaN1-ZPZ:0≦X,Y≦1、X+Y=1、0≦Z<1)などである。特に、III族窒化物半導体素子を構成する主要な材料であるAlXGaYInZN(0≦X,Y,Z≦1、X+Y+Z=1)と格子のマッチングに優れるIII族窒化物半導体材料は優位に利用することができる。

【0033】

III族窒化物半導体層は、MBE法や有機金属化学的気相堆積(英略称:MOCVD)法などにより形成する。MOCVD法でAlXGaYN層を形成するのには、例えば、トリメチルガリウム(分子式(CH3)3Ga)やトリエチルガリウム(分子式(C2H5)3Ga)等をガリウム(Ga)源として、また、トリメチルアルミニウム(分子式(CH3)3Al)やトリイソブチルアルミニウム(分子式(i−C4H9)3Al)などの有機金属(英略称:MO)化合物をアルミニウム(Al)原料として使用する。窒素源としては、アンモニア(分子式NH3)、ヒドラジン(分子式N2H4)等を使用できる。熱分解する温度がより低い非対称型分子構造のジメチルヒドラジン(分子式(CH3)2H2N)類は、より低温でIII族窒化物半導体層を成長させるための窒素の原料として使用できる。

【0034】

また、例えば、AlXGaYInZN(0≦X,Y,Z≦1、X+Y+Z=1)と格子のマッチングに優れる、窒素と、砒素や燐等の窒素とは別のV族元素を含むIII族窒化物半導体層は、固体ソース(source)MBE法にあっては、砒素や燐の原料として例えば、固体砒素や固体燐を利用して形成できる。MOCVD法やガスソースMBE法にあっては、砒素や燐の原料としてアルシン(分子式AsH3)やホスフィン(分子式PH3)を例示できる。固体またはガスソースMBE法に拘らず、III族窒化物半導体層を構成する窒素(N)は、窒素プラズマなどから供給できる。

【0035】

特に、高抵抗なIII族窒化物半導体から成る接合層を利用して、例えば、MESFETを構成するのに際し、その接合層を、シリコン基板を超える高い抵抗を有する結晶層とすると、高性能な例えば、GaN系MESFETを構成するのに優位である。例えば、抵抗率を10KΩ・cmとするアンドープで高抵抗なシリコン基板上に、高抵抗なSi1-XGeXC膜を介して、100KΩ・cmを越す抵抗率を有する高抵抗なAlNからなるIII族窒化物半導体の接合層を設ける。禁止帯幅が広く、尚且つ、高抵抗な接合層を、例えば、チャネル(channel)層(電子走行層)の下地層として配置する構成によれば、ドレイン(drain)電流のピンチオフ(pinch−off)特性に優れる高周波GaN系FETを都合よく作製できる。

【0036】

例えば、表面を{001}結晶面とするSi1-XGeXC層は、{001}結晶面を表面とするシリコンを基板として用いることで形成できる。この{001}結晶面を表面とするSi1-XGeXC層は、その上に立方晶の閃亜鉛鉱結晶型のIII族窒化物半導体層を形成するための有効な下地層として利用できる。これにより、例えば、立方晶結晶の明瞭な劈開性を利用する端面共振型のIII族窒化物半導体LDを好適に構成できる。

【0037】

また、{111}結晶面を表面とするSi1-XGeXC層は、表面を{111}結晶面とするシリコンを基板として利用すれば形成できる。この、表面を{111}結晶面とするSi1-XGeXC層は、その上に六方晶のウルツ鉱結晶型のIII族窒化物半導体層を形成するための有効な下地層として利用できる。これにより、例えば、ピエゾ(piezo)効果の大きな六方晶のIII族窒化物半導体層を利用する2次元電子型電界効果トランジスタを好適に構成できる。

【0038】

Si1-XGeXC層上のIII族窒化物半導体層が立方晶であるか六方晶であるは、例えば、電子線回折法で取得される回折パターンから判別できる。

【0039】

本発明では特に、IV族元素膜のSi1-XGeXCのゲルマニウム(Ge)の組成比(=X)を0.10以上で0.85以下としている。それは、立方晶のGaNやAlN等のIII族窒化物半導体材料との良好なマッチングが得られるからである。Si1-XGeXCのゲルマニウム(Ge)の組成比(=X)が0.10より小では、これらのIII族窒化物半導体材料とのミスマッチング(mismatching)が大となり、良好な結晶性のIII族窒化物半導体層を得るに支障を来たすこととなる。また、Geの組成比が0.85を超えて大きくすると、同じく、Si1-XGeXC層とIII族窒化物半導体層との格子ミスマッチングが大となり不都合である。

【0040】

ゲルマニウム(Ge)の組成比(=X)を0.10以上で0.85以下とするSi1-XGeXC(0.10≦X≦0.85)層の格子定数は、0.438nmから0.451nmの範囲にある。このため、立方晶閃亜鉛鉱結晶型のGaN(格子定数=0.451nm)やAlN(格子定数=0.438nm)等との格子上のマッチングに優れる。また、Si1-XGeXC(0.10≦X≦0.85)層の(110)結晶面の間隔は、六方晶ウルツ鉱結晶型のGaN(a軸の長さ=0.319nm)やAlN(a軸の長さ=0.311nm)のa軸の長さと略一致する。従って、Si1-XGeXC(0.10≦X≦0.85)層を用いれば、格子のマッチング性により、結晶性の良好なIII族窒化物半導体層を形成できる。従って、性能に優れるIII族窒化物半導体発光デバイスや電子デバイスを提供できる。

【0041】

Si1-XGeXC(0.10≦X≦0.85)層にあって、Geの組成比(=X)を増加させるのにともない、格子定数は大きくなる。例えば、固体ソースMBE法でSi1-XGeXC層を形成するのに際し、アセチレン等の炭化水素系の供給量を一定に保ちつつ、Siに対するGeのフラックス(flux)強度の比率をより増大させれば、よりGe組成比を大とするSi1-XGeXC層を形成できる。

【実施例】

【0042】

(実施例1) (001)結晶面を表面とする(001)シリコン基板上に設けられたSiGeC膜を備えた積層構造体を用いて、半導体LEDを構成する場合を例にして、本発明を具体的に説明する。

【0043】

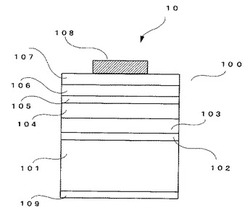

図1に、本実施例1に記載の窒化物半導体LED10の平面模式図を示す。また図2には、図1に示すLED10の破線A−A’に沿った断面模式図を示す。

【0044】

LED10を作製するための積層構造体100は、表面を(001)結晶面とするn形シリコン(珪素単結晶)を基板101として形成した。基板101を、約1×10-8パスカル(圧力単位:Pa)の高真空に保たれたMBE成長用チャンバー内において、1050℃で10分間にわたり加熱処理を施した。これにより、シリコン基板101の表面をなす(001)結晶面に(2×1)再配列構造を形成した。基板101の表面でのこの再配列構造の出現は、一般的な反射高速電子回折(英略称:RHEED)パターンから確認した。

【0045】

次に、清浄化されたシリコン基板101の表面をなす(001)結晶面上には、一般的な固体ソースMBE法により、540℃で、導電性のn形Si0.17Ge0.83CからなるSiGeC膜102を本発明の云うIV族元素膜として形成した。珪素の原料には、高純度珪素を用い、ゲルマニウムの原料には、高純度金属Geを用いた。また、炭素(元素記号:C)の原料には、高純度(純度6N)のアセチレンを用いた。SiGeC膜102の層厚は4nmとした。RHEEDパターンによれば、SiGeC膜102は立方晶の結晶層であり、その表面は、(001)面であった。

【0046】

n形SiGeC膜102の(001)結晶面からなる表面上には、MBE法によりSiドープn形GaN層(キャリア濃度=3×1018cm-3)103を、本発明の云うIII族窒化物半導体層からなる接合層として設けた。RHEEDパターンによれば、接合層をなすn形GaN層103は立方晶であり、その表面は(001)結晶面であった。GaN層103の層厚は1800nmとした。

【0047】

III族窒化物半導体層からなる接合層として設けたn形GaN層103上には、MBE成長法により、次記の(イ)〜(ニ)項に記載の立方晶のGaN系III族窒化物半導体層104〜107を成長させて、LED10用途の積層構造体100を構成した。

(イ)Siドープn形Al0.15Ga0.85N層(キャリア濃度(n)=9×1017cm-3、層厚(t)=460nm)からなる下部クラッド層104

(ロ)n形GaN(t=15nm)層を障壁層とし、n形Ga0.95In0.05N(t=2.0nm)層を井戸層とし、この障壁層と井戸層とを1周期として、その5周期からなる量子井戸構造で構成した発光層105

(ハ)マグネシウム(Mg)p形Al0.10Ga0.90N層(キャリア濃度(p)=6×1017cm-3、t=2.0nm)からなる上部クラッド層106

(ニ)Mgドープp形GaN層(p=9×1017cm-3、t=95nm)からなるコンタクト層107

【0048】

n形下部クラッド層104、発光層105、及びp形上部クラッド層106からなるpn接合型ダブルヘテロ接合構造の発光部を備えた積層構造体100にオーミック(Ohmic)電極108,109を設けてLED10を構成した。p形オーミック電極108は、積層構造体100の最表層をなすp形コンタクト層107の表面の中央に設けた。一方のn形オーミック電極109は、n形シリコン基板101の裏面の略全面に設けた。p形オーミック電極108は、金(元素記号:Au)と酸化ニッケル(NiO)との重層構造から構成した。n形オーミック電極109は、金(Au)から構成した。

【0049】

n形及びp形オーミック電極108,109間に順方向に20mAの素子駆動電流を流通させ、LED10の発光特性を調査した。主たる発光の波長は約430nmであった。順方向電流を20mAとした際の順方向電圧は約3.4Vであった。立方晶GaN結晶との格子マッチング性に優れるSi0.17Ge0.83C層を介して形成した結晶性に優れるIII族窒化物半導体層を利用してpn接合型DH構造の発光部を構成したため、局所的な耐電圧不良(local breakdown)もなかった。また、逆方向電流を10μAとした際の逆方向電圧は15Vを超える耐電圧性に優れるLEDとなった。

【0050】

(実施例2) (111)結晶面を表面とする(111)シリコン基板上に設けられたSiGeC膜を備えた積層構造体を用いて、GaN系MESFETを構成する場合を例にして、本発明を具体的に説明する。

【0051】

図3に、本実施例2に記載のGaN系MESFET20の断面構造を示す模式図を示す。

【0052】

MESFET20を作製するための積層構造体200は、表面を(111)結晶面とする高抵抗なシリコン(珪素単結晶)を基板201として形成した。基板201を、約1×10-8Paの高真空に保たれたMBE成長用チャンバー内において、800℃で5分間にわたり加熱処理を施した。これにより、シリコン基板201の表面をなす(111)結晶面に(7×7)再配列構造を形成した。この再配列構造の出現は、一般的なRHEEDパターンから確認した。

【0053】

次に、清浄化されたシリコン基板201の表面をなす(111)結晶面上には、一般的な固体ソースMBE法により、580℃で、アンドープで高抵抗なSi0.53Ge0.47CからなるSiGeC層202を本発明の云うIV族元素膜として形成した。珪素(Si)の原料には、高純度Siを用い、Geの原料には、高純度金属Geを用いた。また、炭素(C)の原料には、高純度(純度6N)のアセチレンガスを用いた。SiGeC膜202の層厚は5nmとした。RHEEDパターンによれば、SiGeC膜202は立方晶の結晶層であり、その表面は、(111)面であった。また、SiGeC膜202の抵抗率は約3×102Ω・cmと見積もられた。

【0054】

SiGeC膜202の(111)結晶面からなる表面上には、MBE法によりアンドープで高抵抗なAl0.50Ga0.50NからなるAlGaN層(キャリア濃度=3×1016cm-3)203を、本発明の云うIII族窒化物半導体層からなる接合層として設けた。AlGaN層203の層厚は450nmとした。RHEEDパターンによれば、接合層をなす高抵抗なAlGaN層203は六方晶であり、その表面は(0001)結晶面であった。また、AlGaN層203の抵抗率は約5×103Ω・cmであった。

【0055】

III族窒化物半導体層からなる接合層として設けた高抵抗なAlGaN層203上には、MBE成長法により、次記の(a)〜(c)項に記載の六方晶のGaN系III族窒化物半導体層204〜206を成長させて、MESFET20用途の積層構造体200を構成した。

(a)アンドープn形GaN層(キャリア濃度(n)=7×1017cm-3、層厚(t)=26nm)からなる電子走行層(チャネル層)204

(b)アンドープn形Al0.25Ga0.75N(n=4×1018cm-3、t=15nm)からなる電子供給層205

(c)Siドープn形GaN層(n=6×1018cm-3、t=10nm)からなるコンタクト層206

【0056】

次に、ソース電極207及びドレイン電極208の間の、ショットキー接触性のゲート電極209を形成する領域およびその近傍の領域に限り、コンタクト層206を一般的なドライエッチング手段により除去した。ゲート電極209を形成する領域に対向して残存させた、コンタクト層206をなす一方の表面には、オーミック接触性のソース電極207を形成した。また、ゲート電極209を挟んで対向する位置に在る、他方のコンタクト層206の表面上には、ドレイン電極208を設けて、GaN系MESFET20を作製した。ソース電極207及びドレイン電極208をなすオーミック電極は、一般的な真空蒸着法により形成したランタン(元素記号:La)・アルミニウム(Al)合金膜から形成した。

【0057】

コンタクト層206を除去して露出させた電子供給層205の表面には、一般的な電子ビーム蒸着手段により、チタン(Ti)からなるゲート電極209を設けた。これより、MESFET30を作製した。

【0058】

MESFET20は、SiGeC層202との格子マッチングに優れるAlGaN層203を下地層として形成したため、双晶や積層欠陥を殆ど含まないn形GaN層を電子走行層204として構成することができ、相互コンダクタンス(gm)に優れるものとなった。また、チタンからなるショトッキー接触性のゲート電極209を結晶性に優れる電子供給層205に接触させて設けたため、漏洩電流の少ない高い耐電圧性のゲート電極209を備えたGaN系MESFET20がもたらされることとなった。

【図面の簡単な説明】

【0059】

【図1】実施例1に記載のLEDの平面構造を示す模式図である。

【図2】図1に示すLEDの破線A−A’に沿った断面模式図である。

【図3】実施例2に記載のMESFETの断面構造を示す模式図である。

【符号の説明】

【0060】

10 LED

100 LED用途積層構造体

101 (001)シリコン基板

102 SiGeC膜(IV族元素膜)

103 GaN層(接合層(III族窒化物半導体層))

104 下部クラッド層

105 多重量子井戸構造発光層

106 上部クラッド層

107 コンタクト層

108 p形オーミック電極

109 n形オーミック電極

20 MESFET

200 MESFET用途積層構造体

201 (111)シリコン基板

202 SiGeC膜(IV族元素膜)

203 AlGaN層(接合層(III族窒化物半導体層))

204 電子走行層

205 電子供給層

206 コンタクト層

207 ソース電極

208 ドレイン電極

209 ゲート電極

【技術分野】

【0001】

本発明は、珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子に関する。

【背景技術】

【0002】

従来から、珪素単結晶(シリコン)を基板とし成長させたIII−V族化合物半導体層を活性層として利用して半導体素子を作製する技術が開示されている(下記の特許文献1参照)。特に、短波長の可視光を出射する発光ダイオード(英略称:LED)やレーザダイオード(英略称:LD)にあっては、シリコン基板上にIII族窒化物半導体層を活性層(発光層)として備えた積層構造体から構成されている(下記の特許文献2参照)。また、シリコン基板上に形成した窒化ガリウム(GaN)層を活性層(チャネル(channel)層)としてショットキー(Schottky)接合型電界効果トランジスタ(英略称:MESFET)を作製する技術が開示されている(下記の特許文献3参照)。

【特許文献1】米国特許 US−6,069,021号

【特許文献2】特開平7−288231号公報

【特許文献3】特開平10−287497号公報

【0003】

III族窒化物半導体層は、格子不整合を緩和するためにシリコン基板の表面上に炭化珪素(SiC)から成る緩衝膜を設けた後、形成するのが一般的である(下記の非特許文献1参照)。立方晶のSiC(所謂、3C型SiC)から成る緩衝膜を設けるために、予め、シリコン基板の表面をアセチレン(分子式:C2H2)を使用して炭化する手段が採られている(下記の非特許文献2参照)。

【非特許文献1】古川 清二郎、雨宮 好仁編著、「シリコン系ヘテロデバイス」、平成3年7月30日、丸善(株)発行、第5章、92頁。

【非特許文献2】S. Motoyama and S. Kaneda, “Low-Temperature Growth of 3C-SiC by Gas Source Molecular Beam Epitaxial Method”,アプライド フィジクス レターズ(Appl. Phys. Lett.), 第54巻、1989年(米国)、242頁。

【0004】

立方晶の3C型SiCの格子定数は、0.436ナノメーター(nm)である。これに対し、例えば、立方晶のGaNの格子定数は0.451nmある。従って、3C型SiCと立方晶のGaNとは良好な格子整合の関係にあるとは言えない。一方、六方晶のウルツ鉱(Wurtzite)型GaNのa軸は0.319nmである。従って、3C型SiCは、六方晶のGaNとも格子整合する関係にない。この格子のミスマッチ(mismatch)に起因して、従来の3C型炭化珪素層上に形成するIII族窒化物半導体層内には、ミスフィット(misfit)転位等の結晶欠陥が導入されてしまう。

【0005】

従って、転位等の結晶欠陥密度が充分に低い良質の珪素単結晶(シリコン)を基板とした場合でも、結晶欠陥が少なく、素子(デバイス)特性を充分に顕現するための良質のIII族窒化物半導体結晶層は、従来の炭化珪素層を利用する限り、充分に安定して形成できていない。このため、良好な電気伝導性、熱伝導性、及び明瞭な劈開性を呈する珪素単結晶の優位性を利用した発光素子、例えば順方向電圧(Vf)の低いLEDや劈開結晶面を共振面とするLD、また放熱性に優れるが故に低損失の電力(パワー)トランジスタを作製するのに支障を来している。

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明は、上記の従来技術の問題点を克服すべくなされたもので、珪素単結晶を基板としてIII族窒化物半導体層を設けるのに際し、そのIII族窒化物半導体層を良質な結晶層とすることができ、素子特性を優れたものとすることができる半導体素子を提供することを目的とする。

【課題を解決するための手段】

【0007】

1)上記目的を達成するために、第1の発明は、珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子において、上記基板の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜が設けられ、そのIV族元素膜に接合させて上記III族窒化物半導体からなる接合層が設けられているものである。

【0008】

2)第2の発明は、上記した1)項に記載の発明の構成において、上記基板は導電性を有し、上記IV族元素膜はその基板と同一の伝導形の導電性を有しているものである。

【0009】

3)第3の発明は、上記した2)項に記載の発明の構成において、上記接合層は、上記IV族元素膜と同一の伝導形の導電性を有しているものである。

【0010】

4)第4の発明は、上記した1)項に記載の発明の構成において、上記基板、IV族元素膜および接合層を高抵抗とするものである。

【0011】

5)第5の発明は、上記した4)項に記載の発明の構成において、上記接合層を上記基板よりさらに高抵抗とするものである。

【0012】

6)第6の発明は、上記した1)項から5)項の何れか1項に記載の発明の構成において、上記IV族元素膜は上記基板の一表面と同一の面方位を有するものである。

【0013】

第7の発明は、上記した6)項に記載の発明の構成において、上記基板の{001}表面上に上記IV族元素膜が設けられ、そのIV族元素膜の表面は{001}結晶面から構成され、上記接合層はそのIV族元素膜の{001}結晶面に形成されて立方晶の結晶層から構成されているものである。

【0014】

第8の発明は、上記した6)項に記載の発明の構成において、上記基板の{111}表面上に上記IV族元素膜が設けられ、そのIV族元素膜の表面は{111}結晶面から構成され、上記接合層はそのIV族元素膜の{111}結晶面に形成されて六方晶の結晶層から構成されているものである。

【0015】

第9の発明は、上記した1)項から8)項の何れか1項に記載の発明の構成において、上記IV族元素膜は、ゲルマニウムの組成比(=X)を0.10以上で0.85以下とする炭化珪素ゲルマニウム(組成式Si1-XGeXC:0.10≦X≦0.85)からなるものである。

【発明の効果】

【0016】

本発明によれば、珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子において、上記基板の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜を設け、そのIV族元素膜に接合させてIII族窒化物半導体からなる接合層を設ける構成としたので、Si1-XGeXCからなるIV族元素膜と、III族窒化物半導体からなる接合層との間での良好な格子マッチングにより、結晶性に優れるIII族窒化物半導体層が得られ、従って、そのIII族窒化物半導体層の良好な結晶性から素子特性に優れる半導体素子を提供できる。

【0017】

特に、本発明によれば、導電性の珪素単結晶を基板とし、炭化珪素ゲルマニウム(Si1-XGeXC)膜(IV族元素膜)を、その珪素単結晶基板と同一の伝導形の導電性の結晶層から構成することとしたので、珪素単結晶基板側から供給される素子駆動電流を、基板の表面に垂直な方向(縦方向)に流通させて動作させる半導体素子、例えば、受光素子(フォトダイオード)を好都合に構成できる。

【0018】

特に、本発明によれば、導電性珪素単結晶基板と、炭化珪素ゲルマニウム(Si1-XGeXC)膜と、その膜に接合させて設けるIII族窒化物半導体層とを、同一の伝導形としたので、珪素単結晶基板側から供給される素子を駆動させるための電流を、基板の表面に垂直な方向(縦方向)に流通させて動作させる半導体素子、例えばLEDやLDといった発光素子を好都合に構成できる。

【0019】

特に、本発明によれば、高抵抗の珪素単結晶基板上に、高抵抗の炭化珪素ゲルマニウム(Si1-XGeXC)膜を介して高抵抗のIII族窒化物半導体接合層を設ける構成としたので、例えば、高抵抗のIII族窒化物半導体層を緩衝層或いは電子走行層とする電界効果型トランジスタを好適に構成できる。

【0020】

特に、本発明によれば、III族窒化物半導体接合層を、基板を成す珪素単結晶を超える高抵抗の結晶層から構成したので、素子駆動電流のIII族窒化物半導体接合層を介しての漏洩(leak)を低減でき、従って、高周波帯域で動作する高性能の電界効果型トランジスタを構成するのに効果を上げられる。

【0021】

特に、本発明によれば、炭化珪素ゲルマニウム(Si1-XGeXC)膜を、それを設ける珪素単結晶基板と同一の表面の面方位を有する結晶層から構成したので、炭化珪素ゲルマニウム(Si1-XGeXC)膜に接合させて設けるIII族窒化物半導体接合層の結晶系を画一的に制御するのに効果を上げられる。

【0022】

特に、本発明によれば、珪素単結晶基板の{001}表面上に設けた、表面の面方位を{001}とする炭化珪素ゲルマニウム(Si1-XGeXC)膜を用いてIII族窒化物半導体接合層を設ける構成としたので、それに接合させて設けるIII族窒化物半導体接合層を立方晶の結晶層とするのに効果を上げられ、これにより、例えば、立方晶結晶の明瞭な劈開性を利用する端面共振型のIII族窒化物半導体LDを好適に構成できる。

【0023】

また、本発明によれば、珪素単結晶基板の{111}表面上に設けた、表面の面方位を{111}とする炭化珪素ゲルマニウム(組成式Si1-XGeXC)膜を用いてIII族窒化物半導体接合層を設けることとしたので、それに接合させて設けるIII族窒化物半導体接合層を六方晶の結晶層から構成するのに効果を上げられ、これにより、例えば、ピエゾ(piezo)効果の大きな六方晶のIII族窒化物半導体層を利用する2次元電子型電界効果トランジスタを好適に構成できる。

【0024】

特に、本発明によれば、ゲルマニウム(Ge)の組成比(=X)を0.10以上で0.85以下とする炭化珪素ゲルマニウム(Si1-XGeXC:0.10≦X≦0.85)膜を介してIII族窒化物半導体接合層を設ける構成としたので、III族窒化物半導体接合層を、それと格子マッチングに優れるSi1-XGeXC(0.10≦X≦0.85)層を下地層として形成でき、その結果、結晶性に優れるIII族窒化物半導体接合層を構成できるため、性能に優れるIII族窒化物半導体発光デバイスや電子デバイスを提供できる。

【発明を実施するための最良の形態】

【0025】

本発明は、珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子において、その基板の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜を設け、そのIV族元素膜に接合させてIII族窒化物半導体からなる接合層を設けるようにしている。

【0026】

本発明に係るIV族元素膜としての炭化珪素ゲルマニウム(Si1-XGeXC:0<X<1)膜は、{001}や{111}結晶面等を表面とするシリコン基板上に、常圧(略大気圧)或いは減圧化学的気相堆積(英略称:CVD)法や高真空中で成膜する分子線エピタキシャル(英略称:MBE)法等の気相エピタキシャル手段等で形成する。特に、MBE法を利用して、アセチレン(分子式C2H2)等の炭化水素ガス、珪素(元素記号:Si)、及びゲルマニウム(元素記号:Ge)を含むビーム(beam)を高真空中でシリコン基板の表面に吹き付けて、Si1-XGeXCを形成する手法が簡便であり、また、好適である。

【0027】

MBE法によりSi1-XGeXC膜を高真空中で形成するのに際し、高真空の成長環境を利用して、予め表面に珪素原子の再配列構造を出現させる様にシリコン基板を加熱処理すると、結晶欠陥が少なく結晶性に優れるSi1-XGeXC膜を得るのに好適となる。例えば、{001}結晶面を表面とする{001}−シリコン基板にあっては、高真空中で850℃〜1100℃に加熱して、その表面に(2×1)の再配列構造を出現させる処理を施しておくのが好ましい。また、{111}結晶面を表面とする{111}−シリコン基板にあっては、700℃〜900℃で真空加熱処理を施し、(7×7)の再配列構造を出現させた後、Si1-XGeXC膜を形成するのが好ましい。

【0028】

シリコン基板上に形成するSi1-XGeXC膜は、その上に、表面が平坦であり、且つ連続したIII族窒化物半導体層を帰結するのに充分な膜厚を有するのが望ましい。Si1-XGeXC膜は、また、シリコン基板の表面の全面を略一様に被覆する様に設けられているのが好ましいため、2ナノメーター(単位:nm)以上の層厚を有するのが望ましい。また、極端に厚いSi1-XGeXC膜では、表面の平坦性が損なわれてしまうため、上層として平坦性のあるIII族窒化物半導体層を充分に安定して得るに至らない。従って、Si1-XGeXC膜の層厚は、2nm以上で200nm以下とするのが好適である。

【0029】

Si1-XGeXC膜の伝導形を、基板として用いるシリコン単結晶の伝導形と合致させると、シリコン基板の表面に対し垂直方向に素子を駆動させるための電流(素子駆動電流)を流通させる半導体素子を構成する上で好適である。例えば、n形のシリコン基板上に、n形のSi1-XGeXC膜を設ける。n形のSi1-XGeXC膜を形成する際の不純物(ドーパント)としては、n形SiGe混晶層を得る場合と同様に例えば、アンチモン(元素記号:Sb)を用いることができる。p形Si1-XGeXC膜を得るには、例えば、硼素(元素記号:B)をp形のドーパントとして利用できる。

【0030】

更に、Si1-XGeXCから成るIV族元素膜に接合させて設けるIII族窒化物半導体からなる接合層を、基板およびSi1-XGeXC膜と同一の伝導形を有する導電性の結晶層から構成すると、シリコン基板の表面に対し垂直方向に素子駆動電流を流通させる半導体素子を構成する上で更に好適である。例えば、n形シリコン基板上にn形のSi1-XGeXC膜を設け、その上にn形のIII族窒化物半導体層を設ける構成とする。そのn形III族窒化物半導体層上に、例えば、III族窒化物半導体層からなるpn接合型ヘテロ(hetero)構造の発光部を設けてIII族窒化物半導体LEDを構成する。また、例えば、III族窒化物半導体LDを構成する。

【0031】

一方で、シリコン基板の表面に設けるSi1-XGeXC膜を高抵抗層とし、また、それに接合させて設けるIII族窒化物半導体から成る接合層を、高抵抗の結晶層から構成すると、例えば、MESFETを作製するのに利便となる。MESFETを作製するに際し、用いるシリコン基板は、抵抗率にして1キロオーム・センチメートル(KΩ・cm)を超える高抵抗であるのが好ましい。また、MESFETを作製する場合、シリコン基板上に設けるSi1-XGeXC膜及びIII族窒化物半導体接合層は、それを超えて大とする抵抗率を有する高抵抗層であるのが好ましい。MESFETのドレイン(drain)電流の基板への不必要な漏洩を抑止するためである。また、例えば、シリコン基板の同一の表面側上に設けた半導体層に陰極及び陽極の双方を設けてなるLEDを作製するのにも利用できる。高抵抗のSi1-XGeXC膜は不純物を故意に添加しないアンドープ(undope)で形成するのが得策である。

【0032】

接合層を形成するIII族窒化物半導体は、III族元素と、V族元素としての窒素(元素記号:N)とを必須の構成元素として含むIII−V族化合物半導体である。例えば、窒化アルミニウム・ガリウム(AlXGaYN:0≦X,Y≦1、X+Y=1)であり、窒化ガリウム・インジウム(GaXInYN:0≦X,Y≦1、X+Y=1)である。また、窒素と窒素とは別の砒素(元素記号:As)や燐(元素記号:P)等のV族元素を含む窒化燐化ガリウム(GaN1-ZPZ:0≦Z<1)、窒化燐化硼素(BN1-ZPZ:0≦Z<1)、窒化燐化アルミニウム・硼素(BXAlYGaN1-ZPZ:0≦X,Y≦1、X+Y=1、0≦Z<1)などである。特に、III族窒化物半導体素子を構成する主要な材料であるAlXGaYInZN(0≦X,Y,Z≦1、X+Y+Z=1)と格子のマッチングに優れるIII族窒化物半導体材料は優位に利用することができる。

【0033】

III族窒化物半導体層は、MBE法や有機金属化学的気相堆積(英略称:MOCVD)法などにより形成する。MOCVD法でAlXGaYN層を形成するのには、例えば、トリメチルガリウム(分子式(CH3)3Ga)やトリエチルガリウム(分子式(C2H5)3Ga)等をガリウム(Ga)源として、また、トリメチルアルミニウム(分子式(CH3)3Al)やトリイソブチルアルミニウム(分子式(i−C4H9)3Al)などの有機金属(英略称:MO)化合物をアルミニウム(Al)原料として使用する。窒素源としては、アンモニア(分子式NH3)、ヒドラジン(分子式N2H4)等を使用できる。熱分解する温度がより低い非対称型分子構造のジメチルヒドラジン(分子式(CH3)2H2N)類は、より低温でIII族窒化物半導体層を成長させるための窒素の原料として使用できる。

【0034】

また、例えば、AlXGaYInZN(0≦X,Y,Z≦1、X+Y+Z=1)と格子のマッチングに優れる、窒素と、砒素や燐等の窒素とは別のV族元素を含むIII族窒化物半導体層は、固体ソース(source)MBE法にあっては、砒素や燐の原料として例えば、固体砒素や固体燐を利用して形成できる。MOCVD法やガスソースMBE法にあっては、砒素や燐の原料としてアルシン(分子式AsH3)やホスフィン(分子式PH3)を例示できる。固体またはガスソースMBE法に拘らず、III族窒化物半導体層を構成する窒素(N)は、窒素プラズマなどから供給できる。

【0035】

特に、高抵抗なIII族窒化物半導体から成る接合層を利用して、例えば、MESFETを構成するのに際し、その接合層を、シリコン基板を超える高い抵抗を有する結晶層とすると、高性能な例えば、GaN系MESFETを構成するのに優位である。例えば、抵抗率を10KΩ・cmとするアンドープで高抵抗なシリコン基板上に、高抵抗なSi1-XGeXC膜を介して、100KΩ・cmを越す抵抗率を有する高抵抗なAlNからなるIII族窒化物半導体の接合層を設ける。禁止帯幅が広く、尚且つ、高抵抗な接合層を、例えば、チャネル(channel)層(電子走行層)の下地層として配置する構成によれば、ドレイン(drain)電流のピンチオフ(pinch−off)特性に優れる高周波GaN系FETを都合よく作製できる。

【0036】

例えば、表面を{001}結晶面とするSi1-XGeXC層は、{001}結晶面を表面とするシリコンを基板として用いることで形成できる。この{001}結晶面を表面とするSi1-XGeXC層は、その上に立方晶の閃亜鉛鉱結晶型のIII族窒化物半導体層を形成するための有効な下地層として利用できる。これにより、例えば、立方晶結晶の明瞭な劈開性を利用する端面共振型のIII族窒化物半導体LDを好適に構成できる。

【0037】

また、{111}結晶面を表面とするSi1-XGeXC層は、表面を{111}結晶面とするシリコンを基板として利用すれば形成できる。この、表面を{111}結晶面とするSi1-XGeXC層は、その上に六方晶のウルツ鉱結晶型のIII族窒化物半導体層を形成するための有効な下地層として利用できる。これにより、例えば、ピエゾ(piezo)効果の大きな六方晶のIII族窒化物半導体層を利用する2次元電子型電界効果トランジスタを好適に構成できる。

【0038】

Si1-XGeXC層上のIII族窒化物半導体層が立方晶であるか六方晶であるは、例えば、電子線回折法で取得される回折パターンから判別できる。

【0039】

本発明では特に、IV族元素膜のSi1-XGeXCのゲルマニウム(Ge)の組成比(=X)を0.10以上で0.85以下としている。それは、立方晶のGaNやAlN等のIII族窒化物半導体材料との良好なマッチングが得られるからである。Si1-XGeXCのゲルマニウム(Ge)の組成比(=X)が0.10より小では、これらのIII族窒化物半導体材料とのミスマッチング(mismatching)が大となり、良好な結晶性のIII族窒化物半導体層を得るに支障を来たすこととなる。また、Geの組成比が0.85を超えて大きくすると、同じく、Si1-XGeXC層とIII族窒化物半導体層との格子ミスマッチングが大となり不都合である。

【0040】

ゲルマニウム(Ge)の組成比(=X)を0.10以上で0.85以下とするSi1-XGeXC(0.10≦X≦0.85)層の格子定数は、0.438nmから0.451nmの範囲にある。このため、立方晶閃亜鉛鉱結晶型のGaN(格子定数=0.451nm)やAlN(格子定数=0.438nm)等との格子上のマッチングに優れる。また、Si1-XGeXC(0.10≦X≦0.85)層の(110)結晶面の間隔は、六方晶ウルツ鉱結晶型のGaN(a軸の長さ=0.319nm)やAlN(a軸の長さ=0.311nm)のa軸の長さと略一致する。従って、Si1-XGeXC(0.10≦X≦0.85)層を用いれば、格子のマッチング性により、結晶性の良好なIII族窒化物半導体層を形成できる。従って、性能に優れるIII族窒化物半導体発光デバイスや電子デバイスを提供できる。

【0041】

Si1-XGeXC(0.10≦X≦0.85)層にあって、Geの組成比(=X)を増加させるのにともない、格子定数は大きくなる。例えば、固体ソースMBE法でSi1-XGeXC層を形成するのに際し、アセチレン等の炭化水素系の供給量を一定に保ちつつ、Siに対するGeのフラックス(flux)強度の比率をより増大させれば、よりGe組成比を大とするSi1-XGeXC層を形成できる。

【実施例】

【0042】

(実施例1) (001)結晶面を表面とする(001)シリコン基板上に設けられたSiGeC膜を備えた積層構造体を用いて、半導体LEDを構成する場合を例にして、本発明を具体的に説明する。

【0043】

図1に、本実施例1に記載の窒化物半導体LED10の平面模式図を示す。また図2には、図1に示すLED10の破線A−A’に沿った断面模式図を示す。

【0044】

LED10を作製するための積層構造体100は、表面を(001)結晶面とするn形シリコン(珪素単結晶)を基板101として形成した。基板101を、約1×10-8パスカル(圧力単位:Pa)の高真空に保たれたMBE成長用チャンバー内において、1050℃で10分間にわたり加熱処理を施した。これにより、シリコン基板101の表面をなす(001)結晶面に(2×1)再配列構造を形成した。基板101の表面でのこの再配列構造の出現は、一般的な反射高速電子回折(英略称:RHEED)パターンから確認した。

【0045】

次に、清浄化されたシリコン基板101の表面をなす(001)結晶面上には、一般的な固体ソースMBE法により、540℃で、導電性のn形Si0.17Ge0.83CからなるSiGeC膜102を本発明の云うIV族元素膜として形成した。珪素の原料には、高純度珪素を用い、ゲルマニウムの原料には、高純度金属Geを用いた。また、炭素(元素記号:C)の原料には、高純度(純度6N)のアセチレンを用いた。SiGeC膜102の層厚は4nmとした。RHEEDパターンによれば、SiGeC膜102は立方晶の結晶層であり、その表面は、(001)面であった。

【0046】

n形SiGeC膜102の(001)結晶面からなる表面上には、MBE法によりSiドープn形GaN層(キャリア濃度=3×1018cm-3)103を、本発明の云うIII族窒化物半導体層からなる接合層として設けた。RHEEDパターンによれば、接合層をなすn形GaN層103は立方晶であり、その表面は(001)結晶面であった。GaN層103の層厚は1800nmとした。

【0047】

III族窒化物半導体層からなる接合層として設けたn形GaN層103上には、MBE成長法により、次記の(イ)〜(ニ)項に記載の立方晶のGaN系III族窒化物半導体層104〜107を成長させて、LED10用途の積層構造体100を構成した。

(イ)Siドープn形Al0.15Ga0.85N層(キャリア濃度(n)=9×1017cm-3、層厚(t)=460nm)からなる下部クラッド層104

(ロ)n形GaN(t=15nm)層を障壁層とし、n形Ga0.95In0.05N(t=2.0nm)層を井戸層とし、この障壁層と井戸層とを1周期として、その5周期からなる量子井戸構造で構成した発光層105

(ハ)マグネシウム(Mg)p形Al0.10Ga0.90N層(キャリア濃度(p)=6×1017cm-3、t=2.0nm)からなる上部クラッド層106

(ニ)Mgドープp形GaN層(p=9×1017cm-3、t=95nm)からなるコンタクト層107

【0048】

n形下部クラッド層104、発光層105、及びp形上部クラッド層106からなるpn接合型ダブルヘテロ接合構造の発光部を備えた積層構造体100にオーミック(Ohmic)電極108,109を設けてLED10を構成した。p形オーミック電極108は、積層構造体100の最表層をなすp形コンタクト層107の表面の中央に設けた。一方のn形オーミック電極109は、n形シリコン基板101の裏面の略全面に設けた。p形オーミック電極108は、金(元素記号:Au)と酸化ニッケル(NiO)との重層構造から構成した。n形オーミック電極109は、金(Au)から構成した。

【0049】

n形及びp形オーミック電極108,109間に順方向に20mAの素子駆動電流を流通させ、LED10の発光特性を調査した。主たる発光の波長は約430nmであった。順方向電流を20mAとした際の順方向電圧は約3.4Vであった。立方晶GaN結晶との格子マッチング性に優れるSi0.17Ge0.83C層を介して形成した結晶性に優れるIII族窒化物半導体層を利用してpn接合型DH構造の発光部を構成したため、局所的な耐電圧不良(local breakdown)もなかった。また、逆方向電流を10μAとした際の逆方向電圧は15Vを超える耐電圧性に優れるLEDとなった。

【0050】

(実施例2) (111)結晶面を表面とする(111)シリコン基板上に設けられたSiGeC膜を備えた積層構造体を用いて、GaN系MESFETを構成する場合を例にして、本発明を具体的に説明する。

【0051】

図3に、本実施例2に記載のGaN系MESFET20の断面構造を示す模式図を示す。

【0052】

MESFET20を作製するための積層構造体200は、表面を(111)結晶面とする高抵抗なシリコン(珪素単結晶)を基板201として形成した。基板201を、約1×10-8Paの高真空に保たれたMBE成長用チャンバー内において、800℃で5分間にわたり加熱処理を施した。これにより、シリコン基板201の表面をなす(111)結晶面に(7×7)再配列構造を形成した。この再配列構造の出現は、一般的なRHEEDパターンから確認した。

【0053】

次に、清浄化されたシリコン基板201の表面をなす(111)結晶面上には、一般的な固体ソースMBE法により、580℃で、アンドープで高抵抗なSi0.53Ge0.47CからなるSiGeC層202を本発明の云うIV族元素膜として形成した。珪素(Si)の原料には、高純度Siを用い、Geの原料には、高純度金属Geを用いた。また、炭素(C)の原料には、高純度(純度6N)のアセチレンガスを用いた。SiGeC膜202の層厚は5nmとした。RHEEDパターンによれば、SiGeC膜202は立方晶の結晶層であり、その表面は、(111)面であった。また、SiGeC膜202の抵抗率は約3×102Ω・cmと見積もられた。

【0054】

SiGeC膜202の(111)結晶面からなる表面上には、MBE法によりアンドープで高抵抗なAl0.50Ga0.50NからなるAlGaN層(キャリア濃度=3×1016cm-3)203を、本発明の云うIII族窒化物半導体層からなる接合層として設けた。AlGaN層203の層厚は450nmとした。RHEEDパターンによれば、接合層をなす高抵抗なAlGaN層203は六方晶であり、その表面は(0001)結晶面であった。また、AlGaN層203の抵抗率は約5×103Ω・cmであった。

【0055】

III族窒化物半導体層からなる接合層として設けた高抵抗なAlGaN層203上には、MBE成長法により、次記の(a)〜(c)項に記載の六方晶のGaN系III族窒化物半導体層204〜206を成長させて、MESFET20用途の積層構造体200を構成した。

(a)アンドープn形GaN層(キャリア濃度(n)=7×1017cm-3、層厚(t)=26nm)からなる電子走行層(チャネル層)204

(b)アンドープn形Al0.25Ga0.75N(n=4×1018cm-3、t=15nm)からなる電子供給層205

(c)Siドープn形GaN層(n=6×1018cm-3、t=10nm)からなるコンタクト層206

【0056】

次に、ソース電極207及びドレイン電極208の間の、ショットキー接触性のゲート電極209を形成する領域およびその近傍の領域に限り、コンタクト層206を一般的なドライエッチング手段により除去した。ゲート電極209を形成する領域に対向して残存させた、コンタクト層206をなす一方の表面には、オーミック接触性のソース電極207を形成した。また、ゲート電極209を挟んで対向する位置に在る、他方のコンタクト層206の表面上には、ドレイン電極208を設けて、GaN系MESFET20を作製した。ソース電極207及びドレイン電極208をなすオーミック電極は、一般的な真空蒸着法により形成したランタン(元素記号:La)・アルミニウム(Al)合金膜から形成した。

【0057】

コンタクト層206を除去して露出させた電子供給層205の表面には、一般的な電子ビーム蒸着手段により、チタン(Ti)からなるゲート電極209を設けた。これより、MESFET30を作製した。

【0058】

MESFET20は、SiGeC層202との格子マッチングに優れるAlGaN層203を下地層として形成したため、双晶や積層欠陥を殆ど含まないn形GaN層を電子走行層204として構成することができ、相互コンダクタンス(gm)に優れるものとなった。また、チタンからなるショトッキー接触性のゲート電極209を結晶性に優れる電子供給層205に接触させて設けたため、漏洩電流の少ない高い耐電圧性のゲート電極209を備えたGaN系MESFET20がもたらされることとなった。

【図面の簡単な説明】

【0059】

【図1】実施例1に記載のLEDの平面構造を示す模式図である。

【図2】図1に示すLEDの破線A−A’に沿った断面模式図である。

【図3】実施例2に記載のMESFETの断面構造を示す模式図である。

【符号の説明】

【0060】

10 LED

100 LED用途積層構造体

101 (001)シリコン基板

102 SiGeC膜(IV族元素膜)

103 GaN層(接合層(III族窒化物半導体層))

104 下部クラッド層

105 多重量子井戸構造発光層

106 上部クラッド層

107 コンタクト層

108 p形オーミック電極

109 n形オーミック電極

20 MESFET

200 MESFET用途積層構造体

201 (111)シリコン基板

202 SiGeC膜(IV族元素膜)

203 AlGaN層(接合層(III族窒化物半導体層))

204 電子走行層

205 電子供給層

206 コンタクト層

207 ソース電極

208 ドレイン電極

209 ゲート電極

【特許請求の範囲】

【請求項1】

珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子において、

上記基板の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜が設けられ、そのIV族元素膜に接合させて上記III族窒化物半導体からなる接合層が設けられている、

ことを特徴とする半導体素子。

【請求項2】

上記基板は導電性を有し、上記IV族元素膜はその基板と同一の伝導形の導電性を有している、請求項1に記載の半導体素子。

【請求項3】

上記接合層は、上記IV族元素膜と同一の伝導形の導電性を有している、請求項2に記載の半導体素子。

【請求項4】

上記基板、IV族元素膜および接合層は高抵抗である、請求項1に記載の半導体素子。

【請求項5】

上記接合層は上記基板よりさらに高抵抗である、請求項4に記載の半導体素子。

【請求項6】

上記IV族元素膜は上記基板の一表面と同一の面方位を有する、請求項1乃至5の何れか1項に記載の半導体素子。

【請求項7】

上記基板の{001}表面上に上記IV族元素膜が設けられ、そのIV族元素膜の表面は{001}結晶面から構成され、上記接合層はそのIV族元素膜の{001}結晶面に形成されて立方晶の結晶層から構成されている、請求項6に記載の半導体素子。

【請求項8】

上記基板の{111}表面上に上記IV族元素膜が設けられ、そのIV族元素膜の表面は{111}結晶面から構成され、上記接合層はそのIV族元素膜の{111}結晶面に形成されて六方晶の結晶層から構成されている、請求項6に記載の半導体素子。

【請求項9】

上記IV族元素膜は、ゲルマニウムの組成比(=X)を0.10以上で0.85以下とする炭化珪素ゲルマニウム(組成式Si1-XGeXC:0.10≦X≦0.85)からなる、請求項1乃至8の何れか1項に記載の半導体素子。

【請求項1】

珪素単結晶からなる基板上にIII族窒化物半導体からなる層を備えた半導体素子において、

上記基板の一表面に、立方晶の炭化珪素ゲルマニウム(組成式Si1-XGeXC:0<X<1)からなるIV族元素膜が設けられ、そのIV族元素膜に接合させて上記III族窒化物半導体からなる接合層が設けられている、

ことを特徴とする半導体素子。

【請求項2】

上記基板は導電性を有し、上記IV族元素膜はその基板と同一の伝導形の導電性を有している、請求項1に記載の半導体素子。

【請求項3】

上記接合層は、上記IV族元素膜と同一の伝導形の導電性を有している、請求項2に記載の半導体素子。

【請求項4】

上記基板、IV族元素膜および接合層は高抵抗である、請求項1に記載の半導体素子。

【請求項5】

上記接合層は上記基板よりさらに高抵抗である、請求項4に記載の半導体素子。

【請求項6】

上記IV族元素膜は上記基板の一表面と同一の面方位を有する、請求項1乃至5の何れか1項に記載の半導体素子。

【請求項7】

上記基板の{001}表面上に上記IV族元素膜が設けられ、そのIV族元素膜の表面は{001}結晶面から構成され、上記接合層はそのIV族元素膜の{001}結晶面に形成されて立方晶の結晶層から構成されている、請求項6に記載の半導体素子。

【請求項8】

上記基板の{111}表面上に上記IV族元素膜が設けられ、そのIV族元素膜の表面は{111}結晶面から構成され、上記接合層はそのIV族元素膜の{111}結晶面に形成されて六方晶の結晶層から構成されている、請求項6に記載の半導体素子。

【請求項9】

上記IV族元素膜は、ゲルマニウムの組成比(=X)を0.10以上で0.85以下とする炭化珪素ゲルマニウム(組成式Si1-XGeXC:0.10≦X≦0.85)からなる、請求項1乃至8の何れか1項に記載の半導体素子。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2007−73873(P2007−73873A)

【公開日】平成19年3月22日(2007.3.22)

【国際特許分類】

【出願番号】特願2005−261947(P2005−261947)

【出願日】平成17年9月9日(2005.9.9)

【出願人】(000002004)昭和電工株式会社 (3,251)

【Fターム(参考)】

【公開日】平成19年3月22日(2007.3.22)

【国際特許分類】

【出願日】平成17年9月9日(2005.9.9)

【出願人】(000002004)昭和電工株式会社 (3,251)

【Fターム(参考)】

[ Back to top ]