半導体装置、および、それを備えるICカード

【課題】 複数の回路ブロックと、これらの回路ブロック間を互いに接続する内部の信号線とを有しているにも拘わらず、上記各回路ブロック間を伝送されるデータが消費電力解析によって推定される可能性を軽減可能な半導体装置、および、ICカードを実現する。

【解決手段】 ICカード1は、複数の回路ブロック11〜14と、これらの回路ブロック間を互いに接続する内部のデータバス21とを備えている。上記回路ブロックのうち、出力側となるCPUブロック11には、伝送しようとするデータを、データの変化の量が、より一様になるように、予め定められた符号化方法で符号化して、上記データバス22の信号線21aへ出力する符号化回路41が設けられ、入力側となるコプロセッサブロック12には、上記信号線21aを介して伝送される符号化されたデータを復号する復号回路42が設けられている。

【解決手段】 ICカード1は、複数の回路ブロック11〜14と、これらの回路ブロック間を互いに接続する内部のデータバス21とを備えている。上記回路ブロックのうち、出力側となるCPUブロック11には、伝送しようとするデータを、データの変化の量が、より一様になるように、予め定められた符号化方法で符号化して、上記データバス22の信号線21aへ出力する符号化回路41が設けられ、入力側となるコプロセッサブロック12には、上記信号線21aを介して伝送される符号化されたデータを復号する復号回路42が設けられている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、内部の信号線を介して各回路ブロック間を伝送されるデータが、消費電力解析によって推定される可能性を軽減可能な半導体装置、および、それを備えるICカードに関するものである。

【背景技術】

【0002】

ICカードは、内部に半導体回路を有し、暗号処理をはじめとして、種々の演算処理を行うことができるため、磁気カードと比較して、より安全に情報を格納することができる。したがって、例えば、秘密情報を格納して個人を認証する用途など、安全であることが求められる用途での普及が見込まれている。

【0003】

一方で、ICカードの内部へアクセスすることなく、内部の情報を盗み出す攻撃手法も考案されており、これらの1つとして、内部回路の処理に応じて消費電力が変化することに着目し、内部処理と消費電力との相関を取り、消費電力を解析することによって、内部処理を推定する方法も考案されている。なお、この攻撃方法の代表的な手法としては、SPA(Simple Power Analysis:単純電力解析)や、DPA(Differential Power Analysis:電力差分解析)などが挙げられる。

【0004】

これらの攻撃方法は、ICカードの内部へ物理的にアクセスしようとする攻撃方法とは異なって、ICカードに対して、外的な操作を全く必要とせずに行われるため、ICカードが攻撃を検出して情報の漏洩を防止する処理を行うことが難しい。

【0005】

このため、例えば、後述する特許文献1では、CPUと一緒にオンチップされたコプロセッサユニットが、演算メモリの記憶領域を任意に指定可能なポインタを有する構成が記載されている。

【0006】

上記構成では、コプロセッサユニットが上記ポインタを有しているため、演算メモリの一の記憶領域から他の記憶領域へのデータ転送を、アドレスポインタの設定値変更によって実現できる。ここで、上記演算メモリの記憶容量は、剰余演算データを複数組格納可能な記憶容量に設定されているので、所定の演算データについて、コプロセッサユニット内で演算メモリから剰余演算器に転送することが可能になる。

【0007】

これにより、コプロセッサユニットが、CPU制御により、演算データを、外部のRAMから逐次受取ったり、コプロセッサユニットが、演算結果を周期的にCPU制御で外部のRAMへ転送したりする回数を抑制でき、コプロセッサユニットのデータの外部転送を少なくすることができる。この結果、データ転送時間の短縮できると共に、データ転送による電流波形の解析に基づくデータハッキングを抑制できる。

【特許文献1】特開2004−129033(公開日:2004年4月22日)

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、上記従来の構成でも、回数は抑制されているものの、上記演算メモリへ最初のデータおよび暗号鍵を書き込むとき、または、演算が完了して、演算後のデータを読み出すときには、上記CPUとコプロセッサユニットとの間で、バスを介するデータ伝送が行われる。

【0009】

したがって、これらの時点の消費電力を解析することによって、CPUとコプロセッサユニットとの間で伝送されるデータを推定することは不可能ではなく、さらなる安全性の向上が求められている。

【0010】

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、複数の回路ブロックと、これらの回路ブロック間を互いに接続する内部の信号線とを有しているにも拘わらず、上記各回路ブロック間を伝送されるデータが消費電力解析によって推定される可能性を軽減可能な半導体装置、および、それを備えるICカードを実現することにある。

【課題を解決するための手段】

【0011】

本発明に係る半導体装置は、上記課題を解決するために、複数の回路ブロックと、これらの回路ブロック間を互いに接続する内部の信号線とを有する半導体装置において、上記回路ブロックのうち、出力側となる回路ブロックには、伝送しようとするデータを、データの変化の量が、より一様になるように、予め定められた符号化方法で符号化して、上記信号線へ出力する符号化回路が設けられ、上記回路ブロックのうち、入力側となる回路ブロックには、上記信号線を介して伝送される符号化されたデータを復号する復号回路が設けられていることを特徴としている。

【0012】

上記構成では、上記信号線を介して、回路ブロック間をデータが伝送される際、当該データは、符号化回路によって符号化された後で伝送される。したがって、上記信号線上には、符号化されたデータ、すなわち、元のデータと比較して、データの変化量が、より一様になったデータが伝送される。

【0013】

ここで、信号線を介する、回路ブロック間のデータ伝送が行われる場合、回路ブロック内でデータ伝送する場合と比較して、信号線の容量が大きくなるため、より大きな駆動能力の回路で信号線を駆動する必要があり、信号線を伝送されるデータが変化する際には、大きな電力を消費してしまう。したがって、上記信号線にデータをそのまま流す構成では、半導体装置の消費電力は、データに依存して変化してしまう。この結果、上記信号線に直接アクセスできないように半導体装置を構成したとしても、半導体装置の消費電力を解析して、信号線を流れるデータを推定する攻撃が可能になってしまう。

【0014】

これに対して、上記構成では、元のデータと比較して、データの変化量が、より一様になったデータが伝送されるので、半導体装置の消費電力の、データに対する依存性は減少する。この結果、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。

【0015】

なお、上記構成では、入力側となる回路ブロックに復号回路が設けられているので、出力側となる回路ブロックが、符号化したデータを出力しても、入力側となる回路ブロックは、何ら支障なく、符号化前のデータ(元のデータ)を把握でき、何ら支障なく、上記各回路ブロック間のデータ伝送を行うことができる。

【0016】

また、上記構成に加えて、上記符号化回路は、伝送しようとするデータをマンチェスター符号化して出力してもよい。さらに、上記構成に加えて、上記符号化回路には、伝送しようとするデータとクロック信号とを、排他的論理和、または、その否定演算を行う論理回路が設けられていてもよい。また、上記構成に加えて、上記復号回路には、上記信号線からのデータ信号と、上記クロック信号と同期したクロック信号との排他的論理和、または、その否定演算を行う論理回路が設けられていてもよい。

【0017】

当該構成によれば、1ビットのデータが、マンチェスター符号化によって符号化され、”0”は、”01”に、”1”は、”10”に符号化される。これにより、各データビット中には、必ず信号変化が起こるため、消費電力の変化もより一様になる。この結果、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性をさらに軽減できる。

【0018】

さらに、マンチェスター符号化によって符号化する符号化回路は、上記の論理回路によって実現できるため、クロックサイクルを消費せず、しかも、簡単な回路構成の符号化回路を実現できる。また、その復号回路は、上記の論理回路によって実現できるため、例えば、PLL回路などによって同期を取る回路とは異なって、符号化されたデータから同期を取る必要がなく、同期検出回路を省略できる。この結果、復号回路も比較的簡単な回路構成で実現できる。

【0019】

また、上記構成に加えて、上記入力側および出力側の回路ブロックの一方は、中央演算装置ブロックであり、他方は、暗号演算処理を行うコプロセッサブロックであってもよい。

【0020】

ここで、中央演算装置ブロックと、暗号演算処理を行うコプロセッサブロックとの間は、例えば、暗号化のためのパラメータや処理対象のデータなど、重要なデータが伝送されることが多く、そのデータが第三者に推定されると、当該第三者に暗号化したデータが傍聴されたり、半導体装置と同一の処理を実施可能な半導体装置が不正に製造されて、第三者が正規のユーザに成りすましたりできるようになってしまう。

【0021】

これに対して、上記構成では、上記中央演算装置ブロックとコプロセッサブロックとの間を伝送されるデータが、上記消費電力解析によって推定される可能性が軽減されている。この結果、上記暗号化したデータが不所望に傍聴される可能性や成りすましが行われる可能性を低減できる。

【0022】

また、上記構成に加えて、上記信号線は、各回路ブロックをバス接続するバスを構成する信号線であってもよい。

【0023】

ここで、上記信号線がバス接続されている構成では、各回路ブロック間を接続するための信号線の総数を削減できる一方で、信号線の容量負荷が大きくなりがちである。したがって、上記信号線上に、そのままのデータを出力すると、当該データに依存して、より大きな消費電力の変動が発生してしまう。この結果、当該構成では、上記消費電力解析による推定が行いやすい。

【0024】

これに対して、上記構成では、信号線を流れるデータが符号化されているので、各回路ブロック間をバス接続しているにも拘わらず、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。

【0025】

さらに、上記構成に加えて、上記出力側となる回路ブロックには、相補型の回路からなり、上記信号線を駆動する駆動回路を備えていてもよい。

【0026】

ここで、相補型の回路からなる駆動回路によって、信号線を駆動している場合、比較的大きな駆動電流を比較的簡単な回路構成で得ることができる一方で、信号線を流れるデータが変化する際に、当該相補型の回路の貫通電流によって、より大きな電力が消費される。したがって、上記信号線上に、そのままのデータを出力すると、当該データに依存して、より大きな消費電力の変動が発生してしまう。この結果、当該構成では、上記消費電力解析による推定が行いやすい。

【0027】

これに対して、上記構成では、信号線を流れるデータが符号化されているので、上記出力側となる回路ブロックに相補型の回路からなる駆動回路が設けられているにも拘わらず、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。

【0028】

また、本発明に係るICカードは、上記課題を解決するために、上記いずれかの半導体装置を備えていることを特徴としている。ここで、上記構成の半導体装置は、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。したがって、より安全なICカードを実現できる。

【発明の効果】

【0029】

本発明によれば、元のデータと比較して、データの変化量が、より一様になるように符号化された後で、データが伝送されるので、半導体装置の消費電力の、データに対する依存性を減少させることができ、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。この結果、ICカードをはじめとして、種々の用途に使用される半導体装置として、広く好適に用いることができる。

【発明を実施するための最良の形態】

【0030】

本発明の一実施形態について図1ないし図7に基づいて説明すると以下の通りである。すなわち、本実施形態に係る半導体装置は、消費電力のデータ依存性を低減できるため、例えば、暗号化または暗号解読処理を行う装置として、好適に使用できる。なお、当該装置を含む装置としては、ICカードをはじめとして、種々の装置が挙げられるが、以下では、当該装置が、ICカードである場合を例にして説明する。

【0031】

すなわち、本実施形態に係るICカード1には、図2に示すように、半導体装置としてのIC(Integrated Circuit)2が設けられており、当該IC2は、複数の回路ブロック11〜14と、それらの間を接続するバスとして、データ信号を伝送するデータバス21と、アドレス信号および制御信号を伝送するアドレス&コントロールバス22とを備えている。

【0032】

図2の例では、上記各回路ブロックとして、IC2全体を制御するCPU(Central Processing Unit )ブロック11と、例えば、数値演算や暗号化または符号化処理など、予め定められた定型の処理を行うコプロセッサブロック12と、ICカード1の外部との入出力を制御するIO回路ブロック13と、上記各バス21・22を介して、これらのブロック11〜13によって読み書きされるメモリブロック14とが設けられている。また、上記CPUブロック11は、上記各バス21・22を介して、上記コプロセッサブロック12およびIO回路ブロック13を読み書きすることもでき、例えば、暗号演算などの処理の開始や、処理のためのデータ(パラメータや処理対象)をコプロセッサブロック12へ書き込んで、コプロセッサブロック12へ処理を指示したり、入出力の開始や、入出力のためのパラメータ(例えば、入出力すべきデータのアドレス範囲など)をIO回路ブロック13へ書き込んで、IO回路ブロック13へ入出力を指示したりできる。なお、上記コプロセッサブロック12の処理が暗号演算の場合、上記データとしては、鍵データや、平文などが挙げられる。また、処理後に読み出されるデータとしては、例えば、復号化された暗号文などが挙げられる。

【0033】

また、上記ICカード1は、例えば、メモリブロック14として、上記空気に触れるとデータが破壊されるメモリ回路を採用したり、例えば、プローブなど、通常とは異なる端子が接続されたことを検出して、データを破壊する回路などを設けたりして、ICカード1内部へのアクセスを防止している。

【0034】

さらに、上記コプロセッサブロック12では、演算処理のアルゴリズムが、消費電力と内部処理との相関を抑制するように設定されている。一例として、コプロセッサブロック12は、演算メモリの記憶領域を任意に指定可能なポインタを備えている(いずれも図示せず)。当該構成では、コプロセッサブロック12が上記ポインタを有しているため、演算メモリの、ある記憶領域から他の記憶領域へのデータ転送を、アドレスポインタの設定値変更によって実現できる。また、上記演算メモリの記憶容量は、剰余演算データを複数組格納可能な記憶容量に設定されている。この結果、所定の演算データについて、コプロセッサブロック12内で演算メモリから剰余演算器に転送できる。

【0035】

これにより、コプロセッサブロック12が、CPUブロック11の制御によって、演算データを、外部のメモリブロック14から逐次受取ったり、コプロセッサブロック12が、CPUブロック11の制御に従って、演算結果を周期的に外部のメモリブロック14へ転送したりする回数を抑制でき、コプロセッサブロック12のデータの外部転送を削減している。この結果、データ転送時間の短縮できると共に、データ転送による電流波形の解析に基づくデータハッキングを抑制できる。

【0036】

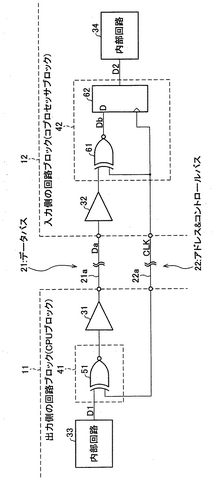

ここで、上記各回路ブロック11〜14間のデータ伝送は、各回路ブロック11〜14内のデータ伝送と比較すると、伝送距離が長くなっているため、データを伝送する信号線の負荷が大きくなっている。したがって、回路ブロック11〜14の内部回路と、信号線(上記のバス21・22など)との間には、図1に示すように、出力装置としての出力バッファ回路(駆動回路)31、あるいは、入力装置としての入力バッファ回路32が設けられている。なお、出力バッファ回路31は、各回路ブロック11〜14のうちの出力側の回路ブロック(図の例では、CPUブロック11)、より詳細には、データを出力する内部回路33と、各バス21・22を構成する信号線(例えば、21a)との間に設けられている。また、入力バッファ回路32は、入力側の回路ブロック(図の例では、コプロセッサブロック12)、より詳細には、バス21・22を構成する信号線(例えば、21a)と、内部回路34との間に設けられている。

【0037】

上記出力バッファ回路31の出力段は、例えば、CMOS構造の回路、あるいは、相補動作型のエミッタフォロワ回路など、相補型の回路によって構成されており、当該出力バッファ回路31の駆動能力は、内部回路33・34の駆動能力と比較して、上記信号線21aを介したデータ伝送に充分な程度に大きく設定されている。また、上記入力バッファ回路32の回路構成も、信号線21aを介して伝送されるため、信号の波形が鈍ったとしても、正しく、信号の値を弁別できるように、時定数等が設定されている。

【0038】

これにより、各回路ブロック11〜14同士の間の距離が、それぞれの内部回路同士より長くなっていたとしても、各回路ブロック11〜14は、何ら支障なく、データを伝送できる。

【0039】

なお、本実施形態では、各回路ブロック11〜14が互いにバス接続されており、各信号線(21aなど)に、全回路ブロック11〜14が接続されているため、信号線21aが、各回路ブロック11〜14を1対1に接続する構成と比較して、負荷が高くなっている。したがって、上記出力バッファ回路31の駆動能力も、1対1の場合よりも大きく設定されている。

【0040】

ただし、上記のように、出力バッファ回路31および入力バッファ回路32が構成されているため、各回路ブロック11〜14の内部回路同士でデータ伝送する場合と比較して、各回路ブロック11〜14間のデータ伝送する場合、より大きな消費電力が必要になる。また、後述する比較例のように、伝送すべきデータを、そのまま信号線21a上を伝送すると、消費電力が、伝送されるデータに依存して変化してしまう。

【0041】

これに対して、本実施形態に係るICカード1では、上記出力側の内部回路33からデータバス21の信号線21aまでの間(図の例では、内部回路33と出力バッファ回路31との間)に、データ変化の量(何ビットのデータが変化したか)がより均一になるような(より好ましくは、データ変化の量が均一になるような)符号化方法で符号化する符号化回路41が設けられている。また、上記信号線21aから上記入力側の内部回路34までの間(図の例では、入力バッファ回路32と内部回路34との間)に、上記符号化回路41によって符号化されたデータを復号する復号回路42が設けられている。

【0042】

本実施形態では、上記符号化方法として、例えば、クロック信号を用いたマンチェスター符号化方法が採用されており、上記符号化回路41は、内部回路33からのデータD1と、クロック信号CLKとの排他的論理和の否定を算出して、上記出力バッファ回路31へ出力するXNOR回路51により実現されている。これにより、上記データD1に代えて、符号化データDaが、データバス21の信号線21a上を伝送される。

【0043】

また、上記復号回路42は、入力バッファ回路32からのデータDaとクロック信号CLKとの排他的論理和の否定を算出して出力するXNOR回路61と、上記クロック信号CLKの示すタイミングで、XNOR回路61の出力Dbを保持するラッチ回路62とを備えている。本実施形態では、ラッチ回路62が、D−FF(フリップフロップ)によって実現されており、クロック信号CLKの立ち上がりタイミングで、上記出力Dbをラッチしている。

【0044】

上記構成では、出力側の内部回路33が図3に示すようなデータD1(例えば、1、0、1、1、1、0、0)を伝送しようとする場合、符号化回路41は、上述した回路構成によって、当該データD1をデータDaに符号化する。これにより、データバス21の信号線21a上には、符号化後のデータDaが出力される。一方、復号回路42のXNOR回路61は、図3に示すように、データDaを復号して、データDbを生成し、ラッチ回路62が、データDbを波形調整して、そのタイミングをクロック信号CLKに合わせる。これにより、復号回路42は、位相が1クロック周期分遅れている以外は、内部回路33が伝送しようとしたデータD1と同一内容のデータ信号D2(この例では、1、0、1、1、1、0、0)を出力できる。なお、図では、説明の便宜上、各回路41・42による遅延や信号線21aの伝送遅延などは省略している。

【0045】

これにより、上記信号線21aには、データD1とは異なるデータDaが伝送されているにも拘わらず、入力側の内部回路34には、上記出力側の内部回路33が伝送しようとしたデータD2(=D1)が入力される。この結果、内部回路33から内部回路34には、正しくデータD1(=D2)が伝送されている。

【0046】

ここで、比較例として、図4に示すように、上記符号化回路41および復号回路42を省略した構成では、図5に示すように、伝送しようとするデータDが、そのまま信号線21aを伝送されるため、ICカード1の消費電力は、伝送すべきデータDに応じて変化してしまう。

【0047】

より詳細には、t1〜t2の期間、および、t3〜t4の期間は、伝送すべきデータDが変化しているため、上記両バッファ回路31・32の消費電力は、比較的高いレベルに保たれ、それに伴なって、ICカード1の消費電力も、比較的高いレベルP1に保たれている。一方、t2〜t3の期間は、伝送すべきデータDが変化していないため、上記両バッファ回路31・32の消費電力は、比較的低いレベルに抑えられ、それに伴なって、ICカード1の消費電力も、比較的低いレベルP2に保たれている。

【0048】

この結果、上記データバス21がICカード1の内部に設けられ、外部からは、当該データバス21の信号に直接はアクセスできないようにICカード1が構成されているにも拘わらず、上記のように、ICカード1の消費電力がデータDに依存して変化するため、ICカード1の消費電力解析によって、データバス21を伝送されるデータDが推定される虞れがある。

【0049】

これに対して、本実施形態では、上記符号化回路41および復号回路42が設けられているため、図3に示すように、データD1の値、および、データD1が変化するか否かに拘わらず、符号化後のデータDaは、頻繁に変化し、クロック周期内で、必ず1回は、変化する。

【0050】

これにより、上記両内部回路33・34間を図5と同じデータD1(=D)が伝送されているにも拘わらず、上記両バッファ回路31・32の消費電力は、常に略一定のレベルに保たれ、それに伴なって、ICカード1の消費電力も、略一定のレベルP3に保たれている。

【0051】

例えば、図5では、t1〜t2の期間およびt3〜t4の期間の消費電力P1と、t2〜t3の期間の消費電力P2とは互いに異なっていたのに対して、本実施形態では、t2〜t3の期間中も、データDaが変化している。したがって、図6に示すように、ICカード1の消費電力は、t2〜t3の間も、比較的高いレベルに保たれ、ICカード1の消費電力は、t1〜t4の間、略一定のレベルP3に固定されている。

【0052】

この結果、図4の構成とは異なって、データ転送による消費電力のデータ依存性を低減させることができ、消費電力波形とデータとの相関を取ることを困難にできるので、ICカード1の消費電力解析による上記データD1の推定(例えば、DPAなどによる推定)を困難にできる。これにより、消費電力解析による内部動作を暴露する攻撃から、内部の情報を守ることができ、より安全なICカード1を実現できる。

【0053】

一例として、コプロセッサブロック12が暗号演算を行う場合の動作を、図7に基づいて説明すると、以下の通りである。なお、暗号演算方式としては、例えば、RSA暗号方式、DES暗号方式など、種々の方式を採用できるが、以下では、一例として、コプロセッサブロック12がRSA暗号方式の暗号演算を行う場合について説明する。

【0054】

すなわち、図7に示すステップ1(以下では、S1のように略称する)において、コプロセッサブロック12は、暗号演算の前処理として、データバス21を介して、CPUブロック11から暗号演算のためのパラメータとして、A、B、Nおよびiを受け取って、図示しないレジスタなどの記憶装置に格納する。

【0055】

次に、コプロセッサブロック12は、S2、S3およびS4において、それぞれ、A=A2 mod N、A=(A・B)mod N、i=i−1の演算を行う。さらに、コプロセッサブロック12は、S5において、iが0か否かを判定し、iが0になるまでの間(当該S5にてNOの場合)、上記S2からS5の処理を繰り返す。

【0056】

一方、iが0になると(上記S5にてYES の場合)、コプロセッサブロック12は、S6において、暗号演算の後処理として、例えば、演算結果Aを、上記データバス21を介して、CPUブロック11に伝えたり、メモリブロック14に書き込むなどの処理を行う。これにより、コプロセッサブロック12は、与えられたデータを暗号化することができる。

【0057】

ところが、この場合、上記S1において、上記データバス21上を、暗号演算のパラメータとして、A、B、Nおよびiが伝送されているため、上述した消費電力解析によって、これらのデータが推定されると、ICカード1が外部に暗号化されたデータを出力したとしても、正規の通信相手とは異なる第三者によって、元のデータ(平文)が推測される虞れがある。また、上記パラメータが判明すると、ICカード1と同一の応答を行う不正なICカードを作成できるので、第三者がICカード1の代わりに当該不正なICカードを利用して、正規のICカード1のユーザに成りすましたりすることができる。

【0058】

これに対して、本実施形態の構成では、上述したように消費電力解析による上記各パラメータの推定を防止できる。この結果、第三者による上記平文の推測(傍聴)や成りすましを防止でき、より安全なICカード1を実現できる。

【0059】

なお、上記では、符号化回路41および復号回路42が、排他的論理和の否定演算を行う論理回路として、XNOR回路51・61を備えている場合を例示したが、これらの回路51・61に代えて、各回路の出力論理を反転して、排他的論理和を出力するXNOR回路を設けても同様の効果が得られる。

【0060】

また、上記では、コプロセッサブロック12が演算メモリの記憶領域を任意に指定可能なポインタを備えている場合について説明したが、これに限るものではない。暗号演算処理を行うコプロセッサブロックであれば、上記のように符号化することによって、各回路ブロック間に伝送されるデータの変化に起因する消費電力の変化を抑制できるので、同様の効果が得られる。

【0061】

ただし、本実施形態のように、コプロセッサブロック12における演算処理のアルゴリズムが、消費電力と内部処理との相関を抑制するように設定されていれば、データの変化に起因する消費電力の変化だけではなく、内部処理の変化に起因する消費電力の変化も防止できるので、さらに安全性を向上できる。

【0062】

さらに、上記では、ICカード1内部へのアクセスを防止するための構成を備えている場合を例にして説明したが、これに限るものではない。ただし、本実施形態のように、ICカード1内部へのアクセスを防止するための構成を備え、耐タンパ性を有していれば、消費電力解析による攻撃だけではなく、ICカード1内部へアクセスすることによる攻撃にも対処できるので、さらに安全性を向上できる。

【0063】

なお、上記では、符号化回路41がマンチェスター符号化する場合を例にして説明したが、これに限るものではない。例えば、CMI符号化方法、具体的には、データが0であれば、0を1に変更し、1であれば、出力データが0または1になるように符号化する方法など、他の符号化方法を採用してもよい。伝送しようとするデータを、データの変化の量が、より一様になるように符号化する方法であれば、同様の効果が得られる。

【0064】

ただし、本実施形態のように、マンチェスター符号化する場合には、各データビット中には、必ず信号変化が起こるため、消費電力の変化もより一様になる。この結果、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性をさらに軽減できる。

【産業上の利用可能性】

【0065】

本発明によれば、元のデータと比較して、データの変化量が、より一様になるように符号化された後で、データが伝送されるので、半導体装置の消費電力の、データに対する依存性を減少させることができ、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。この結果、ICカードをはじめとして、種々の用途に使用される半導体装置として、広く好適に用いることができる。

【図面の簡単な説明】

【0066】

【図1】本発明の実施形態を示すものであり、ICカードのデータバス近傍の要部構成を示す回路図である。

【図2】上記ICカードの要部構成を示すブロック図である。

【図3】上記ICカードの各部の信号波形を示す波形図である。

【図4】比較例と示すものであり、上記ICカードから符号化回路および復号回路を削除した構成において、データバス近傍の要部構成を示す回路図である。

【図5】上記データバスを伝送される信号波形とICカードの消費電力との時間変化を示す波形図である。

【図6】上記データバスを伝送される信号波形とICカードの消費電力との時間変化を示す波形図である。

【図7】上記ICカードに設けられたコプロセッサブロックの動作を示すフローチャートである。

【符号の説明】

【0067】

1 ICカード

2 IC(半導体装置)

11 CPUブロック(回路ブロック、中央演算装置ブロック)

12 コプロセッサブロック(回路ブロック)

13 IO回路ブロック(回路ブロック)

14 メモリブロック(回路ブロック)

21 データバス(バス)

21a 信号線

31 出力バッファ回路(駆動回路)

41 符号化回路

42 復号回路

【技術分野】

【0001】

本発明は、内部の信号線を介して各回路ブロック間を伝送されるデータが、消費電力解析によって推定される可能性を軽減可能な半導体装置、および、それを備えるICカードに関するものである。

【背景技術】

【0002】

ICカードは、内部に半導体回路を有し、暗号処理をはじめとして、種々の演算処理を行うことができるため、磁気カードと比較して、より安全に情報を格納することができる。したがって、例えば、秘密情報を格納して個人を認証する用途など、安全であることが求められる用途での普及が見込まれている。

【0003】

一方で、ICカードの内部へアクセスすることなく、内部の情報を盗み出す攻撃手法も考案されており、これらの1つとして、内部回路の処理に応じて消費電力が変化することに着目し、内部処理と消費電力との相関を取り、消費電力を解析することによって、内部処理を推定する方法も考案されている。なお、この攻撃方法の代表的な手法としては、SPA(Simple Power Analysis:単純電力解析)や、DPA(Differential Power Analysis:電力差分解析)などが挙げられる。

【0004】

これらの攻撃方法は、ICカードの内部へ物理的にアクセスしようとする攻撃方法とは異なって、ICカードに対して、外的な操作を全く必要とせずに行われるため、ICカードが攻撃を検出して情報の漏洩を防止する処理を行うことが難しい。

【0005】

このため、例えば、後述する特許文献1では、CPUと一緒にオンチップされたコプロセッサユニットが、演算メモリの記憶領域を任意に指定可能なポインタを有する構成が記載されている。

【0006】

上記構成では、コプロセッサユニットが上記ポインタを有しているため、演算メモリの一の記憶領域から他の記憶領域へのデータ転送を、アドレスポインタの設定値変更によって実現できる。ここで、上記演算メモリの記憶容量は、剰余演算データを複数組格納可能な記憶容量に設定されているので、所定の演算データについて、コプロセッサユニット内で演算メモリから剰余演算器に転送することが可能になる。

【0007】

これにより、コプロセッサユニットが、CPU制御により、演算データを、外部のRAMから逐次受取ったり、コプロセッサユニットが、演算結果を周期的にCPU制御で外部のRAMへ転送したりする回数を抑制でき、コプロセッサユニットのデータの外部転送を少なくすることができる。この結果、データ転送時間の短縮できると共に、データ転送による電流波形の解析に基づくデータハッキングを抑制できる。

【特許文献1】特開2004−129033(公開日:2004年4月22日)

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、上記従来の構成でも、回数は抑制されているものの、上記演算メモリへ最初のデータおよび暗号鍵を書き込むとき、または、演算が完了して、演算後のデータを読み出すときには、上記CPUとコプロセッサユニットとの間で、バスを介するデータ伝送が行われる。

【0009】

したがって、これらの時点の消費電力を解析することによって、CPUとコプロセッサユニットとの間で伝送されるデータを推定することは不可能ではなく、さらなる安全性の向上が求められている。

【0010】

本発明は、上記の問題点に鑑みてなされたものであり、その目的は、複数の回路ブロックと、これらの回路ブロック間を互いに接続する内部の信号線とを有しているにも拘わらず、上記各回路ブロック間を伝送されるデータが消費電力解析によって推定される可能性を軽減可能な半導体装置、および、それを備えるICカードを実現することにある。

【課題を解決するための手段】

【0011】

本発明に係る半導体装置は、上記課題を解決するために、複数の回路ブロックと、これらの回路ブロック間を互いに接続する内部の信号線とを有する半導体装置において、上記回路ブロックのうち、出力側となる回路ブロックには、伝送しようとするデータを、データの変化の量が、より一様になるように、予め定められた符号化方法で符号化して、上記信号線へ出力する符号化回路が設けられ、上記回路ブロックのうち、入力側となる回路ブロックには、上記信号線を介して伝送される符号化されたデータを復号する復号回路が設けられていることを特徴としている。

【0012】

上記構成では、上記信号線を介して、回路ブロック間をデータが伝送される際、当該データは、符号化回路によって符号化された後で伝送される。したがって、上記信号線上には、符号化されたデータ、すなわち、元のデータと比較して、データの変化量が、より一様になったデータが伝送される。

【0013】

ここで、信号線を介する、回路ブロック間のデータ伝送が行われる場合、回路ブロック内でデータ伝送する場合と比較して、信号線の容量が大きくなるため、より大きな駆動能力の回路で信号線を駆動する必要があり、信号線を伝送されるデータが変化する際には、大きな電力を消費してしまう。したがって、上記信号線にデータをそのまま流す構成では、半導体装置の消費電力は、データに依存して変化してしまう。この結果、上記信号線に直接アクセスできないように半導体装置を構成したとしても、半導体装置の消費電力を解析して、信号線を流れるデータを推定する攻撃が可能になってしまう。

【0014】

これに対して、上記構成では、元のデータと比較して、データの変化量が、より一様になったデータが伝送されるので、半導体装置の消費電力の、データに対する依存性は減少する。この結果、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。

【0015】

なお、上記構成では、入力側となる回路ブロックに復号回路が設けられているので、出力側となる回路ブロックが、符号化したデータを出力しても、入力側となる回路ブロックは、何ら支障なく、符号化前のデータ(元のデータ)を把握でき、何ら支障なく、上記各回路ブロック間のデータ伝送を行うことができる。

【0016】

また、上記構成に加えて、上記符号化回路は、伝送しようとするデータをマンチェスター符号化して出力してもよい。さらに、上記構成に加えて、上記符号化回路には、伝送しようとするデータとクロック信号とを、排他的論理和、または、その否定演算を行う論理回路が設けられていてもよい。また、上記構成に加えて、上記復号回路には、上記信号線からのデータ信号と、上記クロック信号と同期したクロック信号との排他的論理和、または、その否定演算を行う論理回路が設けられていてもよい。

【0017】

当該構成によれば、1ビットのデータが、マンチェスター符号化によって符号化され、”0”は、”01”に、”1”は、”10”に符号化される。これにより、各データビット中には、必ず信号変化が起こるため、消費電力の変化もより一様になる。この結果、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性をさらに軽減できる。

【0018】

さらに、マンチェスター符号化によって符号化する符号化回路は、上記の論理回路によって実現できるため、クロックサイクルを消費せず、しかも、簡単な回路構成の符号化回路を実現できる。また、その復号回路は、上記の論理回路によって実現できるため、例えば、PLL回路などによって同期を取る回路とは異なって、符号化されたデータから同期を取る必要がなく、同期検出回路を省略できる。この結果、復号回路も比較的簡単な回路構成で実現できる。

【0019】

また、上記構成に加えて、上記入力側および出力側の回路ブロックの一方は、中央演算装置ブロックであり、他方は、暗号演算処理を行うコプロセッサブロックであってもよい。

【0020】

ここで、中央演算装置ブロックと、暗号演算処理を行うコプロセッサブロックとの間は、例えば、暗号化のためのパラメータや処理対象のデータなど、重要なデータが伝送されることが多く、そのデータが第三者に推定されると、当該第三者に暗号化したデータが傍聴されたり、半導体装置と同一の処理を実施可能な半導体装置が不正に製造されて、第三者が正規のユーザに成りすましたりできるようになってしまう。

【0021】

これに対して、上記構成では、上記中央演算装置ブロックとコプロセッサブロックとの間を伝送されるデータが、上記消費電力解析によって推定される可能性が軽減されている。この結果、上記暗号化したデータが不所望に傍聴される可能性や成りすましが行われる可能性を低減できる。

【0022】

また、上記構成に加えて、上記信号線は、各回路ブロックをバス接続するバスを構成する信号線であってもよい。

【0023】

ここで、上記信号線がバス接続されている構成では、各回路ブロック間を接続するための信号線の総数を削減できる一方で、信号線の容量負荷が大きくなりがちである。したがって、上記信号線上に、そのままのデータを出力すると、当該データに依存して、より大きな消費電力の変動が発生してしまう。この結果、当該構成では、上記消費電力解析による推定が行いやすい。

【0024】

これに対して、上記構成では、信号線を流れるデータが符号化されているので、各回路ブロック間をバス接続しているにも拘わらず、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。

【0025】

さらに、上記構成に加えて、上記出力側となる回路ブロックには、相補型の回路からなり、上記信号線を駆動する駆動回路を備えていてもよい。

【0026】

ここで、相補型の回路からなる駆動回路によって、信号線を駆動している場合、比較的大きな駆動電流を比較的簡単な回路構成で得ることができる一方で、信号線を流れるデータが変化する際に、当該相補型の回路の貫通電流によって、より大きな電力が消費される。したがって、上記信号線上に、そのままのデータを出力すると、当該データに依存して、より大きな消費電力の変動が発生してしまう。この結果、当該構成では、上記消費電力解析による推定が行いやすい。

【0027】

これに対して、上記構成では、信号線を流れるデータが符号化されているので、上記出力側となる回路ブロックに相補型の回路からなる駆動回路が設けられているにも拘わらず、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。

【0028】

また、本発明に係るICカードは、上記課題を解決するために、上記いずれかの半導体装置を備えていることを特徴としている。ここで、上記構成の半導体装置は、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。したがって、より安全なICカードを実現できる。

【発明の効果】

【0029】

本発明によれば、元のデータと比較して、データの変化量が、より一様になるように符号化された後で、データが伝送されるので、半導体装置の消費電力の、データに対する依存性を減少させることができ、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。この結果、ICカードをはじめとして、種々の用途に使用される半導体装置として、広く好適に用いることができる。

【発明を実施するための最良の形態】

【0030】

本発明の一実施形態について図1ないし図7に基づいて説明すると以下の通りである。すなわち、本実施形態に係る半導体装置は、消費電力のデータ依存性を低減できるため、例えば、暗号化または暗号解読処理を行う装置として、好適に使用できる。なお、当該装置を含む装置としては、ICカードをはじめとして、種々の装置が挙げられるが、以下では、当該装置が、ICカードである場合を例にして説明する。

【0031】

すなわち、本実施形態に係るICカード1には、図2に示すように、半導体装置としてのIC(Integrated Circuit)2が設けられており、当該IC2は、複数の回路ブロック11〜14と、それらの間を接続するバスとして、データ信号を伝送するデータバス21と、アドレス信号および制御信号を伝送するアドレス&コントロールバス22とを備えている。

【0032】

図2の例では、上記各回路ブロックとして、IC2全体を制御するCPU(Central Processing Unit )ブロック11と、例えば、数値演算や暗号化または符号化処理など、予め定められた定型の処理を行うコプロセッサブロック12と、ICカード1の外部との入出力を制御するIO回路ブロック13と、上記各バス21・22を介して、これらのブロック11〜13によって読み書きされるメモリブロック14とが設けられている。また、上記CPUブロック11は、上記各バス21・22を介して、上記コプロセッサブロック12およびIO回路ブロック13を読み書きすることもでき、例えば、暗号演算などの処理の開始や、処理のためのデータ(パラメータや処理対象)をコプロセッサブロック12へ書き込んで、コプロセッサブロック12へ処理を指示したり、入出力の開始や、入出力のためのパラメータ(例えば、入出力すべきデータのアドレス範囲など)をIO回路ブロック13へ書き込んで、IO回路ブロック13へ入出力を指示したりできる。なお、上記コプロセッサブロック12の処理が暗号演算の場合、上記データとしては、鍵データや、平文などが挙げられる。また、処理後に読み出されるデータとしては、例えば、復号化された暗号文などが挙げられる。

【0033】

また、上記ICカード1は、例えば、メモリブロック14として、上記空気に触れるとデータが破壊されるメモリ回路を採用したり、例えば、プローブなど、通常とは異なる端子が接続されたことを検出して、データを破壊する回路などを設けたりして、ICカード1内部へのアクセスを防止している。

【0034】

さらに、上記コプロセッサブロック12では、演算処理のアルゴリズムが、消費電力と内部処理との相関を抑制するように設定されている。一例として、コプロセッサブロック12は、演算メモリの記憶領域を任意に指定可能なポインタを備えている(いずれも図示せず)。当該構成では、コプロセッサブロック12が上記ポインタを有しているため、演算メモリの、ある記憶領域から他の記憶領域へのデータ転送を、アドレスポインタの設定値変更によって実現できる。また、上記演算メモリの記憶容量は、剰余演算データを複数組格納可能な記憶容量に設定されている。この結果、所定の演算データについて、コプロセッサブロック12内で演算メモリから剰余演算器に転送できる。

【0035】

これにより、コプロセッサブロック12が、CPUブロック11の制御によって、演算データを、外部のメモリブロック14から逐次受取ったり、コプロセッサブロック12が、CPUブロック11の制御に従って、演算結果を周期的に外部のメモリブロック14へ転送したりする回数を抑制でき、コプロセッサブロック12のデータの外部転送を削減している。この結果、データ転送時間の短縮できると共に、データ転送による電流波形の解析に基づくデータハッキングを抑制できる。

【0036】

ここで、上記各回路ブロック11〜14間のデータ伝送は、各回路ブロック11〜14内のデータ伝送と比較すると、伝送距離が長くなっているため、データを伝送する信号線の負荷が大きくなっている。したがって、回路ブロック11〜14の内部回路と、信号線(上記のバス21・22など)との間には、図1に示すように、出力装置としての出力バッファ回路(駆動回路)31、あるいは、入力装置としての入力バッファ回路32が設けられている。なお、出力バッファ回路31は、各回路ブロック11〜14のうちの出力側の回路ブロック(図の例では、CPUブロック11)、より詳細には、データを出力する内部回路33と、各バス21・22を構成する信号線(例えば、21a)との間に設けられている。また、入力バッファ回路32は、入力側の回路ブロック(図の例では、コプロセッサブロック12)、より詳細には、バス21・22を構成する信号線(例えば、21a)と、内部回路34との間に設けられている。

【0037】

上記出力バッファ回路31の出力段は、例えば、CMOS構造の回路、あるいは、相補動作型のエミッタフォロワ回路など、相補型の回路によって構成されており、当該出力バッファ回路31の駆動能力は、内部回路33・34の駆動能力と比較して、上記信号線21aを介したデータ伝送に充分な程度に大きく設定されている。また、上記入力バッファ回路32の回路構成も、信号線21aを介して伝送されるため、信号の波形が鈍ったとしても、正しく、信号の値を弁別できるように、時定数等が設定されている。

【0038】

これにより、各回路ブロック11〜14同士の間の距離が、それぞれの内部回路同士より長くなっていたとしても、各回路ブロック11〜14は、何ら支障なく、データを伝送できる。

【0039】

なお、本実施形態では、各回路ブロック11〜14が互いにバス接続されており、各信号線(21aなど)に、全回路ブロック11〜14が接続されているため、信号線21aが、各回路ブロック11〜14を1対1に接続する構成と比較して、負荷が高くなっている。したがって、上記出力バッファ回路31の駆動能力も、1対1の場合よりも大きく設定されている。

【0040】

ただし、上記のように、出力バッファ回路31および入力バッファ回路32が構成されているため、各回路ブロック11〜14の内部回路同士でデータ伝送する場合と比較して、各回路ブロック11〜14間のデータ伝送する場合、より大きな消費電力が必要になる。また、後述する比較例のように、伝送すべきデータを、そのまま信号線21a上を伝送すると、消費電力が、伝送されるデータに依存して変化してしまう。

【0041】

これに対して、本実施形態に係るICカード1では、上記出力側の内部回路33からデータバス21の信号線21aまでの間(図の例では、内部回路33と出力バッファ回路31との間)に、データ変化の量(何ビットのデータが変化したか)がより均一になるような(より好ましくは、データ変化の量が均一になるような)符号化方法で符号化する符号化回路41が設けられている。また、上記信号線21aから上記入力側の内部回路34までの間(図の例では、入力バッファ回路32と内部回路34との間)に、上記符号化回路41によって符号化されたデータを復号する復号回路42が設けられている。

【0042】

本実施形態では、上記符号化方法として、例えば、クロック信号を用いたマンチェスター符号化方法が採用されており、上記符号化回路41は、内部回路33からのデータD1と、クロック信号CLKとの排他的論理和の否定を算出して、上記出力バッファ回路31へ出力するXNOR回路51により実現されている。これにより、上記データD1に代えて、符号化データDaが、データバス21の信号線21a上を伝送される。

【0043】

また、上記復号回路42は、入力バッファ回路32からのデータDaとクロック信号CLKとの排他的論理和の否定を算出して出力するXNOR回路61と、上記クロック信号CLKの示すタイミングで、XNOR回路61の出力Dbを保持するラッチ回路62とを備えている。本実施形態では、ラッチ回路62が、D−FF(フリップフロップ)によって実現されており、クロック信号CLKの立ち上がりタイミングで、上記出力Dbをラッチしている。

【0044】

上記構成では、出力側の内部回路33が図3に示すようなデータD1(例えば、1、0、1、1、1、0、0)を伝送しようとする場合、符号化回路41は、上述した回路構成によって、当該データD1をデータDaに符号化する。これにより、データバス21の信号線21a上には、符号化後のデータDaが出力される。一方、復号回路42のXNOR回路61は、図3に示すように、データDaを復号して、データDbを生成し、ラッチ回路62が、データDbを波形調整して、そのタイミングをクロック信号CLKに合わせる。これにより、復号回路42は、位相が1クロック周期分遅れている以外は、内部回路33が伝送しようとしたデータD1と同一内容のデータ信号D2(この例では、1、0、1、1、1、0、0)を出力できる。なお、図では、説明の便宜上、各回路41・42による遅延や信号線21aの伝送遅延などは省略している。

【0045】

これにより、上記信号線21aには、データD1とは異なるデータDaが伝送されているにも拘わらず、入力側の内部回路34には、上記出力側の内部回路33が伝送しようとしたデータD2(=D1)が入力される。この結果、内部回路33から内部回路34には、正しくデータD1(=D2)が伝送されている。

【0046】

ここで、比較例として、図4に示すように、上記符号化回路41および復号回路42を省略した構成では、図5に示すように、伝送しようとするデータDが、そのまま信号線21aを伝送されるため、ICカード1の消費電力は、伝送すべきデータDに応じて変化してしまう。

【0047】

より詳細には、t1〜t2の期間、および、t3〜t4の期間は、伝送すべきデータDが変化しているため、上記両バッファ回路31・32の消費電力は、比較的高いレベルに保たれ、それに伴なって、ICカード1の消費電力も、比較的高いレベルP1に保たれている。一方、t2〜t3の期間は、伝送すべきデータDが変化していないため、上記両バッファ回路31・32の消費電力は、比較的低いレベルに抑えられ、それに伴なって、ICカード1の消費電力も、比較的低いレベルP2に保たれている。

【0048】

この結果、上記データバス21がICカード1の内部に設けられ、外部からは、当該データバス21の信号に直接はアクセスできないようにICカード1が構成されているにも拘わらず、上記のように、ICカード1の消費電力がデータDに依存して変化するため、ICカード1の消費電力解析によって、データバス21を伝送されるデータDが推定される虞れがある。

【0049】

これに対して、本実施形態では、上記符号化回路41および復号回路42が設けられているため、図3に示すように、データD1の値、および、データD1が変化するか否かに拘わらず、符号化後のデータDaは、頻繁に変化し、クロック周期内で、必ず1回は、変化する。

【0050】

これにより、上記両内部回路33・34間を図5と同じデータD1(=D)が伝送されているにも拘わらず、上記両バッファ回路31・32の消費電力は、常に略一定のレベルに保たれ、それに伴なって、ICカード1の消費電力も、略一定のレベルP3に保たれている。

【0051】

例えば、図5では、t1〜t2の期間およびt3〜t4の期間の消費電力P1と、t2〜t3の期間の消費電力P2とは互いに異なっていたのに対して、本実施形態では、t2〜t3の期間中も、データDaが変化している。したがって、図6に示すように、ICカード1の消費電力は、t2〜t3の間も、比較的高いレベルに保たれ、ICカード1の消費電力は、t1〜t4の間、略一定のレベルP3に固定されている。

【0052】

この結果、図4の構成とは異なって、データ転送による消費電力のデータ依存性を低減させることができ、消費電力波形とデータとの相関を取ることを困難にできるので、ICカード1の消費電力解析による上記データD1の推定(例えば、DPAなどによる推定)を困難にできる。これにより、消費電力解析による内部動作を暴露する攻撃から、内部の情報を守ることができ、より安全なICカード1を実現できる。

【0053】

一例として、コプロセッサブロック12が暗号演算を行う場合の動作を、図7に基づいて説明すると、以下の通りである。なお、暗号演算方式としては、例えば、RSA暗号方式、DES暗号方式など、種々の方式を採用できるが、以下では、一例として、コプロセッサブロック12がRSA暗号方式の暗号演算を行う場合について説明する。

【0054】

すなわち、図7に示すステップ1(以下では、S1のように略称する)において、コプロセッサブロック12は、暗号演算の前処理として、データバス21を介して、CPUブロック11から暗号演算のためのパラメータとして、A、B、Nおよびiを受け取って、図示しないレジスタなどの記憶装置に格納する。

【0055】

次に、コプロセッサブロック12は、S2、S3およびS4において、それぞれ、A=A2 mod N、A=(A・B)mod N、i=i−1の演算を行う。さらに、コプロセッサブロック12は、S5において、iが0か否かを判定し、iが0になるまでの間(当該S5にてNOの場合)、上記S2からS5の処理を繰り返す。

【0056】

一方、iが0になると(上記S5にてYES の場合)、コプロセッサブロック12は、S6において、暗号演算の後処理として、例えば、演算結果Aを、上記データバス21を介して、CPUブロック11に伝えたり、メモリブロック14に書き込むなどの処理を行う。これにより、コプロセッサブロック12は、与えられたデータを暗号化することができる。

【0057】

ところが、この場合、上記S1において、上記データバス21上を、暗号演算のパラメータとして、A、B、Nおよびiが伝送されているため、上述した消費電力解析によって、これらのデータが推定されると、ICカード1が外部に暗号化されたデータを出力したとしても、正規の通信相手とは異なる第三者によって、元のデータ(平文)が推測される虞れがある。また、上記パラメータが判明すると、ICカード1と同一の応答を行う不正なICカードを作成できるので、第三者がICカード1の代わりに当該不正なICカードを利用して、正規のICカード1のユーザに成りすましたりすることができる。

【0058】

これに対して、本実施形態の構成では、上述したように消費電力解析による上記各パラメータの推定を防止できる。この結果、第三者による上記平文の推測(傍聴)や成りすましを防止でき、より安全なICカード1を実現できる。

【0059】

なお、上記では、符号化回路41および復号回路42が、排他的論理和の否定演算を行う論理回路として、XNOR回路51・61を備えている場合を例示したが、これらの回路51・61に代えて、各回路の出力論理を反転して、排他的論理和を出力するXNOR回路を設けても同様の効果が得られる。

【0060】

また、上記では、コプロセッサブロック12が演算メモリの記憶領域を任意に指定可能なポインタを備えている場合について説明したが、これに限るものではない。暗号演算処理を行うコプロセッサブロックであれば、上記のように符号化することによって、各回路ブロック間に伝送されるデータの変化に起因する消費電力の変化を抑制できるので、同様の効果が得られる。

【0061】

ただし、本実施形態のように、コプロセッサブロック12における演算処理のアルゴリズムが、消費電力と内部処理との相関を抑制するように設定されていれば、データの変化に起因する消費電力の変化だけではなく、内部処理の変化に起因する消費電力の変化も防止できるので、さらに安全性を向上できる。

【0062】

さらに、上記では、ICカード1内部へのアクセスを防止するための構成を備えている場合を例にして説明したが、これに限るものではない。ただし、本実施形態のように、ICカード1内部へのアクセスを防止するための構成を備え、耐タンパ性を有していれば、消費電力解析による攻撃だけではなく、ICカード1内部へアクセスすることによる攻撃にも対処できるので、さらに安全性を向上できる。

【0063】

なお、上記では、符号化回路41がマンチェスター符号化する場合を例にして説明したが、これに限るものではない。例えば、CMI符号化方法、具体的には、データが0であれば、0を1に変更し、1であれば、出力データが0または1になるように符号化する方法など、他の符号化方法を採用してもよい。伝送しようとするデータを、データの変化の量が、より一様になるように符号化する方法であれば、同様の効果が得られる。

【0064】

ただし、本実施形態のように、マンチェスター符号化する場合には、各データビット中には、必ず信号変化が起こるため、消費電力の変化もより一様になる。この結果、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性をさらに軽減できる。

【産業上の利用可能性】

【0065】

本発明によれば、元のデータと比較して、データの変化量が、より一様になるように符号化された後で、データが伝送されるので、半導体装置の消費電力の、データに対する依存性を減少させることができ、上記各回路ブロック間を伝送されるデータが、上記消費電力解析によって推定される可能性を軽減できる。この結果、ICカードをはじめとして、種々の用途に使用される半導体装置として、広く好適に用いることができる。

【図面の簡単な説明】

【0066】

【図1】本発明の実施形態を示すものであり、ICカードのデータバス近傍の要部構成を示す回路図である。

【図2】上記ICカードの要部構成を示すブロック図である。

【図3】上記ICカードの各部の信号波形を示す波形図である。

【図4】比較例と示すものであり、上記ICカードから符号化回路および復号回路を削除した構成において、データバス近傍の要部構成を示す回路図である。

【図5】上記データバスを伝送される信号波形とICカードの消費電力との時間変化を示す波形図である。

【図6】上記データバスを伝送される信号波形とICカードの消費電力との時間変化を示す波形図である。

【図7】上記ICカードに設けられたコプロセッサブロックの動作を示すフローチャートである。

【符号の説明】

【0067】

1 ICカード

2 IC(半導体装置)

11 CPUブロック(回路ブロック、中央演算装置ブロック)

12 コプロセッサブロック(回路ブロック)

13 IO回路ブロック(回路ブロック)

14 メモリブロック(回路ブロック)

21 データバス(バス)

21a 信号線

31 出力バッファ回路(駆動回路)

41 符号化回路

42 復号回路

【特許請求の範囲】

【請求項1】

複数の回路ブロックと、これらの回路ブロック間を互いに接続する内部の信号線とを有する半導体装置において、

上記回路ブロックのうち、出力側となる回路ブロックには、伝送しようとするデータを、データの変化の量が、より一様になるように、予め定められた符号化方法で符号化して、上記信号線へ出力する符号化回路が設けられ、

上記回路ブロックのうち、入力側となる回路ブロックには、上記信号線を介して伝送される符号化されたデータを復号する復号回路が設けられていることを特徴とする半導体装置。

【請求項2】

上記符号化回路は、伝送しようとするデータをマンチェスター符号化して出力することを特徴とする請求項1記載の半導体装置。

【請求項3】

上記符号化回路には、伝送しようとするデータとクロック信号とを、排他的論理和、または、その否定演算を行う論理回路が設けられていることを特徴とする請求項2記載の半導体装置。

【請求項4】

上記復号回路には、上記信号線からのデータ信号と、上記クロック信号と同期したクロック信号との排他的論理和、または、その否定演算を行う論理回路が設けられていることを特徴とする請求項3記載の半導体装置。

【請求項5】

上記入力側および出力側の回路ブロックの一方は、中央演算装置ブロックであり、他方は、暗号演算処理を行うコプロセッサブロックであることを特徴とする請求項1記載の半導体装置。

【請求項6】

上記信号線は、各回路ブロックをバス接続するバスを構成する信号線であることを特徴とする請求項1記載の半導体装置。

【請求項7】

上記出力側となる回路ブロックには、相補型の回路からなり、上記信号線を駆動する駆動回路を備えていることを特徴とする請求項1記載の半導体装置。

【請求項8】

請求項1〜7のいずれか1項に記載の半導体装置を備えるICカード。

【請求項1】

複数の回路ブロックと、これらの回路ブロック間を互いに接続する内部の信号線とを有する半導体装置において、

上記回路ブロックのうち、出力側となる回路ブロックには、伝送しようとするデータを、データの変化の量が、より一様になるように、予め定められた符号化方法で符号化して、上記信号線へ出力する符号化回路が設けられ、

上記回路ブロックのうち、入力側となる回路ブロックには、上記信号線を介して伝送される符号化されたデータを復号する復号回路が設けられていることを特徴とする半導体装置。

【請求項2】

上記符号化回路は、伝送しようとするデータをマンチェスター符号化して出力することを特徴とする請求項1記載の半導体装置。

【請求項3】

上記符号化回路には、伝送しようとするデータとクロック信号とを、排他的論理和、または、その否定演算を行う論理回路が設けられていることを特徴とする請求項2記載の半導体装置。

【請求項4】

上記復号回路には、上記信号線からのデータ信号と、上記クロック信号と同期したクロック信号との排他的論理和、または、その否定演算を行う論理回路が設けられていることを特徴とする請求項3記載の半導体装置。

【請求項5】

上記入力側および出力側の回路ブロックの一方は、中央演算装置ブロックであり、他方は、暗号演算処理を行うコプロセッサブロックであることを特徴とする請求項1記載の半導体装置。

【請求項6】

上記信号線は、各回路ブロックをバス接続するバスを構成する信号線であることを特徴とする請求項1記載の半導体装置。

【請求項7】

上記出力側となる回路ブロックには、相補型の回路からなり、上記信号線を駆動する駆動回路を備えていることを特徴とする請求項1記載の半導体装置。

【請求項8】

請求項1〜7のいずれか1項に記載の半導体装置を備えるICカード。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2006−279868(P2006−279868A)

【公開日】平成18年10月12日(2006.10.12)

【国際特許分類】

【出願番号】特願2005−99781(P2005−99781)

【出願日】平成17年3月30日(2005.3.30)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成18年10月12日(2006.10.12)

【国際特許分類】

【出願日】平成17年3月30日(2005.3.30)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]