半導体装置、および半導体装置の作製方法

【課題】水分による電気特性劣化が抑制された半導体装置および半導体装置の作製方法を提供する。

【解決手段】トランジスタを覆う層間絶縁層に接して金属酸化物層が位置する構造とし、金属酸化物層を、アモルファス構造を有する第1の金属酸化物層と、多結晶構造を有する第2の金属酸化物層を含む積層構造とする。アモルファス構造を有する第1の金属酸化物層は結晶粒界が存在せず、また、結晶状態の金属酸化物層と比較して格子間隔が広いため格子間に水分をトラップしやすい。多結晶構造を有する第2の金属酸化物層は、結晶粒界部分を除く結晶部分については緻密な構造を有しており、水分の透過性が非常に低い。このため、第1の金属酸化物層および第2の金属酸化物層を含む金属酸化物層が層間絶縁層に接する構造とすることにより、トランジスタ中への水分の侵入を効果的に防止できる。

【解決手段】トランジスタを覆う層間絶縁層に接して金属酸化物層が位置する構造とし、金属酸化物層を、アモルファス構造を有する第1の金属酸化物層と、多結晶構造を有する第2の金属酸化物層を含む積層構造とする。アモルファス構造を有する第1の金属酸化物層は結晶粒界が存在せず、また、結晶状態の金属酸化物層と比較して格子間隔が広いため格子間に水分をトラップしやすい。多結晶構造を有する第2の金属酸化物層は、結晶粒界部分を除く結晶部分については緻密な構造を有しており、水分の透過性が非常に低い。このため、第1の金属酸化物層および第2の金属酸化物層を含む金属酸化物層が層間絶縁層に接する構造とすることにより、トランジスタ中への水分の侵入を効果的に防止できる。

【発明の詳細な説明】

【技術分野】

【0001】

半導体装置、および半導体装置の作製方法に関する。

【0002】

なお、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

半導体装置に用いられる薄膜トランジスタ(以下、単に「トランジスタ」と記載することもある。)は、外部からの水分侵入により生じる配線部分の腐食や薄膜トランジスタの電気特性変動を防止するため、薄膜トランジスタ上には酸化珪素膜や窒化珪素膜などの絶縁層が設けられている(例えば、特許文献1参照。)。

【0004】

なお、本明細書中の「水分」とは、水、水蒸気、水分子、水素分子および水素原子を含む総称として用いる。なお、例えば「水分の透過性が低い」という表現が用いられている場合、これは「水、水蒸気、水分子、水素分子および水素原子のうちの1つ以上について透過性が低い」と解釈する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−59939号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

薄膜トランジスタへの水分侵入の防止効果を更に高める方法の1つとして、水分の透過性が低い、結晶性を有する金属酸化物層を、絶縁層に接して位置する構造とする方法がある。

【0007】

しかし、結晶性を有する金属酸化物層は、各結晶粒の界面(グレインバウンダリーとも言われる。)では、結晶格子における原子配列がずれている、若しくは連続性が損なわれているため、結晶粒部分に比べて比較的広い格子間隔となっている。このため、結晶粒部分については水分の透過性が非常に低いものの、結晶粒界部分は結晶粒部分と比較して水分が比較的透過しやすい状態にある。

【0008】

このような問題に鑑み、本明細書の一形態では、水分による電気特性劣化が抑制された半導体装置を提供することを目的の1つとする。また、当該半導体装置の作製方法を提供することを目的の1つとする。

【課題を解決するための手段】

【0009】

薄膜トランジスタを覆う絶縁層に接して金属酸化物層が位置する構造とし、当該金属酸化物層を、アモルファス構造(非晶質構造とも言う。)を有する第1の金属酸化物層および多結晶(ポリクリスタルとも言う。)構造を有する第2の金属酸化物層を含む構造とする。

【0010】

アモルファス構造を有する第1の金属酸化物層は、結晶状態の金属酸化物層と比較して水分が通りやすいものの、結晶粒界が存在しないため結晶粒界部分からの水分の侵入が無く、また、格子間に水分をトラップしやすいという特性を有している。

【0011】

また、多結晶構造を有する第2の金属酸化物層は、結晶粒界部分については結晶部分と比較して幾分水分が侵入しやすいものの、結晶部分については緻密な構造を有しており、水分の透過性が非常に低いという特性を有している。

【0012】

このため、金属酸化物層を、アモルファス構造を有する第1の金属酸化物層および多結晶構造を有する第2の金属酸化物層を含む構造とすることにより、第2の金属酸化物層で水分の侵入を防止し、また、第2の金属酸化物層の結晶粒界部分を通して侵入した水分についても、第1の金属酸化物層により侵入を防止する(または膜中に水分を取り込む)ことができる。そして、当該金属酸化物層を絶縁層に接して形成することで、更に水分の侵入を防止できる。したがって、薄膜トランジスタへの水分の侵入を効果的に防止することができる。

【0013】

すなわち、本発明の一態様は、半導体層、ゲート絶縁層、ゲート電極および、ソース電極及びドレイン電極として機能する一対の電極を有するトランジスタと、トランジスタ上の絶縁層と、絶縁層と接する金属酸化物層を有する構造であり、金属酸化物層は、アモルファス構造を有する第1の金属酸化物層と多結晶構造を有する第2の金属酸化物層を少なくとも含む構造であることを特徴とする半導体装置である。

【0014】

本発明の一態様に記載の構造とすることで、絶縁層と、第1の金属酸化物層および第2の金属酸化物層を含む金属酸化物層により、薄膜トランジスタへの水分の侵入を効果的に防止することができる。

【0015】

なお、トランジスタ上の絶縁層、第1の金属酸化物層および第2の金属酸化物層の構成については、以下に示す2通りの構造とすることが好ましい。

【0016】

1つめは、トランジスタ上に絶縁層が位置し、絶縁層上に第1の金属酸化物層が位置し、第1の金属酸化物層上に第2の金属酸化物層が位置する構造である。当該構造では、外部から侵入する水分は、まず第2の金属酸化物層によりブロックされる。次に、第2の金属酸化物層の結晶粒界部分などの比較的水分が透過しやすい部分を通して侵入する水分は、第1の金属酸化物層によりブロックされる、または第1の金属酸化物層中にトラップされる。そして、第1の金属酸化物層を透過して侵入する極微量の水分についても、絶縁層によりブロックされる。したがって、第2の金属酸化物層の外部に存在する水分がトランジスタに到達することを効果的に防止できる。

【0017】

2つめは、トランジスタ上に第1の金属酸化物層が位置し、第1の金属酸化物層上に第2の金属酸化物層が位置し、第2の金属酸化物層上に絶縁層が位置する構造である。当該構造では、外部から侵入する水分に加え、仮に絶縁層を成膜する際に絶縁層中に水分が取り込まれる、或いは第2の金属酸化物層と絶縁層の界面に水分が吸着された場合においても、トランジスタと絶縁層の間には第1の金属酸化物層および第2の金属酸化物層が位置する構造であるため、絶縁層中に取り込まれた水分や第2の金属酸化物層と絶縁層の界面に吸着された水分がトランジスタに到達することを効果的に防止できる。

【0018】

また、半導体層を、酸化物半導体材料を含んでなる膜とすることにより、高い移動度を有するトランジスタとすることができる。

【0019】

また、本発明の一態様は、半導体層、ゲート絶縁層、ゲート電極およびソース電極及びドレイン電極として機能する一対の電極を有するトランジスタを形成し、トランジスタ上に絶縁層を形成し、絶縁層上にアモルファス構造を有する第1の金属酸化物層を形成し、第1の金属酸化物層上に多結晶構造を有する第2の金属酸化物層を形成する工程を有することを特徴とする半導体装置の作製方法である。

【0020】

本発明の一態様に記載の作製方法を用いることで、トランジスタへの水分の侵入防止効果の高い半導体装置を作製することができる。

【0021】

また、本発明の一態様は、半導体層、ゲート絶縁層、ゲート電極およびソース電極及びドレイン電極として機能する一対の電極を有するトランジスタを形成し、トランジスタ上にアモルファス構造を有する第1の金属酸化物層を形成し、第1の金属酸化物層上に多結晶構造を有する第2の金属酸化物層を形成し、第2の金属酸化物層上に絶縁層を形成する工程を有することを特徴とする半導体装置の作製方法である。

【0022】

本発明の一態様に記載の作製方法を用いることで、外部から侵入する水分に加え、絶縁層中に取り込まれた水分、および、第2の金属酸化物層と絶縁層の界面に吸着した(或いは取り込まれた)水分の侵入防止効果の高い半導体装置を作製することができる。

【0023】

なお、第1の金属酸化物層と前記第2の金属酸化物層を、同一装置内にて連続して成膜することにより、第1の金属酸化物層および第2の金属酸化物層の層中への水分混入および第1の金属酸化物層と第2の金属酸化物層の界面への水分の付着を抑制することができるため、好ましいと言える。

【0024】

また、第1の金属酸化物層と前記第2の金属酸化物層を同一のターゲットを用いて成膜することにより、基板を異なる成膜室に移動させることによる製造タクトの増加を抑制できる。また、金属酸化物層を成膜するのに必要なターゲットが1種類のみとなるため、製造コストの増加を抑制できる。

【0025】

また、半導体層として、酸化物半導体材料を含んでなる膜を形成することにより、高い移動度を有するトランジスタを作製することができる。

【発明の効果】

【0026】

金属酸化物層を、アモルファス構造を有する第1の金属酸化物層および多結晶構造を有する第2の金属酸化物層を含む構造とすることにより、第2の金属酸化物層で水分の侵入を防止し、また、第2の金属酸化物層の結晶粒界部分を通して侵入した水分についても、第1の金属酸化物層により侵入を防止する(または膜中に水分を取り込む)ことができる。そして、当該金属酸化物層を絶縁層に接して形成することで、更に水分の侵入を防止できる。したがって、水分による電気特性劣化が抑制された半導体装置を提供できる。また、当該半導体装置の作製方法を提供できる。

【図面の簡単な説明】

【0027】

【図1】本発明の一態様に係る半導体装置の構成を説明する図。

【図2】本発明の一態様に係る半導体装置の作製方法を説明する図。

【図3】本発明の一態様に係る半導体装置の作製方法を説明する図。

【図4】本発明の一態様に係る半導体装置の作製方法を説明する図。

【図5】本発明の一態様に係る半導体装置の構成を説明する図。

【図6】本発明の一態様に係る半導体装置の構成を説明する図。

【図7】本発明の一態様に係る半導体装置を用いた電子機器の一例を説明する図。

【図8】本発明の一態様に係る半導体装置の断面状態を説明する図。

【発明を実施するための形態】

【0028】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0029】

以下に説明する実施の形態において、同じものを指す符号は異なる図面間で共通して用いる場合がある。なお、図面において示す構成要素、すなわち層や領域等の厚さ幅、相対的な位置関係等は、実施の形態において説明する上で明確性のために誇張して示される場合がある。

【0030】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0031】

また、本明細書等において「電極」や「配線」という用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」という用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

【0032】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。

【0033】

また、本明細書等において、平均面粗さ(Ra)とは、JIS B 0601:2001(ISO4287:1997)で定義されている算術平均粗さ(Ra)を、曲面に対して適用できるよう三次元に拡張したものであり、基準面から指定面までの偏差の絶対値を平均した値で表現でき、以下の数式(1)にて定義される。

【0034】

【数1】

【0035】

ここで、指定面とは、粗さ計測の対象となる面であり、座標(x1,y1,f(x1,y1)),(x1,y2,f(x1,y2)),(x2,y1,f(x2,y1)),(x2,y2,f(x2,y2))の4点で表される四角形の領域とし、指定面をxy平面に投影した長方形の面積をS0、基準面の高さ(指定面の平均の高さ)をZ0とする。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて測定可能である。

【0036】

(実施の形態1)

本実施の形態は、本発明の一態様であるトランジスタを有する半導体装置およびその作製方法について、図1乃至図5を用いて説明する。

【0037】

<本実施の形態における半導体装置の構成>

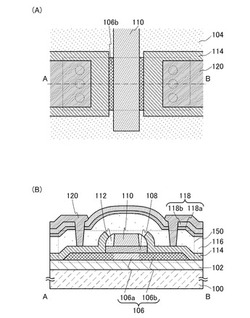

図1は、コプラナー型であるトップゲート・トップコンタクト構造のトランジスタを有する半導体装置の上面図および断面図である。図1(A)はトランジスタの上面図であり、図1(B)は図1(A)の一点鎖線A−B部分に対応する断面である。なお、図1(A)はトランジスタの構造を分かり易くするため、一部の構成要素を省略している。

【0038】

図1(B)に示すように、トランジスタ150は、基板100と、基板100上に設けられた下地絶縁層102と、下地絶縁層102上に設けられた高抵抗領域106aおよび低抵抗領域106bを有する半導体層106と、半導体層106上に設けられたゲート絶縁層108と、ゲート絶縁層108を介して半導体層106と重畳して設けられたゲート電極110と、ゲート電極110の側面と接して設けられた側壁絶縁層112と、半導体層106と接して設けられた一対の電極114と、を有している。また、トランジスタ150上に、ゲート電極110、側壁絶縁層112および一対の電極114を覆って設けられた絶縁層116と、絶縁層116上に設けられた、第1の金属酸化物層118aおよび第2の金属酸化物層118bを有する金属酸化物層118と、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに設けられた開口部を介して一対の電極114と電気的に接続された配線120と、を有している。

【0039】

本実施の形態の構造は、トランジスタ150のチャネル領域が形成される半導体層106上に、絶縁層116および金属酸化物層118が位置し、金属酸化物層118が第1の金属酸化物層118aおよび第2の金属酸化物層118bの積層構造であることが、構造的な特徴である。

【0040】

絶縁層116は、絶縁層116より上に形成された導電層(本実施の形態における配線120。)と絶縁層116より下に形成された導電層(本実施の形態におけるゲート電極110および一対の電極114。)の間で寄生容量が極力生じないように、比誘電率の低い絶縁材料で構成される。なお、当該絶縁層を無機材料で形成することにより、外部から半導体層106に侵入する水分に対して高いバリア性を具備できる。

【0041】

第1の金属酸化物層118aは、アモルファス構造を有する金属酸化物層を用いる。アモルファス構造を有する金属酸化物層は結晶粒界が存在せず、また、結晶状態の金属酸化物層と比較して格子間隔が広いため、格子間に水分をトラップしやすいという特性を有している。

【0042】

第2の金属酸化物層118bは、多結晶構造を有する金属酸化物層を用いる。多結晶構造を有する金属酸化物層は、結晶粒界部分を除く結晶部分については緻密な構造を有しており、水分の透過性が非常に低い、という特性を有している。

【0043】

したがって、半導体装置を上述の構造とすることにより、外部からトランジスタ150への水分の侵入を効果的に防止することができるため、本実施の形態の構造を有する半導体装置は、外部からの水分の侵入に起因した電気的特性の変動を抑制することができる。

【0044】

なお、図1に示すトランジスタは、ゲート電極110をマスクとして用い、自己整合的に半導体層106の低抵抗領域106b(半導体層106のうち、ソース電極やドレイン電極として機能する一対の電極114と接続される領域。ソース領域やドレイン領域とも表現できる。)および高抵抗領域106a(半導体層106のうち、チャネル部が形成される領域を一部に含む領域。チャネル形成領域などとも表現できる。)を形成することができる。そのため、微細なトランジスタを得ることができる。加えて、フォトリソグラフィ工程などによって高抵抗領域106aおよび低抵抗領域106bを形成する場合と比較して、コストの削減や歩留まりの向上が可能となる。また、低抵抗領域106bとゲート電極110の重畳部分がほとんど無いため、重畳部分での寄生容量がほとんど(或いは全く)生じず、トランジスタの高速動作が可能となる。

【0045】

また、図1に示すトランジスタは、トランジスタがオン状態のときには、低抵抗領域106bを介して、一対の電極114の一方から高抵抗領域106aに電流が流れることになる。低抵抗領域106bを介することで、チャネル長の小さい微細なトランジスタにおいてもホットキャリア劣化などの劣化を抑制でき、信頼性を高めることができる。

【0046】

なお、図1に示すトランジスタでは、半導体層106における側壁絶縁層112と重畳する領域を低抵抗領域106bに含めているが、これに限定されない。例えば、半導体層106における側壁絶縁層112と重畳する領域を高抵抗領域106aに含めても構わない。このような構造とすることで、前述のホットキャリア劣化などの劣化をさらに低減することができる。このような構造とする場合、ゲート電極110および側壁絶縁層112をマスクとして用い、自己整合的に半導体層106に低抵抗領域106bおよび高抵抗領域106aを形成すればよい。

【0047】

<本実施の形態における半導体装置の作製方法>

図1に記載されたトランジスタの作製方法を、図2乃至図4を用いて説明する。

【0048】

まず、基板100上に下地絶縁層102を形成する(図2(A)参照。)。

【0049】

基板100としては、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料を用いる。量産する上では、基板100は、第8世代(2160mm×2460mm)、第9世代(2400mm×2800mm、または2450mm×3050mm)、第10世代(2950mm×3400mm)等のマザーガラスを用いることが好ましい。マザーガラスは、処理温度が高く、処理時間が長いと大幅に収縮するため、マザーガラスを使用して量産を行う場合、作製工程の加熱処理は、700℃以下、好ましくは450℃以下、さらに好ましくは350℃以下とすることが望ましい。

【0050】

下地絶縁層102は、PECVD法またはスパッタリング法を用いて50nm以上600nm以下の膜厚で、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜から選ばれた一層またはこれらの積層膜を用いる。下地絶縁層102を形成することにより、後の工程にて形成する半導体層106に、基板100側から不純物が侵入することを抑制できる。なお、下地絶縁層102は必ずしも必要なものではなく、例えば、基板100中の含有不純物量が十分に少ない場合には、下地絶縁層102を設けない構成としてもよい。

【0051】

なお、本明細書中において、酸化窒化シリコンなどの「酸化窒化物」とは、その組成として、窒素よりも酸素の含有量が多いものを示す。また、窒化酸化シリコンなどの「窒化酸化物」とは、その組成として、酸素よりも窒素の含有量が多いものを示す。

【0052】

なお、後の工程にて形成する半導体層106として、酸化物半導体材料を含んでなる層を用いる場合、半導体層106は、酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体層の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。このため、下地絶縁層102として、加熱処理により酸素を放出する絶縁膜を用いることが好ましい。これにより、しきい値電圧がマイナス方向へシフトする要因である、半導体層106の酸素欠損を低減できる。また、下地絶縁層102は、後の工程で形成する半導体層106が結晶成長しやすいように、十分な平坦性を有することが好ましい。

【0053】

上述の「加熱処理により酸素を放出する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が1.0×1018atoms/cm3以上、好ましくは3.0×1020atoms/cm3以上であることをいう。

【0054】

ここで、TDS分析にて、酸素原子に換算しての酸素の放出量の測定方法について、以下に説明する。

【0055】

TDS分析したときの気体の放出量は、スペクトルの積分値に比例する。このため、測定したスペクトルの積分値と、標準試料の基準値に対する比とにより、気体の放出量を計算することができる。標準試料の基準値とは、所定の原子を含む試料の、スペクトルの積分値に対する原子の密度の割合である。

【0056】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量(NO2)は、以下の数式2で求めることができる。ここで、TDS分析で得られる質量数32で検出されるスペクトルの全てが酸素分子由来と仮定する。質量数32のものとしてほかにCH3OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子又は質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0057】

【数2】

【0058】

NH2は、標準試料から脱離した水素分子を密度で換算した値である。SH2は、標準試料をTDS分析したときのスペクトルの積分値である。ここで、標準試料の基準値を、NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのスペクトルの積分値である。αは、TDS分析におけるスペクトル強度に影響する係数である。数式2の詳細に関しては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として1×1016atoms/cm3の水素原子を含むシリコンウェハを用いて測定する。

【0059】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

【0060】

なお、NO2は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

【0061】

上記構成において、加熱処理により酸素を放出する層は、酸素が過剰な酸化シリコン(SiOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法により測定した値である。

【0062】

次に、スパッタリング法、蒸着法、PECVD法、PLD法、ALD(Atomic Layer Deposition)法またはMBE(Molecular Beam Epitaxy)法などを用いて半導体層106を成膜する(図2(B)参照。)。半導体層106としては、非晶質シリコン膜、多結晶シリコン膜、微結晶シリコン膜(マイクロクリスタル、セミアモルファスとも言う。)、単結晶シリコン膜などシリコン膜を用いることができる。また、ガリウム砒素膜やシリコンゲルマニウム膜などの化合物半導体膜を用いることもできる。更に、酸化物半導体材料を含んでなる膜(以下、酸化物半導体層と略記する。)を用いてもよい。近年では、酸化物半導体材料を半導体層として用いたトランジスタの研究、開発が盛んに行われている。この現状を踏まえ、以下では半導体層106に酸化物半導体層を用いる構成についての説明を行う。無論、半導体層106が酸化物半導体層に限定されるものではない。

【0063】

半導体層106は、半導体層106を構成する主要な成分以外に、キャリア供与体となる不純物が極力含まれないように成膜することが好ましい。このため、半導体層106を成膜するための材料(例えば、スパッタ装置に用いるターゲットなど。)および、成膜雰囲気は、キャリア供与体となる不純物が極力含まれない高純度化された材料および雰囲気にて成膜することが好ましい。

【0064】

半導体層106にアルカリ金属またはアルカリ土類金属が含まれると、酸化物半導体と結合することによって、キャリアが生成されることがあり、トランジスタのオフ電流が上昇する原因となる。そのため、半導体層106において、アルカリ金属またはアルカリ土類金属の濃度は、1×1018atoms/cm3以下、好ましくは2×1016atoms/cm3以下とすることが望ましい。

【0065】

また、半導体層106に、水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そのため、半導体層106において、水素濃度は、5×1018atoms/cm3未満、好ましくは1×1018atoms/cm3以下、より好ましくは5×1017atoms/cm3以下、更に好ましくは1×1016atoms/cm3以下とすることが望ましい。なお、上述の半導体層106中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)で測定されるものである。

【0066】

このように、水素濃度が十分に低減され、十分に酸素が供給されることによって、酸素欠損に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体では、キャリア密度が1×1012/cm3未満、望ましくは、1×1011/cm3未満、より望ましくは1.45×1010/cm3未満とすることができる。例えば、室温(25℃)でのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値。)は100zA(1zA(ゼプトアンペア)は1×10−21A)以下、望ましくは10zA以下となる。このように、水素などの不純物が十分に除去され、十分な酸素が供給された酸化物半導体を半導体層106として用いることで、極めて優れたオフ電流特性のトランジスタを得ることができる。

【0067】

なお、オフ電流とは、広義にトランジスタがオフ状態のときに流れるドレイン電流をいう。トランジスタのオフ状態とは、nチャネル型トランジスタにおいて、ゲート電圧がしきい値電圧より低い状態をいう。または、pチャネル型トランジスタにおいて、ゲート電圧がしきい値電圧より高い状態をいう。ドレイン電流とは、トランジスタのソース−ドレイン間の電流をいう。また、ゲート電圧とは、ソース電位を基準としたときのゲート電位との電位差をいう。

【0068】

オフ電流は、ノーマリーオフ型のトランジスタにおいて、ゲート電圧が0Vのときに流れるドレイン電流を指すことがある。ノーマリーオフ型のトランジスタとは、nチャネル型のトランジスタにおいて、しきい値電圧が0Vより大きいものをいう。または、pチャネル型のトランジスタにおいて、しきい値電圧が0Vより小さいものをいう。

【0069】

半導体層106中の水素濃度は、二次イオン質量分析(SIMS:Secondary Ion Mass Spectrometry)において、5×1019cm−3未満、好ましくは5×1018cm−3以下、より好ましくは1×1018cm−3以下、さらに好ましくは5×1017cm−3以下とする。また、アルカリ金属濃度は、二次イオン質量分析において、ナトリウム濃度が5×1016cm−3以下、好ましくは1×1016cm−3以下、さらに好ましくは1×1015cm−3以下とする。同様に、リチウム濃度は、5×1015cm−3以下、好ましくは1×1015cm−3以下とする。同様に、カリウム濃度は、5×1015cm−3以下、好ましくは1×1015cm−3以下とする。

【0070】

半導体層106は単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

【0071】

好ましくは、半導体層106は、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

【0072】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0073】

なお、CAAC−OS膜を半導体層として用いたトランジスタは、表面の平坦性を高めることにより、アモルファス状態の酸化物半導体膜を半導体層として用いたトランジスタ以上の移動度を得ることができる。なお、表面の平坦性を高めるためには、平坦な表面上に半導体層を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。また、平均面粗さ(Ra)が0に近いほど好ましい。本実施の形態においては、下地絶縁層102の表面、または、半導体層106の表面を、上述の平坦度とすればよい。

【0074】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0075】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体層の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0076】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0077】

半導体層106(少なくとも高抵抗領域106a。)としてCAAC−OS膜を用いたトランジスタは、トランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

【0078】

なお、酸化物半導体膜を構成する酸素の一部は窒素で置換されてもよい。

【0079】

半導体層106は、スパッタリング法、MBE法、パルスレーザ堆積法、ALD法等を適宜用いることができる。当該実施の形態では、半導体層106は、スパッタリングターゲット表面に対し、概垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜すればよい。

【0080】

半導体層106の膜厚は、1nm以上100nm以下、好ましくは3nm以上40nm以下、更に好ましくは5nm以上20nm以下とすればよい。特に、チャネル長が30nm以下のトランジスタにおいては、半導体層106の厚さを5nm程度とすることで、短チャネル効果を抑制でき、安定な電気的特性を得ることができる。

【0081】

半導体層106をCAAC−OS膜とするには、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa−b面から劈開し、a−b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、CAAC−OS膜を成膜することができる。

【0082】

また、CAAC−OS膜を成膜するために、以下の条件を適用することが好ましい。

【0083】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度(水素、水、二酸化炭素および窒素など)を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が−80℃以下、好ましくは−100℃以下である成膜ガスを用いる。

【0084】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を100℃以上740℃以下、好ましくは200℃以上500℃以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。

【0085】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

【0086】

スパッタリング用ターゲットの一例として、In−Ga−Zn−O化合物ターゲットについて以下に示す。

【0087】

InOX粉末、GaOY粉末およびZnOZ粉末を所定のmol数で混合し、加圧処理後、1000℃以上1500℃以下の温度で加熱処理をすることで多結晶であるIn−Ga−Zn−O化合物ターゲットとする。なお、X、YおよびZは任意の正数である。ここで、所定のmol数比は、例えば、InOX粉末、GaOY粉末およびZnOZ粉末が、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3または3:1:2である。なお、粉末の種類、およびその混合するmol数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。

【0088】

なお、半導体層106の成膜を行う前に、成膜室の加熱および排気を行って、成膜室中の水分などの不純物を除去しておくことが好ましい。特に成膜室の内壁に吸着して存在するこれらの不純物を除去することが重要である。ここで、加熱処理は、例えば、100℃以上450℃以下で行えばよい。また、処理室の排気は、ドライポンプなどの粗引きポンプと、スパッタイオンポンプ、ターボ分子ポンプおよびクライオポンプなどの高真空ポンプとを適宜組み合わせて行うとよい。ターボ分子ポンプは大きいサイズの分子の排気が優れる一方、水分や水素の排気能力が低い。さらに、水分の排気能力の高いクライオポンプまたは水素の排気能力の高いスパッタイオンポンプを組み合わせることが有効となる。また、このとき、不活性ガスを導入しながら不純物の除去を行うと、排気するだけでは脱離しにくい水分などの脱離速度をさらに大きくすることができる。このような処理を行って酸化物半導体の成膜前に成膜室の不純物を除去することにより、半導体層106への水素、水分、水酸基、水素化物などの混入を抑制することができる。

【0089】

半導体層106の成膜に用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。また、スタビライザーとしてチタン(Ti)を有することが好ましい。また、スタビライザーとしてジルコニウム(Zr)を有することが好ましい。

【0090】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0091】

また、半導体層106は、トランジスタのオフ電流を低減するため、バンドギャップが2.5eV以上、好ましくは2.8eV以上、さらに好ましくは3.0eV以上の材料を用いることが好ましい。

【0092】

トランジスタのオフ抵抗(トランジスタがオフ状態の時における、ソースとドレイン間の抵抗をいう。)は、チャネルが形成される半導体層における熱的に励起するキャリアの濃度に反比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、シリコンの場合にはバンドギャップが1.1eVであるため、室温(300K)での熱励起キャリアの濃度は1×1011cm−3程度である。

【0093】

一方、例えばバンドギャップが3.2eVの半導体(酸化物半導体を想定。)の場合では熱励起キャリアの濃度は1×10−7cm−3程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2eVの半導体の抵抗率は、シリコンより18桁も大きい。

【0094】

このようなバンドギャップの広い酸化物半導体を半導体層106に適用したトランジスタ(OSトランジスタ)は、極めて低いオフ電流を実現できる。

【0095】

半導体層106として、例えば、単元系金属の酸化物である酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0096】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0097】

また、半導体層106として、InMO3(ZnO)m(m>0、且つ、mは整数でない。)で表記される酸化物を用いてもよい。なお、Mは、Ga、Fe、MnおよびCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In2SnO5(ZnO)n(n>0、且つ、nは整数。)で表記される材料を用いてもよい。

【0098】

例えば、半導体層106としてIn:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子比のIn−Ga−Zn系酸化物やその組成の近傍のIn−Ga−Zn系酸化物を用いることができる。また、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子比のIn−Sn−Zn系酸化物やその組成の近傍のIn−Sn−Zn系酸化物を用いてもよい。

【0099】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値電圧、ばらつき等。)に応じて適切な組成の材料を用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

【0100】

例えば、In−Sn−Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn系酸化物でも、バルク内欠陥密度を下げることにより移動度を上げることができる。

【0101】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物の組成の近傍であるとは、a、b、cが、(a−A)2+(b−B)2+(c−C)2≦r2を満たすことをいう。rとしては、例えば、0.05とすればよい。他の酸化物でも同様である。

【0102】

半導体層106としてIn−Ga−Zn系酸化物をスパッタリング法で成膜する場合、好ましくは、原子数比がIn:Ga:Zn=1:1:1、4:2:3、3:1:2、1:1:2、1:3:2、2:1:3、または3:1:4で示されるIn−Ga−Zn−Oターゲットを用いる。前述の原子数比を有するIn−Ga−Zn−Oターゲットを用いて半導体層106を成膜することで、多結晶膜またはCAAC−OS膜が形成されやすくなる。

【0103】

また、半導体層106としてIn−Sn−Zn系酸化物をスパッタリング法で成膜する場合、好ましくは、原子数比がIn:Sn:Zn=1:1:1、2:1:3、1:2:2、または20:45:35で示されるIn−Sn−Zn−Oターゲットを用いる。前述の原子数比を有するIn−Sn−Zn−Oターゲットを用いて半導体層106を成膜することで、多結晶膜またはCAAC−OS膜が形成されやすくなる。

【0104】

また、半導体層106としてIn−Zn系酸化物をスパッタリング法で成膜する場合、好ましくは、原子数比で、In:Zn=50:1〜1:2(mol比に換算するとIn2O3:ZnO=25:1〜1:4)、好ましくはIn:Zn=20:1〜1:1(mol比に換算するとIn2O3:ZnO=10:1〜1:2)、さらに好ましくはIn:Zn=15:1〜1.5:1(mol比に換算するとIn2O3:ZnO=15:2〜3:4)で示されるIn−Zn−Oターゲットを用いる。前述の原子数比を有するIn−Zn−Oターゲットを用いて半導体層106を成膜することで、多結晶膜またはCAAC−OS膜が形成されやすくなる。

【0105】

なお、上述では半導体層106の成膜に用いるターゲット中の金属元素の原子数比は整数にて記載されているが、半導体層106中に含まれる金属元素の原子数比を整数とする場合においては、ターゲット中の金属元素の原子数比は上述の値から若干前後してもよい。例えば、半導体層106として、In:Ga:Zn=1:1:1の半導体層106を形成する場合において、In2O3:Ga2O3:ZnO=1+α:1+β:1+γ[mol比]の組成を有するターゲットを用いればよい。α、βおよびγの値は成膜条件により変動するが、概ね−0.5以上0.5以下の値となる。

【0106】

なお、半導体層106は、成膜時に酸素が多く含まれるような条件(例えば、酸素100%の雰囲気下でスパッタリング法により成膜を行うなど。)で成膜して、酸素を多く含む(好ましくは半導体層の化学量論的組成に対し、酸素の含有量が過剰である領域が含まれている)層とすることが好ましい。

【0107】

成膜の雰囲気は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または、希ガスと酸素の混合雰囲気下などとすればよい。ここで、成膜時に希ガスより酸素の体積比を大きくすることにより、半導体層106に酸素が多く取り込まれるため、半導体層106中の酸素欠損を低減することができる。また、半導体層106への水分の混入を防ぐために、水分が十分に除去された高純度ガスを用いた雰囲気とすることが望ましい。

【0108】

なお、半導体層106としてCAAC−OS膜を用いる場合、CAAC−OS膜を複数の酸化物半導体膜が積層された構造としてもよい。例えば、半導体層106を、第1の酸化物半導体膜、第2の酸化物半導体膜および第3の酸化物半導体膜の積層として、各々を異なる組成としてもよい。例えば、第1の酸化物半導体膜および第3の酸化物半導体膜に三元系金属の酸化物を用い、第2の酸化物半導体膜に二元系金属の酸化物を用いる、または、第1の酸化物半導体膜および第3の酸化物半導体膜に二元系金属の酸化物を用い、第2の酸化物半導体膜に三元系金属の酸化物を用いる。

【0109】

また、第1の酸化物半導体膜、第2の酸化物半導体膜および第3の酸化物半導体膜の構成元素を同一とし、組成を異ならせてもよい。例えば、第1の酸化物半導体膜および第3の酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1とし、第2の酸化物半導体膜の原子数比をIn:Ga:Zn=3:1:2としてもよい。また、第1の酸化物半導体膜および第3の酸化物半導体膜の原子数比をIn:Ga:Zn=1:3:2とし、第2の酸化物半導体膜の原子数比をIn:Ga:Zn=3:1:2としてもよい。

【0110】

この時、第2の酸化物半導体膜はInとGaの含有率をIn>Gaとするとよい。また第1の酸化物半導体膜および第3の酸化物半導体膜のInとGaの含有率をIn≦Gaとするとよい。

【0111】

酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることによりs軌道のオーバーラップが多くなる傾向があるため、In>Gaの組成となる酸化物はIn≦Gaの組成となる酸化物と比較して高い移動度を備える。また、GaはInと比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、In≦Gaの組成となる酸化物はIn>Gaの組成となる酸化物と比較して安定した特性を備える。

【0112】

なお、酸化物半導体膜に接して酸化物半導体膜とは異なる膜(図中では、下地絶縁層102や絶縁層107など。)を形成する際に、酸化物半導体膜に接して形成される膜から酸化物半導体膜中に不純物が拡散する恐れがある。たとえば、下地絶縁層102や絶縁層107中に含まれるシリコンやカーボンなどが酸化物半導体膜中に拡散すると、トランジスタの電気特性に悪影響を及ぼす可能性がある。

【0113】

しかしながら、上述のように酸化物半導体膜の積層構造とし、高い移動度を備える酸化物半導体膜(つまり、In>Gaの組成となる酸化物半導体膜。本実施の形態では第2の酸化物半導体膜に相当する。)に接して、当該高い移動度を備える酸化物半導体膜よりも酸素欠損が少なく安定した特性を備える酸化物半導体膜(つまり、In≦Gaの組成となる酸化物半導体膜。本実施の形態では第1の酸化物半導体膜および第3の酸化物半導体膜に相当する。)を形成し、酸化物半導体膜の積層構造に接する膜(図中では、下地絶縁層102や絶縁層107など。)から高い移動度を備える酸化物半導体膜を離すことにより、不純物拡散に起因したトランジスタの電気特性(例えば、移動度の

低下など。)の悪影響を抑制することができる。したがって、トランジスタの移動度および信頼性を高めることが可能となる。

【0114】

また、半導体層106を成膜後、半導体層106に取り込まれた水分を除去(脱水化または脱水素化)するための加熱処理を行ってもよい。加熱処理を行うことによって、半導体層106中に含まれる水分をさらに除去することができる。加熱処理の温度は、不活性ガス雰囲気下、250℃以上700℃以下、好ましくは450℃以上600℃以下、または基板の歪み点未満とする。不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水分、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とすればよい。

【0115】

当該加熱処理は、例えば、抵抗発熱体などを用いた電気炉に基板を導入し、窒素雰囲気下、450℃、1時間の条件で行うことができる。

【0116】

また、加熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、LRTA(Lamp Rapid Thermal Anneal)装置、GRTA(Gas Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。なお、加熱処理装置としてGRTA装置を用いる場合には、その熱処理時間が短いため、650℃〜700℃の高温に加熱した不活性ガス中で基板を加熱してもよい。

【0117】

なお、上述の加熱処理には水分を除去する効果があるため、当該加熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該加熱処理を行うタイミングは、半導体層106成膜直後に限らず、例えば、半導体層106を島状に加工した後など、別のタイミングで行うことも可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

【0118】

また、上記の加熱処理で半導体層106を加熱した後、同じ炉にて半導体層106に酸素を加える(加酸素化とも言う。)ための加熱処理を行ってもよい。当該加熱処理は、加熱処理装置に高純度の酸素ガス、高純度のN2Oガス、または超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で−55℃)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)を導入し、200℃以上基板の歪み点未満で加熱処理を行えばよい。好ましくは、250℃以上450℃以下加熱処理を行えばよい。特にこれらのガスには、水分、水素などが含まれないことが好ましい。また、同じ炉に導入する酸素ガスまたはN2ガスの純度を、6N以上好ましくは7N以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。この工程により、脱水化または脱水素化処理により生じた半導体層106中の酸素欠損を補填することができる。

【0119】

なお、上述の加熱処理には脱水化処理または脱水素化処理により半導体層106中に生じた酸素欠損を補填する効果があるため、当該加熱処理を、加酸素化処理などと呼ぶこともできる。当該加熱処理についても、脱水化処理または脱水素化処理と同様に、半導体層106を島状に加工した後など、別のタイミングで行うことも可能であり、また、一回に限らず複数回行っても良い。

【0120】

半導体層106に、上述の加熱処理を行うことで、膜中の不純物準位を極めて小さくすることが可能となる。その結果、トランジスタの電界効果移動度を理想的な電界効果移動度近くまで高めることが可能となる。

【0121】

次に、半導体層106に対してフォトリソグラフィ工程などを行い加工して、半導体層106を島状に加工する(図2(C)参照。)。

【0122】

次に、半導体層106上に、絶縁層107と導電層を、スパッタリング法、蒸着法、PECVD法、PLD法、ALD法またはMBE法などを用いて順に成膜し、導電層に対してフォトリソグラフィ工程などを行い加工して、ゲート電極110を形成する(図2(D)参照。)。

【0123】

絶縁層107としては、下地絶縁層102と同様の材料および方法を用いることができる。なお、絶縁層107は、下地絶縁層102と同様に、加熱処理により酸素を放出する絶縁層(好ましくは、絶縁層の化学量論的組成に対し、酸素の含有量が過剰である領域が含まれている絶縁層)を用いると好ましい。これにより、半導体層106から絶縁層107への酸素の移動を抑制することができ、かつ、絶縁層107から半導体層106への酸素の供給を行うことができる。

【0124】

ゲート電極110としては、スパッタリング法などにより、アルミニウム、チタン、クロム、コバルト、ニッケル、銅、モリブデン、銀、タンタルおよびタングステン、それらの窒化物、酸化物ならびに合金から一種以上選択し、単層でまたは積層で用いればよい。または、少なくともInおよびZnを含む酸化物または酸化窒化物を用いても構わない。例えば、In−Ga−Zn−O−N系材料などを用いればよい。

【0125】

次に、イオンドーピング法やイオン注入法により、半導体層106の抵抗値を低減する機能を有する不純物イオン130を、絶縁層107を介して半導体層106に添加する。この際、ゲート電極110がマスクとして機能するため、高抵抗領域106aおよび低抵抗領域106bを有する半導体層106が自己整合的に形成される(図3(A)参照。)。なお、イオン注入法は、必要なイオン(本実施の形態では、不純物イオン130。)のみを取り出す質量分離器を用いているため、対象物(本実施の形態では、半導体層106。)に対して不純物イオン130のみを選択的に添加できる。このため、イオンドーピング法を用いて添加した場合と比べて半導体層106中への不純物(例えば水素など)の混入が少なくなるため好ましい。ただし、イオンドーピング法を除外するものではない。

【0126】

なお、絶縁層107を介して不純物イオン130を添加することにより、半導体層106中に不純物イオン130を添加する際に生じるダメージ(例えば半導体層106中での格子欠陥の発生など)を低減することができる。

【0127】

次に、下地絶縁層102と同様の材料および方法で絶縁層を成膜し、当該絶縁層をエッチングすることにより側壁絶縁層112を形成する(図3(B)参照)。側壁絶縁層112は、絶縁層に異方性の高いエッチング工程を行うことで自己整合的に形成することができる。例えば、ドライエッチング法を用いると好ましい。ドライエッチング法に用いるエッチングガスとしては、例えば、トリフルオロメタン、オクタフルオロシクロブタン、テトラフルオロメタンなどのフッ素を含むガスが挙げられる。エッチングガスには、希ガスまたは水素を添加してもよい。ドライエッチング法は、基板に高周波電圧を印加する、反応性イオンエッチング法(RIE法)を用いると好ましい。

【0128】

側壁絶縁層112を形成した後、ゲート電極110および側壁絶縁層112をマスクとして絶縁層107を加工し、ゲート絶縁層108を形成する(図3(C)参照。)。

【0129】

なお、本実施の形態では、ゲート電極110の形成直後の工程において、ゲート電極110をマスクに用いて半導体層106に不純物イオン130の添加を行ったが、側壁絶縁層112の形成後にゲート電極110および側壁絶縁層112をマスクに用いて、半導体層106に不純物イオン130を添加してもよい。こうすることで、側壁絶縁層112と重畳する半導体層106の領域を高抵抗領域106aに含めることができる。

【0130】

次に、半導体層106、ゲート電極110および側壁絶縁層112上に、ゲート電極110と同様の材料および方法で導電膜を成膜し、フォトリソグラフィ工程などによって当該導電膜を加工して、ソース電極及びドレイン電極として機能する一対の電極114を形成する。これにより、トランジスタ150が形成される(図3(D)参照。)。

【0131】

次に、ゲート電極110、側壁絶縁層112および一対の電極114上に、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bを、この順に成膜する(図4(A)参照)。なお、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bの具体的な作製方法については、実施例1にて詳細に記載する。

【0132】

絶縁層116は、PECVD法またはスパッタリング法を用いて、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜または窒化酸化シリコン膜から選ばれた無機材料膜を一層または積層して用いればよい。

【0133】

絶縁層116として、上述の無機材料膜を一層または積層して用いる場合、半導体層106の成膜と同様に、成膜を行う前に成膜室の加熱および排気を行い、また、水分などの不純物が十分に除去された高純度ガスを用いた雰囲気で成膜することで、絶縁層116中への水分の混入を極力抑制することが好ましい。

【0134】

また、絶縁層116は、スピンコート法、印刷法、ディスペンス法またはインクジェット法などを用いて絶縁性を有する材料を塗布し、塗布した材料に応じた硬化処理(例えば、加熱処理や光照射処理など。)を行い形成してもよい。なお、絶縁性を有する材料としては、例えば、アクリル樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリアミドイミド樹脂、エポキシ樹脂等の有機樹脂、有機ポリシロキサンと上述の無機材料などの有機無機混合材料を用いることもできる。

【0135】

絶縁層116は、絶縁層116より上に形成された導電層(本実施の形態における配線120。)と絶縁層116より下に形成された導電層(本実施の形態におけるゲート電極110および一対の電極114。)の間で寄生容量が極力生じないように、比誘電率の低い絶縁材料で構成することが好ましい。また、絶縁層116は、外部からトランジスタ150に侵入する水分に対して高いバリア性を有することが好ましい。これらの観点から考えると、絶縁層116は上述のうち、無機材料膜を一層または積層した構造が好適であるといえる。ただし、上述の有機材料を除外するものではない。絶縁層116として上述のような有機材料を用いる場合は、ポリイミド樹脂等の吸湿性の低い材料を用い、また、有機材料中にシリカゲルや多孔質アルミナなどの乾燥剤を混ぜることが好ましい。

【0136】

なお、絶縁層116は、上述の寄生容量やバリア性、後の工程にて形成する配線120のコンタクト性、および生産性の観点を鑑みると、無機材料膜を用いた場合は200nm以上2000nm以下の膜厚、有機材料膜を用いた場合は200nm以上5000nm以下の膜厚とすることが好ましい。

【0137】

第1の金属酸化物層118aおよび第2の金属酸化物層118bは、スパッタリング法、MBE法、パルスレーザ堆積法、ALD法などを用いて成膜すればよい。

【0138】

第1の金属酸化物層118aは、酸化アルミニウム、酸化ガリウム、酸化チタン、酸化ジルコニウム、酸化ハフニウム、酸化バナジウム、酸化ニオブまたは酸化モリブデンのいずれか一の、アモルファス構造を有する膜を用いればよい。なお、上述の「アモルファス構造を有する」とは、第1の金属酸化物層118aの断面を透過型電子顕微鏡(Transmission Electron Microscope:TEM)にて観察した際に、明確な格子像や格子縞が確認されない領域を有することを表しており、当該領域が全体の60%以上、好ましくは80%である膜を、第1の金属酸化物層118aとして用いることが好ましい。なお、第1の金属酸化物層118aの任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)を観察し、観察箇所において明確な格子像や格子縞が確認されない領域が60%以上ある場合は、これをもって「全体の60%以上」としてもよい。

【0139】

あるいは、X線反射率測定(XRR:X−Ray Reflectometry)を用いて第1の金属酸化物層118a断面の任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)の膜密度を測定し、全ての測定箇所において膜密度が2.9g/cm3以上3.3g/cm3以下であった場合は、これをもって「アモルファス構造を有する」としてもよい。

【0140】

あるいは、透過型電子顕微鏡を用いて第1の金属酸化物層118a断面の任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)の電子線回折像を観察し、全ての観察箇所において幅広く明確でないパターン(ハローパターン、ハローリングまたはハローとも言われる。)が観察された場合は、これをもって「アモルファス構造を有する」としてもよい。

【0141】

「アモルファス構造を有する」の解釈については、上述のいずれか一以上の解釈が第1の金属酸化物層118aに適合していればよく、必ずしも上述の全ての解釈が適合している必要はない。

【0142】

第2の金属酸化物層118bは、酸化アルミニウム、酸化ガリウム、酸化チタン、酸化ジルコニウム、酸化ハフニウム、酸化バナジウム、酸化ニオブまたは酸化モリブデンのいずれか一の、多結晶構造を有する膜を用いればよい。なお、上述の「多結晶構造を有する」とは、第2の金属酸化物層118bの断面を透過型電子顕微鏡(Transmission Electron Microscope:TEM)にて観察した際に、明確な格子像や格子縞が確認される領域を有することを表しており、当該領域が全体の60%以上、好ましくは80%である膜を、第2の金属酸化物層118bとして用いることが好ましい。なお、第2の金属酸化物層118bの任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)を観察し、観察箇所において明確な格子像や格子縞が確認される領域が60%以上ある場合は、これをもって「全体の60%以上」としてもよい。

【0143】

あるいは、X線反射率測定を用いて第2の金属酸化物層118b断面の任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)の膜密度を測定し、全ての測定箇所において膜密度が3.7g/cm3以上4.1g/cm3以下であった場合は、これをもって「多結晶構造を有する」としてもよい。

【0144】

あるいは、透過型電子顕微鏡を用いて第2の金属酸化物層118b断面の任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)の電子線回折像を観察し、全ての観察箇所においてデバイシェラーパターン(デバイシェラーリングとも言われる。)が観察されることをもって「多結晶構造を有する」としてもよい。

【0145】

「多結晶構造を有する」の解釈については、上述のいずれか一以上の解釈が第2の金属酸化物層118bに適合していればよく、必ずしも上述の全ての解釈が適合している必要はない。

【0146】

なお、第1の金属酸化物層118aおよび第2の金属酸化物層118bは、同一装置内にて高真空状態を保持したまま連続して成膜することが好ましい。これにより、第1の金属酸化物層118aおよび第2の金属酸化物層118bを成膜する際に、膜中への水分混入および界面への水分の付着を抑制できるため、水分の侵入によるトランジスタの劣化を、より抑制することができる。

【0147】

さらに、第1の金属酸化物層118aおよび第2の金属酸化物層118bに加え、絶縁層116についても同一装置内にて高真空状態を保持したまま連続して成膜することにより、絶縁層116,第1の金属酸化物層118aおよび第2の金属酸化物層118bを成膜する際に、膜中への水分混入および界面への水分の付着を抑制できるため、水分の侵入によるトランジスタの劣化を、更に抑制することができる。

【0148】

なお、第1の金属酸化物層118aおよび第2の金属酸化物層118bを同一装置内にて高真空状態を保持したまま連続して成膜する場合、第1の金属酸化物層118aと第2の金属酸化物層118bを、同一のターゲットを用いて成膜することで、基板を異なる成膜室に移動させることによる製造タクトの増加を抑制できる。また、金属酸化物層を成膜するのに必要なターゲットが1種類のみとなるため、製造コストの増加を抑制できる。

【0149】

また、上述にて説明したとおり、絶縁層116より上に形成された導電層(本実施の形態における配線120。)と絶縁層116より下に形成された導電層(本実施の形態におけるゲート電極110および一対の電極114。)の間で寄生容量が極力生じないように、絶縁層116は比誘電率の低い絶縁材料で構成されているため、例えば、多結晶構造を有する第2の金属酸化物層118bが絶縁層116に接する構造とすると、第2の金属酸化物層118bと絶縁層116の間では比誘電率に大きな開きがあるため、誘電率の界面部分(つまり、絶縁層116と第2の金属酸化物層118bの界面部分。)では、両側からの分極電荷が相殺されずに誘導電荷が発生し、当該電荷が半導体層106中に形成されるチャネル領域に影響を及ぼす場合がある。このため、トランジスタの電気的特性に悪影響を及ぼす(例えば、Vth(しきい値電圧とも言う)にバラツキが生じるなど。)といった問題が生じる場合がある。

【0150】

しかし、本実施の形態のように、絶縁層116と、多結晶構造を有する第2の金属酸化物層118bの間に、アモルファス構造を有する第1の金属酸化物層118aが位置する構造とすることにより、第1の金属酸化物層118aが、絶縁層116と多結晶構造を有する第2の金属酸化物層118bの誘電率差を埋める役目を担い、誘導電荷の発生を抑制することができるため、しきい値電圧バラツキなどの電気的特性変動が少ない、信頼性の高いトランジスタとすることができる。

【0151】

次に、フォトリソグラフィ工程などによって、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに、一対の電極114に到達する開口部を形成した後、第2の金属酸化物層118b上に導電層を形成し、当該導電層をフォトリソグラフィ工程などによって加工し、配線120を形成する(図4(B)参照。)。なお、配線120となる導電層は、ゲート電極110と同様の材料および方法で成膜すればよい。

【0152】

なお、図示しないが、第2の金属酸化物層118bおよび配線120を覆う保護膜を有する構造としても構わない。当該構造とすることで、第2の金属酸化物層118bの表面伝導に起因して生じる微小リーク電流を低減することができ、トランジスタのオフ電流を低減することができる。

【0153】

以上が、本実施の形態の半導体装置の作製方法である。

【0154】

上述の方法により半導体装置を作製することにより、当該半導体装置は、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bの効果により、トランジスタ150への水分の侵入を効果的に抑制することができるため、電気的特性の変動が抑制された半導体装置を提供することができる。

【0155】

(実施の形態2)

本実施の形態では、実施の形態1にて記載した半導体装置とは異なる構成の半導体装置について、その構成および作製方法の一例を、図5を用いて説明する。なお、上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0156】

<本実施の形態における半導体装置の構成および作製方法>

図5は、コプラナー型であるトップゲート・トップコンタクト構造のトランジスタを有する半導体装置の上面図および断面図である。図5(A)はトランジスタの上面図であり、図5(B)は図5(A)の一点鎖線C−D部分に対応する断面である。なお、図5(A)はトランジスタの構造を分かり易くするため、一部の構成要素を省略している。

【0157】

図5に示すトランジスタ150を有する半導体装置は、金属酸化物層118の形成位置が絶縁層116の下にある点で、実施の形態1にて記載した図1に示す半導体装置の構造と異なっている。

【0158】

実施の形態1にて記載したとおり、絶縁層116は、膜中に水分などの不純物が極力取り込まれないように成膜することが好ましい。しかし、成膜時などに意図せず水分などが取り込まれてしまう場合がある。実施の形態1にて記載した構造の半導体装置は、外部からの水分の侵入に対しては高いバリア性を有しているが、上述のように絶縁層116中に水分が取り込まれてしまった場合、第1の金属酸化物層118aおよび第2の金属酸化物層118bによる水分侵入抑制効果はほとんど無いため、電気的特性変動の抑制効果が低減してしまう。

【0159】

しかし、半導体装置の構造を図5(B)に示す構造とすることにより、仮に、絶縁層116に水分などの不純物が取り込まれた場合においても、第1の金属酸化物層118aおよび第2の金属酸化物層118bにより、トランジスタ150への水分の侵入を効果的に抑制することができる。

【0160】

図5に示す半導体装置の作製方法については、実施の形態1と同様に下地絶縁層102、半導体層106、ゲート絶縁層108、ゲート電極110、側壁絶縁層112および一対の電極114を形成してトランジスタ150を形成した後、第1の金属酸化物層118a、第2の金属酸化物層118bおよび絶縁層116を、この順に成膜し、最後に一対の電極114に接続された配線120を形成すればよい。なお、各構成要素の使用材料や形成方法については、実施の形態1を参酌することができる。

【0161】

なお、図5(B)では、第1の金属酸化物層118a上に第2の金属酸化物層118bが位置し、第2の金属酸化物層118b上に絶縁層116が位置する構造であるが、第1の金属酸化物層118aと第2の金属酸化物層118bの位置が逆になっていてもよい。

【0162】

以上が、本実施の形態の半導体装置の構成および作製方法である。

【0163】

上述の方法により作製された半導体装置は、絶縁層116を形成する際に当該層に水分が取り込まれた場合においても、トランジスタ150への水分の侵入を効果的に抑制することができるため、電気的特性の変動が抑制された半導体装置を提供することができる。

【0164】

(実施の形態3)

本実施の形態では、実施の形態1にて記載した半導体装置とは異なる構成の半導体装置について、その構成および作製方法の一例を、図6を用いて説明する。なお、上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0165】

本実施の形態において図6(A)乃至図6(C)に示す半導体装置は、ボトムゲート構造のトランジスタを有する半導体装置の一例である。図6(A)乃至図6(C)は、トランジスタ651、トランジスタ652、トランジスタ653におけるチャネル長方向の断面図である。

【0166】

半導体装置の一形態として図6(A)にボトムゲート・トップコンタクト構造のトランジスタ651を有する半導体装置を示す。トランジスタ651は、逆スタガ型トランジスタとも表現できる。

【0167】

図6(A)に示すように、トランジスタ651は、基板100と、基板100上の下地絶縁層102と、下地絶縁層102上のゲート電極110と、ゲート電極110及び下地絶縁層102上のゲート絶縁層108と、ゲート絶縁層108上の半導体層106と、半導体層106上の一対の電極114を有している。また、トランジスタ651上に、半導体層106および一対の電極114を覆って設けられた絶縁層116と、絶縁層116上に設けられた第1の金属酸化物層118aと、第1の金属酸化物層118a上に設けられた第2の金属酸化物層118bと、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに設けられた開口部を介して一対の電極114と電気的に接続して設けられた配線120と、を有している。

【0168】

当該半導体装置は、上述の実施の形態と比較して構成要素の形成順(例えば、ゲート絶縁層108を成膜する前に、ゲート電極110を形成するなど。)が異なっているが、各々の構成要素の使用材料や形成方法は基本的に実施の形態1と同じであるため、上述の実施の形態に記載された作製方法を参酌して作製することができる。

【0169】

また、半導体装置の他の一形態として図6(B)にチャネル保護型(チャネルストップ型ともいう。)ボトムゲート・トップコンタクト構造のトランジスタ652を有する半導体装置を示す。トランジスタ652は、逆スタガ型トランジスタとも表現できる。

【0170】

図6(B)に示すように、トランジスタ652は、基板100と、基板100上の下地絶縁層102と、下地絶縁層102上のゲート電極110と、ゲート電極110及び下地絶縁層102上のゲート絶縁層108と、ゲート絶縁層108上の半導体層106と、半導体層106上の絶縁層602と、半導体層106および絶縁層602上の一対の電極114を有している。また、トランジスタ652上に、半導体層106、絶縁層602および一対の電極114を覆って設けられた絶縁層116と、絶縁層116上に設けられた第1の金属酸化物層118aと、第1の金属酸化物層118a上に設けられた第2の金属酸化物層118bと、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに設けられた開口部を介して一対の電極114と電気的に接続して設けられた配線120と、を有している。

【0171】

当該半導体装置は、図6(A)の半導体装置と比較して半導体層106上に絶縁層602を有している点が異なっている。絶縁層602は、エッチング処理(例えば、ドライエッチング処理やウェットエッチング処理など。)で一対の電極114を形成する際に、一対の電極114よりも下の層までエッチングが到達すること(オーバーエッチングとも言われる。)を防止する効果がある。特に、半導体層106が非常に薄い(具体的には、100nm以下、より具体的には40nm以下、さらに具体的には20nm以下。)場合、ごく僅かな厚さでも半導体層106がエッチングされると、トランジスタ652の電気的特性が大きく変動する可能性があるため、半導体層106の厚さが薄い場合、当該構造とすることが好ましい。なお、各々の構成要素の使用材料や形成方法は基本的に実施の形態1と同じであるため、上述の実施の形態に記載された作製方法を参酌して作製することができる。

【0172】

また、半導体装置の他の一形態として図6(C)にボトムゲート・ボトムコンタクト構造のトランジスタ653を有する半導体装置を示す。トランジスタ653は、逆スタガ型トランジスタとも表現できる。

【0173】

図6(C)に示すように、トランジスタ653は、基板100と、基板100上の下地絶縁層102と、下地絶縁層102上のゲート電極110と、ゲート電極110及び下地絶縁層102上のゲート絶縁層108と、ゲート絶縁層108上の一対の電極114と、ゲート絶縁層108及び一対の電極114上の半導体層106を有している。また、トランジスタ653上に、半導体層106および一対の電極114を覆って設けられた絶縁層116と、絶縁層116上に設けられた第1の金属酸化物層118aと、第1の金属酸化物層118a上に設けられた第2の金属酸化物層118bと、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに設けられた開口部を介して一対の電極114と電気的に接続して設けられた配線120と、を有している。

【0174】

当該半導体装置は、図6(A)の半導体装置と比較して、半導体層106を形成する前に一対の電極114を形成している点で異なっているが、各々の構成要素の使用材料や形成方法は基本的に実施の形態1と同じであるため、上述の実施の形態に記載された作製方法を参酌して作製することができる。

【0175】

なお、図6(A)乃至図6(C)では、第1の金属酸化物層118aおよび第2の金属酸化物層118bが絶縁層116の上に位置する構成となっているが、実施の形態2にて記載したように、第1の金属酸化物層118aおよび第2の金属酸化物層118bが絶縁層116の下に位置する構造となっていてもよい。この際の構造および作製方法については、本実施の形態および実施の形態2を参酌すればよい。

【0176】

以上が、本実施の形態の半導体装置の構成および作製方法である。

【0177】

(実施の形態4)

本実施の形態では、先の実施の形態で説明した半導体装置を電子機器に適用する場合について、図7を用いて説明する。本実施の形態では、コンピュータ、携帯情報端末(携帯電話、携帯型ゲーム機、音響再生装置なども含む。)、電子ペーパー、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう。)、デジタルビデオカメラなどの電子機器に、上述の半導体装置を適用する場合について説明する。

【0178】

図7(A)は、携帯型の情報端末であり、筐体701、筐体702、第1の表示部703a、第2の表示部703bなどによって構成されている。筐体701と筐体702の内部には、様々な電子部品(例えば、CPU、MPU、記憶素子など。)が組み込まれている。また、第1の表示部703aと第2の表示部703bには、画像を表示するために必要な電子回路(例えば、駆動回路や選択回路など。)が搭載されている。これら電子部品や電子回路の中に先の実施の形態に示す、トランジスタへの水分の侵入が抑制された半導体装置が設けられている。そのため、長期間にわたり性能の劣化(例えば、記憶素子であれば、記憶素子中の半導体装置のしきい値電圧が変動し、誤った情報が記憶されるなど。また、駆動装置であれば、駆動装置中の半導体装置のしきい値電圧が変動し、誤った駆動信号を出力するなど。)が抑制された携帯型の情報端末が実現される。なお、先の実施の形態に示す半導体装置は、筐体701、筐体702の少なくとも一に設けられていればよい。

【0179】

なお、第1の表示部703aおよび第2の表示部703bの少なくとも一方は、タッチ入力機能を有する表示部となっており、例えば図7(A)の左図のように、第1の表示部703aに表示される選択ボタン704により「タッチ入力」を行うか、「キーボード入力」を行うかを選択できる。選択ボタンは様々な大きさで表示できるため、幅広い世代の人が使いやすさを実感できる。ここで、例えば「キーボード入力」を選択した場合、図7(A)の右図のように第1の表示部703aにはキーボード705が表示される。これにより、従来の情報端末と同様に、キーボード入力による素早い文字入力などが可能となる。

【0180】

また、図7(A)に示す携帯型の情報端末は、図7(A)の右図のように、筐体701と筐体702を分離することができる。これにより、筐体702を壁に掛けて大人数で画面情報を共有しながら、筐体701で画面情報をコントロールするといった操作が可能となり、非常に便利である。なお、当該装置を使用しない場合は、第1の表示部703a及び第2の表示部703bが向かい合うように、筐体701および筐体702を重ねた状態とすることが好ましい。これにより、外部より加わる衝撃などから第1の表示部703a及び第2の表示部703bを保護することができる。

【0181】

図7(A)に示す携帯型の情報端末は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。

【0182】

また、図7(A)に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0183】

さらに、図7(A)に示す筐体701や筐体702にアンテナやマイク機能や無線機能を持たせ、携帯電話として用いてもよい。

【0184】

図7(B)は、テレビジョン装置であり、筐体721、表示部722、スタンド723、リモコン724などで構成されている。テレビジョン装置についても、上述の携帯型の情報端末と同様に筐体721および表示部722には、様々な電子部品や電子回路が組み込まれており(または搭載されており)、これら電子部品や電子回路の中に先の実施の形態に示す、トランジスタへの水分の侵入が抑制された半導体装置を設けることで、長期間にわたり性能の劣化が抑制されたテレビジョン装置が実現される。

【0185】

図7(C)は、デジタルカメラであり、筐体731、操作スイッチ732、バッテリー733などを備えており、また、背面には表示部(本体の裏面にあるため図示しない。)などを備えている。デジタルカメラについても、筐体731内や表示部などに、先の実施の形態に示す半導体装置が設けられている。そのため、長期間にわたり性能の劣化が抑制されたデジタルカメラが実現される。

【0186】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置が搭載されている。このため、消費電力を低減した電子機器が実現される。

【実施例1】

【0187】

本実施例では、実施の形態1にて記載した、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bの形成方法についての具体例を記載する。また、当該層についての各種分析結果を記載する。

【0188】

絶縁層116は、スパッタリング装置を用いて酸化珪素膜を成膜した。絶縁層116の成膜条件は、使用ターゲット:Si、基板温度:R.T.、成膜雰囲気:100%O2、O2ガス流量:300sccm、チャンバー内圧力:0.7Pa、使用電源:AC電源、印加電力:6kWとし、400nmの膜厚で成膜した。

【0189】

次に、絶縁層116と同一の装置を用い、大気解放を行わずに連続して金属酸化物層118を成膜する。これにより、絶縁層116と金属酸化物層118界面への水分吸着を抑制できる。

【0190】

金属酸化物層118の成膜方法は、使用ターゲット:Pure−Al、基板温度:150℃、成膜雰囲気:100%O2、O2ガス流量:300sccm、チャンバー内圧力:0.7Pa、使用電源:AC電源、印加電力:30kWとし、50nmの膜厚で酸化アルミニウム膜を成膜した。

【0191】

絶縁層116上に成膜した金属酸化物層118の断面を、走査型透過電子顕微鏡(STEM:Scanning Transmission Electron Microscope)を用いて観察した結果を図8に示す。図8より、金属酸化物層118は、第1の金属酸化物層118aと第2の金属酸化物層118bの連続した2層構造となっている。これは、金属酸化物層118は高い印加電力で成膜されるが、その初期段階において、金属酸化物層118を構成する主要元素(ここではアルミニウムおよび酸素。)が、下に形成された層(ここでは、酸化珪素膜。)の元素を弾き出して金属酸化物層118中に混合(ミキシング効果とも言われる。)し、金属酸化物層118の結晶化を阻害することで、アモルファス構造を有する第1の金属酸化物層118aが形成される。そして、成膜が進むにつれてミキシング効果が減少し、多結晶構造を有する第2の金属酸化物層118bが形成される。

【0192】

なお、酸化アルミニウム膜の成膜では、チャンバーの雰囲気、圧力および印加電力などを調整することにより、上述の2層構造における各層(第1の金属酸化物層118aおよび第2の金属酸化物層118b)の膜厚を人為的に調整することが可能である。

【0193】

なお、本実施例では、酸化アルミニウムを用いて第1の金属酸化物層118aおよび第2の金属酸化物層118bの連続した積層の成膜についての説明を行ったが、勿論、他の金属酸化物についても、上述のように成膜における各種パラメータを調整することにより、連続した積層構造を形成してもよい。

【0194】

そして、第1の金属酸化物層118aおよび第2の金属酸化物層118bの膜質調査を行うため、各々の層の3箇所についてXRR測定にて膜密度調査を行った。その結果、第1の金属酸化物層118aでは、3.04g/cm3、3.02g/cm3および3.02g/cm3の膜密度が得られ、第2の金属酸化物層118bでは、3.80g/cm3、3.78g/cm3および3.76g/cm3の膜密度が得られた。当該測定結果より、第1の金属酸化物層118aはアモルファス構造を有する酸化アルミニウムであり、第2の金属酸化物層118bは多結晶構造を有する酸化アルミニウムであることが示唆される。

【0195】

なお、本実施例では、第1の金属酸化物層118aおよび第2の金属酸化物層118bとして酸化アルミニウムを用いた場合について記載したが、他の金属酸化物を用いた場合においても、XRRにより膜密度を測定し、当該測定結果を文献値などと比較することにより、層の状態(アモルファス状態であるか、多結晶状態であるか、など。)を調査することができる。

【0196】

本実施例は、他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

【0197】

100 基板

102 下地絶縁層

106 半導体層

106a 高抵抗領域

106b 低抵抗領域

107 絶縁層

108 ゲート絶縁層

110 ゲート電極

112 側壁絶縁層

114 一対の電極

116 絶縁層

118 金属酸化物層

118a 第1の金属酸化物層

118b 第2の金属酸化物層

120 配線

130 不純物イオン

150 トランジスタ

602 絶縁層

651 トランジスタ

652 トランジスタ

653 トランジスタ

701 筐体

702 筐体

703a 第1の表示部

703b 第2の表示部

704 選択ボタン

705 キーボード

721 筐体

722 表示部

723 スタンド

724 リモコン

731 筐体

732 操作スイッチ

733 バッテリー

【技術分野】

【0001】

半導体装置、および半導体装置の作製方法に関する。

【0002】

なお、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

半導体装置に用いられる薄膜トランジスタ(以下、単に「トランジスタ」と記載することもある。)は、外部からの水分侵入により生じる配線部分の腐食や薄膜トランジスタの電気特性変動を防止するため、薄膜トランジスタ上には酸化珪素膜や窒化珪素膜などの絶縁層が設けられている(例えば、特許文献1参照。)。

【0004】

なお、本明細書中の「水分」とは、水、水蒸気、水分子、水素分子および水素原子を含む総称として用いる。なお、例えば「水分の透過性が低い」という表現が用いられている場合、これは「水、水蒸気、水分子、水素分子および水素原子のうちの1つ以上について透過性が低い」と解釈する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−59939号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

薄膜トランジスタへの水分侵入の防止効果を更に高める方法の1つとして、水分の透過性が低い、結晶性を有する金属酸化物層を、絶縁層に接して位置する構造とする方法がある。

【0007】

しかし、結晶性を有する金属酸化物層は、各結晶粒の界面(グレインバウンダリーとも言われる。)では、結晶格子における原子配列がずれている、若しくは連続性が損なわれているため、結晶粒部分に比べて比較的広い格子間隔となっている。このため、結晶粒部分については水分の透過性が非常に低いものの、結晶粒界部分は結晶粒部分と比較して水分が比較的透過しやすい状態にある。

【0008】

このような問題に鑑み、本明細書の一形態では、水分による電気特性劣化が抑制された半導体装置を提供することを目的の1つとする。また、当該半導体装置の作製方法を提供することを目的の1つとする。

【課題を解決するための手段】

【0009】

薄膜トランジスタを覆う絶縁層に接して金属酸化物層が位置する構造とし、当該金属酸化物層を、アモルファス構造(非晶質構造とも言う。)を有する第1の金属酸化物層および多結晶(ポリクリスタルとも言う。)構造を有する第2の金属酸化物層を含む構造とする。

【0010】

アモルファス構造を有する第1の金属酸化物層は、結晶状態の金属酸化物層と比較して水分が通りやすいものの、結晶粒界が存在しないため結晶粒界部分からの水分の侵入が無く、また、格子間に水分をトラップしやすいという特性を有している。

【0011】

また、多結晶構造を有する第2の金属酸化物層は、結晶粒界部分については結晶部分と比較して幾分水分が侵入しやすいものの、結晶部分については緻密な構造を有しており、水分の透過性が非常に低いという特性を有している。

【0012】

このため、金属酸化物層を、アモルファス構造を有する第1の金属酸化物層および多結晶構造を有する第2の金属酸化物層を含む構造とすることにより、第2の金属酸化物層で水分の侵入を防止し、また、第2の金属酸化物層の結晶粒界部分を通して侵入した水分についても、第1の金属酸化物層により侵入を防止する(または膜中に水分を取り込む)ことができる。そして、当該金属酸化物層を絶縁層に接して形成することで、更に水分の侵入を防止できる。したがって、薄膜トランジスタへの水分の侵入を効果的に防止することができる。

【0013】

すなわち、本発明の一態様は、半導体層、ゲート絶縁層、ゲート電極および、ソース電極及びドレイン電極として機能する一対の電極を有するトランジスタと、トランジスタ上の絶縁層と、絶縁層と接する金属酸化物層を有する構造であり、金属酸化物層は、アモルファス構造を有する第1の金属酸化物層と多結晶構造を有する第2の金属酸化物層を少なくとも含む構造であることを特徴とする半導体装置である。

【0014】

本発明の一態様に記載の構造とすることで、絶縁層と、第1の金属酸化物層および第2の金属酸化物層を含む金属酸化物層により、薄膜トランジスタへの水分の侵入を効果的に防止することができる。

【0015】

なお、トランジスタ上の絶縁層、第1の金属酸化物層および第2の金属酸化物層の構成については、以下に示す2通りの構造とすることが好ましい。

【0016】

1つめは、トランジスタ上に絶縁層が位置し、絶縁層上に第1の金属酸化物層が位置し、第1の金属酸化物層上に第2の金属酸化物層が位置する構造である。当該構造では、外部から侵入する水分は、まず第2の金属酸化物層によりブロックされる。次に、第2の金属酸化物層の結晶粒界部分などの比較的水分が透過しやすい部分を通して侵入する水分は、第1の金属酸化物層によりブロックされる、または第1の金属酸化物層中にトラップされる。そして、第1の金属酸化物層を透過して侵入する極微量の水分についても、絶縁層によりブロックされる。したがって、第2の金属酸化物層の外部に存在する水分がトランジスタに到達することを効果的に防止できる。

【0017】

2つめは、トランジスタ上に第1の金属酸化物層が位置し、第1の金属酸化物層上に第2の金属酸化物層が位置し、第2の金属酸化物層上に絶縁層が位置する構造である。当該構造では、外部から侵入する水分に加え、仮に絶縁層を成膜する際に絶縁層中に水分が取り込まれる、或いは第2の金属酸化物層と絶縁層の界面に水分が吸着された場合においても、トランジスタと絶縁層の間には第1の金属酸化物層および第2の金属酸化物層が位置する構造であるため、絶縁層中に取り込まれた水分や第2の金属酸化物層と絶縁層の界面に吸着された水分がトランジスタに到達することを効果的に防止できる。

【0018】

また、半導体層を、酸化物半導体材料を含んでなる膜とすることにより、高い移動度を有するトランジスタとすることができる。

【0019】

また、本発明の一態様は、半導体層、ゲート絶縁層、ゲート電極およびソース電極及びドレイン電極として機能する一対の電極を有するトランジスタを形成し、トランジスタ上に絶縁層を形成し、絶縁層上にアモルファス構造を有する第1の金属酸化物層を形成し、第1の金属酸化物層上に多結晶構造を有する第2の金属酸化物層を形成する工程を有することを特徴とする半導体装置の作製方法である。

【0020】

本発明の一態様に記載の作製方法を用いることで、トランジスタへの水分の侵入防止効果の高い半導体装置を作製することができる。

【0021】

また、本発明の一態様は、半導体層、ゲート絶縁層、ゲート電極およびソース電極及びドレイン電極として機能する一対の電極を有するトランジスタを形成し、トランジスタ上にアモルファス構造を有する第1の金属酸化物層を形成し、第1の金属酸化物層上に多結晶構造を有する第2の金属酸化物層を形成し、第2の金属酸化物層上に絶縁層を形成する工程を有することを特徴とする半導体装置の作製方法である。

【0022】

本発明の一態様に記載の作製方法を用いることで、外部から侵入する水分に加え、絶縁層中に取り込まれた水分、および、第2の金属酸化物層と絶縁層の界面に吸着した(或いは取り込まれた)水分の侵入防止効果の高い半導体装置を作製することができる。

【0023】

なお、第1の金属酸化物層と前記第2の金属酸化物層を、同一装置内にて連続して成膜することにより、第1の金属酸化物層および第2の金属酸化物層の層中への水分混入および第1の金属酸化物層と第2の金属酸化物層の界面への水分の付着を抑制することができるため、好ましいと言える。

【0024】

また、第1の金属酸化物層と前記第2の金属酸化物層を同一のターゲットを用いて成膜することにより、基板を異なる成膜室に移動させることによる製造タクトの増加を抑制できる。また、金属酸化物層を成膜するのに必要なターゲットが1種類のみとなるため、製造コストの増加を抑制できる。

【0025】

また、半導体層として、酸化物半導体材料を含んでなる膜を形成することにより、高い移動度を有するトランジスタを作製することができる。

【発明の効果】

【0026】

金属酸化物層を、アモルファス構造を有する第1の金属酸化物層および多結晶構造を有する第2の金属酸化物層を含む構造とすることにより、第2の金属酸化物層で水分の侵入を防止し、また、第2の金属酸化物層の結晶粒界部分を通して侵入した水分についても、第1の金属酸化物層により侵入を防止する(または膜中に水分を取り込む)ことができる。そして、当該金属酸化物層を絶縁層に接して形成することで、更に水分の侵入を防止できる。したがって、水分による電気特性劣化が抑制された半導体装置を提供できる。また、当該半導体装置の作製方法を提供できる。

【図面の簡単な説明】

【0027】

【図1】本発明の一態様に係る半導体装置の構成を説明する図。

【図2】本発明の一態様に係る半導体装置の作製方法を説明する図。

【図3】本発明の一態様に係る半導体装置の作製方法を説明する図。

【図4】本発明の一態様に係る半導体装置の作製方法を説明する図。

【図5】本発明の一態様に係る半導体装置の構成を説明する図。

【図6】本発明の一態様に係る半導体装置の構成を説明する図。

【図7】本発明の一態様に係る半導体装置を用いた電子機器の一例を説明する図。

【図8】本発明の一態様に係る半導体装置の断面状態を説明する図。

【発明を実施するための形態】

【0028】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0029】

以下に説明する実施の形態において、同じものを指す符号は異なる図面間で共通して用いる場合がある。なお、図面において示す構成要素、すなわち層や領域等の厚さ幅、相対的な位置関係等は、実施の形態において説明する上で明確性のために誇張して示される場合がある。

【0030】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0031】

また、本明細書等において「電極」や「配線」という用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」という用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

【0032】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。

【0033】

また、本明細書等において、平均面粗さ(Ra)とは、JIS B 0601:2001(ISO4287:1997)で定義されている算術平均粗さ(Ra)を、曲面に対して適用できるよう三次元に拡張したものであり、基準面から指定面までの偏差の絶対値を平均した値で表現でき、以下の数式(1)にて定義される。

【0034】

【数1】

【0035】

ここで、指定面とは、粗さ計測の対象となる面であり、座標(x1,y1,f(x1,y1)),(x1,y2,f(x1,y2)),(x2,y1,f(x2,y1)),(x2,y2,f(x2,y2))の4点で表される四角形の領域とし、指定面をxy平面に投影した長方形の面積をS0、基準面の高さ(指定面の平均の高さ)をZ0とする。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて測定可能である。

【0036】

(実施の形態1)

本実施の形態は、本発明の一態様であるトランジスタを有する半導体装置およびその作製方法について、図1乃至図5を用いて説明する。

【0037】

<本実施の形態における半導体装置の構成>

図1は、コプラナー型であるトップゲート・トップコンタクト構造のトランジスタを有する半導体装置の上面図および断面図である。図1(A)はトランジスタの上面図であり、図1(B)は図1(A)の一点鎖線A−B部分に対応する断面である。なお、図1(A)はトランジスタの構造を分かり易くするため、一部の構成要素を省略している。

【0038】

図1(B)に示すように、トランジスタ150は、基板100と、基板100上に設けられた下地絶縁層102と、下地絶縁層102上に設けられた高抵抗領域106aおよび低抵抗領域106bを有する半導体層106と、半導体層106上に設けられたゲート絶縁層108と、ゲート絶縁層108を介して半導体層106と重畳して設けられたゲート電極110と、ゲート電極110の側面と接して設けられた側壁絶縁層112と、半導体層106と接して設けられた一対の電極114と、を有している。また、トランジスタ150上に、ゲート電極110、側壁絶縁層112および一対の電極114を覆って設けられた絶縁層116と、絶縁層116上に設けられた、第1の金属酸化物層118aおよび第2の金属酸化物層118bを有する金属酸化物層118と、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに設けられた開口部を介して一対の電極114と電気的に接続された配線120と、を有している。

【0039】

本実施の形態の構造は、トランジスタ150のチャネル領域が形成される半導体層106上に、絶縁層116および金属酸化物層118が位置し、金属酸化物層118が第1の金属酸化物層118aおよび第2の金属酸化物層118bの積層構造であることが、構造的な特徴である。

【0040】

絶縁層116は、絶縁層116より上に形成された導電層(本実施の形態における配線120。)と絶縁層116より下に形成された導電層(本実施の形態におけるゲート電極110および一対の電極114。)の間で寄生容量が極力生じないように、比誘電率の低い絶縁材料で構成される。なお、当該絶縁層を無機材料で形成することにより、外部から半導体層106に侵入する水分に対して高いバリア性を具備できる。

【0041】

第1の金属酸化物層118aは、アモルファス構造を有する金属酸化物層を用いる。アモルファス構造を有する金属酸化物層は結晶粒界が存在せず、また、結晶状態の金属酸化物層と比較して格子間隔が広いため、格子間に水分をトラップしやすいという特性を有している。

【0042】

第2の金属酸化物層118bは、多結晶構造を有する金属酸化物層を用いる。多結晶構造を有する金属酸化物層は、結晶粒界部分を除く結晶部分については緻密な構造を有しており、水分の透過性が非常に低い、という特性を有している。

【0043】

したがって、半導体装置を上述の構造とすることにより、外部からトランジスタ150への水分の侵入を効果的に防止することができるため、本実施の形態の構造を有する半導体装置は、外部からの水分の侵入に起因した電気的特性の変動を抑制することができる。

【0044】

なお、図1に示すトランジスタは、ゲート電極110をマスクとして用い、自己整合的に半導体層106の低抵抗領域106b(半導体層106のうち、ソース電極やドレイン電極として機能する一対の電極114と接続される領域。ソース領域やドレイン領域とも表現できる。)および高抵抗領域106a(半導体層106のうち、チャネル部が形成される領域を一部に含む領域。チャネル形成領域などとも表現できる。)を形成することができる。そのため、微細なトランジスタを得ることができる。加えて、フォトリソグラフィ工程などによって高抵抗領域106aおよび低抵抗領域106bを形成する場合と比較して、コストの削減や歩留まりの向上が可能となる。また、低抵抗領域106bとゲート電極110の重畳部分がほとんど無いため、重畳部分での寄生容量がほとんど(或いは全く)生じず、トランジスタの高速動作が可能となる。

【0045】

また、図1に示すトランジスタは、トランジスタがオン状態のときには、低抵抗領域106bを介して、一対の電極114の一方から高抵抗領域106aに電流が流れることになる。低抵抗領域106bを介することで、チャネル長の小さい微細なトランジスタにおいてもホットキャリア劣化などの劣化を抑制でき、信頼性を高めることができる。

【0046】

なお、図1に示すトランジスタでは、半導体層106における側壁絶縁層112と重畳する領域を低抵抗領域106bに含めているが、これに限定されない。例えば、半導体層106における側壁絶縁層112と重畳する領域を高抵抗領域106aに含めても構わない。このような構造とすることで、前述のホットキャリア劣化などの劣化をさらに低減することができる。このような構造とする場合、ゲート電極110および側壁絶縁層112をマスクとして用い、自己整合的に半導体層106に低抵抗領域106bおよび高抵抗領域106aを形成すればよい。

【0047】

<本実施の形態における半導体装置の作製方法>

図1に記載されたトランジスタの作製方法を、図2乃至図4を用いて説明する。

【0048】

まず、基板100上に下地絶縁層102を形成する(図2(A)参照。)。

【0049】

基板100としては、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料を用いる。量産する上では、基板100は、第8世代(2160mm×2460mm)、第9世代(2400mm×2800mm、または2450mm×3050mm)、第10世代(2950mm×3400mm)等のマザーガラスを用いることが好ましい。マザーガラスは、処理温度が高く、処理時間が長いと大幅に収縮するため、マザーガラスを使用して量産を行う場合、作製工程の加熱処理は、700℃以下、好ましくは450℃以下、さらに好ましくは350℃以下とすることが望ましい。

【0050】

下地絶縁層102は、PECVD法またはスパッタリング法を用いて50nm以上600nm以下の膜厚で、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜から選ばれた一層またはこれらの積層膜を用いる。下地絶縁層102を形成することにより、後の工程にて形成する半導体層106に、基板100側から不純物が侵入することを抑制できる。なお、下地絶縁層102は必ずしも必要なものではなく、例えば、基板100中の含有不純物量が十分に少ない場合には、下地絶縁層102を設けない構成としてもよい。

【0051】

なお、本明細書中において、酸化窒化シリコンなどの「酸化窒化物」とは、その組成として、窒素よりも酸素の含有量が多いものを示す。また、窒化酸化シリコンなどの「窒化酸化物」とは、その組成として、酸素よりも窒素の含有量が多いものを示す。

【0052】

なお、後の工程にて形成する半導体層106として、酸化物半導体材料を含んでなる層を用いる場合、半導体層106は、酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体層の酸素欠損は、一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。このため、下地絶縁層102として、加熱処理により酸素を放出する絶縁膜を用いることが好ましい。これにより、しきい値電圧がマイナス方向へシフトする要因である、半導体層106の酸素欠損を低減できる。また、下地絶縁層102は、後の工程で形成する半導体層106が結晶成長しやすいように、十分な平坦性を有することが好ましい。

【0053】

上述の「加熱処理により酸素を放出する」とは、TDS(Thermal Desorption Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての酸素の放出量が1.0×1018atoms/cm3以上、好ましくは3.0×1020atoms/cm3以上であることをいう。

【0054】

ここで、TDS分析にて、酸素原子に換算しての酸素の放出量の測定方法について、以下に説明する。

【0055】

TDS分析したときの気体の放出量は、スペクトルの積分値に比例する。このため、測定したスペクトルの積分値と、標準試料の基準値に対する比とにより、気体の放出量を計算することができる。標準試料の基準値とは、所定の原子を含む試料の、スペクトルの積分値に対する原子の密度の割合である。

【0056】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量(NO2)は、以下の数式2で求めることができる。ここで、TDS分析で得られる質量数32で検出されるスペクトルの全てが酸素分子由来と仮定する。質量数32のものとしてほかにCH3OHがあるが、存在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量数17の酸素原子又は質量数18の酸素原子を含む酸素分子についても、自然界における存在比率が極微量であるため考慮しない。

【0057】

【数2】

【0058】

NH2は、標準試料から脱離した水素分子を密度で換算した値である。SH2は、標準試料をTDS分析したときのスペクトルの積分値である。ここで、標準試料の基準値を、NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのスペクトルの積分値である。αは、TDS分析におけるスペクトル強度に影響する係数である。数式2の詳細に関しては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料として1×1016atoms/cm3の水素原子を含むシリコンウェハを用いて測定する。

【0059】

また、TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量についても見積もることができる。

【0060】

なお、NO2は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の2倍となる。

【0061】

上記構成において、加熱処理により酸素を放出する層は、酸素が過剰な酸化シリコン(SiOX(X>2))であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2))とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法により測定した値である。

【0062】

次に、スパッタリング法、蒸着法、PECVD法、PLD法、ALD(Atomic Layer Deposition)法またはMBE(Molecular Beam Epitaxy)法などを用いて半導体層106を成膜する(図2(B)参照。)。半導体層106としては、非晶質シリコン膜、多結晶シリコン膜、微結晶シリコン膜(マイクロクリスタル、セミアモルファスとも言う。)、単結晶シリコン膜などシリコン膜を用いることができる。また、ガリウム砒素膜やシリコンゲルマニウム膜などの化合物半導体膜を用いることもできる。更に、酸化物半導体材料を含んでなる膜(以下、酸化物半導体層と略記する。)を用いてもよい。近年では、酸化物半導体材料を半導体層として用いたトランジスタの研究、開発が盛んに行われている。この現状を踏まえ、以下では半導体層106に酸化物半導体層を用いる構成についての説明を行う。無論、半導体層106が酸化物半導体層に限定されるものではない。

【0063】

半導体層106は、半導体層106を構成する主要な成分以外に、キャリア供与体となる不純物が極力含まれないように成膜することが好ましい。このため、半導体層106を成膜するための材料(例えば、スパッタ装置に用いるターゲットなど。)および、成膜雰囲気は、キャリア供与体となる不純物が極力含まれない高純度化された材料および雰囲気にて成膜することが好ましい。

【0064】

半導体層106にアルカリ金属またはアルカリ土類金属が含まれると、酸化物半導体と結合することによって、キャリアが生成されることがあり、トランジスタのオフ電流が上昇する原因となる。そのため、半導体層106において、アルカリ金属またはアルカリ土類金属の濃度は、1×1018atoms/cm3以下、好ましくは2×1016atoms/cm3以下とすることが望ましい。

【0065】

また、半導体層106に、水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そのため、半導体層106において、水素濃度は、5×1018atoms/cm3未満、好ましくは1×1018atoms/cm3以下、より好ましくは5×1017atoms/cm3以下、更に好ましくは1×1016atoms/cm3以下とすることが望ましい。なお、上述の半導体層106中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)で測定されるものである。

【0066】

このように、水素濃度が十分に低減され、十分に酸素が供給されることによって、酸素欠損に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体では、キャリア密度が1×1012/cm3未満、望ましくは、1×1011/cm3未満、より望ましくは1.45×1010/cm3未満とすることができる。例えば、室温(25℃)でのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値。)は100zA(1zA(ゼプトアンペア)は1×10−21A)以下、望ましくは10zA以下となる。このように、水素などの不純物が十分に除去され、十分な酸素が供給された酸化物半導体を半導体層106として用いることで、極めて優れたオフ電流特性のトランジスタを得ることができる。

【0067】

なお、オフ電流とは、広義にトランジスタがオフ状態のときに流れるドレイン電流をいう。トランジスタのオフ状態とは、nチャネル型トランジスタにおいて、ゲート電圧がしきい値電圧より低い状態をいう。または、pチャネル型トランジスタにおいて、ゲート電圧がしきい値電圧より高い状態をいう。ドレイン電流とは、トランジスタのソース−ドレイン間の電流をいう。また、ゲート電圧とは、ソース電位を基準としたときのゲート電位との電位差をいう。

【0068】

オフ電流は、ノーマリーオフ型のトランジスタにおいて、ゲート電圧が0Vのときに流れるドレイン電流を指すことがある。ノーマリーオフ型のトランジスタとは、nチャネル型のトランジスタにおいて、しきい値電圧が0Vより大きいものをいう。または、pチャネル型のトランジスタにおいて、しきい値電圧が0Vより小さいものをいう。

【0069】

半導体層106中の水素濃度は、二次イオン質量分析(SIMS:Secondary Ion Mass Spectrometry)において、5×1019cm−3未満、好ましくは5×1018cm−3以下、より好ましくは1×1018cm−3以下、さらに好ましくは5×1017cm−3以下とする。また、アルカリ金属濃度は、二次イオン質量分析において、ナトリウム濃度が5×1016cm−3以下、好ましくは1×1016cm−3以下、さらに好ましくは1×1015cm−3以下とする。同様に、リチウム濃度は、5×1015cm−3以下、好ましくは1×1015cm−3以下とする。同様に、カリウム濃度は、5×1015cm−3以下、好ましくは1×1015cm−3以下とする。

【0070】

半導体層106は単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

【0071】

好ましくは、半導体層106は、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

【0072】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0073】

なお、CAAC−OS膜を半導体層として用いたトランジスタは、表面の平坦性を高めることにより、アモルファス状態の酸化物半導体膜を半導体層として用いたトランジスタ以上の移動度を得ることができる。なお、表面の平坦性を高めるためには、平坦な表面上に半導体層を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。また、平均面粗さ(Ra)が0に近いほど好ましい。本実施の形態においては、下地絶縁層102の表面、または、半導体層106の表面を、上述の平坦度とすればよい。

【0074】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0075】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体層の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0076】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0077】

半導体層106(少なくとも高抵抗領域106a。)としてCAAC−OS膜を用いたトランジスタは、トランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

【0078】

なお、酸化物半導体膜を構成する酸素の一部は窒素で置換されてもよい。

【0079】

半導体層106は、スパッタリング法、MBE法、パルスレーザ堆積法、ALD法等を適宜用いることができる。当該実施の形態では、半導体層106は、スパッタリングターゲット表面に対し、概垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜すればよい。

【0080】

半導体層106の膜厚は、1nm以上100nm以下、好ましくは3nm以上40nm以下、更に好ましくは5nm以上20nm以下とすればよい。特に、チャネル長が30nm以下のトランジスタにおいては、半導体層106の厚さを5nm程度とすることで、短チャネル効果を抑制でき、安定な電気的特性を得ることができる。

【0081】

半導体層106をCAAC−OS膜とするには、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa−b面から劈開し、a−b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、CAAC−OS膜を成膜することができる。

【0082】

また、CAAC−OS膜を成膜するために、以下の条件を適用することが好ましい。

【0083】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度(水素、水、二酸化炭素および窒素など)を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が−80℃以下、好ましくは−100℃以下である成膜ガスを用いる。

【0084】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を100℃以上740℃以下、好ましくは200℃以上500℃以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。

【0085】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

【0086】

スパッタリング用ターゲットの一例として、In−Ga−Zn−O化合物ターゲットについて以下に示す。

【0087】

InOX粉末、GaOY粉末およびZnOZ粉末を所定のmol数で混合し、加圧処理後、1000℃以上1500℃以下の温度で加熱処理をすることで多結晶であるIn−Ga−Zn−O化合物ターゲットとする。なお、X、YおよびZは任意の正数である。ここで、所定のmol数比は、例えば、InOX粉末、GaOY粉末およびZnOZ粉末が、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3または3:1:2である。なお、粉末の種類、およびその混合するmol数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。

【0088】

なお、半導体層106の成膜を行う前に、成膜室の加熱および排気を行って、成膜室中の水分などの不純物を除去しておくことが好ましい。特に成膜室の内壁に吸着して存在するこれらの不純物を除去することが重要である。ここで、加熱処理は、例えば、100℃以上450℃以下で行えばよい。また、処理室の排気は、ドライポンプなどの粗引きポンプと、スパッタイオンポンプ、ターボ分子ポンプおよびクライオポンプなどの高真空ポンプとを適宜組み合わせて行うとよい。ターボ分子ポンプは大きいサイズの分子の排気が優れる一方、水分や水素の排気能力が低い。さらに、水分の排気能力の高いクライオポンプまたは水素の排気能力の高いスパッタイオンポンプを組み合わせることが有効となる。また、このとき、不活性ガスを導入しながら不純物の除去を行うと、排気するだけでは脱離しにくい水分などの脱離速度をさらに大きくすることができる。このような処理を行って酸化物半導体の成膜前に成膜室の不純物を除去することにより、半導体層106への水素、水分、水酸基、水素化物などの混入を抑制することができる。

【0089】

半導体層106の成膜に用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。また、スタビライザーとしてチタン(Ti)を有することが好ましい。また、スタビライザーとしてジルコニウム(Zr)を有することが好ましい。

【0090】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0091】

また、半導体層106は、トランジスタのオフ電流を低減するため、バンドギャップが2.5eV以上、好ましくは2.8eV以上、さらに好ましくは3.0eV以上の材料を用いることが好ましい。

【0092】

トランジスタのオフ抵抗(トランジスタがオフ状態の時における、ソースとドレイン間の抵抗をいう。)は、チャネルが形成される半導体層における熱的に励起するキャリアの濃度に反比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、シリコンの場合にはバンドギャップが1.1eVであるため、室温(300K)での熱励起キャリアの濃度は1×1011cm−3程度である。

【0093】

一方、例えばバンドギャップが3.2eVの半導体(酸化物半導体を想定。)の場合では熱励起キャリアの濃度は1×10−7cm−3程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2eVの半導体の抵抗率は、シリコンより18桁も大きい。

【0094】

このようなバンドギャップの広い酸化物半導体を半導体層106に適用したトランジスタ(OSトランジスタ)は、極めて低いオフ電流を実現できる。

【0095】

半導体層106として、例えば、単元系金属の酸化物である酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0096】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0097】

また、半導体層106として、InMO3(ZnO)m(m>0、且つ、mは整数でない。)で表記される酸化物を用いてもよい。なお、Mは、Ga、Fe、MnおよびCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In2SnO5(ZnO)n(n>0、且つ、nは整数。)で表記される材料を用いてもよい。

【0098】

例えば、半導体層106としてIn:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子比のIn−Ga−Zn系酸化物やその組成の近傍のIn−Ga−Zn系酸化物を用いることができる。また、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子比のIn−Sn−Zn系酸化物やその組成の近傍のIn−Sn−Zn系酸化物を用いてもよい。

【0099】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値電圧、ばらつき等。)に応じて適切な組成の材料を用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

【0100】

例えば、In−Sn−Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn系酸化物でも、バルク内欠陥密度を下げることにより移動度を上げることができる。

【0101】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物の組成の近傍であるとは、a、b、cが、(a−A)2+(b−B)2+(c−C)2≦r2を満たすことをいう。rとしては、例えば、0.05とすればよい。他の酸化物でも同様である。

【0102】

半導体層106としてIn−Ga−Zn系酸化物をスパッタリング法で成膜する場合、好ましくは、原子数比がIn:Ga:Zn=1:1:1、4:2:3、3:1:2、1:1:2、1:3:2、2:1:3、または3:1:4で示されるIn−Ga−Zn−Oターゲットを用いる。前述の原子数比を有するIn−Ga−Zn−Oターゲットを用いて半導体層106を成膜することで、多結晶膜またはCAAC−OS膜が形成されやすくなる。

【0103】

また、半導体層106としてIn−Sn−Zn系酸化物をスパッタリング法で成膜する場合、好ましくは、原子数比がIn:Sn:Zn=1:1:1、2:1:3、1:2:2、または20:45:35で示されるIn−Sn−Zn−Oターゲットを用いる。前述の原子数比を有するIn−Sn−Zn−Oターゲットを用いて半導体層106を成膜することで、多結晶膜またはCAAC−OS膜が形成されやすくなる。

【0104】

また、半導体層106としてIn−Zn系酸化物をスパッタリング法で成膜する場合、好ましくは、原子数比で、In:Zn=50:1〜1:2(mol比に換算するとIn2O3:ZnO=25:1〜1:4)、好ましくはIn:Zn=20:1〜1:1(mol比に換算するとIn2O3:ZnO=10:1〜1:2)、さらに好ましくはIn:Zn=15:1〜1.5:1(mol比に換算するとIn2O3:ZnO=15:2〜3:4)で示されるIn−Zn−Oターゲットを用いる。前述の原子数比を有するIn−Zn−Oターゲットを用いて半導体層106を成膜することで、多結晶膜またはCAAC−OS膜が形成されやすくなる。

【0105】

なお、上述では半導体層106の成膜に用いるターゲット中の金属元素の原子数比は整数にて記載されているが、半導体層106中に含まれる金属元素の原子数比を整数とする場合においては、ターゲット中の金属元素の原子数比は上述の値から若干前後してもよい。例えば、半導体層106として、In:Ga:Zn=1:1:1の半導体層106を形成する場合において、In2O3:Ga2O3:ZnO=1+α:1+β:1+γ[mol比]の組成を有するターゲットを用いればよい。α、βおよびγの値は成膜条件により変動するが、概ね−0.5以上0.5以下の値となる。

【0106】

なお、半導体層106は、成膜時に酸素が多く含まれるような条件(例えば、酸素100%の雰囲気下でスパッタリング法により成膜を行うなど。)で成膜して、酸素を多く含む(好ましくは半導体層の化学量論的組成に対し、酸素の含有量が過剰である領域が含まれている)層とすることが好ましい。

【0107】

成膜の雰囲気は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または、希ガスと酸素の混合雰囲気下などとすればよい。ここで、成膜時に希ガスより酸素の体積比を大きくすることにより、半導体層106に酸素が多く取り込まれるため、半導体層106中の酸素欠損を低減することができる。また、半導体層106への水分の混入を防ぐために、水分が十分に除去された高純度ガスを用いた雰囲気とすることが望ましい。

【0108】

なお、半導体層106としてCAAC−OS膜を用いる場合、CAAC−OS膜を複数の酸化物半導体膜が積層された構造としてもよい。例えば、半導体層106を、第1の酸化物半導体膜、第2の酸化物半導体膜および第3の酸化物半導体膜の積層として、各々を異なる組成としてもよい。例えば、第1の酸化物半導体膜および第3の酸化物半導体膜に三元系金属の酸化物を用い、第2の酸化物半導体膜に二元系金属の酸化物を用いる、または、第1の酸化物半導体膜および第3の酸化物半導体膜に二元系金属の酸化物を用い、第2の酸化物半導体膜に三元系金属の酸化物を用いる。

【0109】

また、第1の酸化物半導体膜、第2の酸化物半導体膜および第3の酸化物半導体膜の構成元素を同一とし、組成を異ならせてもよい。例えば、第1の酸化物半導体膜および第3の酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1とし、第2の酸化物半導体膜の原子数比をIn:Ga:Zn=3:1:2としてもよい。また、第1の酸化物半導体膜および第3の酸化物半導体膜の原子数比をIn:Ga:Zn=1:3:2とし、第2の酸化物半導体膜の原子数比をIn:Ga:Zn=3:1:2としてもよい。

【0110】

この時、第2の酸化物半導体膜はInとGaの含有率をIn>Gaとするとよい。また第1の酸化物半導体膜および第3の酸化物半導体膜のInとGaの含有率をIn≦Gaとするとよい。

【0111】

酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることによりs軌道のオーバーラップが多くなる傾向があるため、In>Gaの組成となる酸化物はIn≦Gaの組成となる酸化物と比較して高い移動度を備える。また、GaはInと比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、In≦Gaの組成となる酸化物はIn>Gaの組成となる酸化物と比較して安定した特性を備える。

【0112】

なお、酸化物半導体膜に接して酸化物半導体膜とは異なる膜(図中では、下地絶縁層102や絶縁層107など。)を形成する際に、酸化物半導体膜に接して形成される膜から酸化物半導体膜中に不純物が拡散する恐れがある。たとえば、下地絶縁層102や絶縁層107中に含まれるシリコンやカーボンなどが酸化物半導体膜中に拡散すると、トランジスタの電気特性に悪影響を及ぼす可能性がある。

【0113】

しかしながら、上述のように酸化物半導体膜の積層構造とし、高い移動度を備える酸化物半導体膜(つまり、In>Gaの組成となる酸化物半導体膜。本実施の形態では第2の酸化物半導体膜に相当する。)に接して、当該高い移動度を備える酸化物半導体膜よりも酸素欠損が少なく安定した特性を備える酸化物半導体膜(つまり、In≦Gaの組成となる酸化物半導体膜。本実施の形態では第1の酸化物半導体膜および第3の酸化物半導体膜に相当する。)を形成し、酸化物半導体膜の積層構造に接する膜(図中では、下地絶縁層102や絶縁層107など。)から高い移動度を備える酸化物半導体膜を離すことにより、不純物拡散に起因したトランジスタの電気特性(例えば、移動度の

低下など。)の悪影響を抑制することができる。したがって、トランジスタの移動度および信頼性を高めることが可能となる。

【0114】

また、半導体層106を成膜後、半導体層106に取り込まれた水分を除去(脱水化または脱水素化)するための加熱処理を行ってもよい。加熱処理を行うことによって、半導体層106中に含まれる水分をさらに除去することができる。加熱処理の温度は、不活性ガス雰囲気下、250℃以上700℃以下、好ましくは450℃以上600℃以下、または基板の歪み点未満とする。不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水分、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とすればよい。

【0115】

当該加熱処理は、例えば、抵抗発熱体などを用いた電気炉に基板を導入し、窒素雰囲気下、450℃、1時間の条件で行うことができる。

【0116】

また、加熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、LRTA(Lamp Rapid Thermal Anneal)装置、GRTA(Gas Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。なお、加熱処理装置としてGRTA装置を用いる場合には、その熱処理時間が短いため、650℃〜700℃の高温に加熱した不活性ガス中で基板を加熱してもよい。

【0117】

なお、上述の加熱処理には水分を除去する効果があるため、当該加熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該加熱処理を行うタイミングは、半導体層106成膜直後に限らず、例えば、半導体層106を島状に加工した後など、別のタイミングで行うことも可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

【0118】

また、上記の加熱処理で半導体層106を加熱した後、同じ炉にて半導体層106に酸素を加える(加酸素化とも言う。)ための加熱処理を行ってもよい。当該加熱処理は、加熱処理装置に高純度の酸素ガス、高純度のN2Oガス、または超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で−55℃)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)を導入し、200℃以上基板の歪み点未満で加熱処理を行えばよい。好ましくは、250℃以上450℃以下加熱処理を行えばよい。特にこれらのガスには、水分、水素などが含まれないことが好ましい。また、同じ炉に導入する酸素ガスまたはN2ガスの純度を、6N以上好ましくは7N以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。この工程により、脱水化または脱水素化処理により生じた半導体層106中の酸素欠損を補填することができる。

【0119】

なお、上述の加熱処理には脱水化処理または脱水素化処理により半導体層106中に生じた酸素欠損を補填する効果があるため、当該加熱処理を、加酸素化処理などと呼ぶこともできる。当該加熱処理についても、脱水化処理または脱水素化処理と同様に、半導体層106を島状に加工した後など、別のタイミングで行うことも可能であり、また、一回に限らず複数回行っても良い。

【0120】

半導体層106に、上述の加熱処理を行うことで、膜中の不純物準位を極めて小さくすることが可能となる。その結果、トランジスタの電界効果移動度を理想的な電界効果移動度近くまで高めることが可能となる。

【0121】

次に、半導体層106に対してフォトリソグラフィ工程などを行い加工して、半導体層106を島状に加工する(図2(C)参照。)。

【0122】

次に、半導体層106上に、絶縁層107と導電層を、スパッタリング法、蒸着法、PECVD法、PLD法、ALD法またはMBE法などを用いて順に成膜し、導電層に対してフォトリソグラフィ工程などを行い加工して、ゲート電極110を形成する(図2(D)参照。)。

【0123】

絶縁層107としては、下地絶縁層102と同様の材料および方法を用いることができる。なお、絶縁層107は、下地絶縁層102と同様に、加熱処理により酸素を放出する絶縁層(好ましくは、絶縁層の化学量論的組成に対し、酸素の含有量が過剰である領域が含まれている絶縁層)を用いると好ましい。これにより、半導体層106から絶縁層107への酸素の移動を抑制することができ、かつ、絶縁層107から半導体層106への酸素の供給を行うことができる。

【0124】

ゲート電極110としては、スパッタリング法などにより、アルミニウム、チタン、クロム、コバルト、ニッケル、銅、モリブデン、銀、タンタルおよびタングステン、それらの窒化物、酸化物ならびに合金から一種以上選択し、単層でまたは積層で用いればよい。または、少なくともInおよびZnを含む酸化物または酸化窒化物を用いても構わない。例えば、In−Ga−Zn−O−N系材料などを用いればよい。

【0125】

次に、イオンドーピング法やイオン注入法により、半導体層106の抵抗値を低減する機能を有する不純物イオン130を、絶縁層107を介して半導体層106に添加する。この際、ゲート電極110がマスクとして機能するため、高抵抗領域106aおよび低抵抗領域106bを有する半導体層106が自己整合的に形成される(図3(A)参照。)。なお、イオン注入法は、必要なイオン(本実施の形態では、不純物イオン130。)のみを取り出す質量分離器を用いているため、対象物(本実施の形態では、半導体層106。)に対して不純物イオン130のみを選択的に添加できる。このため、イオンドーピング法を用いて添加した場合と比べて半導体層106中への不純物(例えば水素など)の混入が少なくなるため好ましい。ただし、イオンドーピング法を除外するものではない。

【0126】

なお、絶縁層107を介して不純物イオン130を添加することにより、半導体層106中に不純物イオン130を添加する際に生じるダメージ(例えば半導体層106中での格子欠陥の発生など)を低減することができる。

【0127】

次に、下地絶縁層102と同様の材料および方法で絶縁層を成膜し、当該絶縁層をエッチングすることにより側壁絶縁層112を形成する(図3(B)参照)。側壁絶縁層112は、絶縁層に異方性の高いエッチング工程を行うことで自己整合的に形成することができる。例えば、ドライエッチング法を用いると好ましい。ドライエッチング法に用いるエッチングガスとしては、例えば、トリフルオロメタン、オクタフルオロシクロブタン、テトラフルオロメタンなどのフッ素を含むガスが挙げられる。エッチングガスには、希ガスまたは水素を添加してもよい。ドライエッチング法は、基板に高周波電圧を印加する、反応性イオンエッチング法(RIE法)を用いると好ましい。

【0128】

側壁絶縁層112を形成した後、ゲート電極110および側壁絶縁層112をマスクとして絶縁層107を加工し、ゲート絶縁層108を形成する(図3(C)参照。)。

【0129】

なお、本実施の形態では、ゲート電極110の形成直後の工程において、ゲート電極110をマスクに用いて半導体層106に不純物イオン130の添加を行ったが、側壁絶縁層112の形成後にゲート電極110および側壁絶縁層112をマスクに用いて、半導体層106に不純物イオン130を添加してもよい。こうすることで、側壁絶縁層112と重畳する半導体層106の領域を高抵抗領域106aに含めることができる。

【0130】

次に、半導体層106、ゲート電極110および側壁絶縁層112上に、ゲート電極110と同様の材料および方法で導電膜を成膜し、フォトリソグラフィ工程などによって当該導電膜を加工して、ソース電極及びドレイン電極として機能する一対の電極114を形成する。これにより、トランジスタ150が形成される(図3(D)参照。)。

【0131】

次に、ゲート電極110、側壁絶縁層112および一対の電極114上に、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bを、この順に成膜する(図4(A)参照)。なお、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bの具体的な作製方法については、実施例1にて詳細に記載する。

【0132】

絶縁層116は、PECVD法またはスパッタリング法を用いて、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜または窒化酸化シリコン膜から選ばれた無機材料膜を一層または積層して用いればよい。

【0133】

絶縁層116として、上述の無機材料膜を一層または積層して用いる場合、半導体層106の成膜と同様に、成膜を行う前に成膜室の加熱および排気を行い、また、水分などの不純物が十分に除去された高純度ガスを用いた雰囲気で成膜することで、絶縁層116中への水分の混入を極力抑制することが好ましい。

【0134】

また、絶縁層116は、スピンコート法、印刷法、ディスペンス法またはインクジェット法などを用いて絶縁性を有する材料を塗布し、塗布した材料に応じた硬化処理(例えば、加熱処理や光照射処理など。)を行い形成してもよい。なお、絶縁性を有する材料としては、例えば、アクリル樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリアミドイミド樹脂、エポキシ樹脂等の有機樹脂、有機ポリシロキサンと上述の無機材料などの有機無機混合材料を用いることもできる。

【0135】

絶縁層116は、絶縁層116より上に形成された導電層(本実施の形態における配線120。)と絶縁層116より下に形成された導電層(本実施の形態におけるゲート電極110および一対の電極114。)の間で寄生容量が極力生じないように、比誘電率の低い絶縁材料で構成することが好ましい。また、絶縁層116は、外部からトランジスタ150に侵入する水分に対して高いバリア性を有することが好ましい。これらの観点から考えると、絶縁層116は上述のうち、無機材料膜を一層または積層した構造が好適であるといえる。ただし、上述の有機材料を除外するものではない。絶縁層116として上述のような有機材料を用いる場合は、ポリイミド樹脂等の吸湿性の低い材料を用い、また、有機材料中にシリカゲルや多孔質アルミナなどの乾燥剤を混ぜることが好ましい。

【0136】

なお、絶縁層116は、上述の寄生容量やバリア性、後の工程にて形成する配線120のコンタクト性、および生産性の観点を鑑みると、無機材料膜を用いた場合は200nm以上2000nm以下の膜厚、有機材料膜を用いた場合は200nm以上5000nm以下の膜厚とすることが好ましい。

【0137】

第1の金属酸化物層118aおよび第2の金属酸化物層118bは、スパッタリング法、MBE法、パルスレーザ堆積法、ALD法などを用いて成膜すればよい。

【0138】

第1の金属酸化物層118aは、酸化アルミニウム、酸化ガリウム、酸化チタン、酸化ジルコニウム、酸化ハフニウム、酸化バナジウム、酸化ニオブまたは酸化モリブデンのいずれか一の、アモルファス構造を有する膜を用いればよい。なお、上述の「アモルファス構造を有する」とは、第1の金属酸化物層118aの断面を透過型電子顕微鏡(Transmission Electron Microscope:TEM)にて観察した際に、明確な格子像や格子縞が確認されない領域を有することを表しており、当該領域が全体の60%以上、好ましくは80%である膜を、第1の金属酸化物層118aとして用いることが好ましい。なお、第1の金属酸化物層118aの任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)を観察し、観察箇所において明確な格子像や格子縞が確認されない領域が60%以上ある場合は、これをもって「全体の60%以上」としてもよい。

【0139】

あるいは、X線反射率測定(XRR:X−Ray Reflectometry)を用いて第1の金属酸化物層118a断面の任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)の膜密度を測定し、全ての測定箇所において膜密度が2.9g/cm3以上3.3g/cm3以下であった場合は、これをもって「アモルファス構造を有する」としてもよい。

【0140】

あるいは、透過型電子顕微鏡を用いて第1の金属酸化物層118a断面の任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)の電子線回折像を観察し、全ての観察箇所において幅広く明確でないパターン(ハローパターン、ハローリングまたはハローとも言われる。)が観察された場合は、これをもって「アモルファス構造を有する」としてもよい。

【0141】

「アモルファス構造を有する」の解釈については、上述のいずれか一以上の解釈が第1の金属酸化物層118aに適合していればよく、必ずしも上述の全ての解釈が適合している必要はない。

【0142】

第2の金属酸化物層118bは、酸化アルミニウム、酸化ガリウム、酸化チタン、酸化ジルコニウム、酸化ハフニウム、酸化バナジウム、酸化ニオブまたは酸化モリブデンのいずれか一の、多結晶構造を有する膜を用いればよい。なお、上述の「多結晶構造を有する」とは、第2の金属酸化物層118bの断面を透過型電子顕微鏡(Transmission Electron Microscope:TEM)にて観察した際に、明確な格子像や格子縞が確認される領域を有することを表しており、当該領域が全体の60%以上、好ましくは80%である膜を、第2の金属酸化物層118bとして用いることが好ましい。なお、第2の金属酸化物層118bの任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)を観察し、観察箇所において明確な格子像や格子縞が確認される領域が60%以上ある場合は、これをもって「全体の60%以上」としてもよい。

【0143】

あるいは、X線反射率測定を用いて第2の金属酸化物層118b断面の任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)の膜密度を測定し、全ての測定箇所において膜密度が3.7g/cm3以上4.1g/cm3以下であった場合は、これをもって「多結晶構造を有する」としてもよい。

【0144】

あるいは、透過型電子顕微鏡を用いて第2の金属酸化物層118b断面の任意の数箇所(1箇所以上、好ましくは3箇所以上、より好ましくは5箇所以上。)の電子線回折像を観察し、全ての観察箇所においてデバイシェラーパターン(デバイシェラーリングとも言われる。)が観察されることをもって「多結晶構造を有する」としてもよい。

【0145】

「多結晶構造を有する」の解釈については、上述のいずれか一以上の解釈が第2の金属酸化物層118bに適合していればよく、必ずしも上述の全ての解釈が適合している必要はない。

【0146】

なお、第1の金属酸化物層118aおよび第2の金属酸化物層118bは、同一装置内にて高真空状態を保持したまま連続して成膜することが好ましい。これにより、第1の金属酸化物層118aおよび第2の金属酸化物層118bを成膜する際に、膜中への水分混入および界面への水分の付着を抑制できるため、水分の侵入によるトランジスタの劣化を、より抑制することができる。

【0147】

さらに、第1の金属酸化物層118aおよび第2の金属酸化物層118bに加え、絶縁層116についても同一装置内にて高真空状態を保持したまま連続して成膜することにより、絶縁層116,第1の金属酸化物層118aおよび第2の金属酸化物層118bを成膜する際に、膜中への水分混入および界面への水分の付着を抑制できるため、水分の侵入によるトランジスタの劣化を、更に抑制することができる。

【0148】

なお、第1の金属酸化物層118aおよび第2の金属酸化物層118bを同一装置内にて高真空状態を保持したまま連続して成膜する場合、第1の金属酸化物層118aと第2の金属酸化物層118bを、同一のターゲットを用いて成膜することで、基板を異なる成膜室に移動させることによる製造タクトの増加を抑制できる。また、金属酸化物層を成膜するのに必要なターゲットが1種類のみとなるため、製造コストの増加を抑制できる。

【0149】

また、上述にて説明したとおり、絶縁層116より上に形成された導電層(本実施の形態における配線120。)と絶縁層116より下に形成された導電層(本実施の形態におけるゲート電極110および一対の電極114。)の間で寄生容量が極力生じないように、絶縁層116は比誘電率の低い絶縁材料で構成されているため、例えば、多結晶構造を有する第2の金属酸化物層118bが絶縁層116に接する構造とすると、第2の金属酸化物層118bと絶縁層116の間では比誘電率に大きな開きがあるため、誘電率の界面部分(つまり、絶縁層116と第2の金属酸化物層118bの界面部分。)では、両側からの分極電荷が相殺されずに誘導電荷が発生し、当該電荷が半導体層106中に形成されるチャネル領域に影響を及ぼす場合がある。このため、トランジスタの電気的特性に悪影響を及ぼす(例えば、Vth(しきい値電圧とも言う)にバラツキが生じるなど。)といった問題が生じる場合がある。

【0150】

しかし、本実施の形態のように、絶縁層116と、多結晶構造を有する第2の金属酸化物層118bの間に、アモルファス構造を有する第1の金属酸化物層118aが位置する構造とすることにより、第1の金属酸化物層118aが、絶縁層116と多結晶構造を有する第2の金属酸化物層118bの誘電率差を埋める役目を担い、誘導電荷の発生を抑制することができるため、しきい値電圧バラツキなどの電気的特性変動が少ない、信頼性の高いトランジスタとすることができる。

【0151】

次に、フォトリソグラフィ工程などによって、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに、一対の電極114に到達する開口部を形成した後、第2の金属酸化物層118b上に導電層を形成し、当該導電層をフォトリソグラフィ工程などによって加工し、配線120を形成する(図4(B)参照。)。なお、配線120となる導電層は、ゲート電極110と同様の材料および方法で成膜すればよい。

【0152】

なお、図示しないが、第2の金属酸化物層118bおよび配線120を覆う保護膜を有する構造としても構わない。当該構造とすることで、第2の金属酸化物層118bの表面伝導に起因して生じる微小リーク電流を低減することができ、トランジスタのオフ電流を低減することができる。

【0153】

以上が、本実施の形態の半導体装置の作製方法である。

【0154】

上述の方法により半導体装置を作製することにより、当該半導体装置は、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bの効果により、トランジスタ150への水分の侵入を効果的に抑制することができるため、電気的特性の変動が抑制された半導体装置を提供することができる。

【0155】

(実施の形態2)

本実施の形態では、実施の形態1にて記載した半導体装置とは異なる構成の半導体装置について、その構成および作製方法の一例を、図5を用いて説明する。なお、上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0156】

<本実施の形態における半導体装置の構成および作製方法>

図5は、コプラナー型であるトップゲート・トップコンタクト構造のトランジスタを有する半導体装置の上面図および断面図である。図5(A)はトランジスタの上面図であり、図5(B)は図5(A)の一点鎖線C−D部分に対応する断面である。なお、図5(A)はトランジスタの構造を分かり易くするため、一部の構成要素を省略している。

【0157】

図5に示すトランジスタ150を有する半導体装置は、金属酸化物層118の形成位置が絶縁層116の下にある点で、実施の形態1にて記載した図1に示す半導体装置の構造と異なっている。

【0158】

実施の形態1にて記載したとおり、絶縁層116は、膜中に水分などの不純物が極力取り込まれないように成膜することが好ましい。しかし、成膜時などに意図せず水分などが取り込まれてしまう場合がある。実施の形態1にて記載した構造の半導体装置は、外部からの水分の侵入に対しては高いバリア性を有しているが、上述のように絶縁層116中に水分が取り込まれてしまった場合、第1の金属酸化物層118aおよび第2の金属酸化物層118bによる水分侵入抑制効果はほとんど無いため、電気的特性変動の抑制効果が低減してしまう。

【0159】

しかし、半導体装置の構造を図5(B)に示す構造とすることにより、仮に、絶縁層116に水分などの不純物が取り込まれた場合においても、第1の金属酸化物層118aおよび第2の金属酸化物層118bにより、トランジスタ150への水分の侵入を効果的に抑制することができる。

【0160】

図5に示す半導体装置の作製方法については、実施の形態1と同様に下地絶縁層102、半導体層106、ゲート絶縁層108、ゲート電極110、側壁絶縁層112および一対の電極114を形成してトランジスタ150を形成した後、第1の金属酸化物層118a、第2の金属酸化物層118bおよび絶縁層116を、この順に成膜し、最後に一対の電極114に接続された配線120を形成すればよい。なお、各構成要素の使用材料や形成方法については、実施の形態1を参酌することができる。

【0161】

なお、図5(B)では、第1の金属酸化物層118a上に第2の金属酸化物層118bが位置し、第2の金属酸化物層118b上に絶縁層116が位置する構造であるが、第1の金属酸化物層118aと第2の金属酸化物層118bの位置が逆になっていてもよい。

【0162】

以上が、本実施の形態の半導体装置の構成および作製方法である。

【0163】

上述の方法により作製された半導体装置は、絶縁層116を形成する際に当該層に水分が取り込まれた場合においても、トランジスタ150への水分の侵入を効果的に抑制することができるため、電気的特性の変動が抑制された半導体装置を提供することができる。

【0164】

(実施の形態3)

本実施の形態では、実施の形態1にて記載した半導体装置とは異なる構成の半導体装置について、その構成および作製方法の一例を、図6を用いて説明する。なお、上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0165】

本実施の形態において図6(A)乃至図6(C)に示す半導体装置は、ボトムゲート構造のトランジスタを有する半導体装置の一例である。図6(A)乃至図6(C)は、トランジスタ651、トランジスタ652、トランジスタ653におけるチャネル長方向の断面図である。

【0166】

半導体装置の一形態として図6(A)にボトムゲート・トップコンタクト構造のトランジスタ651を有する半導体装置を示す。トランジスタ651は、逆スタガ型トランジスタとも表現できる。

【0167】

図6(A)に示すように、トランジスタ651は、基板100と、基板100上の下地絶縁層102と、下地絶縁層102上のゲート電極110と、ゲート電極110及び下地絶縁層102上のゲート絶縁層108と、ゲート絶縁層108上の半導体層106と、半導体層106上の一対の電極114を有している。また、トランジスタ651上に、半導体層106および一対の電極114を覆って設けられた絶縁層116と、絶縁層116上に設けられた第1の金属酸化物層118aと、第1の金属酸化物層118a上に設けられた第2の金属酸化物層118bと、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに設けられた開口部を介して一対の電極114と電気的に接続して設けられた配線120と、を有している。

【0168】

当該半導体装置は、上述の実施の形態と比較して構成要素の形成順(例えば、ゲート絶縁層108を成膜する前に、ゲート電極110を形成するなど。)が異なっているが、各々の構成要素の使用材料や形成方法は基本的に実施の形態1と同じであるため、上述の実施の形態に記載された作製方法を参酌して作製することができる。

【0169】

また、半導体装置の他の一形態として図6(B)にチャネル保護型(チャネルストップ型ともいう。)ボトムゲート・トップコンタクト構造のトランジスタ652を有する半導体装置を示す。トランジスタ652は、逆スタガ型トランジスタとも表現できる。

【0170】

図6(B)に示すように、トランジスタ652は、基板100と、基板100上の下地絶縁層102と、下地絶縁層102上のゲート電極110と、ゲート電極110及び下地絶縁層102上のゲート絶縁層108と、ゲート絶縁層108上の半導体層106と、半導体層106上の絶縁層602と、半導体層106および絶縁層602上の一対の電極114を有している。また、トランジスタ652上に、半導体層106、絶縁層602および一対の電極114を覆って設けられた絶縁層116と、絶縁層116上に設けられた第1の金属酸化物層118aと、第1の金属酸化物層118a上に設けられた第2の金属酸化物層118bと、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに設けられた開口部を介して一対の電極114と電気的に接続して設けられた配線120と、を有している。

【0171】

当該半導体装置は、図6(A)の半導体装置と比較して半導体層106上に絶縁層602を有している点が異なっている。絶縁層602は、エッチング処理(例えば、ドライエッチング処理やウェットエッチング処理など。)で一対の電極114を形成する際に、一対の電極114よりも下の層までエッチングが到達すること(オーバーエッチングとも言われる。)を防止する効果がある。特に、半導体層106が非常に薄い(具体的には、100nm以下、より具体的には40nm以下、さらに具体的には20nm以下。)場合、ごく僅かな厚さでも半導体層106がエッチングされると、トランジスタ652の電気的特性が大きく変動する可能性があるため、半導体層106の厚さが薄い場合、当該構造とすることが好ましい。なお、各々の構成要素の使用材料や形成方法は基本的に実施の形態1と同じであるため、上述の実施の形態に記載された作製方法を参酌して作製することができる。

【0172】

また、半導体装置の他の一形態として図6(C)にボトムゲート・ボトムコンタクト構造のトランジスタ653を有する半導体装置を示す。トランジスタ653は、逆スタガ型トランジスタとも表現できる。

【0173】

図6(C)に示すように、トランジスタ653は、基板100と、基板100上の下地絶縁層102と、下地絶縁層102上のゲート電極110と、ゲート電極110及び下地絶縁層102上のゲート絶縁層108と、ゲート絶縁層108上の一対の電極114と、ゲート絶縁層108及び一対の電極114上の半導体層106を有している。また、トランジスタ653上に、半導体層106および一対の電極114を覆って設けられた絶縁層116と、絶縁層116上に設けられた第1の金属酸化物層118aと、第1の金属酸化物層118a上に設けられた第2の金属酸化物層118bと、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bに設けられた開口部を介して一対の電極114と電気的に接続して設けられた配線120と、を有している。

【0174】

当該半導体装置は、図6(A)の半導体装置と比較して、半導体層106を形成する前に一対の電極114を形成している点で異なっているが、各々の構成要素の使用材料や形成方法は基本的に実施の形態1と同じであるため、上述の実施の形態に記載された作製方法を参酌して作製することができる。

【0175】

なお、図6(A)乃至図6(C)では、第1の金属酸化物層118aおよび第2の金属酸化物層118bが絶縁層116の上に位置する構成となっているが、実施の形態2にて記載したように、第1の金属酸化物層118aおよび第2の金属酸化物層118bが絶縁層116の下に位置する構造となっていてもよい。この際の構造および作製方法については、本実施の形態および実施の形態2を参酌すればよい。

【0176】

以上が、本実施の形態の半導体装置の構成および作製方法である。

【0177】

(実施の形態4)

本実施の形態では、先の実施の形態で説明した半導体装置を電子機器に適用する場合について、図7を用いて説明する。本実施の形態では、コンピュータ、携帯情報端末(携帯電話、携帯型ゲーム機、音響再生装置なども含む。)、電子ペーパー、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう。)、デジタルビデオカメラなどの電子機器に、上述の半導体装置を適用する場合について説明する。

【0178】

図7(A)は、携帯型の情報端末であり、筐体701、筐体702、第1の表示部703a、第2の表示部703bなどによって構成されている。筐体701と筐体702の内部には、様々な電子部品(例えば、CPU、MPU、記憶素子など。)が組み込まれている。また、第1の表示部703aと第2の表示部703bには、画像を表示するために必要な電子回路(例えば、駆動回路や選択回路など。)が搭載されている。これら電子部品や電子回路の中に先の実施の形態に示す、トランジスタへの水分の侵入が抑制された半導体装置が設けられている。そのため、長期間にわたり性能の劣化(例えば、記憶素子であれば、記憶素子中の半導体装置のしきい値電圧が変動し、誤った情報が記憶されるなど。また、駆動装置であれば、駆動装置中の半導体装置のしきい値電圧が変動し、誤った駆動信号を出力するなど。)が抑制された携帯型の情報端末が実現される。なお、先の実施の形態に示す半導体装置は、筐体701、筐体702の少なくとも一に設けられていればよい。

【0179】

なお、第1の表示部703aおよび第2の表示部703bの少なくとも一方は、タッチ入力機能を有する表示部となっており、例えば図7(A)の左図のように、第1の表示部703aに表示される選択ボタン704により「タッチ入力」を行うか、「キーボード入力」を行うかを選択できる。選択ボタンは様々な大きさで表示できるため、幅広い世代の人が使いやすさを実感できる。ここで、例えば「キーボード入力」を選択した場合、図7(A)の右図のように第1の表示部703aにはキーボード705が表示される。これにより、従来の情報端末と同様に、キーボード入力による素早い文字入力などが可能となる。

【0180】

また、図7(A)に示す携帯型の情報端末は、図7(A)の右図のように、筐体701と筐体702を分離することができる。これにより、筐体702を壁に掛けて大人数で画面情報を共有しながら、筐体701で画面情報をコントロールするといった操作が可能となり、非常に便利である。なお、当該装置を使用しない場合は、第1の表示部703a及び第2の表示部703bが向かい合うように、筐体701および筐体702を重ねた状態とすることが好ましい。これにより、外部より加わる衝撃などから第1の表示部703a及び第2の表示部703bを保護することができる。

【0181】

図7(A)に示す携帯型の情報端末は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。

【0182】

また、図7(A)に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0183】

さらに、図7(A)に示す筐体701や筐体702にアンテナやマイク機能や無線機能を持たせ、携帯電話として用いてもよい。

【0184】

図7(B)は、テレビジョン装置であり、筐体721、表示部722、スタンド723、リモコン724などで構成されている。テレビジョン装置についても、上述の携帯型の情報端末と同様に筐体721および表示部722には、様々な電子部品や電子回路が組み込まれており(または搭載されており)、これら電子部品や電子回路の中に先の実施の形態に示す、トランジスタへの水分の侵入が抑制された半導体装置を設けることで、長期間にわたり性能の劣化が抑制されたテレビジョン装置が実現される。

【0185】

図7(C)は、デジタルカメラであり、筐体731、操作スイッチ732、バッテリー733などを備えており、また、背面には表示部(本体の裏面にあるため図示しない。)などを備えている。デジタルカメラについても、筐体731内や表示部などに、先の実施の形態に示す半導体装置が設けられている。そのため、長期間にわたり性能の劣化が抑制されたデジタルカメラが実現される。

【0186】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置が搭載されている。このため、消費電力を低減した電子機器が実現される。

【実施例1】

【0187】

本実施例では、実施の形態1にて記載した、絶縁層116、第1の金属酸化物層118aおよび第2の金属酸化物層118bの形成方法についての具体例を記載する。また、当該層についての各種分析結果を記載する。

【0188】

絶縁層116は、スパッタリング装置を用いて酸化珪素膜を成膜した。絶縁層116の成膜条件は、使用ターゲット:Si、基板温度:R.T.、成膜雰囲気:100%O2、O2ガス流量:300sccm、チャンバー内圧力:0.7Pa、使用電源:AC電源、印加電力:6kWとし、400nmの膜厚で成膜した。

【0189】

次に、絶縁層116と同一の装置を用い、大気解放を行わずに連続して金属酸化物層118を成膜する。これにより、絶縁層116と金属酸化物層118界面への水分吸着を抑制できる。

【0190】

金属酸化物層118の成膜方法は、使用ターゲット:Pure−Al、基板温度:150℃、成膜雰囲気:100%O2、O2ガス流量:300sccm、チャンバー内圧力:0.7Pa、使用電源:AC電源、印加電力:30kWとし、50nmの膜厚で酸化アルミニウム膜を成膜した。

【0191】

絶縁層116上に成膜した金属酸化物層118の断面を、走査型透過電子顕微鏡(STEM:Scanning Transmission Electron Microscope)を用いて観察した結果を図8に示す。図8より、金属酸化物層118は、第1の金属酸化物層118aと第2の金属酸化物層118bの連続した2層構造となっている。これは、金属酸化物層118は高い印加電力で成膜されるが、その初期段階において、金属酸化物層118を構成する主要元素(ここではアルミニウムおよび酸素。)が、下に形成された層(ここでは、酸化珪素膜。)の元素を弾き出して金属酸化物層118中に混合(ミキシング効果とも言われる。)し、金属酸化物層118の結晶化を阻害することで、アモルファス構造を有する第1の金属酸化物層118aが形成される。そして、成膜が進むにつれてミキシング効果が減少し、多結晶構造を有する第2の金属酸化物層118bが形成される。

【0192】

なお、酸化アルミニウム膜の成膜では、チャンバーの雰囲気、圧力および印加電力などを調整することにより、上述の2層構造における各層(第1の金属酸化物層118aおよび第2の金属酸化物層118b)の膜厚を人為的に調整することが可能である。

【0193】

なお、本実施例では、酸化アルミニウムを用いて第1の金属酸化物層118aおよび第2の金属酸化物層118bの連続した積層の成膜についての説明を行ったが、勿論、他の金属酸化物についても、上述のように成膜における各種パラメータを調整することにより、連続した積層構造を形成してもよい。

【0194】

そして、第1の金属酸化物層118aおよび第2の金属酸化物層118bの膜質調査を行うため、各々の層の3箇所についてXRR測定にて膜密度調査を行った。その結果、第1の金属酸化物層118aでは、3.04g/cm3、3.02g/cm3および3.02g/cm3の膜密度が得られ、第2の金属酸化物層118bでは、3.80g/cm3、3.78g/cm3および3.76g/cm3の膜密度が得られた。当該測定結果より、第1の金属酸化物層118aはアモルファス構造を有する酸化アルミニウムであり、第2の金属酸化物層118bは多結晶構造を有する酸化アルミニウムであることが示唆される。

【0195】

なお、本実施例では、第1の金属酸化物層118aおよび第2の金属酸化物層118bとして酸化アルミニウムを用いた場合について記載したが、他の金属酸化物を用いた場合においても、XRRにより膜密度を測定し、当該測定結果を文献値などと比較することにより、層の状態(アモルファス状態であるか、多結晶状態であるか、など。)を調査することができる。

【0196】

本実施例は、他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

【0197】

100 基板

102 下地絶縁層

106 半導体層

106a 高抵抗領域

106b 低抵抗領域

107 絶縁層

108 ゲート絶縁層

110 ゲート電極

112 側壁絶縁層

114 一対の電極

116 絶縁層

118 金属酸化物層

118a 第1の金属酸化物層

118b 第2の金属酸化物層

120 配線

130 不純物イオン

150 トランジスタ

602 絶縁層

651 トランジスタ

652 トランジスタ

653 トランジスタ

701 筐体

702 筐体

703a 第1の表示部

703b 第2の表示部

704 選択ボタン

705 キーボード

721 筐体

722 表示部

723 スタンド

724 リモコン

731 筐体

732 操作スイッチ

733 バッテリー

【特許請求の範囲】