半導体装置、パラメータ最適化方法、及びプログラム

【課題】トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供すること。

【解決手段】MOSトランジスタから構成されたプリミティブゲート回路11aを奇数段でリング状に結合した第1リングオシレータ部11の各前記プリミティブゲート回路の出力部と電気的に接続された負荷部12となる第1配線を有する配線負荷パターンと、第2リングオシレータ部の各プリミティブゲート回路の出力部が第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、第3リングオシレータ部の各プリミティブゲート回路の出力部が第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

【解決手段】MOSトランジスタから構成されたプリミティブゲート回路11aを奇数段でリング状に結合した第1リングオシレータ部11の各前記プリミティブゲート回路の出力部と電気的に接続された負荷部12となる第1配線を有する配線負荷パターンと、第2リングオシレータ部の各プリミティブゲート回路の出力部が第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、第3リングオシレータ部の各プリミティブゲート回路の出力部が第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するために用いる半導体装置、パラメータ最適化方法、及びプログラムに関する。

【背景技術】

【0002】

MOSトランジスタを用いた半導体集積回路の設計では、シリコンウェハ上に作成されたリングオシレータ(Ring Oscillator;ROSC)パターンにより測定した伝達遅延時間(Tpd)とSPICE(Simulation Program with Integrated Circuit Emphasis)を用いてシミュレーションしたTpdとの整合検証が行われる。この整合検証を行う過程において、そのTpd誤差の要因分析をするためには、DC(直流)的な要因とAC(容量)的な要因とに分離することが不可欠となる。

【0003】

AC的な要因には、ゲート容量、ゲートオーバラップ容量、ジャンクション容量のトランジスタ部の容量成分とROSCを形成している配線容量がある。AC的な誤差を最適化するためには、これら各々の容量成分を分析した上で、誤差の起因となっている容量パラメータを最適化しなければならない。容量パラメータを測定するには、一般的には、LCRメータ(コイル(L)/コンデンサ(C)/インピーダンス(Z、R)の測定装置)などで、容量抽出パターンを用いて、直接的にゲート容量、ゲートオーバラップ容量、配線容量の測定を行い、その実測値に対して、パラメータ抽出を行っている(非特許文献1、2参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−251976号公報

【特許文献2】特開2002−261272号公報

【特許文献3】特開2000−298683号公報

【特許文献4】特開2010−10515号公報

【非特許文献】

【0005】

【非特許文献1】青木均著、外2名、「CMOSモデリング技術−SPICE用コンパクトモデリングの理論と実践」、初版、丸善、2006年1月、p.185−193。

【非特許文献2】三浦道子著、外2名、「回路シミュレーション技術とMOSFETモデリング」、リアライズ理工センター、2003年3月、p.385−390。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、LCRメータにて直接測定するには、容量値の感度を高めるために、実回路(インバータ、NAND回路、NOR回路などのプリミティブゲート回路)とは異なる大きなレイアウト構造によりパラメータ抽出を行うため、TEG(Test Element Group)面積効率が悪いことや、実回路動作時の遅延値として、正しく抽出されているかどうかを判別するには、実回路動作時の遅延値の求め、遅延量として、実測値と比較するまでわからないという問題点がある。

【0007】

また、遅延として観測された値は、それぞれの容量パラメータの合計値として観測されるので、実回路の周波数(又はTpd)として観測される値と、シミュレーション値とがずれた場合、各容量成分のうちどの容量成分がずれているのかを判定することが難しいという問題点もある。

【0008】

さらに、ROSCから観測されるTpdから容量換算するには、各容量成分の要因分離が難しいという問題がある。

【0009】

ところで、Tpd検証のシリコン特性とシミュレーション特性とのTpd誤差要因分析過程において、DC的な要因誤差、AC的な要因誤差とに分けて評価しなければ、正確にTpd誤差を最適化することができない。その中でも、AC的な要因誤差においては、トランジスタ起因のゲート容量、ゲートオーバラップ容量、ジャンクション容量の誤差や、配線起因の誤差にそれぞれ分け、パラメータの最適化をしなければならない。

【0010】

従来技術においては、Tpdを検証する上で、個々のパラメータを最適化する手法として、ROSCパターンによるDC的な要因分析法(特許文献1参照)、AC的な要因分析法(特許文献2、3参照)が開示されている。特に、AC的な要因分析法では、配線容量に特化したものが多い。また、特許文献2では、トランジスタのゲートオーバラップ容量のみに特化して議論されている。

【0011】

しかしながら、特許文献1−3に記載の手法では、トランジスタの容量成分までブレークダウンして議論されておらず、トランジスタの容量の各成分や配線容量を分離して、誤差分析することができない。

【0012】

また、特許文献4では、負荷部のコンタクト個数依存性のTpdインパクトを抽出するパターンを提案しているが、コンタクト部の容量パラメータの具体的な最適化、抽出方法については、議論されていない。

【0013】

本発明の主な課題は、トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供することである。

【課題を解決するための手段】

【0014】

本発明の第1の視点においては、半導体装置において、MOSトランジスタから構成されたプリミティブゲート回路を奇数段でリング状に結合した第1リングオシレータ部の各前記プリミティブゲート回路の出力部と電気的に接続された第1配線を有する配線負荷パターンと、前記第1リングオシレータ部と同様な構成の第2リングオシレータ部の各プリミティブゲート回路の出力部が前記第1配線と同様な構成の第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、前記第1リングオシレータ部と同様な構成の第3リングオシレータ部の各プリミティブゲート回路の出力部が前記第1配線と同様な構成の第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、前記複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、前記複数の拡散層負荷パターンは、パターンごとに容量負荷が異なることを特徴とする。

【0015】

本発明の第2の視点においては、前記半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するパラメータ最適化方法であって、前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションする工程と、前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算する工程と、前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化する工程と、を含むことを特徴とする。

【0016】

本発明の第3の視点においては、前記半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するプログラムであって、前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションするステップ(図12のステップA2)と、前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算するステップ(図12のステップA3、A5、A7、A9)と、前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化するステップ(図12のステップA4、A6、A8、A10)と、を実行させることを特徴とする。

【発明の効果】

【0017】

本発明によれば、LCRメータ等の測定装置から直接、容量抽出を行うことなく、伝播遅延時間の感度を用いて、間接的にパラメータを最適化することができる。また、リングオシレータパターンのように、実回路に近いパターンにて、パラメータを最適化することができるため、実際の回路動作時の誤差を最小限に抑えることができる。

【図面の簡単な説明】

【0018】

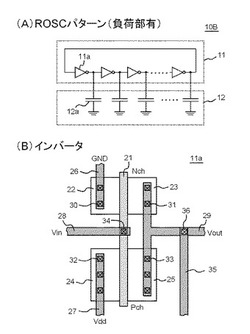

【図1】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置における基本構成となる負荷部が無いROSCパターンの構成を模式的に示した(A)回路図、(B)インバータの平面図である。

【図2】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置における基本構成となる負荷部があるROSCパターンの構成を模式的に示した(A)回路図、(B)インバータの平面図である。

【図3】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける配線負荷パターンの構成を模式的に示した部分平面図である。

【図4】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおけるゲート負荷パターン(負荷本数1本)の構成を模式的に示した部分平面図である。

【図5】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおけるゲート負荷パターン(負荷本数3本)の構成を模式的に示した部分平面図である。

【図6】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン1)の構成を模式的に示した部分平面図である。

【図7】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン2)の構成を模式的に示した部分平面図である。

【図8】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン3)の構成を模式的に示した部分平面図である。

【図9】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン1)の構成を模式的に示した部分平面図である。

【図10】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン2)の構成を模式的に示した部分平面図である。

【図11】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン3)の構成を模式的に示した部分平面図である。

【図12】本発明の実施例1に係るパラメータ最適化方法を模式的に示したフローチャートである。

【図13】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて負荷部が無い場合、及び、配線負荷パターンを有する場合のそれぞれのTpdの実測値及びシミュレーション値を模式的に示したグラフである。

【図14】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいてゲート負荷パターンを有する場合の条件1でのTpdの実測値及びシミュレーション値(最適化前と後)のゲート負荷本数依存性を模式的に示したグラフである。

【図15】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいてゲート負荷パターンを有する場合の条件2でのTpdの実測値及びシミュレーション値(最適化前と後)のゲート負荷本数依存性を模式的に示したグラフである。

【図16】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(STI構成)を有する場合のTpdの実測値及びシミュレーション値(最適化前と後)のSTI周囲長依存性を模式的に示したグラフである。

【図17】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(STI構成)と配線負荷パターンとのTpdとの関係を模式的に示したグラフである。

【図18】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(ゲート構成)を有する場合のTpdの実測値及びシミュレーション値(最適化前と後)のゲート周囲長依存性を模式的に示したグラフである。

【図19】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(ゲート構成)と配線負荷パターンとのTpdとの関係を模式的に示したグラフである。

【発明を実施するための形態】

【0019】

本発明の実施形態1に係る半導体装置では、MOSトランジスタから構成されたプリミティブゲート回路(図2の11a)を奇数段でリング状に結合した第1リングオシレータ部(図2の11)の各前記プリミティブゲート回路の出力部と電気的に接続された第1配線(図3の35〜38)を有する配線負荷パターン(図3参照)と、前記第1リングオシレータ部と同様な構成の第2リングオシレータ部(図2の11)の各プリミティブゲート回路(図2の11a)の出力部が前記第1配線と同様な構成の第2配線(図4、図5の35〜38)を介して負荷部(図4、図5の12)となるMOSトランジスタのゲート(図4、図5の40)に電気的に接続された複数のゲート負荷パターン(図4、図5参照)と、前記第1リングオシレータ部と同様な構成の第3リングオシレータ部(図2の11)の各プリミティブゲート回路(図2の11a)の出力部が前記第1配線と同様な構成の第3配線(図6〜図11の35〜38)を介して負荷部となる拡散層(図6〜図11の50又は52若しくは53)に電気的に接続された複数の拡散層負荷パターン(図6〜図11参照)と、を備え、前記複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、前記複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

【0020】

本発明の前記半導体装置においては、前記複数のゲート負荷パターンは、パターンごとに前記第2配線に電気的に接続される前記ゲートの個数が異なることが好ましい。

【0021】

本発明の前記半導体装置においては、前記ゲート負荷パターンは、前記負荷部となる前記MOSトランジスタのソース、ドレイン及び基板のそれぞれの端子に任意の電位を印加することができるように構成されていることが好ましい。

【0022】

本発明の前記半導体装置においては、前記複数の拡散層負荷パターンは、互いに前記第3配線に電気的に接続される前記拡散層の個数が異なることが好ましい。

【0023】

本発明の前記半導体装置においては、前記複数の拡散層負荷パターンは、前記負荷部となる前記拡散層の周囲の領域にSTIが配されているSTI構成と、前記負荷部となる前記拡散層の周囲の領域にゲートが配されているゲート構成と、を有することが好ましい。

【0024】

本発明の前記半導体装置においては、前記複数の拡散層負荷パターンにおける前記負荷部の基板の電位は、前記第3リングオシレータ部の基板電位と同じ電位であり、

前記複数の拡散層負荷パターンにおける前記ゲート構成の前記ゲートは、任意の電位を印加することができるように構成されていることが好ましい。

【0025】

本発明の実施形態2に係るパラメータ最適化方法では、前記半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するパラメータ最適化方法であって、前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションする工程(図12のステップA2)と、前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算する工程(図12のステップA3、A5、A7、A9)と、前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化する工程(図12のステップA4、A6、A8、A10)と、を含む。

【0026】

本発明の前記パラメータ最適化方法においては、前記伝播遅延時間を実測及びシミュレーションする工程では、前記ゲート負荷パターンの前記負荷部のゲート容量又はゲートオーバラップ容量による伝播遅延時間を実測及びシミュレーションすることが好ましい。

【0027】

本発明の前記パラメータ最適化方法において、前記傾きを計算する工程では、前記ゲート負荷パターンに係る前記伝播遅延時間のゲート個数依存性の実測値及びシミュレーション値の傾きを計算することが好ましい。

【0028】

本発明の前記パラメータ最適化方法においては、前記傾きを計算する工程では、前記拡散層負荷パターンに係る前記伝播遅延時間の前記拡散層がSTIと接するSTI周囲長、又は、前記拡散層が前記ゲートと隣接するゲート周囲長の依存性の実測値及びシミュレーション値の傾きを計算することが好ましい。

【0029】

本発明の前記パラメータ最適化方法においては、前記STI周囲長又は前記ゲート周囲長が0のときの伝播遅延時間と、前記配線負荷パターンの伝播遅延時間との実測値とシミュレーション値の差分が一致しないときに、前記シミュレーション値の差分を前記実測値の差分に一致させるようにようにして、他の所定のパラメータを最適化する工程を含むことが好ましい。

【0030】

本発明の実施形態3に係るプログラムでは、前記半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するプログラムであって、前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションするステップと、前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算するステップと、前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化するステップと、を実行させる。

【0031】

なお、本出願において図面参照符号を付している場合は、それらは、専ら理解を助けるためのものであり、図示の態様に限定することを意図するものではない。

【実施例1】

【0032】

本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置について図面を用いて説明する。図1は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置における基本構成となる負荷部が無いROSCパターンの構成を模式的に示した(A)回路図、(B)インバータの平面図である。図2は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置における基本構成となる負荷部があるROSCパターンの構成を模式的に示した(A)回路図、(B)インバータの平面図である。図3は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける配線負荷パターンの構成を模式的に示した部分平面図である。図4は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおけるゲート負荷パターン(負荷本数1本)の構成を模式的に示した部分平面図である。図5は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおけるゲート負荷パターン(負荷本数3本)の構成を模式的に示した部分平面図である。図6は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン1)の構成を模式的に示した部分平面図である。図7は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン2)の構成を模式的に示した部分平面図である。図8は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン3)の構成を模式的に示した部分平面図である。図9は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン1)の構成を模式的に示した部分平面図である。図10は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン2)の構成を模式的に示した部分平面図である。図11は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン3)の構成を模式的に示した部分平面図である。

【0033】

パラメータ最適化方法は、回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化する方法である。パラメータ最適化方法は、半導体装置に電気的に接続された測定装置(例えば、LCRメータ等)を用いて伝達遅延時間(Tpd)を測定し、半導体装置におけるMOSトランジスタ部と同じモデルについて回路シミュレーションプログラム(例えば、SPICE等)を実行するコンピュータを用いてTpdをシミュレーションすることによって、当該コンピュータにて、Tpdの整合検証を行い、整合していなければ回路シミュレーションソフトにおけるMOSトランジスタのモデルのパラメータを最適化する。このようなパラメータ最適化方法を実施するために、以下のような半導体装置(モデル)が用いられる。

【0034】

半導体装置は、半導体集積回路の動作速度を評価するためのテスト回路として負荷部の無いリングオシレータ部11(ROSC部)のみからなるROSCパターン10Aを有する(図1(A)参照)。ROSCパターン10Aは、MOSトランジスタ(Nch型トランジスタ、Pch型トランジスタ)から構成されたインバータ11a(その他のNAND回路、NOR回路などのプリミティブゲート回路でも可)を多段(奇数段;通常は47段)でリング状に結合した構成となっている。インバータ11aは、電圧が入力されるVin配線28がコンタクト34を介してNch型トランジスタ及びPch型トランジスタの共通のゲート21と電気的に接続され、Nch型トランジスタではゲート21の両側にソース/ドレイン領域となる拡散層22、23が形成され、Pch型トランジスタではゲート21の両側にソース/ドレイン領域となる拡散層24、25が形成され、拡散層22がコンタクト30を介してGND配線26に電気的に接続され、拡散層24がコンタクト32を介してVdd配線27に電気的に接続され、拡散層23、25がそれぞれコンタクト31、33を介して共通のVout配線29に電気的に接続されている(図1(B)参照)。

【0035】

また、半導体装置は、ROSCパターン10Aとは別に、ROSCパターン10AにおけるDC特性の合わせ込みを行うためのモデルとして、リングオシレータ部11に負荷部12を接続したROSCパターン10Bを有する(図2(A)参照)。ROSCパターン10Bは、図1(A)のROSCパターン10AのROSC部11と同様な構成のROSC部11を有し、ROSC部11におけるか各インバータ11aのVout配線29がコンタクト36を介して配線35に電気的にされ(図2(B)参照)、配線35が負荷部12における負荷容量12aの一端に電気的に接続され、負荷容量12aの他端がGNDに電気的に接続されている。負荷容量12aには、複数のモデルがあり、配線負荷パターン(図3参照)と、ゲート負荷パターン(図4、図5参照)と、拡散層負荷パターン(図6〜図11参照)と、がある。

【0036】

図3の配線負荷パターンは、ゲート負荷パターン(図4、図5参照)及び拡散層負荷パターン(図6〜図11参照)での配線容量による誤差を排除するためのものであり、ゲート負荷パターン及び拡散層負荷パターンの配線部分(配線35、コンタクト38、配線37)と同じ構成となっている。配線負荷パターンでは、各インバータ11aのVout配線29から負荷部(図2(A)の12)に引き出された配線35がコンタクト38を介して配線37と電気的に接続された構成となっている。配線負荷パターンは、ゲート負荷パターン及び拡散層負荷パターンの容量負荷パターンのフレームワークとなっており、配線37にコンタクトを介してゲート又は拡散層に接続するのみで、ゲート負荷パターン及び拡散層負荷パターンとすることができるという特徴がある。なお、配線容量は、一般的に、LPE(Layout Parameter Extraction)を使用することで抽出できるが、図3の配線負荷パターンでは、ウェハごとの太り、細り量をTpdとして計測できる。

【0037】

図4、図5のゲート負荷パターンは、負荷部12の配線37とMOSトランジスタのゲート40とがコンタクト41を介して接続された負荷本数を変更したパターン(図4では1本、図5では3本)となっている。ゲート負荷パターンでは、ゲート40の両側に拡散層42が配されたMOSトランジスタがゲート長方向に並んで配されており、所定のゲート40がコンタクト41を介して配線37に電気的に接続されており、各拡散層42がコンタクト44を介して配線43に電気的に接続されている。MOSトランジスタは、NMOSまたは、PMOSのどちらか一方である。配線43のうちソースに係る拡散層42と電気的に接続されている配線43は、ソース端子46に電気的に接続されている。配線43のうちドレインに係る拡散層42と電気的に接続されている配線43は、ドレイン端子47に電気的に接続されている。MOSトランジスタの基板は、基板端子48(ボディ端子)と電気的に接続されている。ソース端子46、ドレイン端子47、基板端子48は、それぞれ任意の電位が与えられるように、回路上、独立した端子となっている。

【0038】

図6〜図11の拡散層負荷パターン(ジャンクション容量負荷パターン)は、図6〜図8のSTI(Shallow Trench Isolation;素子分離)構成と、図9〜図11のゲート構成と、の2種類の構成がある。

【0039】

図6〜図8のSTI構成の拡散層負荷パターンは、複数の拡散層50、52、53が並んでおり、各拡散層50、52、53がSTI(図示せず)に囲まれた構成となっており、各拡散層50、52、53がコンタクト51を介して配線37に電気的に接続されている。図6の各拡散層50は、1本のコンタクト51と接続されており、拡散層52よりも短い。図7の各拡散層52は、2本のコンタクト51と接続されており、拡散層50よりも長く、拡散層53よりも短い。図8の各拡散層53は、3本のコンタクト51と接続されており、拡散層52よりも長い。図6の拡散層50のトータルの拡散層面積は、図7の拡散層52のトータルの拡散層面積、及び、図8の拡散層53のトータルの拡散層面積と一致するように設定されている。図6〜図8のSTI構成の拡散層負荷パターンは、STIと接する拡散層の周囲の長さとなるSTI周囲長を変更したパターンとなっている。STI構成の拡散層負荷パターンにおける基板電位は、ROSC部(図2(A)の11)の基板電位と同電位であり、基板がN+拡散層で形成された場合には、基板電位はGNDとなり、基板がP+拡散層で形成された場合には、基板電位はVddとなる。

【0040】

図9〜図11のゲート構成の拡散層負荷パターンは、複数の拡散層50、52、53が並んでおり、各拡散層50、52、53がゲート55に囲まれた構成となっており、各拡散層50、52、53がコンタクト51を介して配線37に電気的に接続されている。なお、図9〜図11の拡散層50、52、53は、図6〜図8の拡散層50、52、53の構成と同様である。図9の各拡散層50は、1本のコンタクト51と接続されており、拡散層52よりも短い。図10の各拡散層52は、2本のコンタクト51と接続されており、拡散層50よりも長く、拡散層53よりも短い。図11の各拡散層53は、3本のコンタクト51と接続されており、拡散層52よりも長い。図9の拡散層50のトータルの拡散層面積は、図10の拡散層52のトータルの拡散層面積、及び、図11の拡散層53のトータルの拡散層面積と一致するように設定されている。図9〜図11のゲート構成の拡散層負荷パターンは、ゲート55と隣接する拡散層の周囲の長さとなるゲート周囲長を変更したパターンとなっている。ゲート構成の拡散層負荷パターンにおける基板電位は、ROSC部(図2(A)の11)の基板電位と同電位であり、基板がN+拡散層で形成された場合には、基板電位はGNDとなり、基板がP+拡散層で形成された場合には、基板電位は、Vddとなる。負荷部(図2(A)の12)の拡散層50、52、53と電気的に接続されるゲート端子(図示せず)は、任意の電位を与えられるように独立した端子となっている。

【0041】

次に、本発明の実施例1に係るパラメータ最適化方法について図面を用いて説明する。図12は、本発明の実施例1に係るパラメータ最適化方法を模式的に示したフローチャートである。図13は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて負荷部が無い場合、及び、配線負荷パターンを有する場合のそれぞれの場合のTpdの実測値及びシミュレーション値を模式的に示したグラフである。図14は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいてゲート負荷パターンを有する場合の条件1でのTpdの実測値及びシミュレーション値(最適化前と後)のゲート負荷本数依存性を模式的に示したグラフである。図15は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいてゲート負荷パターンを有する場合の条件2でのTpdの実測値及びシミュレーション値(最適化前と後)のゲート負荷本数依存性を模式的に示したグラフである。図16は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(STI構成)を有する場合のTpdの実測値及びシミュレーション値(最適化前と後)のSTI周囲長依存性を模式的に示したグラフである。図17は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(STI構成)と配線負荷パターンとのTpdとの関係を模式的に示したグラフである。図18は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(ゲート構成)を有する場合のTpdの実測値及びシミュレーション値(最適化前と後)のゲート周囲長依存性を模式的に示したグラフである。図19は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(ゲート構成)と配線負荷パターンとのTpdとの関係を模式的に示したグラフである。

【0042】

まず、DC特性の最適化フローとして、ROSCパターン(図1(A)参照)のDC特性を再現するモデルを用意する(図12のステップA1)。ここでは、ROSCパターン(図1(A)の10A)における1つのNMOS、PMOSのそれぞれの端子を抜き出したパターンよりDC特性を測定し、DCパラメータの最適化を行う。具体的には、ドレイン電流Idとゲート電圧VgとのIdVg特性、ドレイン電流Idとドレイン電圧VdとのIdVd特性などの基本特性を測定し、モデルパラメータに反映させる。

【0043】

次に、各バイアス条件でのROSCパターン(図1(A)、図2(A)、図3〜図11参照)の伝播遅延時間(Tpd)を測定(実測、シミュレーション)する(図12のステップA2)。なお、シミュレーションでは、DC測定結果を再現するようにパラメータを調整したモデルを用いる。

【0044】

ここで、負荷部の無いROSCパターン(図1(A)参照)、配線負荷パターン(図3参照)、及び、拡散層負荷パターンのSTI構成パターン(図6〜図8参照)では、基板がN+拡散層で形成された場合には、基板電位をGNDに固定し、基板がP+拡散層で形成された場合には、基板電位をVddに固定して、Tpdの測定を行う。

【0045】

また、ゲート負荷パターン(図4、図5参照)は、負荷部12のトランジスタの各端子が、任意に変更できるパターンであるので、ゲート容量捕捉することを目的とした評価の場合、負荷部12のトランジスタのソース端子46、ドレイン端子47、基板端子48を−Vdd(もしくは、チャネルが形成された状態のバイアス条件)にて固定して、Tpdの測定を行う(条件1)。一方、ゲートオーバラップ容量を捕捉する評価を目的とした場合、ソース端子46、ドレイン端子47をVdd、基板端子48をGND(もしくは、チャネルが形成されないバイアス条件)に固定して、Tpdの測定を行う(条件2)。

【0046】

また、拡散層負荷パターン(ゲート構成)(図9〜図11参照)では、負荷部のゲート55に係るゲート電位をGND(もしくは、チャネルが形成されないバイアス条件)に固定して、Tpdの測定を行う。

【0047】

次に、各ROSCパターン(図1(A)、図2(A)、図3〜図11参照)にて得られたTpdの実測値とシミュレーション値との誤差を計算し、誤差があれば回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化する(図12のステップA3〜ステップA10)。各パターンのTpdの実測値とシミュレーション値との誤差(Tpd誤差)は、[数式1]〜[数式5]の関係となる。

【0048】

負荷無しのROSCパターン(図1(A)参照)のTpd誤差(ΔTpd_ring)は、[数式1]の関係となる。

【0049】

[数式1]

ΔTpd_ring=Tpd_ring_meas−Tpd_ring_sim=ΔCGate+ΔCjtotal+ΔWire_ring

※Tpd_ring_meas:負荷無しのROSCパターンのTpdの測定値

Tpd_ring_sim:負荷無しのROSCパターンのTpdのシミュレーション値

ΔCGate=ΔCg+ΔCov

ΔCGate:負荷無しのROSCパターンのゲート負荷容量起因誤差

ΔCg:ゲート容量成分起因誤差

ΔCov:ゲートオーバラップ容量成分起因誤差

ΔCjtotal=ΔCj+ΔCjsw+ΔCjswg

ΔCjtotal:負荷無しのROSCパターンの拡散層負荷容量起因誤差

ΔCj:拡散層底面容量成分起因誤差

ΔCjsw:拡散層STI周囲長容量成分起因誤差

ΔCjswg:拡散層ゲート周囲長容量成分起因誤差

ΔWire_ring:負荷無しのROSCパターンの配線負荷起因誤差

【0050】

配線負荷パターン(図3参照)のTpd誤差(ΔTpd_wire_load)は、[数式2]の関係となる。

【0051】

[数式2]

ΔTpd_wire_load=Tpd_wire_load_meas−Tpd_wire_load_sim=ΔTpd_ring−ΔWire_load

※Tpd_wire_load_meas:配線負荷パターンのTpdの測定値

Tpd_wire_load_sim:配線負荷パターンのTpdのシミュレーション値

ΔTpd_ring:負荷無しのROSCパターンのTpd誤差

ΔWire_load:負荷部の配線負荷起因誤差

【0052】

ゲート負荷パターン(図4、図5参照)のTpd誤差(ΔTpd_CGate_load)は、[数式3]の関係となる。

【0053】

[数式3]

ΔTpd_CGate_load=Tpd_CGate_load_meas−Tpd_CGate_load_sim

=ΔTpd_wire_load+ΔCGate_load

※Tpd_CGate_load_meas:ゲート負荷パターンのTpdの測定値

Tpd_CGate_load_sim:ゲート負荷パターンのTpdのシミュレーション値

ΔTpd_wire_load:配線負荷パターンのTpd誤差

ΔCGate_load:ゲート負荷パターンのゲート負荷容量起因誤差

【0054】

なお、ゲート負荷パターンのゲート負荷容量起因誤差(ΔCGate_load)が最適化されれば、負荷無しのROSCパターンのゲート負荷容量起因誤差(ΔCGate)も同時に誤差がなくなる。

【0055】

拡散層負荷パターン(STI構成)(図6〜図8参照)のTpd誤差(ΔTpd_CjSTI_load)は、[数式4]の関係となる。

【0056】

[数式4]

ΔTpd_CjSTI_load=Tpd_Cj_load_meas−Tpd_Cj_load_sim

=ΔTpd_wire_load+ΔCjsw_load+ΔCj_load

※Tpd_Cj_load_meas:拡散層負荷パターン(STI構成)のTpdの測定値

Tpd_Cj_load_sim:拡散層負荷パターン(STI構成)のTpdのシミュレーション値

ΔTpd_wire_load:配線負荷パターンのTpd誤差

ΔCjsw_load:拡散層負荷パターン(STI構成)の拡散層STI周囲長容量成分起因誤差

ΔCj_load:拡散層負荷パターン(STI構成)の拡散層底面容量成分起因誤差

【0057】

なお、拡散層負荷パターン(STI構成)の拡散層STI周囲長成分起因誤差(ΔCjsw_load)及び拡散層底面容量成分起因誤差(ΔCj_load)の誤差が最適化されれば、負荷無しのROSCパターンの拡散層STI周囲長容量成分起因誤差(ΔCjsw)及び拡散層底面容量成分起因誤差(ΔCj)も同時に誤差はなくなる。

【0058】

拡散層負荷パターン(ゲート構成)(図9〜図11参照)のTpd誤差(ΔTpd_Cjate_load)は、[数式5]の関係となる。

【0059】

[数式5]

ΔTpd_Cjate_load=Tpd_Cj_load_meas−Tpd_Cj_load_sim

=ΔTpd_wire_load+ΔCjswg_load+ΔCj_load+ΔCov_load

※Tpd_Cj_load_meas:拡散層負荷パターン(ゲート構成)のTpdの測定値

Tpd_Cj_load_sim:拡散層負荷パターン(ゲート構成)のTpdのシミュレーション値

ΔTpd_wire_load:配線負荷パターンのTpd誤差

ΔCjswg_load:拡散層負荷パターン(ゲート構成)の拡散層ゲート周囲長容量成分起因誤差

ΔCj_load:拡散層負荷パターン(ゲート構成)の拡散層底面容量成分起因誤差

ΔCov_load:拡散層負荷パターン(ゲート構成)のゲートオーバラップ容量成分起因誤差

【0060】

なお、拡散層負荷パターン(ゲート構成)の拡散層底面容量成分起因誤差(ΔCj_load)が最適化されるとともに、拡散層負荷パターン(ゲート構成)のゲートオーバラップ容量成分起因誤差(ΔCov_load)が最適化されていれば、拡散層負荷パターンの固有の誤差は拡散層負荷パターン(ゲート構成)の拡散層ゲート周囲長容量成分起因誤差(ΔCjswg_load)のみとなるので、拡散層負荷パターン(ゲート構成)の拡散層ゲート周囲長容量成分起因誤差(ΔCjswg_load)が最適化されれば、負荷無しのROSCパターンの拡散層ゲート周囲長容量成分起因誤差(ΔCjswg)の誤差もなくなる。

【0061】

また、各ROSCパターン(図1(A)、図2(A)、図3〜図11参照)のROSC部(図1(A)、図2(A)の11)で形成されているトランジスタと、負荷部(図2(A)の12)のトランジスタ、拡散層、ゲートの形成条件は、同一のプロセス条件で形成されていることが前提である。

【0062】

負荷無しのROSCパターン(図1(A)参照)のTpdの実測値とシミュレーション値、及び、配線負荷パターン(図2(A)、図3参照)のTpdの実測値とシミュレーション値を図13に示す。最終的な目標は、負荷無しのROSCパターン(図1(A)参照)のTpdの実測値(Tpd_ring_meas)とシミュレーション値(Tpd_ring_sim)の誤差(図13のΔTpd_ring)を「ゼロ」にすることにある。各パターンの誤差は、[数式1]、[数式2]に示した通りの関係が成り立つ。これら、ΔTpd_ringは、各負荷パターンのTpd−負荷依存性(漸近線)の傾きを一致させるようにパラメータを調整することで、簡便にROSC部(図1(A)、図2(A)の11)の誤差をなくすことができる。

【0063】

以下、具体的な各負荷パターン(図2(A)、図3〜図11参照)でのパラメータ最適化方法(図12のステップA3〜ステップA10)の詳細を述べる。

【0064】

ステップA2の後、ゲート負荷パターン(図4、図5参照)のTpdのゲート本数依存性の実測値とシミュレーション値の各傾きを条件1で計算し、各傾きが一致するか否かを判断する(図12のステップA3)。なお、条件1は、負荷トランジスタのチャネルが形成されたバイアス条件であり、負荷トランジスタがNMOSの場合にはソース端子46、ドレイン端子47、基板端子48は−Vdd電位に固定され、負荷トランジスタがPMOSの場合にはソース端子46、ドレイン端子47、基板端子48はVdd電位に固定される。図14に条件1でのTpd−ゲート本数依存性の実測値とシミュレーション値を示す。この傾きのズレは、ゲート容量パラメータ(Cg)の実測値とシミュレーション値の誤差(ΔCg)を示している。Tpdのゲート本数依存性の実測とシミュレーションの各傾きが一致している場合(ステップA3のYES)、ステップA5に進む。

【0065】

Tpdのゲート本数依存性の実測値とシミュレーション値の各傾きが一致していない場合(ステップA3のNO)、シミュレーション値の傾きを実測値の傾きに一致させるようにゲート容量パラメータ(Cg)にて調整することにより、ゲート容量成分起因誤差(ΔCg)を最適化する(図12のステップA4)。

【0066】

ステップA3のYESの場合、又は、ステップA4の後、ゲート負荷パターン(図4、図5参照)のTpdのゲート本数依存性の実測値とシミュレーション値の各傾きを条件2で計算し、各傾きが一致するか否かを判断する(図12のステップA5)。なお、条件2は、負荷トランジスタのチャネルが形成されないバイアス条件であり、負荷トランジスタがNMOSの場合にはソース端子46及びドレイン端子47はVdd電位に固定され、かつ、基板端子48はGND電位に固定され、負荷トランジスタがPMOSの場合にはソース端子46及びドレイン端子47は−Vdd電位に固定され、かつ、基板端子48はGND電位に固定される。図15に条件2でのTpd−ゲート本数依存性の実測値とシミュレーション値を示す。この傾きのズレは、ゲートオーバラップ容量パラメータ(Cov)の誤差(ΔCov)を示している。Tpdのゲート本数依存性の実測値とシミュレーション値の各傾きが一致している場合(ステップA5のYES)、ステップA7に進む。

【0067】

Tpdのゲート本数依存性の実測値とシミュレーション値の各傾きが一致していない場合(ステップA5のNO)、シミュレーション値の傾きを実測値の傾きに一致させるようにゲートオーバラップ容量パラメータ(Cov)を調整することにより、ゲートオーバラップ容量成分起因誤差(ΔCov)を最適化する(図12のステップA6)。

【0068】

ステップA5のYESの場合、又は、ステップA6の後、拡散層負荷パターン(STI構成;図6〜図8参照)のTpdのSTI周囲長依存性の実測値とシミュレーション値の各傾きを計算し、各傾き、及び、STI周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致するか否かを判断する(図12のステップA7)。ここで、STI周囲長は、STIと接する拡散層の周囲の長さである。図16、図17にTpd-STI周囲長依存性の実測値とシミュレーション値を示す。TpdのSTI周囲長依存性の実測値とシミュレーション値の各傾き、及び、STI周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致する場合(ステップA7のYES)、ステップA9に進む。

【0069】

TpdのSTI周囲長依存性の実測値とシミュレーション値の各傾き、及び、STI周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致しない場合(ステップA7のNO)、以下のようにしてパラメータを最適化する(図12のステップA8)。

【0070】

傾きのズレに関しては、Tpd−ゲート本数依存性(図14、図15参照)と同様に、シミュレーション値の傾きを実測値の傾きに一致させるように拡散層STI周囲長容量パラメータ(Cjsw)を調整することにより、拡散層STI周囲長容量成分起因誤差(ΔCjsw)を最適化する(図16参照)。なお、差分のみが一致していない場合は、ΔCjswの最適化を省略することができる。

【0071】

また、差分に関しては、傾きの線とY軸(縦軸)との交点(STI周囲長=0)は、拡散層底面容量パラメータ(Cj)を示しているので、STI周囲長=0のときのTpdは、下記[数式6]の関係が成り立つように、シミュレーション値の差分(Cj_delta(sim))を実測値の差分(Cj_delta(meas))に一致させるように拡散層底面容量パラメータ(Cj)を調整することにより、拡散層底面容量成分起因誤差(ΔCj)を最適化する(図17参照)。なお、傾きのみが一致していない場合は、ΔCjの最適化を省略することができる。

【0072】

[数式6]

Cj_delta(meas)=Tpd_wire_load_meas−Tpd_CjSTI_load_meas

Cj_delta(sim)=Tpd_wire_load_sim−Tpd_CjSTI_load_sim

Cj_delta(meas)=Cj_delta(sim)

※Tpd_wire_load_meas:配線負荷パターンのTpdの実測値

Tpd_CjSTI_load_meas:STI周囲長=0のときのTpdの実測値

Tpd_wire_load_sim:配線負荷パターンのTpdのシミュレーション値(最適化後)

Tpd_CjSTI_load_sim:STI周囲長=0のTpdのシミュレーション値(最適化後)

【0073】

ステップA7のYESの場合、又は、ステップA8の後、拡散層負荷パターン(ゲート構成;図9〜図11参照)のTpdのゲート周囲長依存性の実測値とシミュレーション値の各傾きを計算し、各傾きが一致するか否かを判断する(図12のステップA9)。ここで、ゲート周囲長は、ゲートと隣接する拡散層の周囲の長さである。図18にTpd-ゲート周囲長依存性の実測値とシミュレーション値を示す。なお、ステップA7でSTI周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致するか否かを判断しているので、ステップA9ではゲート周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致するか否かを判断していないが、ステップA7でTpdの差分が一致するか否かを判断しない場合には、ステップA9でTpdの差分が一致するか否かを判断し、その後、差分に関してパラメータの最適化を行ってもよい(図19参照)。Tpdのゲート周囲長依存性の実測値とシミュレーション値の各傾きが一致する場合(ステップA9のYES)、終了する。

【0074】

TpdのSTI周囲長依存性の実測値とシミュレーション値の各傾きが一致しない場合(ステップA9のNO)、Tpd−ゲート本数依存性(図14、図15参照)と同様に、シミュレーション値の傾きを実測値の傾きに一致させるように拡散層ゲート周囲長容量パラメータ(Cjswg)を調整することにより、拡散層ゲート周囲長容量成分起因誤差(ΔCjswg)を最適化し(図12のステップA10)、その後、終了する。

【0075】

ステップA10において、傾きに関して、「Cjswg+Cov」を示しており、傾き誤差は「ΔCjswg_load+ΔCov_load」を示している。ゲートオーバラップ容量はゲート負荷パターン(図4、図5参照)にて最適化されたパラメータを組み込んだ状態で、傾きを一致させるように、拡散層ゲート周囲長容量パラメータ(Cjswg)を調整することにより、拡散層ゲート周囲長容量成分起因誤差(ΔCjswg)を最適化する。一方、差分に関して、傾きの線とY軸(縦軸)との交点、すなわちゲート長=0のときのTpdの値は、下記[数式7]の関係が成り立つように、シミュレーション値の差分(Cj_delta(sim))を実測値の差分(Cj_delta(meas))に一致させるように拡散層底面容量パラメータ(Cj)を調整することにより、拡散層底面容量成分起因誤差(ΔCj)を最適化するが(図19参照)、ステップA8により、ΔCjが最適化されているので、自動的に、[数式6]と[数式7]の値は一致する。

【0076】

[数式7]

Cj_delta(meas)=Tpd_wire_load_meas−Tpd_CjGate_load_meas,

Cj_delta(sim)=Tpd_wire_load_sim−Tpd_CjGate_load_sim

Cj_delta(meas)=Cj_delta(sim)

※Tpd_wire_load_meas:配線負荷パターンのTpdの実測値

Tpd_CjGate_load_meas:ゲート周囲長=0のときのTpdの実測値

Tpd_wire_load_sim:配線負荷パターンのTpdのシミュレーション値(最適化後)

Tpd_CjGate_load_sim:ゲート周囲長=0のTpdのシミュレーション値(最適化後)

【0077】

実施例1によれば、ROSC部11とそのROSC部11の各インバータ11aの出力部に接続された負荷部12のディメンジョン振り(ゲート本数、拡散層STI周囲長、拡散層ゲート周囲長)したパターンを用いて、Tpd−個数(またはディメンジョン)依存性の実測とシミュレーションの傾きを一致させるようにパラメータを最適化することにより、直接、LCRメータから容量抽出を行うことなく、Tpdの感度を用いて、間接的にパラメータを最適化することができる。また、ROSCパターンのように、実回路に近いパターンにて、パラメータを最適化することができるため、実際の回路動作時の誤差を最小限に抑えることができる。

【0078】

また、シリコンとSPICEの一致性検証に際し、Tpdにおける誤差の要因を回路特性から割り出すことが可能になり、さらにSPICEにおけるパラメータへのフィードバックも可能となる。特に、外部のファブレスメーカの採用に伴い、契約上の観点から素子の生の特性を採取することが困難になりつつある今日、本実施例は有効である。その理由は、複数通りの回路特性での測定結果の組み合わせから、Tpdに関わる素子特性の誤差(シリコンとSPICEとの間)を定量化できるからである。さらに、素子特性の採取に法的な制約が無い内部のファブレスメーカの場合であっても、Tpdの測定はアナログ的な電気測定(容量特性カーブなど)に比べて、検査TAT(Turn Around Time)の観点から有利である。

【0079】

なお、本発明の全開示(請求の範囲及び図面を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲及び図面を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0080】

10A、10B ROSCパターン

11 ROSC部

11a インバータ(プリミティブゲート回路)

12 負荷部

12a 負荷容量

21 ゲート

22、23、24、25 拡散層

26 GND配線

27 Vdd配線

28 Vin配線

29 Vout配線

30、31、32、33、34 コンタクト

35 配線

36 コンタクト

37 配線

38 コンタクト

40 ゲート

41 コンタクト

42 拡散層

43 配線

44 コンタクト

46 ソース端子

47 ドレイン端子

48 基板端子

50、52、53 拡散層

51 コンタクト

55 ゲート

【技術分野】

【0001】

本発明は、回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するために用いる半導体装置、パラメータ最適化方法、及びプログラムに関する。

【背景技術】

【0002】

MOSトランジスタを用いた半導体集積回路の設計では、シリコンウェハ上に作成されたリングオシレータ(Ring Oscillator;ROSC)パターンにより測定した伝達遅延時間(Tpd)とSPICE(Simulation Program with Integrated Circuit Emphasis)を用いてシミュレーションしたTpdとの整合検証が行われる。この整合検証を行う過程において、そのTpd誤差の要因分析をするためには、DC(直流)的な要因とAC(容量)的な要因とに分離することが不可欠となる。

【0003】

AC的な要因には、ゲート容量、ゲートオーバラップ容量、ジャンクション容量のトランジスタ部の容量成分とROSCを形成している配線容量がある。AC的な誤差を最適化するためには、これら各々の容量成分を分析した上で、誤差の起因となっている容量パラメータを最適化しなければならない。容量パラメータを測定するには、一般的には、LCRメータ(コイル(L)/コンデンサ(C)/インピーダンス(Z、R)の測定装置)などで、容量抽出パターンを用いて、直接的にゲート容量、ゲートオーバラップ容量、配線容量の測定を行い、その実測値に対して、パラメータ抽出を行っている(非特許文献1、2参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−251976号公報

【特許文献2】特開2002−261272号公報

【特許文献3】特開2000−298683号公報

【特許文献4】特開2010−10515号公報

【非特許文献】

【0005】

【非特許文献1】青木均著、外2名、「CMOSモデリング技術−SPICE用コンパクトモデリングの理論と実践」、初版、丸善、2006年1月、p.185−193。

【非特許文献2】三浦道子著、外2名、「回路シミュレーション技術とMOSFETモデリング」、リアライズ理工センター、2003年3月、p.385−390。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、LCRメータにて直接測定するには、容量値の感度を高めるために、実回路(インバータ、NAND回路、NOR回路などのプリミティブゲート回路)とは異なる大きなレイアウト構造によりパラメータ抽出を行うため、TEG(Test Element Group)面積効率が悪いことや、実回路動作時の遅延値として、正しく抽出されているかどうかを判別するには、実回路動作時の遅延値の求め、遅延量として、実測値と比較するまでわからないという問題点がある。

【0007】

また、遅延として観測された値は、それぞれの容量パラメータの合計値として観測されるので、実回路の周波数(又はTpd)として観測される値と、シミュレーション値とがずれた場合、各容量成分のうちどの容量成分がずれているのかを判定することが難しいという問題点もある。

【0008】

さらに、ROSCから観測されるTpdから容量換算するには、各容量成分の要因分離が難しいという問題がある。

【0009】

ところで、Tpd検証のシリコン特性とシミュレーション特性とのTpd誤差要因分析過程において、DC的な要因誤差、AC的な要因誤差とに分けて評価しなければ、正確にTpd誤差を最適化することができない。その中でも、AC的な要因誤差においては、トランジスタ起因のゲート容量、ゲートオーバラップ容量、ジャンクション容量の誤差や、配線起因の誤差にそれぞれ分け、パラメータの最適化をしなければならない。

【0010】

従来技術においては、Tpdを検証する上で、個々のパラメータを最適化する手法として、ROSCパターンによるDC的な要因分析法(特許文献1参照)、AC的な要因分析法(特許文献2、3参照)が開示されている。特に、AC的な要因分析法では、配線容量に特化したものが多い。また、特許文献2では、トランジスタのゲートオーバラップ容量のみに特化して議論されている。

【0011】

しかしながら、特許文献1−3に記載の手法では、トランジスタの容量成分までブレークダウンして議論されておらず、トランジスタの容量の各成分や配線容量を分離して、誤差分析することができない。

【0012】

また、特許文献4では、負荷部のコンタクト個数依存性のTpdインパクトを抽出するパターンを提案しているが、コンタクト部の容量パラメータの具体的な最適化、抽出方法については、議論されていない。

【0013】

本発明の主な課題は、トランジスタの容量の各成分や配線容量を分離してパラメータを最適化することが可能な半導体装置、パラメータ最適化方法、及びプログラムを提供することである。

【課題を解決するための手段】

【0014】

本発明の第1の視点においては、半導体装置において、MOSトランジスタから構成されたプリミティブゲート回路を奇数段でリング状に結合した第1リングオシレータ部の各前記プリミティブゲート回路の出力部と電気的に接続された第1配線を有する配線負荷パターンと、前記第1リングオシレータ部と同様な構成の第2リングオシレータ部の各プリミティブゲート回路の出力部が前記第1配線と同様な構成の第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、前記第1リングオシレータ部と同様な構成の第3リングオシレータ部の各プリミティブゲート回路の出力部が前記第1配線と同様な構成の第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、を備え、前記複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、前記複数の拡散層負荷パターンは、パターンごとに容量負荷が異なることを特徴とする。

【0015】

本発明の第2の視点においては、前記半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するパラメータ最適化方法であって、前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションする工程と、前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算する工程と、前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化する工程と、を含むことを特徴とする。

【0016】

本発明の第3の視点においては、前記半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するプログラムであって、前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションするステップ(図12のステップA2)と、前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算するステップ(図12のステップA3、A5、A7、A9)と、前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化するステップ(図12のステップA4、A6、A8、A10)と、を実行させることを特徴とする。

【発明の効果】

【0017】

本発明によれば、LCRメータ等の測定装置から直接、容量抽出を行うことなく、伝播遅延時間の感度を用いて、間接的にパラメータを最適化することができる。また、リングオシレータパターンのように、実回路に近いパターンにて、パラメータを最適化することができるため、実際の回路動作時の誤差を最小限に抑えることができる。

【図面の簡単な説明】

【0018】

【図1】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置における基本構成となる負荷部が無いROSCパターンの構成を模式的に示した(A)回路図、(B)インバータの平面図である。

【図2】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置における基本構成となる負荷部があるROSCパターンの構成を模式的に示した(A)回路図、(B)インバータの平面図である。

【図3】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける配線負荷パターンの構成を模式的に示した部分平面図である。

【図4】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおけるゲート負荷パターン(負荷本数1本)の構成を模式的に示した部分平面図である。

【図5】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおけるゲート負荷パターン(負荷本数3本)の構成を模式的に示した部分平面図である。

【図6】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン1)の構成を模式的に示した部分平面図である。

【図7】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン2)の構成を模式的に示した部分平面図である。

【図8】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン3)の構成を模式的に示した部分平面図である。

【図9】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン1)の構成を模式的に示した部分平面図である。

【図10】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン2)の構成を模式的に示した部分平面図である。

【図11】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン3)の構成を模式的に示した部分平面図である。

【図12】本発明の実施例1に係るパラメータ最適化方法を模式的に示したフローチャートである。

【図13】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて負荷部が無い場合、及び、配線負荷パターンを有する場合のそれぞれのTpdの実測値及びシミュレーション値を模式的に示したグラフである。

【図14】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいてゲート負荷パターンを有する場合の条件1でのTpdの実測値及びシミュレーション値(最適化前と後)のゲート負荷本数依存性を模式的に示したグラフである。

【図15】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいてゲート負荷パターンを有する場合の条件2でのTpdの実測値及びシミュレーション値(最適化前と後)のゲート負荷本数依存性を模式的に示したグラフである。

【図16】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(STI構成)を有する場合のTpdの実測値及びシミュレーション値(最適化前と後)のSTI周囲長依存性を模式的に示したグラフである。

【図17】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(STI構成)と配線負荷パターンとのTpdとの関係を模式的に示したグラフである。

【図18】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(ゲート構成)を有する場合のTpdの実測値及びシミュレーション値(最適化前と後)のゲート周囲長依存性を模式的に示したグラフである。

【図19】本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(ゲート構成)と配線負荷パターンとのTpdとの関係を模式的に示したグラフである。

【発明を実施するための形態】

【0019】

本発明の実施形態1に係る半導体装置では、MOSトランジスタから構成されたプリミティブゲート回路(図2の11a)を奇数段でリング状に結合した第1リングオシレータ部(図2の11)の各前記プリミティブゲート回路の出力部と電気的に接続された第1配線(図3の35〜38)を有する配線負荷パターン(図3参照)と、前記第1リングオシレータ部と同様な構成の第2リングオシレータ部(図2の11)の各プリミティブゲート回路(図2の11a)の出力部が前記第1配線と同様な構成の第2配線(図4、図5の35〜38)を介して負荷部(図4、図5の12)となるMOSトランジスタのゲート(図4、図5の40)に電気的に接続された複数のゲート負荷パターン(図4、図5参照)と、前記第1リングオシレータ部と同様な構成の第3リングオシレータ部(図2の11)の各プリミティブゲート回路(図2の11a)の出力部が前記第1配線と同様な構成の第3配線(図6〜図11の35〜38)を介して負荷部となる拡散層(図6〜図11の50又は52若しくは53)に電気的に接続された複数の拡散層負荷パターン(図6〜図11参照)と、を備え、前記複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、前記複数の拡散層負荷パターンは、パターンごとに容量負荷が異なる。

【0020】

本発明の前記半導体装置においては、前記複数のゲート負荷パターンは、パターンごとに前記第2配線に電気的に接続される前記ゲートの個数が異なることが好ましい。

【0021】

本発明の前記半導体装置においては、前記ゲート負荷パターンは、前記負荷部となる前記MOSトランジスタのソース、ドレイン及び基板のそれぞれの端子に任意の電位を印加することができるように構成されていることが好ましい。

【0022】

本発明の前記半導体装置においては、前記複数の拡散層負荷パターンは、互いに前記第3配線に電気的に接続される前記拡散層の個数が異なることが好ましい。

【0023】

本発明の前記半導体装置においては、前記複数の拡散層負荷パターンは、前記負荷部となる前記拡散層の周囲の領域にSTIが配されているSTI構成と、前記負荷部となる前記拡散層の周囲の領域にゲートが配されているゲート構成と、を有することが好ましい。

【0024】

本発明の前記半導体装置においては、前記複数の拡散層負荷パターンにおける前記負荷部の基板の電位は、前記第3リングオシレータ部の基板電位と同じ電位であり、

前記複数の拡散層負荷パターンにおける前記ゲート構成の前記ゲートは、任意の電位を印加することができるように構成されていることが好ましい。

【0025】

本発明の実施形態2に係るパラメータ最適化方法では、前記半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するパラメータ最適化方法であって、前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションする工程(図12のステップA2)と、前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算する工程(図12のステップA3、A5、A7、A9)と、前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化する工程(図12のステップA4、A6、A8、A10)と、を含む。

【0026】

本発明の前記パラメータ最適化方法においては、前記伝播遅延時間を実測及びシミュレーションする工程では、前記ゲート負荷パターンの前記負荷部のゲート容量又はゲートオーバラップ容量による伝播遅延時間を実測及びシミュレーションすることが好ましい。

【0027】

本発明の前記パラメータ最適化方法において、前記傾きを計算する工程では、前記ゲート負荷パターンに係る前記伝播遅延時間のゲート個数依存性の実測値及びシミュレーション値の傾きを計算することが好ましい。

【0028】

本発明の前記パラメータ最適化方法においては、前記傾きを計算する工程では、前記拡散層負荷パターンに係る前記伝播遅延時間の前記拡散層がSTIと接するSTI周囲長、又は、前記拡散層が前記ゲートと隣接するゲート周囲長の依存性の実測値及びシミュレーション値の傾きを計算することが好ましい。

【0029】

本発明の前記パラメータ最適化方法においては、前記STI周囲長又は前記ゲート周囲長が0のときの伝播遅延時間と、前記配線負荷パターンの伝播遅延時間との実測値とシミュレーション値の差分が一致しないときに、前記シミュレーション値の差分を前記実測値の差分に一致させるようにようにして、他の所定のパラメータを最適化する工程を含むことが好ましい。

【0030】

本発明の実施形態3に係るプログラムでは、前記半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するプログラムであって、前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションするステップと、前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算するステップと、前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化するステップと、を実行させる。

【0031】

なお、本出願において図面参照符号を付している場合は、それらは、専ら理解を助けるためのものであり、図示の態様に限定することを意図するものではない。

【実施例1】

【0032】

本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置について図面を用いて説明する。図1は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置における基本構成となる負荷部が無いROSCパターンの構成を模式的に示した(A)回路図、(B)インバータの平面図である。図2は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置における基本構成となる負荷部があるROSCパターンの構成を模式的に示した(A)回路図、(B)インバータの平面図である。図3は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける配線負荷パターンの構成を模式的に示した部分平面図である。図4は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおけるゲート負荷パターン(負荷本数1本)の構成を模式的に示した部分平面図である。図5は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおけるゲート負荷パターン(負荷本数3本)の構成を模式的に示した部分平面図である。図6は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン1)の構成を模式的に示した部分平面図である。図7は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン2)の構成を模式的に示した部分平面図である。図8は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(STI構成;パターン3)の構成を模式的に示した部分平面図である。図9は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン1)の構成を模式的に示した部分平面図である。図10は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン2)の構成を模式的に示した部分平面図である。図11は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおける拡散層負荷パターン(ゲート構成;パターン3)の構成を模式的に示した部分平面図である。

【0033】

パラメータ最適化方法は、回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化する方法である。パラメータ最適化方法は、半導体装置に電気的に接続された測定装置(例えば、LCRメータ等)を用いて伝達遅延時間(Tpd)を測定し、半導体装置におけるMOSトランジスタ部と同じモデルについて回路シミュレーションプログラム(例えば、SPICE等)を実行するコンピュータを用いてTpdをシミュレーションすることによって、当該コンピュータにて、Tpdの整合検証を行い、整合していなければ回路シミュレーションソフトにおけるMOSトランジスタのモデルのパラメータを最適化する。このようなパラメータ最適化方法を実施するために、以下のような半導体装置(モデル)が用いられる。

【0034】

半導体装置は、半導体集積回路の動作速度を評価するためのテスト回路として負荷部の無いリングオシレータ部11(ROSC部)のみからなるROSCパターン10Aを有する(図1(A)参照)。ROSCパターン10Aは、MOSトランジスタ(Nch型トランジスタ、Pch型トランジスタ)から構成されたインバータ11a(その他のNAND回路、NOR回路などのプリミティブゲート回路でも可)を多段(奇数段;通常は47段)でリング状に結合した構成となっている。インバータ11aは、電圧が入力されるVin配線28がコンタクト34を介してNch型トランジスタ及びPch型トランジスタの共通のゲート21と電気的に接続され、Nch型トランジスタではゲート21の両側にソース/ドレイン領域となる拡散層22、23が形成され、Pch型トランジスタではゲート21の両側にソース/ドレイン領域となる拡散層24、25が形成され、拡散層22がコンタクト30を介してGND配線26に電気的に接続され、拡散層24がコンタクト32を介してVdd配線27に電気的に接続され、拡散層23、25がそれぞれコンタクト31、33を介して共通のVout配線29に電気的に接続されている(図1(B)参照)。

【0035】

また、半導体装置は、ROSCパターン10Aとは別に、ROSCパターン10AにおけるDC特性の合わせ込みを行うためのモデルとして、リングオシレータ部11に負荷部12を接続したROSCパターン10Bを有する(図2(A)参照)。ROSCパターン10Bは、図1(A)のROSCパターン10AのROSC部11と同様な構成のROSC部11を有し、ROSC部11におけるか各インバータ11aのVout配線29がコンタクト36を介して配線35に電気的にされ(図2(B)参照)、配線35が負荷部12における負荷容量12aの一端に電気的に接続され、負荷容量12aの他端がGNDに電気的に接続されている。負荷容量12aには、複数のモデルがあり、配線負荷パターン(図3参照)と、ゲート負荷パターン(図4、図5参照)と、拡散層負荷パターン(図6〜図11参照)と、がある。

【0036】

図3の配線負荷パターンは、ゲート負荷パターン(図4、図5参照)及び拡散層負荷パターン(図6〜図11参照)での配線容量による誤差を排除するためのものであり、ゲート負荷パターン及び拡散層負荷パターンの配線部分(配線35、コンタクト38、配線37)と同じ構成となっている。配線負荷パターンでは、各インバータ11aのVout配線29から負荷部(図2(A)の12)に引き出された配線35がコンタクト38を介して配線37と電気的に接続された構成となっている。配線負荷パターンは、ゲート負荷パターン及び拡散層負荷パターンの容量負荷パターンのフレームワークとなっており、配線37にコンタクトを介してゲート又は拡散層に接続するのみで、ゲート負荷パターン及び拡散層負荷パターンとすることができるという特徴がある。なお、配線容量は、一般的に、LPE(Layout Parameter Extraction)を使用することで抽出できるが、図3の配線負荷パターンでは、ウェハごとの太り、細り量をTpdとして計測できる。

【0037】

図4、図5のゲート負荷パターンは、負荷部12の配線37とMOSトランジスタのゲート40とがコンタクト41を介して接続された負荷本数を変更したパターン(図4では1本、図5では3本)となっている。ゲート負荷パターンでは、ゲート40の両側に拡散層42が配されたMOSトランジスタがゲート長方向に並んで配されており、所定のゲート40がコンタクト41を介して配線37に電気的に接続されており、各拡散層42がコンタクト44を介して配線43に電気的に接続されている。MOSトランジスタは、NMOSまたは、PMOSのどちらか一方である。配線43のうちソースに係る拡散層42と電気的に接続されている配線43は、ソース端子46に電気的に接続されている。配線43のうちドレインに係る拡散層42と電気的に接続されている配線43は、ドレイン端子47に電気的に接続されている。MOSトランジスタの基板は、基板端子48(ボディ端子)と電気的に接続されている。ソース端子46、ドレイン端子47、基板端子48は、それぞれ任意の電位が与えられるように、回路上、独立した端子となっている。

【0038】

図6〜図11の拡散層負荷パターン(ジャンクション容量負荷パターン)は、図6〜図8のSTI(Shallow Trench Isolation;素子分離)構成と、図9〜図11のゲート構成と、の2種類の構成がある。

【0039】

図6〜図8のSTI構成の拡散層負荷パターンは、複数の拡散層50、52、53が並んでおり、各拡散層50、52、53がSTI(図示せず)に囲まれた構成となっており、各拡散層50、52、53がコンタクト51を介して配線37に電気的に接続されている。図6の各拡散層50は、1本のコンタクト51と接続されており、拡散層52よりも短い。図7の各拡散層52は、2本のコンタクト51と接続されており、拡散層50よりも長く、拡散層53よりも短い。図8の各拡散層53は、3本のコンタクト51と接続されており、拡散層52よりも長い。図6の拡散層50のトータルの拡散層面積は、図7の拡散層52のトータルの拡散層面積、及び、図8の拡散層53のトータルの拡散層面積と一致するように設定されている。図6〜図8のSTI構成の拡散層負荷パターンは、STIと接する拡散層の周囲の長さとなるSTI周囲長を変更したパターンとなっている。STI構成の拡散層負荷パターンにおける基板電位は、ROSC部(図2(A)の11)の基板電位と同電位であり、基板がN+拡散層で形成された場合には、基板電位はGNDとなり、基板がP+拡散層で形成された場合には、基板電位はVddとなる。

【0040】

図9〜図11のゲート構成の拡散層負荷パターンは、複数の拡散層50、52、53が並んでおり、各拡散層50、52、53がゲート55に囲まれた構成となっており、各拡散層50、52、53がコンタクト51を介して配線37に電気的に接続されている。なお、図9〜図11の拡散層50、52、53は、図6〜図8の拡散層50、52、53の構成と同様である。図9の各拡散層50は、1本のコンタクト51と接続されており、拡散層52よりも短い。図10の各拡散層52は、2本のコンタクト51と接続されており、拡散層50よりも長く、拡散層53よりも短い。図11の各拡散層53は、3本のコンタクト51と接続されており、拡散層52よりも長い。図9の拡散層50のトータルの拡散層面積は、図10の拡散層52のトータルの拡散層面積、及び、図11の拡散層53のトータルの拡散層面積と一致するように設定されている。図9〜図11のゲート構成の拡散層負荷パターンは、ゲート55と隣接する拡散層の周囲の長さとなるゲート周囲長を変更したパターンとなっている。ゲート構成の拡散層負荷パターンにおける基板電位は、ROSC部(図2(A)の11)の基板電位と同電位であり、基板がN+拡散層で形成された場合には、基板電位はGNDとなり、基板がP+拡散層で形成された場合には、基板電位は、Vddとなる。負荷部(図2(A)の12)の拡散層50、52、53と電気的に接続されるゲート端子(図示せず)は、任意の電位を与えられるように独立した端子となっている。

【0041】

次に、本発明の実施例1に係るパラメータ最適化方法について図面を用いて説明する。図12は、本発明の実施例1に係るパラメータ最適化方法を模式的に示したフローチャートである。図13は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて負荷部が無い場合、及び、配線負荷パターンを有する場合のそれぞれの場合のTpdの実測値及びシミュレーション値を模式的に示したグラフである。図14は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいてゲート負荷パターンを有する場合の条件1でのTpdの実測値及びシミュレーション値(最適化前と後)のゲート負荷本数依存性を模式的に示したグラフである。図15は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいてゲート負荷パターンを有する場合の条件2でのTpdの実測値及びシミュレーション値(最適化前と後)のゲート負荷本数依存性を模式的に示したグラフである。図16は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(STI構成)を有する場合のTpdの実測値及びシミュレーション値(最適化前と後)のSTI周囲長依存性を模式的に示したグラフである。図17は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(STI構成)と配線負荷パターンとのTpdとの関係を模式的に示したグラフである。図18は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(ゲート構成)を有する場合のTpdの実測値及びシミュレーション値(最適化前と後)のゲート周囲長依存性を模式的に示したグラフである。図19は、本発明の実施例1に係るパラメータ最適化方法で用いられる半導体装置のROSCパターンにおいて拡散層負荷パターン(ゲート構成)と配線負荷パターンとのTpdとの関係を模式的に示したグラフである。

【0042】

まず、DC特性の最適化フローとして、ROSCパターン(図1(A)参照)のDC特性を再現するモデルを用意する(図12のステップA1)。ここでは、ROSCパターン(図1(A)の10A)における1つのNMOS、PMOSのそれぞれの端子を抜き出したパターンよりDC特性を測定し、DCパラメータの最適化を行う。具体的には、ドレイン電流Idとゲート電圧VgとのIdVg特性、ドレイン電流Idとドレイン電圧VdとのIdVd特性などの基本特性を測定し、モデルパラメータに反映させる。

【0043】

次に、各バイアス条件でのROSCパターン(図1(A)、図2(A)、図3〜図11参照)の伝播遅延時間(Tpd)を測定(実測、シミュレーション)する(図12のステップA2)。なお、シミュレーションでは、DC測定結果を再現するようにパラメータを調整したモデルを用いる。

【0044】

ここで、負荷部の無いROSCパターン(図1(A)参照)、配線負荷パターン(図3参照)、及び、拡散層負荷パターンのSTI構成パターン(図6〜図8参照)では、基板がN+拡散層で形成された場合には、基板電位をGNDに固定し、基板がP+拡散層で形成された場合には、基板電位をVddに固定して、Tpdの測定を行う。

【0045】

また、ゲート負荷パターン(図4、図5参照)は、負荷部12のトランジスタの各端子が、任意に変更できるパターンであるので、ゲート容量捕捉することを目的とした評価の場合、負荷部12のトランジスタのソース端子46、ドレイン端子47、基板端子48を−Vdd(もしくは、チャネルが形成された状態のバイアス条件)にて固定して、Tpdの測定を行う(条件1)。一方、ゲートオーバラップ容量を捕捉する評価を目的とした場合、ソース端子46、ドレイン端子47をVdd、基板端子48をGND(もしくは、チャネルが形成されないバイアス条件)に固定して、Tpdの測定を行う(条件2)。

【0046】

また、拡散層負荷パターン(ゲート構成)(図9〜図11参照)では、負荷部のゲート55に係るゲート電位をGND(もしくは、チャネルが形成されないバイアス条件)に固定して、Tpdの測定を行う。

【0047】

次に、各ROSCパターン(図1(A)、図2(A)、図3〜図11参照)にて得られたTpdの実測値とシミュレーション値との誤差を計算し、誤差があれば回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化する(図12のステップA3〜ステップA10)。各パターンのTpdの実測値とシミュレーション値との誤差(Tpd誤差)は、[数式1]〜[数式5]の関係となる。

【0048】

負荷無しのROSCパターン(図1(A)参照)のTpd誤差(ΔTpd_ring)は、[数式1]の関係となる。

【0049】

[数式1]

ΔTpd_ring=Tpd_ring_meas−Tpd_ring_sim=ΔCGate+ΔCjtotal+ΔWire_ring

※Tpd_ring_meas:負荷無しのROSCパターンのTpdの測定値

Tpd_ring_sim:負荷無しのROSCパターンのTpdのシミュレーション値

ΔCGate=ΔCg+ΔCov

ΔCGate:負荷無しのROSCパターンのゲート負荷容量起因誤差

ΔCg:ゲート容量成分起因誤差

ΔCov:ゲートオーバラップ容量成分起因誤差

ΔCjtotal=ΔCj+ΔCjsw+ΔCjswg

ΔCjtotal:負荷無しのROSCパターンの拡散層負荷容量起因誤差

ΔCj:拡散層底面容量成分起因誤差

ΔCjsw:拡散層STI周囲長容量成分起因誤差

ΔCjswg:拡散層ゲート周囲長容量成分起因誤差

ΔWire_ring:負荷無しのROSCパターンの配線負荷起因誤差

【0050】

配線負荷パターン(図3参照)のTpd誤差(ΔTpd_wire_load)は、[数式2]の関係となる。

【0051】

[数式2]

ΔTpd_wire_load=Tpd_wire_load_meas−Tpd_wire_load_sim=ΔTpd_ring−ΔWire_load

※Tpd_wire_load_meas:配線負荷パターンのTpdの測定値

Tpd_wire_load_sim:配線負荷パターンのTpdのシミュレーション値

ΔTpd_ring:負荷無しのROSCパターンのTpd誤差

ΔWire_load:負荷部の配線負荷起因誤差

【0052】

ゲート負荷パターン(図4、図5参照)のTpd誤差(ΔTpd_CGate_load)は、[数式3]の関係となる。

【0053】

[数式3]

ΔTpd_CGate_load=Tpd_CGate_load_meas−Tpd_CGate_load_sim

=ΔTpd_wire_load+ΔCGate_load

※Tpd_CGate_load_meas:ゲート負荷パターンのTpdの測定値

Tpd_CGate_load_sim:ゲート負荷パターンのTpdのシミュレーション値

ΔTpd_wire_load:配線負荷パターンのTpd誤差

ΔCGate_load:ゲート負荷パターンのゲート負荷容量起因誤差

【0054】

なお、ゲート負荷パターンのゲート負荷容量起因誤差(ΔCGate_load)が最適化されれば、負荷無しのROSCパターンのゲート負荷容量起因誤差(ΔCGate)も同時に誤差がなくなる。

【0055】

拡散層負荷パターン(STI構成)(図6〜図8参照)のTpd誤差(ΔTpd_CjSTI_load)は、[数式4]の関係となる。

【0056】

[数式4]

ΔTpd_CjSTI_load=Tpd_Cj_load_meas−Tpd_Cj_load_sim

=ΔTpd_wire_load+ΔCjsw_load+ΔCj_load

※Tpd_Cj_load_meas:拡散層負荷パターン(STI構成)のTpdの測定値

Tpd_Cj_load_sim:拡散層負荷パターン(STI構成)のTpdのシミュレーション値

ΔTpd_wire_load:配線負荷パターンのTpd誤差

ΔCjsw_load:拡散層負荷パターン(STI構成)の拡散層STI周囲長容量成分起因誤差

ΔCj_load:拡散層負荷パターン(STI構成)の拡散層底面容量成分起因誤差

【0057】

なお、拡散層負荷パターン(STI構成)の拡散層STI周囲長成分起因誤差(ΔCjsw_load)及び拡散層底面容量成分起因誤差(ΔCj_load)の誤差が最適化されれば、負荷無しのROSCパターンの拡散層STI周囲長容量成分起因誤差(ΔCjsw)及び拡散層底面容量成分起因誤差(ΔCj)も同時に誤差はなくなる。

【0058】

拡散層負荷パターン(ゲート構成)(図9〜図11参照)のTpd誤差(ΔTpd_Cjate_load)は、[数式5]の関係となる。

【0059】

[数式5]

ΔTpd_Cjate_load=Tpd_Cj_load_meas−Tpd_Cj_load_sim

=ΔTpd_wire_load+ΔCjswg_load+ΔCj_load+ΔCov_load

※Tpd_Cj_load_meas:拡散層負荷パターン(ゲート構成)のTpdの測定値

Tpd_Cj_load_sim:拡散層負荷パターン(ゲート構成)のTpdのシミュレーション値

ΔTpd_wire_load:配線負荷パターンのTpd誤差

ΔCjswg_load:拡散層負荷パターン(ゲート構成)の拡散層ゲート周囲長容量成分起因誤差

ΔCj_load:拡散層負荷パターン(ゲート構成)の拡散層底面容量成分起因誤差

ΔCov_load:拡散層負荷パターン(ゲート構成)のゲートオーバラップ容量成分起因誤差

【0060】

なお、拡散層負荷パターン(ゲート構成)の拡散層底面容量成分起因誤差(ΔCj_load)が最適化されるとともに、拡散層負荷パターン(ゲート構成)のゲートオーバラップ容量成分起因誤差(ΔCov_load)が最適化されていれば、拡散層負荷パターンの固有の誤差は拡散層負荷パターン(ゲート構成)の拡散層ゲート周囲長容量成分起因誤差(ΔCjswg_load)のみとなるので、拡散層負荷パターン(ゲート構成)の拡散層ゲート周囲長容量成分起因誤差(ΔCjswg_load)が最適化されれば、負荷無しのROSCパターンの拡散層ゲート周囲長容量成分起因誤差(ΔCjswg)の誤差もなくなる。

【0061】

また、各ROSCパターン(図1(A)、図2(A)、図3〜図11参照)のROSC部(図1(A)、図2(A)の11)で形成されているトランジスタと、負荷部(図2(A)の12)のトランジスタ、拡散層、ゲートの形成条件は、同一のプロセス条件で形成されていることが前提である。

【0062】

負荷無しのROSCパターン(図1(A)参照)のTpdの実測値とシミュレーション値、及び、配線負荷パターン(図2(A)、図3参照)のTpdの実測値とシミュレーション値を図13に示す。最終的な目標は、負荷無しのROSCパターン(図1(A)参照)のTpdの実測値(Tpd_ring_meas)とシミュレーション値(Tpd_ring_sim)の誤差(図13のΔTpd_ring)を「ゼロ」にすることにある。各パターンの誤差は、[数式1]、[数式2]に示した通りの関係が成り立つ。これら、ΔTpd_ringは、各負荷パターンのTpd−負荷依存性(漸近線)の傾きを一致させるようにパラメータを調整することで、簡便にROSC部(図1(A)、図2(A)の11)の誤差をなくすことができる。

【0063】

以下、具体的な各負荷パターン(図2(A)、図3〜図11参照)でのパラメータ最適化方法(図12のステップA3〜ステップA10)の詳細を述べる。

【0064】

ステップA2の後、ゲート負荷パターン(図4、図5参照)のTpdのゲート本数依存性の実測値とシミュレーション値の各傾きを条件1で計算し、各傾きが一致するか否かを判断する(図12のステップA3)。なお、条件1は、負荷トランジスタのチャネルが形成されたバイアス条件であり、負荷トランジスタがNMOSの場合にはソース端子46、ドレイン端子47、基板端子48は−Vdd電位に固定され、負荷トランジスタがPMOSの場合にはソース端子46、ドレイン端子47、基板端子48はVdd電位に固定される。図14に条件1でのTpd−ゲート本数依存性の実測値とシミュレーション値を示す。この傾きのズレは、ゲート容量パラメータ(Cg)の実測値とシミュレーション値の誤差(ΔCg)を示している。Tpdのゲート本数依存性の実測とシミュレーションの各傾きが一致している場合(ステップA3のYES)、ステップA5に進む。

【0065】

Tpdのゲート本数依存性の実測値とシミュレーション値の各傾きが一致していない場合(ステップA3のNO)、シミュレーション値の傾きを実測値の傾きに一致させるようにゲート容量パラメータ(Cg)にて調整することにより、ゲート容量成分起因誤差(ΔCg)を最適化する(図12のステップA4)。

【0066】

ステップA3のYESの場合、又は、ステップA4の後、ゲート負荷パターン(図4、図5参照)のTpdのゲート本数依存性の実測値とシミュレーション値の各傾きを条件2で計算し、各傾きが一致するか否かを判断する(図12のステップA5)。なお、条件2は、負荷トランジスタのチャネルが形成されないバイアス条件であり、負荷トランジスタがNMOSの場合にはソース端子46及びドレイン端子47はVdd電位に固定され、かつ、基板端子48はGND電位に固定され、負荷トランジスタがPMOSの場合にはソース端子46及びドレイン端子47は−Vdd電位に固定され、かつ、基板端子48はGND電位に固定される。図15に条件2でのTpd−ゲート本数依存性の実測値とシミュレーション値を示す。この傾きのズレは、ゲートオーバラップ容量パラメータ(Cov)の誤差(ΔCov)を示している。Tpdのゲート本数依存性の実測値とシミュレーション値の各傾きが一致している場合(ステップA5のYES)、ステップA7に進む。

【0067】

Tpdのゲート本数依存性の実測値とシミュレーション値の各傾きが一致していない場合(ステップA5のNO)、シミュレーション値の傾きを実測値の傾きに一致させるようにゲートオーバラップ容量パラメータ(Cov)を調整することにより、ゲートオーバラップ容量成分起因誤差(ΔCov)を最適化する(図12のステップA6)。

【0068】

ステップA5のYESの場合、又は、ステップA6の後、拡散層負荷パターン(STI構成;図6〜図8参照)のTpdのSTI周囲長依存性の実測値とシミュレーション値の各傾きを計算し、各傾き、及び、STI周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致するか否かを判断する(図12のステップA7)。ここで、STI周囲長は、STIと接する拡散層の周囲の長さである。図16、図17にTpd-STI周囲長依存性の実測値とシミュレーション値を示す。TpdのSTI周囲長依存性の実測値とシミュレーション値の各傾き、及び、STI周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致する場合(ステップA7のYES)、ステップA9に進む。

【0069】

TpdのSTI周囲長依存性の実測値とシミュレーション値の各傾き、及び、STI周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致しない場合(ステップA7のNO)、以下のようにしてパラメータを最適化する(図12のステップA8)。

【0070】

傾きのズレに関しては、Tpd−ゲート本数依存性(図14、図15参照)と同様に、シミュレーション値の傾きを実測値の傾きに一致させるように拡散層STI周囲長容量パラメータ(Cjsw)を調整することにより、拡散層STI周囲長容量成分起因誤差(ΔCjsw)を最適化する(図16参照)。なお、差分のみが一致していない場合は、ΔCjswの最適化を省略することができる。

【0071】

また、差分に関しては、傾きの線とY軸(縦軸)との交点(STI周囲長=0)は、拡散層底面容量パラメータ(Cj)を示しているので、STI周囲長=0のときのTpdは、下記[数式6]の関係が成り立つように、シミュレーション値の差分(Cj_delta(sim))を実測値の差分(Cj_delta(meas))に一致させるように拡散層底面容量パラメータ(Cj)を調整することにより、拡散層底面容量成分起因誤差(ΔCj)を最適化する(図17参照)。なお、傾きのみが一致していない場合は、ΔCjの最適化を省略することができる。

【0072】

[数式6]

Cj_delta(meas)=Tpd_wire_load_meas−Tpd_CjSTI_load_meas

Cj_delta(sim)=Tpd_wire_load_sim−Tpd_CjSTI_load_sim

Cj_delta(meas)=Cj_delta(sim)

※Tpd_wire_load_meas:配線負荷パターンのTpdの実測値

Tpd_CjSTI_load_meas:STI周囲長=0のときのTpdの実測値

Tpd_wire_load_sim:配線負荷パターンのTpdのシミュレーション値(最適化後)

Tpd_CjSTI_load_sim:STI周囲長=0のTpdのシミュレーション値(最適化後)

【0073】

ステップA7のYESの場合、又は、ステップA8の後、拡散層負荷パターン(ゲート構成;図9〜図11参照)のTpdのゲート周囲長依存性の実測値とシミュレーション値の各傾きを計算し、各傾きが一致するか否かを判断する(図12のステップA9)。ここで、ゲート周囲長は、ゲートと隣接する拡散層の周囲の長さである。図18にTpd-ゲート周囲長依存性の実測値とシミュレーション値を示す。なお、ステップA7でSTI周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致するか否かを判断しているので、ステップA9ではゲート周囲長が0のときのTpdと配線負荷パターン(図3、図4参照)のTpdとの差分が一致するか否かを判断していないが、ステップA7でTpdの差分が一致するか否かを判断しない場合には、ステップA9でTpdの差分が一致するか否かを判断し、その後、差分に関してパラメータの最適化を行ってもよい(図19参照)。Tpdのゲート周囲長依存性の実測値とシミュレーション値の各傾きが一致する場合(ステップA9のYES)、終了する。

【0074】

TpdのSTI周囲長依存性の実測値とシミュレーション値の各傾きが一致しない場合(ステップA9のNO)、Tpd−ゲート本数依存性(図14、図15参照)と同様に、シミュレーション値の傾きを実測値の傾きに一致させるように拡散層ゲート周囲長容量パラメータ(Cjswg)を調整することにより、拡散層ゲート周囲長容量成分起因誤差(ΔCjswg)を最適化し(図12のステップA10)、その後、終了する。

【0075】

ステップA10において、傾きに関して、「Cjswg+Cov」を示しており、傾き誤差は「ΔCjswg_load+ΔCov_load」を示している。ゲートオーバラップ容量はゲート負荷パターン(図4、図5参照)にて最適化されたパラメータを組み込んだ状態で、傾きを一致させるように、拡散層ゲート周囲長容量パラメータ(Cjswg)を調整することにより、拡散層ゲート周囲長容量成分起因誤差(ΔCjswg)を最適化する。一方、差分に関して、傾きの線とY軸(縦軸)との交点、すなわちゲート長=0のときのTpdの値は、下記[数式7]の関係が成り立つように、シミュレーション値の差分(Cj_delta(sim))を実測値の差分(Cj_delta(meas))に一致させるように拡散層底面容量パラメータ(Cj)を調整することにより、拡散層底面容量成分起因誤差(ΔCj)を最適化するが(図19参照)、ステップA8により、ΔCjが最適化されているので、自動的に、[数式6]と[数式7]の値は一致する。

【0076】

[数式7]

Cj_delta(meas)=Tpd_wire_load_meas−Tpd_CjGate_load_meas,

Cj_delta(sim)=Tpd_wire_load_sim−Tpd_CjGate_load_sim

Cj_delta(meas)=Cj_delta(sim)

※Tpd_wire_load_meas:配線負荷パターンのTpdの実測値

Tpd_CjGate_load_meas:ゲート周囲長=0のときのTpdの実測値

Tpd_wire_load_sim:配線負荷パターンのTpdのシミュレーション値(最適化後)

Tpd_CjGate_load_sim:ゲート周囲長=0のTpdのシミュレーション値(最適化後)

【0077】

実施例1によれば、ROSC部11とそのROSC部11の各インバータ11aの出力部に接続された負荷部12のディメンジョン振り(ゲート本数、拡散層STI周囲長、拡散層ゲート周囲長)したパターンを用いて、Tpd−個数(またはディメンジョン)依存性の実測とシミュレーションの傾きを一致させるようにパラメータを最適化することにより、直接、LCRメータから容量抽出を行うことなく、Tpdの感度を用いて、間接的にパラメータを最適化することができる。また、ROSCパターンのように、実回路に近いパターンにて、パラメータを最適化することができるため、実際の回路動作時の誤差を最小限に抑えることができる。

【0078】

また、シリコンとSPICEの一致性検証に際し、Tpdにおける誤差の要因を回路特性から割り出すことが可能になり、さらにSPICEにおけるパラメータへのフィードバックも可能となる。特に、外部のファブレスメーカの採用に伴い、契約上の観点から素子の生の特性を採取することが困難になりつつある今日、本実施例は有効である。その理由は、複数通りの回路特性での測定結果の組み合わせから、Tpdに関わる素子特性の誤差(シリコンとSPICEとの間)を定量化できるからである。さらに、素子特性の採取に法的な制約が無い内部のファブレスメーカの場合であっても、Tpdの測定はアナログ的な電気測定(容量特性カーブなど)に比べて、検査TAT(Turn Around Time)の観点から有利である。

【0079】

なお、本発明の全開示(請求の範囲及び図面を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲及び図面を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0080】

10A、10B ROSCパターン

11 ROSC部

11a インバータ(プリミティブゲート回路)

12 負荷部

12a 負荷容量

21 ゲート

22、23、24、25 拡散層

26 GND配線

27 Vdd配線

28 Vin配線

29 Vout配線

30、31、32、33、34 コンタクト

35 配線

36 コンタクト

37 配線

38 コンタクト

40 ゲート

41 コンタクト

42 拡散層

43 配線

44 コンタクト

46 ソース端子

47 ドレイン端子

48 基板端子

50、52、53 拡散層

51 コンタクト

55 ゲート

【特許請求の範囲】

【請求項1】

MOSトランジスタから構成されたプリミティブゲート回路を奇数段でリング状に結合した第1リングオシレータ部の各前記プリミティブゲート回路の出力部と電気的に接続された第1配線を有する配線負荷パターンと、

前記第1リングオシレータ部と同様な構成の第2リングオシレータ部の各プリミティブゲート回路の出力部が前記第1配線と同様な構成の第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、

前記第1リングオシレータ部と同様な構成の第3リングオシレータ部の各プリミティブゲート回路の出力部が前記第1配線と同様な構成の第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、

を備え、

前記複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、

前記複数の拡散層負荷パターンは、パターンごとに容量負荷が異なることを特徴とする半導体装置。

【請求項2】

前記複数のゲート負荷パターンは、パターンごとに前記第2配線に電気的に接続される前記ゲートの個数が異なることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記ゲート負荷パターンは、前記負荷部となる前記MOSトランジスタのソース、ドレイン及び基板のそれぞれの端子に任意の電位を印加することができるように構成されていることを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記複数の拡散層負荷パターンは、互いに前記第3配線に電気的に接続される前記拡散層の個数が異なることを特徴とする請求項1乃至3のいずれか一に記載の半導体装置。

【請求項5】

前記複数の拡散層負荷パターンは、前記負荷部となる前記拡散層の周囲の領域にSTIが配されているSTI構成と、前記負荷部となる前記拡散層の周囲の領域にゲートが配されているゲート構成と、を有することを特徴とする請求項1乃至4のいずれか一に記載の半導体装置。

【請求項6】

前記複数の拡散層負荷パターンにおける前記負荷部の基板の電位は、前記第3リングオシレータ部の基板電位と同じ電位であり、

前記複数の拡散層負荷パターンにおける前記ゲート構成の前記ゲートは、任意の電位を印加することができるように構成されていることを特徴とする請求項5記載の半導体装置。

【請求項7】

請求項1乃至6に記載の半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するパラメータ最適化方法であって、

前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションする工程と、

前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算する工程と、

前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化する工程と、

を含むことを特徴とするパラメータ最適化方法。

【請求項8】

前記伝播遅延時間を実測及びシミュレーションする工程では、前記ゲート負荷パターンの前記負荷部のゲート容量又はゲートオーバラップ容量による伝播遅延時間を実測及びシミュレーションすることを特徴とする請求項7記載のパラメータ最適化方法。

【請求項9】

前記傾きを計算する工程では、前記ゲート負荷パターンに係る前記伝播遅延時間のゲート個数依存性の実測値及びシミュレーション値の傾きを計算することを特徴とする請求項7又は8記載のパラメータ最適化方法。

【請求項10】

前記傾きを計算する工程では、前記拡散層負荷パターンに係る前記伝播遅延時間の前記拡散層がSTIと接するSTI周囲長、又は、前記拡散層が前記ゲートと隣接するゲート周囲長の依存性の実測値及びシミュレーション値の傾きを計算することを特徴とする請求項7記載のパラメータ最適化方法。

【請求項11】

前記STI周囲長又は前記ゲート周囲長が0のときの伝播遅延時間と、前記配線負荷パターンの伝播遅延時間との実測値とシミュレーション値の差分が一致しないときに、前記シミュレーション値の差分を前記実測値の差分に一致させるようにようにして、他の所定のパラメータを最適化する工程を含むことを特徴とする請求項10記載のパラメータ最適化方法。

【請求項12】

請求項1乃至6に記載の半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するプログラムであって、

前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションするステップと、

前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算するステップと、

前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化するステップと、

を実行させることを特徴とするプログラム。

【請求項1】

MOSトランジスタから構成されたプリミティブゲート回路を奇数段でリング状に結合した第1リングオシレータ部の各前記プリミティブゲート回路の出力部と電気的に接続された第1配線を有する配線負荷パターンと、

前記第1リングオシレータ部と同様な構成の第2リングオシレータ部の各プリミティブゲート回路の出力部が前記第1配線と同様な構成の第2配線を介して負荷部となるMOSトランジスタのゲートに電気的に接続された複数のゲート負荷パターンと、

前記第1リングオシレータ部と同様な構成の第3リングオシレータ部の各プリミティブゲート回路の出力部が前記第1配線と同様な構成の第3配線を介して負荷部となる拡散層に電気的に接続された複数の拡散層負荷パターンと、

を備え、

前記複数のゲート負荷パターンは、パターンごとに容量負荷が異なり、

前記複数の拡散層負荷パターンは、パターンごとに容量負荷が異なることを特徴とする半導体装置。

【請求項2】

前記複数のゲート負荷パターンは、パターンごとに前記第2配線に電気的に接続される前記ゲートの個数が異なることを特徴とする請求項1記載の半導体装置。

【請求項3】

前記ゲート負荷パターンは、前記負荷部となる前記MOSトランジスタのソース、ドレイン及び基板のそれぞれの端子に任意の電位を印加することができるように構成されていることを特徴とする請求項1又は2記載の半導体装置。

【請求項4】

前記複数の拡散層負荷パターンは、互いに前記第3配線に電気的に接続される前記拡散層の個数が異なることを特徴とする請求項1乃至3のいずれか一に記載の半導体装置。

【請求項5】

前記複数の拡散層負荷パターンは、前記負荷部となる前記拡散層の周囲の領域にSTIが配されているSTI構成と、前記負荷部となる前記拡散層の周囲の領域にゲートが配されているゲート構成と、を有することを特徴とする請求項1乃至4のいずれか一に記載の半導体装置。

【請求項6】

前記複数の拡散層負荷パターンにおける前記負荷部の基板の電位は、前記第3リングオシレータ部の基板電位と同じ電位であり、

前記複数の拡散層負荷パターンにおける前記ゲート構成の前記ゲートは、任意の電位を印加することができるように構成されていることを特徴とする請求項5記載の半導体装置。

【請求項7】

請求項1乃至6に記載の半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するパラメータ最適化方法であって、

前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションする工程と、

前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算する工程と、

前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化する工程と、

を含むことを特徴とするパラメータ最適化方法。

【請求項8】

前記伝播遅延時間を実測及びシミュレーションする工程では、前記ゲート負荷パターンの前記負荷部のゲート容量又はゲートオーバラップ容量による伝播遅延時間を実測及びシミュレーションすることを特徴とする請求項7記載のパラメータ最適化方法。

【請求項9】

前記傾きを計算する工程では、前記ゲート負荷パターンに係る前記伝播遅延時間のゲート個数依存性の実測値及びシミュレーション値の傾きを計算することを特徴とする請求項7又は8記載のパラメータ最適化方法。

【請求項10】

前記傾きを計算する工程では、前記拡散層負荷パターンに係る前記伝播遅延時間の前記拡散層がSTIと接するSTI周囲長、又は、前記拡散層が前記ゲートと隣接するゲート周囲長の依存性の実測値及びシミュレーション値の傾きを計算することを特徴とする請求項7記載のパラメータ最適化方法。

【請求項11】

前記STI周囲長又は前記ゲート周囲長が0のときの伝播遅延時間と、前記配線負荷パターンの伝播遅延時間との実測値とシミュレーション値の差分が一致しないときに、前記シミュレーション値の差分を前記実測値の差分に一致させるようにようにして、他の所定のパラメータを最適化する工程を含むことを特徴とする請求項10記載のパラメータ最適化方法。

【請求項12】

請求項1乃至6に記載の半導体装置と、前記半導体装置に電気的に接続された測定装置と、前記測定装置と電気的に接続されるとともに回路シミュレーションプログラムを実行するコンピュータと、を用いて前記回路シミュレーションプログラムにおけるMOSトランジスタのモデルのパラメータを最適化するプログラムであって、

前記ゲート負荷パターン又は前記拡散層負荷パターンの伝播遅延時間を実測及びシミュレーションするステップと、

前記伝播遅延時間の負荷依存性の実測値及びシミュレーション値の傾きを計算するステップと、

前記実測値及び前記シミュレーション値の傾きが一致しないときに、前記シミュレーション値の傾きを前記実測値の傾きに合わせるようにして、所定のパラメータを最適化するステップと、

を実行させることを特徴とするプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−77672(P2013−77672A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−216110(P2011−216110)

【出願日】平成23年9月30日(2011.9.30)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月30日(2011.9.30)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]