半導体装置、光ディスク装置及び半導体装置のテスト方法

【課題】コストの低減を図りつつ、かつ、精度よく基準電流を生成することが可能な半導体装置、光ディスク装置及び半導体装置のテスト方法を提供する。

【解決手段】半導体装置100は、基準電流を生成する電流生成回路と、記生成された基準電流をテスタ300へ出力する外部端子T1と、基準電流の電流値を制御するための電流制御データを、外部端子T1から出力された基準電流に応じてテスタ300により設定される外部端子T2と、テスタ300により設定された電流制御データにしたがって、電流生成回路により生成される基準電流が所定値となるように調整する電流制御部14と、を備える半導体装置。

【解決手段】半導体装置100は、基準電流を生成する電流生成回路と、記生成された基準電流をテスタ300へ出力する外部端子T1と、基準電流の電流値を制御するための電流制御データを、外部端子T1から出力された基準電流に応じてテスタ300により設定される外部端子T2と、テスタ300により設定された電流制御データにしたがって、電流生成回路により生成される基準電流が所定値となるように調整する電流制御部14と、を備える半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、光ディスク装置及び半導体装置のテスト方法に関し、特に、所定の電流を生成する電流生成回路を有する半導体装置、光ディスク装置及び半導体装置のテスト方法に関する。

【背景技術】

【0002】

近年、光ディスク装置など様々な電子機器において、取り扱う情報量の増大に伴い、動作速度の高速化が急速に進んでいる。このため、より高速に安定して動作するため、電子機器に搭載される半導体装置の特性ばらつきを低減することが強く望まれている。

【0003】

例えば、半導体装置には、供給される基準電流に応じた周波数の発振クロックを生成する発振回路や、供給される基準電流に応じた周波数特性を有するフィルタ回路が設けられている。この発振クロックやフィルタの特性を安定させるためには、一定の基準電流を生成する定電流回路(基準電流回路)の特性変動を抑える必要がある。

【0004】

従来の定電流回路を備えた半導体装置として、例えば、図10及び図11の構成が知られている。

【0005】

図10に示すように、従来の半導体装置900は、半導体装置の内部に定電流回路910を備えており、半導体装置の外部に抵抗918が接続されている。定電流回路910は、定電圧源(VBG)911、オペアンプ912、PMOSトランジスタ913,914、NMOSトランジスタ915,916を備えている。

【0006】

オペアンプ912は、非反転(正転)入力端子が定電圧源911に接続され、出力端子がPMOSトランジスタ913のゲートとPMOSトランジスタ914のゲートに共通接続されている。PMOSトランジスタ913のソースとPMOSトランジスタ914のソースは電源電位VCCに共通接続され、オペアンプ912の反転入力端子とPMOSトランジスタ913のドレインが外部端子917に接続されている。

【0007】

NMOSトランジスタ915とNMOSトランジスタ916は、互いのドレイン及びゲートがPMOSトランジスタ914のドレインに共通接続され、互いのソースが接地電位GNDに共通接続されている。PMOSトランジスタ916のソースは、出力電流Ioutの出力先の回路に接続されている。そして、半導体装置900の外部では、外部端子917と接地電位GNDとの間に抵抗918が接続されている。

【0008】

従来の半導体装置900の定電流回路910では、定電圧源911の電圧と外部の抵抗918の抵抗値とに応じた電流I0が生成される。そして、PMOSトランジスタ913,914及びNMOSトランジスタ915,916を介して、電流I0と等しい出力電流Ioutが他の回路へ出力される。

【0009】

また、図11に示すように、従来の半導体装置901は、半導体装置の内部に定電流回路920を備えている。定電流回路920は、定電圧源(VBG)921、オペアンプ922、PMOSトランジスタ923,924、NMOSトランジスタ925、抵抗926を備えている。

【0010】

オペアンプ922は、非反転入力端子が定電圧源921に接続され、出力端子が反転入力端子とNMOSトランジスタ925のゲートに接続されている。NMOSトランジスタ925のソースと接地電位GNDとの間に抵抗926が接続されている。

【0011】

PMOSトランジスタ923とPMOSトランジスタ924は、互いのソースが電源電位VCCに共通接続され、互いのゲートがPMOSトランジスタ924のドレインとPMOSトランジスタ925のソースに共通接続されている。PMOSトランジスタ923のドレインは、出力電流Ioutの出力先の回路に接続されている。

【0012】

定電流回路920では、定電圧源921の電圧及びNMOSトランジスタ925の閾値電圧Vthから決まる電圧と、抵抗926の抵抗値とに応じた電流I0が生成される。そして、PMOSトランジスタ924,923を介して、電流I0と等しい出力電流Ioutが他の回路へ出力される。

【0013】

なお、特許文献1には、トリミング回路により電流をトリミングする定電流回路が記載されている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2010−217963号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

図10に示した従来の半導体装置900では、半導体装置の外部に抵抗918を外付けとしている。半導体装置900内の定電流回路910が生成する定電流は、定電圧源911の電圧と抵抗918の抵抗値とにより決まる。このため、抵抗918として特性ばらつきの小さい高精度な抵抗を接続することにより、定電流回路910の出力電流の変動を抑えることができる。抵抗918は半導体装置の製造ばらつき等による特性変動がないため、製造プロセス(fab)が変更となった場合でも一定の電流を生成することができる。

【0016】

しかしながら、従来の半導体装置900では、外部の抵抗を接続するための外部端子が必要となる。半導体装置に外部抵抗専用の外部端子を設けると、外部端子が増加するため、半導体装置の小型化や低コスト化の妨げとなる。特に、近年、半導体装置の小型化に伴い外部端子数は減少傾向にあるため、外部抵抗専用の外部端子を設けることは困難となってきている。また、従来の半導体装置900では、外部に接続する抵抗として、特性変動の少ない高精度な抵抗を用意する必要となり、そのような抵抗は一般にコストが高いことから、コストが増大するという問題がある。

【0017】

一方、図11に示した従来の半導体装置901は、従来の半導体装置900と比べると、外部端子が不要であり、外部に抵抗を用意する必要がないため、半導体装置900よりもコストを低減することが可能である。

【0018】

しかしながら、従来の半導体装置901は、抵抗926に製造ばらつき等による特性変動の影響を受けるため、製造プロセスが変更となった場合の特性変動が大きく、定電流回路920の出力電流のばらつきが大きいという問題がある。例えば、半導体装置内の抵抗の絶対値ばらつきが±20%とすると、定電流回路の出力電流も±20%変動することになる。

【0019】

このように、従来の半導体装置では、コストの低減を図りつつ、かつ、精度よく基準電流を生成することが困難であるという問題があった。

【課題を解決するための手段】

【0020】

本発明に係る半導体装置は、電流生成回路(図3の電流生成部11、電流切替部13及び電流出力部17に相当)、第1の外部端子(図3の外部端子T1に相当)、第2の外部端子(図3の外部端子T2に相当)及び電流制御回路(図3の電流制御部14に相当)を備えている。電流生成回路は、基準電流(Iout及びIREFに相当)を生成する電流生成回路である。また、第1の外部端子は、電流生成回路により生成された基準電流をテスタへ出力するための端子である。そして、第2の外部端子は、電流生成回路が生成する基準電流の電流値を制御するための電流制御データを、第1の外部端子から出力された基準電流に応じてテスタにより設定される端子である。さらに、電流制御回路は、第2の外部端子を介してテスタにより設定された電流制御データにしたがって、電流生成回路により生成される基準電流が所定値となるように調整する。以上の構成により、基準電流の電流値を一定の所定値にトリミングすることができるため、抵抗等により生じる電流ばらつきを防ぎ精度のよい基準電流を生成できる。また、外部に高精度な抵抗を別途用意する必要がないため、コストを低減することができる。

【0021】

ここで、電流生成回路は、抵抗電流生成部(図3の電流生成部11に相当)と電流切替部(図3の電流切替部13に相当)とを備えていてもよい。抵抗電流生成部は、定電圧に応じた抵抗電流を抵抗により生成する。電流切替部は、抵抗電流生成部により生成された抵抗電流をミラーする第1のカレントミラー回路のミラー比を、電流制御回路から入力される電流制御データに応じて切り替えることで基準電流を生成する。

【0022】

また、電流生成回路は、電流出力部(図3の電流出力部17に相当)をさらに備えていてもよい。電流出力部は、電流切替部により生成された基準電流を第2のカレントミラー回路によりミラーして出力する。

【0023】

また、上記第1のカレントミラー回路または上記第2のカレントミラー回路には、カスコードトランジスタ(図5のカスコードトランジスタ群20、カスコードトランジスタ群21に相当)が接続されていてもよい。これにより、カレントミラー回路の電流ミラーの精度が向上するため、より精度のよい基準電流を生成することができる。

【0024】

さらに、上記半導体装置は、電流生成回路が生成する基準電流を測定する電流測定回路(図6の電流計に相当)を有していてもよい。そして、テスタにより電流制御データが設定された後、電流制御回路は、電流測定回路による基準電流の測定結果に応じて、電流生成回路により生成される基準電流が所定値となるようにさらに調整してもよい。また、上記半導体装置は、温度を測定する温度センサ(図7の温度センサ23に相当)を有していてもよい。そして、テスタにより電流制御データが設定された後、電流制御回路は、温度センサによる温度の測定結果に応じて、前記電流生成回路により生成される基準電流が前記所定値となるようにさらに調整してもよい。これにより、テスタにより電流トリミングした後においても、半導体装置内部で基準電流を一定の所定値とすることができるため、温度等により生じる電流ばらつきを防ぎさらに精度のよい基準電流を生成できる。

【0025】

また、上記半導体装置では、テスタが、メモリのテストと基準電流のテストとを同じ工程で実施してもよい。すなわち、テスタが、半導体装置に含まれるメモリの欠陥救済のためのメモリテスト工程において、第1の外部端子から出力された基準電流を測定し、基準電流の測定結果に応じて前記第2の外部端子へ電流制御データを設定してもよい。これにより、メモリと基準電流のテスト及びトリミングをまとめて実施できるため、効率よくテスト及びトリミングを行うことができ、テストのコストを低減することができる。

【0026】

本発明に係る光ディスク装置は、光ディスクにレーザ光を照射するピックアップと、ピックアップの動作を制御する半導体装置を備えている。そして、半導体装置は、電流生成回路、第1の外部端子、第2の外部端子、電流制御回路及び信号処理回路(図1のRF系回路113、ウォブル検出回路114、ライトPLL115、サーボ系回路116に相当)を備えている。電流生成回路、第1の外部端子、第2の外部端子及び電流制御回路の構成は上記半導体装置と同様である。また、信号処理回路は、電流制御回路により記調整された電流生成回路の基準電流に基づいて、ピックアップから出力される信号を処理する。以上の構成により、光ディスク装置において、基準電流の電流値を一定の所定値にトリミングし、抵抗等により生じる電流ばらつきを防ぎ精度のよい基準電流を生成できる。また、外部に高精度な抵抗を別途用意する必要がないため、コストを低減することができる。そして、基準電流を安定させることで、光ディスク装置における信号処理回路の特性ばらつきを抑止し、倍速モード等の場合でも精度よく動作することが可能である。

【0027】

本発明に係る半導体装置のテスト方法は、基準電流を生成する電流生成回路と生成される基準電流を調整する電流制御回路と第1及び第2の外部端子とを有する半導体装置のテスト方法である。半導体装置のテスト方法では、まず、テスタは、第1及び第2の外部端子にプローブを接続し、第1の外部端子を介して電流生成回路と電気的に接続し、第2の外部端子を介して電流制御回路と電気的に接続する。次に、テスタは、基準電流の電流値を制御するための電流制御データの初期値を決定し、初期値として決定した前記電流制御データを前記第2の外部端子を介して電流制御回路へ変更可能に設定する。次に、電流制御回路は、設定された電流制御データにしたがって、電流生成回路により生成される基準電流を調整する。次に、電流生成回路は、電流制御データにより調整された基準電流を第1の外部端子を介してテスタへ出力する。次に、テスタは、出力された基準電流の電流値を測定し、基準電流の測定結果と所定値との比較結果に応じて、電流制御データの最適値を決定する。次に、テスタは、最適値として決定した電流制御データを第2の外部端子を介して電流制御回路へ変更不可能に設定する。以上の動作により、基準電流の電流値を一定の所定値にトリミングすることができるため、抵抗等により生じる電流ばらつきを防ぎ精度のよい基準電流を生成できる。また、外部に高精度な抵抗を別途用意する必要がないため、コストを低減することができる。

【発明の効果】

【0028】

本発明によれば、コストの低減を図りつつ、かつ、精度よく基準電流を生成することが可能な半導体装置、光ディスク装置及び半導体装置のテスト方法を提供することができる。

【図面の簡単な説明】

【0029】

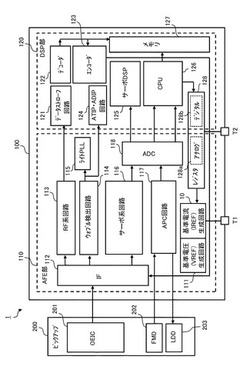

【図1】本発明の実施の形態1に係る光ディスク装置の構成を示すブロック図である。

【図2】本発明の実施の形態1に係る光ディスク装置の信号特性を示すグラフである。

【図3】本発明の実施の形態1に係る半導体装置の回路構成を示す回路図である。

【図4】本発明の実施の形態1に係る半導体装置のテスト方法(トリミング方法)を示すフローチャートである。

【図5】本発明の実施の形態2に係る半導体装置の回路構成を示す回路図である。

【図6】本発明の実施の形態3に係る半導体装置の回路構成を示す回路図である。

【図7】本発明の実施の形態4に係る半導体装置の回路構成を示す回路図である。

【図8】本発明の実施の形態5に係る半導体装置のテスト構成を示す構成図である。

【図9】本発明の実施の形態5に係る半導体装置のテスト方法(トリミング方法)を示すフローチャートである。

【図10】従来の半導体装置の回路構成を示す回路図である。

【図11】従来の半導体装置の回路構成を示す回路図である。

【発明を実施するための形態】

【0030】

(本発明の実施の形態1)

以下、図面を参照して本発明の実施の形態1について説明する。図1は、本発明の実施の形態1に係る光ディスク装置(光ディスクシステム)1の構成を示している。図1に示すように、光ディスク装置1は、半導体装置100とピックアップ200とを備えている。

【0031】

ピックアップ200は、半導体装置100からの制御にしたがって光ディスクにレーザ光を照射する光ピックアップである。ピックアップ200は、光電変換回路OEIC201、フロントモニタダイオードFMD202、レーザダイオードドライバLDD203を備えている。ピックアップ200内には、その他、光ディスクに対してレーザ光を照射するレーザダイオードや、フォーカス方向及びトラッキング方向に位置合わせをするサーボ機構(アクチュエータ)等が備えられている(不図示)。

【0032】

レーザダイオードドライバLDD203は、レーザダイオードを駆動する駆動回路である。フロントモニタダイオードFMD202は、レーザダイオードの発光強度を調整するために光ディスクからの反射光を検出する検出回路である。

【0033】

光電変換回路OEIC201は、光ディスクからの反射光を電気信号に変換する変換回路である。例えば、光ディスクからの反射光を検出する検出回路(フォトディテクタ)がA,B,C,Dの4つの領域に田の字状に分割されている。光電変換回路OEIC201は、4つの各領域で検出された信号A,B,C,Dを電気信号として出力する。また、信号A,B,C,Dとは別にデータを示すRF(Radio Frequency)信号を出力することも可能である。

【0034】

半導体装置100は、AFE(Analog Front End)部110、DSP(Digital Signal Processor )部120を備えている。また、半導体装置100は、外部装置と接続するための外部端子T1,T2を有している。後述のように、外部端子T1,T2は、テスト時(トリミング時)にのみテスト端子として使用し、通常動作時は、各内部回路が外部と入出力を行うための通常の外部端子として使用可能である。

【0035】

AFE部110は、ピックアップ200から入力される各信号をDSP部120で処理可能な信号に変換するアナログ回路である。DSP部120は、AFE部110を介して入力されるピックアップ200の各信号に基づいて演算処理を行い、データのリード/ライト、サーボ制御等を行うデジタル回路である。

【0036】

例えば、半導体装置100は、SoC(System on Chip)やSiP(System in Package)の半導体装置である。AFE部110及びDSP部120を含む1つの半導体チップから構成されてもよいし、AFE部110の半導体チップとDSP部120の半導体チップを1パッケージとして構成してもよいし、AFE部110の半導体チップとDSP部120の半導体チップ、メモリ127の半導体チップを1パッケージとして構成してもよい。

【0037】

AFE部110は、基準電流生成回路10、基準電圧生成回路111、インタフェースIF112、RF系回路113、ウォブル(Wobble)検出回路114、ライトPLL115、サーボ系回路116、APC回路(自動パワー制御回路)117、ADC(A/Dコンバータ)118を備えている。AFE部110には、レジスタ128の一部であるアナログレジスタ128aも含まれている。

【0038】

基準電流生成回路10は、一定の基準電流IREF(定電流)を生成し、半導体装置100内のAFE部110及びDSP部120の各回路へ基準電流IREF(バイアス電流)を供給する定電流回路である。後述のように、基準電流生成回路10は、レジスタ128に保持されている電流コード値(電流制御データ)にしたがって基準電流IREFを可変に設定することができる。また、基準電流生成回路10は、外部端子T1に接続されており、テスト時に、生成した基準電流IREFを外部端子T1を介して外部のテスタへ出力する。

【0039】

基準電圧生成回路111は、一定の基準電圧VREF(定電圧)を生成し、半導体装置100内のAFE部110及びDSP部120の各回路へ基準電圧VREF(バイアス電圧)を供給する定電圧回路である。基準電圧生成回路111は、基準電圧VREFとして温度等によるばらつきが少ないバンドギャップ電圧VBGを生成するバンドギャップ電圧生成回路である。

【0040】

インタフェースIF112は、ピックアップ200とのインタフェースであり、ピックアップ200の光電変換回路OEIC201で光電変換された各信号が入力され、レベル変換等を行って、各信号を処理するRF系回路113、ウォブル検出回路114、サーボ系回路116へ出力する。すなわち、インタフェースIF112は、信号A、B、C、Dから、RF信号、ウォブル信号、フォーカスエラー信号、トラッキングエラー信号等を生成するために各回路へ出力する。また、ピックアップ200からRF信号が入力される場合は、インタフェースIF112は、入力されたRF信号をRF系回路113へ出力する。

【0041】

RF系回路113は、RF信号からデータを示す再生データ信号を生成する。RF系回路113は、インタフェースIF112からRF信号が入力される場合は、入力される信号を使用し、信号A,B,C,Dが入力される場合には、例えば、信号(A+B+C+D)の演算からRF信号を生成する。RF系回路113は、基準電流IREFに応じて動作するフィルタ等を有している。RF系回路113は、RF信号からフィルタにより所定周波数成分を除去し、包絡線の抽出等を行って、再生データ信号を生成する。

【0042】

ウォブル検出回路114は、インタフェースIF112により入力される信号から、光ディスク上のアドレスや同期タイミングを示すウォブルを検出してウォブル信号を生成する。ウォブル検出回路114は、基準電流IREFに応じて動作するフィルタ等を有している。例えば、ウォブル検出回路114は、信号(A+D)−(B+C)の演算を行い、演算された信号からフィルタにより所定周波数成分を除去し、包絡線の抽出等を行って、ウォブル信号を生成する。

【0043】

ライトPLL115は、ウォブル検出回路114により生成されたウォブル信号に基づいて、光ディスクに書き込みを行うためのライトクロックを生成する。ライトPLL115は、基準電流IREFに応じて動作する発振回路を有している。ライトPLL115は、ウォブル信号が入力されると、発振回路による発振を繰り返してロック状態となり、ライトクロックを生成する。

【0044】

サーボ系回路116は、インタフェースIF112により入力される信号から、サーボ制御のためのサーボ制御信号を生成する。サーボ系回路116は、位相差を検出するDPD回路を有している。例えば、サーボ系回路116は、信号(A+B)−(C+D)の演算からトラッキング方向に制御するためのトラッキングエラー信号TEを生成し、信号(A+C)−(B+D)の演算からフォーカス方向に制御するためのフォーカスエラー信号FEを生成し、信号(A+C),(B+D)の位相差からサーボ制御するためのDPD信号を生成し、サーボ制御信号として出力する。

APC回路(自動パワー制御回路)117は、フロントモニタダイオードFMD202が検出したレーザダイオードの発光強度が入力され、検出した発光強度に応じて、レーザダイオードが所定の発光強度となるように、レーザダイオードドライバLDD203へ発光制御する発光制御信号を出力する。

【0045】

ADC118は、サーボ系回路116のサーボ制御信号やAPC回路117の出力するアナログ信号をデジタル信号に変換して、DSP部120のサーボDSP125やCPU126へ出力する。なお、ADC118のデータ処理は、アナログ回路でもデジタル回路でも構成できるため、AFE部110に設けてもよいし、DSP部120に設けてもよい。

【0046】

DSP部120は、データストローブ回路121、デコーダ122、エンコーダ123、ATIP・ADIP回路124、サーボDSP125、CPU126、メモリ127、レジスタ128を備えている。

【0047】

データストローブ回路121は、RF系回路113により生成された再生データ信号からデータをデコードするタイミングを示すデータストローブ信号を生成する。デコーダ122は、データストローブ回路121により生成されたデータストローブ信号のタイミングに基づいて、再生データ信号を伸長・復号化処理等によりデコードし、リードデータを生成する。リードデータは、メモリ127に記憶されて、外部のデータ処理装置等へ出力される。

【0048】

エンコーダ123は、外部のデータ処理装置等からメモリ127に記憶されたライトデータを、圧縮・符号化処理等によりエンコードし、ライトデータを生成する。ライトデータは、インタフェースIF112を介してピックアップ200へ出力され、ライトPLL115により生成されたライトクロックに基づいて光ディスクへ書き込まれる。

【0049】

ATIP・ADIP回路124は、ウォブル検出回路114により生成されたウォブル信号に対し、ATIP復調やADIP復調を行い、アドレス情報や絶対位置情報を生成する。このアドレス情報や絶対位置情報に基づいて、ライトデータの書き込み等が行われる。

【0050】

サーボDSP125は、ADC118を介して入力されるサーボ制御信号に基づいて、ピックアップ200のサーボを制御し、ピックアップ200の位置を調整する。サーボDPS125は、トラッキングエラー信号TE、フォーカスエラー信号FE、DPD信号等に基づいて、演算処理を行い、トラッキングサーボやフォーカスサーボを制御してピックアップ200の位置合わせを行う。

【0051】

CPU126は、メモリ127に記憶されたプログラムを実行し、プログラムにしたがって演算処理を行ってシステム全体の動作を制御する演算処理部である。メモリ127は、フラッシュメモリやSDRAM等で構成され、各種のプログラムやデータを記憶し、また、光ディスクのリードデータ、ライトデータ等を記憶する。

【0052】

レジスタ128は、CPU126における演算処理等で用いるデータや、各回路で必要とするデータを保持する。レジスタ128は、アナログ回路で構成されるアナログレジスタ128aと、デジタル回路で構成されるデジタルレジスタ128bを含んでいる。

【0053】

このような半導体装置100において、本実施形態では、基準電流生成回路10の生成する基準電流IREFは、主に、RF系回路113、ウォブル検出回路114、ライトPLL115、サーボ系回路116へ供給されている。これらの回路に基準電流IREFを供給し、回路動作を電流制御することで、電圧制御の場合と比べて、幅広いダイナミックレンジに対応でき、必要な電源電圧を小さくすることができる。

【0054】

RF系回路113、ウォブル検出回路114では、内部のフィルタに基準電流IREFが供給されている。このフィルタは、例えば、gmcフィルタであり、入力される基準電流IREFに従って動作し、基準電流IREFを用いたフィルタの設定を切り替えることでブースト量・ブースト周波数やカットオフ周波数等の周波数特性を変化させることができる。

【0055】

図2は、RF系回路113におけるRF信号の周波数特性を示している。光ディスク装置では、読み出し速度を選択することができ、選択される読み出し速度によってRF信号の周波数特性が異なる。たとえば、図2(a)は、ブースト前のRF信号、図2(b)は、ある光ディスクの4倍速モードで読み出す場合のRF信号、図2(c)は、8倍速モードで読み出す場合のRF信号の周波数特性である。

【0056】

RF系回路113では、このRF信号の周波数特性に合わせてフィルタの特性を設定する。すなわち、図2(b)、図2(c)に示すように倍速モードの場合、フィルタは倍速数に応じた周波数をブーストする設定となる。また、他の倍速モードでは、他の周波数をブーストまたはカットする必要がある。

【0057】

したがって、RF系回路113やウォブル検出回路114では、倍速モードによってフィルタ特性のブーストやカットが必要であり、より高精度な特性が求められるため、フィルタに供給される基準電流IREFのばらつきを抑える必要がある。

【0058】

また、サーボ系回路116では、基準電流IREFに応じて、ピックアップから入力されるDC信号のオフセット調整や入力バッファのバイアス調整等が行われている。このため、サーボ系回路116で、入力信号からサーボ制御信号を精度よく生成するためには、基準電流IREFのばらつきを抑える必要がある。

【0059】

なお、ADC118は、サーボ系回路116から出力される複数のサーボ制御信号ごとにレベルがばらついていると、正常にA/D変換できない場合があるため、サーボ制御信号のレベルを一定に保つためにも、サーボ系回路116に供給する基準電流IREFのばらつきを抑える必要がある。

【0060】

また、ライトPLL回路115では、基準電流IREFに応じて、ウォブル信号に基づいた所定周波数のライトクロックを生成している。このため、ライトPLL回路115で、ウォブル信号に同期したライトクロックを精度よく生成するためには、基準電流IREFのばらつきを抑える必要がある。

【0061】

このため、本実施形態では、基準電流IREFの精度を向上させ、RF系回路113、ウォブル検出回路114、ライトPLL115、サーボ系回路116等を安定して動作させるために、以下のような構成とした。図3は、本発明の実施の形態1に係る基準電流生成回路10の回路構成、及びテスト時のテスタ300の接続状態を示している。

【0062】

図3に示すように、半導体装置100における基準電流生成回路10は、電流生成部11、電流切替部13、電流制御部14、電流出力部17を備えている。例えば、電流生成部11と電流切替部13と電流出力部17とが、基準電流IREFを生成する電流生成回路であり、電流制御部14が、電流コード値にしたがって、基準電流IREFを所定値となるように調整する電流制御回路である。

【0063】

電流生成部(抵抗電流生成部)11は、定電圧VBGと抵抗に基づいて、主に抵抗によるばらつきを含む電流I0を生成する。電流生成部11は、定電圧源12、オペアンプOP1、PMOSトランジスタP0、抵抗R1を備えている。

【0064】

定電圧源12は、定電圧として定電圧(バンドギャップ電圧)VBGを生成するバンドギャップ電圧生成回路である。定電圧源12は、製造ばらつきによる電圧変動が少なく、温度変化に対しても電圧変動が少なくなるように回路構成されている。例えば、定電圧源12は、図1の基準電圧生成回路111に対応しており、定電圧VBGは、基準電圧生成回路111が生成する基準電圧VREFそのものか、もしくは基準電圧VREFに基づいた所定の電圧である。

【0065】

オペアンプOP1は、非反転入力端子と反転入力端子に入力される入力信号を差動増幅した出力信号を出力端子から出力する差動増幅回路である。オペアンプOP1は、非反転入力端子に定電圧源12からバンドギャップ電圧VBGが入力されている。PMOSトランジスタP0は、ソースが電源電位VCCに接続され、ゲートがオペアンプOP1の出力端子に接続され、ドレイン(ノードND1)がオペアンプOP1の反転入力端子と抵抗R1の一端とに接続されている。

【0066】

抵抗R1の他端は接地電位GNDに接続されている。抵抗R1は、ポリシリコンにより形成されたポリシリコン抵抗である。抵抗R1の抵抗値は、主に製造工程により生じる絶対値ばらつきを有し、また、温度変化によるばらつきも有する。

【0067】

オペアンプOP1では反転入力端子にノードND1から帰還信号が入力されるため、オペアンプOP1、PMOSトランジスタP0及び抵抗R1により負帰還増幅回路が構成される。そうすると、オペアンプOP1はイマジナルショートの状態となって、非反転入力端子と反転入力端子の電圧が同じとなり、PMOSトランジスタP0と抵抗R1間のノードND1の電圧が、定電圧VBGと等しくなる。したがって、抵抗R1及びPMOSトランジスタP0に、定電圧VBGと抵抗R1の抵抗値に応じた電流I0(抵抗電流)が流れる。例えば、定電圧VBG=1.25V、抵抗R1=12.5KΩとすると、電流I0=100μAとなる。

【0068】

電流切替部(電流選択部)13は、電流生成部11により生成された電流I0をもとに、電流コード値にしたがって電流値を切り替えて出力電流Ioutを生成する。電流切替部13は、電流I0をミラーするカレントミラー回路のミラー比を、電流コード値に応じて切り替えることで出力電流Ioutを生成する。電流切替部13は、電流コード値のデジタル値に応じたアナログ値の電流を出力する電流DAC(D/Aコンバータ)でもある。電流切替部13は、PMOSトランジスタP1〜P5、スイッチSW1〜SW5を備えている。

【0069】

PMOSトランジスタP1〜P5は、各ソースが電源電位VCCに共通接続され、各ゲートがPMOSトランジスタP0のゲートに共通接続され、各ドレインがそれぞれスイッチSW1〜SW5を介して出力電流Ioutを生成するノードND2(基準電流生成ノード)に接続されている。

【0070】

PMOSトランジスタP0とPMOSトランジスタP1〜P5とはカレントミラー接続された第1のカレントミラー回路を構成している。したがって、PMOSトランジスタP0の電流I0に対して、PMOSトランジスタP0とPMOSトランジスタP1〜P5とのトランジスタサイズ比に応じた電流I1〜I5が、PMOSトランジスタP1〜P5に生成される。そうすると、ノードND2において電流I1〜I5を合計した電流が出力電流Ioutとなる。このため、スイッチSW1〜SW5のオン/オフを切り替えて合計する電流I1〜I5を選択することで出力電流Ioutを可変可能としている。

【0071】

ここでは、スイッチSW1は常にオンとし、スイッチSW2〜SW5を切り替え可能とする。4ビットの電流コード値の各ビットをスイッチSW2〜SW5及びPMOSトランジスタP2〜P5に対応付け、電流コード値にしたがってスイッチSW2〜SW5をオン/オフし出力電流Ioutを切り替える。なお、スイッチSW1を切り替え可能としてもよい。

【0072】

電流コード値のMSB(最上位ビット)がスイッチSW2及びPMOSトランジスタP2に対応し、電流コード値のLSB(最下位ビット)がスイッチSW5及びPMOSトランジスタP5に対応している。PMOSトランジスタP2:P3:P4:P5のサイズ比(カレントミラー比)は、8:4:2:1であり、電流I2:I3:I4:I5の比も、8:4:2:1となる。これにより、電流コード値の各ビットの数値に対応した電流Ioutが生成される。

【0073】

例えば、PMOSトランジスタP0〜P5の電流を、I0=100μA、I1=78μA、I2=24μA、I3=12μA、I4=6μA、I5=3μAとする。基準となるPMOSトランジスタP5のW/Lサイズを基準サイズとして、PMOSトランジスタP0〜P4を、PMOSトランジスタP5に対する電流比に応じたサイズとする。この場合、Iout=78μA+(電流コード値×3)μAとなる。したがって、電流コード値=(0001)の場合、Iout=78+3=81μAとなり、電流コード値=(0111)の場合、Iout=78+12+6+3=99μAとなり、電流コード値=(1111)の場合、Iout=78+24+12+6+3=123μAとなる。

【0074】

電流制御部14は、ヒューズレジスタ15または割り込みレジスタ16の電流コード値にしたがって電流切替部13が生成する電流Ioutの電流値を制御する。電流制御部14は、スイッチSW1〜SW5、ヒューズレジスタ15及び割り込みレジスタ16に接続されている。電流制御部14は、ロジック回路で構成されており、ヒューズレジスタ15または割り込みレジスタ16に保持されている電流コード値に応じた制御信号を生成し、スイッチSW1〜SW5のオン/オフを切り替える。

【0075】

ヒューズレジスタ15と割り込みレジスタ16のいずれの電流コード値により電流制御するかは、選択可能である。例えば、いずれを選択するか制御する選択制御信号をCPUから電流制御部14に供給し、選択制御信号にしたがって電流コード値を選択してもよい。また、ヒューズレジスタ15の電流コード値を優先的に設定してもよいし、割り込みレジスタ16の電流コード値を優先的に設定してもよい。この場合、両方のレジスタに電流コード値が設定されている場合、優先させるレジスタの電流コード値を使用する。

【0076】

また、ヒューズレジスタ15と割り込みレジスタ16の両方の電流コード値により電流制御してもよい。例えば、ヒューズレジスタ15の電流コード値を基準値とし、割り込みレジスタの電流コード値を補正値として、基準値と補正値の加算値あるいは減算値により電流制御してもよい。

【0077】

ヒューズレジスタ15は、ヒューズの切断により電流コード値を固定的に変更不可能な状態で保持し、割り込みレジスタ16は、CPUやテスタ等からの入力により電流コード値を動的に変更可能な状態で保持する。ヒューズレジスタ15及び割り込みレジスタ16は、外部端子T2に接続されており、テスタ300から外部端子T2を介して電流制御値を書き込むことができる。外部端子T2は、テスタ300からレジスタの書き込みを制御するレジスタ制御端子である。なお、ヒューズレジスタ15及び割り込みレジスタ16は、図1のレジスタ128のアナログレジスタ128aもしくはデジタルレジスタ128bに対応している。

【0078】

電流出力部17は、電流切替部13により生成された出力電流Iout(基準電流IREF)を半導体装置100内の各回路へ出力し、また、テストのために外部へも出力する。電流出力部17は、NMOSトランジスタN1〜N4を備えている。

【0079】

NMOSトランジスタN1のドレインが、ノードND2に接続されるとともに、NMOSトランジスタN1〜N4のゲートに共通接続されている。NMOSトランジスタN1〜N4のソースは接地電位GNDに共通接続されている。NMOSトランジスタN2〜N4のドレインは、それぞれ出力電流Ioutの出力先の回路に接続されている。

【0080】

NMOSトランジスタN1とNMOSトランジスタN2〜N4とはカレントミラー接続された第2のカレントミラー回路を構成している。したがって、NMOSトランジスタN1の電流Ioutに対して、NMOSトランジスタN1とNMOSトランジスタN2〜4とのトランジスタサイズ比に応じた電流がNMOSトランジスタN2〜N4に流れる。ここでは、NMOSトランジスタN1〜N4は全て同じサイズのトランジスタであり、NMOSトランジスタN1の電流と同じ出力電流Iout(基準電流IREF)が、NMOSトランジスタN2〜N4にも流れて、各接続先の回路に出力される。なお、NMOSトランジスタN2〜N4のサイズを変更して、各回路に出力電流Ioutに基づいた電流を出力することもできる。

【0081】

NMOSトランジスタN2,N3は、半導体装置100の内部回路へ電流Iout(基準電流IREF)を出力する出力回路である。すなわち、電流Ioutを、RF系回路113、ウォブル検出回路114、ライトPLL115、サーボ系回路116等へ出力する。

【0082】

NMOSトランジスタN4は、半導体装置100の外部のテスタ300へ電流Iout(基準電流IREF)を出力する出力回路である。NMOSトランジスタN4は、マルチプレクサ18、内部バッファ19を介して外部端子T1に接続される。

【0083】

マルチプレクサ18は、NMOSトランジスタN4の他に、通常動作時に外部装置と入出力を行う内部回路と接続されている。マルチプレクサ18と外部端子T1との接続、内部バッファ19と外部端子T1との接続はスイッチSW11、SW12により切り替えられる。

【0084】

通常動作時、マルチプレクサ18が内部回路との接続を選択し、スイッチSW11がオン、スイッチSW12がオフしている。このため、内部回路と外部端子T1が接続された状態となり、外部端子T1を介して、内部回路と外部装置が電気的に接続される。また、テスト時(トリミング時)は、マルチプレクサ18、スイッチSW11,SW12にテスト選択信号が入力されると、マルチプレクサ18がNMOSトランジスタN4との接続を選択し、スイッチSW11がオフし、スイッチSW12がオンする。このため、NMOSトランジスタN4と外部端子T1が接続された状態となり、外部端子T1を介して、NMOSトランジスタN4とテスタ300とが電気的に接続され、テスタ300へ出力電流Iout(基準電流IREF)が出力される。

【0085】

なお、外部端子T1も同様にテスト選択信号により、通常動作時とテスト時で接続が切り替えられて、テスト時にのみ、外部端子T1を介してヒューズレジスタ15及び割り込みレジスタ16とテスタ300とが接続される。

【0086】

テスタ300は、半導体装置100の動作をテストするための装置であり、また、基準電流生成回路10の出力電流Iout(基準電流IREF)を測定して、所定の電流となるようにトリミングを行う装置である。

【0087】

テスタ300は、複数のプローブを有しており、プローブテスト時に半導体装置100の外部端子T1,T2にプローブを接続する。テスタ300は、電流計301を有しており、外部端子T1を介してNMOSトランジスタN4から出力される出力電流Ioutの電流を測定する。テスタ300は、出力電流Ioutの測定結果に応じて、出力電流Ioutが所定値となるように電流コード値を決定し、外部端子T2を介してヒューズレジスタ15または割り込みレジスタ16へ書き込む。

【0088】

出力電流Ioutの電流測定方法として、種々の方法が採用できる。例えば、テスタ300のテストボード上に設けられた特性ばらつきの少ない高精度抵抗を外部端子T1に接続して、電圧変換した値により電流測定してもよい。また、テスタ300が有する電流計により、電流Ioutを直接測定してもよい。

【0089】

図4は、本発明の実施の形態1に係るテスト方法の流れを示している。このテスト方法は、図3の構成により、テスタ300が半導体装置100の基準電流IREFをトリミングする方法である。

【0090】

まず、テスタ300は、LSIを初期化する(S101)。テスタ300は、基準電流IREFをトリミングするため、プローブを外部端子T1,T2に接続し、半導体装置100をテストモードに設定し、必要な初期設定を行う。ここでは、電流コード値の初期値を決定する。4ビットの初期値としては、最小値(0000)、最大値(1111)、中心値(0111または1000)等を使用できる。中心値から測定を開始することが、最も効率よくテストできるため、中心値を初期値に決定する。また、他の半導体装置100のテストがすでに完了している場合、他の半導体装置100でトリミング設定した電流コード値を初期値と決定してもよい。

【0091】

次に、テスタ300は、電流コード値を割り込みレジスタ16に設定する(S102)。テスタ300は、S101またはS104の判定により決定した電流コード値を検証するため、外部端子T2を介して割り込みレジスタ16へ書き込む。S104の電流判定後に再度設定する場合には、測定した測定電流と目標とする目標電流との大小に応じて、電流コード値を1(1LSB)ずつ加算または減算し、電流を逐次比較する。1より大きい数値を加算または減算してもよいし、順次中心値を選択して二分探索するようにしてもよい。目標値との差分に応じた値を加算または減算してもよい。また、他の半導体装置100のテストがすでに完了している場合、他の半導体装置100で加算または減算した値をもとに設定してもよい。

【0092】

次に、テスタ300は、半導体装置100の基準電流IREFの電流を測定する(S103)。テスタ300は、外部端子T2を介して出力される基準電流IREFを、電流計等により測定する。

【0093】

次に、テスタ300は、測定した基準電流IREFの大小を判定する(S104)。テスタ300は、測定した基準電流IREFの電流値と、目標とする目標電流値とを比較し、基準電流IREFが目標とする範囲内かどうか判定する。例えば、±1LSBの範囲かどうか判定する。つまり、1LSBが3μAとすると、±3μAの範囲かどうか判定する。±1LSBの範囲内であれば、現在の電流コード値を最適値として決定してS105へ進み、±1LSBの範囲外であれば、S102以降を再度繰り返し、電流コード値の最適値を求める。

【0094】

次に、テスタ300は、電流コード値をヒューズレジスタ(トリミング用メモリ)15に格納する(S105)、トリミングを実行する(S106)。テスタ300は、電流測定により最適値と決定された電流コード値を、外部端子T2を介してヒューズレジスタ15へ書き込む。これにより、電流コード値が固定的に設定され、基準電流IREFが絶対値ばらつきの無い電流にトリミングされる。

【0095】

以上のように、本実施形態では、半導体装置の基準電流をテスタにより測定し、基準電流が所定値となるように電流コード値を決定し、電流コード値を半導体装置に設定するようにした。これにより、抵抗の絶対値ばらつきにより生じる電流変動をトリミングすることができるため、精度のよい基準電流を生成することができる。実際に出力される基準電流に基づいて電流をトリミングするため、抵抗のばらつきの他、VBGのばらつき等も含めてトリミングすることができる。また、外部端子を介して外部に抵抗を接続する必要がないため、効果な抵抗を用意する必要がなく、外部端子も不要であるため、コストを低減することができる。

【0096】

従来回路では、例えば±20%の電流ばらつきを有する場合、要求されるダイナミックレンジと帯域を確保するためには、−20%の特性を考慮して電力を20%大きくする必要があるが、本実施形態では、電流をトリミングして安定化させることで、各ブロックのバイアス電流を必要最小限とすることができるため、電力低減を図ることが可能である。

【0097】

(本発明の実施の形態2)

以下、図面を参照して本発明の実施の形態2について説明する。図5は、本発明の実施の形態2に係る基準電流生成回路10の回路構成を示しており、その他の構成については、実施の形態1と同様である。

【0098】

図5の基準電流生成回路10では、図3の回路構成に加えて、PMOSトランジスタP11〜P15(第1のカスコードトランジスタ)を含むカスコードトランジスタ群20、NMOSトランジスタN11〜N12(第2のカスコードトランジスタ)を含むカスコードトランジスタ群21を有している。

【0099】

図5に示すように、基準電流生成回路10は、PMOSトランジスタP1〜P5とスイッチSW1〜SW5との間に、それぞれPMOSトランジスタP11〜P15が接続されている。すなわち、PMOSトランジスタP11〜P15は、各ソースがそれぞれPMOSトランジスタP1〜P5の各ドレインに接続され、各ゲートがバイアス入力端子に共通接続され、各ドレインがそれぞれスイッチSW1〜SW5の一端に接続されている。

【0100】

したがって、PMOSトランジスタP0、PMOSトランジスタP1〜P5及びPMOSトランジスタP11〜P15によりカスコード接続されたカスコードカレントミラー回路を構成している。カスコードカレントミラー回路の効果により、ND2からみたP1〜P5およびP11〜P15の出力抵抗が高くなり、ND2が変動した場合においても精度よくカレントミラー比に応じた電流I0〜I5を生成できる。

【0101】

同様に、基準電流生成回路10は、NMOSトランジスタN1〜N2とND2の間に、それぞれNMOSトランジスタN11〜N12が接続されている。すなわち、NMOSトランジスタN1〜N2及びNMOSトランジスタN11〜N12によりカスコード接続されたカスコードカレントミラー回路を構成している。したがって、精度よくカレントミラー比に応じた電流が生成でき、ここでは、NMOSトランジスタN1及びN11と同じ電流Ioutが、NMOSトランジスタN2及びN12で生成される。なお、NMOSトランジスタN3,N4の図示を省略しているが、同様にカスコード接続されている。

【0102】

このように、本実施形態では、基準電流生成回路のカレントミラー回路をカスコード接続されたカスコードカレントミラー回路とした。これにより、カレントミラーの電流コピー比の精度が向上するため、基準電流IREFをより一定に保つことができる。

【0103】

(本発明の実施の形態3)

以下、図面を参照して本発明の実施の形態3について説明する。図6は、本発明の実施の形態3に係る基準電流生成回路10を含む半導体装置100の回路構成を示しており、その他の構成については、実施の形態1と同様である。なお、図6では、図3及び図4と同様にして、すでにテスタにより電流トリミングが行われており、ヒューズレジスタ15に電流コード値が設定されている状態である。

【0104】

図6の半導体装置100では、図3の回路構成に加えて、電流計22を有しており、電流計22、ADC118、CPU126、割り込みレジスタ16の順に接続されている。

【0105】

電流計22は、電流生成部11が生成する電流I0の電流値を測定する。電流I0の測定方法としては、電流計により直接電流I0を測定してもよいし、特性ばらつきの少ない高精度抵抗を用いて電流を測定してもよい。

【0106】

電流計22の測定値をADC118によりA/D変換し、CPU126がA/D変換された測定値を演算処理する。CPU126(電流演算処理部)は、電流I0の電流値の変動に応じて、基準電流IREFが一定となるように電流コード値を決定し、電流コード値を割り込みレジスタ16に設定する。トリミング完了後の電流I0の初期値と、現在の電流I0とを比較し、電流値の大小に応じて、電流コード値を決定する。なお、CPU126に限らず、その他のロジック回路により構成してもよい。

【0107】

なお、ここでは、電流I0を測定したがその他の電流等を測定してもよい。例えば、電流Ioutを測定し、電流Ioutの変動に応じて電流制御してもよい。また、基準電流IREF(電流Iout)が供給されているフィルタや発振回路の特性変動を検出し、この特性変動に応じて電流制御してもよい。

【0108】

このように、本実施形態では、テスタによりトリミング完了後に、半導体装置内部で、電流を測定し電流値の変動に応じて電流制御することとした。これにより、トリミング完了後に、温度変化等により電流がばらついた場合でも、基準電流IREFを一定に保つことができる。

【0109】

(本発明の実施の形態4)

以下、図面を参照して本発明の実施の形態4について説明する。図7は、本発明の実施の形態4に係る基準電流生成回路10を含む半導体装置100の回路構成を示しており、その他の構成については、実施の形態1、実施の形態3と同様である。なお、図6では、実施の形態3と同様に、すでにテスタにより電流トリミングが行われており、ヒューズレジスタ15に電流コード値が設定されている状態である。

【0110】

図7の半導体装置100では、図6の構成と比べて、電流計22の代わりに、温度センサ23を備えている。温度センサ23は、ダイオード等で構成することができる。また、温度センサ23として、定電圧源12に内蔵される温度センサを用いてもよい。

【0111】

温度センサ23は、半導体装置100の温度を測定し、この測定結果が、ADC118を介してCPU126に入力される。CPU126(温度演算処理部)は、温度センサ23の検出した温度の変動に応じて、基準電流IREFが一定となるように電流コード値を決定し、電流コード値を割り込みレジスタ16に設定する。例えば、抵抗R1の温度特性を予め設定しておき、検出する温度にしたがって、温度特性から抵抗R1の変動を求めることで、電流コード値を決定する。

【0112】

このように、本実施形態では、テスタによりトリミング完了後に、半導体装置内部で、温度を測定し温度の変動に応じて電流制御することとした。これにより、トリミング完了後に、温度変化により電流がばらついた場合でも、基準電流IREFを一定に保つことができる。

【0113】

(本発明の実施の形態5)

以下、図面を参照して本発明の実施の形態5について説明する。図8は、本発明の実施の形態5に係る半導体装置100及びテスト時のテスタ300の接続状態を示している。半導体装置100の内部構成については実施の形態1〜4と同様である。

【0114】

図8に示すように、本実施形態では、半導体装置100のプローブテスト時に、半導体装置100の外部端子T1〜T3と半導体装置100とを接続する。外部端子T1を介して、基準電流生成回路10とテスタ300とを接続し、外部端子T2を介して、レジスタ128(割り込みレジスタ及びヒューズレジスタ)とテスタ300とを接続し、外部端子T3を介して、メモリ127とテスタ300とを接続する。そして、テスタ300は、メモリ127のテストを行うとともに、図4と同様に、基準電流生成回路10の基準電流IREFのトリミングテストも行う。

【0115】

図9は、本発明の実施の形態5に係るテスト方法の流れを示している。図9に示すように、メモリのテスト工程において、まず、テスタ300は、半導体装置100に対しメモリのテストを行い(S201)、メモリのトリミングを行う(S202)。テスタ300は、プローブを外部端子T1〜T3に接続して、半導体装置100をテストモードに設定する。テスタ300は、外部端子T3を介してメモリ127の欠陥の有無を検証するためにテストを行う。そして、テスタ300は、メモリ127に欠陥を発見した場合には、欠陥メモリセルを救済するためにメモリの救済情報をメモリ127に設定し、メモリのトリミングを行う。

【0116】

次に、テスタ300は、半導体装置100に対し基準電流のテストを行い(S203)、基準電流のトリミングを行う(S204)。図4のS101〜S106と同様に、テスタ300は、外部端子T1を介して基準電流IREFを測定して、電流コード値を決定し、最適な電流コード値を外部端子T2を介してレジスタ128(ヒューズレジスタ15)に設定することで、基準電流のトリミングを行う。

【0117】

なお、図9のテスト方法において、先にS203〜S204の電流トリミングを実施し、次にS201〜S202のメモリトリミングを実施してもよい。また、電流トリミングとメモリトリミングを同時に実施してもよい。

【0118】

このように、本実施形態では、メモリのテスト及びトリミングと、基準電流のテスト及びトリミングを同じプローブテストにより実施することとした。メモリテストは、メモリの欠陥救済のために常に必要なテスト工程であるため、基準電流のためのテストを別工程で実施する必要がなく、効率よくテスト及びトリミングを行うことができる。

【0119】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、上記の例では、光ディスク装置について説明したが、定電流回路を有するその他の電子機器であってもよい。

【符号の説明】

【0120】

1 光ディスク装置

10 基準電流生成回路

11 電流生成部

12 定電圧源

13 電流切替部

14 電流制御部

15 ヒューズレジスタ

16 割り込みレジスタ

17 電流出力部

18 マルチプレクサ

19 内部バッファ

20 カスコードトランジスタ群

21 カスコードトランジスタ群

22 電流計

23 温度センサ

100 半導体装置

110 AFE(アナログフロントエンド)部

111 基準電圧生成回路

112 インタフェースIF

113 RF系回路

114 ウォブル検出回路

115 ライトPLL回路

116 サーボ系回路

117 APC回路

118 ADC

120 DSP(デジタルシグナルプロセッサ)部

121 データストローブ回路

122 デコーダ

123 エンコーダ

124 ATIP・ADIP回路

125 サーボDSP

126 CPU

127 メモリ

128 レジスタ

128a アナログレジスタ

128b デジタルレジスタ

200 ピックアップ

201 光電変換回路OEIC

202 フロントモニタダイオードFMD

203 レーザダイオードドライバLDD

300 テスタ

301 電流計

OP1 オペアンプ

R1 抵抗

P0〜P5,P11〜P15 PMOSトランジスタ

N1〜N4,N11〜N12 NMOSトランジスタ

SW1〜SW5,SW11〜SW12 スイッチ

T1〜T3 外部端子

【技術分野】

【0001】

本発明は、半導体装置、光ディスク装置及び半導体装置のテスト方法に関し、特に、所定の電流を生成する電流生成回路を有する半導体装置、光ディスク装置及び半導体装置のテスト方法に関する。

【背景技術】

【0002】

近年、光ディスク装置など様々な電子機器において、取り扱う情報量の増大に伴い、動作速度の高速化が急速に進んでいる。このため、より高速に安定して動作するため、電子機器に搭載される半導体装置の特性ばらつきを低減することが強く望まれている。

【0003】

例えば、半導体装置には、供給される基準電流に応じた周波数の発振クロックを生成する発振回路や、供給される基準電流に応じた周波数特性を有するフィルタ回路が設けられている。この発振クロックやフィルタの特性を安定させるためには、一定の基準電流を生成する定電流回路(基準電流回路)の特性変動を抑える必要がある。

【0004】

従来の定電流回路を備えた半導体装置として、例えば、図10及び図11の構成が知られている。

【0005】

図10に示すように、従来の半導体装置900は、半導体装置の内部に定電流回路910を備えており、半導体装置の外部に抵抗918が接続されている。定電流回路910は、定電圧源(VBG)911、オペアンプ912、PMOSトランジスタ913,914、NMOSトランジスタ915,916を備えている。

【0006】

オペアンプ912は、非反転(正転)入力端子が定電圧源911に接続され、出力端子がPMOSトランジスタ913のゲートとPMOSトランジスタ914のゲートに共通接続されている。PMOSトランジスタ913のソースとPMOSトランジスタ914のソースは電源電位VCCに共通接続され、オペアンプ912の反転入力端子とPMOSトランジスタ913のドレインが外部端子917に接続されている。

【0007】

NMOSトランジスタ915とNMOSトランジスタ916は、互いのドレイン及びゲートがPMOSトランジスタ914のドレインに共通接続され、互いのソースが接地電位GNDに共通接続されている。PMOSトランジスタ916のソースは、出力電流Ioutの出力先の回路に接続されている。そして、半導体装置900の外部では、外部端子917と接地電位GNDとの間に抵抗918が接続されている。

【0008】

従来の半導体装置900の定電流回路910では、定電圧源911の電圧と外部の抵抗918の抵抗値とに応じた電流I0が生成される。そして、PMOSトランジスタ913,914及びNMOSトランジスタ915,916を介して、電流I0と等しい出力電流Ioutが他の回路へ出力される。

【0009】

また、図11に示すように、従来の半導体装置901は、半導体装置の内部に定電流回路920を備えている。定電流回路920は、定電圧源(VBG)921、オペアンプ922、PMOSトランジスタ923,924、NMOSトランジスタ925、抵抗926を備えている。

【0010】

オペアンプ922は、非反転入力端子が定電圧源921に接続され、出力端子が反転入力端子とNMOSトランジスタ925のゲートに接続されている。NMOSトランジスタ925のソースと接地電位GNDとの間に抵抗926が接続されている。

【0011】

PMOSトランジスタ923とPMOSトランジスタ924は、互いのソースが電源電位VCCに共通接続され、互いのゲートがPMOSトランジスタ924のドレインとPMOSトランジスタ925のソースに共通接続されている。PMOSトランジスタ923のドレインは、出力電流Ioutの出力先の回路に接続されている。

【0012】

定電流回路920では、定電圧源921の電圧及びNMOSトランジスタ925の閾値電圧Vthから決まる電圧と、抵抗926の抵抗値とに応じた電流I0が生成される。そして、PMOSトランジスタ924,923を介して、電流I0と等しい出力電流Ioutが他の回路へ出力される。

【0013】

なお、特許文献1には、トリミング回路により電流をトリミングする定電流回路が記載されている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2010−217963号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

図10に示した従来の半導体装置900では、半導体装置の外部に抵抗918を外付けとしている。半導体装置900内の定電流回路910が生成する定電流は、定電圧源911の電圧と抵抗918の抵抗値とにより決まる。このため、抵抗918として特性ばらつきの小さい高精度な抵抗を接続することにより、定電流回路910の出力電流の変動を抑えることができる。抵抗918は半導体装置の製造ばらつき等による特性変動がないため、製造プロセス(fab)が変更となった場合でも一定の電流を生成することができる。

【0016】

しかしながら、従来の半導体装置900では、外部の抵抗を接続するための外部端子が必要となる。半導体装置に外部抵抗専用の外部端子を設けると、外部端子が増加するため、半導体装置の小型化や低コスト化の妨げとなる。特に、近年、半導体装置の小型化に伴い外部端子数は減少傾向にあるため、外部抵抗専用の外部端子を設けることは困難となってきている。また、従来の半導体装置900では、外部に接続する抵抗として、特性変動の少ない高精度な抵抗を用意する必要となり、そのような抵抗は一般にコストが高いことから、コストが増大するという問題がある。

【0017】

一方、図11に示した従来の半導体装置901は、従来の半導体装置900と比べると、外部端子が不要であり、外部に抵抗を用意する必要がないため、半導体装置900よりもコストを低減することが可能である。

【0018】

しかしながら、従来の半導体装置901は、抵抗926に製造ばらつき等による特性変動の影響を受けるため、製造プロセスが変更となった場合の特性変動が大きく、定電流回路920の出力電流のばらつきが大きいという問題がある。例えば、半導体装置内の抵抗の絶対値ばらつきが±20%とすると、定電流回路の出力電流も±20%変動することになる。

【0019】

このように、従来の半導体装置では、コストの低減を図りつつ、かつ、精度よく基準電流を生成することが困難であるという問題があった。

【課題を解決するための手段】

【0020】

本発明に係る半導体装置は、電流生成回路(図3の電流生成部11、電流切替部13及び電流出力部17に相当)、第1の外部端子(図3の外部端子T1に相当)、第2の外部端子(図3の外部端子T2に相当)及び電流制御回路(図3の電流制御部14に相当)を備えている。電流生成回路は、基準電流(Iout及びIREFに相当)を生成する電流生成回路である。また、第1の外部端子は、電流生成回路により生成された基準電流をテスタへ出力するための端子である。そして、第2の外部端子は、電流生成回路が生成する基準電流の電流値を制御するための電流制御データを、第1の外部端子から出力された基準電流に応じてテスタにより設定される端子である。さらに、電流制御回路は、第2の外部端子を介してテスタにより設定された電流制御データにしたがって、電流生成回路により生成される基準電流が所定値となるように調整する。以上の構成により、基準電流の電流値を一定の所定値にトリミングすることができるため、抵抗等により生じる電流ばらつきを防ぎ精度のよい基準電流を生成できる。また、外部に高精度な抵抗を別途用意する必要がないため、コストを低減することができる。

【0021】

ここで、電流生成回路は、抵抗電流生成部(図3の電流生成部11に相当)と電流切替部(図3の電流切替部13に相当)とを備えていてもよい。抵抗電流生成部は、定電圧に応じた抵抗電流を抵抗により生成する。電流切替部は、抵抗電流生成部により生成された抵抗電流をミラーする第1のカレントミラー回路のミラー比を、電流制御回路から入力される電流制御データに応じて切り替えることで基準電流を生成する。

【0022】

また、電流生成回路は、電流出力部(図3の電流出力部17に相当)をさらに備えていてもよい。電流出力部は、電流切替部により生成された基準電流を第2のカレントミラー回路によりミラーして出力する。

【0023】

また、上記第1のカレントミラー回路または上記第2のカレントミラー回路には、カスコードトランジスタ(図5のカスコードトランジスタ群20、カスコードトランジスタ群21に相当)が接続されていてもよい。これにより、カレントミラー回路の電流ミラーの精度が向上するため、より精度のよい基準電流を生成することができる。

【0024】

さらに、上記半導体装置は、電流生成回路が生成する基準電流を測定する電流測定回路(図6の電流計に相当)を有していてもよい。そして、テスタにより電流制御データが設定された後、電流制御回路は、電流測定回路による基準電流の測定結果に応じて、電流生成回路により生成される基準電流が所定値となるようにさらに調整してもよい。また、上記半導体装置は、温度を測定する温度センサ(図7の温度センサ23に相当)を有していてもよい。そして、テスタにより電流制御データが設定された後、電流制御回路は、温度センサによる温度の測定結果に応じて、前記電流生成回路により生成される基準電流が前記所定値となるようにさらに調整してもよい。これにより、テスタにより電流トリミングした後においても、半導体装置内部で基準電流を一定の所定値とすることができるため、温度等により生じる電流ばらつきを防ぎさらに精度のよい基準電流を生成できる。

【0025】

また、上記半導体装置では、テスタが、メモリのテストと基準電流のテストとを同じ工程で実施してもよい。すなわち、テスタが、半導体装置に含まれるメモリの欠陥救済のためのメモリテスト工程において、第1の外部端子から出力された基準電流を測定し、基準電流の測定結果に応じて前記第2の外部端子へ電流制御データを設定してもよい。これにより、メモリと基準電流のテスト及びトリミングをまとめて実施できるため、効率よくテスト及びトリミングを行うことができ、テストのコストを低減することができる。

【0026】

本発明に係る光ディスク装置は、光ディスクにレーザ光を照射するピックアップと、ピックアップの動作を制御する半導体装置を備えている。そして、半導体装置は、電流生成回路、第1の外部端子、第2の外部端子、電流制御回路及び信号処理回路(図1のRF系回路113、ウォブル検出回路114、ライトPLL115、サーボ系回路116に相当)を備えている。電流生成回路、第1の外部端子、第2の外部端子及び電流制御回路の構成は上記半導体装置と同様である。また、信号処理回路は、電流制御回路により記調整された電流生成回路の基準電流に基づいて、ピックアップから出力される信号を処理する。以上の構成により、光ディスク装置において、基準電流の電流値を一定の所定値にトリミングし、抵抗等により生じる電流ばらつきを防ぎ精度のよい基準電流を生成できる。また、外部に高精度な抵抗を別途用意する必要がないため、コストを低減することができる。そして、基準電流を安定させることで、光ディスク装置における信号処理回路の特性ばらつきを抑止し、倍速モード等の場合でも精度よく動作することが可能である。

【0027】

本発明に係る半導体装置のテスト方法は、基準電流を生成する電流生成回路と生成される基準電流を調整する電流制御回路と第1及び第2の外部端子とを有する半導体装置のテスト方法である。半導体装置のテスト方法では、まず、テスタは、第1及び第2の外部端子にプローブを接続し、第1の外部端子を介して電流生成回路と電気的に接続し、第2の外部端子を介して電流制御回路と電気的に接続する。次に、テスタは、基準電流の電流値を制御するための電流制御データの初期値を決定し、初期値として決定した前記電流制御データを前記第2の外部端子を介して電流制御回路へ変更可能に設定する。次に、電流制御回路は、設定された電流制御データにしたがって、電流生成回路により生成される基準電流を調整する。次に、電流生成回路は、電流制御データにより調整された基準電流を第1の外部端子を介してテスタへ出力する。次に、テスタは、出力された基準電流の電流値を測定し、基準電流の測定結果と所定値との比較結果に応じて、電流制御データの最適値を決定する。次に、テスタは、最適値として決定した電流制御データを第2の外部端子を介して電流制御回路へ変更不可能に設定する。以上の動作により、基準電流の電流値を一定の所定値にトリミングすることができるため、抵抗等により生じる電流ばらつきを防ぎ精度のよい基準電流を生成できる。また、外部に高精度な抵抗を別途用意する必要がないため、コストを低減することができる。

【発明の効果】

【0028】

本発明によれば、コストの低減を図りつつ、かつ、精度よく基準電流を生成することが可能な半導体装置、光ディスク装置及び半導体装置のテスト方法を提供することができる。

【図面の簡単な説明】

【0029】

【図1】本発明の実施の形態1に係る光ディスク装置の構成を示すブロック図である。

【図2】本発明の実施の形態1に係る光ディスク装置の信号特性を示すグラフである。

【図3】本発明の実施の形態1に係る半導体装置の回路構成を示す回路図である。

【図4】本発明の実施の形態1に係る半導体装置のテスト方法(トリミング方法)を示すフローチャートである。

【図5】本発明の実施の形態2に係る半導体装置の回路構成を示す回路図である。

【図6】本発明の実施の形態3に係る半導体装置の回路構成を示す回路図である。

【図7】本発明の実施の形態4に係る半導体装置の回路構成を示す回路図である。

【図8】本発明の実施の形態5に係る半導体装置のテスト構成を示す構成図である。

【図9】本発明の実施の形態5に係る半導体装置のテスト方法(トリミング方法)を示すフローチャートである。

【図10】従来の半導体装置の回路構成を示す回路図である。

【図11】従来の半導体装置の回路構成を示す回路図である。

【発明を実施するための形態】

【0030】

(本発明の実施の形態1)

以下、図面を参照して本発明の実施の形態1について説明する。図1は、本発明の実施の形態1に係る光ディスク装置(光ディスクシステム)1の構成を示している。図1に示すように、光ディスク装置1は、半導体装置100とピックアップ200とを備えている。

【0031】

ピックアップ200は、半導体装置100からの制御にしたがって光ディスクにレーザ光を照射する光ピックアップである。ピックアップ200は、光電変換回路OEIC201、フロントモニタダイオードFMD202、レーザダイオードドライバLDD203を備えている。ピックアップ200内には、その他、光ディスクに対してレーザ光を照射するレーザダイオードや、フォーカス方向及びトラッキング方向に位置合わせをするサーボ機構(アクチュエータ)等が備えられている(不図示)。

【0032】

レーザダイオードドライバLDD203は、レーザダイオードを駆動する駆動回路である。フロントモニタダイオードFMD202は、レーザダイオードの発光強度を調整するために光ディスクからの反射光を検出する検出回路である。

【0033】

光電変換回路OEIC201は、光ディスクからの反射光を電気信号に変換する変換回路である。例えば、光ディスクからの反射光を検出する検出回路(フォトディテクタ)がA,B,C,Dの4つの領域に田の字状に分割されている。光電変換回路OEIC201は、4つの各領域で検出された信号A,B,C,Dを電気信号として出力する。また、信号A,B,C,Dとは別にデータを示すRF(Radio Frequency)信号を出力することも可能である。

【0034】

半導体装置100は、AFE(Analog Front End)部110、DSP(Digital Signal Processor )部120を備えている。また、半導体装置100は、外部装置と接続するための外部端子T1,T2を有している。後述のように、外部端子T1,T2は、テスト時(トリミング時)にのみテスト端子として使用し、通常動作時は、各内部回路が外部と入出力を行うための通常の外部端子として使用可能である。

【0035】

AFE部110は、ピックアップ200から入力される各信号をDSP部120で処理可能な信号に変換するアナログ回路である。DSP部120は、AFE部110を介して入力されるピックアップ200の各信号に基づいて演算処理を行い、データのリード/ライト、サーボ制御等を行うデジタル回路である。

【0036】

例えば、半導体装置100は、SoC(System on Chip)やSiP(System in Package)の半導体装置である。AFE部110及びDSP部120を含む1つの半導体チップから構成されてもよいし、AFE部110の半導体チップとDSP部120の半導体チップを1パッケージとして構成してもよいし、AFE部110の半導体チップとDSP部120の半導体チップ、メモリ127の半導体チップを1パッケージとして構成してもよい。

【0037】

AFE部110は、基準電流生成回路10、基準電圧生成回路111、インタフェースIF112、RF系回路113、ウォブル(Wobble)検出回路114、ライトPLL115、サーボ系回路116、APC回路(自動パワー制御回路)117、ADC(A/Dコンバータ)118を備えている。AFE部110には、レジスタ128の一部であるアナログレジスタ128aも含まれている。

【0038】

基準電流生成回路10は、一定の基準電流IREF(定電流)を生成し、半導体装置100内のAFE部110及びDSP部120の各回路へ基準電流IREF(バイアス電流)を供給する定電流回路である。後述のように、基準電流生成回路10は、レジスタ128に保持されている電流コード値(電流制御データ)にしたがって基準電流IREFを可変に設定することができる。また、基準電流生成回路10は、外部端子T1に接続されており、テスト時に、生成した基準電流IREFを外部端子T1を介して外部のテスタへ出力する。

【0039】

基準電圧生成回路111は、一定の基準電圧VREF(定電圧)を生成し、半導体装置100内のAFE部110及びDSP部120の各回路へ基準電圧VREF(バイアス電圧)を供給する定電圧回路である。基準電圧生成回路111は、基準電圧VREFとして温度等によるばらつきが少ないバンドギャップ電圧VBGを生成するバンドギャップ電圧生成回路である。

【0040】

インタフェースIF112は、ピックアップ200とのインタフェースであり、ピックアップ200の光電変換回路OEIC201で光電変換された各信号が入力され、レベル変換等を行って、各信号を処理するRF系回路113、ウォブル検出回路114、サーボ系回路116へ出力する。すなわち、インタフェースIF112は、信号A、B、C、Dから、RF信号、ウォブル信号、フォーカスエラー信号、トラッキングエラー信号等を生成するために各回路へ出力する。また、ピックアップ200からRF信号が入力される場合は、インタフェースIF112は、入力されたRF信号をRF系回路113へ出力する。

【0041】

RF系回路113は、RF信号からデータを示す再生データ信号を生成する。RF系回路113は、インタフェースIF112からRF信号が入力される場合は、入力される信号を使用し、信号A,B,C,Dが入力される場合には、例えば、信号(A+B+C+D)の演算からRF信号を生成する。RF系回路113は、基準電流IREFに応じて動作するフィルタ等を有している。RF系回路113は、RF信号からフィルタにより所定周波数成分を除去し、包絡線の抽出等を行って、再生データ信号を生成する。

【0042】

ウォブル検出回路114は、インタフェースIF112により入力される信号から、光ディスク上のアドレスや同期タイミングを示すウォブルを検出してウォブル信号を生成する。ウォブル検出回路114は、基準電流IREFに応じて動作するフィルタ等を有している。例えば、ウォブル検出回路114は、信号(A+D)−(B+C)の演算を行い、演算された信号からフィルタにより所定周波数成分を除去し、包絡線の抽出等を行って、ウォブル信号を生成する。

【0043】

ライトPLL115は、ウォブル検出回路114により生成されたウォブル信号に基づいて、光ディスクに書き込みを行うためのライトクロックを生成する。ライトPLL115は、基準電流IREFに応じて動作する発振回路を有している。ライトPLL115は、ウォブル信号が入力されると、発振回路による発振を繰り返してロック状態となり、ライトクロックを生成する。

【0044】

サーボ系回路116は、インタフェースIF112により入力される信号から、サーボ制御のためのサーボ制御信号を生成する。サーボ系回路116は、位相差を検出するDPD回路を有している。例えば、サーボ系回路116は、信号(A+B)−(C+D)の演算からトラッキング方向に制御するためのトラッキングエラー信号TEを生成し、信号(A+C)−(B+D)の演算からフォーカス方向に制御するためのフォーカスエラー信号FEを生成し、信号(A+C),(B+D)の位相差からサーボ制御するためのDPD信号を生成し、サーボ制御信号として出力する。

APC回路(自動パワー制御回路)117は、フロントモニタダイオードFMD202が検出したレーザダイオードの発光強度が入力され、検出した発光強度に応じて、レーザダイオードが所定の発光強度となるように、レーザダイオードドライバLDD203へ発光制御する発光制御信号を出力する。

【0045】

ADC118は、サーボ系回路116のサーボ制御信号やAPC回路117の出力するアナログ信号をデジタル信号に変換して、DSP部120のサーボDSP125やCPU126へ出力する。なお、ADC118のデータ処理は、アナログ回路でもデジタル回路でも構成できるため、AFE部110に設けてもよいし、DSP部120に設けてもよい。

【0046】

DSP部120は、データストローブ回路121、デコーダ122、エンコーダ123、ATIP・ADIP回路124、サーボDSP125、CPU126、メモリ127、レジスタ128を備えている。

【0047】

データストローブ回路121は、RF系回路113により生成された再生データ信号からデータをデコードするタイミングを示すデータストローブ信号を生成する。デコーダ122は、データストローブ回路121により生成されたデータストローブ信号のタイミングに基づいて、再生データ信号を伸長・復号化処理等によりデコードし、リードデータを生成する。リードデータは、メモリ127に記憶されて、外部のデータ処理装置等へ出力される。

【0048】

エンコーダ123は、外部のデータ処理装置等からメモリ127に記憶されたライトデータを、圧縮・符号化処理等によりエンコードし、ライトデータを生成する。ライトデータは、インタフェースIF112を介してピックアップ200へ出力され、ライトPLL115により生成されたライトクロックに基づいて光ディスクへ書き込まれる。

【0049】

ATIP・ADIP回路124は、ウォブル検出回路114により生成されたウォブル信号に対し、ATIP復調やADIP復調を行い、アドレス情報や絶対位置情報を生成する。このアドレス情報や絶対位置情報に基づいて、ライトデータの書き込み等が行われる。

【0050】

サーボDSP125は、ADC118を介して入力されるサーボ制御信号に基づいて、ピックアップ200のサーボを制御し、ピックアップ200の位置を調整する。サーボDPS125は、トラッキングエラー信号TE、フォーカスエラー信号FE、DPD信号等に基づいて、演算処理を行い、トラッキングサーボやフォーカスサーボを制御してピックアップ200の位置合わせを行う。

【0051】

CPU126は、メモリ127に記憶されたプログラムを実行し、プログラムにしたがって演算処理を行ってシステム全体の動作を制御する演算処理部である。メモリ127は、フラッシュメモリやSDRAM等で構成され、各種のプログラムやデータを記憶し、また、光ディスクのリードデータ、ライトデータ等を記憶する。

【0052】

レジスタ128は、CPU126における演算処理等で用いるデータや、各回路で必要とするデータを保持する。レジスタ128は、アナログ回路で構成されるアナログレジスタ128aと、デジタル回路で構成されるデジタルレジスタ128bを含んでいる。

【0053】

このような半導体装置100において、本実施形態では、基準電流生成回路10の生成する基準電流IREFは、主に、RF系回路113、ウォブル検出回路114、ライトPLL115、サーボ系回路116へ供給されている。これらの回路に基準電流IREFを供給し、回路動作を電流制御することで、電圧制御の場合と比べて、幅広いダイナミックレンジに対応でき、必要な電源電圧を小さくすることができる。

【0054】

RF系回路113、ウォブル検出回路114では、内部のフィルタに基準電流IREFが供給されている。このフィルタは、例えば、gmcフィルタであり、入力される基準電流IREFに従って動作し、基準電流IREFを用いたフィルタの設定を切り替えることでブースト量・ブースト周波数やカットオフ周波数等の周波数特性を変化させることができる。

【0055】

図2は、RF系回路113におけるRF信号の周波数特性を示している。光ディスク装置では、読み出し速度を選択することができ、選択される読み出し速度によってRF信号の周波数特性が異なる。たとえば、図2(a)は、ブースト前のRF信号、図2(b)は、ある光ディスクの4倍速モードで読み出す場合のRF信号、図2(c)は、8倍速モードで読み出す場合のRF信号の周波数特性である。

【0056】

RF系回路113では、このRF信号の周波数特性に合わせてフィルタの特性を設定する。すなわち、図2(b)、図2(c)に示すように倍速モードの場合、フィルタは倍速数に応じた周波数をブーストする設定となる。また、他の倍速モードでは、他の周波数をブーストまたはカットする必要がある。

【0057】

したがって、RF系回路113やウォブル検出回路114では、倍速モードによってフィルタ特性のブーストやカットが必要であり、より高精度な特性が求められるため、フィルタに供給される基準電流IREFのばらつきを抑える必要がある。

【0058】

また、サーボ系回路116では、基準電流IREFに応じて、ピックアップから入力されるDC信号のオフセット調整や入力バッファのバイアス調整等が行われている。このため、サーボ系回路116で、入力信号からサーボ制御信号を精度よく生成するためには、基準電流IREFのばらつきを抑える必要がある。

【0059】

なお、ADC118は、サーボ系回路116から出力される複数のサーボ制御信号ごとにレベルがばらついていると、正常にA/D変換できない場合があるため、サーボ制御信号のレベルを一定に保つためにも、サーボ系回路116に供給する基準電流IREFのばらつきを抑える必要がある。

【0060】

また、ライトPLL回路115では、基準電流IREFに応じて、ウォブル信号に基づいた所定周波数のライトクロックを生成している。このため、ライトPLL回路115で、ウォブル信号に同期したライトクロックを精度よく生成するためには、基準電流IREFのばらつきを抑える必要がある。

【0061】

このため、本実施形態では、基準電流IREFの精度を向上させ、RF系回路113、ウォブル検出回路114、ライトPLL115、サーボ系回路116等を安定して動作させるために、以下のような構成とした。図3は、本発明の実施の形態1に係る基準電流生成回路10の回路構成、及びテスト時のテスタ300の接続状態を示している。

【0062】

図3に示すように、半導体装置100における基準電流生成回路10は、電流生成部11、電流切替部13、電流制御部14、電流出力部17を備えている。例えば、電流生成部11と電流切替部13と電流出力部17とが、基準電流IREFを生成する電流生成回路であり、電流制御部14が、電流コード値にしたがって、基準電流IREFを所定値となるように調整する電流制御回路である。

【0063】

電流生成部(抵抗電流生成部)11は、定電圧VBGと抵抗に基づいて、主に抵抗によるばらつきを含む電流I0を生成する。電流生成部11は、定電圧源12、オペアンプOP1、PMOSトランジスタP0、抵抗R1を備えている。

【0064】

定電圧源12は、定電圧として定電圧(バンドギャップ電圧)VBGを生成するバンドギャップ電圧生成回路である。定電圧源12は、製造ばらつきによる電圧変動が少なく、温度変化に対しても電圧変動が少なくなるように回路構成されている。例えば、定電圧源12は、図1の基準電圧生成回路111に対応しており、定電圧VBGは、基準電圧生成回路111が生成する基準電圧VREFそのものか、もしくは基準電圧VREFに基づいた所定の電圧である。

【0065】

オペアンプOP1は、非反転入力端子と反転入力端子に入力される入力信号を差動増幅した出力信号を出力端子から出力する差動増幅回路である。オペアンプOP1は、非反転入力端子に定電圧源12からバンドギャップ電圧VBGが入力されている。PMOSトランジスタP0は、ソースが電源電位VCCに接続され、ゲートがオペアンプOP1の出力端子に接続され、ドレイン(ノードND1)がオペアンプOP1の反転入力端子と抵抗R1の一端とに接続されている。

【0066】

抵抗R1の他端は接地電位GNDに接続されている。抵抗R1は、ポリシリコンにより形成されたポリシリコン抵抗である。抵抗R1の抵抗値は、主に製造工程により生じる絶対値ばらつきを有し、また、温度変化によるばらつきも有する。

【0067】

オペアンプOP1では反転入力端子にノードND1から帰還信号が入力されるため、オペアンプOP1、PMOSトランジスタP0及び抵抗R1により負帰還増幅回路が構成される。そうすると、オペアンプOP1はイマジナルショートの状態となって、非反転入力端子と反転入力端子の電圧が同じとなり、PMOSトランジスタP0と抵抗R1間のノードND1の電圧が、定電圧VBGと等しくなる。したがって、抵抗R1及びPMOSトランジスタP0に、定電圧VBGと抵抗R1の抵抗値に応じた電流I0(抵抗電流)が流れる。例えば、定電圧VBG=1.25V、抵抗R1=12.5KΩとすると、電流I0=100μAとなる。

【0068】

電流切替部(電流選択部)13は、電流生成部11により生成された電流I0をもとに、電流コード値にしたがって電流値を切り替えて出力電流Ioutを生成する。電流切替部13は、電流I0をミラーするカレントミラー回路のミラー比を、電流コード値に応じて切り替えることで出力電流Ioutを生成する。電流切替部13は、電流コード値のデジタル値に応じたアナログ値の電流を出力する電流DAC(D/Aコンバータ)でもある。電流切替部13は、PMOSトランジスタP1〜P5、スイッチSW1〜SW5を備えている。

【0069】

PMOSトランジスタP1〜P5は、各ソースが電源電位VCCに共通接続され、各ゲートがPMOSトランジスタP0のゲートに共通接続され、各ドレインがそれぞれスイッチSW1〜SW5を介して出力電流Ioutを生成するノードND2(基準電流生成ノード)に接続されている。

【0070】

PMOSトランジスタP0とPMOSトランジスタP1〜P5とはカレントミラー接続された第1のカレントミラー回路を構成している。したがって、PMOSトランジスタP0の電流I0に対して、PMOSトランジスタP0とPMOSトランジスタP1〜P5とのトランジスタサイズ比に応じた電流I1〜I5が、PMOSトランジスタP1〜P5に生成される。そうすると、ノードND2において電流I1〜I5を合計した電流が出力電流Ioutとなる。このため、スイッチSW1〜SW5のオン/オフを切り替えて合計する電流I1〜I5を選択することで出力電流Ioutを可変可能としている。

【0071】

ここでは、スイッチSW1は常にオンとし、スイッチSW2〜SW5を切り替え可能とする。4ビットの電流コード値の各ビットをスイッチSW2〜SW5及びPMOSトランジスタP2〜P5に対応付け、電流コード値にしたがってスイッチSW2〜SW5をオン/オフし出力電流Ioutを切り替える。なお、スイッチSW1を切り替え可能としてもよい。

【0072】

電流コード値のMSB(最上位ビット)がスイッチSW2及びPMOSトランジスタP2に対応し、電流コード値のLSB(最下位ビット)がスイッチSW5及びPMOSトランジスタP5に対応している。PMOSトランジスタP2:P3:P4:P5のサイズ比(カレントミラー比)は、8:4:2:1であり、電流I2:I3:I4:I5の比も、8:4:2:1となる。これにより、電流コード値の各ビットの数値に対応した電流Ioutが生成される。

【0073】

例えば、PMOSトランジスタP0〜P5の電流を、I0=100μA、I1=78μA、I2=24μA、I3=12μA、I4=6μA、I5=3μAとする。基準となるPMOSトランジスタP5のW/Lサイズを基準サイズとして、PMOSトランジスタP0〜P4を、PMOSトランジスタP5に対する電流比に応じたサイズとする。この場合、Iout=78μA+(電流コード値×3)μAとなる。したがって、電流コード値=(0001)の場合、Iout=78+3=81μAとなり、電流コード値=(0111)の場合、Iout=78+12+6+3=99μAとなり、電流コード値=(1111)の場合、Iout=78+24+12+6+3=123μAとなる。

【0074】

電流制御部14は、ヒューズレジスタ15または割り込みレジスタ16の電流コード値にしたがって電流切替部13が生成する電流Ioutの電流値を制御する。電流制御部14は、スイッチSW1〜SW5、ヒューズレジスタ15及び割り込みレジスタ16に接続されている。電流制御部14は、ロジック回路で構成されており、ヒューズレジスタ15または割り込みレジスタ16に保持されている電流コード値に応じた制御信号を生成し、スイッチSW1〜SW5のオン/オフを切り替える。

【0075】

ヒューズレジスタ15と割り込みレジスタ16のいずれの電流コード値により電流制御するかは、選択可能である。例えば、いずれを選択するか制御する選択制御信号をCPUから電流制御部14に供給し、選択制御信号にしたがって電流コード値を選択してもよい。また、ヒューズレジスタ15の電流コード値を優先的に設定してもよいし、割り込みレジスタ16の電流コード値を優先的に設定してもよい。この場合、両方のレジスタに電流コード値が設定されている場合、優先させるレジスタの電流コード値を使用する。

【0076】

また、ヒューズレジスタ15と割り込みレジスタ16の両方の電流コード値により電流制御してもよい。例えば、ヒューズレジスタ15の電流コード値を基準値とし、割り込みレジスタの電流コード値を補正値として、基準値と補正値の加算値あるいは減算値により電流制御してもよい。

【0077】

ヒューズレジスタ15は、ヒューズの切断により電流コード値を固定的に変更不可能な状態で保持し、割り込みレジスタ16は、CPUやテスタ等からの入力により電流コード値を動的に変更可能な状態で保持する。ヒューズレジスタ15及び割り込みレジスタ16は、外部端子T2に接続されており、テスタ300から外部端子T2を介して電流制御値を書き込むことができる。外部端子T2は、テスタ300からレジスタの書き込みを制御するレジスタ制御端子である。なお、ヒューズレジスタ15及び割り込みレジスタ16は、図1のレジスタ128のアナログレジスタ128aもしくはデジタルレジスタ128bに対応している。

【0078】

電流出力部17は、電流切替部13により生成された出力電流Iout(基準電流IREF)を半導体装置100内の各回路へ出力し、また、テストのために外部へも出力する。電流出力部17は、NMOSトランジスタN1〜N4を備えている。

【0079】

NMOSトランジスタN1のドレインが、ノードND2に接続されるとともに、NMOSトランジスタN1〜N4のゲートに共通接続されている。NMOSトランジスタN1〜N4のソースは接地電位GNDに共通接続されている。NMOSトランジスタN2〜N4のドレインは、それぞれ出力電流Ioutの出力先の回路に接続されている。

【0080】

NMOSトランジスタN1とNMOSトランジスタN2〜N4とはカレントミラー接続された第2のカレントミラー回路を構成している。したがって、NMOSトランジスタN1の電流Ioutに対して、NMOSトランジスタN1とNMOSトランジスタN2〜4とのトランジスタサイズ比に応じた電流がNMOSトランジスタN2〜N4に流れる。ここでは、NMOSトランジスタN1〜N4は全て同じサイズのトランジスタであり、NMOSトランジスタN1の電流と同じ出力電流Iout(基準電流IREF)が、NMOSトランジスタN2〜N4にも流れて、各接続先の回路に出力される。なお、NMOSトランジスタN2〜N4のサイズを変更して、各回路に出力電流Ioutに基づいた電流を出力することもできる。

【0081】

NMOSトランジスタN2,N3は、半導体装置100の内部回路へ電流Iout(基準電流IREF)を出力する出力回路である。すなわち、電流Ioutを、RF系回路113、ウォブル検出回路114、ライトPLL115、サーボ系回路116等へ出力する。

【0082】

NMOSトランジスタN4は、半導体装置100の外部のテスタ300へ電流Iout(基準電流IREF)を出力する出力回路である。NMOSトランジスタN4は、マルチプレクサ18、内部バッファ19を介して外部端子T1に接続される。

【0083】

マルチプレクサ18は、NMOSトランジスタN4の他に、通常動作時に外部装置と入出力を行う内部回路と接続されている。マルチプレクサ18と外部端子T1との接続、内部バッファ19と外部端子T1との接続はスイッチSW11、SW12により切り替えられる。

【0084】

通常動作時、マルチプレクサ18が内部回路との接続を選択し、スイッチSW11がオン、スイッチSW12がオフしている。このため、内部回路と外部端子T1が接続された状態となり、外部端子T1を介して、内部回路と外部装置が電気的に接続される。また、テスト時(トリミング時)は、マルチプレクサ18、スイッチSW11,SW12にテスト選択信号が入力されると、マルチプレクサ18がNMOSトランジスタN4との接続を選択し、スイッチSW11がオフし、スイッチSW12がオンする。このため、NMOSトランジスタN4と外部端子T1が接続された状態となり、外部端子T1を介して、NMOSトランジスタN4とテスタ300とが電気的に接続され、テスタ300へ出力電流Iout(基準電流IREF)が出力される。

【0085】

なお、外部端子T1も同様にテスト選択信号により、通常動作時とテスト時で接続が切り替えられて、テスト時にのみ、外部端子T1を介してヒューズレジスタ15及び割り込みレジスタ16とテスタ300とが接続される。

【0086】

テスタ300は、半導体装置100の動作をテストするための装置であり、また、基準電流生成回路10の出力電流Iout(基準電流IREF)を測定して、所定の電流となるようにトリミングを行う装置である。

【0087】

テスタ300は、複数のプローブを有しており、プローブテスト時に半導体装置100の外部端子T1,T2にプローブを接続する。テスタ300は、電流計301を有しており、外部端子T1を介してNMOSトランジスタN4から出力される出力電流Ioutの電流を測定する。テスタ300は、出力電流Ioutの測定結果に応じて、出力電流Ioutが所定値となるように電流コード値を決定し、外部端子T2を介してヒューズレジスタ15または割り込みレジスタ16へ書き込む。

【0088】

出力電流Ioutの電流測定方法として、種々の方法が採用できる。例えば、テスタ300のテストボード上に設けられた特性ばらつきの少ない高精度抵抗を外部端子T1に接続して、電圧変換した値により電流測定してもよい。また、テスタ300が有する電流計により、電流Ioutを直接測定してもよい。

【0089】

図4は、本発明の実施の形態1に係るテスト方法の流れを示している。このテスト方法は、図3の構成により、テスタ300が半導体装置100の基準電流IREFをトリミングする方法である。

【0090】

まず、テスタ300は、LSIを初期化する(S101)。テスタ300は、基準電流IREFをトリミングするため、プローブを外部端子T1,T2に接続し、半導体装置100をテストモードに設定し、必要な初期設定を行う。ここでは、電流コード値の初期値を決定する。4ビットの初期値としては、最小値(0000)、最大値(1111)、中心値(0111または1000)等を使用できる。中心値から測定を開始することが、最も効率よくテストできるため、中心値を初期値に決定する。また、他の半導体装置100のテストがすでに完了している場合、他の半導体装置100でトリミング設定した電流コード値を初期値と決定してもよい。

【0091】

次に、テスタ300は、電流コード値を割り込みレジスタ16に設定する(S102)。テスタ300は、S101またはS104の判定により決定した電流コード値を検証するため、外部端子T2を介して割り込みレジスタ16へ書き込む。S104の電流判定後に再度設定する場合には、測定した測定電流と目標とする目標電流との大小に応じて、電流コード値を1(1LSB)ずつ加算または減算し、電流を逐次比較する。1より大きい数値を加算または減算してもよいし、順次中心値を選択して二分探索するようにしてもよい。目標値との差分に応じた値を加算または減算してもよい。また、他の半導体装置100のテストがすでに完了している場合、他の半導体装置100で加算または減算した値をもとに設定してもよい。

【0092】

次に、テスタ300は、半導体装置100の基準電流IREFの電流を測定する(S103)。テスタ300は、外部端子T2を介して出力される基準電流IREFを、電流計等により測定する。

【0093】

次に、テスタ300は、測定した基準電流IREFの大小を判定する(S104)。テスタ300は、測定した基準電流IREFの電流値と、目標とする目標電流値とを比較し、基準電流IREFが目標とする範囲内かどうか判定する。例えば、±1LSBの範囲かどうか判定する。つまり、1LSBが3μAとすると、±3μAの範囲かどうか判定する。±1LSBの範囲内であれば、現在の電流コード値を最適値として決定してS105へ進み、±1LSBの範囲外であれば、S102以降を再度繰り返し、電流コード値の最適値を求める。

【0094】

次に、テスタ300は、電流コード値をヒューズレジスタ(トリミング用メモリ)15に格納する(S105)、トリミングを実行する(S106)。テスタ300は、電流測定により最適値と決定された電流コード値を、外部端子T2を介してヒューズレジスタ15へ書き込む。これにより、電流コード値が固定的に設定され、基準電流IREFが絶対値ばらつきの無い電流にトリミングされる。

【0095】

以上のように、本実施形態では、半導体装置の基準電流をテスタにより測定し、基準電流が所定値となるように電流コード値を決定し、電流コード値を半導体装置に設定するようにした。これにより、抵抗の絶対値ばらつきにより生じる電流変動をトリミングすることができるため、精度のよい基準電流を生成することができる。実際に出力される基準電流に基づいて電流をトリミングするため、抵抗のばらつきの他、VBGのばらつき等も含めてトリミングすることができる。また、外部端子を介して外部に抵抗を接続する必要がないため、効果な抵抗を用意する必要がなく、外部端子も不要であるため、コストを低減することができる。

【0096】

従来回路では、例えば±20%の電流ばらつきを有する場合、要求されるダイナミックレンジと帯域を確保するためには、−20%の特性を考慮して電力を20%大きくする必要があるが、本実施形態では、電流をトリミングして安定化させることで、各ブロックのバイアス電流を必要最小限とすることができるため、電力低減を図ることが可能である。

【0097】

(本発明の実施の形態2)

以下、図面を参照して本発明の実施の形態2について説明する。図5は、本発明の実施の形態2に係る基準電流生成回路10の回路構成を示しており、その他の構成については、実施の形態1と同様である。

【0098】

図5の基準電流生成回路10では、図3の回路構成に加えて、PMOSトランジスタP11〜P15(第1のカスコードトランジスタ)を含むカスコードトランジスタ群20、NMOSトランジスタN11〜N12(第2のカスコードトランジスタ)を含むカスコードトランジスタ群21を有している。

【0099】

図5に示すように、基準電流生成回路10は、PMOSトランジスタP1〜P5とスイッチSW1〜SW5との間に、それぞれPMOSトランジスタP11〜P15が接続されている。すなわち、PMOSトランジスタP11〜P15は、各ソースがそれぞれPMOSトランジスタP1〜P5の各ドレインに接続され、各ゲートがバイアス入力端子に共通接続され、各ドレインがそれぞれスイッチSW1〜SW5の一端に接続されている。

【0100】

したがって、PMOSトランジスタP0、PMOSトランジスタP1〜P5及びPMOSトランジスタP11〜P15によりカスコード接続されたカスコードカレントミラー回路を構成している。カスコードカレントミラー回路の効果により、ND2からみたP1〜P5およびP11〜P15の出力抵抗が高くなり、ND2が変動した場合においても精度よくカレントミラー比に応じた電流I0〜I5を生成できる。

【0101】

同様に、基準電流生成回路10は、NMOSトランジスタN1〜N2とND2の間に、それぞれNMOSトランジスタN11〜N12が接続されている。すなわち、NMOSトランジスタN1〜N2及びNMOSトランジスタN11〜N12によりカスコード接続されたカスコードカレントミラー回路を構成している。したがって、精度よくカレントミラー比に応じた電流が生成でき、ここでは、NMOSトランジスタN1及びN11と同じ電流Ioutが、NMOSトランジスタN2及びN12で生成される。なお、NMOSトランジスタN3,N4の図示を省略しているが、同様にカスコード接続されている。

【0102】

このように、本実施形態では、基準電流生成回路のカレントミラー回路をカスコード接続されたカスコードカレントミラー回路とした。これにより、カレントミラーの電流コピー比の精度が向上するため、基準電流IREFをより一定に保つことができる。

【0103】

(本発明の実施の形態3)

以下、図面を参照して本発明の実施の形態3について説明する。図6は、本発明の実施の形態3に係る基準電流生成回路10を含む半導体装置100の回路構成を示しており、その他の構成については、実施の形態1と同様である。なお、図6では、図3及び図4と同様にして、すでにテスタにより電流トリミングが行われており、ヒューズレジスタ15に電流コード値が設定されている状態である。

【0104】

図6の半導体装置100では、図3の回路構成に加えて、電流計22を有しており、電流計22、ADC118、CPU126、割り込みレジスタ16の順に接続されている。

【0105】

電流計22は、電流生成部11が生成する電流I0の電流値を測定する。電流I0の測定方法としては、電流計により直接電流I0を測定してもよいし、特性ばらつきの少ない高精度抵抗を用いて電流を測定してもよい。

【0106】

電流計22の測定値をADC118によりA/D変換し、CPU126がA/D変換された測定値を演算処理する。CPU126(電流演算処理部)は、電流I0の電流値の変動に応じて、基準電流IREFが一定となるように電流コード値を決定し、電流コード値を割り込みレジスタ16に設定する。トリミング完了後の電流I0の初期値と、現在の電流I0とを比較し、電流値の大小に応じて、電流コード値を決定する。なお、CPU126に限らず、その他のロジック回路により構成してもよい。

【0107】

なお、ここでは、電流I0を測定したがその他の電流等を測定してもよい。例えば、電流Ioutを測定し、電流Ioutの変動に応じて電流制御してもよい。また、基準電流IREF(電流Iout)が供給されているフィルタや発振回路の特性変動を検出し、この特性変動に応じて電流制御してもよい。

【0108】

このように、本実施形態では、テスタによりトリミング完了後に、半導体装置内部で、電流を測定し電流値の変動に応じて電流制御することとした。これにより、トリミング完了後に、温度変化等により電流がばらついた場合でも、基準電流IREFを一定に保つことができる。

【0109】

(本発明の実施の形態4)

以下、図面を参照して本発明の実施の形態4について説明する。図7は、本発明の実施の形態4に係る基準電流生成回路10を含む半導体装置100の回路構成を示しており、その他の構成については、実施の形態1、実施の形態3と同様である。なお、図6では、実施の形態3と同様に、すでにテスタにより電流トリミングが行われており、ヒューズレジスタ15に電流コード値が設定されている状態である。

【0110】

図7の半導体装置100では、図6の構成と比べて、電流計22の代わりに、温度センサ23を備えている。温度センサ23は、ダイオード等で構成することができる。また、温度センサ23として、定電圧源12に内蔵される温度センサを用いてもよい。

【0111】

温度センサ23は、半導体装置100の温度を測定し、この測定結果が、ADC118を介してCPU126に入力される。CPU126(温度演算処理部)は、温度センサ23の検出した温度の変動に応じて、基準電流IREFが一定となるように電流コード値を決定し、電流コード値を割り込みレジスタ16に設定する。例えば、抵抗R1の温度特性を予め設定しておき、検出する温度にしたがって、温度特性から抵抗R1の変動を求めることで、電流コード値を決定する。

【0112】

このように、本実施形態では、テスタによりトリミング完了後に、半導体装置内部で、温度を測定し温度の変動に応じて電流制御することとした。これにより、トリミング完了後に、温度変化により電流がばらついた場合でも、基準電流IREFを一定に保つことができる。

【0113】

(本発明の実施の形態5)

以下、図面を参照して本発明の実施の形態5について説明する。図8は、本発明の実施の形態5に係る半導体装置100及びテスト時のテスタ300の接続状態を示している。半導体装置100の内部構成については実施の形態1〜4と同様である。

【0114】

図8に示すように、本実施形態では、半導体装置100のプローブテスト時に、半導体装置100の外部端子T1〜T3と半導体装置100とを接続する。外部端子T1を介して、基準電流生成回路10とテスタ300とを接続し、外部端子T2を介して、レジスタ128(割り込みレジスタ及びヒューズレジスタ)とテスタ300とを接続し、外部端子T3を介して、メモリ127とテスタ300とを接続する。そして、テスタ300は、メモリ127のテストを行うとともに、図4と同様に、基準電流生成回路10の基準電流IREFのトリミングテストも行う。

【0115】

図9は、本発明の実施の形態5に係るテスト方法の流れを示している。図9に示すように、メモリのテスト工程において、まず、テスタ300は、半導体装置100に対しメモリのテストを行い(S201)、メモリのトリミングを行う(S202)。テスタ300は、プローブを外部端子T1〜T3に接続して、半導体装置100をテストモードに設定する。テスタ300は、外部端子T3を介してメモリ127の欠陥の有無を検証するためにテストを行う。そして、テスタ300は、メモリ127に欠陥を発見した場合には、欠陥メモリセルを救済するためにメモリの救済情報をメモリ127に設定し、メモリのトリミングを行う。

【0116】

次に、テスタ300は、半導体装置100に対し基準電流のテストを行い(S203)、基準電流のトリミングを行う(S204)。図4のS101〜S106と同様に、テスタ300は、外部端子T1を介して基準電流IREFを測定して、電流コード値を決定し、最適な電流コード値を外部端子T2を介してレジスタ128(ヒューズレジスタ15)に設定することで、基準電流のトリミングを行う。

【0117】

なお、図9のテスト方法において、先にS203〜S204の電流トリミングを実施し、次にS201〜S202のメモリトリミングを実施してもよい。また、電流トリミングとメモリトリミングを同時に実施してもよい。

【0118】

このように、本実施形態では、メモリのテスト及びトリミングと、基準電流のテスト及びトリミングを同じプローブテストにより実施することとした。メモリテストは、メモリの欠陥救済のために常に必要なテスト工程であるため、基準電流のためのテストを別工程で実施する必要がなく、効率よくテスト及びトリミングを行うことができる。

【0119】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、上記の例では、光ディスク装置について説明したが、定電流回路を有するその他の電子機器であってもよい。

【符号の説明】

【0120】

1 光ディスク装置

10 基準電流生成回路

11 電流生成部

12 定電圧源

13 電流切替部

14 電流制御部

15 ヒューズレジスタ

16 割り込みレジスタ

17 電流出力部

18 マルチプレクサ

19 内部バッファ

20 カスコードトランジスタ群

21 カスコードトランジスタ群

22 電流計

23 温度センサ

100 半導体装置

110 AFE(アナログフロントエンド)部

111 基準電圧生成回路

112 インタフェースIF

113 RF系回路

114 ウォブル検出回路

115 ライトPLL回路

116 サーボ系回路

117 APC回路

118 ADC

120 DSP(デジタルシグナルプロセッサ)部

121 データストローブ回路

122 デコーダ

123 エンコーダ

124 ATIP・ADIP回路

125 サーボDSP

126 CPU

127 メモリ

128 レジスタ

128a アナログレジスタ

128b デジタルレジスタ

200 ピックアップ

201 光電変換回路OEIC

202 フロントモニタダイオードFMD

203 レーザダイオードドライバLDD

300 テスタ

301 電流計

OP1 オペアンプ

R1 抵抗

P0〜P5,P11〜P15 PMOSトランジスタ

N1〜N4,N11〜N12 NMOSトランジスタ

SW1〜SW5,SW11〜SW12 スイッチ

T1〜T3 外部端子

【特許請求の範囲】

【請求項1】

基準電流を生成する電流生成回路と、

前記生成された基準電流をテスタへ出力する第1の外部端子と、

前記基準電流の電流値を制御するための電流制御データを、前記第1の外部端子から出力された基準電流に応じて前記テスタにより設定される第2の外部端子と、

前記テスタにより設定された電流制御データにしたがって、前記電流生成回路により生成される基準電流が所定値となるように調整する電流制御回路と、

を備える半導体装置。

【請求項2】

前記電流制御データを記憶するレジスタを有し、

前記第2の外部端子は、前記テスタから前記レジスタの書き込みを制御するレジスタ制御端子である、

請求項1に記載の半導体装置。

【請求項3】

前記電流生成回路は、

定電圧に応じた抵抗電流を抵抗により生成する抵抗電流生成部と、

前記生成された抵抗電流をミラーする第1のカレントミラー回路のミラー比を、前記電流制御回路から入力される電流制御データに応じて切り替えることで前記基準電流を生成する電流切替部と、を備える

請求項1または2に記載の半導体装置。

【請求項4】

前記抵抗電流生成部は、

一方の入力端子に前記定電圧が入力されたオペアンプと、

制御端子が前記オペアンプの出力端子に接続され、第1の端子が前記抵抗を介して第1の電源に接続された第1のトランジスタと、を有し、

前記電流切替部は、

各制御端子が前記第1のトランジスタの制御端子に共通接続され、各第1の端子が前記第1の電源に共通接続され、前記第1のカレントミラー回路を構成する複数の第2のトランジスタと、

前記複数の第2のトランジスタの各第2の端子と前記基準電流を生成する基準電流生成ノードとの間のそれぞれに接続され、前記電流制御データに応じてそれぞれオン/オフされる複数のスイッチと、を備えた、

請求項3に記載の半導体装置。

【請求項5】

前記抵抗は、ポリシリコン抵抗である、

請求項3または4に記載の半導体装置。

【請求項6】

前記複数の第2のトランジスタに含まれる各トランジスタは、それぞれ異なるトランジスタサイズである、

請求項4または5に記載の半導体装置。

【請求項7】

前記複数の第2のトランジスタに含まれる各トランジスタのトランジスタサイズは、それぞれ前記電流制御データの各ビットに対応している、

請求項6に記載の半導体装置。

【請求項8】

前記複数の第2のトランジスタと前記複数のスイッチとの間のそれぞれに接続され、各制御端子が共通接続された複数の第1のカスコードトランジスタを有する、

請求項4乃至7のいずれか一項に記載の半導体装置。

【請求項9】

所定の演算処理を行う演算処理部を有し、

前記電流切替部は、前記演算処理に基づいて前記演算処理部から出力される割り込み信号により設定された前記電流制御データに応じて前記基準電流を生成する、

請求項3乃至8のいずれか一項に記載の半導体装置。

【請求項10】

前記電流生成回路は、

前記電流切替部により生成された前記基準電流を第2のカレントミラー回路によりミラーして出力する電流出力部を、さらに備えた、

請求項3乃至9のいずれか一項に記載の半導体装置。

【請求項11】

前記電流生成回路は、

第1の端子及び制御端子が前記基準電流生成ノードに接続され、第2の端子が前記第2の電源に接続された第3のトランジスタと、

各制御端子が前記第3のトランジスタの制御端子に共通接続され、各第1の端子が出力先の回路に接続され、各第2の端子が前記第2の電源に共通接続されて、第2のカレントミラー回路を構成する複数の第4のトランジスタと、を備えた、

請求項4乃至9のいずれか一項に記載の半導体装置。

【請求項12】

前記第3のトランジスタ及び前記複数の第4のトランジスタに含まれる各トランジスタは、同じトランジスタサイズである、

請求項11に記載の半導体装置。

【請求項13】

前記基準電流生成ノードと、前記第3のトランジスタ及び前記複数の第4のトランジスタの各第1の端子との間のそれぞれに接続され、各制御端子が共通接続された複数の第2のカスコードトランジスタを有する、

請求項11または12に記載の半導体装置。

【請求項14】

前記電流生成回路が生成する基準電流を測定する電流測定回路を有し、

前記テスタにより前記電流制御データが設定された後、前記電流制御回路は、前記電流測定回路による前記基準電流の測定結果に応じて、前記電流生成回路により生成される基準電流が前記所定値となるようにさらに調整する、

請求項1乃至13のいずれか一項に記載の半導体装置。

【請求項15】

前記電流測定回路による測定結果に対し演算処理を行う電流演算処理部を有し、

前記電流制御回路は、前記測定結果に基づいて前記電流演算処理部から出力される割り込み信号に応じて前記電流生成回路の基準電流を調整する、

請求項14に記載の半導体装置。

【請求項16】

温度を測定する温度センサを有し、

前記テスタにより前記電流制御データが設定された後、前記電流制御回路は、前記温度センサによる温度の測定結果に応じて、前記電流生成回路により生成される基準電流が前記所定値となるようにさらに調整する、

請求項1乃至13のいずれか一項に記載の半導体装置。

【請求項17】

前記温度センサによる測定結果に対し演算処理を行う温度演算処理部を有し、

前記電流制御回路は、前記測定結果に基づいて前記温度演算処理部から出力される割り込み信号に応じて前記電流生成回路の基準電流を調整する、

請求項16に記載の半導体装置。

【請求項18】

前記テスタは、前記半導体装置に含まれるメモリの欠陥救済のためのメモリテスト工程において、前記第1の外部端子から出力された基準電流を測定し、前記基準電流の測定結果に応じて前記第2の外部端子へ前記電流制御データを設定する、

請求項1乃至17のいずれか一項に記載の半導体装置。

【請求項19】

光ディスクにレーザ光を照射するピックアップと、前記ピックアップの動作を制御する半導体装置を備えた光ディスク装置であって、

前記半導体装置は、

基準電流を生成する電流生成回路と、

前記生成された基準電流をテスタへ出力する第1の外部端子と、

前記基準電流の電流値を制御するための電流制御データを、前記第1の外部端子から出力された基準電流に応じて前記テスタにより設定される第2の外部端子と、

前記テスタにより設定された電流制御データにしたがって、前記電流生成回路により生成される基準電流が所定値となるように調整する電流制御回路と、

前記調整された前記電流生成回路の基準電流に基づいて、前記ピックアップから出力される信号を処理する信号処理回路と、

を備える光ディスク装置。

【請求項20】

基準電流を生成する電流生成回路と前記生成される基準電流を調整する電流制御回路と第1及び第2の外部端子とを有する半導体装置のテスト方法であって、

テスタは、前記第1及び第2の外部端子にプローブを接続し、前記第1の外部端子を介して前記電流生成回路と電気的に接続し、前記第2の外部端子を介して前記電流制御回路と電気的に接続し、

前記テスタは、前記基準電流の電流値を制御するための電流制御データの初期値を決定し、前記初期値として決定した前記電流制御データを前記第2の外部端子を介して前記電流制御回路へ変更可能に設定し、

前記電流制御回路は、前記設定された電流制御データにしたがって、前記電流生成回路により生成される基準電流を調整し、

前記電流生成回路は、前記電流制御データにより調整された前記基準電流を前記第1の外部端子を介して前記テスタへ出力し、

前記テスタは、前記出力された基準電流の電流値を測定し、前記基準電流の測定結果と前記所定値との比較結果に応じて、前記電流制御データの最適値を決定し、

前記テスタは、前記最適値として決定した電流制御データを前記第2の外部端子を介して前記電流制御回路へ変更不可能に設定する、

半導体装置のテスト方法。

【請求項1】

基準電流を生成する電流生成回路と、

前記生成された基準電流をテスタへ出力する第1の外部端子と、

前記基準電流の電流値を制御するための電流制御データを、前記第1の外部端子から出力された基準電流に応じて前記テスタにより設定される第2の外部端子と、

前記テスタにより設定された電流制御データにしたがって、前記電流生成回路により生成される基準電流が所定値となるように調整する電流制御回路と、

を備える半導体装置。

【請求項2】

前記電流制御データを記憶するレジスタを有し、

前記第2の外部端子は、前記テスタから前記レジスタの書き込みを制御するレジスタ制御端子である、

請求項1に記載の半導体装置。

【請求項3】

前記電流生成回路は、

定電圧に応じた抵抗電流を抵抗により生成する抵抗電流生成部と、

前記生成された抵抗電流をミラーする第1のカレントミラー回路のミラー比を、前記電流制御回路から入力される電流制御データに応じて切り替えることで前記基準電流を生成する電流切替部と、を備える

請求項1または2に記載の半導体装置。

【請求項4】

前記抵抗電流生成部は、

一方の入力端子に前記定電圧が入力されたオペアンプと、

制御端子が前記オペアンプの出力端子に接続され、第1の端子が前記抵抗を介して第1の電源に接続された第1のトランジスタと、を有し、

前記電流切替部は、

各制御端子が前記第1のトランジスタの制御端子に共通接続され、各第1の端子が前記第1の電源に共通接続され、前記第1のカレントミラー回路を構成する複数の第2のトランジスタと、

前記複数の第2のトランジスタの各第2の端子と前記基準電流を生成する基準電流生成ノードとの間のそれぞれに接続され、前記電流制御データに応じてそれぞれオン/オフされる複数のスイッチと、を備えた、

請求項3に記載の半導体装置。

【請求項5】

前記抵抗は、ポリシリコン抵抗である、

請求項3または4に記載の半導体装置。

【請求項6】

前記複数の第2のトランジスタに含まれる各トランジスタは、それぞれ異なるトランジスタサイズである、

請求項4または5に記載の半導体装置。

【請求項7】

前記複数の第2のトランジスタに含まれる各トランジスタのトランジスタサイズは、それぞれ前記電流制御データの各ビットに対応している、

請求項6に記載の半導体装置。

【請求項8】

前記複数の第2のトランジスタと前記複数のスイッチとの間のそれぞれに接続され、各制御端子が共通接続された複数の第1のカスコードトランジスタを有する、

請求項4乃至7のいずれか一項に記載の半導体装置。

【請求項9】

所定の演算処理を行う演算処理部を有し、

前記電流切替部は、前記演算処理に基づいて前記演算処理部から出力される割り込み信号により設定された前記電流制御データに応じて前記基準電流を生成する、

請求項3乃至8のいずれか一項に記載の半導体装置。

【請求項10】

前記電流生成回路は、

前記電流切替部により生成された前記基準電流を第2のカレントミラー回路によりミラーして出力する電流出力部を、さらに備えた、

請求項3乃至9のいずれか一項に記載の半導体装置。

【請求項11】

前記電流生成回路は、

第1の端子及び制御端子が前記基準電流生成ノードに接続され、第2の端子が前記第2の電源に接続された第3のトランジスタと、

各制御端子が前記第3のトランジスタの制御端子に共通接続され、各第1の端子が出力先の回路に接続され、各第2の端子が前記第2の電源に共通接続されて、第2のカレントミラー回路を構成する複数の第4のトランジスタと、を備えた、

請求項4乃至9のいずれか一項に記載の半導体装置。

【請求項12】

前記第3のトランジスタ及び前記複数の第4のトランジスタに含まれる各トランジスタは、同じトランジスタサイズである、

請求項11に記載の半導体装置。

【請求項13】

前記基準電流生成ノードと、前記第3のトランジスタ及び前記複数の第4のトランジスタの各第1の端子との間のそれぞれに接続され、各制御端子が共通接続された複数の第2のカスコードトランジスタを有する、

請求項11または12に記載の半導体装置。

【請求項14】

前記電流生成回路が生成する基準電流を測定する電流測定回路を有し、

前記テスタにより前記電流制御データが設定された後、前記電流制御回路は、前記電流測定回路による前記基準電流の測定結果に応じて、前記電流生成回路により生成される基準電流が前記所定値となるようにさらに調整する、

請求項1乃至13のいずれか一項に記載の半導体装置。

【請求項15】

前記電流測定回路による測定結果に対し演算処理を行う電流演算処理部を有し、

前記電流制御回路は、前記測定結果に基づいて前記電流演算処理部から出力される割り込み信号に応じて前記電流生成回路の基準電流を調整する、

請求項14に記載の半導体装置。

【請求項16】

温度を測定する温度センサを有し、

前記テスタにより前記電流制御データが設定された後、前記電流制御回路は、前記温度センサによる温度の測定結果に応じて、前記電流生成回路により生成される基準電流が前記所定値となるようにさらに調整する、

請求項1乃至13のいずれか一項に記載の半導体装置。

【請求項17】

前記温度センサによる測定結果に対し演算処理を行う温度演算処理部を有し、

前記電流制御回路は、前記測定結果に基づいて前記温度演算処理部から出力される割り込み信号に応じて前記電流生成回路の基準電流を調整する、

請求項16に記載の半導体装置。

【請求項18】

前記テスタは、前記半導体装置に含まれるメモリの欠陥救済のためのメモリテスト工程において、前記第1の外部端子から出力された基準電流を測定し、前記基準電流の測定結果に応じて前記第2の外部端子へ前記電流制御データを設定する、

請求項1乃至17のいずれか一項に記載の半導体装置。

【請求項19】

光ディスクにレーザ光を照射するピックアップと、前記ピックアップの動作を制御する半導体装置を備えた光ディスク装置であって、

前記半導体装置は、

基準電流を生成する電流生成回路と、

前記生成された基準電流をテスタへ出力する第1の外部端子と、

前記基準電流の電流値を制御するための電流制御データを、前記第1の外部端子から出力された基準電流に応じて前記テスタにより設定される第2の外部端子と、

前記テスタにより設定された電流制御データにしたがって、前記電流生成回路により生成される基準電流が所定値となるように調整する電流制御回路と、

前記調整された前記電流生成回路の基準電流に基づいて、前記ピックアップから出力される信号を処理する信号処理回路と、

を備える光ディスク装置。

【請求項20】

基準電流を生成する電流生成回路と前記生成される基準電流を調整する電流制御回路と第1及び第2の外部端子とを有する半導体装置のテスト方法であって、

テスタは、前記第1及び第2の外部端子にプローブを接続し、前記第1の外部端子を介して前記電流生成回路と電気的に接続し、前記第2の外部端子を介して前記電流制御回路と電気的に接続し、

前記テスタは、前記基準電流の電流値を制御するための電流制御データの初期値を決定し、前記初期値として決定した前記電流制御データを前記第2の外部端子を介して前記電流制御回路へ変更可能に設定し、

前記電流制御回路は、前記設定された電流制御データにしたがって、前記電流生成回路により生成される基準電流を調整し、

前記電流生成回路は、前記電流制御データにより調整された前記基準電流を前記第1の外部端子を介して前記テスタへ出力し、

前記テスタは、前記出力された基準電流の電流値を測定し、前記基準電流の測定結果と前記所定値との比較結果に応じて、前記電流制御データの最適値を決定し、

前記テスタは、前記最適値として決定した電流制御データを前記第2の外部端子を介して前記電流制御回路へ変更不可能に設定する、

半導体装置のテスト方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−114446(P2013−114446A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−259933(P2011−259933)

【出願日】平成23年11月29日(2011.11.29)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月29日(2011.11.29)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]