半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、半導体集積回路によって構成され、主要な内部制御信号のタイミングをチップごとに測定することを可能とした半導体装置、内部信号タイミング測定回路、及び遅延時間測定方法に関する。

【背景技術】

【0002】

半導体プロセスの微細化が進み、デバイスの仕上がりのバラツキが回路動作に与える影響が大きくなってきている。従来、プロセス、電圧、温度が全てベストの条件と全てワーストの条件で回路動作を保証することで、内部回路のタイミングマージンを確保してきた。しかし、プロセスばらつきの影響が大きくなった結果、上記設計手法では回路動作マージンが確保できず、要求性能を満足することが困難になってきた。

【0003】

そこで、デバイスの仕上がりをモニタできる回路をチップ上に設け、その測定結果をもとに、例えば、内部電圧を微調整するなどして、回路の動作マージンを確保する手法が提案されている。しかし、同手法にも問題がある。そのひとつは、例えば、トランジスタの仕上がりのバラツキにはロット間、ウェハ間でばらつくと共に、ウェハ内でもばらつくことが判明した。このため、例え、チップサイズを犠牲にして上記モニタ回路を同一チップ内に複数設置しても、チップ内のバラツキを考慮してモニタ回路の測定結果にある程度のマージンをもたせて、内部電圧などを微調整して微妙に加減する必要があるが、この微調整は難しく、過剰マージンとなることが多い。

【0004】

更に、モニタ回路を使用してデバイスの仕上がりをモニタする手法をより具体的に説明する。通常、半導体装置を形成する半導体集積回路に、クロック同期遅延制御回路を組み込むことが行われている。クロック同期遅延制御回路は、外部クロック信号に同期し、外部クロック信号のn周期分(nは整数)遅延した信号を生成し、半導体集積回路の内部回路の遅延時間を調整している。

【0005】

このようなクロック同期遅延制御回路には、SAD(Synchronous Adjustable Delay)方式と、DLL(Delay Locked Loop)方式とがあるが、いずれの場合にも、ディレイモニタが使用されている。この場合、外部クロック信号に対する内部クロック信号の同期精度を高めるためには、ディレイモニタにおける遅延時間を正確にクロックレシーバの遅延時間と出力バッファの遅延時間との和に等しくする必要がある。

【0006】

即ち、クロック同期遅延制御回路は、本来、外部クロック入力に対するクロックレシーバの入力遅延量tRCと出力バッファにおける出力遅延量tDRを測定するために使用されている。このように、クロックレシーバ及び出力バッファにおける遅延量を測定することによって、半導体集積回路に実装された状態で、遅延測定モードによる動作を行なわせることにより、各回路の実際の信号遅延時間や外部データバスの負荷状態に応じたデータ出力時の遅延時間をディレイモニタに設定することができる。このため、ディレイモニタを含む半導体集積回路では、実際の遅延時間を正確に設定できる。

【0007】

一方、特許文献1には、改良されたクロック同期遅延制御回路を含む半導体集積回路が開示されている。特許文献1に示されたクロック同期遅延制御回路では、外部クロック信号に応答してクロックレシーバから信号CLKを出力し、当該信号CLKを同期遅延制御回路及びディレイモニタに供給する構成が採用されている。

【0008】

更に、同期遅延制御回路は、遅延測定モードの際、測定用信号である疑似内部クロック信号DCLKを出力する回路を備えており、当該疑似内部クロック信号DCLKはクロックドライバ及び出力制御回路で遅延されて、内部クロック信号としてデータ入出力回路に出力されている。データ入出力回路は、内部クロック信号に同期して、データを出力バッファ及び出力ドライバを介して外部データバスに出力すると共に、当該データをデータレシーバによって取り込むような構成を備えている。

【0009】

この場合、ディレイモニタには、疑似内部クロック信号DCLKの発生から出力データDOUTが外部データバスに出力されるまでの出力遅延量tDRと、データレシーバにおける遅延量tRCとの和に相当する遅延時間が設定されている。

【0010】

このような構成では、外部データバスに”H”レベルの疑似データを出力するようにしておくと、データレシーバによる入力遅延量tRCだけ、遅延してデータ信号DATが出力される。

【0011】

この場合、疑似内部クロック信号DCLKに応答して、測定開始信号STRを生成し、データ信号DATに応答して測定停止信号STPを生成して、ディレイモニタに入力することによって、(出力遅延量tDR)+(入力遅延量tRC)を測定でき、ディレイモニタに、遅延時間を設定する。

【0012】

特許文献1では、クロックレシーバにおける遅延量と、データレシーバにおける遅延量とが実質的に等しいものとして扱うことにより、ディレイモニタで実際の遅延時間を正確に設定できる。

【0013】

換言すれば、特許文献1では、クロックレシーバとデータレシーバとを等価な回路構成にすると共に、外部クロック入力は外部データバスに出力された疑似データに置き換えて測定している。この条件の下で、クロックレシーバとデータレシーバにおける遅延量を実質的に等しくすることができる。

【0014】

【特許文献1】特開2000−269423号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

このように、クロックレシーバとデータレシーバにおける遅延量を等しいとして、外部クロックを疑似データに置き換えた場合、次に述べるような問題を含んでおり、この手法により得られた測定値は通常動作時の回路特性を正確には反映していないという問題があった。

【0016】

第1には、トランジスタ等のデバイスは短チャネル化等、高性能化が進み、製造プロセスのばらつきに対して敏感になっており、半導体ウェハ間のみならず、チップ内のばらつきも無視できない状況であるため、クロックレシーバとデータレシーバについて回路構成をあわせても同一特性を有するとは限らないという問題点がある。

【0017】

即ち、クロックレシーバとデータレシーバとはチップ内の互いに異なる位置に設けられているため、正確に同一の特性を示すとは云えない。この結果、特許文献1の手法では、チップ毎の遅延時間の相違を正確に把握することができない。

【0018】

第2には、外部クロックバスと外部データバスはそれぞれ接続されるデバイスの個数やインターフェースが全く異なり、信号波形、例えば、信号のライズ・フォール波形やノイズ特性が異なるため、それらに対する回路の応答特性は異なるという問題点がある。

【0019】

第3には、クロックの遅延量及びデータの遅延量だけについて考慮されているだけで、DRAM等で使用される各種信号の遅延量については、全く考慮されていない。

【課題を解決するための手段】

【0020】

本発明によれば、タイミングマージンがクリティカルな信号を設計段階で選び出し、そのタイミングをチップごとに測定する手段を設け、ウェハテスト時に同タイミングを測定してその結果でチップごとに調整を実施できる半導体装置が得られる。

【0021】

即ち、本発明の一実施形態によれば、第1の内部回路制御信号と該第1の内部回路制御信号から所定の遅延時間経過後に発生する第2の内部回路制御信号を生成する内部回路と、

前記第1の内部回路制御信号と前記第2の内部回路制御信号を受け、前記第1の内部回路制御信号を遅延時間測定開始信号として発生すると共に、前記第2の内部回路制御信号を遅延時間測定終了信号として発生する測定用信号発生回路と、前記遅延時間測定開始信号と前記遅延時間測定終了信号を入力とし、遅延時間測定結果を出力する遅延時間測定回路を備えていることを特徴とする半導体装置が得られる。

【0022】

このように、本発明では、モニタ回路ではなく実動作で使用する内部回路のスピードを測定しているため、モニタ回路と実動作回路間の相違を考慮する必要が無く、その分マージンを少なくすることができる。

【0023】

本発明の別の実施形態によれば、電子回路を実際に動作させるために使用される複数の信号から第1及び第2の信号を選択し、前記第1の信号及び第2の信号を遅延時間測定開始信号及び遅延時間測定終了信号に変換して、遅延時間測定回路に供給し、前記遅延時間測定回路では、前記遅延時間測定開始信号及び前記遅延時間測定終了信号との間の遅延時間を測定し、測定結果を出力することを特徴とする遅延時間測定方法が得られる。

【発明の効果】

【0024】

本発明では、チップ上のリング発振器等の遅延時間測定回路を、チップで使用される主要信号および/又はクロックで発振、停止させ、発振回数をカウントし、カウント結果を、データ出力回路を介して出力することで、主要信号のタイミングをチップ毎にウェハテスト時に測定することができる。この構成によれば、モニタ回路ではなく実動作で使用する回路のスピードを測定しているため、モニタ回路と実動作回路間の相違を考慮する必要が無く、その分マージンを少なくすることができる。

【発明を実施するための最良の形態】

【0025】

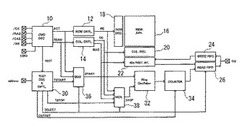

図1を参照して、本発明の第1の実施形態に係る半導体装置を説明する。図1では、本発明をDDR-SDRAMに適用した場合における回路構成概略図が示されている。図示されたDDR-SDRAMは集積回路化されており、図2及び図3にその動作波形図が示されている。

【0026】

図1に示されているように、本発明の第1の実施形態に係る半導体装置、即ち、DDR-SDRAMは、コマンドデコーダ(CMDDEC)10、ロウ制御回路(ROWCNTL)12、カラム制御回路(COLCNTL)14、メモリアレイ(MEMARY)16、ロウデコーダ(ROWDEC)18、カラムデコーダ(COLDEC)20、メインアンプ/バッファ回路(MA/WRT)22、ライトFIFO(WRITEFIFO)24、リードFIFO(READFIFO)26、及びDQ端子(DQ)を備え、これらの回路は、半導体集積回路の内部回路を構成している。コマンドデコーダ(CMDEC)10には、通常のDRAMと同様に、コマンド(CMD),/CS,/RAS/,/CAS,及び/WEが与えられ、図示されたコマンドデコーダ(CMDEC)10は、テストコマンドをデコードしてテストモード信号(TEST)を出力する機能を有している。

【0027】

更に、図示された半導体集積回路は、テスト制御回路(TESTDEC&CNTL)30、リング発振器(Ring Oscillator)32、及びカウンタ(COUNTER)34を含み、リングオシレータ32は第1のマルチプレクサ(MUX)36及び第2のマルチプレクサ(MUX)38と接続されている。

【0028】

ここで、テスト制御回路(TESTDEC&CNTL)30、及び、第1のマルチプレクサ(MUX)36及び第2のマルチプレクサ(MUX)38は、遅延時間測定開始を指示するテストスタート信号(遅延時間測定開始信号)STARTを発生すると共に、遅延時間測定終了をあらわすテストストップ信号(遅延時間測定終了信号)STOPを発生する測定用信号発生回路として動作する。一方、リング発振器(Ring Oscillator)32、及びカウンタ(COUNTER)34は遅延時間測定回路を構成している。

【0029】

第1のマルチプレクサ36には、内部回路であるコマンド制御回路10からバンク起動信号ACTと読み出し信号READが与えられており、更に、テスト制御回路30からテストスタート信号TSTARTが与えられている。他方、第2のマルチプレクサ38には、ROWデコーダ起動信号RE、カラムデコーダ起動信号CE、及び、メインアンプ起動信号MAEが与えられると共に、テストストップ信号TSTOPが与えられている。

【0030】

また、テスト制御回路30は、上記したテストスタート信号TSTART及びテストストップ信号TSTOPを出力すると共に、第1及び第2のマルチプレクサ36及び38及びリードFIFO26に選択信号(SELECT)を出力し、更に、カウンタ34にカウンタリセット信号(CNTRRST)を出力している。

【0031】

本実施形態では、タイミングを測定する信号として、内部回路であるロウ制御回路12及びカラム制御回路14から出力されるROWデコーダ起動信号RE及びカラムデコーダ起動信号CEを測定すると共に、カラム制御回路14から出力されるメインアンプ起動信号MAEを測定することができる。

【0032】

これらの信号タイミングを測定するために、第1及び第2のマルチプレクサ(MUX)36、38、リング発振器32、及び、カウンタ34が設けられている。

【0033】

図示された半導体装置では、まず、内部タイミング信号の測定に利用されるリング発振器32の発振周期を測定する段階と、内部タイミング信号を測定する段階とに分けて測定が行われる。このうち、リング発振器32の発振周期の測定は、ウェハテスト条件(電圧、温度)の下に行われる。

【0034】

(1)図2を参照して、ウェハテスト測定条件(電圧、温度)におけるリング発振器32の発振周期を測定について説明する。

【0035】

まず、テスト制御回路30に、テストモード信号TESTとして、TEST0のコードが図2に示すように、コマンドデコーダ10から入力される。これにより、テスト制御回路30は、カウンタリセット信号CNTRSTをカウンタ34に出力し、この結果、カウンタ34におけるリング発振器32のカウンタ値が0にリセットされる。

【0036】

同時に、テスト制御回路30は第1及び第2のマルチプレクサ(MUX)36及び38に制御信号として、選択信号(SELECT)を出力し、この結果、図示された半導体装置はクロック測定モードに設定される。

【0037】

第1及び第2のマルチプレクサ36及び38は、選択信号(SELECT)にしたがって、テストスタート信号TSTART及びテスト終了信号TSTOPをスタート信号START及びストップ信号STOPをそれぞれ選択する状態となる。この結果、スタート信号STARTとストップ信号STOPをバイパスする第1及び第2のマルチプレクサ36及び38の経路が選択される。一方、選択信号(SELECT)はリードFIFO26にも与えられ、リードFIFO26の入力がカウンタ34の出力を選択する経路に切り替えられる。

【0038】

次に、図2に示すように、半導体集積回路であるDRAMに、テストTEST1のコードが入力される。これにより、テスト制御回路30からリング発振器32にテスト起動信号TSTARTが発生する。テスト起動信号TSTARTは、第1のマルチプレクサ36から、スタート信号STARTとしてリング発振器32に送出され、リング発振器32が発振動作を開始する。これと同時に、カウンタ34もリング発振器32の出力のカウント動作を開始する。

【0039】

続いて、テスト制御回路30は、特定時間後(図2では2クロック(CLK)サイクル後)に、テストストップ信号TSTOPのコードを出力する。これにより、テスト制御回路30は、リング発振器32のテストストップ信号TSTOPを出力し、これが、ストップ信号STOPとなってリング発振器32に与えられる。ストップ信号STOPを受けて、リング発振器32は発振を停止し、カウンタ34もカウント動作を停止して、停止したときのカウンタ値がカウンタ34に保持される。

【0040】

次に、1クロックサイクル後、テストTEST3のコードがテスト制御回路30に入力されると、カウンタ34に保持されたカウント値がデジタル信号としてDQ端子に出力される。図2では、クロックCLKの立ち上がり/立下りとともに1桁ずつ順次出力される例が示されている。

【0041】

テストコードTEST1とTEST2を入力した時間の差はテスタプログラム上あらかじめ分かっているので、上記のように出力されたカウンタの値で同時間差の除算を実行することで、チップ内に組み込まれたリング発振器32の実際の発振周期が求められる。

【0042】

(2)図3を参照して、内部タイミング信号を測定する動作を説明する。

【0043】

この場合、半導体集積回路であるDRAMのテスト制御回路30にTEST0’のコードが入力される。このコードは、内部タイミング信号測定モード、即ち、テストモードをあらわしており、このコードを受けると、テスト制御回路30はカウンタリセット信号CNTRSTを発生し、カウンタ34に出力する。カウンタリセット信号CNTRSTを受けると、カウンタ34はカウンタ値を0にリセットされ、リードFIFO26の入力がカウンタ34の出力を選択する経路に切り替えられる。この動作は、上記した(1)の場合と同様である。

【0044】

しかしながら、内部タイミング信号を測定する場合、テスト制御回路30は選択信号(SELECT)をも出力する。ここでは、バンク起動信号ACTとロウデコーダ起動信号REが測定されるものとする。この場合、バンク起動信号ACTとロウデコーダ起動信号REがそれぞれ第1及び第2の内部回路制御信号として第1及び第2のマルチプレクサ36及び38に与えられるものとする。

【0045】

第1及び第2のマルチプレクサ36及び38は、選択信号(SELECT)をテスト制御回路30から受けると、それぞれバンク起動信号ACTとロウデコーダ起動信号REを選択する状態になり、これらの信号をそれぞれSTARTとSTOPとしてバイパスする経路を選択する状態に切り替えられる。ここで、バンク起動信号ACT及びロウデコーダ起動信号REは、実際にチップの実動作に使われる信号である。

【0046】

この状態で、DRAMのコマンド制御回路10にバンク起動命令を入力されると、コマンド制御回路10は、バンク起動信号ACTを発生して第1のマルチプレクサ36に出力し、これがそのままスタート信号STARTとなってリング発振器32に送られる。この結果、リング発振器32が発振動作を開始し、カウンタ34もリング発振器32の出力のカウント動作を開始する。続いて、ロウ制御回路12は、コマンド制御回路10からバンク起動信号ACTを受けた後、ロウデコーダ起動信号REを出力する。ロウデコーダ起動信号REは、そのままストップ信号STOPとして、リング発振器31に出力される。ストップ信号STOPを受けると、リング発振器32は発振を停止する一方、カウンタ34はカウント動作を停止し、停止したときのカウント値を保持する。

【0047】

次に、図3に示すように、テストTEST3のコードが入力されると、(1)と同様に保持されたカウンタ34のカウント値がデジタル信号の形で、DQに出力される。この出力されたカウンタ34のカウント値を(1)で求めたリング発振器32の発振周期で乗算することでACT/RE間の遅延時間が求められる。

【0048】

上記した例では、バンク起動信号ACTとロウデコーダ起動信号REとの間の遅延時間を求める場合についてのみ説明したが、カラムデコーダ起動信号CE、メインアンプ起動信号MAEの遅延時間も、選択信号(SELECT)により、第1及び第2のマルチプレクサ36、38の経路を選択すれば、これらを第1及び第2の内部回路制御信号として同様の手順で求めることができる。

【0049】

このように、上記した実施の形態は、チップ上の異なる位置に設けられた内部回路(即ち、コマンド制御回路10及びロウ制御回路12)からの2つの内部信号(上記した例では、ACTとRE)の遷移時間差を、チップ外に読み出すことが可能なデジタル信号に変換する回路手段(例:リング発振器32とカウンタ34)が設けられていることを第1の特徴としている。

【0050】

したがって、上記した実施形態では、ロウ制御回路12、第1及び第2のマルチプレクサ36、38は、スタート制御信号START及びストップ制御信号STOPをリング発振器32に第1及び第2の内部回路制御信号として出力する内部回路として動作する。

【0051】

更に、上記変換されたデジタル信号を実時間に変換するための回路手段(例:外部から入力されるクロックのサイクルで、上記リング発振器32をオン/オフすることで、クロックサイクルのリング発振器32によるカウント値を測定し、(1)の測定結果を実時間に変換する手段)が設けられ、リング発振器32のキャリブレーションを行っていることを第2の特徴とする。

【0052】

[変形例]

測定する内部信号は、回路規模さえ許せば、マルチプレクサのサイズ及び/または数を拡大することによって、種々の内部信号の遅延時間を測定することが可能となる。また、上記はDDR−SDRAMの例を説明したが、タイミングが厳しい信号がある程度限られる場合には、本発明は、他のメモリやロジックにも適用可能である。

【0053】

上記した実施形態では、実動作に使用する2つの内部信号のスピードをモニタすることが可能になるため、従来のモニタ回路のようなチップ内バラツキによるモニタ回路と実動作回路の相違を気にする必要が無く、デバイス調整時のマージンを減らしても回路の動作が可能となる。

【0054】

図4を参照して、本発明の第2の実施形態に係る半導体装置を説明する。図4には、半導体集積回路によって形成された内部信号タイミング測定回路のうち、リング発振器32に接続されたカウンタ35、及び、これらリング発振器32及びカウンタ35に関連して変更された部分のみが示されている。図示された内部信号タイミング測定回路は、マルチプレクサから出力されるスタート信号START及びストップ信号STOPに応答して内部タイミング信号を生成する内部タイミング測定回路を構成している。

【0055】

図4に示された内部信号タイミング測定回路は、リング発振器32及びカウンタ35のほかに、エッジ検出回路40、レジスタ42、及び、DQ出力部44を備え、DQ出力部44は、DQ端子に接続された構成を備えている。

【0056】

図示されたリング発振器32は、インバータ相当の回路素子を奇数段(ここでは、5ステージ)接続して構成され、その各ステージの出力R0〜R4は、出力端子を介してエッジ検出回路40に接続されている。即ち、リング発振器32の各ステージの出力R0〜R4は出力電圧としてエッジ検出回路40に与えられ、当該エッジ検出回路40は各ステージの出力電位を判定し、判定結果を出力する判定結果出力回路として動作する。

【0057】

エッジ検出回路40はリング発振器32のストップ時のエッジ位置(即ち、位相)を検出する位相検出回路として動作し、検出したエッジ位置をレジスタ42に記憶する。また、リング発振器32の各ステージの出力のうちひとつはカウンタ35に接続されており、リング発振器32が何周回ったかをカウントしている。カウント結果はレジスタ42に記憶される。レジスタ42に記憶した情報はDQ出力部44を介してDQ端子に出力される。

【0058】

図4に示された内部タイミング測定回路の動作を図5及び図6をも参照して説明する。ここで、図5は、リング発振器32とエッジ検出回路40の回路図を示し、図6は、動作波形図を示している。図5に示されたエッジ検出回路40は、リング発振器32の各ステージの出力R0〜R4と、ストップ信号STOPを受けて動作する2つのNAND素子によって構成された5組のアービタ(即ち、フリップフロップ)を備え、アービタは、それぞれアービタ出力E0〜E4を生成する。また、アービタ出力E0〜E4は、直接又はインバータを介して、5つのNANDゲートに与えられ、これらNANDゲートからは、エッジ検出信号D0〜D4がそれぞれ生成される。具体的に云えば、エッジ検出信号D0はアービタ出力E0と、インバータを介して与えられたアービタ出力E2とを受けて生成され、エッジ検出信号D1は、アービタ出力E1と、インバータを介して与えられたアービタ出力E3を受けて生成される。同様に、エッジ検出信号D2は、アービタ出力E2とインバータで反転されたアービタ出力E4とを受けて生成され、エッジ検出信号D3は、アービタ出力E3とインバータで反転されたアービタ出力E0により生成され、更に、エッジ検出信号D4は、アービタ出力E4とインバータで反転されたアービタ出力E1により生成される。

【0059】

リング発振器32のスタート信号STARTとストップ信号STOPとしては、図1を参照して説明したように、それぞれマルチプレクサを介して、測定したい信号が与えられている。初期状態では、図6に示すように、スタート信号START、ストップ信号STOPは、共にローレベルLにある。

【0060】

まず、この状態で、スタート信号STARTがハイレベルHになると、リング発振器32が発振を始め、立ち上がりエッジ及び立ち下がりエッジがリング発振器32内を伝播し始める(図6中のR0−R4)。そして、ストップ信号STOPがHになると、リング発振器32が停止する。

【0061】

停止の瞬間、リング発振器32を構成する各ステージの出力R0−R4は、それぞれ2つのNAND素子から構成されるアービタにより判定され、Rn=Lならアービタ出力En=L、Rn=HならEn=Hとなる。

【0062】

立ち上がりエッジの伝播を検出する場合、アービタ出力は、エッジ通過前にはL、エッジ通過後はHとなるため、立ち上がりエッジは、En=HかつEn+2=Lのところに存在することになる。よって、En+2の反転信号とEnのAND演算結果がHとなるところに発振器停止時のエッジが存在することになる。この結果がエッジ検出信号D0−D4としてエッジ検出回路40から出力される。この結果、測定分解能はリング発振器構成素子2段分の遅延時間にまで高めることが出来る。

【0063】

図7に、測定対象となる各種信号(測定対象信号)とリング発振器(R/O)32間に設けるマルチプレクサの配置のチップイメージを示す。図7の最上段に示された最初のマルチプレクサには、チップで実際に使用される測定対象信号が入力されるが、ここでは、これら複数の測定対象信号は図中省略されている。図7に示すように、チップ内に、複数の測定対象信号に対して、ほぼ均等な数のマルチプレクサ(MUX)が配置され、リング発振器32に対して等しい遅延量を有する経路が形成されている。

【0064】

具体的には、図7には、最上段(即ち、第1段)の4つのマルチプレクサからなる階層、第2段目の2つのマルチプレクサからなる階層、中央に配置された単一マルチプレクサとインバータからなる階層、及び、図4に示されたリングカウンタ32、カウンタ35、及び、DQ出力部42及びDQ端子からなる階層が設けられている。更に、図7には、最下段の4つのマルチプレクサからなる階層及び4つのマルチプレクサに接続された2つのマルチプレクサからなる階層が示されている。図示されているように、各マルチプレクサ間を階層ごとに等長配線にすることで、最上層のマルチプレクサ(MUX)からリング発振器32までの遅延時間をそろえることができる。これは、最下段のマルチプレクサからリング発振器32までの遅延時間についても同様である。

【0065】

これにより、同じような作用をする信号の遅延時間をチップ内で比較する場合、配線長による影響を考慮する必要がなくなり、判断が容易になる。

【0066】

図8に示すように、リング発振器32の直前に、2入力(ここでは、CNTL、IN)に応答するマルチプレクサが設けられている。このマルチプレクサは、測定対象信号の立ち上がりエッジを測定する場合には、同相側(上側)の経路を、立下りエッジを測定する場合には、反転側(下側)の経路を選択して、リング発振器32は、入力は常に立ちあがりエッジとなるような出力を生成する出力回路として動作する。

【0067】

このように、図4〜図8に示された内部タイミング測定回路では、リング発振器32にエッジ検出回路40を設け、発振停止時の立ち上がり(または立下り)エッジの場所を検出保持し、外部に読み出せるようにすることで、リング発振器32の発振周期以下の高分解能を実現できる。即ち、この実施形態によれば、リング発振器の発振周期(1ns程度)以下の測定分解能(例えば、200ps以下)の分解能を実現できる。

【0068】

また、測定対象信号について、チップ内の局所領域ごとにマルチプレクサを設け、さらに各マルチプレクサの出力を入力としてそのうちのひとつを出力する別のマルチプレクサを複数直列接続し、最終的にリング発振器32の入力として樹形図的にひとつにしぼることで、配線チャネルを最小限にすることができる。

【0069】

更に、各マルチプレクサ間を結ぶ信号を、樹形図の同一階層に当たる部分ごとに等長配線にすることで各信号間の入力からリング発振器までの伝播遅延時間差を無くし、結果の解釈(チップ内バラツキによる信号遅延差)を容易にする。さらにリング発振器の入力の直前に、2入力マルチプレクサを設け、一方の入力では入力信号の同相信号を、他方の入力では入力信号の逆相(反転)信号を出力するようにすることで、測定対象が立下りエッジでも立ち上がりエッジでもリング発振器への入力はどちらか一方に統一することができる。これによって、測定対象信号の配線が存在する領域ごとにリング発振器32までの距離が異なり、伝播遅延時間に差があっても、仕上がりばらつきのチップ内場所依存性をなくすことができる。

【0070】

このように、第2の実施形態によれば、チップ上のリング発振器を、主要信号およびクロックで発振、停止させ、発振回数および停止時の発振器内の立ち上がりエッジの位置を、データ出力回路を介して出力することで、主要信号のタイミングをチップごとにウェハテスト時に測定することができる。これによって、立下りエッジを立ち上がりエッジに変換する等の手段が不要となり、素子数の増加を防止できる。

【0071】

以上説明したように、第2の実施形態に係る半導体装置は、リング発振器32に、発振回数をカウントするカウンタ35と、リング発振器32停止時のリング発振器32内の信号エッジ位置を検出するエッジ検出回路40を設けた構成の内部信号タイミング測定回路を有している。更に、内部信号タイミング測定回路には、カウンタの発振回数とエッジ検出回路の結果を必要時間保持するレジスタが設けられても良い。

【0072】

更に、第2の実施形態に係る内部信号タイミング測定回路は、測定対象となる内部信号の発生回路と測定手段(リング発振器)の間に、複数のマルチプレクサを設け、これらのマルチプレクサを樹形図的な接続を経て最終的にひとつの信号出力に絞られるように配置すると共に、各階層内での出力配線長を等しくした構成を備えていても良い。

【0073】

また、図8に示すように、上記測定手段であるリング発振器の直前に2入力マルチプレクサを設け、一方の入力では入力信号の同相信号を、他方の入力では入力信号の逆相(反転)信号を出力するようにすることで、測定対象が立下りエッジでも立ち上がりエッジでもリング発振器への入力はどちらか一方に統一することができることを特徴とする内部信号タイミング測定回路が得られる。

【0074】

図9を参照して、本発明の第3の実施形態に係る半導体装置を説明する。図9に示された半導体装置は、リング発振器32とカウンタ35の間にハザードリジェクタ46を備えると共に、エッジ検出回路40aの回路構成の点で、図4に示された内部信号タイミング測定回路と相違している。尚、ハザードリジェクタ46は、エッジ検出回路40からの出力信号を受けて、後述する特定条件において、カウンタ35へのカウントアップ信号出力を停止させる機能を有する回路、即ち、予め定められた状態になるのを禁止する機能を備えた回路である。

【0075】

図10には、リング発振器32、エッジ検出回路40a、及びハザードリジェクタ46の詳細回路図が示されており、図11には、その動作波形図が示されている。図10に示されたエッジ検出回路40aは、図5に示されたエッジ検出回路40のアービタの出力E0〜E4を更に論理演算して、D0〜D4だけでなく、D5〜D9をエッジ検出出力として生成するNAND素子及びインバータを設けると共に、これらD0〜D9を論理演算する論理回路を設け、エッジ検出回路40aの判定結果信号J0〜J9を生成している。

【0076】

具体的に説明すると、アービタ出力E0〜E4を出力する5つのアービタは図5に示されたものと同様である。一方、アービタ出力E0〜E4を演算して出力D0〜D9を出力する論理回路は、アービタ出力E0及びE1が与えられるNAND素子及びNOR素子を備える共に、アービタ出力E0はアービタ出力E4が与えられるNAND素子及びNOR素子にも与えられている。このように、リング発振器32の互いに隣接する段の出力から生成されたアービタ出力EnとEn+1が一組のNAND素子及びNOR素子に与えられている。更に、各NOR素子は、それぞれ、インバータに出力されており、この結果、インバータからは、D0、D6、D2、D8、及び、D4が出力されると共に、NAND素子からはD5、D1、D7、D3、及びD9が出力されている。出力D0はインバータを介して、出力D4と共にNAND素子に与えられ、エッジ検出信号J0として出力される。また、出力D0は、直接、隣接するNAND素子で、出力D6を反転した信号とのNAND動作によりエッジ検出信号J6が出力されている。出力D5の反転信号と出力D9はNAND素子に与えられ、エッジ検出信号J5が出力されている。以下、他のエッジ検出信号も同様な論理回路を介して出力されている。

【0077】

また、図示されたハザードリジェクタ46は、2のインバータを介して与えられるストップ制御信号STOPを遅延する遅延回路(DLY)460、出力D8、D9をそれぞれ反転するインバータ461、462、リング発振器32のR3出力を反転するインバータ463、インバータ463の出力を遅延する遅延回路464、遅延回路460の入力及びインバータ462に接続されたNAND素子465、遅延回路460の出力及びインバータ461に接続されたNAND素子466とを備えている。遅延回路464、NAND素子465及び466の出力はNAND素子467に与えられ、当該NAND素子467の出力は2つのNAND素子、インバータ、及び遅延回路によって構成されたフリップフロップ回路469に与えられている。

【0078】

図示されたエッジ検出回路40aは、リング発振器32停止時の出力がH又はLレベルである単位遅延素子が3段以上連続した場合、その連続した単位遅延素子に対しエッジの伝播遅延時間がもっとも早い単位遅延素子にてエッジが検出されたと判定する。

【0079】

ここでは、まず、測定時間分解能の高精度化から説明する。リング発振器32のスタート制御信号STARTとストップ信号STOPは、それぞれ前述した形式で、マルチプレクサを介して、測定対象信号に基づいて生成される。

【0080】

図11に示すように、初期状態はSTART、STOPともにLである。スタート制御信号STARTがHになると、リング発振器32が発振を始め、立ち上がりエッジ及び立ち下がりエッジがリング発振器32内を伝播し始める(図11中のR0−R4)。そして、ストップSTOPがHになるとリング発振器32が停止する。停止の瞬間、リング発振器32を構成する各段の出力R0−R4は、それぞれ2つのNAND素子から構成されるアービタにより判定され、Rn=Lならアービタ出力En=L、Rn=HならEn=Hとなる。よって、En=HかつEn+1=Hのところ、またはEn=LかつEn+1=Lのところにエッジは存在することになり、これらを、D0,2,4,6,8を出力するNOR+INV列とD1,3,5,7,9を出力するNAND列で検出する。

【0081】

図11の場合、E4=LかつE0=LなのでLエッジがここで検出されD4=Lになる。上記によりリング発振器32の遅延素子(図10の場合、2NAND)1段分が測定時間分解能になる。

【0082】

ほとんどの場合、リング発振器32停止時にEn=HかつEn+1=H、またはEn=LかつEn+1=Lになるのは1箇所であるが、場合によってはEn=HかつEn+1=HかつEn+2=H、またはEn=LかつEn+1=LかつEn+2=Lとなる場合がある。この場合、2箇所のDnがLになってエッジ判定を誤ってしまう。

【0083】

これを避けるため、連続するふたつのLエッジ判定結果(D0とD6など)またはHエッジ判定結果(D5とD1など)を比較し、リング発振器32の伝播遅延時間が早い方(上記例ではD0またはD5)のエッジ判定結果がLになれば、遅い方(上記例ではD6またはD1)はHにしてしまう回路を設けてある。この回路を通して最終的に得られるエッジ判定結果信号がJ0−9である。

【0084】

図10では、R3=Lになったときに、カウンタ35がカウントアップすることでリング発振器32の周回数をカウントしている。ここで注意しなければならないのは、リング発振器32がSTARTから実際に1周するタイミングはR4がHになったタイミングであるということである。つまり、もしR3=Lになったタイミングでリング発振器が停止した場合、あるいはR4=Hになったタイミングでリング発振器32が停止した場合には、カウンタ35のカウントアップ動作は起きてはならない。

【0085】

このカウントアップ動作が生じないように保証するために、図10のハザードリジェクタ46が設けられている。図示されたハザードリジェクタ46は、リング発振器32における停止状態を監視して、特定の停止状態が発生しないようにするための回路であり、図示された例は、R3=Lになったタイミングでカウンタがカウントアップするのを防止する論理回路によって構成されている。

【0086】

図示されたハザードリジェクタ46を設けることにより、例えば、R3=Lになったタイミングでリング発振器32が停止した場合、D8=Lとなる。このため、図示されたハザードリジェクタ46は、D8=Lの場合、R3=Lがカウンタに伝わらないように、3入力NANDを遮断するような論理回路構成を備えている。更に、R3からの信号経路にはD8発生の伝播遅延時間を保証するため遅延回路が挿入されている。同様に、R4=Hになったタイミングでリング発振器32が停止した場合にはD9=Lとなるので、D9=Lの場合にもR3=Lがカウンタに伝わらないように3入力NANDを遮断する論理回路が設けられている。

【0087】

第3の実施形態に係る内部信号タイミング測定回路は、リング発振器32とカウンタ35の間にハザードリジェクタ46を設け、エッジ検出回路40aの検出結果がある特定の場合(カウンタへカウントアップ信号を出力するリング発振器内の遅延素子の前後一定範囲内でエッジが検出された場合)、カウンタのカウントアップ動作が起こらないようにすることで、誤カウントアップを起こらないようにすることができる。また、エッジ判定回路46を工夫することで、時間分解能が単位遅延素子1段分の高分解能を実現する。

【0088】

以下、第3の実施形態に係る内部信号タイミング測定回路は、チップ上のリング発振器32を、主要信号およびクロックで発振、停止させ、発振回数および停止時のリング発振器32内の立ち上がりエッジの位置を、誤動作を生じることなく、データ出力回路を介して出力することができ、且つ、他の実施形態に係る内部信号タイミング測定回路と同様に、主要信号のタイミングをチップごとにウェハテスト時に測定することができる。

【0089】

更に、第2の実施形態に比較して、単位遅延素子1段分の高分解能が実現できると言う利点もある。

【0090】

本発明の第3の実施形態に係る内部信号タイミング測定回路は、リング発振器に、発振回数をカウントするカウンタ、リング発振器停止時のリング発振器内の信号エッジ位置を検出するエッジ検出回路、カウンタ及びエッジ検出回路の結果を必要期間保持するレジスタ、及び、カウンタとリング発振器の間にハザードリジェクタを有することによって特徴付けられる。

【0091】

更に、本発明の第3の実施形態に係るエッジ検出回路は、連続した単位遅延素子2段のリング発振器停止時の出力がHレベルであることを検出する回路と、連続した単位遅延素子2段のリング発振器停止時の出力がLレベルであることを検出する回路によって特徴付けられる。具体的には、エッジ検出回路は、リング発振器停止時の出力がHレベルである単位遅延素子が3段以上連続した場合、または、リング発振器停止時の出力がLレベルである単位遅延素子が3段以上連続した場合には、その連続した単位遅延素子に対しエッジの伝播遅延時間がもっとも早い単位遅延素子にてエッジが検出されたと判定する処理を実施する回路を有することによっても特徴付けられる。

【産業上の利用可能性】

【0092】

本発明は、DRAM等の半導体装置だけでなく、内部信号のタイミングを高精度で測定し、設定する必要のある電子回路等に広く応用できる。

【図面の簡単な説明】

【0093】

【図1】本発明の第1の実施形態に係る半導体装置を示す回路図である。

【図2】図1に示された半導体装置内に設けられたリング発振器の発振周期を測定する場合における動作を説明する波形図である。

【図3】図1に示された半導体装置の内部信号タイミングを測定する動作を説明する波形図である。

【図4】本発明の第2の実施形態に係る内部信号タイミング回路の概略を示す回路図である。

【図5】図4の一部をより詳細に示す回路図である。

【図6】図5の回路の動作を説明する波形図である。

【図7】図4に示された内部信号タイミング回路におけるマルチプレクサとリング発振器の配置関係を示す概略図である。

【図8】図4に示された内部信号タイミング回路の出力部を示す図である。

【図9】本発明の第3の実施形態に係る内部信号タイミング回路の概略を示す回路図である。

【図10】図9に示された内部信号タイミング回路の一部をより具体的に示す回路図である。

【図11】図10に示された内部信号タイミング回路の動作を説明する波形図である。

【符号の説明】

【0094】

10 コマンドデコーダ(CMDDEC)

12 ロウ制御回路(ROWCNTL)

14 カラム制御回路(COLCNTL)

16 メモリアレイ(MEMARY)

18 ロウデコーダ(ROWDEC)

20 カラムデコーダ(COLDEC)

22 メインアンプ/バッファ回路(MA/WRT.BF.)

24 ライトFIFO(WRITEFIFO)

26 リードFIFO(READFIFO)

30 テスト制御回路

32 リング発振器

34、35 カウンタ

36 第1のマルチプレクサ

38 第2のマルチプレクサ

40、40a エッジ検出回路

42 レジスタ

44 DQ出力部

46 ハザードリジェクタ

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、半導体集積回路によって構成され、主要な内部制御信号のタイミングをチップごとに測定することを可能とした半導体装置、内部信号タイミング測定回路、及び遅延時間測定方法に関する。

【背景技術】

【0002】

半導体プロセスの微細化が進み、デバイスの仕上がりのバラツキが回路動作に与える影響が大きくなってきている。従来、プロセス、電圧、温度が全てベストの条件と全てワーストの条件で回路動作を保証することで、内部回路のタイミングマージンを確保してきた。しかし、プロセスばらつきの影響が大きくなった結果、上記設計手法では回路動作マージンが確保できず、要求性能を満足することが困難になってきた。

【0003】

そこで、デバイスの仕上がりをモニタできる回路をチップ上に設け、その測定結果をもとに、例えば、内部電圧を微調整するなどして、回路の動作マージンを確保する手法が提案されている。しかし、同手法にも問題がある。そのひとつは、例えば、トランジスタの仕上がりのバラツキにはロット間、ウェハ間でばらつくと共に、ウェハ内でもばらつくことが判明した。このため、例え、チップサイズを犠牲にして上記モニタ回路を同一チップ内に複数設置しても、チップ内のバラツキを考慮してモニタ回路の測定結果にある程度のマージンをもたせて、内部電圧などを微調整して微妙に加減する必要があるが、この微調整は難しく、過剰マージンとなることが多い。

【0004】

更に、モニタ回路を使用してデバイスの仕上がりをモニタする手法をより具体的に説明する。通常、半導体装置を形成する半導体集積回路に、クロック同期遅延制御回路を組み込むことが行われている。クロック同期遅延制御回路は、外部クロック信号に同期し、外部クロック信号のn周期分(nは整数)遅延した信号を生成し、半導体集積回路の内部回路の遅延時間を調整している。

【0005】

このようなクロック同期遅延制御回路には、SAD(Synchronous Adjustable Delay)方式と、DLL(Delay Locked Loop)方式とがあるが、いずれの場合にも、ディレイモニタが使用されている。この場合、外部クロック信号に対する内部クロック信号の同期精度を高めるためには、ディレイモニタにおける遅延時間を正確にクロックレシーバの遅延時間と出力バッファの遅延時間との和に等しくする必要がある。

【0006】

即ち、クロック同期遅延制御回路は、本来、外部クロック入力に対するクロックレシーバの入力遅延量tRCと出力バッファにおける出力遅延量tDRを測定するために使用されている。このように、クロックレシーバ及び出力バッファにおける遅延量を測定することによって、半導体集積回路に実装された状態で、遅延測定モードによる動作を行なわせることにより、各回路の実際の信号遅延時間や外部データバスの負荷状態に応じたデータ出力時の遅延時間をディレイモニタに設定することができる。このため、ディレイモニタを含む半導体集積回路では、実際の遅延時間を正確に設定できる。

【0007】

一方、特許文献1には、改良されたクロック同期遅延制御回路を含む半導体集積回路が開示されている。特許文献1に示されたクロック同期遅延制御回路では、外部クロック信号に応答してクロックレシーバから信号CLKを出力し、当該信号CLKを同期遅延制御回路及びディレイモニタに供給する構成が採用されている。

【0008】

更に、同期遅延制御回路は、遅延測定モードの際、測定用信号である疑似内部クロック信号DCLKを出力する回路を備えており、当該疑似内部クロック信号DCLKはクロックドライバ及び出力制御回路で遅延されて、内部クロック信号としてデータ入出力回路に出力されている。データ入出力回路は、内部クロック信号に同期して、データを出力バッファ及び出力ドライバを介して外部データバスに出力すると共に、当該データをデータレシーバによって取り込むような構成を備えている。

【0009】

この場合、ディレイモニタには、疑似内部クロック信号DCLKの発生から出力データDOUTが外部データバスに出力されるまでの出力遅延量tDRと、データレシーバにおける遅延量tRCとの和に相当する遅延時間が設定されている。

【0010】

このような構成では、外部データバスに”H”レベルの疑似データを出力するようにしておくと、データレシーバによる入力遅延量tRCだけ、遅延してデータ信号DATが出力される。

【0011】

この場合、疑似内部クロック信号DCLKに応答して、測定開始信号STRを生成し、データ信号DATに応答して測定停止信号STPを生成して、ディレイモニタに入力することによって、(出力遅延量tDR)+(入力遅延量tRC)を測定でき、ディレイモニタに、遅延時間を設定する。

【0012】

特許文献1では、クロックレシーバにおける遅延量と、データレシーバにおける遅延量とが実質的に等しいものとして扱うことにより、ディレイモニタで実際の遅延時間を正確に設定できる。

【0013】

換言すれば、特許文献1では、クロックレシーバとデータレシーバとを等価な回路構成にすると共に、外部クロック入力は外部データバスに出力された疑似データに置き換えて測定している。この条件の下で、クロックレシーバとデータレシーバにおける遅延量を実質的に等しくすることができる。

【0014】

【特許文献1】特開2000−269423号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

このように、クロックレシーバとデータレシーバにおける遅延量を等しいとして、外部クロックを疑似データに置き換えた場合、次に述べるような問題を含んでおり、この手法により得られた測定値は通常動作時の回路特性を正確には反映していないという問題があった。

【0016】

第1には、トランジスタ等のデバイスは短チャネル化等、高性能化が進み、製造プロセスのばらつきに対して敏感になっており、半導体ウェハ間のみならず、チップ内のばらつきも無視できない状況であるため、クロックレシーバとデータレシーバについて回路構成をあわせても同一特性を有するとは限らないという問題点がある。

【0017】

即ち、クロックレシーバとデータレシーバとはチップ内の互いに異なる位置に設けられているため、正確に同一の特性を示すとは云えない。この結果、特許文献1の手法では、チップ毎の遅延時間の相違を正確に把握することができない。

【0018】

第2には、外部クロックバスと外部データバスはそれぞれ接続されるデバイスの個数やインターフェースが全く異なり、信号波形、例えば、信号のライズ・フォール波形やノイズ特性が異なるため、それらに対する回路の応答特性は異なるという問題点がある。

【0019】

第3には、クロックの遅延量及びデータの遅延量だけについて考慮されているだけで、DRAM等で使用される各種信号の遅延量については、全く考慮されていない。

【課題を解決するための手段】

【0020】

本発明によれば、タイミングマージンがクリティカルな信号を設計段階で選び出し、そのタイミングをチップごとに測定する手段を設け、ウェハテスト時に同タイミングを測定してその結果でチップごとに調整を実施できる半導体装置が得られる。

【0021】

即ち、本発明の一実施形態によれば、第1の内部回路制御信号と該第1の内部回路制御信号から所定の遅延時間経過後に発生する第2の内部回路制御信号を生成する内部回路と、

前記第1の内部回路制御信号と前記第2の内部回路制御信号を受け、前記第1の内部回路制御信号を遅延時間測定開始信号として発生すると共に、前記第2の内部回路制御信号を遅延時間測定終了信号として発生する測定用信号発生回路と、前記遅延時間測定開始信号と前記遅延時間測定終了信号を入力とし、遅延時間測定結果を出力する遅延時間測定回路を備えていることを特徴とする半導体装置が得られる。

【0022】

このように、本発明では、モニタ回路ではなく実動作で使用する内部回路のスピードを測定しているため、モニタ回路と実動作回路間の相違を考慮する必要が無く、その分マージンを少なくすることができる。

【0023】

本発明の別の実施形態によれば、電子回路を実際に動作させるために使用される複数の信号から第1及び第2の信号を選択し、前記第1の信号及び第2の信号を遅延時間測定開始信号及び遅延時間測定終了信号に変換して、遅延時間測定回路に供給し、前記遅延時間測定回路では、前記遅延時間測定開始信号及び前記遅延時間測定終了信号との間の遅延時間を測定し、測定結果を出力することを特徴とする遅延時間測定方法が得られる。

【発明の効果】

【0024】

本発明では、チップ上のリング発振器等の遅延時間測定回路を、チップで使用される主要信号および/又はクロックで発振、停止させ、発振回数をカウントし、カウント結果を、データ出力回路を介して出力することで、主要信号のタイミングをチップ毎にウェハテスト時に測定することができる。この構成によれば、モニタ回路ではなく実動作で使用する回路のスピードを測定しているため、モニタ回路と実動作回路間の相違を考慮する必要が無く、その分マージンを少なくすることができる。

【発明を実施するための最良の形態】

【0025】

図1を参照して、本発明の第1の実施形態に係る半導体装置を説明する。図1では、本発明をDDR-SDRAMに適用した場合における回路構成概略図が示されている。図示されたDDR-SDRAMは集積回路化されており、図2及び図3にその動作波形図が示されている。

【0026】

図1に示されているように、本発明の第1の実施形態に係る半導体装置、即ち、DDR-SDRAMは、コマンドデコーダ(CMDDEC)10、ロウ制御回路(ROWCNTL)12、カラム制御回路(COLCNTL)14、メモリアレイ(MEMARY)16、ロウデコーダ(ROWDEC)18、カラムデコーダ(COLDEC)20、メインアンプ/バッファ回路(MA/WRT)22、ライトFIFO(WRITEFIFO)24、リードFIFO(READFIFO)26、及びDQ端子(DQ)を備え、これらの回路は、半導体集積回路の内部回路を構成している。コマンドデコーダ(CMDEC)10には、通常のDRAMと同様に、コマンド(CMD),/CS,/RAS/,/CAS,及び/WEが与えられ、図示されたコマンドデコーダ(CMDEC)10は、テストコマンドをデコードしてテストモード信号(TEST)を出力する機能を有している。

【0027】

更に、図示された半導体集積回路は、テスト制御回路(TESTDEC&CNTL)30、リング発振器(Ring Oscillator)32、及びカウンタ(COUNTER)34を含み、リングオシレータ32は第1のマルチプレクサ(MUX)36及び第2のマルチプレクサ(MUX)38と接続されている。

【0028】

ここで、テスト制御回路(TESTDEC&CNTL)30、及び、第1のマルチプレクサ(MUX)36及び第2のマルチプレクサ(MUX)38は、遅延時間測定開始を指示するテストスタート信号(遅延時間測定開始信号)STARTを発生すると共に、遅延時間測定終了をあらわすテストストップ信号(遅延時間測定終了信号)STOPを発生する測定用信号発生回路として動作する。一方、リング発振器(Ring Oscillator)32、及びカウンタ(COUNTER)34は遅延時間測定回路を構成している。

【0029】

第1のマルチプレクサ36には、内部回路であるコマンド制御回路10からバンク起動信号ACTと読み出し信号READが与えられており、更に、テスト制御回路30からテストスタート信号TSTARTが与えられている。他方、第2のマルチプレクサ38には、ROWデコーダ起動信号RE、カラムデコーダ起動信号CE、及び、メインアンプ起動信号MAEが与えられると共に、テストストップ信号TSTOPが与えられている。

【0030】

また、テスト制御回路30は、上記したテストスタート信号TSTART及びテストストップ信号TSTOPを出力すると共に、第1及び第2のマルチプレクサ36及び38及びリードFIFO26に選択信号(SELECT)を出力し、更に、カウンタ34にカウンタリセット信号(CNTRRST)を出力している。

【0031】

本実施形態では、タイミングを測定する信号として、内部回路であるロウ制御回路12及びカラム制御回路14から出力されるROWデコーダ起動信号RE及びカラムデコーダ起動信号CEを測定すると共に、カラム制御回路14から出力されるメインアンプ起動信号MAEを測定することができる。

【0032】

これらの信号タイミングを測定するために、第1及び第2のマルチプレクサ(MUX)36、38、リング発振器32、及び、カウンタ34が設けられている。

【0033】

図示された半導体装置では、まず、内部タイミング信号の測定に利用されるリング発振器32の発振周期を測定する段階と、内部タイミング信号を測定する段階とに分けて測定が行われる。このうち、リング発振器32の発振周期の測定は、ウェハテスト条件(電圧、温度)の下に行われる。

【0034】

(1)図2を参照して、ウェハテスト測定条件(電圧、温度)におけるリング発振器32の発振周期を測定について説明する。

【0035】

まず、テスト制御回路30に、テストモード信号TESTとして、TEST0のコードが図2に示すように、コマンドデコーダ10から入力される。これにより、テスト制御回路30は、カウンタリセット信号CNTRSTをカウンタ34に出力し、この結果、カウンタ34におけるリング発振器32のカウンタ値が0にリセットされる。

【0036】

同時に、テスト制御回路30は第1及び第2のマルチプレクサ(MUX)36及び38に制御信号として、選択信号(SELECT)を出力し、この結果、図示された半導体装置はクロック測定モードに設定される。

【0037】

第1及び第2のマルチプレクサ36及び38は、選択信号(SELECT)にしたがって、テストスタート信号TSTART及びテスト終了信号TSTOPをスタート信号START及びストップ信号STOPをそれぞれ選択する状態となる。この結果、スタート信号STARTとストップ信号STOPをバイパスする第1及び第2のマルチプレクサ36及び38の経路が選択される。一方、選択信号(SELECT)はリードFIFO26にも与えられ、リードFIFO26の入力がカウンタ34の出力を選択する経路に切り替えられる。

【0038】

次に、図2に示すように、半導体集積回路であるDRAMに、テストTEST1のコードが入力される。これにより、テスト制御回路30からリング発振器32にテスト起動信号TSTARTが発生する。テスト起動信号TSTARTは、第1のマルチプレクサ36から、スタート信号STARTとしてリング発振器32に送出され、リング発振器32が発振動作を開始する。これと同時に、カウンタ34もリング発振器32の出力のカウント動作を開始する。

【0039】

続いて、テスト制御回路30は、特定時間後(図2では2クロック(CLK)サイクル後)に、テストストップ信号TSTOPのコードを出力する。これにより、テスト制御回路30は、リング発振器32のテストストップ信号TSTOPを出力し、これが、ストップ信号STOPとなってリング発振器32に与えられる。ストップ信号STOPを受けて、リング発振器32は発振を停止し、カウンタ34もカウント動作を停止して、停止したときのカウンタ値がカウンタ34に保持される。

【0040】

次に、1クロックサイクル後、テストTEST3のコードがテスト制御回路30に入力されると、カウンタ34に保持されたカウント値がデジタル信号としてDQ端子に出力される。図2では、クロックCLKの立ち上がり/立下りとともに1桁ずつ順次出力される例が示されている。

【0041】

テストコードTEST1とTEST2を入力した時間の差はテスタプログラム上あらかじめ分かっているので、上記のように出力されたカウンタの値で同時間差の除算を実行することで、チップ内に組み込まれたリング発振器32の実際の発振周期が求められる。

【0042】

(2)図3を参照して、内部タイミング信号を測定する動作を説明する。

【0043】

この場合、半導体集積回路であるDRAMのテスト制御回路30にTEST0’のコードが入力される。このコードは、内部タイミング信号測定モード、即ち、テストモードをあらわしており、このコードを受けると、テスト制御回路30はカウンタリセット信号CNTRSTを発生し、カウンタ34に出力する。カウンタリセット信号CNTRSTを受けると、カウンタ34はカウンタ値を0にリセットされ、リードFIFO26の入力がカウンタ34の出力を選択する経路に切り替えられる。この動作は、上記した(1)の場合と同様である。

【0044】

しかしながら、内部タイミング信号を測定する場合、テスト制御回路30は選択信号(SELECT)をも出力する。ここでは、バンク起動信号ACTとロウデコーダ起動信号REが測定されるものとする。この場合、バンク起動信号ACTとロウデコーダ起動信号REがそれぞれ第1及び第2の内部回路制御信号として第1及び第2のマルチプレクサ36及び38に与えられるものとする。

【0045】

第1及び第2のマルチプレクサ36及び38は、選択信号(SELECT)をテスト制御回路30から受けると、それぞれバンク起動信号ACTとロウデコーダ起動信号REを選択する状態になり、これらの信号をそれぞれSTARTとSTOPとしてバイパスする経路を選択する状態に切り替えられる。ここで、バンク起動信号ACT及びロウデコーダ起動信号REは、実際にチップの実動作に使われる信号である。

【0046】

この状態で、DRAMのコマンド制御回路10にバンク起動命令を入力されると、コマンド制御回路10は、バンク起動信号ACTを発生して第1のマルチプレクサ36に出力し、これがそのままスタート信号STARTとなってリング発振器32に送られる。この結果、リング発振器32が発振動作を開始し、カウンタ34もリング発振器32の出力のカウント動作を開始する。続いて、ロウ制御回路12は、コマンド制御回路10からバンク起動信号ACTを受けた後、ロウデコーダ起動信号REを出力する。ロウデコーダ起動信号REは、そのままストップ信号STOPとして、リング発振器31に出力される。ストップ信号STOPを受けると、リング発振器32は発振を停止する一方、カウンタ34はカウント動作を停止し、停止したときのカウント値を保持する。

【0047】

次に、図3に示すように、テストTEST3のコードが入力されると、(1)と同様に保持されたカウンタ34のカウント値がデジタル信号の形で、DQに出力される。この出力されたカウンタ34のカウント値を(1)で求めたリング発振器32の発振周期で乗算することでACT/RE間の遅延時間が求められる。

【0048】

上記した例では、バンク起動信号ACTとロウデコーダ起動信号REとの間の遅延時間を求める場合についてのみ説明したが、カラムデコーダ起動信号CE、メインアンプ起動信号MAEの遅延時間も、選択信号(SELECT)により、第1及び第2のマルチプレクサ36、38の経路を選択すれば、これらを第1及び第2の内部回路制御信号として同様の手順で求めることができる。

【0049】

このように、上記した実施の形態は、チップ上の異なる位置に設けられた内部回路(即ち、コマンド制御回路10及びロウ制御回路12)からの2つの内部信号(上記した例では、ACTとRE)の遷移時間差を、チップ外に読み出すことが可能なデジタル信号に変換する回路手段(例:リング発振器32とカウンタ34)が設けられていることを第1の特徴としている。

【0050】

したがって、上記した実施形態では、ロウ制御回路12、第1及び第2のマルチプレクサ36、38は、スタート制御信号START及びストップ制御信号STOPをリング発振器32に第1及び第2の内部回路制御信号として出力する内部回路として動作する。

【0051】

更に、上記変換されたデジタル信号を実時間に変換するための回路手段(例:外部から入力されるクロックのサイクルで、上記リング発振器32をオン/オフすることで、クロックサイクルのリング発振器32によるカウント値を測定し、(1)の測定結果を実時間に変換する手段)が設けられ、リング発振器32のキャリブレーションを行っていることを第2の特徴とする。

【0052】

[変形例]

測定する内部信号は、回路規模さえ許せば、マルチプレクサのサイズ及び/または数を拡大することによって、種々の内部信号の遅延時間を測定することが可能となる。また、上記はDDR−SDRAMの例を説明したが、タイミングが厳しい信号がある程度限られる場合には、本発明は、他のメモリやロジックにも適用可能である。

【0053】

上記した実施形態では、実動作に使用する2つの内部信号のスピードをモニタすることが可能になるため、従来のモニタ回路のようなチップ内バラツキによるモニタ回路と実動作回路の相違を気にする必要が無く、デバイス調整時のマージンを減らしても回路の動作が可能となる。

【0054】

図4を参照して、本発明の第2の実施形態に係る半導体装置を説明する。図4には、半導体集積回路によって形成された内部信号タイミング測定回路のうち、リング発振器32に接続されたカウンタ35、及び、これらリング発振器32及びカウンタ35に関連して変更された部分のみが示されている。図示された内部信号タイミング測定回路は、マルチプレクサから出力されるスタート信号START及びストップ信号STOPに応答して内部タイミング信号を生成する内部タイミング測定回路を構成している。

【0055】

図4に示された内部信号タイミング測定回路は、リング発振器32及びカウンタ35のほかに、エッジ検出回路40、レジスタ42、及び、DQ出力部44を備え、DQ出力部44は、DQ端子に接続された構成を備えている。

【0056】

図示されたリング発振器32は、インバータ相当の回路素子を奇数段(ここでは、5ステージ)接続して構成され、その各ステージの出力R0〜R4は、出力端子を介してエッジ検出回路40に接続されている。即ち、リング発振器32の各ステージの出力R0〜R4は出力電圧としてエッジ検出回路40に与えられ、当該エッジ検出回路40は各ステージの出力電位を判定し、判定結果を出力する判定結果出力回路として動作する。

【0057】

エッジ検出回路40はリング発振器32のストップ時のエッジ位置(即ち、位相)を検出する位相検出回路として動作し、検出したエッジ位置をレジスタ42に記憶する。また、リング発振器32の各ステージの出力のうちひとつはカウンタ35に接続されており、リング発振器32が何周回ったかをカウントしている。カウント結果はレジスタ42に記憶される。レジスタ42に記憶した情報はDQ出力部44を介してDQ端子に出力される。

【0058】

図4に示された内部タイミング測定回路の動作を図5及び図6をも参照して説明する。ここで、図5は、リング発振器32とエッジ検出回路40の回路図を示し、図6は、動作波形図を示している。図5に示されたエッジ検出回路40は、リング発振器32の各ステージの出力R0〜R4と、ストップ信号STOPを受けて動作する2つのNAND素子によって構成された5組のアービタ(即ち、フリップフロップ)を備え、アービタは、それぞれアービタ出力E0〜E4を生成する。また、アービタ出力E0〜E4は、直接又はインバータを介して、5つのNANDゲートに与えられ、これらNANDゲートからは、エッジ検出信号D0〜D4がそれぞれ生成される。具体的に云えば、エッジ検出信号D0はアービタ出力E0と、インバータを介して与えられたアービタ出力E2とを受けて生成され、エッジ検出信号D1は、アービタ出力E1と、インバータを介して与えられたアービタ出力E3を受けて生成される。同様に、エッジ検出信号D2は、アービタ出力E2とインバータで反転されたアービタ出力E4とを受けて生成され、エッジ検出信号D3は、アービタ出力E3とインバータで反転されたアービタ出力E0により生成され、更に、エッジ検出信号D4は、アービタ出力E4とインバータで反転されたアービタ出力E1により生成される。

【0059】

リング発振器32のスタート信号STARTとストップ信号STOPとしては、図1を参照して説明したように、それぞれマルチプレクサを介して、測定したい信号が与えられている。初期状態では、図6に示すように、スタート信号START、ストップ信号STOPは、共にローレベルLにある。

【0060】

まず、この状態で、スタート信号STARTがハイレベルHになると、リング発振器32が発振を始め、立ち上がりエッジ及び立ち下がりエッジがリング発振器32内を伝播し始める(図6中のR0−R4)。そして、ストップ信号STOPがHになると、リング発振器32が停止する。

【0061】

停止の瞬間、リング発振器32を構成する各ステージの出力R0−R4は、それぞれ2つのNAND素子から構成されるアービタにより判定され、Rn=Lならアービタ出力En=L、Rn=HならEn=Hとなる。

【0062】

立ち上がりエッジの伝播を検出する場合、アービタ出力は、エッジ通過前にはL、エッジ通過後はHとなるため、立ち上がりエッジは、En=HかつEn+2=Lのところに存在することになる。よって、En+2の反転信号とEnのAND演算結果がHとなるところに発振器停止時のエッジが存在することになる。この結果がエッジ検出信号D0−D4としてエッジ検出回路40から出力される。この結果、測定分解能はリング発振器構成素子2段分の遅延時間にまで高めることが出来る。

【0063】

図7に、測定対象となる各種信号(測定対象信号)とリング発振器(R/O)32間に設けるマルチプレクサの配置のチップイメージを示す。図7の最上段に示された最初のマルチプレクサには、チップで実際に使用される測定対象信号が入力されるが、ここでは、これら複数の測定対象信号は図中省略されている。図7に示すように、チップ内に、複数の測定対象信号に対して、ほぼ均等な数のマルチプレクサ(MUX)が配置され、リング発振器32に対して等しい遅延量を有する経路が形成されている。

【0064】

具体的には、図7には、最上段(即ち、第1段)の4つのマルチプレクサからなる階層、第2段目の2つのマルチプレクサからなる階層、中央に配置された単一マルチプレクサとインバータからなる階層、及び、図4に示されたリングカウンタ32、カウンタ35、及び、DQ出力部42及びDQ端子からなる階層が設けられている。更に、図7には、最下段の4つのマルチプレクサからなる階層及び4つのマルチプレクサに接続された2つのマルチプレクサからなる階層が示されている。図示されているように、各マルチプレクサ間を階層ごとに等長配線にすることで、最上層のマルチプレクサ(MUX)からリング発振器32までの遅延時間をそろえることができる。これは、最下段のマルチプレクサからリング発振器32までの遅延時間についても同様である。

【0065】

これにより、同じような作用をする信号の遅延時間をチップ内で比較する場合、配線長による影響を考慮する必要がなくなり、判断が容易になる。

【0066】

図8に示すように、リング発振器32の直前に、2入力(ここでは、CNTL、IN)に応答するマルチプレクサが設けられている。このマルチプレクサは、測定対象信号の立ち上がりエッジを測定する場合には、同相側(上側)の経路を、立下りエッジを測定する場合には、反転側(下側)の経路を選択して、リング発振器32は、入力は常に立ちあがりエッジとなるような出力を生成する出力回路として動作する。

【0067】

このように、図4〜図8に示された内部タイミング測定回路では、リング発振器32にエッジ検出回路40を設け、発振停止時の立ち上がり(または立下り)エッジの場所を検出保持し、外部に読み出せるようにすることで、リング発振器32の発振周期以下の高分解能を実現できる。即ち、この実施形態によれば、リング発振器の発振周期(1ns程度)以下の測定分解能(例えば、200ps以下)の分解能を実現できる。

【0068】

また、測定対象信号について、チップ内の局所領域ごとにマルチプレクサを設け、さらに各マルチプレクサの出力を入力としてそのうちのひとつを出力する別のマルチプレクサを複数直列接続し、最終的にリング発振器32の入力として樹形図的にひとつにしぼることで、配線チャネルを最小限にすることができる。

【0069】

更に、各マルチプレクサ間を結ぶ信号を、樹形図の同一階層に当たる部分ごとに等長配線にすることで各信号間の入力からリング発振器までの伝播遅延時間差を無くし、結果の解釈(チップ内バラツキによる信号遅延差)を容易にする。さらにリング発振器の入力の直前に、2入力マルチプレクサを設け、一方の入力では入力信号の同相信号を、他方の入力では入力信号の逆相(反転)信号を出力するようにすることで、測定対象が立下りエッジでも立ち上がりエッジでもリング発振器への入力はどちらか一方に統一することができる。これによって、測定対象信号の配線が存在する領域ごとにリング発振器32までの距離が異なり、伝播遅延時間に差があっても、仕上がりばらつきのチップ内場所依存性をなくすことができる。

【0070】

このように、第2の実施形態によれば、チップ上のリング発振器を、主要信号およびクロックで発振、停止させ、発振回数および停止時の発振器内の立ち上がりエッジの位置を、データ出力回路を介して出力することで、主要信号のタイミングをチップごとにウェハテスト時に測定することができる。これによって、立下りエッジを立ち上がりエッジに変換する等の手段が不要となり、素子数の増加を防止できる。

【0071】

以上説明したように、第2の実施形態に係る半導体装置は、リング発振器32に、発振回数をカウントするカウンタ35と、リング発振器32停止時のリング発振器32内の信号エッジ位置を検出するエッジ検出回路40を設けた構成の内部信号タイミング測定回路を有している。更に、内部信号タイミング測定回路には、カウンタの発振回数とエッジ検出回路の結果を必要時間保持するレジスタが設けられても良い。

【0072】

更に、第2の実施形態に係る内部信号タイミング測定回路は、測定対象となる内部信号の発生回路と測定手段(リング発振器)の間に、複数のマルチプレクサを設け、これらのマルチプレクサを樹形図的な接続を経て最終的にひとつの信号出力に絞られるように配置すると共に、各階層内での出力配線長を等しくした構成を備えていても良い。

【0073】

また、図8に示すように、上記測定手段であるリング発振器の直前に2入力マルチプレクサを設け、一方の入力では入力信号の同相信号を、他方の入力では入力信号の逆相(反転)信号を出力するようにすることで、測定対象が立下りエッジでも立ち上がりエッジでもリング発振器への入力はどちらか一方に統一することができることを特徴とする内部信号タイミング測定回路が得られる。

【0074】

図9を参照して、本発明の第3の実施形態に係る半導体装置を説明する。図9に示された半導体装置は、リング発振器32とカウンタ35の間にハザードリジェクタ46を備えると共に、エッジ検出回路40aの回路構成の点で、図4に示された内部信号タイミング測定回路と相違している。尚、ハザードリジェクタ46は、エッジ検出回路40からの出力信号を受けて、後述する特定条件において、カウンタ35へのカウントアップ信号出力を停止させる機能を有する回路、即ち、予め定められた状態になるのを禁止する機能を備えた回路である。

【0075】

図10には、リング発振器32、エッジ検出回路40a、及びハザードリジェクタ46の詳細回路図が示されており、図11には、その動作波形図が示されている。図10に示されたエッジ検出回路40aは、図5に示されたエッジ検出回路40のアービタの出力E0〜E4を更に論理演算して、D0〜D4だけでなく、D5〜D9をエッジ検出出力として生成するNAND素子及びインバータを設けると共に、これらD0〜D9を論理演算する論理回路を設け、エッジ検出回路40aの判定結果信号J0〜J9を生成している。

【0076】

具体的に説明すると、アービタ出力E0〜E4を出力する5つのアービタは図5に示されたものと同様である。一方、アービタ出力E0〜E4を演算して出力D0〜D9を出力する論理回路は、アービタ出力E0及びE1が与えられるNAND素子及びNOR素子を備える共に、アービタ出力E0はアービタ出力E4が与えられるNAND素子及びNOR素子にも与えられている。このように、リング発振器32の互いに隣接する段の出力から生成されたアービタ出力EnとEn+1が一組のNAND素子及びNOR素子に与えられている。更に、各NOR素子は、それぞれ、インバータに出力されており、この結果、インバータからは、D0、D6、D2、D8、及び、D4が出力されると共に、NAND素子からはD5、D1、D7、D3、及びD9が出力されている。出力D0はインバータを介して、出力D4と共にNAND素子に与えられ、エッジ検出信号J0として出力される。また、出力D0は、直接、隣接するNAND素子で、出力D6を反転した信号とのNAND動作によりエッジ検出信号J6が出力されている。出力D5の反転信号と出力D9はNAND素子に与えられ、エッジ検出信号J5が出力されている。以下、他のエッジ検出信号も同様な論理回路を介して出力されている。

【0077】

また、図示されたハザードリジェクタ46は、2のインバータを介して与えられるストップ制御信号STOPを遅延する遅延回路(DLY)460、出力D8、D9をそれぞれ反転するインバータ461、462、リング発振器32のR3出力を反転するインバータ463、インバータ463の出力を遅延する遅延回路464、遅延回路460の入力及びインバータ462に接続されたNAND素子465、遅延回路460の出力及びインバータ461に接続されたNAND素子466とを備えている。遅延回路464、NAND素子465及び466の出力はNAND素子467に与えられ、当該NAND素子467の出力は2つのNAND素子、インバータ、及び遅延回路によって構成されたフリップフロップ回路469に与えられている。

【0078】

図示されたエッジ検出回路40aは、リング発振器32停止時の出力がH又はLレベルである単位遅延素子が3段以上連続した場合、その連続した単位遅延素子に対しエッジの伝播遅延時間がもっとも早い単位遅延素子にてエッジが検出されたと判定する。

【0079】

ここでは、まず、測定時間分解能の高精度化から説明する。リング発振器32のスタート制御信号STARTとストップ信号STOPは、それぞれ前述した形式で、マルチプレクサを介して、測定対象信号に基づいて生成される。

【0080】

図11に示すように、初期状態はSTART、STOPともにLである。スタート制御信号STARTがHになると、リング発振器32が発振を始め、立ち上がりエッジ及び立ち下がりエッジがリング発振器32内を伝播し始める(図11中のR0−R4)。そして、ストップSTOPがHになるとリング発振器32が停止する。停止の瞬間、リング発振器32を構成する各段の出力R0−R4は、それぞれ2つのNAND素子から構成されるアービタにより判定され、Rn=Lならアービタ出力En=L、Rn=HならEn=Hとなる。よって、En=HかつEn+1=Hのところ、またはEn=LかつEn+1=Lのところにエッジは存在することになり、これらを、D0,2,4,6,8を出力するNOR+INV列とD1,3,5,7,9を出力するNAND列で検出する。

【0081】

図11の場合、E4=LかつE0=LなのでLエッジがここで検出されD4=Lになる。上記によりリング発振器32の遅延素子(図10の場合、2NAND)1段分が測定時間分解能になる。

【0082】

ほとんどの場合、リング発振器32停止時にEn=HかつEn+1=H、またはEn=LかつEn+1=Lになるのは1箇所であるが、場合によってはEn=HかつEn+1=HかつEn+2=H、またはEn=LかつEn+1=LかつEn+2=Lとなる場合がある。この場合、2箇所のDnがLになってエッジ判定を誤ってしまう。

【0083】

これを避けるため、連続するふたつのLエッジ判定結果(D0とD6など)またはHエッジ判定結果(D5とD1など)を比較し、リング発振器32の伝播遅延時間が早い方(上記例ではD0またはD5)のエッジ判定結果がLになれば、遅い方(上記例ではD6またはD1)はHにしてしまう回路を設けてある。この回路を通して最終的に得られるエッジ判定結果信号がJ0−9である。

【0084】

図10では、R3=Lになったときに、カウンタ35がカウントアップすることでリング発振器32の周回数をカウントしている。ここで注意しなければならないのは、リング発振器32がSTARTから実際に1周するタイミングはR4がHになったタイミングであるということである。つまり、もしR3=Lになったタイミングでリング発振器が停止した場合、あるいはR4=Hになったタイミングでリング発振器32が停止した場合には、カウンタ35のカウントアップ動作は起きてはならない。

【0085】

このカウントアップ動作が生じないように保証するために、図10のハザードリジェクタ46が設けられている。図示されたハザードリジェクタ46は、リング発振器32における停止状態を監視して、特定の停止状態が発生しないようにするための回路であり、図示された例は、R3=Lになったタイミングでカウンタがカウントアップするのを防止する論理回路によって構成されている。

【0086】

図示されたハザードリジェクタ46を設けることにより、例えば、R3=Lになったタイミングでリング発振器32が停止した場合、D8=Lとなる。このため、図示されたハザードリジェクタ46は、D8=Lの場合、R3=Lがカウンタに伝わらないように、3入力NANDを遮断するような論理回路構成を備えている。更に、R3からの信号経路にはD8発生の伝播遅延時間を保証するため遅延回路が挿入されている。同様に、R4=Hになったタイミングでリング発振器32が停止した場合にはD9=Lとなるので、D9=Lの場合にもR3=Lがカウンタに伝わらないように3入力NANDを遮断する論理回路が設けられている。

【0087】

第3の実施形態に係る内部信号タイミング測定回路は、リング発振器32とカウンタ35の間にハザードリジェクタ46を設け、エッジ検出回路40aの検出結果がある特定の場合(カウンタへカウントアップ信号を出力するリング発振器内の遅延素子の前後一定範囲内でエッジが検出された場合)、カウンタのカウントアップ動作が起こらないようにすることで、誤カウントアップを起こらないようにすることができる。また、エッジ判定回路46を工夫することで、時間分解能が単位遅延素子1段分の高分解能を実現する。

【0088】

以下、第3の実施形態に係る内部信号タイミング測定回路は、チップ上のリング発振器32を、主要信号およびクロックで発振、停止させ、発振回数および停止時のリング発振器32内の立ち上がりエッジの位置を、誤動作を生じることなく、データ出力回路を介して出力することができ、且つ、他の実施形態に係る内部信号タイミング測定回路と同様に、主要信号のタイミングをチップごとにウェハテスト時に測定することができる。

【0089】

更に、第2の実施形態に比較して、単位遅延素子1段分の高分解能が実現できると言う利点もある。

【0090】

本発明の第3の実施形態に係る内部信号タイミング測定回路は、リング発振器に、発振回数をカウントするカウンタ、リング発振器停止時のリング発振器内の信号エッジ位置を検出するエッジ検出回路、カウンタ及びエッジ検出回路の結果を必要期間保持するレジスタ、及び、カウンタとリング発振器の間にハザードリジェクタを有することによって特徴付けられる。

【0091】

更に、本発明の第3の実施形態に係るエッジ検出回路は、連続した単位遅延素子2段のリング発振器停止時の出力がHレベルであることを検出する回路と、連続した単位遅延素子2段のリング発振器停止時の出力がLレベルであることを検出する回路によって特徴付けられる。具体的には、エッジ検出回路は、リング発振器停止時の出力がHレベルである単位遅延素子が3段以上連続した場合、または、リング発振器停止時の出力がLレベルである単位遅延素子が3段以上連続した場合には、その連続した単位遅延素子に対しエッジの伝播遅延時間がもっとも早い単位遅延素子にてエッジが検出されたと判定する処理を実施する回路を有することによっても特徴付けられる。

【産業上の利用可能性】

【0092】

本発明は、DRAM等の半導体装置だけでなく、内部信号のタイミングを高精度で測定し、設定する必要のある電子回路等に広く応用できる。

【図面の簡単な説明】

【0093】

【図1】本発明の第1の実施形態に係る半導体装置を示す回路図である。

【図2】図1に示された半導体装置内に設けられたリング発振器の発振周期を測定する場合における動作を説明する波形図である。

【図3】図1に示された半導体装置の内部信号タイミングを測定する動作を説明する波形図である。

【図4】本発明の第2の実施形態に係る内部信号タイミング回路の概略を示す回路図である。

【図5】図4の一部をより詳細に示す回路図である。

【図6】図5の回路の動作を説明する波形図である。

【図7】図4に示された内部信号タイミング回路におけるマルチプレクサとリング発振器の配置関係を示す概略図である。

【図8】図4に示された内部信号タイミング回路の出力部を示す図である。

【図9】本発明の第3の実施形態に係る内部信号タイミング回路の概略を示す回路図である。

【図10】図9に示された内部信号タイミング回路の一部をより具体的に示す回路図である。

【図11】図10に示された内部信号タイミング回路の動作を説明する波形図である。

【符号の説明】

【0094】

10 コマンドデコーダ(CMDDEC)

12 ロウ制御回路(ROWCNTL)

14 カラム制御回路(COLCNTL)

16 メモリアレイ(MEMARY)

18 ロウデコーダ(ROWDEC)

20 カラムデコーダ(COLDEC)

22 メインアンプ/バッファ回路(MA/WRT.BF.)

24 ライトFIFO(WRITEFIFO)

26 リードFIFO(READFIFO)

30 テスト制御回路

32 リング発振器

34、35 カウンタ

36 第1のマルチプレクサ

38 第2のマルチプレクサ

40、40a エッジ検出回路

42 レジスタ

44 DQ出力部

46 ハザードリジェクタ

【特許請求の範囲】

【請求項1】

第1の内部回路制御信号と該第1の内部回路制御信号から所定の遅延時間経過後に発生する第2の内部回路制御信号を生成する内部回路と、

前記第1の内部回路制御信号と前記第2の内部回路制御信号を受け、前記第1の内部回路制御信号を遅延時間測定開始信号として発生すると共に、前記第2の内部回路制御信号を遅延時間測定終了信号として発生する測定用信号発生回路と、

前記遅延時間測定開始信号と前記遅延時間測定終了信号を入力とし、遅延時間測定結果を出力する遅延時間測定回路を備えていることを特徴とする半導体装置。

【請求項2】

請求項1において、前記遅延時間測定回路は、リングオシレータとカウンタとを含み、前記リングオシレータは前記遅延時間測定開始信号を受けて発振を開始して発振出力を出力し、前記遅延時間測定終了信号に応じて発振を停止するように構成されており、前記カウンタは前記リングオシレータの前記発振出力をカウントする構成を備えていることを特徴とする半導体装置。

【請求項3】

請求項2において、前記遅延時間測定回路は、更に、前記リングオシレータの発振停止時における位相情報を出力する位相検出回路を有することを特徴とする半導体装置。

【請求項4】

請求項3において、前記位相検出回路は、前記リングオシレータの各ステージの出力電位を判定し、判定結果を出力する判定結果出力回路を備えていることを特徴とする半導体装置。

【請求項5】

請求項1において、前記遅延時間測定開始信号及び前記遅延時間測定終了信号は外部から与えられるテストモード信号に基づいて生成されることを特徴とする半導体装置。

【請求項6】

請求項1において、前記測定用信号発生回路は、外部より与えられる第1のテスト信号を前記遅延時間測定開始信号として発生すると共に、外部より与えられる第2のテスト信号を前記遅延時間測定終了信号として発生できることを特徴とする半導体装置。

【請求項7】

請求項1において、前記測定用信号発生回路は前記テストモード信号に応答して、テスト開始信号を生成するテスト制御回路と、前記第1及び第2の内部回路制御信号、及び、前記テスト開始信号とを受け、前記遅延時間測定開始信号及び前記遅延時間測定終了信号を前記遅延時間測定回路に出力するマルチプレクサを有することを特徴とする半導体装置。

【請求項8】

請求項4において、前記判定結果出力回路は、前記リングオシレータの各ステージにおける出力電位の立ち上がり又は立下りを検出する論理回路であることを特徴とする半導体装置。

【請求項9】

請求項8において、前記論理回路は、前記出力電位の立ち上がり又は立下りのいずれか一方の電位にして出力する出力回路を含むことを特徴とする半導体装置。

【請求項10】

請求項8又は9において、前記論理回路は、前記出力電位の立下り又は立下りが生じた前記リングオシレータのステージを検出する回路を有することを特徴とする半導体装置。

【請求項11】

請求項1〜10のいずれかにおいて、前記第1及び第2の内部回路制御信号は、実質上等しい遅延量を有する経路を介して前記遅延時間測定回路に供給されることを特徴とする半導体装置。

【請求項12】

請求項11において、前記経路は前記第1及び第2の内部回路制御信号に対して、等しい数のマルチプレクサを含んでいることを特徴とする半導体装置。

【請求項13】

請求項2において、更に、前記リングカウンタにおける複数ステージの状態が予め定められた状態で停止した場合に前記カウンタがカウントアップするのを防止するハザードリジェクタを有していることを特徴とする半導体装置。

【請求項14】

第1の内部回路制御信号と該第1の内部回路制御信号から所定の遅延時間経過後に発生する第2の内部回路制御信号を生成する内部回路と、

前記第1の内部回路制御信号と前記第2の内部回路制御信号を受け、前記第1の内部回路制御信号を遅延時間測定開始信号として発生すると共に、前記第2の内部回路制御信号を遅延時間測定終了信号として発生する測定用信号発生回路と、

前記遅延時間測定開始信号と前記遅延時間測定終了信号を入力とし、遅延時間測定結果を出力する遅延時間測定回路を備えていることを特徴とする内部信号タイミング回路。

【請求項15】

請求項14において、前記遅延時間測定回路は、リングオシレータとカウンタとを含み、前記リングオシレータは前記遅延時間測定開始信号を受けて発振を開始して発振出力を出力し、前記遅延時間測定終了信号に応じて発振を停止するように構成されており、前記カウンタは前記リングオシレータの前記発振出力をカウントする構成を備えていることを特徴とする内部信号タイミング回路。

【請求項16】

請求項15において、前記遅延時間測定回路は、更に、前記リングオシレータの発振停止時における位相情報を出力する位相検出回路を有することを特徴とする内部信号タイミング回路。

【請求項17】

請求項16において、前記位相検出回路は、前記リングオシレータの各ステージの出力電位を判定し、判定結果を出力する回路を備えていることを特徴とする内部信号タイミング回路。

【請求項18】

請求項14〜17のいずれかにおいて、前記遅延時間測定開始信号及び前記遅延時間測定終了信号は外部から与えられるテスト信号に基づいて生成されることを特徴とする内部信号タイミング回路。

【請求項19】

電子回路を実際に動作させるために使用される複数の信号から第1及び第2の信号を選択し、前記第1の信号及び第2の信号を遅延時間測定開始信号及び遅延時間測定終了信号に変換して、遅延時間測定回路に供給し、前記遅延時間測定回路では、前記遅延時間測定開始信号及び前記遅延時間測定終了信号との間の遅延時間を測定し、測定結果を出力することを特徴とする遅延時間測定方法。

【請求項20】

請求項19において、前記遅延時間測定回路はリング発振器及びカウンタにより構成され、前記遅延時間の測定の前に、前記リング発振器の発振周期を測定することを特徴とする遅延時間測定方法。

【請求項21】

請求項20において、前記リング発振器の発振周期は予め定められた時間間隔で発生されるテスト信号を用いて行われることを特徴とする遅延時間測定方法。

【請求項22】

請求項21において、前記リング発振器の発振周期の測定結果に基づいて、前記遅延時間が演算されることを特徴とする遅延時間測定方法。

【請求項1】

第1の内部回路制御信号と該第1の内部回路制御信号から所定の遅延時間経過後に発生する第2の内部回路制御信号を生成する内部回路と、

前記第1の内部回路制御信号と前記第2の内部回路制御信号を受け、前記第1の内部回路制御信号を遅延時間測定開始信号として発生すると共に、前記第2の内部回路制御信号を遅延時間測定終了信号として発生する測定用信号発生回路と、

前記遅延時間測定開始信号と前記遅延時間測定終了信号を入力とし、遅延時間測定結果を出力する遅延時間測定回路を備えていることを特徴とする半導体装置。

【請求項2】

請求項1において、前記遅延時間測定回路は、リングオシレータとカウンタとを含み、前記リングオシレータは前記遅延時間測定開始信号を受けて発振を開始して発振出力を出力し、前記遅延時間測定終了信号に応じて発振を停止するように構成されており、前記カウンタは前記リングオシレータの前記発振出力をカウントする構成を備えていることを特徴とする半導体装置。

【請求項3】

請求項2において、前記遅延時間測定回路は、更に、前記リングオシレータの発振停止時における位相情報を出力する位相検出回路を有することを特徴とする半導体装置。

【請求項4】

請求項3において、前記位相検出回路は、前記リングオシレータの各ステージの出力電位を判定し、判定結果を出力する判定結果出力回路を備えていることを特徴とする半導体装置。

【請求項5】

請求項1において、前記遅延時間測定開始信号及び前記遅延時間測定終了信号は外部から与えられるテストモード信号に基づいて生成されることを特徴とする半導体装置。

【請求項6】

請求項1において、前記測定用信号発生回路は、外部より与えられる第1のテスト信号を前記遅延時間測定開始信号として発生すると共に、外部より与えられる第2のテスト信号を前記遅延時間測定終了信号として発生できることを特徴とする半導体装置。

【請求項7】

請求項1において、前記測定用信号発生回路は前記テストモード信号に応答して、テスト開始信号を生成するテスト制御回路と、前記第1及び第2の内部回路制御信号、及び、前記テスト開始信号とを受け、前記遅延時間測定開始信号及び前記遅延時間測定終了信号を前記遅延時間測定回路に出力するマルチプレクサを有することを特徴とする半導体装置。

【請求項8】

請求項4において、前記判定結果出力回路は、前記リングオシレータの各ステージにおける出力電位の立ち上がり又は立下りを検出する論理回路であることを特徴とする半導体装置。

【請求項9】

請求項8において、前記論理回路は、前記出力電位の立ち上がり又は立下りのいずれか一方の電位にして出力する出力回路を含むことを特徴とする半導体装置。

【請求項10】

請求項8又は9において、前記論理回路は、前記出力電位の立下り又は立下りが生じた前記リングオシレータのステージを検出する回路を有することを特徴とする半導体装置。

【請求項11】

請求項1〜10のいずれかにおいて、前記第1及び第2の内部回路制御信号は、実質上等しい遅延量を有する経路を介して前記遅延時間測定回路に供給されることを特徴とする半導体装置。

【請求項12】

請求項11において、前記経路は前記第1及び第2の内部回路制御信号に対して、等しい数のマルチプレクサを含んでいることを特徴とする半導体装置。

【請求項13】

請求項2において、更に、前記リングカウンタにおける複数ステージの状態が予め定められた状態で停止した場合に前記カウンタがカウントアップするのを防止するハザードリジェクタを有していることを特徴とする半導体装置。

【請求項14】

第1の内部回路制御信号と該第1の内部回路制御信号から所定の遅延時間経過後に発生する第2の内部回路制御信号を生成する内部回路と、

前記第1の内部回路制御信号と前記第2の内部回路制御信号を受け、前記第1の内部回路制御信号を遅延時間測定開始信号として発生すると共に、前記第2の内部回路制御信号を遅延時間測定終了信号として発生する測定用信号発生回路と、

前記遅延時間測定開始信号と前記遅延時間測定終了信号を入力とし、遅延時間測定結果を出力する遅延時間測定回路を備えていることを特徴とする内部信号タイミング回路。

【請求項15】

請求項14において、前記遅延時間測定回路は、リングオシレータとカウンタとを含み、前記リングオシレータは前記遅延時間測定開始信号を受けて発振を開始して発振出力を出力し、前記遅延時間測定終了信号に応じて発振を停止するように構成されており、前記カウンタは前記リングオシレータの前記発振出力をカウントする構成を備えていることを特徴とする内部信号タイミング回路。

【請求項16】

請求項15において、前記遅延時間測定回路は、更に、前記リングオシレータの発振停止時における位相情報を出力する位相検出回路を有することを特徴とする内部信号タイミング回路。

【請求項17】

請求項16において、前記位相検出回路は、前記リングオシレータの各ステージの出力電位を判定し、判定結果を出力する回路を備えていることを特徴とする内部信号タイミング回路。

【請求項18】

請求項14〜17のいずれかにおいて、前記遅延時間測定開始信号及び前記遅延時間測定終了信号は外部から与えられるテスト信号に基づいて生成されることを特徴とする内部信号タイミング回路。

【請求項19】

電子回路を実際に動作させるために使用される複数の信号から第1及び第2の信号を選択し、前記第1の信号及び第2の信号を遅延時間測定開始信号及び遅延時間測定終了信号に変換して、遅延時間測定回路に供給し、前記遅延時間測定回路では、前記遅延時間測定開始信号及び前記遅延時間測定終了信号との間の遅延時間を測定し、測定結果を出力することを特徴とする遅延時間測定方法。

【請求項20】

請求項19において、前記遅延時間測定回路はリング発振器及びカウンタにより構成され、前記遅延時間の測定の前に、前記リング発振器の発振周期を測定することを特徴とする遅延時間測定方法。

【請求項21】

請求項20において、前記リング発振器の発振周期は予め定められた時間間隔で発生されるテスト信号を用いて行われることを特徴とする遅延時間測定方法。

【請求項22】

請求項21において、前記リング発振器の発振周期の測定結果に基づいて、前記遅延時間が演算されることを特徴とする遅延時間測定方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−109154(P2010−109154A)

【公開日】平成22年5月13日(2010.5.13)

【国際特許分類】

【出願番号】特願2008−279774(P2008−279774)

【出願日】平成20年10月30日(2008.10.30)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成22年5月13日(2010.5.13)

【国際特許分類】

【出願日】平成20年10月30日(2008.10.30)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]