半導体装置、半導体素子、及び半導体装置の製造方法

【課題】はんだによる短絡不良を低減すること。

【解決手段】半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。電極端子13の基端部(金属端子部15の基端部16及びバリア層14)は電極パッド11に接続されている。電極端子13(金属端子部15)の先端部17は略半円柱状に形成されている。この略半円柱状の先端部17は、先端面の弧部分が半導体素子10の外側を向くように形成されている。配線基板20の接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。電極端子13は接続パッド22にはんだ30により電気的に接続される。

【解決手段】半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。電極端子13の基端部(金属端子部15の基端部16及びバリア層14)は電極パッド11に接続されている。電極端子13(金属端子部15)の先端部17は略半円柱状に形成されている。この略半円柱状の先端部17は、先端面の弧部分が半導体素子10の外側を向くように形成されている。配線基板20の接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。電極端子13は接続パッド22にはんだ30により電気的に接続される。

【発明の詳細な説明】

【技術分野】

【0001】

半導体装置、半導体素子、及び半導体装置の製造方法に関する。

【背景技術】

【0002】

小型化及び高機能化された電子機器に組み込まれる半導体素子は、小型化、高密度化、多端子化されている。このため、その半導体素子は、高い信頼性が要求されている。この半導体素子は、一般に配線基板に接続される端子を有している。この端子は、半導体素子の小型化及び高密度化に要求に従って、小型化及び高密度化されている。

【0003】

半導体素子の実装方法としてはフリップチップ実装が多く用いられている(例えば、特許文献1参照)。このフリップチップ実装は、半導体素子に突起状の電極端子(バンプ)を形成しておき、配線基板のチップ実装面側の保護膜(ソルダレジスト層)から露出させたパッドに、はんだ等の導電性材料を用いて上記バンプを直接電気的に接合させる方法である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平11−186322号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところが、近年の小型化及び高精度化された半導体素子の場合には、バンプピッチの狭小化に伴ってパッドピッチが狭くなるため、隣り合うはんだが互いに接続される、いわゆるはんだブリッジなどの不良が発生する。

【課題を解決するための手段】

【0006】

本発明の一観点によれば、複数の電極パッドが配列形成された半導体素子と、各々の前記電極パッドに対応して配列された複数の接続パッドを有する配線基板と、前記電極パッドに接続された基端部と、前記基端部から突出するように形成された誘導部とを有し、柱状に形成された複数の電極端子と、前記誘導部と前記接続パッドとを互いに電気的に接続するはんだを有し、前記誘導部は、平面視断面積が前記基端部の平面視断面積よりも小さく、外周の一部が前記基端部の外周の一部と面一な外周を有し、前記基端部の外周と面一な外周側に向って前記はんだを誘導するように形成される。

【発明の効果】

【0007】

本発明の一観点によれば、はんだによる短絡不良を低減することができる。

【図面の簡単な説明】

【0008】

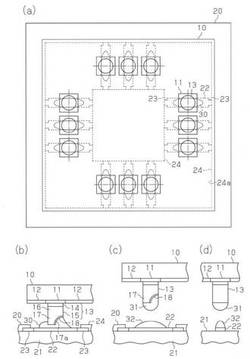

【図1】(a)は、半導体装置の概略平面図、(b)〜(d)は、半導体素子と配線基板の接続を示す説明図である。

【図2】(a)(b)は、半導体素子と配線基板の接続を示す説明図である。

【図3】(a)(b)は、電極端子の製造工程を示す説明図である。

【図4】(a)(b)は、電極端子の製造工程を示す説明図である。

【図5】(a)(b)は、電極端子の製造工程を示す説明図である。

【図6】(a)(b)は、電極端子の製造工程を示す説明図である。

【図7】(a)〜(c)は、別の電極端子の説明図である。

【図8】(a)〜(c)は、別の電極端子の説明図である。

【図9】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図10】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図11】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図12】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図13】(a)〜(c)は、別の電極端子の説明図である。

【図14】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図15】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図16】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図17】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図18】(a)〜(c)は、別の電極端子の説明図である。

【図19】(a)〜(c)は、別の電極端子の説明図である。

【図20】(a)(b)は、電極端子の製造工程を示す説明図である。

【図21】(a)〜(d)は、はんだの移動方向を示す説明図である。

【図22】(a)(b)は、はんだの移動方向を示す説明図である。

【発明を実施するための形態】

【0009】

以下、一実施形態を図1〜図6に従って説明する。

図1(a)に示すように、半導体素子10は、配線基板20の上面(図1(b)参照)に実装されている。

【0010】

図1(a)に示すように、半導体素子10は、一主面(例えば、回路素子が形成された面:図1(b)において下面)に複数の電極パッド11が形成されている。これら複数の電極パッド11は、ペリフェラル配置、つまり、半導体素子10の外周に沿って環状に配置されている。各電極パッド11は、例えば平面視正方形状に形成されている。各電極パッド11の材質は、例えばアルミニウムである。半導体素子10の一主面には保護膜(パッシベーション膜)12が形成されている。保護膜12には、シリコン酸化膜、シリコン窒化膜などが用いられる。

【0011】

図1(b)に示すように、各電極パッド11には、柱状の電極端子(ピラー)13がそれぞれ立設されている。図1(a)に示すように、各電極端子13は、例えば略円柱状に形成されている。電極端子13と電極パッド11との間の接続強度を確保するため、電極端子13の外径は、電極パッド11の外形に対し、可能な限り大きいほうが好ましい。例えば、電極パッド11は、一辺が50ミクロン(μm)の正方形状に形成され、電極端子13の直径は40ミクロン(μm)である。なお、図1(a)において、電極パッド11及び電極端子13を、後述する配線基板20の部材との区別を容易にするために実線で示している。

【0012】

図1(b)に示すように、電極端子13は、電極パッド11の上面(図では下面)に形成されたバリア層14(UBM:Under Barrier Metal)と、バリア層14の上面(図では下面)から電極パッド11と垂直方向に沿って延びる金属端子部15を有している。バリア層14は、例えばチタン(Ti)(又はチタンとタングステン(W)の合金)/銅(Cu)である。バリア層14は、例えばめっき法により形成される。金属端子部15は、例えば銅である。金属端子部15は、例えばめっき法により形成される。

【0013】

図1(b)に示すように、金属端子部15の基端部16は円柱状に形成され、バリア層14に接続されている。金属端子部15の先端部17は略半円形状に形成されている。従って、この先端部17は、基端部16の外周の一部と面一な外周を有している。換言すれば、電極端子13は、基端部と先端面を含む誘導部とからなり、誘導部は、基端部と面一な外周を有する円柱に、その外周の一部を残すような切り欠きが形成された形状である。

【0014】

この略半円形状の先端部17は、先端面の弧部分、即ち基端部16の外周と面一な外周が半導体素子10の外側を向くように形成されている。そして、先端部17において半導体素子10の内側の側面17aは、側面視円弧状に形成されている。この側面17aには、はんだ層18が形成されている。このはんだ層18は、例えばはんだめっき法により形成される。

【0015】

配線基板20は、板状に形成された基板本体21を含む。基板本体21は、例えばエポキシ系の絶縁樹脂により形成されている。基板本体21の上面(チップ搭載面:図1(b)において上面)には、複数の接続パッド22が形成されている。接続パッド22の材料は、例えば銅である。図1(a)に示すように、複数の接続パッド22は、接続対象である半導体素子10の電極パッド11に対応して、電極パッド11の配列方向に沿って矩形環状に配列されている。

【0016】

各接続パッド22は、半導体素子10の電極パッド11の配列方向と直交する方向に沿って延びる平面視長方形状に形成されている。各接続パッド22の幅(接続パッド22の配列方向の長さであって、半導体素子10の辺と平行な方向における長さ)は、電極端子13の大きさ(直径)に対応して設定されている。例えば、接続パッド22の幅は、22ミクロン(μm)に設定されている。なお、接続パッド22の長さ(接続パッド22の配列方向と直交する方向の長さ)は、例えば100ミクロン(μm)である。

【0017】

各接続パッド22は、基板本体21の上面に形成された配線23と接続されている。なお、図示しないが、配線基板20は、半導体素子10を他の素子と接続するための配線やビアを有している。なお、配線基板20を、半導体素子10と他の配線基板とを接続するための基板(パッケージの基板)としてもよい。

【0018】

図1(b)に示すように、基板本体21の上面には、保護膜(ソルダレジスト層)24が形成されている。保護膜24の材料は、例えばエポキシ系の絶縁性樹脂である。図1(a)に示すように、保護膜24には、半導体素子10の外形形状に対応する矩形枠状の開口部が形成され、その開口部から接続パッド22が露出している。

【0019】

図1(a)に示すように、各接続パッド22の長手方向中心は、半導体素子10の電極パッド11の中心と一致するように形成されている。そして、電極端子13は、接続パッド22の中心に形成されている。そして、電極端子13の先端部17は、接続パッド22に応じて、例えば、長手方向両側のうちの何れか一方、例えば、半導体素子10の外側に形成され、側面17aは半導体素子10の内側を向いている。

【0020】

図1(b)に示すように、半導体素子10の電極端子13と配線基板20の接続パッド22は、はんだ30により互いに接続されている。はんだ30は、例えばスズ(Sn)と銀(Ag)の合金である。なお、はんだ30に、スズと亜鉛(Zn)の合金、等を用いることもできる。各接続パッド22上のはんだ30は、接続パッド22と電極端子13の相対的な位置関係に応じた形状に形成される。

【0021】

次に、上記の半導体素子10及び配線基板20における作用を説明する。

図1(c)及び図1(d)に示すように、電極端子13の先端部17には、はんだ31が形成される。このはんだ31は、先端部17の先端面と側面17aとに披着し、図において下方に向って略半球状に形成される。はんだ31は、例えば、半田リフロー処理により形成される。

【0022】

一方、配線基板20の接続パッド22の上面には、ドーム状のはんだ32が形成される。はんだ32は、中央部分が膨出するように形成される。このはんだ32は、接続パッド22の上面に形成されたはんだ32の母材を溶融した際、表面張力により、溶融したはんだが接続パッド22の上面に集まる。これにより、頂点が接続パッド22の中心と略一致するはんだ32が形成される。また、はんだ32の形成に、例えば、スーパージャフィット(登録商標)法を用いることができる。

【0023】

なお、電極端子13の先端と接続パッド22の上面には、電極端子13と接続パッド22を互いに接続するのに必要なはんだ量よりも多い量のはんだが形成される。つまり、電極端子13に形成されたはんだ31の量と接続パッド22上面に披着したはんだ32の量の合計は、電極端子13と接続パッド22を互いに接続するのに必要なはんだ量よりも多い。

【0024】

次に、半導体素子10と配線基板20とを相対的に位置合せする。そして、半導体素子10を配線基板20に対して所定の圧力で押し付け、半田リフロー処理を行う。この半田リフロー処理により、電極端子13先端のはんだ31と、接続パッド22上面のはんだ32は溶融する。このとき、はんだ32の頂点と、電極端子13の先端部17の位置がずれているため、接続パッド22上面のはんだ32は、電極端子13を押し下げる力により、先端部17が形成された方向に応じて移動する。

【0025】

図1(a)に示すように、接続パッド22は、配列方向と直交する方向に沿って延びる長方形状に形成されている。そして、電極端子13の先端部17は、接続パッド22の中心から、その接続パッド22が延びる方向に沿って、半導体素子10の各辺側(外側)に形成されている。従って、接続パッド22上面のはんだ32は、接続パッド22が延びる方向に沿って、半導体素子10の外側に向って移動する。

【0026】

そして、はんだ31とはんだ32を硬化させることにより、図1(b)に示すはんだ30が形成される。このはんだ30は、接続パッド22の配列方向の突出する部分が少ない。これは、電極端子13の先端部17が、溶融したはんだ31,32を、半導体素子10の外側、即ち基端部16の外周と面一な外周側に向って誘導するためである。これにより、隣り合う2つの接続パッド22間におけるはんだによる短絡不良の発生を低減する。

【0027】

なお、電極端子の先端部が円柱状に形成され、その先端面が接続パッド22上面と略平行な平坦面に形成された場合、溶融したはんだ31,32は、電極端子の先端面及び接続パッド22の面に沿って移動するため、接続パッド22の配列方向の突出量が多くなる。この配列方向に突出したはんだは、隣り合う2つの接続パッド22で相互に接続され、はんだによる短絡不良が発生する。

【0028】

ところで、1つの半導体素子10に形成された複数の電極端子13の長さは、製造工程においてばらつく場合がある。例えば、図2(a)に示すように、1つの半導体素子10に形成された電極端子13aの長さLaに対し、同じ半導体素子10に形成された電極端子13bの長さLbがΔLだけ短い場合がある。各電極端子13a,13bには、はんだ31a,31bがそれぞれ形成される。これらのはんだ31a,31bの量は、同様に形成されるため、互いに等しい。

【0029】

電極端子13aに対応する接続パッド22a上面には、はんだ32aが形成される。同様に、電極端子13bに対応する接続パッド22b上面にははんだ32bが形成される。そして、図2(b)に示すように、電極端子13aと接続パッド22aは、はんだ30aにより、電気的に互いに接続される。この場合、電極端子13aにより逃げるはんだ32aの量に対し、電極端子13bにより逃げるはんだ32bの量が少なくなる。しかし、これらはんだ31b、32bを合計したはんだ量は、電極端子13a及び接続パッド22のはんだ31a,31bと同量である。従って、電極端子13bと接続パッド22bとの間に、はんだ31b,32bが残存する。このため、図2(b)に示すように、電極端子13bと接続パッド22bは、はんだ30bにより、電気的に互いに接続される。

【0030】

次に、上記の電極端子13の製造方法を説明する。

先ず、図3(a)及び図3(b)に示すように、電極パッド11及び保護膜12が形成された半導体素子10上にレジスト層41を形成し、レジスト層41に開口部41aを形成する。レジスト層41の膜厚は、電極パッド11の上面から電極端子13の先端面までの高さ(図1(b)参照)に等しい。開口部41aは、電極パッド11上に形成される電極端子13の形成領域に対応する部分の電極パッド11の上面を露出するように形成される。レジスト層41の材料としては、感光性のドライフィルムや液状のフォトレジスト(ノボラック系樹脂、エポキシ系樹脂等の液状レジスト)を用いることができる。

【0031】

次いで、図4(a)及び図4(b)に示すように、レジスト層41をめっきマスクとして、めっき法により、電極パッド11上に円柱状の電極部42を形成する。具体的には、レジスト層41の開口部41aから露出された電極パッド11の上面に、図1(b)に示すバリア層14を形成する。次いで、バリア層14上に柱状の金属端子部15を形成する。

【0032】

次いで、図5(a)及び図5(b)に示すように、レジスト層41上に、開口部43aを有するレジスト層43を形成する。レジスト層43は、図1(b)に示す先端部17を覆うように形成される。従って、レジスト層43(開口部43a)の形状により、先端部17の大きさ、形状、形成方向を適宜設定することができる。

【0033】

次いで、図6(a)及び図6(b)に示すように、レジスト層43の開口部43aから電極部42に対して例えばエッチング処理を行い、湾曲した側面17aを形成する。従って、エッチング処理の条件(処理時間,エッチング液の濃度,等)により、側面17aの大きさ、つまり先端部17の長さを適宜設定することができる。

【0034】

次いで、レジスト層43の開口部43aから側面17aに対して、例えばはんだめっき法により、はんだ層18を形成する。次いで、レジスト層41,43を、例えばアッシングにより除去する。これにより、先端部17を有する電極端子13が形成される。

【0035】

なお、電極端子13は、ウェハ状態の半導体素子10に対して形成される。即ち、複数の半導体素子10を形成するためのウェハに対し、上記図3〜図6に示す処理が実施される。これにより、複数の半導体素子10に対して、電極パッド11上に電極端子13が一括して形成される。このように電極端子13を形成することにより、金(Au)等を用いたバンプを形成する工程と比べ、製造に要する時間を短縮することができる。金などのバンプは、個々に形成する必要があるため、時間を要する。また、マスクを用いて電極端子13を形成することにより、電極端子13のピッチ(隣り合う2つの電極端子13の中心間の距離)を、バンプを個々に形成する場合と比べ、短くすることができる。

【0036】

以上記述したように、本実施形態によれば、以下の効果を奏する。

(1)半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。電極端子13の基端部(金属端子部15の基端部16及びバリア層14)は電極パッド11に接続されている。電極端子13(金属端子部15)の先端部17は略半円柱状に形成されている。この略半円柱状の先端部17は、先端面の弧部分が半導体素子10の外側を向くように形成されている。

【0037】

半導体素子10が実装される配線基板20には、半導体素子10の電極パッド11と対応する複数の接続パッド22が形成されている。各接続パッド22の中心は、半導体素子10の電極パッド11の中心と略一致する。また、各接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。

【0038】

各接続パッド22の上面には、はんだ32が披着されている。電極端子13の先端部17は、その形成方向、詳しくは基端部16の外周と面一な外周側、即ち半導体素子10の外側に向って溶融したはんだ31,32を誘導する。これにより、接続パッド22の配列方向、即ち、隣り合う接続パッド22の方向にはみだすはんだ30の量が少なくなる。このため、はんだ30により隣り合う接続パッド22が互いに電気的に接続される短絡不良を低減することができる。

【0039】

(2)各電極端子13の先端面にははんだ31が形成される。この電極端子31に形成されたはんだ31と、接続パッド22上面に披着したはんだ32とが半田リフロー処理により互いに融合してはんだ30が形成される。このはんだ30の量、つまり電極端子13に形成されたはんだ31の量と接続パッド22上面に披着したはんだ32の量の合計は、電極端子13と接続パッド22を互いに接続するのに必要なはんだ量よりも多い。

【0040】

めっき法により形成される電極端子13は、長さにばらつきが生じる。従って、電極端子13aよりも短い電極端子13bの場合、電極端子13bと接続パッド22bの間に、はんだ31b,32bが残存し、これらによるはんだ30bにより、電極端子13bと接続パッド22bが電気的に接続される。このように、はんだ31a,31b,32a,32bの量を多くすることにより、長さにばらつきが生じる電極端子13a,13bは、ぞれぞれに対応する接続パッド22a,22bと接続される。従って、ばらつきによる接続不良を低減することができる。

【0041】

(3)先端部17の側面17aにははんだ層18が形成されている。このはんだ層18は、溶融したはんだ31,32を側面17aに披着させるように働く。従って、余剰なはんだを側面17aに積極的に披着させることで、はんだのはみだしを低減することができる。

【0042】

尚、上記実施形態は、以下の態様で実施してもよい。

・上記実施形態では、略円柱状の電極端子13(図1(a)参照)を用いたが、電極端子の形状を適宜変更してもよい。例えば、図7(a)に示すように、略四角柱状の電極端子51を用いるようにしてもよい。この電極端子51は、四角柱状に形成された基端部52に対し、先端部53の側面53aが湾曲して形成されている。

【0043】

この電極端子51は、例えば、図3(a)に示すレジスト層41の開口部41aを、矩形状とすることにより得られる。この電極端子51においても、図7(b)に白抜きの矢印にて示すように、はんだを誘導することができ、短絡を防止することができる。

【0044】

なお、先端部側面の一部を残すようにエッチング処理して上記の側面53a等を形成する際に、エッチング処理の条件等によって、図7(c)に示すように、レジスト膜(図6(b)参照)に沿ってエッチング残りが生じる場合がある。しかし、このようにエッチング残りが生じた電極端子51aであっても、上記実施形態と同様に、はんだのはみだしを低減することができる。

【0045】

・上記実施形態では、先端部17に湾曲する側面17aを形成したが、側面17aの形状を適宜変更してもよい。例えば、図8(a)に示すように、電極端子61aは、円柱状の基端部62aに対し、先端部63aに対して側面64aが平坦に形成されている。同様に、図8(b)に示すように、電極端子61bは、四角柱状の基端部62bに対し、先端部63bに対して側面64bが平坦に形成されている。これらの電極端子61a,61bにおいても、上記実施形態と同様に、図8(c)に白抜きの矢印にて示すように、はんだを誘導することができ、短絡を防止することができる。

【0046】

なお、図8(a)(b)に示す電極端子61a,61bは、例えば、図6に示す処理において、開口部43aからブラスト処理を行うことにより得られる。

また、図9〜図12に示す各工程により電極端子61aを得ることもできる。

【0047】

即ち、図9(a)及び図9(b)に示すように、電極パッド11及び保護膜12が形成された半導体素子10上にレジスト層71を形成し、レジスト層71に開口部71aを形成する。レジスト層71の膜厚は、電極端子61bの基端部62bの高さ(図8(b)参照)に等しい。開口部71aは、電極パッド11上に形成される電極端子13の形成領域に対応する部分の電極パッド11の上面を露出するように形成される。レジスト層71の材料としては、感光性のドライフィルムや液状のフォトレジスト(ノボラック系樹脂、エポキシ系樹脂等の液状レジスト)を用いることができる。

【0048】

次いで、図10(a)及び図10(b)に示すように、レジスト層71をめっきマスクとして、めっき法により、円柱状の基端部62bを形成する。

次いで、図11(a)及び図11(b)に示すように、レジスト層71上に、開口部72aを有するレジスト層72を形成する。レジスト層72は、図8(b)に示す先端部63bに対応する形状に形成される。従って、レジスト層72(開口部72a)の形状により、先端部63bの大きさ、形状、形成方向を適宜設定することができる。

【0049】

次いで、図12(a)及び図12(b)に示すように、レジスト層72をめっきマスクとして、めっき法により、半円柱状の先端部63bを形成する。

そして、レジスト層71,72を、例えばアッシングにより除去する。これにより、平坦な側面64bの先端部63bを有する電極端子61bが形成される。

【0050】

図9〜図12に示す工程において、レジスト層71,72に形成する開口部71a,72aの形状を矩形状とすることにより、図8(b)に示す電極端子61bが得られる。そして、開口部71a,72aの形状を適宜変更することにより、略半円形状、略矩形形状、略扇形形状等、様々な形状の誘導部を有する電極端子を得ることができる。

【0051】

・上記形態では、溶融したはんだを1つの方向に誘導する電極端子としたが、複数の方向にはんだを誘導するように電極端子を形成してもよい。

例えば、図13(a)に示すように、電極端子81aは略円柱状に形成されている。電極端子81aの先端面中央は、側面視円弧状の底面82aに形成され、この底面82aは、所定方向に沿って延びる溝83aを形成する。この溝83aの幅、即ち両側における先端部84a,85aの間隔は、例えば、図1(a)に示す接続パッド22の幅以上に設定されている。そして、電極端子81aは、溝83aが延びる方向と、接続パッド22が延びる方向が一致するように、電極パッド11上に形成される。そして、電極端子81aの溝83a及び先端部84a,85aにははんだが披着される。

【0052】

この電極端子81aを有する半導体素子を配線基板20に実装する際、電極端子81aは、先端部84a,85aの間に形成された溝83aにより、はんだをその溝83aが延びる方向に誘導する。即ち、1つの電極端子81aは、2つの誘導部(先端部84a,85a)を有している。そして、電極端子81aは、はんだの誘導方向と、接続パッド22の長手方向と一致するように形成される。これにより、接続パッド22の幅方向、つまり接続パッド22の配列方向へのはんだのはみ出しを少なくすることで、余剰なはんだによる短絡を防止することができる。

【0053】

なお、図13(b)に示すように、矩形柱状の電極端子81bを用いるようにしてもよい。この電極端子81bは、先端の底面82bにより形成された溝83bを有している。また、図13(c)に示すように、矩形柱状の電極端子81cは、2つの斜面82cにより形成された溝83cを有している。また、2つの側面と1つの底面により形成される矩形状の溝(コ字状の溝)を形成してもよい。

【0054】

図13(a)に示す電極端子81aの製造工程の一例を図14〜図17に従って説明する。

先ず、図14(a)及び図14(b)に示すように、電極パッド11及び保護膜12が形成された半導体素子10上にレジスト層91を形成し、レジスト層91に開口部91aを形成する。開口部91aは、電極パッド11上に形成される電極端子81aの形成領域に対応する部分の電極パッド11の上面を露出するように形成される。レジスト層91の材料としては、感光性のドライフィルムや液状のフォトレジスト(ノボラック系樹脂、エポキシ系樹脂等の液状レジスト)を用いることができる。

【0055】

次いで、図15(a)及び図15(b)に示すように、レジスト層91をめっきマスクとして、めっき法により、電極パッド11上に円柱状の電極部92を形成する。

次いで、図16(a)及び図16(b)に示すように、レジスト層91上に、開口部93aを有するレジスト層93を形成する。レジスト層93は、図13(a)に示す先端部84a,85aを覆うように形成される。従って、レジスト層93(開口部93a)の形状により、先端部84a,85aの大きさ、形状、図13(a)に示す溝83aの形成方向を適宜設定することができる。

【0056】

次いで、図17(a)及び図17(b)に示すように、レジスト層93の開口部93aから電極部92に対して例えばエッチング処理を行い、湾曲した底面82aを形成する。従って、エッチング処理の時間により、底面82aの深さを適宜設定することができる。

【0057】

次いで、レジスト層93の開口部93aから底面82aに対して、例えばはんだめっき法により、はんだ層を形成する。次いで、レジスト層91,93を、例えばアッシングにより除去する。これにより、図13(a)に示す電極端子81aが得られる。

【0058】

なお、レジスト層91に形成する開口部91aの形状を矩形状とすることにより、図13(b)に示す電極端子81bが得られる。また、図17で示したエッチング処理に替えてブラスト処理等の他の処理を行うようにしてもよく、実施する処理に応じた形状の溝を電極端子の先端に形成することができる。

【0059】

・上記各形態に対し、先端部がデーパ状に形成された電極端子を用いるようにしてもよい。

例えば、図18(a)に示すように、電極端子101aは、円柱状に形成され、先端面102aが所定の方向に傾いて形成されている。また、図18(b)に示すように、電極端子101bは矩形柱状に形成され、先端面102bが所定の方向に傾いて形成されている。このように形成された電極端子101a,101bは、図18(c)に示すように、先端面102a,102bの傾斜方向にはんだを誘導する。

【0060】

また、先端部がテーパ状に形成されるとともに先端を平坦に形成した電極端子を用いるようにしてもよい。

例えば、図19(a)に示すように、電極端子111aは、略円柱状に形成され、先端部112aを斜めに切り欠いて傾斜面113aが形成されている。同様に、図19(a)に示すように、電極端子111bは、矩形柱状に形成され、先端部112bを斜めに切り欠いて傾斜面113bが形成されている。このように形成された電極端子111a,111bは、図19(c)に示すように、先端部112a,112bの方向にはんだを誘導する。

【0061】

図18及び図19に示す電極端子は、例えば、図20に示すように、形成される。

即ち、図20(a)に示すように、半導体素子に柱状の金属端子121を形成し、その金属端子121の先端部が突出するようにレジスト層122を形成する。次いで、金属端子121を形成した半導体素子を保持するステージを、図20(b)に示すように傾け、研磨処理のためのヘッド123(例えば、化学的機械的研磨(CMP:Chemical Mechanical Polishing)に用いるヘッド)を用いて金属端子121を研削して斜面を形成する。ステージとヘッド123の相対的な傾きにより、斜面の角度が設定される。レジスト層122がストッパとして機能し、レジスト層122から金属端子121の突出量により、斜面の大きさが設定される。なお、研削時間を制御するようにしてもよい。

【0062】

・上記各形態において、はんだを誘導する方向を適宜変更してもよい。

例えば、図13に示す電極端子81aを用いた場合、図21(a)に白抜きの矢印で示すように、電極端子81aの両側であって、例えば接続パッド22が延びる方向に沿ってはんだを誘導することができる。このため、隣り合う接続パッド22の方向にはみ出すはんだの量を低減し、はんだによる短絡を防止することができる。

【0063】

また、1つの方向にはんだを誘導する電極端子(図1(b)に示す電極端子13)を用い、図21(b)に白抜きの矢印で示すように、隣り合う接続パッド22において互いに逆方向にはんだを誘導するようにしてもよい。この場合、誘導されたはんだが接続パッド22の幅方向にはみ出しても、隣り合う接続パッド22におけるはんだは、電極端子13に対して逆方向に誘導されている。このため、隣り合う接続パッド22におけるはんだが互いに接触することはないため、はんだによる短絡を防止することができる。

【0064】

また、図21(c)に白抜きの矢印で示すように、接続パッド22の配列方向に沿って、各電極端子13において同じ方向にはんだを誘導するようにしてもよい。

また、図21(d)に示すように、半導体素子10aの周辺に沿って、端部から第1の距離に配置される電極端子13に対応する接続パッド22aと、端部から第2の距離に配置される電極端子13に対応する接続パッド22bが交互に配列された、所謂千鳥配置の場合、隣り合う接続パッド22a,22bの中心を通る直線に沿って1つの方向にはんだを誘導するように電極端子を形成してもよい。なお、このように配置された接続パッド22a,22bにおいて、図21(b)に示すように、互いに逆方向にはんだを誘導するように電極端子を形成するようにしてもよい。

【0065】

・上記各形態は、ペリフェラル配置の半導体素子と、それを実装する配線基板について説明したが、上記各電極端子を、他の配置の半導体素子に適用してもよい。

例えば、電極パッド11がマトリックス配置された半導体素子を配線基板に実装する場合に適用する。この場合、図22(a)に白抜きの矢印で示すように、半導体素子10cの各電極パッド11に形成された電極端子13において、1つの方向(例えば、電極パッド11の1つの対角線に沿った方向)にはんだを誘導するようにしてもよい。また、図22(b)に示すように、隣り合う電極パッド11において、互いに逆方向にはんだを誘導するように電極端子13を形成してもよい。

【0066】

・上記各形態では、電極端子を略円柱状,略四角柱状としたが、5角形以上の多角形柱状としてもよい。

【符号の説明】

【0067】

10 半導体素子

11 電極パッド

13 電極端子

17 先端部(誘導部)

20 配線基板

22 接続パッド

30 はんだ

【技術分野】

【0001】

半導体装置、半導体素子、及び半導体装置の製造方法に関する。

【背景技術】

【0002】

小型化及び高機能化された電子機器に組み込まれる半導体素子は、小型化、高密度化、多端子化されている。このため、その半導体素子は、高い信頼性が要求されている。この半導体素子は、一般に配線基板に接続される端子を有している。この端子は、半導体素子の小型化及び高密度化に要求に従って、小型化及び高密度化されている。

【0003】

半導体素子の実装方法としてはフリップチップ実装が多く用いられている(例えば、特許文献1参照)。このフリップチップ実装は、半導体素子に突起状の電極端子(バンプ)を形成しておき、配線基板のチップ実装面側の保護膜(ソルダレジスト層)から露出させたパッドに、はんだ等の導電性材料を用いて上記バンプを直接電気的に接合させる方法である。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平11−186322号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところが、近年の小型化及び高精度化された半導体素子の場合には、バンプピッチの狭小化に伴ってパッドピッチが狭くなるため、隣り合うはんだが互いに接続される、いわゆるはんだブリッジなどの不良が発生する。

【課題を解決するための手段】

【0006】

本発明の一観点によれば、複数の電極パッドが配列形成された半導体素子と、各々の前記電極パッドに対応して配列された複数の接続パッドを有する配線基板と、前記電極パッドに接続された基端部と、前記基端部から突出するように形成された誘導部とを有し、柱状に形成された複数の電極端子と、前記誘導部と前記接続パッドとを互いに電気的に接続するはんだを有し、前記誘導部は、平面視断面積が前記基端部の平面視断面積よりも小さく、外周の一部が前記基端部の外周の一部と面一な外周を有し、前記基端部の外周と面一な外周側に向って前記はんだを誘導するように形成される。

【発明の効果】

【0007】

本発明の一観点によれば、はんだによる短絡不良を低減することができる。

【図面の簡単な説明】

【0008】

【図1】(a)は、半導体装置の概略平面図、(b)〜(d)は、半導体素子と配線基板の接続を示す説明図である。

【図2】(a)(b)は、半導体素子と配線基板の接続を示す説明図である。

【図3】(a)(b)は、電極端子の製造工程を示す説明図である。

【図4】(a)(b)は、電極端子の製造工程を示す説明図である。

【図5】(a)(b)は、電極端子の製造工程を示す説明図である。

【図6】(a)(b)は、電極端子の製造工程を示す説明図である。

【図7】(a)〜(c)は、別の電極端子の説明図である。

【図8】(a)〜(c)は、別の電極端子の説明図である。

【図9】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図10】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図11】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図12】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図13】(a)〜(c)は、別の電極端子の説明図である。

【図14】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図15】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図16】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図17】(a)(b)は、別の電極端子の製造工程を示す説明図である。

【図18】(a)〜(c)は、別の電極端子の説明図である。

【図19】(a)〜(c)は、別の電極端子の説明図である。

【図20】(a)(b)は、電極端子の製造工程を示す説明図である。

【図21】(a)〜(d)は、はんだの移動方向を示す説明図である。

【図22】(a)(b)は、はんだの移動方向を示す説明図である。

【発明を実施するための形態】

【0009】

以下、一実施形態を図1〜図6に従って説明する。

図1(a)に示すように、半導体素子10は、配線基板20の上面(図1(b)参照)に実装されている。

【0010】

図1(a)に示すように、半導体素子10は、一主面(例えば、回路素子が形成された面:図1(b)において下面)に複数の電極パッド11が形成されている。これら複数の電極パッド11は、ペリフェラル配置、つまり、半導体素子10の外周に沿って環状に配置されている。各電極パッド11は、例えば平面視正方形状に形成されている。各電極パッド11の材質は、例えばアルミニウムである。半導体素子10の一主面には保護膜(パッシベーション膜)12が形成されている。保護膜12には、シリコン酸化膜、シリコン窒化膜などが用いられる。

【0011】

図1(b)に示すように、各電極パッド11には、柱状の電極端子(ピラー)13がそれぞれ立設されている。図1(a)に示すように、各電極端子13は、例えば略円柱状に形成されている。電極端子13と電極パッド11との間の接続強度を確保するため、電極端子13の外径は、電極パッド11の外形に対し、可能な限り大きいほうが好ましい。例えば、電極パッド11は、一辺が50ミクロン(μm)の正方形状に形成され、電極端子13の直径は40ミクロン(μm)である。なお、図1(a)において、電極パッド11及び電極端子13を、後述する配線基板20の部材との区別を容易にするために実線で示している。

【0012】

図1(b)に示すように、電極端子13は、電極パッド11の上面(図では下面)に形成されたバリア層14(UBM:Under Barrier Metal)と、バリア層14の上面(図では下面)から電極パッド11と垂直方向に沿って延びる金属端子部15を有している。バリア層14は、例えばチタン(Ti)(又はチタンとタングステン(W)の合金)/銅(Cu)である。バリア層14は、例えばめっき法により形成される。金属端子部15は、例えば銅である。金属端子部15は、例えばめっき法により形成される。

【0013】

図1(b)に示すように、金属端子部15の基端部16は円柱状に形成され、バリア層14に接続されている。金属端子部15の先端部17は略半円形状に形成されている。従って、この先端部17は、基端部16の外周の一部と面一な外周を有している。換言すれば、電極端子13は、基端部と先端面を含む誘導部とからなり、誘導部は、基端部と面一な外周を有する円柱に、その外周の一部を残すような切り欠きが形成された形状である。

【0014】

この略半円形状の先端部17は、先端面の弧部分、即ち基端部16の外周と面一な外周が半導体素子10の外側を向くように形成されている。そして、先端部17において半導体素子10の内側の側面17aは、側面視円弧状に形成されている。この側面17aには、はんだ層18が形成されている。このはんだ層18は、例えばはんだめっき法により形成される。

【0015】

配線基板20は、板状に形成された基板本体21を含む。基板本体21は、例えばエポキシ系の絶縁樹脂により形成されている。基板本体21の上面(チップ搭載面:図1(b)において上面)には、複数の接続パッド22が形成されている。接続パッド22の材料は、例えば銅である。図1(a)に示すように、複数の接続パッド22は、接続対象である半導体素子10の電極パッド11に対応して、電極パッド11の配列方向に沿って矩形環状に配列されている。

【0016】

各接続パッド22は、半導体素子10の電極パッド11の配列方向と直交する方向に沿って延びる平面視長方形状に形成されている。各接続パッド22の幅(接続パッド22の配列方向の長さであって、半導体素子10の辺と平行な方向における長さ)は、電極端子13の大きさ(直径)に対応して設定されている。例えば、接続パッド22の幅は、22ミクロン(μm)に設定されている。なお、接続パッド22の長さ(接続パッド22の配列方向と直交する方向の長さ)は、例えば100ミクロン(μm)である。

【0017】

各接続パッド22は、基板本体21の上面に形成された配線23と接続されている。なお、図示しないが、配線基板20は、半導体素子10を他の素子と接続するための配線やビアを有している。なお、配線基板20を、半導体素子10と他の配線基板とを接続するための基板(パッケージの基板)としてもよい。

【0018】

図1(b)に示すように、基板本体21の上面には、保護膜(ソルダレジスト層)24が形成されている。保護膜24の材料は、例えばエポキシ系の絶縁性樹脂である。図1(a)に示すように、保護膜24には、半導体素子10の外形形状に対応する矩形枠状の開口部が形成され、その開口部から接続パッド22が露出している。

【0019】

図1(a)に示すように、各接続パッド22の長手方向中心は、半導体素子10の電極パッド11の中心と一致するように形成されている。そして、電極端子13は、接続パッド22の中心に形成されている。そして、電極端子13の先端部17は、接続パッド22に応じて、例えば、長手方向両側のうちの何れか一方、例えば、半導体素子10の外側に形成され、側面17aは半導体素子10の内側を向いている。

【0020】

図1(b)に示すように、半導体素子10の電極端子13と配線基板20の接続パッド22は、はんだ30により互いに接続されている。はんだ30は、例えばスズ(Sn)と銀(Ag)の合金である。なお、はんだ30に、スズと亜鉛(Zn)の合金、等を用いることもできる。各接続パッド22上のはんだ30は、接続パッド22と電極端子13の相対的な位置関係に応じた形状に形成される。

【0021】

次に、上記の半導体素子10及び配線基板20における作用を説明する。

図1(c)及び図1(d)に示すように、電極端子13の先端部17には、はんだ31が形成される。このはんだ31は、先端部17の先端面と側面17aとに披着し、図において下方に向って略半球状に形成される。はんだ31は、例えば、半田リフロー処理により形成される。

【0022】

一方、配線基板20の接続パッド22の上面には、ドーム状のはんだ32が形成される。はんだ32は、中央部分が膨出するように形成される。このはんだ32は、接続パッド22の上面に形成されたはんだ32の母材を溶融した際、表面張力により、溶融したはんだが接続パッド22の上面に集まる。これにより、頂点が接続パッド22の中心と略一致するはんだ32が形成される。また、はんだ32の形成に、例えば、スーパージャフィット(登録商標)法を用いることができる。

【0023】

なお、電極端子13の先端と接続パッド22の上面には、電極端子13と接続パッド22を互いに接続するのに必要なはんだ量よりも多い量のはんだが形成される。つまり、電極端子13に形成されたはんだ31の量と接続パッド22上面に披着したはんだ32の量の合計は、電極端子13と接続パッド22を互いに接続するのに必要なはんだ量よりも多い。

【0024】

次に、半導体素子10と配線基板20とを相対的に位置合せする。そして、半導体素子10を配線基板20に対して所定の圧力で押し付け、半田リフロー処理を行う。この半田リフロー処理により、電極端子13先端のはんだ31と、接続パッド22上面のはんだ32は溶融する。このとき、はんだ32の頂点と、電極端子13の先端部17の位置がずれているため、接続パッド22上面のはんだ32は、電極端子13を押し下げる力により、先端部17が形成された方向に応じて移動する。

【0025】

図1(a)に示すように、接続パッド22は、配列方向と直交する方向に沿って延びる長方形状に形成されている。そして、電極端子13の先端部17は、接続パッド22の中心から、その接続パッド22が延びる方向に沿って、半導体素子10の各辺側(外側)に形成されている。従って、接続パッド22上面のはんだ32は、接続パッド22が延びる方向に沿って、半導体素子10の外側に向って移動する。

【0026】

そして、はんだ31とはんだ32を硬化させることにより、図1(b)に示すはんだ30が形成される。このはんだ30は、接続パッド22の配列方向の突出する部分が少ない。これは、電極端子13の先端部17が、溶融したはんだ31,32を、半導体素子10の外側、即ち基端部16の外周と面一な外周側に向って誘導するためである。これにより、隣り合う2つの接続パッド22間におけるはんだによる短絡不良の発生を低減する。

【0027】

なお、電極端子の先端部が円柱状に形成され、その先端面が接続パッド22上面と略平行な平坦面に形成された場合、溶融したはんだ31,32は、電極端子の先端面及び接続パッド22の面に沿って移動するため、接続パッド22の配列方向の突出量が多くなる。この配列方向に突出したはんだは、隣り合う2つの接続パッド22で相互に接続され、はんだによる短絡不良が発生する。

【0028】

ところで、1つの半導体素子10に形成された複数の電極端子13の長さは、製造工程においてばらつく場合がある。例えば、図2(a)に示すように、1つの半導体素子10に形成された電極端子13aの長さLaに対し、同じ半導体素子10に形成された電極端子13bの長さLbがΔLだけ短い場合がある。各電極端子13a,13bには、はんだ31a,31bがそれぞれ形成される。これらのはんだ31a,31bの量は、同様に形成されるため、互いに等しい。

【0029】

電極端子13aに対応する接続パッド22a上面には、はんだ32aが形成される。同様に、電極端子13bに対応する接続パッド22b上面にははんだ32bが形成される。そして、図2(b)に示すように、電極端子13aと接続パッド22aは、はんだ30aにより、電気的に互いに接続される。この場合、電極端子13aにより逃げるはんだ32aの量に対し、電極端子13bにより逃げるはんだ32bの量が少なくなる。しかし、これらはんだ31b、32bを合計したはんだ量は、電極端子13a及び接続パッド22のはんだ31a,31bと同量である。従って、電極端子13bと接続パッド22bとの間に、はんだ31b,32bが残存する。このため、図2(b)に示すように、電極端子13bと接続パッド22bは、はんだ30bにより、電気的に互いに接続される。

【0030】

次に、上記の電極端子13の製造方法を説明する。

先ず、図3(a)及び図3(b)に示すように、電極パッド11及び保護膜12が形成された半導体素子10上にレジスト層41を形成し、レジスト層41に開口部41aを形成する。レジスト層41の膜厚は、電極パッド11の上面から電極端子13の先端面までの高さ(図1(b)参照)に等しい。開口部41aは、電極パッド11上に形成される電極端子13の形成領域に対応する部分の電極パッド11の上面を露出するように形成される。レジスト層41の材料としては、感光性のドライフィルムや液状のフォトレジスト(ノボラック系樹脂、エポキシ系樹脂等の液状レジスト)を用いることができる。

【0031】

次いで、図4(a)及び図4(b)に示すように、レジスト層41をめっきマスクとして、めっき法により、電極パッド11上に円柱状の電極部42を形成する。具体的には、レジスト層41の開口部41aから露出された電極パッド11の上面に、図1(b)に示すバリア層14を形成する。次いで、バリア層14上に柱状の金属端子部15を形成する。

【0032】

次いで、図5(a)及び図5(b)に示すように、レジスト層41上に、開口部43aを有するレジスト層43を形成する。レジスト層43は、図1(b)に示す先端部17を覆うように形成される。従って、レジスト層43(開口部43a)の形状により、先端部17の大きさ、形状、形成方向を適宜設定することができる。

【0033】

次いで、図6(a)及び図6(b)に示すように、レジスト層43の開口部43aから電極部42に対して例えばエッチング処理を行い、湾曲した側面17aを形成する。従って、エッチング処理の条件(処理時間,エッチング液の濃度,等)により、側面17aの大きさ、つまり先端部17の長さを適宜設定することができる。

【0034】

次いで、レジスト層43の開口部43aから側面17aに対して、例えばはんだめっき法により、はんだ層18を形成する。次いで、レジスト層41,43を、例えばアッシングにより除去する。これにより、先端部17を有する電極端子13が形成される。

【0035】

なお、電極端子13は、ウェハ状態の半導体素子10に対して形成される。即ち、複数の半導体素子10を形成するためのウェハに対し、上記図3〜図6に示す処理が実施される。これにより、複数の半導体素子10に対して、電極パッド11上に電極端子13が一括して形成される。このように電極端子13を形成することにより、金(Au)等を用いたバンプを形成する工程と比べ、製造に要する時間を短縮することができる。金などのバンプは、個々に形成する必要があるため、時間を要する。また、マスクを用いて電極端子13を形成することにより、電極端子13のピッチ(隣り合う2つの電極端子13の中心間の距離)を、バンプを個々に形成する場合と比べ、短くすることができる。

【0036】

以上記述したように、本実施形態によれば、以下の効果を奏する。

(1)半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。電極端子13の基端部(金属端子部15の基端部16及びバリア層14)は電極パッド11に接続されている。電極端子13(金属端子部15)の先端部17は略半円柱状に形成されている。この略半円柱状の先端部17は、先端面の弧部分が半導体素子10の外側を向くように形成されている。

【0037】

半導体素子10が実装される配線基板20には、半導体素子10の電極パッド11と対応する複数の接続パッド22が形成されている。各接続パッド22の中心は、半導体素子10の電極パッド11の中心と略一致する。また、各接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。

【0038】

各接続パッド22の上面には、はんだ32が披着されている。電極端子13の先端部17は、その形成方向、詳しくは基端部16の外周と面一な外周側、即ち半導体素子10の外側に向って溶融したはんだ31,32を誘導する。これにより、接続パッド22の配列方向、即ち、隣り合う接続パッド22の方向にはみだすはんだ30の量が少なくなる。このため、はんだ30により隣り合う接続パッド22が互いに電気的に接続される短絡不良を低減することができる。

【0039】

(2)各電極端子13の先端面にははんだ31が形成される。この電極端子31に形成されたはんだ31と、接続パッド22上面に披着したはんだ32とが半田リフロー処理により互いに融合してはんだ30が形成される。このはんだ30の量、つまり電極端子13に形成されたはんだ31の量と接続パッド22上面に披着したはんだ32の量の合計は、電極端子13と接続パッド22を互いに接続するのに必要なはんだ量よりも多い。

【0040】

めっき法により形成される電極端子13は、長さにばらつきが生じる。従って、電極端子13aよりも短い電極端子13bの場合、電極端子13bと接続パッド22bの間に、はんだ31b,32bが残存し、これらによるはんだ30bにより、電極端子13bと接続パッド22bが電気的に接続される。このように、はんだ31a,31b,32a,32bの量を多くすることにより、長さにばらつきが生じる電極端子13a,13bは、ぞれぞれに対応する接続パッド22a,22bと接続される。従って、ばらつきによる接続不良を低減することができる。

【0041】

(3)先端部17の側面17aにははんだ層18が形成されている。このはんだ層18は、溶融したはんだ31,32を側面17aに披着させるように働く。従って、余剰なはんだを側面17aに積極的に披着させることで、はんだのはみだしを低減することができる。

【0042】

尚、上記実施形態は、以下の態様で実施してもよい。

・上記実施形態では、略円柱状の電極端子13(図1(a)参照)を用いたが、電極端子の形状を適宜変更してもよい。例えば、図7(a)に示すように、略四角柱状の電極端子51を用いるようにしてもよい。この電極端子51は、四角柱状に形成された基端部52に対し、先端部53の側面53aが湾曲して形成されている。

【0043】

この電極端子51は、例えば、図3(a)に示すレジスト層41の開口部41aを、矩形状とすることにより得られる。この電極端子51においても、図7(b)に白抜きの矢印にて示すように、はんだを誘導することができ、短絡を防止することができる。

【0044】

なお、先端部側面の一部を残すようにエッチング処理して上記の側面53a等を形成する際に、エッチング処理の条件等によって、図7(c)に示すように、レジスト膜(図6(b)参照)に沿ってエッチング残りが生じる場合がある。しかし、このようにエッチング残りが生じた電極端子51aであっても、上記実施形態と同様に、はんだのはみだしを低減することができる。

【0045】

・上記実施形態では、先端部17に湾曲する側面17aを形成したが、側面17aの形状を適宜変更してもよい。例えば、図8(a)に示すように、電極端子61aは、円柱状の基端部62aに対し、先端部63aに対して側面64aが平坦に形成されている。同様に、図8(b)に示すように、電極端子61bは、四角柱状の基端部62bに対し、先端部63bに対して側面64bが平坦に形成されている。これらの電極端子61a,61bにおいても、上記実施形態と同様に、図8(c)に白抜きの矢印にて示すように、はんだを誘導することができ、短絡を防止することができる。

【0046】

なお、図8(a)(b)に示す電極端子61a,61bは、例えば、図6に示す処理において、開口部43aからブラスト処理を行うことにより得られる。

また、図9〜図12に示す各工程により電極端子61aを得ることもできる。

【0047】

即ち、図9(a)及び図9(b)に示すように、電極パッド11及び保護膜12が形成された半導体素子10上にレジスト層71を形成し、レジスト層71に開口部71aを形成する。レジスト層71の膜厚は、電極端子61bの基端部62bの高さ(図8(b)参照)に等しい。開口部71aは、電極パッド11上に形成される電極端子13の形成領域に対応する部分の電極パッド11の上面を露出するように形成される。レジスト層71の材料としては、感光性のドライフィルムや液状のフォトレジスト(ノボラック系樹脂、エポキシ系樹脂等の液状レジスト)を用いることができる。

【0048】

次いで、図10(a)及び図10(b)に示すように、レジスト層71をめっきマスクとして、めっき法により、円柱状の基端部62bを形成する。

次いで、図11(a)及び図11(b)に示すように、レジスト層71上に、開口部72aを有するレジスト層72を形成する。レジスト層72は、図8(b)に示す先端部63bに対応する形状に形成される。従って、レジスト層72(開口部72a)の形状により、先端部63bの大きさ、形状、形成方向を適宜設定することができる。

【0049】

次いで、図12(a)及び図12(b)に示すように、レジスト層72をめっきマスクとして、めっき法により、半円柱状の先端部63bを形成する。

そして、レジスト層71,72を、例えばアッシングにより除去する。これにより、平坦な側面64bの先端部63bを有する電極端子61bが形成される。

【0050】

図9〜図12に示す工程において、レジスト層71,72に形成する開口部71a,72aの形状を矩形状とすることにより、図8(b)に示す電極端子61bが得られる。そして、開口部71a,72aの形状を適宜変更することにより、略半円形状、略矩形形状、略扇形形状等、様々な形状の誘導部を有する電極端子を得ることができる。

【0051】

・上記形態では、溶融したはんだを1つの方向に誘導する電極端子としたが、複数の方向にはんだを誘導するように電極端子を形成してもよい。

例えば、図13(a)に示すように、電極端子81aは略円柱状に形成されている。電極端子81aの先端面中央は、側面視円弧状の底面82aに形成され、この底面82aは、所定方向に沿って延びる溝83aを形成する。この溝83aの幅、即ち両側における先端部84a,85aの間隔は、例えば、図1(a)に示す接続パッド22の幅以上に設定されている。そして、電極端子81aは、溝83aが延びる方向と、接続パッド22が延びる方向が一致するように、電極パッド11上に形成される。そして、電極端子81aの溝83a及び先端部84a,85aにははんだが披着される。

【0052】

この電極端子81aを有する半導体素子を配線基板20に実装する際、電極端子81aは、先端部84a,85aの間に形成された溝83aにより、はんだをその溝83aが延びる方向に誘導する。即ち、1つの電極端子81aは、2つの誘導部(先端部84a,85a)を有している。そして、電極端子81aは、はんだの誘導方向と、接続パッド22の長手方向と一致するように形成される。これにより、接続パッド22の幅方向、つまり接続パッド22の配列方向へのはんだのはみ出しを少なくすることで、余剰なはんだによる短絡を防止することができる。

【0053】

なお、図13(b)に示すように、矩形柱状の電極端子81bを用いるようにしてもよい。この電極端子81bは、先端の底面82bにより形成された溝83bを有している。また、図13(c)に示すように、矩形柱状の電極端子81cは、2つの斜面82cにより形成された溝83cを有している。また、2つの側面と1つの底面により形成される矩形状の溝(コ字状の溝)を形成してもよい。

【0054】

図13(a)に示す電極端子81aの製造工程の一例を図14〜図17に従って説明する。

先ず、図14(a)及び図14(b)に示すように、電極パッド11及び保護膜12が形成された半導体素子10上にレジスト層91を形成し、レジスト層91に開口部91aを形成する。開口部91aは、電極パッド11上に形成される電極端子81aの形成領域に対応する部分の電極パッド11の上面を露出するように形成される。レジスト層91の材料としては、感光性のドライフィルムや液状のフォトレジスト(ノボラック系樹脂、エポキシ系樹脂等の液状レジスト)を用いることができる。

【0055】

次いで、図15(a)及び図15(b)に示すように、レジスト層91をめっきマスクとして、めっき法により、電極パッド11上に円柱状の電極部92を形成する。

次いで、図16(a)及び図16(b)に示すように、レジスト層91上に、開口部93aを有するレジスト層93を形成する。レジスト層93は、図13(a)に示す先端部84a,85aを覆うように形成される。従って、レジスト層93(開口部93a)の形状により、先端部84a,85aの大きさ、形状、図13(a)に示す溝83aの形成方向を適宜設定することができる。

【0056】

次いで、図17(a)及び図17(b)に示すように、レジスト層93の開口部93aから電極部92に対して例えばエッチング処理を行い、湾曲した底面82aを形成する。従って、エッチング処理の時間により、底面82aの深さを適宜設定することができる。

【0057】

次いで、レジスト層93の開口部93aから底面82aに対して、例えばはんだめっき法により、はんだ層を形成する。次いで、レジスト層91,93を、例えばアッシングにより除去する。これにより、図13(a)に示す電極端子81aが得られる。

【0058】

なお、レジスト層91に形成する開口部91aの形状を矩形状とすることにより、図13(b)に示す電極端子81bが得られる。また、図17で示したエッチング処理に替えてブラスト処理等の他の処理を行うようにしてもよく、実施する処理に応じた形状の溝を電極端子の先端に形成することができる。

【0059】

・上記各形態に対し、先端部がデーパ状に形成された電極端子を用いるようにしてもよい。

例えば、図18(a)に示すように、電極端子101aは、円柱状に形成され、先端面102aが所定の方向に傾いて形成されている。また、図18(b)に示すように、電極端子101bは矩形柱状に形成され、先端面102bが所定の方向に傾いて形成されている。このように形成された電極端子101a,101bは、図18(c)に示すように、先端面102a,102bの傾斜方向にはんだを誘導する。

【0060】

また、先端部がテーパ状に形成されるとともに先端を平坦に形成した電極端子を用いるようにしてもよい。

例えば、図19(a)に示すように、電極端子111aは、略円柱状に形成され、先端部112aを斜めに切り欠いて傾斜面113aが形成されている。同様に、図19(a)に示すように、電極端子111bは、矩形柱状に形成され、先端部112bを斜めに切り欠いて傾斜面113bが形成されている。このように形成された電極端子111a,111bは、図19(c)に示すように、先端部112a,112bの方向にはんだを誘導する。

【0061】

図18及び図19に示す電極端子は、例えば、図20に示すように、形成される。

即ち、図20(a)に示すように、半導体素子に柱状の金属端子121を形成し、その金属端子121の先端部が突出するようにレジスト層122を形成する。次いで、金属端子121を形成した半導体素子を保持するステージを、図20(b)に示すように傾け、研磨処理のためのヘッド123(例えば、化学的機械的研磨(CMP:Chemical Mechanical Polishing)に用いるヘッド)を用いて金属端子121を研削して斜面を形成する。ステージとヘッド123の相対的な傾きにより、斜面の角度が設定される。レジスト層122がストッパとして機能し、レジスト層122から金属端子121の突出量により、斜面の大きさが設定される。なお、研削時間を制御するようにしてもよい。

【0062】

・上記各形態において、はんだを誘導する方向を適宜変更してもよい。

例えば、図13に示す電極端子81aを用いた場合、図21(a)に白抜きの矢印で示すように、電極端子81aの両側であって、例えば接続パッド22が延びる方向に沿ってはんだを誘導することができる。このため、隣り合う接続パッド22の方向にはみ出すはんだの量を低減し、はんだによる短絡を防止することができる。

【0063】

また、1つの方向にはんだを誘導する電極端子(図1(b)に示す電極端子13)を用い、図21(b)に白抜きの矢印で示すように、隣り合う接続パッド22において互いに逆方向にはんだを誘導するようにしてもよい。この場合、誘導されたはんだが接続パッド22の幅方向にはみ出しても、隣り合う接続パッド22におけるはんだは、電極端子13に対して逆方向に誘導されている。このため、隣り合う接続パッド22におけるはんだが互いに接触することはないため、はんだによる短絡を防止することができる。

【0064】

また、図21(c)に白抜きの矢印で示すように、接続パッド22の配列方向に沿って、各電極端子13において同じ方向にはんだを誘導するようにしてもよい。

また、図21(d)に示すように、半導体素子10aの周辺に沿って、端部から第1の距離に配置される電極端子13に対応する接続パッド22aと、端部から第2の距離に配置される電極端子13に対応する接続パッド22bが交互に配列された、所謂千鳥配置の場合、隣り合う接続パッド22a,22bの中心を通る直線に沿って1つの方向にはんだを誘導するように電極端子を形成してもよい。なお、このように配置された接続パッド22a,22bにおいて、図21(b)に示すように、互いに逆方向にはんだを誘導するように電極端子を形成するようにしてもよい。

【0065】

・上記各形態は、ペリフェラル配置の半導体素子と、それを実装する配線基板について説明したが、上記各電極端子を、他の配置の半導体素子に適用してもよい。

例えば、電極パッド11がマトリックス配置された半導体素子を配線基板に実装する場合に適用する。この場合、図22(a)に白抜きの矢印で示すように、半導体素子10cの各電極パッド11に形成された電極端子13において、1つの方向(例えば、電極パッド11の1つの対角線に沿った方向)にはんだを誘導するようにしてもよい。また、図22(b)に示すように、隣り合う電極パッド11において、互いに逆方向にはんだを誘導するように電極端子13を形成してもよい。

【0066】

・上記各形態では、電極端子を略円柱状,略四角柱状としたが、5角形以上の多角形柱状としてもよい。

【符号の説明】

【0067】

10 半導体素子

11 電極パッド

13 電極端子

17 先端部(誘導部)

20 配線基板

22 接続パッド

30 はんだ

【特許請求の範囲】

【請求項1】

複数の電極パッドが配列形成された半導体素子と、

各々の前記電極パッドに対応して配列された複数の接続パッドを有する配線基板と、

前記電極パッドに接続された基端部と、前記基端部から突出するように形成された誘導部とを有し、柱状に形成された複数の電極端子と、

前記誘導部と前記接続パッドとを互いに電気的に接続するはんだと、

を有し、

前記誘導部は、平面視断面積が前記基端部の平面視断面積よりも小さく、外周の一部が前記基端部の外周の一部と面一な外周を有し、前記基端部の外周と面一な外周側に向って前記はんだを誘導するように形成されたこと、

を特徴とする半導体装置。

【請求項2】

前記複数の接続パッドは、前記複数の電極パッドの配列方向と直交する方向矩形状に形成され、

前記誘導部は、前記接続パッドの長手方向に前記はんだを誘導するように形成されたこと、

を特徴とする請求項1記載の半導体装置。

【請求項3】

前記複数の電極端子にはそれぞれ1つの誘導部が形成され、

前記複数の電極端子それぞれの誘導部は、隣り合う前記電極パッドにおいて互いに同じ方向に前記はんだを誘導するように形成されたこと

を特徴とする請求項2に記載の半導体装置。

【請求項4】

前記複数の電極端子にはそれぞれ1つの誘導部が形成され、

前記複数の電極端子それぞれの誘導部は、隣り合う前記電極パッドにおいて互いに逆方向に前記はんだを誘導するように形成されたこと

を特徴とする請求項2に記載の半導体装置。

【請求項5】

一主面に配列形成された複数の電極パッドと、

前記電極パッドに接続され、柱状に形成された複数の電極端子と、

を有し、

前記電極端子は、前記電極パッドに接続された基端部と、前記基端部から突出するように形成された誘導部とを備え、

前記誘導部の外周の一部は、基端部の外周の一部と面一であり、

前記誘導部の平面視断面積は、前記基端部の平面視断面積よりも小さく、

前記誘導部は、前記電極パッドと対応して配線基板に形成された接続パッドとはんだにより互いに電気的に接続されること

を特徴とする半導体素子。

【請求項6】

複数の電極パッドが配列形成された半導体素子と、前記半導体素子の各々の電極パッドに対応して配列された複数の接続パッドを有する配線基板と、を有する半導体装置の製造方法であって、

前記電極パッドに接続される基端部と、前記基端部から突出するように形成された誘導部とを含み、前記誘導部は前記基端部の外周の一部と面一な外周を有し、前記誘導部の平面視断面積は前記基端部の平面視断面積よりも小さい、柱状の電極端子を形成し、

前記誘導部と前記接続パッドをはんだにより互いに電気的に接続し、

前記はんだによる電気的な接続に際し、前記誘導部は前記基端部の外周と面一な外周側に向って前記はんだを誘導すること

を特徴とする半導体装置の製造方法。

【請求項7】

前記複数の電極端子に含まれる誘導部を、隣り合う前記電極パッドにおいて互いに同じ方向に形成することを特徴とする請求項6記載の半導体装置の製造方法。

【請求項8】

前記複数の電極端子に含まれる誘導部を、隣り合う前記電極パッドにおいて互いに逆方向に形成することを特徴とする請求項6記載の半導体装置の製造方法。

【請求項1】

複数の電極パッドが配列形成された半導体素子と、

各々の前記電極パッドに対応して配列された複数の接続パッドを有する配線基板と、

前記電極パッドに接続された基端部と、前記基端部から突出するように形成された誘導部とを有し、柱状に形成された複数の電極端子と、

前記誘導部と前記接続パッドとを互いに電気的に接続するはんだと、

を有し、

前記誘導部は、平面視断面積が前記基端部の平面視断面積よりも小さく、外周の一部が前記基端部の外周の一部と面一な外周を有し、前記基端部の外周と面一な外周側に向って前記はんだを誘導するように形成されたこと、

を特徴とする半導体装置。

【請求項2】

前記複数の接続パッドは、前記複数の電極パッドの配列方向と直交する方向矩形状に形成され、

前記誘導部は、前記接続パッドの長手方向に前記はんだを誘導するように形成されたこと、

を特徴とする請求項1記載の半導体装置。

【請求項3】

前記複数の電極端子にはそれぞれ1つの誘導部が形成され、

前記複数の電極端子それぞれの誘導部は、隣り合う前記電極パッドにおいて互いに同じ方向に前記はんだを誘導するように形成されたこと

を特徴とする請求項2に記載の半導体装置。

【請求項4】

前記複数の電極端子にはそれぞれ1つの誘導部が形成され、

前記複数の電極端子それぞれの誘導部は、隣り合う前記電極パッドにおいて互いに逆方向に前記はんだを誘導するように形成されたこと

を特徴とする請求項2に記載の半導体装置。

【請求項5】

一主面に配列形成された複数の電極パッドと、

前記電極パッドに接続され、柱状に形成された複数の電極端子と、

を有し、

前記電極端子は、前記電極パッドに接続された基端部と、前記基端部から突出するように形成された誘導部とを備え、

前記誘導部の外周の一部は、基端部の外周の一部と面一であり、

前記誘導部の平面視断面積は、前記基端部の平面視断面積よりも小さく、

前記誘導部は、前記電極パッドと対応して配線基板に形成された接続パッドとはんだにより互いに電気的に接続されること

を特徴とする半導体素子。

【請求項6】

複数の電極パッドが配列形成された半導体素子と、前記半導体素子の各々の電極パッドに対応して配列された複数の接続パッドを有する配線基板と、を有する半導体装置の製造方法であって、

前記電極パッドに接続される基端部と、前記基端部から突出するように形成された誘導部とを含み、前記誘導部は前記基端部の外周の一部と面一な外周を有し、前記誘導部の平面視断面積は前記基端部の平面視断面積よりも小さい、柱状の電極端子を形成し、

前記誘導部と前記接続パッドをはんだにより互いに電気的に接続し、

前記はんだによる電気的な接続に際し、前記誘導部は前記基端部の外周と面一な外周側に向って前記はんだを誘導すること

を特徴とする半導体装置の製造方法。

【請求項7】

前記複数の電極端子に含まれる誘導部を、隣り合う前記電極パッドにおいて互いに同じ方向に形成することを特徴とする請求項6記載の半導体装置の製造方法。

【請求項8】

前記複数の電極端子に含まれる誘導部を、隣り合う前記電極パッドにおいて互いに逆方向に形成することを特徴とする請求項6記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【公開番号】特開2013−115214(P2013−115214A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−259485(P2011−259485)

【出願日】平成23年11月28日(2011.11.28)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月28日(2011.11.28)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【Fターム(参考)】

[ Back to top ]