半導体装置、半導体素子及びその検査方法

【課題】テスト用電極パッドを設けることなく、電極パッドと該電極パッドの上に設ける金属ボール又は金属突起との合金化を確実に図れるようにする。

【解決手段】半導体装置は、第1の半導体チップ2と、該第1の半導体チップ2の上にその少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を上にして固着された第2の半導体チップ3とを有している。第1の半導体チップ2は、第2の半導体チップ3の側面に沿って形成された複数の内側電極パッド7を有し、該内側電極パッド7の上には金属からなるバンプ9が形成されている。第2の半導体チップ3は、素子形成面に形成された複数の電極パッド10を有し、各電極パッド10と各内側電極パッド7上のバンプ9とはそれぞれワイヤ11により接続され、内側電極パッド7は平面長方形状を有している。

【解決手段】半導体装置は、第1の半導体チップ2と、該第1の半導体チップ2の上にその少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を上にして固着された第2の半導体チップ3とを有している。第1の半導体チップ2は、第2の半導体チップ3の側面に沿って形成された複数の内側電極パッド7を有し、該内側電極パッド7の上には金属からなるバンプ9が形成されている。第2の半導体チップ3は、素子形成面に形成された複数の電極パッド10を有し、各電極パッド10と各内側電極パッド7上のバンプ9とはそれぞれワイヤ11により接続され、内側電極パッド7は平面長方形状を有している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の半導体素子(半導体チップ)を搭載した半導体装置(例えば、システムインパッケージ)、該半導体装置を構成する半導体素子及びその検査方法に関する。

【背景技術】

【0002】

高鮮度及び高精細の動画処理を行う電子機器、例えばハイビジョンデジタルテレビは、小型化及び低コスト化を図るために、すべての機能を1つの半導体チップに集積化する方向が採られており、このため、半導体素子のウエハプロセスは微細化が進み、チップ面積が縮小化されている。

【0003】

一方、電子機器と半導体素子との接続は、従来の半導体素子用パッケージである、例えばQFP(Quad Flat Package)又はBGA(Ball Grid Array)パッケージ等を用いた従来の接続形態の要求が強く残っている。このため、パッケージ内の配線電極と半導体素子のパッド電極との間の製造規格のギャップが大きくなりつつある。

【0004】

また、電子機器に組み込まれる半導体装置も、配線基板に実装する実装面積の縮小化のため小型化が求められている。これらを解決する方法の1つとして複数の半導体チップを1つにパッケージする構成、例えばシステムインパッケージ(System in Package、以下、SiPと呼ぶ。)構造が採られるようになってきている。このSiPは例えば下記のような構成を持つ。

【0005】

すなわち、SiPは、基板(実装用基板)と、該基板の主面上に素子形成面を上にして固着された第1の半導体チップと、該第1の半導体チップの上に素子形成面を上にして固着された第2の半導体チップとを有している。さらに、第1の半導体素子の素子形成面に形成された電極パッドと基板に形成された電極パッドとが金属細線によって接続され、第2の半導体素子の素子形成面に形成された電極パッドと、基板に形成された電極パッド又は第1の半導体チップに形成された電極パッドとが金属細線によって接続されている。また、第1の半導体チップと第2の半導体チップとはモールド樹脂体により覆われている。

【0006】

SiPは、既存のプローブテスト用装置又は設備を用いて、配線基板として用いられる半導体チップのオープンショートテストを行うことができ、テストコストを削減可能な積層型SiP構造を採る半導体装置として以下の構造が提案されている。

【0007】

配線基板として用いられる第1の半導体チップの上には、第2の半導体チップが固着され、第2の半導体チップの上には第3の半導体チップが固着されており、第2の半導体チップの素子形成面には、外周部電極パッドと、その内側に配置され且つ外周部電極パッドと配線を介して接続され、第3の半導体チップの電極パッドと接続される中央部電極パッドと、第2の半導体チップの外周部に配置され、中央部電極パッドと配線を介して接続されたテスト用電極パッドとが形成されている(例えば、特許文献1を参照。)。

【特許文献1】特開2004−253609号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

ところで、SiPにおいては、チップ同士を金属細線(以下、ワイヤと呼ぶ。)又は金属からなる突起部(以下、バンプと呼ぶ。)によって電気的に接続する必要がある。

【0009】

狭パッドピッチ構造において、ワイヤを用いて接続する場合を想定すると、チップ同士を接続するワイヤのステッチ側(第2ボンド部)には電極パッドの上にバンプを形成する必要がある。また、ワイヤの接続開始側である、いわゆる第1ボンド部にもワイヤの端部に金属ボールを形成する必要がある。このとき、電極パッドにおける金属ボール又はバンプとの接続部分に、プローブテストの際に付けられたプローブ痕(接触痕)が残存すると、金属ボール又はバンプと電極パッドとの間に十分な強度を有する合金部が形成されない場合がある。このため、プローブテスト時のプローブの接触部分とワイヤ先端の金属ボール又はバンプとの接続部分を分離することが、パッドサイズが小さい狭パッドピッチ構造の接続には必須となる。

【0010】

従って、例えば特許文献1等に記載された従来例は、テスト用電極パッドとワイヤ接続用の電極パッドとを分離して形成していることから、ワイヤ接続用の電極パッドと金属ボール又はバンプとの間の合金部の形成には問題がない。

【0011】

しかしながら、本従来例においては、テスト用電極パッドは、接続用の電極パッドから細い配線によって接続されているため、配線の抵抗及び容量の影響により信号に遅延が生じてしまい、高クロックレートを要求される信号を測定することは困難である。このため、本従来例に示されているように、オープンショートテスト程度にしか活用できないという問題がある。

【0012】

また、接続用の電極パッドとテスト用電極パッドとの配線が断線していた場合は、良否判定自体が行えないという問題も生じる。

【0013】

さらには、テスト用電極パッドと、該テスト用電極パッドと接続用の電極パッドとを接続する新たな配線とを設ける必要から、半導体チップにおける配線の自由度が制限されたり、余分なチップ面積が要求されたりして、特性劣化さらにはコストの上昇を招くおそれがある。

【0014】

本発明は、前記従来の問題を解決し、テスト用電極パッドを設けることなく、電極パッドと該電極パッドの上に設ける金属ボール又は金属突起との合金化を確実に図れるようにすることを目的とする。

【課題を解決するための手段】

【0015】

前記の目的を達成するため、本発明は、半導体装置における電極パッドの平面形状を長方形とすることにより、電極パッドにおけるプローブの接触痕とバンプ等の金属突起部の形成位置との重なり部分を小さくする構成とする。

【0016】

具体的に、本発明に係る第1の半導体装置は、チップ状の第1の半導体素子と、第1の半導体素子の上に、第1の半導体素子の少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を上にして固着されたチップ状の第2の半導体素子とを備え、第1の半導体素子は、第2の半導体素子の側面に沿って形成された複数の第1の電極パッドを有し、第1の電極パッドの上には金属からなる突起部が形成されており、第2の半導体素子は、素子形成面に形成された複数の第2の電極パッドを有し、各第2の電極パッドと各第1の電極パッドの突起部とはそれぞれ第1の金属細線により接続され、第1の電極パッドは平面長方形状を有していることを特徴とする。

【0017】

第1の半導体装置によると、第1の電極パッドは平面長方形状を有しているため、検査時のプローブ痕と金属からなる突起部との形成位置を分離するか又は互いの重なり部分を小さくすることができる。これにより、金属からなる突起部と第1の電極パッドとの合金化が十分になされるので、金属細線による接続の信頼性が向上する。その上、電極パッドの他にテスト用電極パッドを設けないため、電極パッドとテスト用電極パッドとの間の配線の抵抗及び容量の影響がなくなるので、信号遅延を排除して高クロックレート信号を測定することができる。

【0018】

第1の半導体装置は、上面に第1の半導体素子を固着すると共に第3の電極パッドを有する半導体基板、又は上面に第1の半導体素子を固着すると共に電極を有するリードフレームをさらに備え、第3の電極パッドは、複数の第1の電極パッドの一部又は複数の第2の電極パッドの一部と第2の金属細線により接続され、又はリードフレームの電極は、複数の第1の電極パッドの一部又は複数の第2の電極パッドの一部と第2の金属細線により接続されることが好ましい。

【0019】

本発明に係る第2の半導体装置は、チップ状の第1の半導体素子と、第1の半導体素子の上に、第1の半導体素子の少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を下にして固着されたチップ状の第2の半導体素子とを備え、第1の半導体素子は、第2の半導体素子の素子形成面と対向する位置に形成された複数の第1の電極パッドを有し、第1の電極パッドの上には金属からなる突起部が形成されており、第2の半導体素子は、第1の半導体素子の複数の第1の電極パッドと接続される複数の第2の電極パッドを有し、第1の電極パッドは平面長方形状を有していることを特徴とする。

【0020】

第2の半導体装置によると、第1の電極パッドは平面長方形状を有しているため、検査時のプローブ痕と金属からなる突起部との形成位置を分離するか又は互いの重なり部分を小さくすることができる。これにより、金属からなる突起部と第1の電極パッドとの合金化が十分になされるので、突起部と第1の電極パッドとの間の接続の信頼性が向上する。その上、電極パッドの他にテスト用電極パッドを設けないため、電極パッドとテスト用電極パッドとの間の配線の抵抗及び容量の影響がなくなるので、信号遅延を排除して高クロックレート信号を測定することができる。

【0021】

第2の半導体装置は、上面に第1の半導体素子を固着すると共に第3の電極パッドを有する半導体基板、又は上面に第1の半導体素子を固着すると共に電極を有するリードフレームをさらに備え、第3の電極パッド又はリードフレームの電極は、複数の第1の電極パッドの一部と金属細線により接続されることが好ましい。

【0022】

第1又は第2の半導体装置において、第1の電極パッドにおける長辺の長さは、短辺の長さの1.5倍以上であることが好ましい。

【0023】

第1又は第2の半導体装置において、第1の電極パッドには、長辺に沿って検査プローブによる接触痕が残存しており、突起部は、接触痕の一部の上に形成されていることが好ましい。

【0024】

本発明に係る半導体素子は、素子形成面にそれぞれ平面長方形状の複数の電極パッドを備え、電極パッドにおける長辺の長さは、短辺の長さの1.5倍以上であることを特徴とする。

【0025】

本発明の半導体素子によると、電極パッドは平面長方形状を有しているため、電極パッドの上に、バンプ又は金属ボールからなる突起部を形成する際に、検査時のプローブ痕と突起部との形成位置を分離するか又は互いの重なり部分を小さくすることができる。これにより、突起部と電極パッドとの合金化が十分になされるので、金属細線による接続の信頼性が向上する。その上、電極パッドの他にテスト用電極パッドを設けないため、電極パッドとテスト用電極パッドとの間の配線の抵抗及び容量の影響がなくなるので、信号遅延を排除して高クロックレート信号を測定することができる。

【0026】

本発明に係る半導体素子の電気的特性を検査する検査方法を対象とし、平面長方形状の電極パッドに、検査用の検査プローブを接触させる際に、電極パッドにおける短辺側の領域に、検査プローブを接触させることを特徴とする。

【発明の効果】

【0027】

本発明に係る半導体装置、半導体素子及びそれを用いた検査方法によると、金属からなる突起部と電極パッドとの合金化が十分になされるので、突起部における接続の信頼性が向上する。その上、テスト用電極パッドを設けないことから、電極パッドとテスト用電極パッドとの間の配線の抵抗及び容量の影響がなくなるので、高クロックレート信号を測定することができる。これにより、狭パッドピッチのワイヤ接続用の電極パッドを有する高コストな配線基板又はリードフレームを用いることなく、従来構成のパッケージを用いることができる。従って、チップ同士又はチップと配線基板等の接続の信頼性が高く、伝送電気信号歪みが小さく、外見上は従来構造を持つパッケージを容易に実現することができ、加えて、動作が安定した半導体装置を得ることができ、ひいては安定して動作する電子機器を得ることができる。

【発明を実施するための最良の形態】

【0028】

(第1の実施形態)

本発明の第1の実施形態について図面を参照しながら説明する。

【0029】

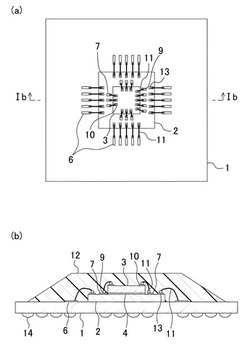

図1(a)及び(b)は本発明の第1の実施形態に係る半導体装置であって、(a)は模式的な平面構成を示し、(b)は(a)のIb−Ib線における断面構成を示している。

【0030】

図1(a)及び(b)に示すように、第1の実施形態に係る半導体装置は、例えば、内部に複数の配線層を有する樹脂材又はセラミック材等からなる配線基板1の主面上に、素子形成面を上にして固着された第1の半導体チップ2と、該第1の半導体チップ2の上に素子形成面を上にして接着材4により固着された第2の半導体チップ3とを有している。第1の半導体チップ2及び第2の半導体チップ3は、配線基板1の上に形成された封止樹脂材12によって封止されている。なお、図1(a)においては、封止樹脂材12を省略している。

【0031】

配線基板1の主面上には、第1の半導体チップ2の各側面と対向するように、複数の電極パッド6が形成され、配線基板1の主面と反対側の面には、複数の電極パッド6のいずれかと電気的に接続された複数の半田ボール14が形成されており、本実施形態に係る半導体装置はBGAパッケージである。なお、配線基板1をリードフレームに代えたQFPにも本発明は適用可能である。

【0032】

第1の半導体チップ2の素子形成面における第2の半導体チップ3と近い領域には該第2の半導体チップ3の各側面と対向するように、それぞれが平面長方形状の複数の内側電極パッド7が形成され、また、第1の半導体チップ2の素子形成面における周縁部には配線基板1の各電極パッド6と対向するように複数の外側電極パッド13が形成されている。

【0033】

第2の半導体チップ3の素子形成面には第1の半導体チップ2の各内側電極パッド7と対向するように、複数の電極パッド10が形成されている。

【0034】

第2の半導体チップ3の各電極パッド10は、第1の半導体チップ2の各内側電極パッド7と金属からなる突起部であるバンプ9を介在させてワイヤ11により電気的に接続されている。

【0035】

第1の半導体チップ2の各外側電極パッド13は、配線基板1の各電極パッド6とワイヤ11により電気的に接続されている。

【0036】

第1の実施形態の特徴として、第1の半導体チップ2に形成された内側電極パッド7は、図2(a)の拡大平面図に示すように平面長方形状を有している。ここで、各内側電極パッド7は、それぞれ長方形の短辺が第2の半導体チップ3の側面と対向するように配置される。

【0037】

一般に、半導体チップに対してプローブ検査を行う場合は、図2(a)及び(b)に示すように、検査プローブ15の先端部が内側電極パッド7のプローブ接触領域7aに対してオーバドライブされることにより、内側電極パッド7におけるプローブ接触領域7aの表面に線状のプローブ痕(接触痕)7cが残る。従って、図2(a)に示すように、内側電極パッド7の平面形状をプローブ痕7cが延びる方向に対して突起部形成領域7bが形成されるように長方形状とし、該突起部形成領域7bに金属からなるボール又はバンプを形成することにより、ボール又はバンプは内側電極パッド7を構成する金属との合金化を十分に図ることができる。

【0038】

しかしながら、内側電極パッド7の突起部形成領域7bを大きくすれば、該突起部形成領域7bとプローブ痕7cとが互いに重ならないようにすることは可能となるものの、そのようにすれば内側電極パッド7を形成する領域自体の面積が増大してしまう。

【0039】

そこで、本願発明者は、内側電極パッド7における長辺と短辺との比の値の最小値を検討した。以下、その検討結果を説明する。

【0040】

まず、[表1]に想定した電極パッドのサイズ及びボール(バンプ)径等の規格並びにプローブ痕7cのばらつき等を示す。

【0041】

【表1】

【0042】

図3はプローブ痕とボールの接合部とが重なった場合で、且つ引っ張り試験で接合部がはずれる前にワイヤが切れてしまう場合の、重なり部分の面積の最大値、すなわち合金化部分の面積の最小値を取る場合を示している。ここで、プローブ痕7cは、通常通り6回程度の測定が行われると仮定した場合の複数の線状痕である。

【0043】

図3から分かるように、この場合の合金化部分の面積は、1385.4μm2−523.7μm2=861.7μm2となる。ここで、1385.4μm2は、ボール径の規格の最小値である49μmの85%が接合するとしたときの接合面積であり、523.7μm2は、ボールの接合部とプローブ痕7cとの重なり部分の面積を計算した最大値である。

【0044】

さらに、内側パッド電極7は、ボールが内側パッド電極7からはみ出さない程度の幅寸法が必要なことから、電極パッドにおける長辺と短辺との比の値は、95μm/61μm≒1.56が最小値となる。

【0045】

従って、第1の実施形態に係る、テスト用電極パッドと接続用電極パッドを兼用する内側電極パッド7における長辺と短辺との比の値は1.5以上、さらには1.56以上が好ましい。このようにすると、内側電極パッド7にプローブ痕7cが残存し、金属からなるボール又はバンプがプローブ痕7cと重なる場合であっても、ボール又はバンプと内側電極パッド7との接合部は合金化が十分に図られるため、内側電極パッド7とボール又はバンプとの接続の信頼性が向上する。

【0046】

以下、前記のように構成された半導体装置の製造方法について図面を参照しながら説明する。

【0047】

図4(a)〜図4(d)及び図5(a)〜図5(d)は本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示している。

【0048】

まず、図4(a)に示すように、ウエハ状態にある第1の半導体チップ2にそれぞれ形成されている複数の内側電極パッド7と複数の外側パッド電極13とに検査プローブ15を接触させて、第1の半導体チップ2に形成された各素子の電気的特性を検査する。ここで、図2(a)に示したように、各検査プローブ15の先端部は、内側電極パッド7に対して第1の半導体チップ2の外側に位置する短辺側からプローブ接触領域7aに進入する。

【0049】

次に、図4(b)に示すように、ウエハ状態にある第1の半導体チップ2を複数の個片(ダイ)に切り出す。

【0050】

次に、図4(c)に示すように、複数の電極パッド6が形成された配線基板1の主面上に、第1の半導体チップ2を素子形成面を上にした状態で固着する。

【0051】

次に、図4(d)に示すように、第1の半導体チップ2の素子形成面上における内側電極パッド7よりも内側の領域に、第2の半導体チップ3をその素子形成面を上にした状態で接着材4によって固着する。

【0052】

次に、図5(a)に示すように、第1の半導体チップ2の外側電極パッド13と配線基板1の電極パッド6とを金(Au)からなるワイヤ11によりそれぞれ接続する。

【0053】

次に、図5(b)に示すように、第1の半導体チップ2の内側電極パッド7、すなわち図2(a)に示した内側電極パッド7の突起部形成領域に金(Au)からなるバンプ9それぞれを形成する。

【0054】

次に、図5(c)に示すように、一方の端部にボール11aを形成し、形成されたワイヤ11のボール11aを第2の半導体チップ3の電極パッド10と接続する。続いて、ワイヤ11の他方の端部を第1の半導体チップ2の内側電極パッド7に形成されたバンプ9と接続する。

【0055】

次に、図5(d)に示すように、配線基板1の主面上に封止樹脂材12を塗布することにより、各ワイヤ11を含め第1の半導体チップ2及び第2の半導体チップ3を封止樹脂材12によって覆う。

【0056】

以上の工程により、図1に示すBGA構成を採るSiPである半導体装置を得ることができる。

【0057】

なお、図5(b)及び図5(c)に示したように、第1の実施形態においては、第2の半導体チップ3から第1の半導体チップ2に向かってワイヤ11を接続する、いわゆる打ち下ろし法を用いたが、これとは逆に、第1の半導体チップ2から第2の半導体チップ3に向かってワイヤ11を接続する、いわゆる打ち上げ法を用いてもよい。但し、打ち上げ法を用いる場合には、先に第2の半導体チップの各電極パッド10にバンプ9を形成しておき、その後、第1の半導体チップ2における内側電極パッド7の突起部形成領域7bに、ワイヤ11の一方の端部に形成したボール11aを接続し、続いて、ワイヤ11の他方の端部を第2の半導体チップ3の電極パッド10に形成されたバンプ9と接続すればよい。このとき、第2の半導体チップ3の電極パッド10においても、その平面形状は、図2(a)に示した長方形状であることが好ましい。

【0058】

(第2の実施形態)

以下、本発明の第2の実施形態について図面を参照しながら説明する。

【0059】

図6は本発明の第2の実施形態に係る半導体装置の模式的な断面構成を示している。

【0060】

第2の実施形態においても、半導体装置としてBGAパッケージを想定しており、配線基板1に代えてリードフレームを用いたQFPとしてもよい。また、図6において、図1(a)及び(b)に付した符号と同一の構成部材には同一の符号を付すことにより説明を省略する。

【0061】

第2の実施形態においては、第2の半導体チップ3の素子形成面が第1の半導体チップ2の素子形成面と対向するように、アンダーフィル材17により固着されている。

【0062】

すなわち、第2の半導体チップ3と第1の半導体チップ2とは、第2の半導体チップ3の電極パッド10と第1の半導体チップ2の内側電極パッド7とがバンプ9を介在させた状態で電気的に接続されている。このとき、バンプ9は、第1の実施形態と同様に、第1の半導体チップ2における平面長方形状の内側電極パッド7の突起部形成領域7bに形成されている。

【0063】

なお、バンプ9は、第1の半導体チップ2の内側電極パッド7ではなく、第2の半導体チップ3の電極パッド10の上に形成することも可能である。このとき、第2の半導体チップ3の電極パッド10の平面形状は、図2(a)に示したように長方形状であることが好ましい。

【0064】

また、第1の実施形態及び第2の実施形態において、第2の半導体チップ3は、素子を含まず配線のみが形成されたシリコン(Si)からなるインターポーザであってもよい。

【0065】

また、図1及び図6は一例であって、第2の半導体チップ3に設けられた電極パッド10、第1の半導体チップ2に設けられた内側電極パッド7及び外側電極パッド13並びに配線基板1に設けられた電極パッド6は、必ずしもチップ又は基板の4辺に沿って設ける必要はない。また、各電極パッドは必ずしも直線状に設ける必要はなく、千鳥状に設けてもよいことはいうまでもない。

【0066】

以上説明したように、本発明に係る半導体装置によると、SiP構造を採ることにより半導体装置の小型化を図ることができるため、本発明に係る半導体装置を電子機器に搭載することにより実装面積を小さくすることが可能となるので、電子機器の小型化にも貢献できる。

【0067】

また、微細加工プロセスにより製造された多機能狭パッドピッチ化が図られた半導体チップを従来型のパッケージに搭載することが可能となるため、高コストな配線基板等を用いる必要がなくなるので、電子機器の高機能化を低コストで実現することが可能となる。

【産業上の利用可能性】

【0068】

本発明に係る半導体装置、半導体素子及びその検査方法は、金属からなる突起部と電極パッドとの合金化が十分になされるので、突起部における接続の信頼性が向上すると共に、高クロックレート信号を測定することが可能となり、従って、複数の半導体チップを搭載した半導体装置(例えば、SiP)等に有用である。

【図面の簡単な説明】

【0069】

【図1】(a)及び(b)は本発明の第1の実施形態に係る半導体装置を示し、(a)は模式的な平面図であり(但し、封止樹脂材は省略)、(b)は(a)のIb−Ib線における模式的な断面図である。

【図2】(a)は本発明に係るパッド電極のプローブ検査後の平面図であり、(b)はプローブ検査中の模式的な正面図である。

【図3】本発明に係るパッド電極の縦横比を検討する際の平面図である。

【図4】(a)〜(d)は本発明の第1の実施形態に係る半導体装置の製造方法を模式的に示し、(a)は平面図及びその部分的な正面図であり、(b)〜(d)は工程順の断面図である。

【図5】(a)〜(d)は本発明の第1の実施形態に係る半導体装置の製造方法を模式的に示す工程順の断面図である。

【図6】本発明の第2の実施形態に係る半導体装置を示す模式的な断面図である。

【符号の説明】

【0070】

1 配線基板

2 第1の半導体チップ

3 第2の半導体チップ

4 接着材

6 電極パッド

7 内側パッド電極

7a プローブ接触領域

7b 突起部形成領域

7c プローブ痕(接触痕)

9 バンプ(突起部)

10 電極パッド

11 ワイヤ(金属細線)

11a ボール(突起部)

12 封止樹脂材

13 外側電極パッド

14 半田ボール

15 検査プローブ

17 アンダーフィル材

【技術分野】

【0001】

本発明は、複数の半導体素子(半導体チップ)を搭載した半導体装置(例えば、システムインパッケージ)、該半導体装置を構成する半導体素子及びその検査方法に関する。

【背景技術】

【0002】

高鮮度及び高精細の動画処理を行う電子機器、例えばハイビジョンデジタルテレビは、小型化及び低コスト化を図るために、すべての機能を1つの半導体チップに集積化する方向が採られており、このため、半導体素子のウエハプロセスは微細化が進み、チップ面積が縮小化されている。

【0003】

一方、電子機器と半導体素子との接続は、従来の半導体素子用パッケージである、例えばQFP(Quad Flat Package)又はBGA(Ball Grid Array)パッケージ等を用いた従来の接続形態の要求が強く残っている。このため、パッケージ内の配線電極と半導体素子のパッド電極との間の製造規格のギャップが大きくなりつつある。

【0004】

また、電子機器に組み込まれる半導体装置も、配線基板に実装する実装面積の縮小化のため小型化が求められている。これらを解決する方法の1つとして複数の半導体チップを1つにパッケージする構成、例えばシステムインパッケージ(System in Package、以下、SiPと呼ぶ。)構造が採られるようになってきている。このSiPは例えば下記のような構成を持つ。

【0005】

すなわち、SiPは、基板(実装用基板)と、該基板の主面上に素子形成面を上にして固着された第1の半導体チップと、該第1の半導体チップの上に素子形成面を上にして固着された第2の半導体チップとを有している。さらに、第1の半導体素子の素子形成面に形成された電極パッドと基板に形成された電極パッドとが金属細線によって接続され、第2の半導体素子の素子形成面に形成された電極パッドと、基板に形成された電極パッド又は第1の半導体チップに形成された電極パッドとが金属細線によって接続されている。また、第1の半導体チップと第2の半導体チップとはモールド樹脂体により覆われている。

【0006】

SiPは、既存のプローブテスト用装置又は設備を用いて、配線基板として用いられる半導体チップのオープンショートテストを行うことができ、テストコストを削減可能な積層型SiP構造を採る半導体装置として以下の構造が提案されている。

【0007】

配線基板として用いられる第1の半導体チップの上には、第2の半導体チップが固着され、第2の半導体チップの上には第3の半導体チップが固着されており、第2の半導体チップの素子形成面には、外周部電極パッドと、その内側に配置され且つ外周部電極パッドと配線を介して接続され、第3の半導体チップの電極パッドと接続される中央部電極パッドと、第2の半導体チップの外周部に配置され、中央部電極パッドと配線を介して接続されたテスト用電極パッドとが形成されている(例えば、特許文献1を参照。)。

【特許文献1】特開2004−253609号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

ところで、SiPにおいては、チップ同士を金属細線(以下、ワイヤと呼ぶ。)又は金属からなる突起部(以下、バンプと呼ぶ。)によって電気的に接続する必要がある。

【0009】

狭パッドピッチ構造において、ワイヤを用いて接続する場合を想定すると、チップ同士を接続するワイヤのステッチ側(第2ボンド部)には電極パッドの上にバンプを形成する必要がある。また、ワイヤの接続開始側である、いわゆる第1ボンド部にもワイヤの端部に金属ボールを形成する必要がある。このとき、電極パッドにおける金属ボール又はバンプとの接続部分に、プローブテストの際に付けられたプローブ痕(接触痕)が残存すると、金属ボール又はバンプと電極パッドとの間に十分な強度を有する合金部が形成されない場合がある。このため、プローブテスト時のプローブの接触部分とワイヤ先端の金属ボール又はバンプとの接続部分を分離することが、パッドサイズが小さい狭パッドピッチ構造の接続には必須となる。

【0010】

従って、例えば特許文献1等に記載された従来例は、テスト用電極パッドとワイヤ接続用の電極パッドとを分離して形成していることから、ワイヤ接続用の電極パッドと金属ボール又はバンプとの間の合金部の形成には問題がない。

【0011】

しかしながら、本従来例においては、テスト用電極パッドは、接続用の電極パッドから細い配線によって接続されているため、配線の抵抗及び容量の影響により信号に遅延が生じてしまい、高クロックレートを要求される信号を測定することは困難である。このため、本従来例に示されているように、オープンショートテスト程度にしか活用できないという問題がある。

【0012】

また、接続用の電極パッドとテスト用電極パッドとの配線が断線していた場合は、良否判定自体が行えないという問題も生じる。

【0013】

さらには、テスト用電極パッドと、該テスト用電極パッドと接続用の電極パッドとを接続する新たな配線とを設ける必要から、半導体チップにおける配線の自由度が制限されたり、余分なチップ面積が要求されたりして、特性劣化さらにはコストの上昇を招くおそれがある。

【0014】

本発明は、前記従来の問題を解決し、テスト用電極パッドを設けることなく、電極パッドと該電極パッドの上に設ける金属ボール又は金属突起との合金化を確実に図れるようにすることを目的とする。

【課題を解決するための手段】

【0015】

前記の目的を達成するため、本発明は、半導体装置における電極パッドの平面形状を長方形とすることにより、電極パッドにおけるプローブの接触痕とバンプ等の金属突起部の形成位置との重なり部分を小さくする構成とする。

【0016】

具体的に、本発明に係る第1の半導体装置は、チップ状の第1の半導体素子と、第1の半導体素子の上に、第1の半導体素子の少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を上にして固着されたチップ状の第2の半導体素子とを備え、第1の半導体素子は、第2の半導体素子の側面に沿って形成された複数の第1の電極パッドを有し、第1の電極パッドの上には金属からなる突起部が形成されており、第2の半導体素子は、素子形成面に形成された複数の第2の電極パッドを有し、各第2の電極パッドと各第1の電極パッドの突起部とはそれぞれ第1の金属細線により接続され、第1の電極パッドは平面長方形状を有していることを特徴とする。

【0017】

第1の半導体装置によると、第1の電極パッドは平面長方形状を有しているため、検査時のプローブ痕と金属からなる突起部との形成位置を分離するか又は互いの重なり部分を小さくすることができる。これにより、金属からなる突起部と第1の電極パッドとの合金化が十分になされるので、金属細線による接続の信頼性が向上する。その上、電極パッドの他にテスト用電極パッドを設けないため、電極パッドとテスト用電極パッドとの間の配線の抵抗及び容量の影響がなくなるので、信号遅延を排除して高クロックレート信号を測定することができる。

【0018】

第1の半導体装置は、上面に第1の半導体素子を固着すると共に第3の電極パッドを有する半導体基板、又は上面に第1の半導体素子を固着すると共に電極を有するリードフレームをさらに備え、第3の電極パッドは、複数の第1の電極パッドの一部又は複数の第2の電極パッドの一部と第2の金属細線により接続され、又はリードフレームの電極は、複数の第1の電極パッドの一部又は複数の第2の電極パッドの一部と第2の金属細線により接続されることが好ましい。

【0019】

本発明に係る第2の半導体装置は、チップ状の第1の半導体素子と、第1の半導体素子の上に、第1の半導体素子の少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を下にして固着されたチップ状の第2の半導体素子とを備え、第1の半導体素子は、第2の半導体素子の素子形成面と対向する位置に形成された複数の第1の電極パッドを有し、第1の電極パッドの上には金属からなる突起部が形成されており、第2の半導体素子は、第1の半導体素子の複数の第1の電極パッドと接続される複数の第2の電極パッドを有し、第1の電極パッドは平面長方形状を有していることを特徴とする。

【0020】

第2の半導体装置によると、第1の電極パッドは平面長方形状を有しているため、検査時のプローブ痕と金属からなる突起部との形成位置を分離するか又は互いの重なり部分を小さくすることができる。これにより、金属からなる突起部と第1の電極パッドとの合金化が十分になされるので、突起部と第1の電極パッドとの間の接続の信頼性が向上する。その上、電極パッドの他にテスト用電極パッドを設けないため、電極パッドとテスト用電極パッドとの間の配線の抵抗及び容量の影響がなくなるので、信号遅延を排除して高クロックレート信号を測定することができる。

【0021】

第2の半導体装置は、上面に第1の半導体素子を固着すると共に第3の電極パッドを有する半導体基板、又は上面に第1の半導体素子を固着すると共に電極を有するリードフレームをさらに備え、第3の電極パッド又はリードフレームの電極は、複数の第1の電極パッドの一部と金属細線により接続されることが好ましい。

【0022】

第1又は第2の半導体装置において、第1の電極パッドにおける長辺の長さは、短辺の長さの1.5倍以上であることが好ましい。

【0023】

第1又は第2の半導体装置において、第1の電極パッドには、長辺に沿って検査プローブによる接触痕が残存しており、突起部は、接触痕の一部の上に形成されていることが好ましい。

【0024】

本発明に係る半導体素子は、素子形成面にそれぞれ平面長方形状の複数の電極パッドを備え、電極パッドにおける長辺の長さは、短辺の長さの1.5倍以上であることを特徴とする。

【0025】

本発明の半導体素子によると、電極パッドは平面長方形状を有しているため、電極パッドの上に、バンプ又は金属ボールからなる突起部を形成する際に、検査時のプローブ痕と突起部との形成位置を分離するか又は互いの重なり部分を小さくすることができる。これにより、突起部と電極パッドとの合金化が十分になされるので、金属細線による接続の信頼性が向上する。その上、電極パッドの他にテスト用電極パッドを設けないため、電極パッドとテスト用電極パッドとの間の配線の抵抗及び容量の影響がなくなるので、信号遅延を排除して高クロックレート信号を測定することができる。

【0026】

本発明に係る半導体素子の電気的特性を検査する検査方法を対象とし、平面長方形状の電極パッドに、検査用の検査プローブを接触させる際に、電極パッドにおける短辺側の領域に、検査プローブを接触させることを特徴とする。

【発明の効果】

【0027】

本発明に係る半導体装置、半導体素子及びそれを用いた検査方法によると、金属からなる突起部と電極パッドとの合金化が十分になされるので、突起部における接続の信頼性が向上する。その上、テスト用電極パッドを設けないことから、電極パッドとテスト用電極パッドとの間の配線の抵抗及び容量の影響がなくなるので、高クロックレート信号を測定することができる。これにより、狭パッドピッチのワイヤ接続用の電極パッドを有する高コストな配線基板又はリードフレームを用いることなく、従来構成のパッケージを用いることができる。従って、チップ同士又はチップと配線基板等の接続の信頼性が高く、伝送電気信号歪みが小さく、外見上は従来構造を持つパッケージを容易に実現することができ、加えて、動作が安定した半導体装置を得ることができ、ひいては安定して動作する電子機器を得ることができる。

【発明を実施するための最良の形態】

【0028】

(第1の実施形態)

本発明の第1の実施形態について図面を参照しながら説明する。

【0029】

図1(a)及び(b)は本発明の第1の実施形態に係る半導体装置であって、(a)は模式的な平面構成を示し、(b)は(a)のIb−Ib線における断面構成を示している。

【0030】

図1(a)及び(b)に示すように、第1の実施形態に係る半導体装置は、例えば、内部に複数の配線層を有する樹脂材又はセラミック材等からなる配線基板1の主面上に、素子形成面を上にして固着された第1の半導体チップ2と、該第1の半導体チップ2の上に素子形成面を上にして接着材4により固着された第2の半導体チップ3とを有している。第1の半導体チップ2及び第2の半導体チップ3は、配線基板1の上に形成された封止樹脂材12によって封止されている。なお、図1(a)においては、封止樹脂材12を省略している。

【0031】

配線基板1の主面上には、第1の半導体チップ2の各側面と対向するように、複数の電極パッド6が形成され、配線基板1の主面と反対側の面には、複数の電極パッド6のいずれかと電気的に接続された複数の半田ボール14が形成されており、本実施形態に係る半導体装置はBGAパッケージである。なお、配線基板1をリードフレームに代えたQFPにも本発明は適用可能である。

【0032】

第1の半導体チップ2の素子形成面における第2の半導体チップ3と近い領域には該第2の半導体チップ3の各側面と対向するように、それぞれが平面長方形状の複数の内側電極パッド7が形成され、また、第1の半導体チップ2の素子形成面における周縁部には配線基板1の各電極パッド6と対向するように複数の外側電極パッド13が形成されている。

【0033】

第2の半導体チップ3の素子形成面には第1の半導体チップ2の各内側電極パッド7と対向するように、複数の電極パッド10が形成されている。

【0034】

第2の半導体チップ3の各電極パッド10は、第1の半導体チップ2の各内側電極パッド7と金属からなる突起部であるバンプ9を介在させてワイヤ11により電気的に接続されている。

【0035】

第1の半導体チップ2の各外側電極パッド13は、配線基板1の各電極パッド6とワイヤ11により電気的に接続されている。

【0036】

第1の実施形態の特徴として、第1の半導体チップ2に形成された内側電極パッド7は、図2(a)の拡大平面図に示すように平面長方形状を有している。ここで、各内側電極パッド7は、それぞれ長方形の短辺が第2の半導体チップ3の側面と対向するように配置される。

【0037】

一般に、半導体チップに対してプローブ検査を行う場合は、図2(a)及び(b)に示すように、検査プローブ15の先端部が内側電極パッド7のプローブ接触領域7aに対してオーバドライブされることにより、内側電極パッド7におけるプローブ接触領域7aの表面に線状のプローブ痕(接触痕)7cが残る。従って、図2(a)に示すように、内側電極パッド7の平面形状をプローブ痕7cが延びる方向に対して突起部形成領域7bが形成されるように長方形状とし、該突起部形成領域7bに金属からなるボール又はバンプを形成することにより、ボール又はバンプは内側電極パッド7を構成する金属との合金化を十分に図ることができる。

【0038】

しかしながら、内側電極パッド7の突起部形成領域7bを大きくすれば、該突起部形成領域7bとプローブ痕7cとが互いに重ならないようにすることは可能となるものの、そのようにすれば内側電極パッド7を形成する領域自体の面積が増大してしまう。

【0039】

そこで、本願発明者は、内側電極パッド7における長辺と短辺との比の値の最小値を検討した。以下、その検討結果を説明する。

【0040】

まず、[表1]に想定した電極パッドのサイズ及びボール(バンプ)径等の規格並びにプローブ痕7cのばらつき等を示す。

【0041】

【表1】

【0042】

図3はプローブ痕とボールの接合部とが重なった場合で、且つ引っ張り試験で接合部がはずれる前にワイヤが切れてしまう場合の、重なり部分の面積の最大値、すなわち合金化部分の面積の最小値を取る場合を示している。ここで、プローブ痕7cは、通常通り6回程度の測定が行われると仮定した場合の複数の線状痕である。

【0043】

図3から分かるように、この場合の合金化部分の面積は、1385.4μm2−523.7μm2=861.7μm2となる。ここで、1385.4μm2は、ボール径の規格の最小値である49μmの85%が接合するとしたときの接合面積であり、523.7μm2は、ボールの接合部とプローブ痕7cとの重なり部分の面積を計算した最大値である。

【0044】

さらに、内側パッド電極7は、ボールが内側パッド電極7からはみ出さない程度の幅寸法が必要なことから、電極パッドにおける長辺と短辺との比の値は、95μm/61μm≒1.56が最小値となる。

【0045】

従って、第1の実施形態に係る、テスト用電極パッドと接続用電極パッドを兼用する内側電極パッド7における長辺と短辺との比の値は1.5以上、さらには1.56以上が好ましい。このようにすると、内側電極パッド7にプローブ痕7cが残存し、金属からなるボール又はバンプがプローブ痕7cと重なる場合であっても、ボール又はバンプと内側電極パッド7との接合部は合金化が十分に図られるため、内側電極パッド7とボール又はバンプとの接続の信頼性が向上する。

【0046】

以下、前記のように構成された半導体装置の製造方法について図面を参照しながら説明する。

【0047】

図4(a)〜図4(d)及び図5(a)〜図5(d)は本発明の第1の実施形態に係る半導体装置の製造方法を工程順に示している。

【0048】

まず、図4(a)に示すように、ウエハ状態にある第1の半導体チップ2にそれぞれ形成されている複数の内側電極パッド7と複数の外側パッド電極13とに検査プローブ15を接触させて、第1の半導体チップ2に形成された各素子の電気的特性を検査する。ここで、図2(a)に示したように、各検査プローブ15の先端部は、内側電極パッド7に対して第1の半導体チップ2の外側に位置する短辺側からプローブ接触領域7aに進入する。

【0049】

次に、図4(b)に示すように、ウエハ状態にある第1の半導体チップ2を複数の個片(ダイ)に切り出す。

【0050】

次に、図4(c)に示すように、複数の電極パッド6が形成された配線基板1の主面上に、第1の半導体チップ2を素子形成面を上にした状態で固着する。

【0051】

次に、図4(d)に示すように、第1の半導体チップ2の素子形成面上における内側電極パッド7よりも内側の領域に、第2の半導体チップ3をその素子形成面を上にした状態で接着材4によって固着する。

【0052】

次に、図5(a)に示すように、第1の半導体チップ2の外側電極パッド13と配線基板1の電極パッド6とを金(Au)からなるワイヤ11によりそれぞれ接続する。

【0053】

次に、図5(b)に示すように、第1の半導体チップ2の内側電極パッド7、すなわち図2(a)に示した内側電極パッド7の突起部形成領域に金(Au)からなるバンプ9それぞれを形成する。

【0054】

次に、図5(c)に示すように、一方の端部にボール11aを形成し、形成されたワイヤ11のボール11aを第2の半導体チップ3の電極パッド10と接続する。続いて、ワイヤ11の他方の端部を第1の半導体チップ2の内側電極パッド7に形成されたバンプ9と接続する。

【0055】

次に、図5(d)に示すように、配線基板1の主面上に封止樹脂材12を塗布することにより、各ワイヤ11を含め第1の半導体チップ2及び第2の半導体チップ3を封止樹脂材12によって覆う。

【0056】

以上の工程により、図1に示すBGA構成を採るSiPである半導体装置を得ることができる。

【0057】

なお、図5(b)及び図5(c)に示したように、第1の実施形態においては、第2の半導体チップ3から第1の半導体チップ2に向かってワイヤ11を接続する、いわゆる打ち下ろし法を用いたが、これとは逆に、第1の半導体チップ2から第2の半導体チップ3に向かってワイヤ11を接続する、いわゆる打ち上げ法を用いてもよい。但し、打ち上げ法を用いる場合には、先に第2の半導体チップの各電極パッド10にバンプ9を形成しておき、その後、第1の半導体チップ2における内側電極パッド7の突起部形成領域7bに、ワイヤ11の一方の端部に形成したボール11aを接続し、続いて、ワイヤ11の他方の端部を第2の半導体チップ3の電極パッド10に形成されたバンプ9と接続すればよい。このとき、第2の半導体チップ3の電極パッド10においても、その平面形状は、図2(a)に示した長方形状であることが好ましい。

【0058】

(第2の実施形態)

以下、本発明の第2の実施形態について図面を参照しながら説明する。

【0059】

図6は本発明の第2の実施形態に係る半導体装置の模式的な断面構成を示している。

【0060】

第2の実施形態においても、半導体装置としてBGAパッケージを想定しており、配線基板1に代えてリードフレームを用いたQFPとしてもよい。また、図6において、図1(a)及び(b)に付した符号と同一の構成部材には同一の符号を付すことにより説明を省略する。

【0061】

第2の実施形態においては、第2の半導体チップ3の素子形成面が第1の半導体チップ2の素子形成面と対向するように、アンダーフィル材17により固着されている。

【0062】

すなわち、第2の半導体チップ3と第1の半導体チップ2とは、第2の半導体チップ3の電極パッド10と第1の半導体チップ2の内側電極パッド7とがバンプ9を介在させた状態で電気的に接続されている。このとき、バンプ9は、第1の実施形態と同様に、第1の半導体チップ2における平面長方形状の内側電極パッド7の突起部形成領域7bに形成されている。

【0063】

なお、バンプ9は、第1の半導体チップ2の内側電極パッド7ではなく、第2の半導体チップ3の電極パッド10の上に形成することも可能である。このとき、第2の半導体チップ3の電極パッド10の平面形状は、図2(a)に示したように長方形状であることが好ましい。

【0064】

また、第1の実施形態及び第2の実施形態において、第2の半導体チップ3は、素子を含まず配線のみが形成されたシリコン(Si)からなるインターポーザであってもよい。

【0065】

また、図1及び図6は一例であって、第2の半導体チップ3に設けられた電極パッド10、第1の半導体チップ2に設けられた内側電極パッド7及び外側電極パッド13並びに配線基板1に設けられた電極パッド6は、必ずしもチップ又は基板の4辺に沿って設ける必要はない。また、各電極パッドは必ずしも直線状に設ける必要はなく、千鳥状に設けてもよいことはいうまでもない。

【0066】

以上説明したように、本発明に係る半導体装置によると、SiP構造を採ることにより半導体装置の小型化を図ることができるため、本発明に係る半導体装置を電子機器に搭載することにより実装面積を小さくすることが可能となるので、電子機器の小型化にも貢献できる。

【0067】

また、微細加工プロセスにより製造された多機能狭パッドピッチ化が図られた半導体チップを従来型のパッケージに搭載することが可能となるため、高コストな配線基板等を用いる必要がなくなるので、電子機器の高機能化を低コストで実現することが可能となる。

【産業上の利用可能性】

【0068】

本発明に係る半導体装置、半導体素子及びその検査方法は、金属からなる突起部と電極パッドとの合金化が十分になされるので、突起部における接続の信頼性が向上すると共に、高クロックレート信号を測定することが可能となり、従って、複数の半導体チップを搭載した半導体装置(例えば、SiP)等に有用である。

【図面の簡単な説明】

【0069】

【図1】(a)及び(b)は本発明の第1の実施形態に係る半導体装置を示し、(a)は模式的な平面図であり(但し、封止樹脂材は省略)、(b)は(a)のIb−Ib線における模式的な断面図である。

【図2】(a)は本発明に係るパッド電極のプローブ検査後の平面図であり、(b)はプローブ検査中の模式的な正面図である。

【図3】本発明に係るパッド電極の縦横比を検討する際の平面図である。

【図4】(a)〜(d)は本発明の第1の実施形態に係る半導体装置の製造方法を模式的に示し、(a)は平面図及びその部分的な正面図であり、(b)〜(d)は工程順の断面図である。

【図5】(a)〜(d)は本発明の第1の実施形態に係る半導体装置の製造方法を模式的に示す工程順の断面図である。

【図6】本発明の第2の実施形態に係る半導体装置を示す模式的な断面図である。

【符号の説明】

【0070】

1 配線基板

2 第1の半導体チップ

3 第2の半導体チップ

4 接着材

6 電極パッド

7 内側パッド電極

7a プローブ接触領域

7b 突起部形成領域

7c プローブ痕(接触痕)

9 バンプ(突起部)

10 電極パッド

11 ワイヤ(金属細線)

11a ボール(突起部)

12 封止樹脂材

13 外側電極パッド

14 半田ボール

15 検査プローブ

17 アンダーフィル材

【特許請求の範囲】

【請求項1】

チップ状の第1の半導体素子と、

前記第1の半導体素子の上に、前記第1の半導体素子の少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を上にして固着されたチップ状の第2の半導体素子とを備え、

前記第1の半導体素子は、前記第2の半導体素子の側面に沿って形成された複数の第1の電極パッドを有し、前記第1の電極パッドの上には金属からなる突起部が形成されており、

前記第2の半導体素子は、前記素子形成面に形成された複数の第2の電極パッドを有し、

前記各第2の電極パッドと前記各第1の電極パッドの前記突起部とはそれぞれ第1の金属細線により接続され、

前記第1の電極パッドは平面長方形状を有していることを特徴とする半導体装置。

【請求項2】

上面に前記第1の半導体素子を固着すると共に第3の電極パッドを有する半導体基板、又は上面に前記第1の半導体素子を固着すると共に電極を有するリードフレームをさらに備え、

前記第3の電極パッドは、前記複数の第1の電極パッドの一部又は前記複数の第2の電極パッドの一部と第2の金属細線により接続され、

又は前記リードフレームの電極は、前記複数の第1の電極パッドの一部又は前記複数の第2の電極パッドの一部と第2の金属細線により接続されることを特徴とする請求項1に記載の半導体装置。

【請求項3】

チップ状の第1の半導体素子と、

前記第1の半導体素子の上に、前記第1の半導体素子の少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を下にして固着されたチップ状の第2の半導体素子とを備え、

前記第1の半導体素子は、前記第2の半導体素子の前記素子形成面と対向する位置に形成された複数の第1の電極パッドを有し、前記第1の電極パッドの上には金属からなる突起部が形成されており、

前記第2の半導体素子は、前記第1の半導体素子の前記複数の第1の電極パッドと接続される複数の第2の電極パッドを有し、

前記第1の電極パッドは平面長方形状を有していることを特徴とする半導体装置。

【請求項4】

上面に前記第1の半導体素子を固着すると共に第3の電極パッドを有する半導体基板、又は上面に前記第1の半導体素子を固着すると共に電極を有するリードフレームをさらに備え、

前記第3の電極パッド又は前記リードフレームの電極は、前記複数の第1の電極パッドの一部と金属細線により接続されることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第1の電極パッドにおける長辺の長さは、短辺の長さの1.5倍以上であることを特徴とする請求項1〜4のいずれか1項に記載の半導体装置。

【請求項6】

前記第1の電極パッドには、長辺に沿って検査プローブによる接触痕が残存しており、

前記突起部は、前記接触痕の一部の上に形成されていることを特徴とする請求項1〜5のいずれか1項に記載の半導体装置。

【請求項7】

素子形成面にそれぞれ平面長方形状の複数の電極パッドを備え、

前記電極パッドにおける長辺の長さは、短辺の長さの1.5倍以上であることを特徴とする半導体素子。

【請求項8】

請求項7に記載の半導体素子の電気的特性を検査する検査方法であって、

平面長方形状の前記電極パッドに、検査用の検査プローブを接触させる際に、前記電極パッドにおける短辺側の領域に、前記検査プローブを接触させることを特徴とする半導体素子の検査方法。

【請求項1】

チップ状の第1の半導体素子と、

前記第1の半導体素子の上に、前記第1の半導体素子の少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を上にして固着されたチップ状の第2の半導体素子とを備え、

前記第1の半導体素子は、前記第2の半導体素子の側面に沿って形成された複数の第1の電極パッドを有し、前記第1の電極パッドの上には金属からなる突起部が形成されており、

前記第2の半導体素子は、前記素子形成面に形成された複数の第2の電極パッドを有し、

前記各第2の電極パッドと前記各第1の電極パッドの前記突起部とはそれぞれ第1の金属細線により接続され、

前記第1の電極パッドは平面長方形状を有していることを特徴とする半導体装置。

【請求項2】

上面に前記第1の半導体素子を固着すると共に第3の電極パッドを有する半導体基板、又は上面に前記第1の半導体素子を固着すると共に電極を有するリードフレームをさらに備え、

前記第3の電極パッドは、前記複数の第1の電極パッドの一部又は前記複数の第2の電極パッドの一部と第2の金属細線により接続され、

又は前記リードフレームの電極は、前記複数の第1の電極パッドの一部又は前記複数の第2の電極パッドの一部と第2の金属細線により接続されることを特徴とする請求項1に記載の半導体装置。

【請求項3】

チップ状の第1の半導体素子と、

前記第1の半導体素子の上に、前記第1の半導体素子の少なくとも1つの側面から内側に間隔をおいて、且つ素子形成面を下にして固着されたチップ状の第2の半導体素子とを備え、

前記第1の半導体素子は、前記第2の半導体素子の前記素子形成面と対向する位置に形成された複数の第1の電極パッドを有し、前記第1の電極パッドの上には金属からなる突起部が形成されており、

前記第2の半導体素子は、前記第1の半導体素子の前記複数の第1の電極パッドと接続される複数の第2の電極パッドを有し、

前記第1の電極パッドは平面長方形状を有していることを特徴とする半導体装置。

【請求項4】

上面に前記第1の半導体素子を固着すると共に第3の電極パッドを有する半導体基板、又は上面に前記第1の半導体素子を固着すると共に電極を有するリードフレームをさらに備え、

前記第3の電極パッド又は前記リードフレームの電極は、前記複数の第1の電極パッドの一部と金属細線により接続されることを特徴とする請求項3に記載の半導体装置。

【請求項5】

前記第1の電極パッドにおける長辺の長さは、短辺の長さの1.5倍以上であることを特徴とする請求項1〜4のいずれか1項に記載の半導体装置。

【請求項6】

前記第1の電極パッドには、長辺に沿って検査プローブによる接触痕が残存しており、

前記突起部は、前記接触痕の一部の上に形成されていることを特徴とする請求項1〜5のいずれか1項に記載の半導体装置。

【請求項7】

素子形成面にそれぞれ平面長方形状の複数の電極パッドを備え、

前記電極パッドにおける長辺の長さは、短辺の長さの1.5倍以上であることを特徴とする半導体素子。

【請求項8】

請求項7に記載の半導体素子の電気的特性を検査する検査方法であって、

平面長方形状の前記電極パッドに、検査用の検査プローブを接触させる際に、前記電極パッドにおける短辺側の領域に、前記検査プローブを接触させることを特徴とする半導体素子の検査方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2010−67913(P2010−67913A)

【公開日】平成22年3月25日(2010.3.25)

【国際特許分類】

【出願番号】特願2008−235171(P2008−235171)

【出願日】平成20年9月12日(2008.9.12)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成22年3月25日(2010.3.25)

【国際特許分類】

【出願日】平成20年9月12日(2008.9.12)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]