半導体装置、半導体装置の製造方法、基板処理システムおよびプログラム

【課題】閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜30と、ゲート絶縁膜上に形成されたTiN膜41と、TiN膜41上に形成されたTiAlN膜43と、TiAlN膜43上に形成されたシリコン膜45と、を有する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜30と、ゲート絶縁膜上に形成されたTiN膜41と、TiN膜41上に形成されたTiAlN膜43と、TiAlN膜43上に形成されたシリコン膜45と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、半導体装置の製造方法、基板処理システムおよびプログラムに関し、特に、MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)、その製造方法、基板処理システムおよびプログラムに関する。

【背景技術】

【0002】

MOSFETの高集積化及び高性能化に合わせて、ゲート絶縁膜の薄膜化(EOT(Effective Oxide Thickness)スケーリング化)が行われている。従来、ゲート絶縁膜にはSiO2膜が用いられてきたが、ゲート絶縁膜を薄膜化していくとゲートリーク電流の増大が顕著となる。そこで、ゲートリーク電流を低減するために、現在は、SiO2膜よりも高い誘電率を有する絶縁膜(High-k絶縁膜)がゲート絶縁膜に適用され始めている。その中でも、HfO2膜が有望視されている。一方、ゲート電極材料としては、従来は多結晶シリコン(Poly-Si)が用いられてきたが、多結晶シリコン電極を使用すると、空乏化層が形成されその分実効的なゲート絶縁膜の厚さが厚くなってしまい、ゲート絶縁膜の薄膜化に反してしまう。そこで、空乏化層が生じない金属(メタル)材料をゲート電極に使用することが検討されている。

【0003】

近年、このような金属ゲート電極とHigh-kゲート絶縁膜とを用いたMOSFETスタック構造であって、ゲート絶縁膜と多結晶シリコンゲート電極との間に金属ゲート電極を挿入したMIPS (Metal Inserted Poly Silicon)構造のゲート電極を用い、ゲート電極形成後にソース/ドレイン領域の活性化アニールを行うゲートファーストプロセスが注目されている(非特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【非特許文献1】"A Highly Manufacturable MIPS (Metal Inserted Poly-Si Stack) Technology with Novel Threshold Voltage Control" 2005 Symposium on VLSI Technology Digest of Technical Papers pp. 232-233

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、このMIPS構造では、ソース/ドレイン領域の活性化アニール中に、多結晶シリコン中のSiが金属膜を通過して金属電極とHigh-kゲート絶縁膜との界面にまで到達し、フェルミレベルピニングと呼ばれる現象を引き起こし、閾値電圧が上昇する(フラットバンド電圧が低下する)という問題があった。

【0006】

本発明の主な目的は、閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置、半導体装置の製造方法、当該半導体装置の製造に好適に使用される基板処理システム、および当該基板処理システムで好適に使用されるプログラムを提供することにある。

【課題を解決するための手段】

【0007】

本発明の一態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の第1の金属含有膜と、

前記第1の金属含有膜上に形成され、アルミニウムを添加してなる導電性の第2の金属含有膜と、

前記第2の金属含有膜上に形成されたシリコン膜と、

を有する半導体装置が提供される。

【0008】

本発明の他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する工程と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する工程と、

前記第2の金属含有膜上にシリコン膜を形成する工程と、

を有する半導体装置の製造方法が提供される。

【0009】

本発明のさらに他の態様によれば、

半導体基板上にゲート絶縁膜を形成する第1の処理部と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する第2の処理部と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する第3の処理部と、

前記第2の金属含有膜上にシリコン膜を形成する第4の処理部と、

を有する基板処理システムが提供される。

【0010】

本発明のさらに他の態様によれば、

基板処理システムの第1の処理部で半導体基板上にゲート絶縁膜を形成する手順と、

前記基板処理システムの第2の処理部で前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する手順と、

前記基板処理システムの第3の処理部で前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する手順と、

前記基板処理システムの第4の処理部で前記第2の金属含有膜上にシリコン膜を形成する手順と、

をコンピュータに実行させるためのプログラムが提供される。

【発明の効果】

【0011】

本発明によれば、閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置、半導体装置の製造方法、当該半導体装置の製造に好適に使用される基板処理システム、および当該基板処理システムで好適に使用されるプログラムが提供される。

【図面の簡単な説明】

【0012】

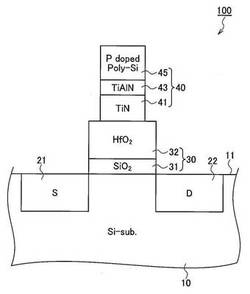

【図1】図1は、本発明の好ましい一実施の形態のMOSFETを説明するための概略縦断面図である。

【図2】図2は、本発明の好ましい一実施の形態のMOSFETの製造方法を説明するためのフローチャートである。

【図3】図3は、本発明の好ましい一実施の形態のMOSFETを説明するための概略縦断面図である。

【図4】図4は、本発明の好ましい一実施の形態のMOSFET用の評価サンプルを説明するための概略縦断面図である。

【図5】図5は、比較例のMOSFET用の評価サンプルを説明するための概略縦断面図である。

【図6】図6は、比較例のMOSFET用の評価サンプルの製造方法を説明するためのフローチャートである。

【図7】図7は、本発明の好ましい一実施の形態のMOSFET用の評価サンプルのC−V特性の図である。

【図8】図8は、比較例のMOSFET用の評価サンプルのC−V特性の図である。

【図9】図9は、本発明の好ましい一実施の形態のMOSFET用の評価サンプルと、比較例のMOSFET用の評価サンプルの、EOT(等価酸化膜厚)とVfb(フラットバンド電圧)を示す表である。

【図10】図10は、他の比較例のMOSFET用の評価サンプルを説明するための概略縦断面図である。

【図11】図11は、本発明の好ましい他の実施の形態のMOSFETを説明するための概略縦断面図である。

【図12】図12は、本発明の好ましい一実施の形態のMOSFETを製造する際に好適に使用されるクラスタ装置の一例を説明するための概略図である。

【図13】図13は、図12、図14のクラスタ装置に使用されるコントローラを説明するための概略図である。

【図14】図14は、本発明の好ましい一実施の形態のMOSFETを製造する際に好適に使用されるクラスタ装置の他の例を説明するための概略図である。

【発明を実施するための形態】

【0013】

以下、本発明の好ましい実施の形態について図面を参照しながら説明する。

【0014】

図1を参照すれば、本発明の好ましい一実施の形態の半導体装置(デバイス)としてのMOSFET100は、半導体基板であるシリコン基板10と、シリコン基板10の一主面11の表面に設けられたゲート絶縁膜30と、ゲート絶縁膜30上に設けられたゲート電極40と、ゲート電極40の両側のシリコン基板10の一主面11にそれぞれ設けられたソース領域21およびドレイン領域22とを備えている。

【0015】

ゲート絶縁膜30は、シリコン基板10の一主面11上に設けられたSiO2膜31とSiO2膜31上に設けられた高誘電率(High-k)絶縁膜であるHfO2膜32とを備えている。高誘電率絶縁膜であるHfO2膜32を使用することにより、ゲートリーク電流を低減している。

【0016】

ゲート電極40は、ゲート絶縁膜30のHfO2膜32上に設けられたTiN膜41と、TiN膜41上に設けられたTiAlN膜43と、TiAlN膜43上に設けられたPをドーピングした多結晶シリコン膜(P Doped Poly−Si膜)45とを備えている。HfO2膜32上に金属膜であるTiN膜41を使用しているので、空乏化層が生じることはなく、実効的なゲート絶縁膜の厚さが厚くなってしまうことを防止している。また、多結晶シリコン膜45とTiN膜41との間にTiAlN膜43を設けているので、ゲート電極40の形成後にソース領域21およびドレイン領域22の活性化アニールを行う際に、多結晶シリコン膜45中のSiが金属膜であるTiN膜41中に拡散するのを防止できる。その結果、多結晶シリコン膜45中のSiがTiN膜41中を通過してTiN膜41と高誘電率ゲート絶縁膜であるHfO2膜32との界面にまで到達するのを防止でき、閾値電圧が上昇するのを防止あるいは抑制でき、フラットバンド電圧が低下するのを防止あるいは抑制できる。

【0017】

次に、図2を参照して、本発明の好ましい一実施の形態のMOSFETの製造方法を説明する。

【0018】

まず、シリコン基板10を、例えば、1%HF水溶液で処理して、シリコン基板10の一主面11の犠牲酸化膜を除去する(ステップS101)。

【0019】

次に、シリコン基板10の一主面11の表面に、シリコン系絶縁膜としての酸化シリコン膜(SiO2膜)31を熱酸化により形成する(ステップS102)。SiO2膜31は、シリコン基板10と、その後に形成する高誘電率絶縁膜であるHfO2膜32と、の界面における界面層として形成される。SiO2膜31は、ゲート絶縁膜30の一部を構成することとなる。

【0020】

具体的には、例えば、酸化炉を用い、酸化炉の処理室内にシリコン基板10を収容し、この処理室内にO2ガス等の酸化性ガスを供給して、熱酸化(ドライ酸化)によりシリコン基板10の一主面11の表面に、界面層としてSiO2膜31を形成する。処理条件は、例えば、下記のとおりである。

シリコン基板10の温度:850〜1000℃

処理室内圧力:1〜1000Pa

O2ガス供給流量:10〜1000sccm

SiO2膜31の膜厚:0.4〜1.5nm

【0021】

なお、ドライ酸化の他に、ウェット酸化、減圧酸化、プラズマ酸化等によりSiO2膜31を形成するようにしてもよい。

【0022】

次に、SiO2膜31上に、高誘電率絶縁膜(High-k膜)として、酸化ハフニウム膜(HfO2膜)32を成膜する(ステップS103)。HfO2膜32はゲート絶縁膜30として形成される。

【0023】

具体的には、例えば、ALD(Atomic layer Deposition)炉を用い、ALD炉の処理室内に、SiO2膜31形成後のシリコン基板10を収容し、この処理室内へのTDMAHガスとO3ガスとの交互供給(TDMAHガス供給→N2パージ→O3ガス供給→N2パージを1サイクルとしてこのサイクルを所定回数繰り返すこと)によりSiO2膜31上にゲート絶縁膜としてHfO2膜32を形成する。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:100〜400℃

処理室内圧力:1〜2000Pa

TDMAHガス供給流量:10〜2000sccm

O3ガス供給流量:10〜2000sccm

N2ガス供給流量:10〜10000sccm

HfO2膜32の膜厚:0.9〜4nm

【0024】

Hfを含む原料としては、テトラキスジメチルアミノハフニウム(Hf[N(CH3)2]4、略称:TDMAH)の他、テトラキスエチルメチルアミノハフニウム(Hf[N(C2H5)(CH3)]4、略称:TEMAH)、テトラキスジエチルアミノハフニウム(Hf[N(C2H5)2]4、略称:TDEAH)などの有機原料や、ハフニウムテトラクロライド(HfCl4)などの無機原料を用いることができる。酸化剤としては、O3ガスの他、H2Oガス等の酸化性ガス(酸素含有ガス)を用いることができる。パージガス(不活性ガス)としては、N2ガスの他、Ar、He、Ne、Xe等の希ガスを用いることができる。なお、TDMAH等のように常温常圧下で液体状態である液体原料を用いる場合は、液体原料を気化器やバブラ等の気化システムにより気化して、原料ガスとして供給することとなる。

【0025】

HfO2膜32の成膜後、PDA(Post Deposition Annealing)が行われる(ステップS104)。具体的には、例えば、熱処理炉(例えばRTP(Rapid Thermal Process)装置)を用い、RTP装置の処理室内にHfO2膜32形成後のシリコン基板10を収容し、この処理室内にN2ガスを供給してアニールを行う。PDAは、HfO2膜32中の不純物除去、HfO2膜32の緻密化もしくは結晶化を目的として行う。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:400〜800℃

処理室内圧力:1〜1000Pa

N2ガス供給流量:10〜10000sccm

アニール時間:10〜60秒

【0026】

次に、PDA後のHfO2膜32上に、第1の金属膜、すなわち、導電性の第1の金属含有膜として窒化チタン膜(TiN膜)41を形成する(ステップS105)。TiN膜41はゲート電極40の一部を構成することとなる。

【0027】

具体的には、例えば、ALD炉を用い、ALD炉の処理室内にPDA後のシリコン基板10を収容し、この処理室内へのTiCl4ガスとNH3ガスとの交互供給(TiCl4ガス供給→N2パージ→NH3ガス供給→N2パージを1サイクルとしてこのサイクルを所定回数繰り返すこと)により、PDA後のHfO2膜32上にTiN膜41を形成する。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:300〜450℃

処理室内圧力:1〜10000Pa

TiCl4ガス供給流量:10〜10000sccm

NH3ガス供給流量:10〜50000sccm

N2ガス供給流量:10〜10000sccm

TiN膜41の膜厚:5〜20nm

【0028】

Tiを含む原料としては、無機原料であるチタニウムテトラクロライド(TiCl4)の他、テトラキスエチルメチルアミノチタニウム(Ti[N(C2H5)(CH3)]4、略称:TEMAT)、テトラキスジメチルアミノチタニウム(Ti[N(CH3)2]4、略称:TDMAT)、テトラキスジエチルアミノチタニウム(Ti[N(C2H5)2]4、略称:TDEAT)などの有機原料を用いることができる。窒化剤としては、アンモニア(NH3)ガスの他、ジアジン(N2H2)ガス、ヒドラジン(N2H4)ガス、N3H8ガス等の窒化性ガス(窒素含有ガス)を用いることができる。パージガス(不活性ガス)としては、N2ガスの他、Ar、He、Ne、Xe等の希ガスを用いることができる。なお、TiCl4等のように常温常圧下で液体状態である液体原料を用いる場合は、液体原料を気化器やバブラ等の気化システムにより気化して、原料ガスとして供給することとなる。

【0029】

次に、TiN膜41上に、第2の金属膜、すなわち、導電性の第2の金属含有膜として窒化アルミニウムチタン膜(TiAlN膜)43を形成する(ステップS106)。TiAlN膜43は、TiN膜にアルミニウム(Al)を添加した導電性の金属含有膜であり、その後に形成する多結晶シリコン膜45からTiN膜41とHfO2膜32との界面へのシリコン(Si)の拡散を防止する拡散防止膜、すなわち、Si拡散ブロック層として機能する。このTiAlN膜43により、多結晶シリコン膜45中のSiがTiN膜41を通過して、TiN膜41とHfO2膜32との界面にまで到達するのを防止できる。TiAlN膜43は、図1に示すように、多結晶シリコン膜45とTiN膜41との界面に形成されることとなる。

【0030】

TiAlN膜43はTiN膜41と共にゲート電極40の一部を構成することとなる。なお、TiN膜41とTiAlN膜43は、異なる成膜装置、すなわち異なる処理室にて別々に形成してもよいが、両膜は同様なコンディション下で成膜できることから、同一の処理室内でin−situにて連続的に形成するのが好ましい。

【0031】

具体的には、例えば、ALD炉を用い、ALD炉の処理室内にTiN膜41形成後のシリコン基板10を収容し、この処理室内へのTiCl4ガスとTMAガスとNH3ガスとの交互供給(TiCl4ガス供給→N2パージ→NH3ガス供給→N2パージを1サイクルとしてこのサイクルを所定回数(m回)行ってTiNを形成後、TMAガス供給→N2パージ→NH3ガス供給→N2パージを1サイクルとしてこのサイクルを1回行ってAlNを形成し、このTiNの形成とAlNの形成を1サイクルとしてこのサイクルを所定回数(n回)行うこと)によりTiN膜41上にTiNとAlNが交互に積層されてなるTiAlN膜43を形成する。なお、TiN膜41とTiAlN膜43は、同一の処理室内でin−situにて連続的に形成する。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:300〜450℃

処理室内圧力:1〜10000Pa

TiCl4ガス供給流量:10〜10000sccm

TMAガス供給流量:10〜10000sccm

NH3ガス供給流量:10〜50000sccm

N2ガス供給流量:10〜10000sccm

TiAlN膜43の膜厚:3〜20nm、好ましくは5〜10nm

【0032】

TiAlN膜43の膜厚を薄くして、3nm未満とすると、Si拡散のブロック効果が低下し、Siの拡散を十分に抑制できなくなることがある。TiAlN膜43の膜厚を3nm以上とすれば、十分なSi拡散のブロック効果が得られ、Siの拡散を十分に抑制することが可能となる。TiAlN膜43の膜厚を5nm以上とすれば、Siの拡散をより十分に抑制することが可能となる。一方、TiAlN膜43の膜厚を20nmより大きくすると、TiNの抵抗率よりもTiAlNの抵抗率が大きいので、ゲート電極40全体での抵抗率が必要以上に上がってしまうことがある。TiAlN膜43の膜厚を20nm以下とすることでこれを防止できる。特に、TiAlN膜43の膜厚を10nm以下とすることで、ゲート電極40全体での抵抗率の上昇をより抑えることが可能となり、より適正な値とすることが可能となる。よって、TiAlN膜43の膜厚は、好ましくは3〜20nm、より好ましくは5〜10nmとするのがよい。また、TiAlN膜43のAl濃度を10%未満とすると、Al濃度が低くなり過ぎて、Si拡散のブロック効果が低下し、Siの拡散を十分に抑制できなくなることがある。TiAlN膜43のAl濃度を10%以上とすれば、十分なSi拡散のブロック効果が得られ、Siの拡散を十分に抑制することが可能となる。一方、TiAlN膜43のAl濃度を20%より大きくすると、TiAlN膜43の絶縁性が強くなり、抵抗率が大きくなり、ゲート電極40全体での抵抗率が必要以上に大きくなってしまうことがある。TiAlN膜43のAl濃度を20%以下とすることでこれを防止できる。よって、TiAlN膜43のAl濃度は、好ましくは10〜20%とするのがよい。

【0033】

なお、Tiを含む原料、窒化剤、パージガス(不活性ガス)としては、TiN膜41の成膜工程(ステップS105)におけるそれらと同様のものを用いることができる。Alを含む原料としては、有機原料であるトリメチルアルミニウム(Al(CH3)3、略称:TMA)の他、トリクロロアルミニウム(AlCl3)などの無機原料を用いることができる。なお、TMA等のように常温常圧下で液体状態である液体原料を用いる場合は、液体原料を気化器やバブラ等の気化システムにより気化して、原料ガスとして供給することとなる。

【0034】

なお、TiAlN膜43は、図3に示すようにTiN膜41中、すなわち上側のTiN膜41と下側のTiN膜41との間に形成するようにしてもよい。但し、この場合、図3に示すように、TiAlN膜43はHfO2膜32から2nm以上離間させることが好ましい。TiAlN膜43とHfO2膜32との距離を2nm未満、例えば1nmとすると、TiAlN膜43の仕事関数の影響が出てしまい、Vfb(フラットバンド電圧)に影響を及ぼすことがあるからである。TiAlN膜43をHfO2膜32から2nm以上離せば、その影響がなくなる。

【0035】

次に、TiAlN膜43上に、多結晶シリコン膜45、すなわち、ポリシリコン膜(Poly−Si膜)45を形成する(ステップS107)。Poly−Si膜45には、後述するイオン注入工程において、不純物(ドーパント)としてリン(P)もしくはボロン(B)がドーピングされ、Poly−Si膜45は、リンドープポリシリコン膜(P Doped Poly−Si膜)もしくはボロンドープポリシリコン膜(B Doped Poly−Si膜)となる。本実施の形態では、リンドープポリシリコン膜(P Doped Poly−Si膜)を形成している。Poly−Si膜45はTiAlN膜43およびTiN膜41と共にゲート電極40の一部を構成することとなる。

【0036】

具体的には、例えば、CVD炉を用い、CVD炉の処理室内にTiAlN膜43形成後のシリコン基板10を収容し、この処理室内へのモノシラン(SiH4)ガスの連続供給により、TiAlN膜43上にPoly−Si膜45を形成する。シリコン原料ガスとしては、SiH4ガスの他、ジシラン(Si2H6)ガスやジクロロシラン(SiH2Cl2)ガス等のシラン系ガスを用いてもよい。このとき、希釈ガスとしてN2ガス等の不活性ガスを同時に供給してもよい。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:600〜700℃

処理室内圧力:10〜48000Pa

SiH4ガス供給流量:10〜20000sccm

N2ガス供給流量:10〜10000sccm

Poly−Si膜45の膜厚:50〜200nm

【0037】

その後、ゲート電極40の上に選択的に形成されたレジスト(図示せず)をマスクにして、ゲート電極40のフォトリソグラフィ技術を用いたパターニング(Patterning)およびドライエッチング技術を用いたパターンエッチング(Etching)を行う(ステップS108)。その後、レジスト(図示せず)を除去する(ステップS109)。このように、ゲート電極40を加工した後、ゲート絶縁膜30も同様に加工し、シリコン基板10の一主面11の表面を露出させる。なお、ゲート絶縁膜30の加工は、別途、ウェットエッチングにより行うようにしてもよい。

【0038】

次に、Poly−Si膜45上に、SiO2膜(図示せず)を形成する(ステップS110)。具体的には、例えば、CVD炉を用い、CVD炉の処理室内に、パターニング、エッチングおよびレジスト除去後のシリコン基板10を収容し、この処理室内に、TEOSガスを供給してPoly−Si膜45上にSiO2膜を形成する。SiO2膜は、次のイオン注入工程においてPoly−Si膜45に注入されるリン(P)のPoly−Si膜45からのアウトディフュージョン(外方拡散)を防止するキャップ膜として形成される。SiO2膜は、また、ソース領域21およびドレイン領域22が形成されることとなるシリコン基板10の一主面11の表面上にも形成され、ソース領域21およびドレイン領域22用にイオン注入する際のチャネリング防止膜等としても機能する。Poly−Si膜45の膜厚とイオン注入工程における注入エネルギーにもよるが、SiO2膜の膜厚は例えば、5〜20nmとする。

【0039】

次に、イオン注入装置にてイオン注入法によりSiO2膜越しにソース領域21、ドレイン領域22やPoly−Si膜45に不純物(ドーパント)を注入する(ステップS111)。本実施の形態では、Poly−Si膜45にリン(P)を注入する。これにより、Poly−Si膜45はリンドープポリシリコン膜(P Doped Poly−Si膜)となる。また、ソース領域21やドレイン領域22には、リン(P)またはボロン(B)を注入する。例えば、リンを注入する際は、リンの固体ソースを用いる。ソース領域21、ドレイン領域22の不純物の濃度分布等やPoly−Si膜45中の不純物の濃度等に応じて複数回イオン注入を行う。リンをイオン注入する際の注入エネルギーは例えば30keVとする。なお、ポリシリコン膜(Poly−Si膜)45を形成する工程(ステップS107)にて、CVD炉で、SiH4ガスとPH3とを用いて、P Doped Poly−Si膜45を形成することも可能である。

【0040】

次に、ソース領域21、ドレイン領域22およびP Doped Poly−Si膜45の活性化アニールを行う(ステップS112)。具体的には、例えば、熱処理炉(アニール装置)を用い、アニール装置の処理室内にイオン注入後のシリコン基板10を収容し、この処理室内に、N2ガスを供給して、1000℃で活性化アニールを行う。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:950〜1050℃の範囲内、例えば1000℃

処理室内圧力:1〜1000Pa(なお、加熱するのが目的なので、大気圧でもよい) N2ガス供給流量:10〜10000sccm

アニール時間:0.05秒(50msec)〜20秒

【0041】

なお、本実施の形態では、多結晶シリコン膜45とTiN膜41との間にTiAlN膜43が形成されているので、この活性化アニールの際に、多結晶シリコン膜45中のSiがTiN膜41を通過して、TiN膜41とHfO2膜32との界面にまで到達するのを防止できる。すなわち、本実施の形態におけるTiAlN膜43は、Siの拡散をブロックするSi拡散ブロック層(Si拡散バリア層)として機能する。

【0042】

その後、400℃、10分の水素ガスアニーリング等のFGA(Forming gas annealing)処理を行う(ステップS113)。このようにして、MIPS構造のMOS構造を形成する。

【0043】

次に、図11を参照して、本発明の好ましい他の実施の形態を説明する。上述した、好ましい一実施の形態のMOSFET100では、ゲート絶縁膜30として、シリコン基板10の一主面11上に設けられたSiO2膜31とSiO2膜31上に設けられた高誘電率絶縁膜であるHfO2膜32とを備えていたが、本発明の好ましい他の実施の形態のMOSFET102では、ゲート絶縁膜30として、シリコン基板10の一主面11上に設けられた高誘電率絶縁膜であるHfO2膜32のみを備え、SiO2膜31を備えていない点が一実施の形態のMOSFET100と異なるが、他の点は同じである。

【0044】

本実施の形態においても、高誘電率絶縁膜であるHfO2膜32を使用することにより、ゲートリーク電流を低減している。また、ゲート電極40は、ゲート絶縁膜30のHfO2膜32上に設けられたTiN膜41と、TiN膜41上に設けられたTiAlN膜43と、TiAlN膜43上に設けられたPをドーピングした多結晶シリコン膜45とを備えており、HfO2膜32上に金属膜であるTiN膜41を使用しているので、空乏化層が生じることはなく、実効的なゲート絶縁膜の厚さが厚くなってしまうことを防止している。また、多結晶シリコン膜45とTiN膜41との間にTiAlN膜43を設けているので、ゲート電極40の形成後にソース領域21およびドレイン領域22の活性化アニールを行う際に、多結晶シリコン膜45中のSiが金属膜であるTiN膜41中に拡散するのを防止できる。その結果、多結晶シリコン膜45中のSiがTiN膜41中を通過してTiN膜41と高誘電率ゲート絶縁膜であるHfO2膜32との界面にまで到達するのを防止でき、閾値電圧が上昇するのを防止あるいは抑制でき、フラットバンド電圧が低下するのを防止あるいは抑制できる。

【0045】

上記本発明の好ましい実施の形態においては、シリコン基板と高誘電率絶縁膜であるHfO2膜との界面層としてのシリコン系絶縁膜として、SiO2膜を用いたが、SiO2膜の他、酸窒化シリコン膜(SiON膜)を用いてもよい。また、高誘電率ゲート絶縁膜として、HfO2膜を用いたが、HfO2膜の他、酸化ジルコニウム膜(ZrO2膜)、酸化チタン膜(TiO2膜)、酸化ニオブ膜(Nb2O5膜)、酸化タンタル膜(Ta2O5膜)、ハフニウムシリケート膜(HfSiOx膜)、ジルコニウムシリケート膜(ZrSiOx膜)、ハフニウムアルミネート膜(HfAlOx膜)、ジルコニウムアルミネート膜(ZrAlOx膜)や、これらを組み合わせたり混合させたりした膜を用いてもよい。

【0046】

ゲート電極の一部を構成することとなる、高誘電率ゲート絶縁膜上の金属含有膜としては、TiN膜の他、窒化ハフニウム膜(HfN膜)、窒化ジルコニウム膜(ZrN)、窒化タンタル膜(TaN膜)、タングステン膜(W膜)、窒化タングステン膜(WN膜)等を用いてもよい。

【0047】

また、ゲート電極の一部を構成することとなり、Si拡散防止膜として用いられる金属含有膜としては、TiAlN膜の他、TaAlN膜やTaCAlN膜、TiCAlN膜、TaCAl膜、TiCAl膜、HfAlN膜、ZrAlN膜などの窒素および炭素のうち少なくとも一方とAlを含む金属膜や、W膜やTa膜、Ti膜などの金属膜中へAlを添加したものも用いることができる。

【0048】

なお、本明細書では、金属膜という用語は、金属原子を含む導電性の物質で構成される膜、すなわち、導電性の金属含有膜を意味しており、これには、金属単体で構成される導電性の金属単体膜の他、導電性の金属窒化膜、導電性の金属酸化膜、導電性の金属酸窒化膜、導電性の金属炭化膜(金属カーバイド膜)、導電性の金属炭窒化膜、導電性の金属複合膜、導電性の金属合金膜、導電性の金属シリサイド膜等も含まれる。なお、TiN膜は導電性の金属窒化膜であり、TiAlN膜は導電性の金属複合膜である。

【0049】

上記実施形態におけるステップS102〜S107の少なくとも一部のステップについては、基板処理システムとしてのクラスタ装置を用いて連続的に行うようにしてもよい。

【0050】

例えば、ステップS102〜S103までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS102〜S104までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS102〜S105までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS102〜S106までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS102〜S107までをクラスタ装置を用いて連続的に行うようにしてもよい。

【0051】

また、例えば、ステップS103〜S104までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS103〜S105までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS103〜S106までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS103〜S107までをクラスタ装置を用いて連続的に行うようにしてもよい。

【0052】

また、例えば、ステップS105〜S106までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS105〜S107までをクラスタ装置を用いて連続的に行うようにしてもよい。

【0053】

例えば、ステップS102〜S107の全てのステップをクラスタ装置を用いて連続的に行う場合、図12に示すようなクラスタ装置200を用いて行うことができる。

【0054】

基板処理システムとしてのクラスタ装置200は、シリコン基板10を処理する処理部としての処理室201、202、203、204、205、シリコン基板10をクラスタ装置200に搬入する搬入室208、シリコン基板10をクラスタ装置200から搬出する搬出室209、シリコン基板10を冷却する冷却室206、207、処理室201、202、203、204、205、搬入室208、搬出室209、冷却室206、207が取り付けられ、シリコン基板10をこれらの室の間で移載する移載機211が設けられた移載室210を備えている。移載室210と、処理室201、202、203、204、205、搬入室208、搬出室209との間には、ゲートバルブ201a、202a、203a、204a、205a、208a、209aがそれぞれ設けられている。搬入室208、搬出室209には、ゲートバルブ208a、209aと反対側にゲートバルブ208b、209bがそれぞれ設けられている。

【0055】

クラスタ装置200は、また、処理室201、202、203、204、205内にガス配管334を介して処理ガスや不活性ガスを供給し、移載室210、搬入室208、搬出室209、冷却室206、207内にガス配管334を介して不活性ガスを供給するガス供給系333と、処理室201、202、203、204、205、移載室210、搬入室208、搬出室209、冷却室206、207内を排気配管337を介して排気する排気系336と、を備えている。

【0056】

図12、図13を参照すれば、クラスタ装置200は、さらに、ゲートバルブ201a、202a、203a、204a、205a、208a、209a、208b、209bの開閉動作を制御するゲートバルブ制御部231、移載機211の動作を制御する移載機制御部232、ガス供給系333を制御するガス供給系制御部233、排気系336を制御する排気系制御部236、処理室201、202、203、204、205内の温度を制御する温度制御部237、処理室201、202、203、204、205、移載室210、搬入室208、搬出室209、冷却室206、207内の圧力を制御する圧力制御部238等を備えている。図13を参照すれば、クラスタ装置200は、さらに、コントローラ220を備えている。コントローラ220については、後に詳述する。

【0057】

このクラスタ装置200では、例えば、次のようにしてシリコン基板10を処理する。

【0058】

ゲートバルブ208bを開き、搬入用予備室としての搬入室(ロードロック室)208内にシリコン基板10としてのウエハ10を搬入する。搬入後、ゲートバルブ208bを閉じ、搬入室208内を真空排気する。搬入室208内が所定の圧力になると、ゲートバルブ208aが開かれる。なお、移載室210内は予め真空排気され、所定の圧力に維持されている。

【0059】

ゲートバルブ208aが開かれると、ウエハ10がウエハ移載機211によりピックアップされ、搬入室208内から移載室210内に取り出される。その後、ゲートバルブ208aが閉じられる。ゲートバルブ208aが閉じられると、ゲートバルブ201aが開かれ、ウエハ10がウエハ移載機211により、移載室210内から第1の処理室201内に搬入される。搬入後、ゲートバルブ201aが閉じられ、処理室201内でウエハ10上にSiO2膜を形成する処理が行われる(ステップS102)。

【0060】

その後、ゲートバルブ201aが開かれ、SiO2膜を形成した後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室201内から移載室210内に取り出される。その後、ゲートバルブ201aが閉じられる。ゲートバルブ201aが閉じられると、ゲートバルブ202aが開かれ、SiO2膜を形成した後のウエハ10が、ウエハ移載機211により、移載室210内から処理室202内に搬入される。搬入後、ゲートバルブ202aが閉じられ、処理室202内で、ウエハ10上のSiO2膜上にHfO2膜を形成する処理が行われる(ステップS103)。

【0061】

その後、ゲートバルブ202aが開かれ、HfO2膜を形成した後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室202内から移載室210内に取り出される。その後、ゲートバルブ202aが閉じられる。ゲートバルブ202aが閉じられると、ゲートバルブ203aが開かれ、HfO2膜を形成した後のウエハ10が、ウエハ移載機211により、移載室210内から処理室203内に搬入される。搬入後、ゲートバルブ203aが閉じられ、処理室203内で、ウエハ10上のHfO2膜に対してPDA処理が行われる(ステップS104)。

【0062】

その後、ゲートバルブ203aが開かれ、PDA後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室203内から移載室210内に取り出される。その後、ゲートバルブ203aが閉じられる。ゲートバルブ203aが閉じられると、ゲートバルブ204aが開かれ、PDA後のウエハ10が、ウエハ移載機211により、移載室210内から処理室204内に搬入される。搬入後、ゲートバルブ204aが閉じられ、処理室204内で、ウエハ10上のPDA後のHfO2膜上に、TiN膜を形成する処理と、TiAlN膜を形成する処理と、がin−situにて連続的に行われる(ステップS105、S106)。このとき、TiN膜とTiAlN膜は、図1のように積層して形成してもよいし、図3のように積層して形成してもよい。

【0063】

その後、ゲートバルブ204aが開かれ、TiN膜およびTiAlN膜形成後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室204内から移載室210内に取り出される。その後、ゲートバルブ204aが閉じられる。ゲートバルブ204aが閉じられると、ゲートバルブ205aが開かれ、TiN膜およびTiAlN膜形成後のウエハ10が、ウエハ移載機211により、移載室210内から処理室205内に搬入される。搬入後、ゲートバルブ205aが閉じられ、処理室205内で、ウエハ10上のTiAlN膜(図1参照)またはTiN膜(図3参照)上に、Poly−Si膜を形成する処理が行われる(ステップS107)。

【0064】

その後、ゲートバルブ205aが開かれ、Poly−Si膜形成後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室205内から移載室210内に取り出される。その後、ゲートバルブ205aが閉じられる。ゲートバルブ205aが閉じられると、ゲートバルブ209aが開かれ、ステップS102〜S107の一連の処理を終えたウエハ10が、ウエハ移載機211により、移載室210内から搬出用予備室としての搬出室(ロードロック室)209内に搬送される。搬送後、ゲートバルブ209aが閉じられ、搬出室209内が大気圧に戻された後、ゲートバルブ209bが開かれ、一連の処理後のウエハ10が取り出される。

【0065】

なお、上記各ステップを実施した後のウエハ10は、必要に応じて、冷却室206、冷却室207内に搬送され、冷却される場合もある。その場合、ウエハ10は、所定の温度となるまで冷却室206または冷却室207内にて待機させられ、所定の温度まで冷却された後、次のステップを行うための処理室内に搬送され、あるいは搬出室209を介して搬出されることとなる。

【0066】

次に、ステップS102〜S107の全てのステップを連続的に行うクラスタ装置の他の例を、図14を参照して説明する。図12に示すクラスタ装置200は、5つの処理室

処理室201、202、203、204、205を備えていたが、図14に示すクラスタ装置300は、6つの処理室201、202、203、204、254、205を備えている点が図12に示すクラスタ装置200と異なるが他の点は同様である。

【0067】

図14に示すクラスタ装置300では、移載室210と、処理室254との間に、ゲートバルブ254aが設けられている。処理室254内には、ガス配管334を介して処理ガスや不活性ガスがガス供給系333から供給される。処理室254内は、排気配管337を介して排気系336によって排気される。ゲートバルブ254aの開閉動作は、ゲートバルブ制御部231によって制御され、処理室254内の温度は、温度制御部237によって制御される。処理室254内の圧力は圧力制御部238によって制御される。

【0068】

図12に示すクラスタ装置200では、処理室204内で、ウエハ10上のPDA後のHfO2膜上に、TiN膜を形成する処理と、TiAlN膜を形成する処理と、を連続的に行ったが、図14に示すクラスタ装置300では、処理室204内で、TiN膜を形成する処理を行い、処理室254内で、TiAlN膜を形成する処理を行う。

【0069】

なお、上記一連の処理は、クラスタ装置200、300を構成する各部の動作を、コントローラ220により制御することで行われる。

【0070】

図13を参照すれば、制御部(制御手段)であるコントローラ220は、CPU(Central Processing Unit)121a、RAM(Random Access Memory)121b、記憶装置121c、I/Oポート121dを備えたコンピュータとして構成されている。RAM121b、記憶装置121c、I/Oポート121dは、内部バス121eを介して、CPU121aとデータ交換可能なように構成されている。コントローラ220には、例えばタッチパネル等として構成された入出力装置122が接続されている。

【0071】

記憶装置121cは、例えばフラッシュメモリ、HDD(Hard Disk Drive)等から構成されている。記憶装置121c内には、クラスタ装置200の動作を制御する制御プログラムや、上述の一連のウエハ処理の手順や条件などが記載されたプロセスレシピ等が、読み出し可能に格納されている。なお、プロセスレシピは、上述の一連のウエハ処理における各手順(各ステップ)をコントローラ220に実行させ、所定の結果を得ることが出来るように組み合わされたものであり、プログラムとして機能する。以下、このプロセスレシピや制御プログラム等を総称して、単にプログラムともいう。なお、本明細書においてプログラムという言葉を用いた場合は、プロセスレシピ単体のみを含む場合、制御プログラム単体のみを含む場合、または、その両方を含む場合がある。また、RAM121bは、CPU121aによって読み出されたプログラムやデータ等が一時的に保持されるメモリ領域(ワークエリア)として構成されている。

【0072】

I/Oポート121dは、バス240を介して、上述のゲートバルブ制御部231、移載機制御部232、ガス供給系制御部233、排気系制御部236、温度制御部237、圧力制御部238等に接続されている。

【0073】

CPU121aは、記憶装置121cから制御プログラムを読み出して実行すると共に、入出力装置122からの操作コマンドの入力等に応じて記憶装置121cからプロセスレシピを読み出すように構成されている。そして、CPU121aは、読み出したプロセスレシピの内容に沿うように、ゲートバルブ制御部231、移載機制御部232、ガス供給系制御部233、排気系制御部236、温度制御部237、圧力制御部238等を制御して、ゲートバルブ201a、202a、203a、204a、254a、205a、208a、209a、208b、209b、移載機211、ガス供給系333、排気系336、処理室201、202、203、204、254、205を加熱するヒータ(図示せず)等の動作を制御するように構成されている。

【0074】

なお、コントローラ220は、専用のコンピュータとして構成されている場合に限らず、汎用のコンピュータとして構成されていてもよい。例えば、上述のプログラムを格納した外部記憶装置(例えば、磁気テープ、フレキシブルディスクやハードディスク等の磁気ディスク、CDやDVD等の光ディスク、MO等の光磁気ディスク、USBメモリやメモリカード等の半導体メモリ)123を用意し、係る外部記憶装置123を用いて汎用のコンピュータにプログラムをインストールすること等により、本実施形態に係るコントローラ220を構成することができる。なお、コンピュータにプログラムを供給するための手段は、外部記憶装置123を介して供給する場合に限らない。例えば、インターネットや専用回線等の通信手段を用い、外部記憶装置123を介さずにプログラムを供給するようにしてもよい。なお、記憶装置121cや外部記憶装置123は、コンピュータ読み取り可能な記録媒体として構成される。以下、これらを総称して、単に記録媒体ともいう。なお、本明細書において記録媒体という言葉を用いた場合は、記憶装置121c単体のみを含む場合、外部記憶装置123単体のみを含む場合、または、その両方を含む場合がある。

【0075】

なお、基板処理システムとして、クラスタ装置の代わりに、各ステップにおける処理をそれぞれ単独で行うスタンドアローンタイプの装置をそれぞれ準備して、これらの一連の処理を行うようにしてもよい。また、上述の各実施形態や各応用例等は、適宜組み合わせて用いることができる。

【0076】

また、本発明は、例えば、既存の基板処理システムのプロセスレシピを変更することでも実現できる。プロセスレシピを変更する場合は、本発明に係るプロセスレシピを電気通信回線や当該プロセスレシピを記録した記録媒体を介して既存の基板処理システムにインストールしたり、また、既存の基板処理システムの入出力装置を操作し、そのプロセスレシピ自体を本発明に係るプロセスレシピに変更することも可能である。

【実施例1】

【0077】

本発明の好ましい一実施の形態のMOSFET用の評価サンプルと、比較例の評価サンプルを作成し、それらの電気的特性等の特性を比較した。

【0078】

まず、図4を参照して、本発明の好ましい一実施の形態のMOSFET用の評価サンプル200を説明する。図1の本発明の好ましい一実施の形態のMOSFET100では、ソース領域21およびドレイン領域22が存在したが、この評価サンプル200ではソース領域21およびドレイン領域22が存在しない点が一実施の形態のMOSFET100と異なるが、他の点は同じであるので、説明は省略する。また、製造方法も、図2を参照して説明した製造方法と同様であるので、説明は省略する。但し、評価サンプル200の製造では、FGA処理(ステップS113)の後に、酸化防止等の目的で、シリコン基板10の裏面へのAl成膜を行った。

【0079】

次に、図5を参照して、比較例の評価サンプル202を説明する。図4の本発明の好ましい一実施の形態のMOSFET用の評価サンプルでは、TiAlN膜43が存在したが、比較例の評価サンプル202では、TiAlN膜43がなく、多結晶シリコン膜45とTiN膜41からなるゲート電極42を備える点が一実施の形態のMOSFET用の評価サンプルと異なる。他の点は同じであるので、説明は省略する。また、この評価サンプル202の製造方法も、評価サンプル200の製造方法において、TiAlN膜43を成膜するステップS106がないだけで、それ以外は同じなので、説明は省略する(図6参照)。

【0080】

図7は、本発明の好ましい一実施の形態のMOSFET用の評価サンプル200のC−V特性を示す図であり、図8は、比較例に係る評価サンプル202のC−V特性を示す図である。図7、図8の横軸は、C−V特性の測定に際してゲート電極に印加したゲート電圧Vg(V)を示しており、縦軸は、静電容量C(μF/cm2)を示している。図7、図8中の●印は1000℃の活性化アニール処理を行わなかった場合(以下、1000℃処理無し、ともいう)、□印は1000℃活性化アニール処理を行った場合(以下、1000℃処理有り、ともいう)を示している。図9は、図7、図8に示すそれぞれのC−Vカーブから抽出したEOT(等価酸化膜厚)およびVfb(フラットバンド電圧)を示した表である。

【0081】

図7、8、9より、比較例では、1000℃処理無しの場合と比較し、1000℃処理有りの場合ではEOTは増加し、かつ、Vfbは負方向へシフトしていることがわかる。これは、多結晶シリコン膜45中のSiがTiN膜41中に拡散し、TiN膜41とHfO2膜32との界面にまで到達したことによって、その界面においてSi−O結合が生じ、その結果、EOTが増加したものと考えられる。また、多結晶シリコン膜45中のSiがTiN膜41とHfO2膜32との界面にまで到達したことによって、フェルミレベルピニング現象が生じ、その結果、仕事関数が低下してVfbが負方向へシフトしたものと考えられる。なお、Vfbが負方向へシフトすると、閾値電圧が増加してしまう。一方、本発明の好ましい一実施の形態による構造では、1000℃処理無しの場合と比較し、1000℃処理有りの場合ではEOTは薄くなり、かつ、Vfbは正方向へシフトしていることがわかる。Vfbが正方向へシフトすると、閾値電圧が減少する。EOTの薄膜化は、1000℃処理によるHfO2膜32の緻密化によるものと考えられる。このように、TiN膜41上にTiAlN膜43を設けることで、多結晶シリコン膜45からのSi拡散を防止または抑制でき、それにより、多結晶シリコン膜45中のSiがTiN膜41とHfO2膜32との界面にまで到達することを防止または抑制できる。そしてそれにより、閾値電圧が上昇するのを防止または抑制でき、Vfbの低下を防止または抑制できる。

【0082】

次に、図10を参照して、他の比較例の評価サンプル204を説明する。この比較例に係る評価サンプル204では、TiN膜41を設けずに、HfO2膜32上にTiAlN膜43を設け、TiAlN膜43上に多結晶シリコン膜45を設けている。この場合には、多結晶シリコン膜45からのSiの拡散は、TiAlN膜43で阻止される。しかしながら、TiAlN膜43中のAlがHfO2膜32内に拡散してEOTを増加させてしまう。また、TiAlNの仕事関数がTiNより小さいため、ゲートリーク電流が大きくなってしまう。これに対して、図4を参照して説明した、本発明の好ましい一実施の形態のMOSFET用の評価サンプル200では、TiAlN膜43を設けているので、多結晶シリコン膜45からのSiの拡散を阻止できるだけでなく、TiAlN膜43とHfO2膜32との間にTiN膜41を設けているので、TiAlN膜43中のAlがHfO2膜32内に拡散するのを防止または抑制でき、その結果、EOTが増加するのを防止または抑制できる。さらに、ゲート絶縁膜であるHfO2膜32上には、TiN膜41が存在し、TiNの仕事関数がTiAlNより大きいため、ゲートリーク電流は小さくなる。

【0083】

(本発明の好ましい態様)

以下に、本発明の好ましい態様について付記する。

【0084】

(付記1)

本発明の好ましい一態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の第1の金属含有膜と、

前記第1の金属含有膜上に形成され、アルミニウムを添加してなる導電性の第2の金属含有膜と、

前記第2の金属含有膜上に形成されたシリコン膜と、

を有する半導体装置が提供される。

【0085】

(付記2)

付記1の半導体装置であって、好ましくは、前記第2の金属含有膜は、前記第1の金属含有膜にアルミニウムを添加してなる導電性の金属含有膜である。

【0086】

(付記3)

付記1または2の半導体装置であって、好ましくは、前記ゲート絶縁膜は高誘電率絶縁膜を含む。

【0087】

(付記4)

付記1または2の半導体装置であって、好ましくは、前記ゲート絶縁膜は、シリコン系絶縁膜と、該シリコン系絶縁膜上に形成された高誘電率絶縁膜と、を含む。

【0088】

(付記5)

付記1〜4のいずれかの半導体装置であって、好ましくは、前記第2の金属含有膜はTiAlN膜を含む。

【0089】

(付記6)

付記1〜4のいずれかの半導体装置であって、好ましくは、前記第1の金属含有膜はTiN膜を含み、前記第2の金属含有膜はTiAlN膜を含む。

【0090】

(付記7)

本発明の好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する工程と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する工程と、

前記第2の金属含有膜上にシリコン膜を形成する工程と、

を有する半導体装置の製造方法が提供される。

【0091】

(付記8)

付記7の半導体装置の製造方法であって、好ましくは、前記第2の金属含有膜は、前記第1の金属含有膜にアルミニウムを添加してなる導電性の金属含有膜である。

【0092】

(付記9)

付記7または8半導体装置の製造方法であって、好ましくは、前記ゲート絶縁膜は高誘電率絶縁膜を含む。

【0093】

(付記10)

付記7または8の半導体装置の製造方法であって、好ましくは、前記ゲート絶縁膜は、シリコン系絶縁膜と、該シリコン系絶縁膜上に形成された高誘電率絶縁膜と、を含む。

【0094】

(付記11)

付記7〜10のいずれかの半導体装置の製造方法であって、好ましくは、前記第2の金属含有膜はTiAlN膜を含む。

【0095】

(付記12)

付記7〜10のいずれかの半導体装置の製造方法であって、好ましくは、前記第1の金属含有膜はTiN膜を含み、前記第2の金属含有膜はTiAlN膜を含む。

【0096】

(付記13)

付記7〜12のいずれかの半導体装置の製造方法であって、好ましくは、前記シリコン膜を形成する工程の後に、活性化アニールを行う工程を有する。

【0097】

(付記14)

本発明のさらに好ましい他の態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の金属含有膜と、

前記金属含有膜上に形成されたシリコン膜と、を有し、

前記金属含有膜と前記シリコン膜との間には、前記シリコン膜から前記金属含有膜中へのシリコンの拡散を防止する拡散防止膜が設けられている半導体装置が提供される。

【0098】

(付記15)

本発明のさらに好ましい他の態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の金属含有膜と、

前記金属含有膜上に形成されたシリコン膜と、を有し、

前記金属含有膜中には、前記シリコン膜から前記金属含有膜と前記絶縁膜との界面へのシリコンの拡散を防止する拡散防止膜が設けられている半導体装置が提供される。

【0099】

(付記16)

付記14または15の半導体装置であって、好ましくは、前記拡散防止膜は、前記シリコン膜と接触するように設けられる。

【0100】

(付記17)

付記14または15の半導体装置であって、好ましくは、前記拡散防止膜は、前記金属含有膜と前記シリコン膜との界面に設けられる。

【0101】

(付記18)

付記14〜17のいずれかの半導体装置であって、好ましくは、前記ゲート絶縁膜は高誘電率絶縁膜を含む。

【0102】

(付記19)

付記14〜17のいずれかの半導体装置であって、好ましくは、前記ゲート絶縁膜はシリコン系絶縁膜と、該シリコン系絶縁膜上に形成された高誘電率絶縁膜と、を含む。

【0103】

(付記20)

付記14〜19のいずれかの半導体装置であって、好ましくは、前記拡散防止膜が前記金属含有膜にアルミニウムを添加した導電性の金属含有膜である。

【0104】

(付記21)

付記20の半導体装置であって、好ましくは、前記拡散防止膜はTiAlN膜を含む。

【0105】

(付記22)

付記14〜20のいずれかの半導体装置であって、好ましくは、前記金属含有膜はTiN膜を含み、前記拡散防止膜はTiAlN膜を含む。

【0106】

(付記23)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の金属含有膜を形成する工程と、

前記金属含有膜上にシリコン膜を形成する工程と、を有し、

前記金属含有膜と前記シリコン膜との間に、前記シリコン膜から前記金属含有膜中へのシリコンの拡散を防止する拡散防止膜を形成する工程を有する半導体装置の製造方法が提供される。

【0107】

(付記24)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の金属含有膜を形成する工程と、

前記金属含有膜上にシリコン膜を形成する工程と、を有し、

前記金属含有膜を形成する工程では、前記金属含有膜中に、前記シリコン膜から前記金属含有膜と前記ゲート絶縁膜との界面へのシリコンの拡散を防止する拡散防止膜を形成する半導体装置の製造方法が提供される。

【0108】

(付記25)

付記23または24の半導体装置の製造方法であって、好ましくは、前記拡散防止膜は、前記シリコン膜と接触するように設けられる。

【0109】

(付記26)

付記23または24の半導体装置の製造方法であって、好ましくは、前記拡散防止膜は、前記金属含有膜と前記シリコン膜との界面に設けられる。

【0110】

(付記27)

付記23〜26のいずれかの半導体装置の製造方法であって、好ましくは、前記ゲート絶縁膜は高誘電率絶縁膜を含む。

【0111】

(付記28)

付記23〜26のいずれかの半導体装置の製造方法であって、好ましくは、前記ゲート絶縁膜はシリコン系絶縁膜と、該シリコン系絶縁膜上に形成された高誘電率絶縁膜と、を含む。

【0112】

(付記29)

付記23〜28のいずれかの半導体装置の製造方法であって、好ましくは、前記拡散防止膜が前記金属含有膜にアルミニウムを添加した導電性の金属含有膜である。

【0113】

(付記30)

付記29の半導体装置の製造方法であって、好ましくは、前記拡散防止膜はTiAlN膜を含む。

【0114】

(付記31)

付記23〜29のいずれかの半導体装置の製造方法であって、好ましくは、前記金属含有膜はTiN膜を含み、前記拡散防止膜はTiAlN膜を含む。

【0115】

(付記32)

付記23〜31のいずれかの半導体装置の製造方法であって、好ましくは、前記シリコン膜を形成する工程の後に、活性化アニールを行う工程を有する。

【0116】

(付記33)

本発明のさらに好ましい他の態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、電圧を印加した場合に空乏化層が生じない導電性膜と、

前記導電性膜上に形成されたシリコン膜と、を有し、

前記導電性膜と前記シリコン膜との間には、前記シリコン膜から前記導電性膜中へのシリコンの拡散を防止する拡散防止膜が設けられている半導体装置が提供される。

【0117】

(付記34)

本発明のさらに好ましい他の態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、電圧を印加した場合に空乏化層が生じない導電性膜と、

前記導電性膜上に形成されたシリコン膜と、を有し、

前記導電性膜中には、前記シリコン膜から前記導電性膜と前記絶縁膜との界面へのシリコンの拡散を防止する拡散防止膜が設けられている半導体装置が提供される。

【0118】

(付記35)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、電圧を印加した場合に空乏化層が生じない導電性膜を形成する工程と、

前記導電性膜上にシリコン膜を形成する工程と、を有し、

前記導電性膜と前記シリコン膜との間に、前記シリコン膜から前記導電性膜中へのシリコンの拡散を防止する拡散防止膜を形成する工程を有する半導体装置の製造方法が提供される。

【0119】

(付記36)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、電圧を印加した場合に空乏化層が生じない導電性膜を形成する工程と、

前記導電性膜上にシリコン膜を形成する工程と、を有し、

前記導電性膜を形成する工程では、前記導電性膜中に、前記シリコン膜から前記導電性膜と前記ゲート絶縁膜との界面へのシリコンの拡散を防止する拡散防止膜を形成する半導体装置の製造方法が提供される。

【0120】

(付記37)

本発明のさらに好ましい他の態様によれば、

基板上に形成された高誘電率絶縁膜と、

前記高誘電率絶縁膜上に形成されたTiN膜と、

前記TiN膜上に形成されたTiAlN膜と、

前記TiAlN膜上に形成されたシリコン膜と、

を有する半導体装置が提供される。

【0121】

(付記38)

本発明のさらに好ましい他の態様によれば、

基板上に高誘電率絶縁膜を形成する工程と、

前記高誘電率絶縁膜上にTiN膜を形成する工程と、

前記TiN膜上にTiAlN膜を形成する工程と、

前記TiAlN膜上にシリコン膜を形成する工程と、

を有する半導体装置の製造方法が提供される。

【0122】

(付記39)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する第1の処理部と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する第2の処理部と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する第3の処理部と、

前記第2の金属含有膜上にシリコン膜を形成する第4の処理部と、

を有する基板処理システムが提供される。

【0123】

(付記40)

付記39の基板処理システムであって、好ましくは、前記第2の処理部と前記第3の処理部は同一の処理部である。

【0124】

(付記41)

本発明のさらに好ましい他の態様によれば、

基板処理システムの第1の処理部で半導体基板上にゲート絶縁膜を形成する手順と、

前記基板処理システムの第2の処理部で前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する手順と、

前記基板処理システムの第3の処理部で前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する手順と、

前記基板処理システムの第4の処理部で前記第2の金属含有膜上にシリコン膜を形成する手順と、

をコンピュータに実行させるためのプログラムが提供される。

【0125】

(付記42)

本発明のさらに好ましい他の態様によれば、

基板処理システムの第1の処理部で半導体基板上にゲート絶縁膜を形成する手順と、

前記基板処理システムの第2の処理部で前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する手順と、

前記基板処理システムの第3の処理部で前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する手順と、

前記基板処理システムの第4の処理部で前記第2の金属含有膜上にシリコン膜を形成する手順と、

をコンピュータに実行させるためのプログラムを記録したコンピュータ読み取り可能な記録媒体が提供される。

【0126】

以上、本発明の種々の典型的な実施の形態を説明してきたが、本発明はそれらの実施の形態に限定されない。従って、本発明の範囲は、次の特許請求の範囲によってのみ限定されるものである。

【符号の説明】

【0127】

10 シリコン基板

11 一主面

21 ソース領域

22 ドレイン領域

30 ゲート絶縁膜

31 SiO2膜

32 HfO2膜

40 ゲート電極

41 TiN膜

43 TiAlN膜

45 多結晶シリコン膜

100、102 MOSFET

200、202、204 評価サンプル

【技術分野】

【0001】

本発明は、半導体装置、半導体装置の製造方法、基板処理システムおよびプログラムに関し、特に、MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)、その製造方法、基板処理システムおよびプログラムに関する。

【背景技術】

【0002】

MOSFETの高集積化及び高性能化に合わせて、ゲート絶縁膜の薄膜化(EOT(Effective Oxide Thickness)スケーリング化)が行われている。従来、ゲート絶縁膜にはSiO2膜が用いられてきたが、ゲート絶縁膜を薄膜化していくとゲートリーク電流の増大が顕著となる。そこで、ゲートリーク電流を低減するために、現在は、SiO2膜よりも高い誘電率を有する絶縁膜(High-k絶縁膜)がゲート絶縁膜に適用され始めている。その中でも、HfO2膜が有望視されている。一方、ゲート電極材料としては、従来は多結晶シリコン(Poly-Si)が用いられてきたが、多結晶シリコン電極を使用すると、空乏化層が形成されその分実効的なゲート絶縁膜の厚さが厚くなってしまい、ゲート絶縁膜の薄膜化に反してしまう。そこで、空乏化層が生じない金属(メタル)材料をゲート電極に使用することが検討されている。

【0003】

近年、このような金属ゲート電極とHigh-kゲート絶縁膜とを用いたMOSFETスタック構造であって、ゲート絶縁膜と多結晶シリコンゲート電極との間に金属ゲート電極を挿入したMIPS (Metal Inserted Poly Silicon)構造のゲート電極を用い、ゲート電極形成後にソース/ドレイン領域の活性化アニールを行うゲートファーストプロセスが注目されている(非特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【非特許文献1】"A Highly Manufacturable MIPS (Metal Inserted Poly-Si Stack) Technology with Novel Threshold Voltage Control" 2005 Symposium on VLSI Technology Digest of Technical Papers pp. 232-233

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、このMIPS構造では、ソース/ドレイン領域の活性化アニール中に、多結晶シリコン中のSiが金属膜を通過して金属電極とHigh-kゲート絶縁膜との界面にまで到達し、フェルミレベルピニングと呼ばれる現象を引き起こし、閾値電圧が上昇する(フラットバンド電圧が低下する)という問題があった。

【0006】

本発明の主な目的は、閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置、半導体装置の製造方法、当該半導体装置の製造に好適に使用される基板処理システム、および当該基板処理システムで好適に使用されるプログラムを提供することにある。

【課題を解決するための手段】

【0007】

本発明の一態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の第1の金属含有膜と、

前記第1の金属含有膜上に形成され、アルミニウムを添加してなる導電性の第2の金属含有膜と、

前記第2の金属含有膜上に形成されたシリコン膜と、

を有する半導体装置が提供される。

【0008】

本発明の他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する工程と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する工程と、

前記第2の金属含有膜上にシリコン膜を形成する工程と、

を有する半導体装置の製造方法が提供される。

【0009】

本発明のさらに他の態様によれば、

半導体基板上にゲート絶縁膜を形成する第1の処理部と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する第2の処理部と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する第3の処理部と、

前記第2の金属含有膜上にシリコン膜を形成する第4の処理部と、

を有する基板処理システムが提供される。

【0010】

本発明のさらに他の態様によれば、

基板処理システムの第1の処理部で半導体基板上にゲート絶縁膜を形成する手順と、

前記基板処理システムの第2の処理部で前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する手順と、

前記基板処理システムの第3の処理部で前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する手順と、

前記基板処理システムの第4の処理部で前記第2の金属含有膜上にシリコン膜を形成する手順と、

をコンピュータに実行させるためのプログラムが提供される。

【発明の効果】

【0011】

本発明によれば、閾値電圧が上昇するのを防止または抑制でき、フラットバンド電圧が低下するのを防止または抑制できる半導体装置、半導体装置の製造方法、当該半導体装置の製造に好適に使用される基板処理システム、および当該基板処理システムで好適に使用されるプログラムが提供される。

【図面の簡単な説明】

【0012】

【図1】図1は、本発明の好ましい一実施の形態のMOSFETを説明するための概略縦断面図である。

【図2】図2は、本発明の好ましい一実施の形態のMOSFETの製造方法を説明するためのフローチャートである。

【図3】図3は、本発明の好ましい一実施の形態のMOSFETを説明するための概略縦断面図である。

【図4】図4は、本発明の好ましい一実施の形態のMOSFET用の評価サンプルを説明するための概略縦断面図である。

【図5】図5は、比較例のMOSFET用の評価サンプルを説明するための概略縦断面図である。

【図6】図6は、比較例のMOSFET用の評価サンプルの製造方法を説明するためのフローチャートである。

【図7】図7は、本発明の好ましい一実施の形態のMOSFET用の評価サンプルのC−V特性の図である。

【図8】図8は、比較例のMOSFET用の評価サンプルのC−V特性の図である。

【図9】図9は、本発明の好ましい一実施の形態のMOSFET用の評価サンプルと、比較例のMOSFET用の評価サンプルの、EOT(等価酸化膜厚)とVfb(フラットバンド電圧)を示す表である。

【図10】図10は、他の比較例のMOSFET用の評価サンプルを説明するための概略縦断面図である。

【図11】図11は、本発明の好ましい他の実施の形態のMOSFETを説明するための概略縦断面図である。

【図12】図12は、本発明の好ましい一実施の形態のMOSFETを製造する際に好適に使用されるクラスタ装置の一例を説明するための概略図である。

【図13】図13は、図12、図14のクラスタ装置に使用されるコントローラを説明するための概略図である。

【図14】図14は、本発明の好ましい一実施の形態のMOSFETを製造する際に好適に使用されるクラスタ装置の他の例を説明するための概略図である。

【発明を実施するための形態】

【0013】

以下、本発明の好ましい実施の形態について図面を参照しながら説明する。

【0014】

図1を参照すれば、本発明の好ましい一実施の形態の半導体装置(デバイス)としてのMOSFET100は、半導体基板であるシリコン基板10と、シリコン基板10の一主面11の表面に設けられたゲート絶縁膜30と、ゲート絶縁膜30上に設けられたゲート電極40と、ゲート電極40の両側のシリコン基板10の一主面11にそれぞれ設けられたソース領域21およびドレイン領域22とを備えている。

【0015】

ゲート絶縁膜30は、シリコン基板10の一主面11上に設けられたSiO2膜31とSiO2膜31上に設けられた高誘電率(High-k)絶縁膜であるHfO2膜32とを備えている。高誘電率絶縁膜であるHfO2膜32を使用することにより、ゲートリーク電流を低減している。

【0016】

ゲート電極40は、ゲート絶縁膜30のHfO2膜32上に設けられたTiN膜41と、TiN膜41上に設けられたTiAlN膜43と、TiAlN膜43上に設けられたPをドーピングした多結晶シリコン膜(P Doped Poly−Si膜)45とを備えている。HfO2膜32上に金属膜であるTiN膜41を使用しているので、空乏化層が生じることはなく、実効的なゲート絶縁膜の厚さが厚くなってしまうことを防止している。また、多結晶シリコン膜45とTiN膜41との間にTiAlN膜43を設けているので、ゲート電極40の形成後にソース領域21およびドレイン領域22の活性化アニールを行う際に、多結晶シリコン膜45中のSiが金属膜であるTiN膜41中に拡散するのを防止できる。その結果、多結晶シリコン膜45中のSiがTiN膜41中を通過してTiN膜41と高誘電率ゲート絶縁膜であるHfO2膜32との界面にまで到達するのを防止でき、閾値電圧が上昇するのを防止あるいは抑制でき、フラットバンド電圧が低下するのを防止あるいは抑制できる。

【0017】

次に、図2を参照して、本発明の好ましい一実施の形態のMOSFETの製造方法を説明する。

【0018】

まず、シリコン基板10を、例えば、1%HF水溶液で処理して、シリコン基板10の一主面11の犠牲酸化膜を除去する(ステップS101)。

【0019】

次に、シリコン基板10の一主面11の表面に、シリコン系絶縁膜としての酸化シリコン膜(SiO2膜)31を熱酸化により形成する(ステップS102)。SiO2膜31は、シリコン基板10と、その後に形成する高誘電率絶縁膜であるHfO2膜32と、の界面における界面層として形成される。SiO2膜31は、ゲート絶縁膜30の一部を構成することとなる。

【0020】

具体的には、例えば、酸化炉を用い、酸化炉の処理室内にシリコン基板10を収容し、この処理室内にO2ガス等の酸化性ガスを供給して、熱酸化(ドライ酸化)によりシリコン基板10の一主面11の表面に、界面層としてSiO2膜31を形成する。処理条件は、例えば、下記のとおりである。

シリコン基板10の温度:850〜1000℃

処理室内圧力:1〜1000Pa

O2ガス供給流量:10〜1000sccm

SiO2膜31の膜厚:0.4〜1.5nm

【0021】

なお、ドライ酸化の他に、ウェット酸化、減圧酸化、プラズマ酸化等によりSiO2膜31を形成するようにしてもよい。

【0022】

次に、SiO2膜31上に、高誘電率絶縁膜(High-k膜)として、酸化ハフニウム膜(HfO2膜)32を成膜する(ステップS103)。HfO2膜32はゲート絶縁膜30として形成される。

【0023】

具体的には、例えば、ALD(Atomic layer Deposition)炉を用い、ALD炉の処理室内に、SiO2膜31形成後のシリコン基板10を収容し、この処理室内へのTDMAHガスとO3ガスとの交互供給(TDMAHガス供給→N2パージ→O3ガス供給→N2パージを1サイクルとしてこのサイクルを所定回数繰り返すこと)によりSiO2膜31上にゲート絶縁膜としてHfO2膜32を形成する。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:100〜400℃

処理室内圧力:1〜2000Pa

TDMAHガス供給流量:10〜2000sccm

O3ガス供給流量:10〜2000sccm

N2ガス供給流量:10〜10000sccm

HfO2膜32の膜厚:0.9〜4nm

【0024】

Hfを含む原料としては、テトラキスジメチルアミノハフニウム(Hf[N(CH3)2]4、略称:TDMAH)の他、テトラキスエチルメチルアミノハフニウム(Hf[N(C2H5)(CH3)]4、略称:TEMAH)、テトラキスジエチルアミノハフニウム(Hf[N(C2H5)2]4、略称:TDEAH)などの有機原料や、ハフニウムテトラクロライド(HfCl4)などの無機原料を用いることができる。酸化剤としては、O3ガスの他、H2Oガス等の酸化性ガス(酸素含有ガス)を用いることができる。パージガス(不活性ガス)としては、N2ガスの他、Ar、He、Ne、Xe等の希ガスを用いることができる。なお、TDMAH等のように常温常圧下で液体状態である液体原料を用いる場合は、液体原料を気化器やバブラ等の気化システムにより気化して、原料ガスとして供給することとなる。

【0025】

HfO2膜32の成膜後、PDA(Post Deposition Annealing)が行われる(ステップS104)。具体的には、例えば、熱処理炉(例えばRTP(Rapid Thermal Process)装置)を用い、RTP装置の処理室内にHfO2膜32形成後のシリコン基板10を収容し、この処理室内にN2ガスを供給してアニールを行う。PDAは、HfO2膜32中の不純物除去、HfO2膜32の緻密化もしくは結晶化を目的として行う。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:400〜800℃

処理室内圧力:1〜1000Pa

N2ガス供給流量:10〜10000sccm

アニール時間:10〜60秒

【0026】

次に、PDA後のHfO2膜32上に、第1の金属膜、すなわち、導電性の第1の金属含有膜として窒化チタン膜(TiN膜)41を形成する(ステップS105)。TiN膜41はゲート電極40の一部を構成することとなる。

【0027】

具体的には、例えば、ALD炉を用い、ALD炉の処理室内にPDA後のシリコン基板10を収容し、この処理室内へのTiCl4ガスとNH3ガスとの交互供給(TiCl4ガス供給→N2パージ→NH3ガス供給→N2パージを1サイクルとしてこのサイクルを所定回数繰り返すこと)により、PDA後のHfO2膜32上にTiN膜41を形成する。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:300〜450℃

処理室内圧力:1〜10000Pa

TiCl4ガス供給流量:10〜10000sccm

NH3ガス供給流量:10〜50000sccm

N2ガス供給流量:10〜10000sccm

TiN膜41の膜厚:5〜20nm

【0028】

Tiを含む原料としては、無機原料であるチタニウムテトラクロライド(TiCl4)の他、テトラキスエチルメチルアミノチタニウム(Ti[N(C2H5)(CH3)]4、略称:TEMAT)、テトラキスジメチルアミノチタニウム(Ti[N(CH3)2]4、略称:TDMAT)、テトラキスジエチルアミノチタニウム(Ti[N(C2H5)2]4、略称:TDEAT)などの有機原料を用いることができる。窒化剤としては、アンモニア(NH3)ガスの他、ジアジン(N2H2)ガス、ヒドラジン(N2H4)ガス、N3H8ガス等の窒化性ガス(窒素含有ガス)を用いることができる。パージガス(不活性ガス)としては、N2ガスの他、Ar、He、Ne、Xe等の希ガスを用いることができる。なお、TiCl4等のように常温常圧下で液体状態である液体原料を用いる場合は、液体原料を気化器やバブラ等の気化システムにより気化して、原料ガスとして供給することとなる。

【0029】

次に、TiN膜41上に、第2の金属膜、すなわち、導電性の第2の金属含有膜として窒化アルミニウムチタン膜(TiAlN膜)43を形成する(ステップS106)。TiAlN膜43は、TiN膜にアルミニウム(Al)を添加した導電性の金属含有膜であり、その後に形成する多結晶シリコン膜45からTiN膜41とHfO2膜32との界面へのシリコン(Si)の拡散を防止する拡散防止膜、すなわち、Si拡散ブロック層として機能する。このTiAlN膜43により、多結晶シリコン膜45中のSiがTiN膜41を通過して、TiN膜41とHfO2膜32との界面にまで到達するのを防止できる。TiAlN膜43は、図1に示すように、多結晶シリコン膜45とTiN膜41との界面に形成されることとなる。

【0030】

TiAlN膜43はTiN膜41と共にゲート電極40の一部を構成することとなる。なお、TiN膜41とTiAlN膜43は、異なる成膜装置、すなわち異なる処理室にて別々に形成してもよいが、両膜は同様なコンディション下で成膜できることから、同一の処理室内でin−situにて連続的に形成するのが好ましい。

【0031】

具体的には、例えば、ALD炉を用い、ALD炉の処理室内にTiN膜41形成後のシリコン基板10を収容し、この処理室内へのTiCl4ガスとTMAガスとNH3ガスとの交互供給(TiCl4ガス供給→N2パージ→NH3ガス供給→N2パージを1サイクルとしてこのサイクルを所定回数(m回)行ってTiNを形成後、TMAガス供給→N2パージ→NH3ガス供給→N2パージを1サイクルとしてこのサイクルを1回行ってAlNを形成し、このTiNの形成とAlNの形成を1サイクルとしてこのサイクルを所定回数(n回)行うこと)によりTiN膜41上にTiNとAlNが交互に積層されてなるTiAlN膜43を形成する。なお、TiN膜41とTiAlN膜43は、同一の処理室内でin−situにて連続的に形成する。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:300〜450℃

処理室内圧力:1〜10000Pa

TiCl4ガス供給流量:10〜10000sccm

TMAガス供給流量:10〜10000sccm

NH3ガス供給流量:10〜50000sccm

N2ガス供給流量:10〜10000sccm

TiAlN膜43の膜厚:3〜20nm、好ましくは5〜10nm

【0032】

TiAlN膜43の膜厚を薄くして、3nm未満とすると、Si拡散のブロック効果が低下し、Siの拡散を十分に抑制できなくなることがある。TiAlN膜43の膜厚を3nm以上とすれば、十分なSi拡散のブロック効果が得られ、Siの拡散を十分に抑制することが可能となる。TiAlN膜43の膜厚を5nm以上とすれば、Siの拡散をより十分に抑制することが可能となる。一方、TiAlN膜43の膜厚を20nmより大きくすると、TiNの抵抗率よりもTiAlNの抵抗率が大きいので、ゲート電極40全体での抵抗率が必要以上に上がってしまうことがある。TiAlN膜43の膜厚を20nm以下とすることでこれを防止できる。特に、TiAlN膜43の膜厚を10nm以下とすることで、ゲート電極40全体での抵抗率の上昇をより抑えることが可能となり、より適正な値とすることが可能となる。よって、TiAlN膜43の膜厚は、好ましくは3〜20nm、より好ましくは5〜10nmとするのがよい。また、TiAlN膜43のAl濃度を10%未満とすると、Al濃度が低くなり過ぎて、Si拡散のブロック効果が低下し、Siの拡散を十分に抑制できなくなることがある。TiAlN膜43のAl濃度を10%以上とすれば、十分なSi拡散のブロック効果が得られ、Siの拡散を十分に抑制することが可能となる。一方、TiAlN膜43のAl濃度を20%より大きくすると、TiAlN膜43の絶縁性が強くなり、抵抗率が大きくなり、ゲート電極40全体での抵抗率が必要以上に大きくなってしまうことがある。TiAlN膜43のAl濃度を20%以下とすることでこれを防止できる。よって、TiAlN膜43のAl濃度は、好ましくは10〜20%とするのがよい。

【0033】

なお、Tiを含む原料、窒化剤、パージガス(不活性ガス)としては、TiN膜41の成膜工程(ステップS105)におけるそれらと同様のものを用いることができる。Alを含む原料としては、有機原料であるトリメチルアルミニウム(Al(CH3)3、略称:TMA)の他、トリクロロアルミニウム(AlCl3)などの無機原料を用いることができる。なお、TMA等のように常温常圧下で液体状態である液体原料を用いる場合は、液体原料を気化器やバブラ等の気化システムにより気化して、原料ガスとして供給することとなる。

【0034】

なお、TiAlN膜43は、図3に示すようにTiN膜41中、すなわち上側のTiN膜41と下側のTiN膜41との間に形成するようにしてもよい。但し、この場合、図3に示すように、TiAlN膜43はHfO2膜32から2nm以上離間させることが好ましい。TiAlN膜43とHfO2膜32との距離を2nm未満、例えば1nmとすると、TiAlN膜43の仕事関数の影響が出てしまい、Vfb(フラットバンド電圧)に影響を及ぼすことがあるからである。TiAlN膜43をHfO2膜32から2nm以上離せば、その影響がなくなる。

【0035】

次に、TiAlN膜43上に、多結晶シリコン膜45、すなわち、ポリシリコン膜(Poly−Si膜)45を形成する(ステップS107)。Poly−Si膜45には、後述するイオン注入工程において、不純物(ドーパント)としてリン(P)もしくはボロン(B)がドーピングされ、Poly−Si膜45は、リンドープポリシリコン膜(P Doped Poly−Si膜)もしくはボロンドープポリシリコン膜(B Doped Poly−Si膜)となる。本実施の形態では、リンドープポリシリコン膜(P Doped Poly−Si膜)を形成している。Poly−Si膜45はTiAlN膜43およびTiN膜41と共にゲート電極40の一部を構成することとなる。

【0036】

具体的には、例えば、CVD炉を用い、CVD炉の処理室内にTiAlN膜43形成後のシリコン基板10を収容し、この処理室内へのモノシラン(SiH4)ガスの連続供給により、TiAlN膜43上にPoly−Si膜45を形成する。シリコン原料ガスとしては、SiH4ガスの他、ジシラン(Si2H6)ガスやジクロロシラン(SiH2Cl2)ガス等のシラン系ガスを用いてもよい。このとき、希釈ガスとしてN2ガス等の不活性ガスを同時に供給してもよい。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:600〜700℃

処理室内圧力:10〜48000Pa

SiH4ガス供給流量:10〜20000sccm

N2ガス供給流量:10〜10000sccm

Poly−Si膜45の膜厚:50〜200nm

【0037】

その後、ゲート電極40の上に選択的に形成されたレジスト(図示せず)をマスクにして、ゲート電極40のフォトリソグラフィ技術を用いたパターニング(Patterning)およびドライエッチング技術を用いたパターンエッチング(Etching)を行う(ステップS108)。その後、レジスト(図示せず)を除去する(ステップS109)。このように、ゲート電極40を加工した後、ゲート絶縁膜30も同様に加工し、シリコン基板10の一主面11の表面を露出させる。なお、ゲート絶縁膜30の加工は、別途、ウェットエッチングにより行うようにしてもよい。

【0038】

次に、Poly−Si膜45上に、SiO2膜(図示せず)を形成する(ステップS110)。具体的には、例えば、CVD炉を用い、CVD炉の処理室内に、パターニング、エッチングおよびレジスト除去後のシリコン基板10を収容し、この処理室内に、TEOSガスを供給してPoly−Si膜45上にSiO2膜を形成する。SiO2膜は、次のイオン注入工程においてPoly−Si膜45に注入されるリン(P)のPoly−Si膜45からのアウトディフュージョン(外方拡散)を防止するキャップ膜として形成される。SiO2膜は、また、ソース領域21およびドレイン領域22が形成されることとなるシリコン基板10の一主面11の表面上にも形成され、ソース領域21およびドレイン領域22用にイオン注入する際のチャネリング防止膜等としても機能する。Poly−Si膜45の膜厚とイオン注入工程における注入エネルギーにもよるが、SiO2膜の膜厚は例えば、5〜20nmとする。

【0039】

次に、イオン注入装置にてイオン注入法によりSiO2膜越しにソース領域21、ドレイン領域22やPoly−Si膜45に不純物(ドーパント)を注入する(ステップS111)。本実施の形態では、Poly−Si膜45にリン(P)を注入する。これにより、Poly−Si膜45はリンドープポリシリコン膜(P Doped Poly−Si膜)となる。また、ソース領域21やドレイン領域22には、リン(P)またはボロン(B)を注入する。例えば、リンを注入する際は、リンの固体ソースを用いる。ソース領域21、ドレイン領域22の不純物の濃度分布等やPoly−Si膜45中の不純物の濃度等に応じて複数回イオン注入を行う。リンをイオン注入する際の注入エネルギーは例えば30keVとする。なお、ポリシリコン膜(Poly−Si膜)45を形成する工程(ステップS107)にて、CVD炉で、SiH4ガスとPH3とを用いて、P Doped Poly−Si膜45を形成することも可能である。

【0040】

次に、ソース領域21、ドレイン領域22およびP Doped Poly−Si膜45の活性化アニールを行う(ステップS112)。具体的には、例えば、熱処理炉(アニール装置)を用い、アニール装置の処理室内にイオン注入後のシリコン基板10を収容し、この処理室内に、N2ガスを供給して、1000℃で活性化アニールを行う。処理条件は、例えば下記のとおりである。

シリコン基板10の温度:950〜1050℃の範囲内、例えば1000℃

処理室内圧力:1〜1000Pa(なお、加熱するのが目的なので、大気圧でもよい) N2ガス供給流量:10〜10000sccm

アニール時間:0.05秒(50msec)〜20秒

【0041】

なお、本実施の形態では、多結晶シリコン膜45とTiN膜41との間にTiAlN膜43が形成されているので、この活性化アニールの際に、多結晶シリコン膜45中のSiがTiN膜41を通過して、TiN膜41とHfO2膜32との界面にまで到達するのを防止できる。すなわち、本実施の形態におけるTiAlN膜43は、Siの拡散をブロックするSi拡散ブロック層(Si拡散バリア層)として機能する。

【0042】

その後、400℃、10分の水素ガスアニーリング等のFGA(Forming gas annealing)処理を行う(ステップS113)。このようにして、MIPS構造のMOS構造を形成する。

【0043】

次に、図11を参照して、本発明の好ましい他の実施の形態を説明する。上述した、好ましい一実施の形態のMOSFET100では、ゲート絶縁膜30として、シリコン基板10の一主面11上に設けられたSiO2膜31とSiO2膜31上に設けられた高誘電率絶縁膜であるHfO2膜32とを備えていたが、本発明の好ましい他の実施の形態のMOSFET102では、ゲート絶縁膜30として、シリコン基板10の一主面11上に設けられた高誘電率絶縁膜であるHfO2膜32のみを備え、SiO2膜31を備えていない点が一実施の形態のMOSFET100と異なるが、他の点は同じである。

【0044】

本実施の形態においても、高誘電率絶縁膜であるHfO2膜32を使用することにより、ゲートリーク電流を低減している。また、ゲート電極40は、ゲート絶縁膜30のHfO2膜32上に設けられたTiN膜41と、TiN膜41上に設けられたTiAlN膜43と、TiAlN膜43上に設けられたPをドーピングした多結晶シリコン膜45とを備えており、HfO2膜32上に金属膜であるTiN膜41を使用しているので、空乏化層が生じることはなく、実効的なゲート絶縁膜の厚さが厚くなってしまうことを防止している。また、多結晶シリコン膜45とTiN膜41との間にTiAlN膜43を設けているので、ゲート電極40の形成後にソース領域21およびドレイン領域22の活性化アニールを行う際に、多結晶シリコン膜45中のSiが金属膜であるTiN膜41中に拡散するのを防止できる。その結果、多結晶シリコン膜45中のSiがTiN膜41中を通過してTiN膜41と高誘電率ゲート絶縁膜であるHfO2膜32との界面にまで到達するのを防止でき、閾値電圧が上昇するのを防止あるいは抑制でき、フラットバンド電圧が低下するのを防止あるいは抑制できる。

【0045】

上記本発明の好ましい実施の形態においては、シリコン基板と高誘電率絶縁膜であるHfO2膜との界面層としてのシリコン系絶縁膜として、SiO2膜を用いたが、SiO2膜の他、酸窒化シリコン膜(SiON膜)を用いてもよい。また、高誘電率ゲート絶縁膜として、HfO2膜を用いたが、HfO2膜の他、酸化ジルコニウム膜(ZrO2膜)、酸化チタン膜(TiO2膜)、酸化ニオブ膜(Nb2O5膜)、酸化タンタル膜(Ta2O5膜)、ハフニウムシリケート膜(HfSiOx膜)、ジルコニウムシリケート膜(ZrSiOx膜)、ハフニウムアルミネート膜(HfAlOx膜)、ジルコニウムアルミネート膜(ZrAlOx膜)や、これらを組み合わせたり混合させたりした膜を用いてもよい。

【0046】

ゲート電極の一部を構成することとなる、高誘電率ゲート絶縁膜上の金属含有膜としては、TiN膜の他、窒化ハフニウム膜(HfN膜)、窒化ジルコニウム膜(ZrN)、窒化タンタル膜(TaN膜)、タングステン膜(W膜)、窒化タングステン膜(WN膜)等を用いてもよい。

【0047】

また、ゲート電極の一部を構成することとなり、Si拡散防止膜として用いられる金属含有膜としては、TiAlN膜の他、TaAlN膜やTaCAlN膜、TiCAlN膜、TaCAl膜、TiCAl膜、HfAlN膜、ZrAlN膜などの窒素および炭素のうち少なくとも一方とAlを含む金属膜や、W膜やTa膜、Ti膜などの金属膜中へAlを添加したものも用いることができる。

【0048】

なお、本明細書では、金属膜という用語は、金属原子を含む導電性の物質で構成される膜、すなわち、導電性の金属含有膜を意味しており、これには、金属単体で構成される導電性の金属単体膜の他、導電性の金属窒化膜、導電性の金属酸化膜、導電性の金属酸窒化膜、導電性の金属炭化膜(金属カーバイド膜)、導電性の金属炭窒化膜、導電性の金属複合膜、導電性の金属合金膜、導電性の金属シリサイド膜等も含まれる。なお、TiN膜は導電性の金属窒化膜であり、TiAlN膜は導電性の金属複合膜である。

【0049】

上記実施形態におけるステップS102〜S107の少なくとも一部のステップについては、基板処理システムとしてのクラスタ装置を用いて連続的に行うようにしてもよい。

【0050】

例えば、ステップS102〜S103までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS102〜S104までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS102〜S105までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS102〜S106までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS102〜S107までをクラスタ装置を用いて連続的に行うようにしてもよい。

【0051】

また、例えば、ステップS103〜S104までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS103〜S105までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS103〜S106までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS103〜S107までをクラスタ装置を用いて連続的に行うようにしてもよい。

【0052】

また、例えば、ステップS105〜S106までをクラスタ装置を用いて連続的に行うようにしてもよく、また例えば、ステップS105〜S107までをクラスタ装置を用いて連続的に行うようにしてもよい。

【0053】

例えば、ステップS102〜S107の全てのステップをクラスタ装置を用いて連続的に行う場合、図12に示すようなクラスタ装置200を用いて行うことができる。

【0054】

基板処理システムとしてのクラスタ装置200は、シリコン基板10を処理する処理部としての処理室201、202、203、204、205、シリコン基板10をクラスタ装置200に搬入する搬入室208、シリコン基板10をクラスタ装置200から搬出する搬出室209、シリコン基板10を冷却する冷却室206、207、処理室201、202、203、204、205、搬入室208、搬出室209、冷却室206、207が取り付けられ、シリコン基板10をこれらの室の間で移載する移載機211が設けられた移載室210を備えている。移載室210と、処理室201、202、203、204、205、搬入室208、搬出室209との間には、ゲートバルブ201a、202a、203a、204a、205a、208a、209aがそれぞれ設けられている。搬入室208、搬出室209には、ゲートバルブ208a、209aと反対側にゲートバルブ208b、209bがそれぞれ設けられている。

【0055】

クラスタ装置200は、また、処理室201、202、203、204、205内にガス配管334を介して処理ガスや不活性ガスを供給し、移載室210、搬入室208、搬出室209、冷却室206、207内にガス配管334を介して不活性ガスを供給するガス供給系333と、処理室201、202、203、204、205、移載室210、搬入室208、搬出室209、冷却室206、207内を排気配管337を介して排気する排気系336と、を備えている。

【0056】

図12、図13を参照すれば、クラスタ装置200は、さらに、ゲートバルブ201a、202a、203a、204a、205a、208a、209a、208b、209bの開閉動作を制御するゲートバルブ制御部231、移載機211の動作を制御する移載機制御部232、ガス供給系333を制御するガス供給系制御部233、排気系336を制御する排気系制御部236、処理室201、202、203、204、205内の温度を制御する温度制御部237、処理室201、202、203、204、205、移載室210、搬入室208、搬出室209、冷却室206、207内の圧力を制御する圧力制御部238等を備えている。図13を参照すれば、クラスタ装置200は、さらに、コントローラ220を備えている。コントローラ220については、後に詳述する。

【0057】

このクラスタ装置200では、例えば、次のようにしてシリコン基板10を処理する。

【0058】

ゲートバルブ208bを開き、搬入用予備室としての搬入室(ロードロック室)208内にシリコン基板10としてのウエハ10を搬入する。搬入後、ゲートバルブ208bを閉じ、搬入室208内を真空排気する。搬入室208内が所定の圧力になると、ゲートバルブ208aが開かれる。なお、移載室210内は予め真空排気され、所定の圧力に維持されている。

【0059】

ゲートバルブ208aが開かれると、ウエハ10がウエハ移載機211によりピックアップされ、搬入室208内から移載室210内に取り出される。その後、ゲートバルブ208aが閉じられる。ゲートバルブ208aが閉じられると、ゲートバルブ201aが開かれ、ウエハ10がウエハ移載機211により、移載室210内から第1の処理室201内に搬入される。搬入後、ゲートバルブ201aが閉じられ、処理室201内でウエハ10上にSiO2膜を形成する処理が行われる(ステップS102)。

【0060】

その後、ゲートバルブ201aが開かれ、SiO2膜を形成した後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室201内から移載室210内に取り出される。その後、ゲートバルブ201aが閉じられる。ゲートバルブ201aが閉じられると、ゲートバルブ202aが開かれ、SiO2膜を形成した後のウエハ10が、ウエハ移載機211により、移載室210内から処理室202内に搬入される。搬入後、ゲートバルブ202aが閉じられ、処理室202内で、ウエハ10上のSiO2膜上にHfO2膜を形成する処理が行われる(ステップS103)。

【0061】

その後、ゲートバルブ202aが開かれ、HfO2膜を形成した後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室202内から移載室210内に取り出される。その後、ゲートバルブ202aが閉じられる。ゲートバルブ202aが閉じられると、ゲートバルブ203aが開かれ、HfO2膜を形成した後のウエハ10が、ウエハ移載機211により、移載室210内から処理室203内に搬入される。搬入後、ゲートバルブ203aが閉じられ、処理室203内で、ウエハ10上のHfO2膜に対してPDA処理が行われる(ステップS104)。

【0062】

その後、ゲートバルブ203aが開かれ、PDA後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室203内から移載室210内に取り出される。その後、ゲートバルブ203aが閉じられる。ゲートバルブ203aが閉じられると、ゲートバルブ204aが開かれ、PDA後のウエハ10が、ウエハ移載機211により、移載室210内から処理室204内に搬入される。搬入後、ゲートバルブ204aが閉じられ、処理室204内で、ウエハ10上のPDA後のHfO2膜上に、TiN膜を形成する処理と、TiAlN膜を形成する処理と、がin−situにて連続的に行われる(ステップS105、S106)。このとき、TiN膜とTiAlN膜は、図1のように積層して形成してもよいし、図3のように積層して形成してもよい。

【0063】

その後、ゲートバルブ204aが開かれ、TiN膜およびTiAlN膜形成後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室204内から移載室210内に取り出される。その後、ゲートバルブ204aが閉じられる。ゲートバルブ204aが閉じられると、ゲートバルブ205aが開かれ、TiN膜およびTiAlN膜形成後のウエハ10が、ウエハ移載機211により、移載室210内から処理室205内に搬入される。搬入後、ゲートバルブ205aが閉じられ、処理室205内で、ウエハ10上のTiAlN膜(図1参照)またはTiN膜(図3参照)上に、Poly−Si膜を形成する処理が行われる(ステップS107)。

【0064】

その後、ゲートバルブ205aが開かれ、Poly−Si膜形成後のウエハ10が、ウエハ移載機211によりピックアップされ、処理室205内から移載室210内に取り出される。その後、ゲートバルブ205aが閉じられる。ゲートバルブ205aが閉じられると、ゲートバルブ209aが開かれ、ステップS102〜S107の一連の処理を終えたウエハ10が、ウエハ移載機211により、移載室210内から搬出用予備室としての搬出室(ロードロック室)209内に搬送される。搬送後、ゲートバルブ209aが閉じられ、搬出室209内が大気圧に戻された後、ゲートバルブ209bが開かれ、一連の処理後のウエハ10が取り出される。

【0065】

なお、上記各ステップを実施した後のウエハ10は、必要に応じて、冷却室206、冷却室207内に搬送され、冷却される場合もある。その場合、ウエハ10は、所定の温度となるまで冷却室206または冷却室207内にて待機させられ、所定の温度まで冷却された後、次のステップを行うための処理室内に搬送され、あるいは搬出室209を介して搬出されることとなる。

【0066】

次に、ステップS102〜S107の全てのステップを連続的に行うクラスタ装置の他の例を、図14を参照して説明する。図12に示すクラスタ装置200は、5つの処理室

処理室201、202、203、204、205を備えていたが、図14に示すクラスタ装置300は、6つの処理室201、202、203、204、254、205を備えている点が図12に示すクラスタ装置200と異なるが他の点は同様である。

【0067】

図14に示すクラスタ装置300では、移載室210と、処理室254との間に、ゲートバルブ254aが設けられている。処理室254内には、ガス配管334を介して処理ガスや不活性ガスがガス供給系333から供給される。処理室254内は、排気配管337を介して排気系336によって排気される。ゲートバルブ254aの開閉動作は、ゲートバルブ制御部231によって制御され、処理室254内の温度は、温度制御部237によって制御される。処理室254内の圧力は圧力制御部238によって制御される。

【0068】

図12に示すクラスタ装置200では、処理室204内で、ウエハ10上のPDA後のHfO2膜上に、TiN膜を形成する処理と、TiAlN膜を形成する処理と、を連続的に行ったが、図14に示すクラスタ装置300では、処理室204内で、TiN膜を形成する処理を行い、処理室254内で、TiAlN膜を形成する処理を行う。

【0069】

なお、上記一連の処理は、クラスタ装置200、300を構成する各部の動作を、コントローラ220により制御することで行われる。

【0070】

図13を参照すれば、制御部(制御手段)であるコントローラ220は、CPU(Central Processing Unit)121a、RAM(Random Access Memory)121b、記憶装置121c、I/Oポート121dを備えたコンピュータとして構成されている。RAM121b、記憶装置121c、I/Oポート121dは、内部バス121eを介して、CPU121aとデータ交換可能なように構成されている。コントローラ220には、例えばタッチパネル等として構成された入出力装置122が接続されている。

【0071】

記憶装置121cは、例えばフラッシュメモリ、HDD(Hard Disk Drive)等から構成されている。記憶装置121c内には、クラスタ装置200の動作を制御する制御プログラムや、上述の一連のウエハ処理の手順や条件などが記載されたプロセスレシピ等が、読み出し可能に格納されている。なお、プロセスレシピは、上述の一連のウエハ処理における各手順(各ステップ)をコントローラ220に実行させ、所定の結果を得ることが出来るように組み合わされたものであり、プログラムとして機能する。以下、このプロセスレシピや制御プログラム等を総称して、単にプログラムともいう。なお、本明細書においてプログラムという言葉を用いた場合は、プロセスレシピ単体のみを含む場合、制御プログラム単体のみを含む場合、または、その両方を含む場合がある。また、RAM121bは、CPU121aによって読み出されたプログラムやデータ等が一時的に保持されるメモリ領域(ワークエリア)として構成されている。

【0072】

I/Oポート121dは、バス240を介して、上述のゲートバルブ制御部231、移載機制御部232、ガス供給系制御部233、排気系制御部236、温度制御部237、圧力制御部238等に接続されている。

【0073】

CPU121aは、記憶装置121cから制御プログラムを読み出して実行すると共に、入出力装置122からの操作コマンドの入力等に応じて記憶装置121cからプロセスレシピを読み出すように構成されている。そして、CPU121aは、読み出したプロセスレシピの内容に沿うように、ゲートバルブ制御部231、移載機制御部232、ガス供給系制御部233、排気系制御部236、温度制御部237、圧力制御部238等を制御して、ゲートバルブ201a、202a、203a、204a、254a、205a、208a、209a、208b、209b、移載機211、ガス供給系333、排気系336、処理室201、202、203、204、254、205を加熱するヒータ(図示せず)等の動作を制御するように構成されている。

【0074】

なお、コントローラ220は、専用のコンピュータとして構成されている場合に限らず、汎用のコンピュータとして構成されていてもよい。例えば、上述のプログラムを格納した外部記憶装置(例えば、磁気テープ、フレキシブルディスクやハードディスク等の磁気ディスク、CDやDVD等の光ディスク、MO等の光磁気ディスク、USBメモリやメモリカード等の半導体メモリ)123を用意し、係る外部記憶装置123を用いて汎用のコンピュータにプログラムをインストールすること等により、本実施形態に係るコントローラ220を構成することができる。なお、コンピュータにプログラムを供給するための手段は、外部記憶装置123を介して供給する場合に限らない。例えば、インターネットや専用回線等の通信手段を用い、外部記憶装置123を介さずにプログラムを供給するようにしてもよい。なお、記憶装置121cや外部記憶装置123は、コンピュータ読み取り可能な記録媒体として構成される。以下、これらを総称して、単に記録媒体ともいう。なお、本明細書において記録媒体という言葉を用いた場合は、記憶装置121c単体のみを含む場合、外部記憶装置123単体のみを含む場合、または、その両方を含む場合がある。

【0075】

なお、基板処理システムとして、クラスタ装置の代わりに、各ステップにおける処理をそれぞれ単独で行うスタンドアローンタイプの装置をそれぞれ準備して、これらの一連の処理を行うようにしてもよい。また、上述の各実施形態や各応用例等は、適宜組み合わせて用いることができる。

【0076】

また、本発明は、例えば、既存の基板処理システムのプロセスレシピを変更することでも実現できる。プロセスレシピを変更する場合は、本発明に係るプロセスレシピを電気通信回線や当該プロセスレシピを記録した記録媒体を介して既存の基板処理システムにインストールしたり、また、既存の基板処理システムの入出力装置を操作し、そのプロセスレシピ自体を本発明に係るプロセスレシピに変更することも可能である。

【実施例1】

【0077】

本発明の好ましい一実施の形態のMOSFET用の評価サンプルと、比較例の評価サンプルを作成し、それらの電気的特性等の特性を比較した。

【0078】

まず、図4を参照して、本発明の好ましい一実施の形態のMOSFET用の評価サンプル200を説明する。図1の本発明の好ましい一実施の形態のMOSFET100では、ソース領域21およびドレイン領域22が存在したが、この評価サンプル200ではソース領域21およびドレイン領域22が存在しない点が一実施の形態のMOSFET100と異なるが、他の点は同じであるので、説明は省略する。また、製造方法も、図2を参照して説明した製造方法と同様であるので、説明は省略する。但し、評価サンプル200の製造では、FGA処理(ステップS113)の後に、酸化防止等の目的で、シリコン基板10の裏面へのAl成膜を行った。

【0079】

次に、図5を参照して、比較例の評価サンプル202を説明する。図4の本発明の好ましい一実施の形態のMOSFET用の評価サンプルでは、TiAlN膜43が存在したが、比較例の評価サンプル202では、TiAlN膜43がなく、多結晶シリコン膜45とTiN膜41からなるゲート電極42を備える点が一実施の形態のMOSFET用の評価サンプルと異なる。他の点は同じであるので、説明は省略する。また、この評価サンプル202の製造方法も、評価サンプル200の製造方法において、TiAlN膜43を成膜するステップS106がないだけで、それ以外は同じなので、説明は省略する(図6参照)。

【0080】

図7は、本発明の好ましい一実施の形態のMOSFET用の評価サンプル200のC−V特性を示す図であり、図8は、比較例に係る評価サンプル202のC−V特性を示す図である。図7、図8の横軸は、C−V特性の測定に際してゲート電極に印加したゲート電圧Vg(V)を示しており、縦軸は、静電容量C(μF/cm2)を示している。図7、図8中の●印は1000℃の活性化アニール処理を行わなかった場合(以下、1000℃処理無し、ともいう)、□印は1000℃活性化アニール処理を行った場合(以下、1000℃処理有り、ともいう)を示している。図9は、図7、図8に示すそれぞれのC−Vカーブから抽出したEOT(等価酸化膜厚)およびVfb(フラットバンド電圧)を示した表である。

【0081】

図7、8、9より、比較例では、1000℃処理無しの場合と比較し、1000℃処理有りの場合ではEOTは増加し、かつ、Vfbは負方向へシフトしていることがわかる。これは、多結晶シリコン膜45中のSiがTiN膜41中に拡散し、TiN膜41とHfO2膜32との界面にまで到達したことによって、その界面においてSi−O結合が生じ、その結果、EOTが増加したものと考えられる。また、多結晶シリコン膜45中のSiがTiN膜41とHfO2膜32との界面にまで到達したことによって、フェルミレベルピニング現象が生じ、その結果、仕事関数が低下してVfbが負方向へシフトしたものと考えられる。なお、Vfbが負方向へシフトすると、閾値電圧が増加してしまう。一方、本発明の好ましい一実施の形態による構造では、1000℃処理無しの場合と比較し、1000℃処理有りの場合ではEOTは薄くなり、かつ、Vfbは正方向へシフトしていることがわかる。Vfbが正方向へシフトすると、閾値電圧が減少する。EOTの薄膜化は、1000℃処理によるHfO2膜32の緻密化によるものと考えられる。このように、TiN膜41上にTiAlN膜43を設けることで、多結晶シリコン膜45からのSi拡散を防止または抑制でき、それにより、多結晶シリコン膜45中のSiがTiN膜41とHfO2膜32との界面にまで到達することを防止または抑制できる。そしてそれにより、閾値電圧が上昇するのを防止または抑制でき、Vfbの低下を防止または抑制できる。

【0082】

次に、図10を参照して、他の比較例の評価サンプル204を説明する。この比較例に係る評価サンプル204では、TiN膜41を設けずに、HfO2膜32上にTiAlN膜43を設け、TiAlN膜43上に多結晶シリコン膜45を設けている。この場合には、多結晶シリコン膜45からのSiの拡散は、TiAlN膜43で阻止される。しかしながら、TiAlN膜43中のAlがHfO2膜32内に拡散してEOTを増加させてしまう。また、TiAlNの仕事関数がTiNより小さいため、ゲートリーク電流が大きくなってしまう。これに対して、図4を参照して説明した、本発明の好ましい一実施の形態のMOSFET用の評価サンプル200では、TiAlN膜43を設けているので、多結晶シリコン膜45からのSiの拡散を阻止できるだけでなく、TiAlN膜43とHfO2膜32との間にTiN膜41を設けているので、TiAlN膜43中のAlがHfO2膜32内に拡散するのを防止または抑制でき、その結果、EOTが増加するのを防止または抑制できる。さらに、ゲート絶縁膜であるHfO2膜32上には、TiN膜41が存在し、TiNの仕事関数がTiAlNより大きいため、ゲートリーク電流は小さくなる。

【0083】

(本発明の好ましい態様)

以下に、本発明の好ましい態様について付記する。

【0084】

(付記1)

本発明の好ましい一態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の第1の金属含有膜と、

前記第1の金属含有膜上に形成され、アルミニウムを添加してなる導電性の第2の金属含有膜と、

前記第2の金属含有膜上に形成されたシリコン膜と、

を有する半導体装置が提供される。

【0085】

(付記2)

付記1の半導体装置であって、好ましくは、前記第2の金属含有膜は、前記第1の金属含有膜にアルミニウムを添加してなる導電性の金属含有膜である。

【0086】

(付記3)

付記1または2の半導体装置であって、好ましくは、前記ゲート絶縁膜は高誘電率絶縁膜を含む。

【0087】

(付記4)

付記1または2の半導体装置であって、好ましくは、前記ゲート絶縁膜は、シリコン系絶縁膜と、該シリコン系絶縁膜上に形成された高誘電率絶縁膜と、を含む。

【0088】

(付記5)

付記1〜4のいずれかの半導体装置であって、好ましくは、前記第2の金属含有膜はTiAlN膜を含む。

【0089】

(付記6)

付記1〜4のいずれかの半導体装置であって、好ましくは、前記第1の金属含有膜はTiN膜を含み、前記第2の金属含有膜はTiAlN膜を含む。

【0090】

(付記7)

本発明の好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する工程と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する工程と、

前記第2の金属含有膜上にシリコン膜を形成する工程と、

を有する半導体装置の製造方法が提供される。

【0091】

(付記8)

付記7の半導体装置の製造方法であって、好ましくは、前記第2の金属含有膜は、前記第1の金属含有膜にアルミニウムを添加してなる導電性の金属含有膜である。

【0092】

(付記9)

付記7または8半導体装置の製造方法であって、好ましくは、前記ゲート絶縁膜は高誘電率絶縁膜を含む。

【0093】

(付記10)

付記7または8の半導体装置の製造方法であって、好ましくは、前記ゲート絶縁膜は、シリコン系絶縁膜と、該シリコン系絶縁膜上に形成された高誘電率絶縁膜と、を含む。

【0094】

(付記11)

付記7〜10のいずれかの半導体装置の製造方法であって、好ましくは、前記第2の金属含有膜はTiAlN膜を含む。

【0095】

(付記12)

付記7〜10のいずれかの半導体装置の製造方法であって、好ましくは、前記第1の金属含有膜はTiN膜を含み、前記第2の金属含有膜はTiAlN膜を含む。

【0096】

(付記13)

付記7〜12のいずれかの半導体装置の製造方法であって、好ましくは、前記シリコン膜を形成する工程の後に、活性化アニールを行う工程を有する。

【0097】

(付記14)

本発明のさらに好ましい他の態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の金属含有膜と、

前記金属含有膜上に形成されたシリコン膜と、を有し、

前記金属含有膜と前記シリコン膜との間には、前記シリコン膜から前記金属含有膜中へのシリコンの拡散を防止する拡散防止膜が設けられている半導体装置が提供される。

【0098】

(付記15)

本発明のさらに好ましい他の態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の金属含有膜と、

前記金属含有膜上に形成されたシリコン膜と、を有し、

前記金属含有膜中には、前記シリコン膜から前記金属含有膜と前記絶縁膜との界面へのシリコンの拡散を防止する拡散防止膜が設けられている半導体装置が提供される。

【0099】

(付記16)

付記14または15の半導体装置であって、好ましくは、前記拡散防止膜は、前記シリコン膜と接触するように設けられる。

【0100】

(付記17)

付記14または15の半導体装置であって、好ましくは、前記拡散防止膜は、前記金属含有膜と前記シリコン膜との界面に設けられる。

【0101】

(付記18)

付記14〜17のいずれかの半導体装置であって、好ましくは、前記ゲート絶縁膜は高誘電率絶縁膜を含む。

【0102】

(付記19)

付記14〜17のいずれかの半導体装置であって、好ましくは、前記ゲート絶縁膜はシリコン系絶縁膜と、該シリコン系絶縁膜上に形成された高誘電率絶縁膜と、を含む。

【0103】

(付記20)

付記14〜19のいずれかの半導体装置であって、好ましくは、前記拡散防止膜が前記金属含有膜にアルミニウムを添加した導電性の金属含有膜である。

【0104】

(付記21)

付記20の半導体装置であって、好ましくは、前記拡散防止膜はTiAlN膜を含む。

【0105】

(付記22)

付記14〜20のいずれかの半導体装置であって、好ましくは、前記金属含有膜はTiN膜を含み、前記拡散防止膜はTiAlN膜を含む。

【0106】

(付記23)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の金属含有膜を形成する工程と、

前記金属含有膜上にシリコン膜を形成する工程と、を有し、

前記金属含有膜と前記シリコン膜との間に、前記シリコン膜から前記金属含有膜中へのシリコンの拡散を防止する拡散防止膜を形成する工程を有する半導体装置の製造方法が提供される。

【0107】

(付記24)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の金属含有膜を形成する工程と、

前記金属含有膜上にシリコン膜を形成する工程と、を有し、

前記金属含有膜を形成する工程では、前記金属含有膜中に、前記シリコン膜から前記金属含有膜と前記ゲート絶縁膜との界面へのシリコンの拡散を防止する拡散防止膜を形成する半導体装置の製造方法が提供される。

【0108】

(付記25)

付記23または24の半導体装置の製造方法であって、好ましくは、前記拡散防止膜は、前記シリコン膜と接触するように設けられる。

【0109】

(付記26)

付記23または24の半導体装置の製造方法であって、好ましくは、前記拡散防止膜は、前記金属含有膜と前記シリコン膜との界面に設けられる。

【0110】

(付記27)

付記23〜26のいずれかの半導体装置の製造方法であって、好ましくは、前記ゲート絶縁膜は高誘電率絶縁膜を含む。

【0111】

(付記28)

付記23〜26のいずれかの半導体装置の製造方法であって、好ましくは、前記ゲート絶縁膜はシリコン系絶縁膜と、該シリコン系絶縁膜上に形成された高誘電率絶縁膜と、を含む。

【0112】

(付記29)

付記23〜28のいずれかの半導体装置の製造方法であって、好ましくは、前記拡散防止膜が前記金属含有膜にアルミニウムを添加した導電性の金属含有膜である。

【0113】

(付記30)

付記29の半導体装置の製造方法であって、好ましくは、前記拡散防止膜はTiAlN膜を含む。

【0114】

(付記31)

付記23〜29のいずれかの半導体装置の製造方法であって、好ましくは、前記金属含有膜はTiN膜を含み、前記拡散防止膜はTiAlN膜を含む。

【0115】

(付記32)

付記23〜31のいずれかの半導体装置の製造方法であって、好ましくは、前記シリコン膜を形成する工程の後に、活性化アニールを行う工程を有する。

【0116】

(付記33)

本発明のさらに好ましい他の態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、電圧を印加した場合に空乏化層が生じない導電性膜と、

前記導電性膜上に形成されたシリコン膜と、を有し、

前記導電性膜と前記シリコン膜との間には、前記シリコン膜から前記導電性膜中へのシリコンの拡散を防止する拡散防止膜が設けられている半導体装置が提供される。

【0117】

(付記34)

本発明のさらに好ましい他の態様によれば、

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、電圧を印加した場合に空乏化層が生じない導電性膜と、

前記導電性膜上に形成されたシリコン膜と、を有し、

前記導電性膜中には、前記シリコン膜から前記導電性膜と前記絶縁膜との界面へのシリコンの拡散を防止する拡散防止膜が設けられている半導体装置が提供される。

【0118】

(付記35)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、電圧を印加した場合に空乏化層が生じない導電性膜を形成する工程と、

前記導電性膜上にシリコン膜を形成する工程と、を有し、

前記導電性膜と前記シリコン膜との間に、前記シリコン膜から前記導電性膜中へのシリコンの拡散を防止する拡散防止膜を形成する工程を有する半導体装置の製造方法が提供される。

【0119】

(付記36)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に、電圧を印加した場合に空乏化層が生じない導電性膜を形成する工程と、

前記導電性膜上にシリコン膜を形成する工程と、を有し、

前記導電性膜を形成する工程では、前記導電性膜中に、前記シリコン膜から前記導電性膜と前記ゲート絶縁膜との界面へのシリコンの拡散を防止する拡散防止膜を形成する半導体装置の製造方法が提供される。

【0120】

(付記37)

本発明のさらに好ましい他の態様によれば、

基板上に形成された高誘電率絶縁膜と、

前記高誘電率絶縁膜上に形成されたTiN膜と、

前記TiN膜上に形成されたTiAlN膜と、

前記TiAlN膜上に形成されたシリコン膜と、

を有する半導体装置が提供される。

【0121】

(付記38)

本発明のさらに好ましい他の態様によれば、

基板上に高誘電率絶縁膜を形成する工程と、

前記高誘電率絶縁膜上にTiN膜を形成する工程と、

前記TiN膜上にTiAlN膜を形成する工程と、

前記TiAlN膜上にシリコン膜を形成する工程と、

を有する半導体装置の製造方法が提供される。

【0122】

(付記39)

本発明のさらに好ましい他の態様によれば、

半導体基板上にゲート絶縁膜を形成する第1の処理部と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する第2の処理部と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する第3の処理部と、

前記第2の金属含有膜上にシリコン膜を形成する第4の処理部と、

を有する基板処理システムが提供される。

【0123】

(付記40)

付記39の基板処理システムであって、好ましくは、前記第2の処理部と前記第3の処理部は同一の処理部である。

【0124】

(付記41)

本発明のさらに好ましい他の態様によれば、

基板処理システムの第1の処理部で半導体基板上にゲート絶縁膜を形成する手順と、

前記基板処理システムの第2の処理部で前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する手順と、

前記基板処理システムの第3の処理部で前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する手順と、

前記基板処理システムの第4の処理部で前記第2の金属含有膜上にシリコン膜を形成する手順と、

をコンピュータに実行させるためのプログラムが提供される。

【0125】

(付記42)

本発明のさらに好ましい他の態様によれば、

基板処理システムの第1の処理部で半導体基板上にゲート絶縁膜を形成する手順と、

前記基板処理システムの第2の処理部で前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する手順と、

前記基板処理システムの第3の処理部で前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する手順と、

前記基板処理システムの第4の処理部で前記第2の金属含有膜上にシリコン膜を形成する手順と、

をコンピュータに実行させるためのプログラムを記録したコンピュータ読み取り可能な記録媒体が提供される。

【0126】

以上、本発明の種々の典型的な実施の形態を説明してきたが、本発明はそれらの実施の形態に限定されない。従って、本発明の範囲は、次の特許請求の範囲によってのみ限定されるものである。

【符号の説明】

【0127】

10 シリコン基板

11 一主面

21 ソース領域

22 ドレイン領域

30 ゲート絶縁膜

31 SiO2膜

32 HfO2膜

40 ゲート電極

41 TiN膜

43 TiAlN膜

45 多結晶シリコン膜

100、102 MOSFET

200、202、204 評価サンプル

【特許請求の範囲】

【請求項1】

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の第1の金属含有膜と、

前記第1の金属含有膜上に形成され、アルミニウムを添加してなる導電性の第2の金属含有膜と、

前記第2の金属含有膜上に形成されたシリコン膜と、

を有する半導体装置。

【請求項2】

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する工程と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する工程と、

前記第2の金属含有膜上にシリコン膜を形成する工程と、

を有する半導体装置の製造方法。

【請求項3】

半導体基板上にゲート絶縁膜を形成する第1の処理部と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する第2の処理部と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する第3の処理部と、

前記第2の金属含有膜上にシリコン膜を形成する第4の処理部と、

を有する基板処理システム。

【請求項4】

基板処理システムの第1の処理部で半導体基板上にゲート絶縁膜を形成する手順と、

前記基板処理システムの第2の処理部で前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する手順と、

前記基板処理システムの第3の処理部で前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する手順と、

前記基板処理システムの第4の処理部で前記第2の金属含有膜上にシリコン膜を形成する手順と、

をコンピュータに実行させるためのプログラム。

【請求項1】

半導体基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成された導電性の第1の金属含有膜と、

前記第1の金属含有膜上に形成され、アルミニウムを添加してなる導電性の第2の金属含有膜と、

前記第2の金属含有膜上に形成されたシリコン膜と、

を有する半導体装置。

【請求項2】

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する工程と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する工程と、

前記第2の金属含有膜上にシリコン膜を形成する工程と、

を有する半導体装置の製造方法。

【請求項3】

半導体基板上にゲート絶縁膜を形成する第1の処理部と、

前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する第2の処理部と、

前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する第3の処理部と、

前記第2の金属含有膜上にシリコン膜を形成する第4の処理部と、

を有する基板処理システム。

【請求項4】

基板処理システムの第1の処理部で半導体基板上にゲート絶縁膜を形成する手順と、

前記基板処理システムの第2の処理部で前記ゲート絶縁膜上に導電性の第1の金属含有膜を形成する手順と、

前記基板処理システムの第3の処理部で前記第1の金属含有膜上に、アルミニウムを添加してなる導電性の第2の金属含有膜を形成する手順と、

前記基板処理システムの第4の処理部で前記第2の金属含有膜上にシリコン膜を形成する手順と、

をコンピュータに実行させるためのプログラム。

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図1】

【公開番号】特開2012−231123(P2012−231123A)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願番号】特願2012−43872(P2012−43872)

【出願日】平成24年2月29日(2012.2.29)

【出願人】(000001122)株式会社日立国際電気 (5,007)

【Fターム(参考)】

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願日】平成24年2月29日(2012.2.29)

【出願人】(000001122)株式会社日立国際電気 (5,007)

【Fターム(参考)】

[ Back to top ]