半導体装置、半導体装置の製造方法、電子部品、回路基板及び電子機器

【課題】小型化,薄型化及び高機能化を実現することが可能な半導体装置、半導体装置の製造方法、電子部品、回路基板及び電子機器を提供すること。

【解決手段】半導体基板10と、半導体基板10の第1の面10aに設けられた外部接続端子37と、半導体基板10の第1の面10aに設けられるとともに、外部接続端子37と電気的に接続された第1電極22と、半導体基板10の第1の面10aと対向する第2の面10bに設けられる電子素子と電気的に接続される第2電極23と、半導体基板10の第2の面10bに設けられるとともに、第2電極23に至る溝11と、該溝11の内部に設けられるとともに、第2電極23の裏面23aと電気的に接続された導電部12とを備えることを特徴とする。

【解決手段】半導体基板10と、半導体基板10の第1の面10aに設けられた外部接続端子37と、半導体基板10の第1の面10aに設けられるとともに、外部接続端子37と電気的に接続された第1電極22と、半導体基板10の第1の面10aと対向する第2の面10bに設けられる電子素子と電気的に接続される第2電極23と、半導体基板10の第2の面10bに設けられるとともに、第2電極23に至る溝11と、該溝11の内部に設けられるとともに、第2電極23の裏面23aと電気的に接続された導電部12とを備えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、半導体装置の製造方法、電子部品、回路基板及び電子機器に関する。

【背景技術】

【0002】

近年、携帯電話やテレビ受像機等の電子機器において、例えば、共振子や帯域フィルタ等として弾性表面波素子(以下、適宜「SAW(Surface Acoustic Wave)素子」と称する)を備えた電子部品が使用されている。下記特許文献1、2にはSAW素子を備えた電子部品に関する技術の一例が開示されている。特許文献1には、SAW素子とそのSAW素子を駆動制御する集積回路とを同一の空間に配置した電子部品のパッケージに関する技術が開示されている。また、特許文献2には、SAW素子を第1基板に実装し、集積回路を第2基板に実装した電子部品のパッケージに関する技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−290184号公報

【特許文献2】特開2002−290200号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、SAW素子を備えた電子部品が実装される電子機器の小型化の要求に伴って、SAW素子等の電子素子が実装される半導体装置や電子素子が実装された電子部品自体の小型化も要求されている。しかしながら、上述の特許文献1の構成では、SAW素子と集積回路とを並列に配置する構成であるため、小型化が困難である。同様に、特許文献2の構成では、SAW素子を実装した第1基板と集積回路を実装した第2基板とを重ねるように配置する構成であるため、薄型化(小型化)が困難である。

【0005】

また、SAW素子を備えた電子部品のみならず、特に水晶振動子、圧電振動子、圧電音叉等の気密封止が必要な電子素子を備えた電子部品の小型化も要求される。

【0006】

本発明は、上記の課題を解決するためになされたものであって、小型化,薄型化及び高機能化を実現することが可能な半導体装置、半導体装置の製造方法、電子部品、回路基板及び電子機器を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明は、以下の手段を提供する。

本発明の半導体装置は、半導体基板と、前記半導体基板の第1の面に設けられた外部接続端子と、前記半導体基板の第1の面に設けられるとともに、前記外部接続端子と電気的に接続された第1電極と、前記半導体基板の第1の面と対向する第2の面に設けられる電子素子と電気的に接続される第2電極と、前記半導体基板の第2の面に設けられるとともに、前記第2電極に至る溝と、該溝の内部に設けられるとともに、前記第2電極の裏面と電気的に接続された導電部とを備えることを特徴とする。

【0008】

本発明に係る半導体装置では、第2電極に至る溝の内部に導電部を形成することにより、第2電極が導電部を介して電子素子と電気的に接続することが可能となり、また、第1電極が外部接続端子と電気的に接続されているため、外部機器(例えば、回路基板)等と接続可能な半導体装置全体の小型化,薄型化及び高機能化を実現することが可能となる。

【0009】

また、本発明の半導体装置は、前記半導体基板の第1の面に設けられるとともに、前記第1電極と前記外部接続端子とを電気的に接続させる配線と、前記半導体基板と前記外部接続端子との間に設けられた応力緩和層とを備えることが好ましい。

【0010】

本発明に係る半導体装置では、配線を介して第1電極と外部接続端子とを電気的に接続させることにより、半導体装置に再配置配線が形成されるので、外部接続端子の形状,配置の自由度が広がる。また、応力緩和層を設けることにより、外部機器等と半導体装置との接続信頼性が高いものとなる。

【0011】

また、本発明の半導体装置は、前記第2電極の表面には、前記配線と同一の材料の金属膜が設けられていることが好ましい。

本発明に係る半導体装置では、一般的に配線の材料としては、耐腐食性の高い材料が用いられている。したがって、第2電極の表面にも配線と同一の材料の金属膜を設けることにより、第2電極の表面の腐食を防止することができるので、電気的不良の発生を防止することが可能となる。

【0012】

また、本発明の半導体装置は、前記半導体基板の第2の面に、前記導電部と電気的に接続された他面電極を備えることが好ましい。

本発明に係る半導体装置では、導電部と電気的に接続された他面電極を備えることにより、例えば、電子素子の電極形状に応じた他面電極を形成することで、電子素子との接続形態(実装形態)の設計の自由度を向上させることができる。

【0013】

また、本発明の半導体装置の製造方法は、半導体基板の第1の面に第1電極を形成する工程と、前記半導体基板の第1の面に第2電極を形成する工程と、前記半導体基板上に前記第1電極と前記外部接続端子とを電気的に接続する配線を形成する工程と、前記半導体基板と前記外部接続端子との間に応力緩和層を形成する工程と、前記半導体基板の第1の面に対向する第2の面から前記第2電極に向かって前記半導体基板に溝を形成する工程と、前記溝の側壁に絶縁膜を形成する工程と、前記溝に前記電子素子と前記第2電極とを電気的に接続する導電部を形成する工程とを有することを特徴とする。

【0014】

本発明に係る半導体装置の製造方法では、第2電極が形成されていない半導体基板の第2の面から溝を形成するため、第2電極と電気的に接続させる導電部を形成し易い。また、溝の側壁に絶縁膜を形成した後、溝に第2電極と電気的に接続された導電部を形成するので、導電部と半導体基板とは良好に絶縁が取れた状態になるため、第2電極から導電部を介して電子素子に正確に電圧を供給することができ、電子素子を良好に駆動させることが可能となる。

【0015】

また、本発明の半導体装置の製造方法は、前記溝を形成する工程は、フォトリソグラフィ法及びエッチング法を用いることが好ましい。

本発明に係る半導体装置の製造方法では、シリコン基板に溝をフォトリソグラフィ及びエッチングにより形成するため、高精度に形成することができる。

【0016】

また、本発明の半導体装置の製造方法は、前記半導体装置の第2の面に設けられる他面電極と、前記導電部とを一体に形成することが好ましい。

本発明に係る半導体装置の製造方法では、他面電極と導電部とを一体に形成することにより、効率良く半導体装置を製造することができ、半導体装置の低コスト化を実現することが可能となる。

【0017】

また、本発明の半導体装置の製造方法は、前記半導体装置を同一の基板に複数同時に形成した後、前記基板を前記半導体装置毎に切断することが好ましい。

本発明に係る半導体装置の製造方法では、基板上に複数の半導体装置を同時に形成し、その後、その基板を半導体装置毎に切断することで、効率良く半導体装置を製造することができ、半導体装置の低コスト化を実現できる。

【0018】

本発明の電子部品は、半導体基板と、前記半導体基板の第1の面に設けられた外部接続端子と、前記半導体基板の第1の面に設けられるとともに、前記外部接続端子と電気的に接続された第1電極と、前記半導体基板の第1の面と対向する第2の面に設けられる電子素子と電気的に接続される第2電極と、前記半導体基板の第2の面に設けられるとともに、前記第2電極に至る溝と、該溝の内部に設けられるとともに、前記第2電極の裏面と電気的に接続された導電部と、前記半導体基板の第2の面に設けられ、前記導電部と電気的に接続された電子素子と、前記電子素子を封止する封止部材とを備えることを特徴とする。

【0019】

本発明に係る電子部品では、半導体基板の第2の面に電子素子を設け、この電子素子と導電部とを電気的に接続させることにより、第2電極が導電部を介して電子素子と電気的に接続することが可能となる。また、第1電極が外部接続端子と電気的に接続しているため、外部機器等と接続可能な電子部品全体の小型化及び薄型化を実現することが可能となる。さらに、電子素子は封止部材によって封止されているので、電子部品全体の小型化及び薄型化を実現しつつ、電子素子を良好に駆動させることが可能となる。

【0020】

また、本発明の電子部品は、前記封止部材が前記半導体基板の第2の面から離間されて配置されるとともに、前記電子素子が前記封止部材側に設けられていることが好ましい。

【0021】

本発明に係る電子部品では、電子素子が封止部材側に設けられているため、電子素子と導電部とを電気的に接続させることで、電子素子の封止を行うことができる。したがって、簡易な構成により、封止された電子部品を得ることが可能となる。

【0022】

また、本発明の電子部品は、前記半導体基板の第2の面と前記半導体基板の第2の面から離間されて配置された前記封止部材との間に支持基板が設けられ、前記電子素子が、前記支持基板上に設けられていることが好ましい。

【0023】

本発明に係る電子部品では、支持基板に電子素子が設けられているため、電子素子を良好に支持した状態で電子素子と導電部とを電気的に接続させることができる。したがって、電子素子を良好に駆動させることができる。

【0024】

また、本発明の電子部品は、前記電子素子が、前記半導体基板の第2の面から離間されて配置された支持基板に保持され、前記封止部材が、前記支持基板に保持された電子素子を封止するとともに、前記電子素子と電気的に接続された電子素子電極を備えることが好ましい。

【0025】

本発明に係る電子部品では、支持基板に保持された電子素子が封止部材により封止されているため、封止部材に設けられた電子素子電極と導電部とを電気的に接続させることにより、小型化,薄型化を実現しつつ、電子素子を良好に駆動させることができる。

【0026】

前記半導体基板の第2の面に、前記導電部と前記電子素子とを電気的に接続させた他面電極を備えることが好ましい。

本発明に係る電子部品では、導電部と電子素子とを電気的に接続させた他面電極を備えることにより、例えば、電子素子の電極形状に応じた他面電極を形成することで、電子素子と第2電極との導通状態を良好にすることが可能となる。

【0027】

本発明の回路基板は、上記の電子部品が実装されていることを特徴とする。

本発明に係る回路基板では、小型化・薄型化が実現された電子部品が実装された回路基板(プリント配線板等)を提供することができる。したがって、この回路基板を電子機器等に実装した際にも、電子機器全体の大型化を防止することができる。

【0028】

本発明の電子機器は、上記の電子部品が実装されていることを特徴とする。

本発明に係る電子機器では、小型化・薄型化が実現された電子部品が実装された電子機器を提供することができる。したがって、小型化された電子機器を得ることができる。

【図面の簡単な説明】

【0029】

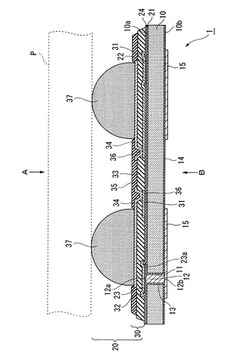

【図1】本発明の一実施形態に係る半導体装置を示す断面図である。

【図2】図1の半導体装置のA矢視における平面図である。

【図3】図1の半導体装置のB矢視における平面図である。

【図4】本発明の一実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】本発明の一実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】本発明の一実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】本発明の第1実施形態に係る電子部品を示す断面図である。

【図8】図7の電子部品の電極を示す平面図である。

【図9】本発明の第2実施形態に係る電子部品を示す断面図である。

【図10】本発明の第3実施形態に係る電子部品を示す断面図である。

【図11】本発明の第4実施形態に係る電子部品を示す断面図である。

【図12】本発明の電子部品が搭載された電子機器を示す図である。

【発明を実施するための形態】

【0030】

[半導体装置の一実施形態]

次に、本発明の半導体装置の一実施形態について、図1から図6を参照して説明する。

本実施形態に係る半導体装置1は、図1に示すように、シリコン基板(半導体基板)10と、シリコン基板10の第1の面10aに形成され、外部機器であるプリント配線板(回路基板)Pに電気的に接続される接続部20とを備えている。

【0031】

シリコン基板10は、図1に示すように、第1の面10aから対向する第2の面10bに第2電極23に至る溝11が形成されており、この溝11の内部には導電性材料が充填された導電部12が設けられている。また、溝11の側壁には絶縁膜13が設けられており、導電部12とシリコン基板10とは電気的に絶縁されている。

また、シリコン基板10の第2の面10bの表面には、溝11が形成された領域以外の領域に裏面絶縁層14が形成されている。この裏面絶縁層14上には、電子素子として、例えば、弾性表面波素子「SAW(Surface Acoustic Wave)素子」の電極に応じた裏面電極(他面電極)15が、図3に示すように形成されている。

【0032】

接続部20は、シリコン基板10の第1の面10a上に設けられた下地層21と、下地層21の複数の所定領域のそれぞれに設けられた第1電極22及び第2電極23と、これら電極22,23が設けられた領域以外の領域に設けられた第1絶縁層24と、この第1絶縁層24上に形成された配線部30とを備えている。この下地層21は、例えば酸化珪素(SiO2)、窒化珪素(Si3N4)等の絶縁性材料によって形成されている。また、第1,第2電極22,23の材料としては、チタン(Ti)、窒化チタン(TiN)、アルミニウム(Al)、銅(Cu)、あるいは、これらを含む合金等が挙げられる。

なお、シリコン基板10には、図2に示すように、複数の電極が形成されていても構わないが、本実施形態では、第1電極22及び第2電極23のみについて説明する。

また、第2電極23は、第1絶縁層24に覆われていても構わない。

なお、不図示ではあるが、下地層21の下には、例えばトランジスタ,メモリ素子を有する集積回路が形成されている。そして、この集積回路が、第1電極22及び第2電極23と電気的に接続されている。

【0033】

配線部30は、図1及び図2に示すように、第1絶縁層24上に設けられた第1電極22と電気的に接続された第1配線(配線)31と、第2電極23の表面に設けられた金属膜32と、この第1配線(配線)31及び金属膜32上に設けられた第2絶縁層(応力緩和層)33と、第2絶縁層33上に形成されるとともに、第1配線31と電気的に接続された第2配線(配線)34と、第2配線34上に形成された第3絶縁層35とを備えている。また、第1配線31の一部が第2絶縁層33より露出してランド部36を形成しており、このランド部36と第2配線34とが電気的に接続されている。さらに、第2配線34上にはバンプ(外部接続端子)37が設けられ、半導体装置1はこのバンプ37を介してプリント配線板Pに電気的に接続されている。また、第3絶縁層35は、第2絶縁層33上及び第2配線34上のバンプ37が形成される領域以外の領域を覆うように設けられている。

【0034】

また、第1電極22は、第1配線31及び第2配線34を介してバンプ37と電気的に接続されている。また、第2電極23は、シリコン基板10の第1の面10a上に設けられた下地層21上に形成されとともに、溝11により一部が露出されている。これにより、この第2電極23は、第2電極23の裏面23aで溝11の内部の導電部12の一端部12aと電気的に接続されている。また、導電部12の他端部12bは、シリコン基板10の第2の面10bに設けられた裏面電極15と電気的に接続されている。すなわち、第2電極23はシリコン基板10の第2の面10bに設けられる電子素子と電気的に接続されるようになっている。

【0035】

また、第1,第2配線31,34の材料としては、金(Au)、銅(Cu)、銀(Ag)、チタン(Ti)、タングステン(W)、チタンタングステン(TiW)、窒化チタン(TiN)、ニッケル(Ni)、ニッケルバナジウム(NiV)、クロム(Cr)、アルミニウム(Al)、パラジウム(Pd)等が挙げられる。この第1,第2配線31,34としては、上述した材料の単層構造であっても良いし、複数組み合わせて積層構造にしても良い。

また、第1,第2,第3絶縁層24,33,35は、樹脂(合成樹脂)によって形成されている。これら第1,第2,第3絶縁層24,33,35を形成するための形成材料としては、ポリイミド樹脂、シリコーン変性ポリイミド樹脂、エポキシ樹脂、シリコーン変性エポキシ樹脂、アクリル樹脂、フェノール樹脂、BCB(benzocyclobutene)及びPBO(polybenzoxazole)等、絶縁性がある材料であれば良い。

なお、第1絶縁層24は、酸化珪素(SiO2)、窒化珪素(Si3N4)等の絶縁性材料によって形成されていても良い。

【0036】

また、金属膜32の材料は、第1,第2配線31,34と同一の材料であることが好ましい。金属膜32の材料としては、Au、TiW、Cu、Cr、Ni、Ti、W、NiV、Al等の金属を使用することができる。また、金属膜32は、これらの金属を積層して形成することも可能である。なお、金属膜(積層構造の場合、少なくとも1層)32は、電極よりも耐腐食性の高い材料、例えばAu、TiW、Crを用いて形成することが好ましい。これにより、電極の腐食を阻止して、電気的不良の発生を防止することが可能になるからである。

【0037】

[半導体装置の製造方法]

次に、図4及び図5を参照しながら半導体装置1の製造方法について説明する。ここで、本実施形態においては、半導体装置1は同一のシリコン基板(基板)100上に複数(図6参照)同時に一括して形成されるが、簡単のため図4及び図5においては1つの半導体装置1を形成する場合が示されている。

【0038】

まず、図4(a)に示すように、シリコン基板10の第1の面10a上に下地層21を形成した後、下地層21上に第1,第2電極22,23を形成する。そして、第1,第2電極22,23上に第1絶縁層24を形成し、周知のフォトリソグラフィ法及びエッチング法により、第1,第2電極22,23を覆う絶縁材料を除去する。なお、第2電極23を覆う絶縁材料は必ずしも除去しなくても良い。次いで、第1電極22を含む第1絶縁層24上には第1配線31を形成し、第2電極23の表面には金属膜32を形成する。第1配線31の形成方法としては、例えば、TiW、Cuの順にスパッタ法により形成した後、Cuをめっき法で形成することにより行われる。

【0039】

次に、第1配線31及び金属膜32を覆うように第2絶縁層33を形成し、周知のフォトリソグラフィ法により、第2絶縁層33のランド部36に対応する領域が除去され、第1配線31の一部が露出されてランド部36となる。そして、ランド部36に接続するように、第2絶縁層33上に第2配線34が形成され、その後、第2絶縁層33上及び第2配線34上のバンプ37が形成される領域以外の領域を覆うように第3絶縁層35を設けることにより、図4(a)に示すような形態となる。

【0040】

次に、図4(b)に示すように、シリコン基板10の第2の面10b上にフォトレジスト40をマスクとして用い、ドライエッチングにより、第2電極23に対応したシリコン基板10及び下地層21を除去する。これにより、図4(c)に示すように、シリコン基板10の第2の面10bから、第1の面10aに設けられた第2電極23の裏面23aが露出するまでエッチングを行い、溝11を形成する。

なお、フォトレジスト40をマスクとしたが、これに限ることはなく、例えば、ハードマスクとしてSiO2膜を用いても良く、フォトレジストマスク及びハードマスクを併用しても良い。また、エッチング方法としてはドライエッチングに限らず、ウエットエッチング、レーザ加工、あるいはこれらを併用しても良い。

【0041】

次に、図5(a)に示すように、シリコン基板10の第2の面10b及び溝11の内壁に裏面絶縁層14及び絶縁膜13を形成する。裏面絶縁層14及び絶縁膜13は、電流リークの発生、酸素及び水分等による半導体基板10の浸食等を防止するために設けられ、PECVD(Plasma Enhanced Chemical Vapor Deposition)を用いて形成した正珪酸四エチル(Tetra Ethyl Ortho Silicate:Si(OC2H5)4:以下、TEOSという)、すなわちPE−TEOS、及び、オゾンCVDを用いて形成したTEOS、すなわちO3−TEOSまたはCVDを用いて形成した酸化珪素(SiO2)を用いることができる。なお、裏面絶縁層14及び絶縁膜13は、絶縁性があれば、他の物でも良く、樹脂でもよい。そして、第2電極23の裏面23a部分に設けられた絶縁膜13をドライエッチングあるいはレーザ加工により除去することで、図5(b)に示すように、溝11の側壁のみに絶縁層13が設けられた形態となる。

【0042】

次に、電気化学プレーティング(ECP)法を用いて、溝11の内部にめっき処理が施され、その溝11の内側に導電部12を形成するための導電性材料を配置し、導電部12の一端部12aと露出した第2電極23とが、第2電極23の裏面23aで電気的に接続される。導電部12を形成するための導電性材料としては、例えば銅(Cu)を用いることができ、導電部12には銅(Cu)が埋め込まれる。本実施形態における導電部12を形成する工程には、例えば、TiN、Cuをスパッタ法で形成(積層)する工程と、Cuをめっき法で形成する工程とが含まれる。なお、TiW、Cuをスパッタ法で形成(積層)する工程と、Cuをめっき法で形成する工程とが含まれたものであってもよい。なお、導電部12の形成方法としては、上述した方法に限らず、導電ペースト、溶融金属、金属ワイヤ等を埋め込んでもよい。

また、本実施形態では、溝11の内部を導電部12で埋め込んでいるが、完全に埋め込まなくても、溝11の内壁に導電部12を設けて、第2電極23の裏面23aで電気的に接続される形態でも良い。

【0043】

導電部12を形成した後、シリコン基板10の第2の面10bにこの導電部12と電気的に接続されるように裏面電極15を形成することにより、図5(c)に示すような形態となる。なお、裏面電極15は、導電部12と同時、すなわち、一体的に形成しても良い。次に、シリコン基板10の第1の面10a側に設けられた第2配線34上に、例えば鉛フリーはんだからなるバンプ37を搭載する。なお、バンプ37を設ける際には、はんだボールを第2配線34上に搭載する形態でもよいし、はんだペーストを第2配線34上に印刷する形態でもよい。

【0044】

そして、図6に示すように、ダイシング装置110によって、シリコン基板100が半導体装置1毎にダイシング(切断)される。このように、シリコン基板100上に複数の半導体装置1を略同時に形成し、その後、そのシリコン基板100を半導体装置1毎に切断することで、図1に示す半導体装置1を得ることができる。このようにして、効率良く半導体装置1を製造することができ、半導体装置1の低コスト化を実現できる。

【0045】

本実施形態に係る半導体装置1によれば、第2電極23に至る溝11の内部に導電部12を形成することにより、第2電極23が、導電部12を介して電子素子と電気的に接続することが可能となり、また、第1電極22がバンプ37と電気的に接続されているため、外部機器等と接続可能な半導体装置1全体の小型化,薄型化及び高機能化を実現することが可能となる。

【0046】

[電子部品の第1実施形態]

次に、上述した半導体装置1に電子素子としてSAW素子(電子素子)60が実装された電子部品50の第1実施形態について、図7を参照して説明する。なお、以下に説明する各実施形態において、上述した一実施形態に係る半導体装置1と構成を共通とする箇所には同一符号を付けて、説明を省略することにする。

本実施形態の電子部品50に用いられる半導体装置51は、裏面電極15を設けていない点以外は上述した半導体装置1と同一の構成を有している。

【0047】

電子部品50は、図8に示すように、圧電薄膜(図示略)とこの圧電薄膜に接する櫛歯電極61とを備えている。そして、電子部品50は、図7に示すように、シリコン基板10の第2の面10b側に、導電部12の他端部12bと電気的に接続されるように、直接電子素子60が形成されている。また、不図示ではあるが、シリコン基板10の第1の面10a側には、例えばトランジスタ,メモリ素子を有する集積回路が形成されている。そして、導電部12の一端部12aが、この集積回路と第2電極23を介して電気的に接続されている。したがって、シリコン基板10の第2の面10bに設けられた電子素子60と、シリコン基板10の第1の面10a側に設けられた集積回路とが導電部12を介して電気的に接続されている。

【0048】

また、電子部品50は、シリコン基板10の第2の面10bとの間でSAW素子60を封止する封止部材52を備えている。本実施形態において封止部材52はガラス基板によって形成されているが、シリコン基板であってもよい。封止部材52は、シリコン基板10の第2の面10bから離間された位置に設けられている。シリコン基板10の第2の面10bの周縁部と封止部材52の内面52aの周縁部とは、接着剤層53により接着されている。接着剤層53は、例えばポリイミド樹脂等の合成樹脂で形成されている。そして、シリコン基板10の第2の面10bと、封止部材52の内面52aと、接着剤層53とで囲まれた内部空間55は略密閉(気密封止)されており、その内部空間55にSAW素子60が配置された構成となっている。

【0049】

[電子部品の製造方法]

次に、電子部品50の製造方法について説明する。

まず、上述した半導体装置1の製造方法と同様の工程により、導電部12まで形成した後、シリコン基板10の第2の面10bにSAW素子60を形成する。このSAW素子60を形成する工程には、圧電薄膜を形成する工程と、圧電薄膜に接するように、図8に示すような櫛歯電極61を形成する工程と、保護膜(図示略)を形成する工程とが含まれる。さらには、SAW素子60を形成する工程には、プラズマ等をSAW素子60に照射して周波数調整を行う工程が含まれる。圧電薄膜の形成材料としては、酸化亜鉛(ZnO)、窒化アルミニウム(AlN)、ニオブ酸リチウム(LiNbO3)、タンタル酸リチウム(LiTaO3)、ニオブ酸カリウム(KNbO3)等が挙げられる。櫛歯電極61の形成材料としては、アルミニウムを含む金属が挙げられる。保護膜の形成材料としては、酸化珪素(SiO2)、窒化珪素(Si3N4)、窒化チタン(TiN)等が挙げられる。そして、形成されるSAW素子60は、シリコン基板10の第2の面10bで、導電部12の他端部12bと電気的に接続される。

【0050】

次に、シリコン基板10の第2の面10b及び封止部材52の内面52aのうち少なくとも一方に、接着剤層53を形成するための接着剤が設けられる。接着剤層53としては、例えば感光性のポリイミド接着剤等を使用することができる。そして、その接着剤層53を介して、シリコン基板10の第2の面10bと封止部材52の内面52aとが対向するように、それらシリコン基板10と封止部材52とが接合される。これにより、図7に示すような形態が得られる。

【0051】

ここで、封止は、内部空間55を真空にする真空封止、内部空間55をN2、Ar、He等の所定ガスで置換するガス置換封止等してもよい。なお、シリコン基板10と封止部材52とを接合するとき、シリコン基板10の第2の面10bの周縁部に沿って金属突起を設け、封止部材52の内面52aに、前記金属突起と接着するための金属層を設け、それら金属突起及び金属層を介してシリコン基板10と封止部材52とを接合するようにしてもよい。封止部材52にガラスを用いた場合には、封止後に、レーザー等によりSAW素子60の周波数調整が可能となる。その後、シリコン基板10の第1の面10a側に設けられた第2配線34上に、例えば鉛フリーはんだからなるバンプ37が搭載される。なお、バンプ37を設ける際には、はんだボールを第2配線34上に搭載する形態でもよいし、はんだペーストを第2配線34上に印刷する形態でもよい。

【0052】

その後、この電子部品50も半導体装置1と同様に、同一のシリコン基板(基板)上に半導体装置50,SAW素子60及び封止部材52等を同時に一括して形成している。そこで、この電子部品50を半導体装置1と同様にしてダイシング装置110によって、電子部品50毎にダイシング(切断)される。これにより、電子部品50を低コストで製造できる。製造された電子部品50は、バンプ37を介してプリント配線板P等に搭載される。

【0053】

本実施形態に係る電子部品50によれば、シリコン基板10の第2の面10b側にSAW素子60を設け、導電部12の他端部12bとこのSAW素子60とを接続したので、シリコン基板10の第1の面10a側にSAW素子60を駆動制御する集積回路を設けておくことで、導電部12を介してSAW素子60と集積回路とを電気的に接続することができる。したがって、電子部品50全体の小型化・薄型化を実現しつつ、SAW素子60を良好に駆動することができる。そして、SAW素子60は封止部材52によって第2の面10bとの間で封止されるので、小型化・薄型化を実現しつつ、SAW素子60を良好に封止することができ、SAW素子60を良好に駆動することができる。

【0054】

[電子部品の第2実施形態]

次に、上述した半導体装置1に電子素子としてSAW素子71が実装された電子部品70の第2実施形態について、図9を参照して説明する。なお、以下に説明する各実施形態において、上述した第1実施形態に係る電子部品50と構成を共通とする箇所には同一符号を付けて、説明を省略することにする。

本実施形態に係る電子部品70は、SAW素子71が、シリコン基板10の第2の面10bに形成されておらず、シリコン基板10の第2の面10bから離間された位置に配された封止部材52に設けられている点で第1実施形態と異なる。

【0055】

SAW素子71は、シリコン基板10の第2の面10bと対向する封止部材52の内面52aに設けられている。また、SAW素子71には、シリコン基板10の第2の面10bと対向する面に端子72が設けられている。

半導体装置73には、シリコン基板10の第2の面10bの溝11上に裏面電極(他面電極)54が形成されている。そして、この裏面電極54と導電部12の他端部12bとが電気的に接続されている。裏面電極54は、SAW素子71の端子72に対応した位置に形成されている。すなわち、第2電極23は、シリコン基板10の第2の面10bに設けられるSAW素子71と導電部12及び裏面電極54を介して電気的に接続されるようになっている。

また、封止部材52は、シリコン基板、水晶基板、シリコン及びダイヤを有する基板によって構成されている。

【0056】

電子部品70の製造方法としては、封止部材52の内面52a上に予めSAW素子71を形成しておき、その後、シリコン基板10の第2の面10bに形成され裏面電極54と、封止部材52の内面52a上に形成されたSAW素子71の端子72とが電気的に接続するように、シリコン基板10と封止部材52とを接着剤層53を介して接合することにより、図9に示す電子部品70が得られる。なお、裏面電極54と端子51とは、接着剤層30の収縮による圧接でもよい。

【0057】

本実施形態に係る電子部品70によれば、シリコン基板10とは別の部材、すなわち、封止部材52にSAW素子71を設けることにより、シリコン基板10に掛かる熱応力、膜応力の影響を受けにくいため、良好な特性を得ることができる。

【0058】

[電子部品の第3実施形態]

次に、上述した半導体装置1に電子素子としてSAW素子81が実装された電子部品80の第3実施形態について、図10を参照して説明する。

本実施形態に係る電子部品80は、SAW素子81は、シリコン基板10の第2の面10bに形成されておらず、SAW素子81が支持基板82上に設けられている点で、第2実施形態と異なる。

【0059】

支持基板82は、シリコン基板10の第2の面10bとシリコン基板10の第2の面10bから離間された位置に配された封止部材52との間に設けられている。また、SAW素子81は、シリコン基板10の第2の面10bと対向する支持基板82の面82a側に設けられている。さらに、SAW素子81は、電子部品70の第2実施形態と同様に、シリコン基板10の第2の面10bと対向する面に端子83が設けられている。そして、この端子83と裏面電極54とが電気的に接続されている。

【0060】

本実施形態に係る電子部品80によれば、シリコン基板10とは別の部材、すなわち、支持基板82にSAW素子81を設けることにより、シリコン基板10に掛かる熱応力、膜応力の影響を受けにくいため、良好な特性を得ることができる。また、支持基板82により、SAW素子81を良好に支持した状態で、SAW素子81と導電部12とを電気的に接続させることが可能となる。

【0061】

[電子部品の第4実施形態]

次に、上述した半導体装置1に電子素子としてAT振動子(水晶振動子)91が実装された電子部品90の第4実施形態について、図11を参照して説明する。

本実施形態に係る電子部品90は、AT振動子91が、支持基板92に保持された状態で封止部材93により封止されている点で第2実施形態と異なる。

【0062】

支持基板92は、シリコン基板10の第2の面10bから離間されて配置されており、AT振動子91が、シリコン基板10の第2の面10bと対向する支持基板92の内面92aに設けられている。そして、AT振動子91は、支持基板92とシリコン基板10の第2の面10bとの間に設けられたガラス基板からなる封止部材93により封止されている。そして、支持基板92の内面92aと、封止部材93の内面93aとで囲まれた内部空間95は略密閉(気密封止)されている。

【0063】

また、封止部材93には、シリコン基板10の第2の面10bと対向する面に電子素子電極94が設けられている。そして、この電子素子電極94と裏面電極54とが電気的に接続されている。すなわち、第2電極23は、シリコン基板10の第2の面10bに設けられる導電部12及び裏面電極54を介して、AT振動子91と電気的に接続されるようになっている。

また、シリコン基板10の第2の面10bの周縁部と支持基板92の周縁部及び第2の面10bと封止部材93との間は、封止樹脂96により封止されている。

【0064】

本実施形態に係る電子部品90によれば、封止部材93により支持基板92に保持されたAT振動子が封止されているため、封止部材93に設けられた電子素子電極94と導電部12とを電気的に接続させることにより、小型化,薄型化を実現しつつ、電子素子を良好に駆動させることができる。

【0065】

<電子機器>

図12は、上述した電子部品50,70,80,90を搭載した電子機器の一例を示す図であって、携帯電話300を示す図である。小型化・薄型化及び高機能化が実現された本発明の電子部品を搭載したので、小型の携帯電話300が実現される。

【0066】

なお、本発明の技術範囲は上記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更を加えることが可能である。

例えば、上記半導体装置1の一実施形態において裏面電極15を設けたが、電子部品の電極が直接導電部12の他端部12bに接続されていても良い。

また、電子素子60,71,81,91と接続する裏面電極15,54の表面あるいは導電部12の他端部12bの表面には、金属接続しやすいように、金などの表面処理、あるいはロウ材(SnAgめっき等)を設けることが好ましい。また、上記各本実施形態においても、最終工程でダイシングする形態の他に、適切な工程(途中工程)で個片化するようにしてもよい。

【0067】

さらに、封止部材52,93をガラス基板によって構成した場合、そのガラス基板からなる封止部材52,93をダイシング(切断)する際には、図6を参照して説明したダイシング装置110によってダイシングすることもできるが、レーザを照射することによってダイシングを行うことや、ドライエッチング又はウエットエッチングの手法を用いてダイシングを行うこともできる。

また、本発明に係る電子素子としては、第1,第2,第3実施形態においてSAW素子を用いて説明したが、これに限らす、封止を必要とする素子、例えば、水晶振動子、圧電振動子、圧電音叉等であってもよい。また、第4実施形態においてはAT振動子(水晶振動子)を用いて説明したが、これに限らす、封止を必要とする素子、例えば、SAW素子、圧電振動子、圧電音叉等であってもよい。

【0068】

また、必要に応じては、シリコン基板10に接続部30を形成した後、シリコン基板10の薄型化を行うことも可能である。シリコン基板10を薄くする方法としては、まず、紫外光(UV光)の照射により剥離可能な接着剤で、シリコン基板10の第1の面10a側に不図示のガラス板を貼り付ける。このガラス板はWSS(Wafer Support System)と呼ばれるものの一部であって、シリコン基板10をガラス板に支持した後、このガラス板を貼り付けた状態で、シリコン基板10の第2の面10bに対して研磨処理、ドライエッチング処理、あるいはウエットエッチング処理等の所定の処理を施す。これにより、シリコン基板10が薄くされる。

【符号の説明】

【0069】

P…プリント配線板(回路基板)、1,51,73…半導体装置、10…シリコン基板(半導体基板)、10a…シリコン基板の第1の面、10b…シリコン基板の第2の面、11…溝、12…導電部、15,54…裏面電極(他面電極)、22…第1電極、23…第2電極、23a…第2電極の裏面、31…第1配線層(配線層)、33…第2絶縁層(応力緩和層)、34…第2配線層(配線層)、37…バンプ(外部接続端子)、50,70,80,90…電子部品、52,93…封止部材、60,71,81,91…SAW素子(電子素子)、92…支持基板、94…電子素子電極、100…シリコン基板(基板)、300…電子機器。

【技術分野】

【0001】

本発明は、半導体装置、半導体装置の製造方法、電子部品、回路基板及び電子機器に関する。

【背景技術】

【0002】

近年、携帯電話やテレビ受像機等の電子機器において、例えば、共振子や帯域フィルタ等として弾性表面波素子(以下、適宜「SAW(Surface Acoustic Wave)素子」と称する)を備えた電子部品が使用されている。下記特許文献1、2にはSAW素子を備えた電子部品に関する技術の一例が開示されている。特許文献1には、SAW素子とそのSAW素子を駆動制御する集積回路とを同一の空間に配置した電子部品のパッケージに関する技術が開示されている。また、特許文献2には、SAW素子を第1基板に実装し、集積回路を第2基板に実装した電子部品のパッケージに関する技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−290184号公報

【特許文献2】特開2002−290200号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、SAW素子を備えた電子部品が実装される電子機器の小型化の要求に伴って、SAW素子等の電子素子が実装される半導体装置や電子素子が実装された電子部品自体の小型化も要求されている。しかしながら、上述の特許文献1の構成では、SAW素子と集積回路とを並列に配置する構成であるため、小型化が困難である。同様に、特許文献2の構成では、SAW素子を実装した第1基板と集積回路を実装した第2基板とを重ねるように配置する構成であるため、薄型化(小型化)が困難である。

【0005】

また、SAW素子を備えた電子部品のみならず、特に水晶振動子、圧電振動子、圧電音叉等の気密封止が必要な電子素子を備えた電子部品の小型化も要求される。

【0006】

本発明は、上記の課題を解決するためになされたものであって、小型化,薄型化及び高機能化を実現することが可能な半導体装置、半導体装置の製造方法、電子部品、回路基板及び電子機器を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明は、以下の手段を提供する。

本発明の半導体装置は、半導体基板と、前記半導体基板の第1の面に設けられた外部接続端子と、前記半導体基板の第1の面に設けられるとともに、前記外部接続端子と電気的に接続された第1電極と、前記半導体基板の第1の面と対向する第2の面に設けられる電子素子と電気的に接続される第2電極と、前記半導体基板の第2の面に設けられるとともに、前記第2電極に至る溝と、該溝の内部に設けられるとともに、前記第2電極の裏面と電気的に接続された導電部とを備えることを特徴とする。

【0008】

本発明に係る半導体装置では、第2電極に至る溝の内部に導電部を形成することにより、第2電極が導電部を介して電子素子と電気的に接続することが可能となり、また、第1電極が外部接続端子と電気的に接続されているため、外部機器(例えば、回路基板)等と接続可能な半導体装置全体の小型化,薄型化及び高機能化を実現することが可能となる。

【0009】

また、本発明の半導体装置は、前記半導体基板の第1の面に設けられるとともに、前記第1電極と前記外部接続端子とを電気的に接続させる配線と、前記半導体基板と前記外部接続端子との間に設けられた応力緩和層とを備えることが好ましい。

【0010】

本発明に係る半導体装置では、配線を介して第1電極と外部接続端子とを電気的に接続させることにより、半導体装置に再配置配線が形成されるので、外部接続端子の形状,配置の自由度が広がる。また、応力緩和層を設けることにより、外部機器等と半導体装置との接続信頼性が高いものとなる。

【0011】

また、本発明の半導体装置は、前記第2電極の表面には、前記配線と同一の材料の金属膜が設けられていることが好ましい。

本発明に係る半導体装置では、一般的に配線の材料としては、耐腐食性の高い材料が用いられている。したがって、第2電極の表面にも配線と同一の材料の金属膜を設けることにより、第2電極の表面の腐食を防止することができるので、電気的不良の発生を防止することが可能となる。

【0012】

また、本発明の半導体装置は、前記半導体基板の第2の面に、前記導電部と電気的に接続された他面電極を備えることが好ましい。

本発明に係る半導体装置では、導電部と電気的に接続された他面電極を備えることにより、例えば、電子素子の電極形状に応じた他面電極を形成することで、電子素子との接続形態(実装形態)の設計の自由度を向上させることができる。

【0013】

また、本発明の半導体装置の製造方法は、半導体基板の第1の面に第1電極を形成する工程と、前記半導体基板の第1の面に第2電極を形成する工程と、前記半導体基板上に前記第1電極と前記外部接続端子とを電気的に接続する配線を形成する工程と、前記半導体基板と前記外部接続端子との間に応力緩和層を形成する工程と、前記半導体基板の第1の面に対向する第2の面から前記第2電極に向かって前記半導体基板に溝を形成する工程と、前記溝の側壁に絶縁膜を形成する工程と、前記溝に前記電子素子と前記第2電極とを電気的に接続する導電部を形成する工程とを有することを特徴とする。

【0014】

本発明に係る半導体装置の製造方法では、第2電極が形成されていない半導体基板の第2の面から溝を形成するため、第2電極と電気的に接続させる導電部を形成し易い。また、溝の側壁に絶縁膜を形成した後、溝に第2電極と電気的に接続された導電部を形成するので、導電部と半導体基板とは良好に絶縁が取れた状態になるため、第2電極から導電部を介して電子素子に正確に電圧を供給することができ、電子素子を良好に駆動させることが可能となる。

【0015】

また、本発明の半導体装置の製造方法は、前記溝を形成する工程は、フォトリソグラフィ法及びエッチング法を用いることが好ましい。

本発明に係る半導体装置の製造方法では、シリコン基板に溝をフォトリソグラフィ及びエッチングにより形成するため、高精度に形成することができる。

【0016】

また、本発明の半導体装置の製造方法は、前記半導体装置の第2の面に設けられる他面電極と、前記導電部とを一体に形成することが好ましい。

本発明に係る半導体装置の製造方法では、他面電極と導電部とを一体に形成することにより、効率良く半導体装置を製造することができ、半導体装置の低コスト化を実現することが可能となる。

【0017】

また、本発明の半導体装置の製造方法は、前記半導体装置を同一の基板に複数同時に形成した後、前記基板を前記半導体装置毎に切断することが好ましい。

本発明に係る半導体装置の製造方法では、基板上に複数の半導体装置を同時に形成し、その後、その基板を半導体装置毎に切断することで、効率良く半導体装置を製造することができ、半導体装置の低コスト化を実現できる。

【0018】

本発明の電子部品は、半導体基板と、前記半導体基板の第1の面に設けられた外部接続端子と、前記半導体基板の第1の面に設けられるとともに、前記外部接続端子と電気的に接続された第1電極と、前記半導体基板の第1の面と対向する第2の面に設けられる電子素子と電気的に接続される第2電極と、前記半導体基板の第2の面に設けられるとともに、前記第2電極に至る溝と、該溝の内部に設けられるとともに、前記第2電極の裏面と電気的に接続された導電部と、前記半導体基板の第2の面に設けられ、前記導電部と電気的に接続された電子素子と、前記電子素子を封止する封止部材とを備えることを特徴とする。

【0019】

本発明に係る電子部品では、半導体基板の第2の面に電子素子を設け、この電子素子と導電部とを電気的に接続させることにより、第2電極が導電部を介して電子素子と電気的に接続することが可能となる。また、第1電極が外部接続端子と電気的に接続しているため、外部機器等と接続可能な電子部品全体の小型化及び薄型化を実現することが可能となる。さらに、電子素子は封止部材によって封止されているので、電子部品全体の小型化及び薄型化を実現しつつ、電子素子を良好に駆動させることが可能となる。

【0020】

また、本発明の電子部品は、前記封止部材が前記半導体基板の第2の面から離間されて配置されるとともに、前記電子素子が前記封止部材側に設けられていることが好ましい。

【0021】

本発明に係る電子部品では、電子素子が封止部材側に設けられているため、電子素子と導電部とを電気的に接続させることで、電子素子の封止を行うことができる。したがって、簡易な構成により、封止された電子部品を得ることが可能となる。

【0022】

また、本発明の電子部品は、前記半導体基板の第2の面と前記半導体基板の第2の面から離間されて配置された前記封止部材との間に支持基板が設けられ、前記電子素子が、前記支持基板上に設けられていることが好ましい。

【0023】

本発明に係る電子部品では、支持基板に電子素子が設けられているため、電子素子を良好に支持した状態で電子素子と導電部とを電気的に接続させることができる。したがって、電子素子を良好に駆動させることができる。

【0024】

また、本発明の電子部品は、前記電子素子が、前記半導体基板の第2の面から離間されて配置された支持基板に保持され、前記封止部材が、前記支持基板に保持された電子素子を封止するとともに、前記電子素子と電気的に接続された電子素子電極を備えることが好ましい。

【0025】

本発明に係る電子部品では、支持基板に保持された電子素子が封止部材により封止されているため、封止部材に設けられた電子素子電極と導電部とを電気的に接続させることにより、小型化,薄型化を実現しつつ、電子素子を良好に駆動させることができる。

【0026】

前記半導体基板の第2の面に、前記導電部と前記電子素子とを電気的に接続させた他面電極を備えることが好ましい。

本発明に係る電子部品では、導電部と電子素子とを電気的に接続させた他面電極を備えることにより、例えば、電子素子の電極形状に応じた他面電極を形成することで、電子素子と第2電極との導通状態を良好にすることが可能となる。

【0027】

本発明の回路基板は、上記の電子部品が実装されていることを特徴とする。

本発明に係る回路基板では、小型化・薄型化が実現された電子部品が実装された回路基板(プリント配線板等)を提供することができる。したがって、この回路基板を電子機器等に実装した際にも、電子機器全体の大型化を防止することができる。

【0028】

本発明の電子機器は、上記の電子部品が実装されていることを特徴とする。

本発明に係る電子機器では、小型化・薄型化が実現された電子部品が実装された電子機器を提供することができる。したがって、小型化された電子機器を得ることができる。

【図面の簡単な説明】

【0029】

【図1】本発明の一実施形態に係る半導体装置を示す断面図である。

【図2】図1の半導体装置のA矢視における平面図である。

【図3】図1の半導体装置のB矢視における平面図である。

【図4】本発明の一実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】本発明の一実施形態に係る半導体装置の製造方法を示す断面図である。

【図6】本発明の一実施形態に係る半導体装置の製造方法を示す断面図である。

【図7】本発明の第1実施形態に係る電子部品を示す断面図である。

【図8】図7の電子部品の電極を示す平面図である。

【図9】本発明の第2実施形態に係る電子部品を示す断面図である。

【図10】本発明の第3実施形態に係る電子部品を示す断面図である。

【図11】本発明の第4実施形態に係る電子部品を示す断面図である。

【図12】本発明の電子部品が搭載された電子機器を示す図である。

【発明を実施するための形態】

【0030】

[半導体装置の一実施形態]

次に、本発明の半導体装置の一実施形態について、図1から図6を参照して説明する。

本実施形態に係る半導体装置1は、図1に示すように、シリコン基板(半導体基板)10と、シリコン基板10の第1の面10aに形成され、外部機器であるプリント配線板(回路基板)Pに電気的に接続される接続部20とを備えている。

【0031】

シリコン基板10は、図1に示すように、第1の面10aから対向する第2の面10bに第2電極23に至る溝11が形成されており、この溝11の内部には導電性材料が充填された導電部12が設けられている。また、溝11の側壁には絶縁膜13が設けられており、導電部12とシリコン基板10とは電気的に絶縁されている。

また、シリコン基板10の第2の面10bの表面には、溝11が形成された領域以外の領域に裏面絶縁層14が形成されている。この裏面絶縁層14上には、電子素子として、例えば、弾性表面波素子「SAW(Surface Acoustic Wave)素子」の電極に応じた裏面電極(他面電極)15が、図3に示すように形成されている。

【0032】

接続部20は、シリコン基板10の第1の面10a上に設けられた下地層21と、下地層21の複数の所定領域のそれぞれに設けられた第1電極22及び第2電極23と、これら電極22,23が設けられた領域以外の領域に設けられた第1絶縁層24と、この第1絶縁層24上に形成された配線部30とを備えている。この下地層21は、例えば酸化珪素(SiO2)、窒化珪素(Si3N4)等の絶縁性材料によって形成されている。また、第1,第2電極22,23の材料としては、チタン(Ti)、窒化チタン(TiN)、アルミニウム(Al)、銅(Cu)、あるいは、これらを含む合金等が挙げられる。

なお、シリコン基板10には、図2に示すように、複数の電極が形成されていても構わないが、本実施形態では、第1電極22及び第2電極23のみについて説明する。

また、第2電極23は、第1絶縁層24に覆われていても構わない。

なお、不図示ではあるが、下地層21の下には、例えばトランジスタ,メモリ素子を有する集積回路が形成されている。そして、この集積回路が、第1電極22及び第2電極23と電気的に接続されている。

【0033】

配線部30は、図1及び図2に示すように、第1絶縁層24上に設けられた第1電極22と電気的に接続された第1配線(配線)31と、第2電極23の表面に設けられた金属膜32と、この第1配線(配線)31及び金属膜32上に設けられた第2絶縁層(応力緩和層)33と、第2絶縁層33上に形成されるとともに、第1配線31と電気的に接続された第2配線(配線)34と、第2配線34上に形成された第3絶縁層35とを備えている。また、第1配線31の一部が第2絶縁層33より露出してランド部36を形成しており、このランド部36と第2配線34とが電気的に接続されている。さらに、第2配線34上にはバンプ(外部接続端子)37が設けられ、半導体装置1はこのバンプ37を介してプリント配線板Pに電気的に接続されている。また、第3絶縁層35は、第2絶縁層33上及び第2配線34上のバンプ37が形成される領域以外の領域を覆うように設けられている。

【0034】

また、第1電極22は、第1配線31及び第2配線34を介してバンプ37と電気的に接続されている。また、第2電極23は、シリコン基板10の第1の面10a上に設けられた下地層21上に形成されとともに、溝11により一部が露出されている。これにより、この第2電極23は、第2電極23の裏面23aで溝11の内部の導電部12の一端部12aと電気的に接続されている。また、導電部12の他端部12bは、シリコン基板10の第2の面10bに設けられた裏面電極15と電気的に接続されている。すなわち、第2電極23はシリコン基板10の第2の面10bに設けられる電子素子と電気的に接続されるようになっている。

【0035】

また、第1,第2配線31,34の材料としては、金(Au)、銅(Cu)、銀(Ag)、チタン(Ti)、タングステン(W)、チタンタングステン(TiW)、窒化チタン(TiN)、ニッケル(Ni)、ニッケルバナジウム(NiV)、クロム(Cr)、アルミニウム(Al)、パラジウム(Pd)等が挙げられる。この第1,第2配線31,34としては、上述した材料の単層構造であっても良いし、複数組み合わせて積層構造にしても良い。

また、第1,第2,第3絶縁層24,33,35は、樹脂(合成樹脂)によって形成されている。これら第1,第2,第3絶縁層24,33,35を形成するための形成材料としては、ポリイミド樹脂、シリコーン変性ポリイミド樹脂、エポキシ樹脂、シリコーン変性エポキシ樹脂、アクリル樹脂、フェノール樹脂、BCB(benzocyclobutene)及びPBO(polybenzoxazole)等、絶縁性がある材料であれば良い。

なお、第1絶縁層24は、酸化珪素(SiO2)、窒化珪素(Si3N4)等の絶縁性材料によって形成されていても良い。

【0036】

また、金属膜32の材料は、第1,第2配線31,34と同一の材料であることが好ましい。金属膜32の材料としては、Au、TiW、Cu、Cr、Ni、Ti、W、NiV、Al等の金属を使用することができる。また、金属膜32は、これらの金属を積層して形成することも可能である。なお、金属膜(積層構造の場合、少なくとも1層)32は、電極よりも耐腐食性の高い材料、例えばAu、TiW、Crを用いて形成することが好ましい。これにより、電極の腐食を阻止して、電気的不良の発生を防止することが可能になるからである。

【0037】

[半導体装置の製造方法]

次に、図4及び図5を参照しながら半導体装置1の製造方法について説明する。ここで、本実施形態においては、半導体装置1は同一のシリコン基板(基板)100上に複数(図6参照)同時に一括して形成されるが、簡単のため図4及び図5においては1つの半導体装置1を形成する場合が示されている。

【0038】

まず、図4(a)に示すように、シリコン基板10の第1の面10a上に下地層21を形成した後、下地層21上に第1,第2電極22,23を形成する。そして、第1,第2電極22,23上に第1絶縁層24を形成し、周知のフォトリソグラフィ法及びエッチング法により、第1,第2電極22,23を覆う絶縁材料を除去する。なお、第2電極23を覆う絶縁材料は必ずしも除去しなくても良い。次いで、第1電極22を含む第1絶縁層24上には第1配線31を形成し、第2電極23の表面には金属膜32を形成する。第1配線31の形成方法としては、例えば、TiW、Cuの順にスパッタ法により形成した後、Cuをめっき法で形成することにより行われる。

【0039】

次に、第1配線31及び金属膜32を覆うように第2絶縁層33を形成し、周知のフォトリソグラフィ法により、第2絶縁層33のランド部36に対応する領域が除去され、第1配線31の一部が露出されてランド部36となる。そして、ランド部36に接続するように、第2絶縁層33上に第2配線34が形成され、その後、第2絶縁層33上及び第2配線34上のバンプ37が形成される領域以外の領域を覆うように第3絶縁層35を設けることにより、図4(a)に示すような形態となる。

【0040】

次に、図4(b)に示すように、シリコン基板10の第2の面10b上にフォトレジスト40をマスクとして用い、ドライエッチングにより、第2電極23に対応したシリコン基板10及び下地層21を除去する。これにより、図4(c)に示すように、シリコン基板10の第2の面10bから、第1の面10aに設けられた第2電極23の裏面23aが露出するまでエッチングを行い、溝11を形成する。

なお、フォトレジスト40をマスクとしたが、これに限ることはなく、例えば、ハードマスクとしてSiO2膜を用いても良く、フォトレジストマスク及びハードマスクを併用しても良い。また、エッチング方法としてはドライエッチングに限らず、ウエットエッチング、レーザ加工、あるいはこれらを併用しても良い。

【0041】

次に、図5(a)に示すように、シリコン基板10の第2の面10b及び溝11の内壁に裏面絶縁層14及び絶縁膜13を形成する。裏面絶縁層14及び絶縁膜13は、電流リークの発生、酸素及び水分等による半導体基板10の浸食等を防止するために設けられ、PECVD(Plasma Enhanced Chemical Vapor Deposition)を用いて形成した正珪酸四エチル(Tetra Ethyl Ortho Silicate:Si(OC2H5)4:以下、TEOSという)、すなわちPE−TEOS、及び、オゾンCVDを用いて形成したTEOS、すなわちO3−TEOSまたはCVDを用いて形成した酸化珪素(SiO2)を用いることができる。なお、裏面絶縁層14及び絶縁膜13は、絶縁性があれば、他の物でも良く、樹脂でもよい。そして、第2電極23の裏面23a部分に設けられた絶縁膜13をドライエッチングあるいはレーザ加工により除去することで、図5(b)に示すように、溝11の側壁のみに絶縁層13が設けられた形態となる。

【0042】

次に、電気化学プレーティング(ECP)法を用いて、溝11の内部にめっき処理が施され、その溝11の内側に導電部12を形成するための導電性材料を配置し、導電部12の一端部12aと露出した第2電極23とが、第2電極23の裏面23aで電気的に接続される。導電部12を形成するための導電性材料としては、例えば銅(Cu)を用いることができ、導電部12には銅(Cu)が埋め込まれる。本実施形態における導電部12を形成する工程には、例えば、TiN、Cuをスパッタ法で形成(積層)する工程と、Cuをめっき法で形成する工程とが含まれる。なお、TiW、Cuをスパッタ法で形成(積層)する工程と、Cuをめっき法で形成する工程とが含まれたものであってもよい。なお、導電部12の形成方法としては、上述した方法に限らず、導電ペースト、溶融金属、金属ワイヤ等を埋め込んでもよい。

また、本実施形態では、溝11の内部を導電部12で埋め込んでいるが、完全に埋め込まなくても、溝11の内壁に導電部12を設けて、第2電極23の裏面23aで電気的に接続される形態でも良い。

【0043】

導電部12を形成した後、シリコン基板10の第2の面10bにこの導電部12と電気的に接続されるように裏面電極15を形成することにより、図5(c)に示すような形態となる。なお、裏面電極15は、導電部12と同時、すなわち、一体的に形成しても良い。次に、シリコン基板10の第1の面10a側に設けられた第2配線34上に、例えば鉛フリーはんだからなるバンプ37を搭載する。なお、バンプ37を設ける際には、はんだボールを第2配線34上に搭載する形態でもよいし、はんだペーストを第2配線34上に印刷する形態でもよい。

【0044】

そして、図6に示すように、ダイシング装置110によって、シリコン基板100が半導体装置1毎にダイシング(切断)される。このように、シリコン基板100上に複数の半導体装置1を略同時に形成し、その後、そのシリコン基板100を半導体装置1毎に切断することで、図1に示す半導体装置1を得ることができる。このようにして、効率良く半導体装置1を製造することができ、半導体装置1の低コスト化を実現できる。

【0045】

本実施形態に係る半導体装置1によれば、第2電極23に至る溝11の内部に導電部12を形成することにより、第2電極23が、導電部12を介して電子素子と電気的に接続することが可能となり、また、第1電極22がバンプ37と電気的に接続されているため、外部機器等と接続可能な半導体装置1全体の小型化,薄型化及び高機能化を実現することが可能となる。

【0046】

[電子部品の第1実施形態]

次に、上述した半導体装置1に電子素子としてSAW素子(電子素子)60が実装された電子部品50の第1実施形態について、図7を参照して説明する。なお、以下に説明する各実施形態において、上述した一実施形態に係る半導体装置1と構成を共通とする箇所には同一符号を付けて、説明を省略することにする。

本実施形態の電子部品50に用いられる半導体装置51は、裏面電極15を設けていない点以外は上述した半導体装置1と同一の構成を有している。

【0047】

電子部品50は、図8に示すように、圧電薄膜(図示略)とこの圧電薄膜に接する櫛歯電極61とを備えている。そして、電子部品50は、図7に示すように、シリコン基板10の第2の面10b側に、導電部12の他端部12bと電気的に接続されるように、直接電子素子60が形成されている。また、不図示ではあるが、シリコン基板10の第1の面10a側には、例えばトランジスタ,メモリ素子を有する集積回路が形成されている。そして、導電部12の一端部12aが、この集積回路と第2電極23を介して電気的に接続されている。したがって、シリコン基板10の第2の面10bに設けられた電子素子60と、シリコン基板10の第1の面10a側に設けられた集積回路とが導電部12を介して電気的に接続されている。

【0048】

また、電子部品50は、シリコン基板10の第2の面10bとの間でSAW素子60を封止する封止部材52を備えている。本実施形態において封止部材52はガラス基板によって形成されているが、シリコン基板であってもよい。封止部材52は、シリコン基板10の第2の面10bから離間された位置に設けられている。シリコン基板10の第2の面10bの周縁部と封止部材52の内面52aの周縁部とは、接着剤層53により接着されている。接着剤層53は、例えばポリイミド樹脂等の合成樹脂で形成されている。そして、シリコン基板10の第2の面10bと、封止部材52の内面52aと、接着剤層53とで囲まれた内部空間55は略密閉(気密封止)されており、その内部空間55にSAW素子60が配置された構成となっている。

【0049】

[電子部品の製造方法]

次に、電子部品50の製造方法について説明する。

まず、上述した半導体装置1の製造方法と同様の工程により、導電部12まで形成した後、シリコン基板10の第2の面10bにSAW素子60を形成する。このSAW素子60を形成する工程には、圧電薄膜を形成する工程と、圧電薄膜に接するように、図8に示すような櫛歯電極61を形成する工程と、保護膜(図示略)を形成する工程とが含まれる。さらには、SAW素子60を形成する工程には、プラズマ等をSAW素子60に照射して周波数調整を行う工程が含まれる。圧電薄膜の形成材料としては、酸化亜鉛(ZnO)、窒化アルミニウム(AlN)、ニオブ酸リチウム(LiNbO3)、タンタル酸リチウム(LiTaO3)、ニオブ酸カリウム(KNbO3)等が挙げられる。櫛歯電極61の形成材料としては、アルミニウムを含む金属が挙げられる。保護膜の形成材料としては、酸化珪素(SiO2)、窒化珪素(Si3N4)、窒化チタン(TiN)等が挙げられる。そして、形成されるSAW素子60は、シリコン基板10の第2の面10bで、導電部12の他端部12bと電気的に接続される。

【0050】

次に、シリコン基板10の第2の面10b及び封止部材52の内面52aのうち少なくとも一方に、接着剤層53を形成するための接着剤が設けられる。接着剤層53としては、例えば感光性のポリイミド接着剤等を使用することができる。そして、その接着剤層53を介して、シリコン基板10の第2の面10bと封止部材52の内面52aとが対向するように、それらシリコン基板10と封止部材52とが接合される。これにより、図7に示すような形態が得られる。

【0051】

ここで、封止は、内部空間55を真空にする真空封止、内部空間55をN2、Ar、He等の所定ガスで置換するガス置換封止等してもよい。なお、シリコン基板10と封止部材52とを接合するとき、シリコン基板10の第2の面10bの周縁部に沿って金属突起を設け、封止部材52の内面52aに、前記金属突起と接着するための金属層を設け、それら金属突起及び金属層を介してシリコン基板10と封止部材52とを接合するようにしてもよい。封止部材52にガラスを用いた場合には、封止後に、レーザー等によりSAW素子60の周波数調整が可能となる。その後、シリコン基板10の第1の面10a側に設けられた第2配線34上に、例えば鉛フリーはんだからなるバンプ37が搭載される。なお、バンプ37を設ける際には、はんだボールを第2配線34上に搭載する形態でもよいし、はんだペーストを第2配線34上に印刷する形態でもよい。

【0052】

その後、この電子部品50も半導体装置1と同様に、同一のシリコン基板(基板)上に半導体装置50,SAW素子60及び封止部材52等を同時に一括して形成している。そこで、この電子部品50を半導体装置1と同様にしてダイシング装置110によって、電子部品50毎にダイシング(切断)される。これにより、電子部品50を低コストで製造できる。製造された電子部品50は、バンプ37を介してプリント配線板P等に搭載される。

【0053】

本実施形態に係る電子部品50によれば、シリコン基板10の第2の面10b側にSAW素子60を設け、導電部12の他端部12bとこのSAW素子60とを接続したので、シリコン基板10の第1の面10a側にSAW素子60を駆動制御する集積回路を設けておくことで、導電部12を介してSAW素子60と集積回路とを電気的に接続することができる。したがって、電子部品50全体の小型化・薄型化を実現しつつ、SAW素子60を良好に駆動することができる。そして、SAW素子60は封止部材52によって第2の面10bとの間で封止されるので、小型化・薄型化を実現しつつ、SAW素子60を良好に封止することができ、SAW素子60を良好に駆動することができる。

【0054】

[電子部品の第2実施形態]

次に、上述した半導体装置1に電子素子としてSAW素子71が実装された電子部品70の第2実施形態について、図9を参照して説明する。なお、以下に説明する各実施形態において、上述した第1実施形態に係る電子部品50と構成を共通とする箇所には同一符号を付けて、説明を省略することにする。

本実施形態に係る電子部品70は、SAW素子71が、シリコン基板10の第2の面10bに形成されておらず、シリコン基板10の第2の面10bから離間された位置に配された封止部材52に設けられている点で第1実施形態と異なる。

【0055】

SAW素子71は、シリコン基板10の第2の面10bと対向する封止部材52の内面52aに設けられている。また、SAW素子71には、シリコン基板10の第2の面10bと対向する面に端子72が設けられている。

半導体装置73には、シリコン基板10の第2の面10bの溝11上に裏面電極(他面電極)54が形成されている。そして、この裏面電極54と導電部12の他端部12bとが電気的に接続されている。裏面電極54は、SAW素子71の端子72に対応した位置に形成されている。すなわち、第2電極23は、シリコン基板10の第2の面10bに設けられるSAW素子71と導電部12及び裏面電極54を介して電気的に接続されるようになっている。

また、封止部材52は、シリコン基板、水晶基板、シリコン及びダイヤを有する基板によって構成されている。

【0056】

電子部品70の製造方法としては、封止部材52の内面52a上に予めSAW素子71を形成しておき、その後、シリコン基板10の第2の面10bに形成され裏面電極54と、封止部材52の内面52a上に形成されたSAW素子71の端子72とが電気的に接続するように、シリコン基板10と封止部材52とを接着剤層53を介して接合することにより、図9に示す電子部品70が得られる。なお、裏面電極54と端子51とは、接着剤層30の収縮による圧接でもよい。

【0057】

本実施形態に係る電子部品70によれば、シリコン基板10とは別の部材、すなわち、封止部材52にSAW素子71を設けることにより、シリコン基板10に掛かる熱応力、膜応力の影響を受けにくいため、良好な特性を得ることができる。

【0058】

[電子部品の第3実施形態]

次に、上述した半導体装置1に電子素子としてSAW素子81が実装された電子部品80の第3実施形態について、図10を参照して説明する。

本実施形態に係る電子部品80は、SAW素子81は、シリコン基板10の第2の面10bに形成されておらず、SAW素子81が支持基板82上に設けられている点で、第2実施形態と異なる。

【0059】

支持基板82は、シリコン基板10の第2の面10bとシリコン基板10の第2の面10bから離間された位置に配された封止部材52との間に設けられている。また、SAW素子81は、シリコン基板10の第2の面10bと対向する支持基板82の面82a側に設けられている。さらに、SAW素子81は、電子部品70の第2実施形態と同様に、シリコン基板10の第2の面10bと対向する面に端子83が設けられている。そして、この端子83と裏面電極54とが電気的に接続されている。

【0060】

本実施形態に係る電子部品80によれば、シリコン基板10とは別の部材、すなわち、支持基板82にSAW素子81を設けることにより、シリコン基板10に掛かる熱応力、膜応力の影響を受けにくいため、良好な特性を得ることができる。また、支持基板82により、SAW素子81を良好に支持した状態で、SAW素子81と導電部12とを電気的に接続させることが可能となる。

【0061】

[電子部品の第4実施形態]

次に、上述した半導体装置1に電子素子としてAT振動子(水晶振動子)91が実装された電子部品90の第4実施形態について、図11を参照して説明する。

本実施形態に係る電子部品90は、AT振動子91が、支持基板92に保持された状態で封止部材93により封止されている点で第2実施形態と異なる。

【0062】

支持基板92は、シリコン基板10の第2の面10bから離間されて配置されており、AT振動子91が、シリコン基板10の第2の面10bと対向する支持基板92の内面92aに設けられている。そして、AT振動子91は、支持基板92とシリコン基板10の第2の面10bとの間に設けられたガラス基板からなる封止部材93により封止されている。そして、支持基板92の内面92aと、封止部材93の内面93aとで囲まれた内部空間95は略密閉(気密封止)されている。

【0063】

また、封止部材93には、シリコン基板10の第2の面10bと対向する面に電子素子電極94が設けられている。そして、この電子素子電極94と裏面電極54とが電気的に接続されている。すなわち、第2電極23は、シリコン基板10の第2の面10bに設けられる導電部12及び裏面電極54を介して、AT振動子91と電気的に接続されるようになっている。

また、シリコン基板10の第2の面10bの周縁部と支持基板92の周縁部及び第2の面10bと封止部材93との間は、封止樹脂96により封止されている。

【0064】

本実施形態に係る電子部品90によれば、封止部材93により支持基板92に保持されたAT振動子が封止されているため、封止部材93に設けられた電子素子電極94と導電部12とを電気的に接続させることにより、小型化,薄型化を実現しつつ、電子素子を良好に駆動させることができる。

【0065】

<電子機器>

図12は、上述した電子部品50,70,80,90を搭載した電子機器の一例を示す図であって、携帯電話300を示す図である。小型化・薄型化及び高機能化が実現された本発明の電子部品を搭載したので、小型の携帯電話300が実現される。

【0066】

なお、本発明の技術範囲は上記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更を加えることが可能である。

例えば、上記半導体装置1の一実施形態において裏面電極15を設けたが、電子部品の電極が直接導電部12の他端部12bに接続されていても良い。

また、電子素子60,71,81,91と接続する裏面電極15,54の表面あるいは導電部12の他端部12bの表面には、金属接続しやすいように、金などの表面処理、あるいはロウ材(SnAgめっき等)を設けることが好ましい。また、上記各本実施形態においても、最終工程でダイシングする形態の他に、適切な工程(途中工程)で個片化するようにしてもよい。

【0067】

さらに、封止部材52,93をガラス基板によって構成した場合、そのガラス基板からなる封止部材52,93をダイシング(切断)する際には、図6を参照して説明したダイシング装置110によってダイシングすることもできるが、レーザを照射することによってダイシングを行うことや、ドライエッチング又はウエットエッチングの手法を用いてダイシングを行うこともできる。

また、本発明に係る電子素子としては、第1,第2,第3実施形態においてSAW素子を用いて説明したが、これに限らす、封止を必要とする素子、例えば、水晶振動子、圧電振動子、圧電音叉等であってもよい。また、第4実施形態においてはAT振動子(水晶振動子)を用いて説明したが、これに限らす、封止を必要とする素子、例えば、SAW素子、圧電振動子、圧電音叉等であってもよい。

【0068】

また、必要に応じては、シリコン基板10に接続部30を形成した後、シリコン基板10の薄型化を行うことも可能である。シリコン基板10を薄くする方法としては、まず、紫外光(UV光)の照射により剥離可能な接着剤で、シリコン基板10の第1の面10a側に不図示のガラス板を貼り付ける。このガラス板はWSS(Wafer Support System)と呼ばれるものの一部であって、シリコン基板10をガラス板に支持した後、このガラス板を貼り付けた状態で、シリコン基板10の第2の面10bに対して研磨処理、ドライエッチング処理、あるいはウエットエッチング処理等の所定の処理を施す。これにより、シリコン基板10が薄くされる。

【符号の説明】

【0069】

P…プリント配線板(回路基板)、1,51,73…半導体装置、10…シリコン基板(半導体基板)、10a…シリコン基板の第1の面、10b…シリコン基板の第2の面、11…溝、12…導電部、15,54…裏面電極(他面電極)、22…第1電極、23…第2電極、23a…第2電極の裏面、31…第1配線層(配線層)、33…第2絶縁層(応力緩和層)、34…第2配線層(配線層)、37…バンプ(外部接続端子)、50,70,80,90…電子部品、52,93…封止部材、60,71,81,91…SAW素子(電子素子)、92…支持基板、94…電子素子電極、100…シリコン基板(基板)、300…電子機器。

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板の第1の面上に設けられた第1電極と、

前記半導体基板の前記第1の面上の前記第1電極から離れた位置に設けられた第2電極と、

前記半導体基板の前記第1の面側に設けられた外部接続端子と、

前記半導体基板の前記第1の面と反対側の第2の面から前記第1の面上の前記第2電極に至る溝と、

前記溝の内部に設けられ、前記第2電極と電気的に接続された導電部と、を備え、

前記第1電極は、前記半導体基板の前記第1の面側に設けられた前記外部接続端子と電気的に接続される一方、

前記第2電極は、前記半導体基板の前記第2の面側に実装される電子素子と前記導電部を介して電気的に接続されるものであることを特徴とする半導体装置。

【請求項2】

前記半導体基板の第1の面に設けられるとともに、前記第1電極と前記外部接続端子とを電気的に接続させる配線と、

前記半導体基板と前記外部接続端子との間に設けられた応力緩和層とを備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2電極の表面には、前記配線と同一の材料の金属膜が設けられていることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記半導体基板の第2の面に、前記導電部と電気的に接続された他面電極を備えることを特徴とする請求項1から請求項3のいずれか1項に記載の半導体装置。

【請求項5】

半導体基板の第1の面に、後で形成する外部接続端子と電気的に接続される第1電極を形成する工程と、

前記半導体基板の第1の面に、後で形成する導電部と電気的に接続される第2電極を形成する工程と、

前記半導体基板上に前記第1電極と後で形成する外部接続端子とを電気的に接続する配線を形成する工程と、

前記半導体基板と前記外部接続端子との間に応力緩和層を形成する工程と、

前記半導体基板の第1の面の反対側の第2の面から前記第2電極に向かって前記半導体基板に溝を形成する工程と、

前記溝の側壁に絶縁膜を形成する工程と、

前記溝に電子素子と前記第2電極とを電気的に接続する導電部を形成する工程と、

前記配線上に、前記第1電極および前記配線と電気的に接続される外部接続端子を形成する工程と、を有することを特徴とする半導体装置の製造方法。

【請求項6】

前記溝を形成する工程は、フォトリソグラフィ法及びエッチング法を用いることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記導電部を形成する工程において、前記半導体基板の第2の面に、他面電極を前記導電部と一体に形成することを特徴とする請求項5または請求項6に記載の半導体装置の製造方法。

【請求項8】

前記半導体装置を同一の基板に複数同時に形成した後、前記基板を前記半導体装置毎に切断することを特徴とする請求項5から請求項7のいずれか1項に記載の半導体装置の製造方法。

【請求項9】

半導体基板と、

前記半導体基板の第1の面上に設けられた第1電極と、

前記半導体基板の前記第1の面上の前記第1電極から離れた位置に設けられた第2電極と、

前記半導体基板の前記第1の面側に設けられた外部接続端子と、

前記半導体基板の前記第1の面と反対側の第2の面から前記第1の面上の前記第2電極に至る溝と、

前記溝の内部に設けられ、前記第2電極と電気的に接続された導電部と、

前記半導体基板の前記第2の面側に実装され、前記導電部と電気的に接続された電子素子と、

前記電子素子を封止する封止部材と、を備え、

前記第1電極は、前記半導体基板の前記第1の面側に設けられた前記外部接続端子と電気的に接続される一方、

前記第2電極は、前記半導体基板の前記第2の面側に実装される電子素子と前記導電部を介して電気的に接続されていることを特徴とする電子部品。

【請求項10】

前記封止部材が前記半導体基板の第2の面から離間されて配置されるとともに、前記電子素子が前記封止部材側に設けられていることを特徴とする請求項9に記載の電子部品。

【請求項11】

前記半導体基板の第2の面と前記半導体基板の第2の面から離間されて配置された前記封止部材との間に支持基板が設けられ、

前記電子素子が、前記支持基板上に設けられていることを特徴とする請求項9に記載の電子部品。

【請求項12】

前記電子素子が、前記半導体基板の第2の面から離間されて配置された支持基板に保持され、

前記封止部材が、前記支持基板に保持された電子素子を封止するとともに、前記電子素子と電気的に接続された電子素子電極を備えることを特徴とする請求項9に記載の電子部品。

【請求項13】

前記半導体基板の第2の面に、前記導電部と前記電子素子とを電気的に接続させた他面電極を備えることを特徴とする請求項9から請求項12のいずれか1項に記載の電子部品。

【請求項14】

請求項9から請求項13のいずれか1項に記載の電子部品が実装されていることを特徴とする回路基板。

【請求項15】

請求項9から請求項13のいずれか1項に記載の電子部品が実装されていることを特徴とする電子機器。

【請求項1】

半導体基板と、

前記半導体基板の第1の面上に設けられた第1電極と、

前記半導体基板の前記第1の面上の前記第1電極から離れた位置に設けられた第2電極と、

前記半導体基板の前記第1の面側に設けられた外部接続端子と、

前記半導体基板の前記第1の面と反対側の第2の面から前記第1の面上の前記第2電極に至る溝と、

前記溝の内部に設けられ、前記第2電極と電気的に接続された導電部と、を備え、

前記第1電極は、前記半導体基板の前記第1の面側に設けられた前記外部接続端子と電気的に接続される一方、

前記第2電極は、前記半導体基板の前記第2の面側に実装される電子素子と前記導電部を介して電気的に接続されるものであることを特徴とする半導体装置。

【請求項2】

前記半導体基板の第1の面に設けられるとともに、前記第1電極と前記外部接続端子とを電気的に接続させる配線と、

前記半導体基板と前記外部接続端子との間に設けられた応力緩和層とを備えることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2電極の表面には、前記配線と同一の材料の金属膜が設けられていることを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記半導体基板の第2の面に、前記導電部と電気的に接続された他面電極を備えることを特徴とする請求項1から請求項3のいずれか1項に記載の半導体装置。

【請求項5】

半導体基板の第1の面に、後で形成する外部接続端子と電気的に接続される第1電極を形成する工程と、

前記半導体基板の第1の面に、後で形成する導電部と電気的に接続される第2電極を形成する工程と、

前記半導体基板上に前記第1電極と後で形成する外部接続端子とを電気的に接続する配線を形成する工程と、

前記半導体基板と前記外部接続端子との間に応力緩和層を形成する工程と、

前記半導体基板の第1の面の反対側の第2の面から前記第2電極に向かって前記半導体基板に溝を形成する工程と、

前記溝の側壁に絶縁膜を形成する工程と、

前記溝に電子素子と前記第2電極とを電気的に接続する導電部を形成する工程と、

前記配線上に、前記第1電極および前記配線と電気的に接続される外部接続端子を形成する工程と、を有することを特徴とする半導体装置の製造方法。

【請求項6】

前記溝を形成する工程は、フォトリソグラフィ法及びエッチング法を用いることを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記導電部を形成する工程において、前記半導体基板の第2の面に、他面電極を前記導電部と一体に形成することを特徴とする請求項5または請求項6に記載の半導体装置の製造方法。

【請求項8】

前記半導体装置を同一の基板に複数同時に形成した後、前記基板を前記半導体装置毎に切断することを特徴とする請求項5から請求項7のいずれか1項に記載の半導体装置の製造方法。

【請求項9】

半導体基板と、

前記半導体基板の第1の面上に設けられた第1電極と、

前記半導体基板の前記第1の面上の前記第1電極から離れた位置に設けられた第2電極と、

前記半導体基板の前記第1の面側に設けられた外部接続端子と、

前記半導体基板の前記第1の面と反対側の第2の面から前記第1の面上の前記第2電極に至る溝と、

前記溝の内部に設けられ、前記第2電極と電気的に接続された導電部と、

前記半導体基板の前記第2の面側に実装され、前記導電部と電気的に接続された電子素子と、

前記電子素子を封止する封止部材と、を備え、

前記第1電極は、前記半導体基板の前記第1の面側に設けられた前記外部接続端子と電気的に接続される一方、

前記第2電極は、前記半導体基板の前記第2の面側に実装される電子素子と前記導電部を介して電気的に接続されていることを特徴とする電子部品。

【請求項10】

前記封止部材が前記半導体基板の第2の面から離間されて配置されるとともに、前記電子素子が前記封止部材側に設けられていることを特徴とする請求項9に記載の電子部品。

【請求項11】

前記半導体基板の第2の面と前記半導体基板の第2の面から離間されて配置された前記封止部材との間に支持基板が設けられ、

前記電子素子が、前記支持基板上に設けられていることを特徴とする請求項9に記載の電子部品。

【請求項12】

前記電子素子が、前記半導体基板の第2の面から離間されて配置された支持基板に保持され、

前記封止部材が、前記支持基板に保持された電子素子を封止するとともに、前記電子素子と電気的に接続された電子素子電極を備えることを特徴とする請求項9に記載の電子部品。

【請求項13】

前記半導体基板の第2の面に、前記導電部と前記電子素子とを電気的に接続させた他面電極を備えることを特徴とする請求項9から請求項12のいずれか1項に記載の電子部品。

【請求項14】

請求項9から請求項13のいずれか1項に記載の電子部品が実装されていることを特徴とする回路基板。

【請求項15】

請求項9から請求項13のいずれか1項に記載の電子部品が実装されていることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−182468(P2011−182468A)

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願番号】特願2011−128945(P2011−128945)

【出願日】平成23年6月9日(2011.6.9)

【分割の表示】特願2008−56820(P2008−56820)の分割

【原出願日】平成17年6月8日(2005.6.8)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願日】平成23年6月9日(2011.6.9)

【分割の表示】特願2008−56820(P2008−56820)の分割

【原出願日】平成17年6月8日(2005.6.8)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]