半導体装置、半導体装置の製造方法

【課題】半導体チップが複数積層され、外部接続端子を仲介基板上に有する半導体装置において、半導体チップと仲介基板との接続信頼性を向上しかつコストダウンを図る構造体を提供する。

【解決手段】第1貫通電極群をもつ第1半導体チップと:第2貫通電極群と接続端子群とを有し、この端子群が第1半導体チップの裏面側の第1貫通電極群に対向、電気導通し、積層された第2半導体チップと:接続端子群と;第3貫通電極群と;接続端子群とは反対の側の面上の再配線層44と;該再配線層44のある面上に該再配線層44と電気的導通を有し形成された、配置の最小ピッチが第2貫通電極群のそれより長い対仲介基板接続端子61群と;を有し、積層された仲介基板100とを具備する。

【解決手段】第1貫通電極群をもつ第1半導体チップと:第2貫通電極群と接続端子群とを有し、この端子群が第1半導体チップの裏面側の第1貫通電極群に対向、電気導通し、積層された第2半導体チップと:接続端子群と;第3貫通電極群と;接続端子群とは反対の側の面上の再配線層44と;該再配線層44のある面上に該再配線層44と電気的導通を有し形成された、配置の最小ピッチが第2貫通電極群のそれより長い対仲介基板接続端子61群と;を有し、積層された仲介基板100とを具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の半導体チップが積層配置された半導体装置およびその製造方法に係り、特に、半導体装置としての外部接続用の端子を別の仲介基板上に有する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置としての高集積化の一環として、近年、複数の半導体チップが積層配置された構成のものが市場投入されている。例えば、特許第3896112号公報に開示されたような構成が一例である。積層配置された半導体チップどうしの電気的接続のため、半導体チップには貫通電極が形成され、これにより半導体基板を貫通する方向の電気の通り道(縦方向の配線)が確保される。貫通電極は、半導体製造プロセスにおけるレイアウトルールで形成され得るので、比較的細くかつ狭ピッチで設けることができる。

【0003】

特許第3896112号公報に開示された構成では、さらに、半導体装置としての外部接続用の端子を設けるため、半導体チップとは別の仲介基板(インターポーザ)が設けられている。この仲介基板上に設けられた外部接続端子により、半導体装置として、別の基板(マザーボードなど)上に実装が可能になっている。すなわち、仲介基板は、半導体チップが有する貫通電極の狭ピッチ配置を、基板実装に対応できる比較的広いピッチの端子に変換する機能を有している。

【0004】

上記文献では、半導体チップと仲介基板との電気的接続の詳細については言及が何らない。一般に、半導体チップと仲介基板とは設計や製造の素性が異なり、半導体チップと仲介基板との接続を半導体チップの貫通電極の狭ピッチに対応してなす場合には、接続の信頼性は半導体チップどうしの接続のようには高信頼性にならない。また、仲介基板のコストは、その最も微細な配線パターンの形成ルールに応じて決まるため、半導体チップの貫通電極の狭ピッチ配置に応じるものを用いるとすると非常に高価なものになる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3896112号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、上記した事情を考慮してなされたもので、複数の半導体チップが積層配置され、半導体装置としての外部接続用の端子を別の仲介基板上に有する半導体装置およびその製造方法において、半導体チップと仲介基板との接続の信頼性を向上しかつ半導体装置としてコストダウンを図ることができる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記の課題を解決するため、本発明の一態様である半導体装置は、第1半導体素子群および第1配線層が集積形成された第1機能面と;該第1機能面と該第1機能面に対向する第1裏面との間に貫通形成された、配置の最小ピッチが第1のピッチ長である第1貫通電極群と;を有する第1の半導体チップと、第2半導体素子群および第2配線層が集積形成された第2機能面と;前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第2機能面に配置された1,2チップ間接続端子群と;前記第2機能面と前記第2裏面との間に貫通形成された、配置の最小ピッチが第2のピッチ長である第2貫通電極群と;を有し、前記1,2チップ間接続端子群が前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、前記第1の半導体チップに対して積層配置された第2の半導体チップと、第3半導体素子群および第3配線層が集積形成された第3機能面と;前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第3機能面上にまたは該第3機能面に対向する第3裏面上に配置された2,3チップ間接続端子群と;前記第3機能面と前記第3裏面との間に貫通形成された第3貫通電極群と;前記2,3チップ間接続端子群が設けられた面とは反対の側の面上に設けられた再配線層と;該再配線層が設けられた面上に該再配線層と電気的導通を有して形成された、配置の最小ピッチが前記第2のピッチ長より長い第3のピッチ長である対仲介基板接続端子群と;を有し、前記2,3チップ間接続端子群が前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、前記第2の半導体チップに対して積層配置された第3の半導体チップと、第1の面と該第1の面に対向する第2の面とを有し;該第1の面上に、前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置された対半導体チップ接続端子群を有し;前記第2の面上に、前記対半導体チップ接続端子群に電気的に連なる外部接続端子群を有し;前記対半導体チップ接続端子群が前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気導通するように、前記第3の半導体チップに対して積層配置された仲介基板とを具備することを特徴とする。

【0008】

すなわち、下から、仲介基板、第3の半導体チップ、第2の半導体チップ、第1の半導体チップの配置の積層構造において、仲介基板と第3の半導体チップとの接続を担う対半導体チップ接続端子群および対仲介基板接続端子群の配置の最小ピッチ(上記で第3のピッチ長)が、第3の半導体チップと第2の半導体チップとの接続を担う2,3チップ間接続端子群および第2貫通電極群の配置の最小ピッチ(上記で第2のピッチ長)より長くなっている。したがって、仲介基板は、より粗いレイアウトルールを有するものを使用できる。粗いレイアウトルールによりコストダウンを図ることができ、かつ、積層形成時の位置合わせも容易になるため電気的接続の信頼性も向上する。

【0009】

また、本発明の別の態様である半導体装置の製造方法は、第1半導体素子群および第1配線層が集積形成された第1機能面と;該第1機能面と該第1機能面に対向する第1裏面との間に貫通形成された、配置の最小ピッチが第1のピッチ長である第1貫通電極群と;を有する第1の半導体チップが複数形成された第1のウエハに対して、第2半導体素子群および第2配線層が集積形成された第2機能面と;前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第2機能面に配置された1,2チップ間接続端子群と;前記第2機能面と前記第2裏面との間に貫通形成された、配置の最小ピッチが第2のピッチ長である第2貫通電極群と;を有する第2の半導体チップが複数形成された第2のウエハを、前記1,2チップ間接続端子群が前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、積層する工程と、前記第2のウエハに対して、第3半導体素子群および第3配線層が集積形成された第3機能面と;前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第3機能面上にまたは該第3機能面に対向する第3裏面上に配置された2,3チップ間接続端子群と;前記第3機能面と前記第3裏面との間に貫通形成された第3貫通電極群と;前記2,3チップ間接続端子群が設けられた面とは反対の側の面上に設けられた再配線層と;該再配線層が設けられた面上に該再配線層と電気的導通を有して形成された、配置の最小ピッチが前記第2のピッチ長より長い第3のピッチ長である対仲介基板接続端子群と;を有する第3の半導体チップが複数形成された第3のウエハを、前記2,3チップ間接続端子群が前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、積層する工程と、前記第1、第2、第3のウエハを有する積層体を、前記第1、第2、第3の半導体チップをそれぞれ1つずつ有するように個片化し、積層化半導体チップを形成する工程と、前記積層化半導体チップに対して、第1の面と該第1の面に対向する第2の面とを有し;該第1の面上に、前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置された対半導体チップ接続端子群を有し;前記第2の面上に、前記対半導体チップ接続端子群に電気的に連なる外部接続端子群を有する仲介基板を、前記対半導体チップ接続端子群が前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気導通するように、積層する工程とを具備することを特徴とする。

【0010】

この製造方法は、上記の半導体装置を製造するひとつの方法である。ここで特徴的なのは、半導体チップどうしの積層は個片化する前の状態であるウエハで行い、その後個片化して積層化半導体チップを得ている点である。半導体チップ上の素子や電極、配線のレイアウト精度は高く、ウエハどうしで積層しても位置合わせ精度が保てる。また、これによりさらに生産性を向上しコストダウンを図れる。

【発明の効果】

【0011】

本発明によれば、複数の半導体チップが積層配置され、半導体装置としての外部接続用の端子を別の仲介基板上に有する半導体装置およびその製造方法において、半導体チップと仲介基板との接続の信頼性を向上しかつ半導体装置としてコストダウンを図ることができる。

【図面の簡単な説明】

【0012】

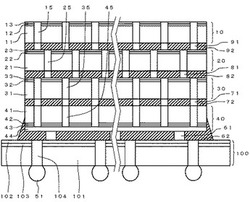

【図1】本発明の一実施形態に係る半導体装置の構成を模式的に示す断面図。

【図2】図1に示した半導体装置の製造過程の一部を模式的に断面で示す工程図。

【図3】図2に示した工程を概観する斜視図。

【図4】図1に示した半導体装置の製造過程の別の一部を模式的に断面で示す工程図。

【図5】図1に示した半導体装置の製造過程のさらに別の一部を模式的に断面で示す工程図。

【図6】図1に示した半導体装置における半導体チップ40の素子形成層42によって構成される例示的回路(マルチプレクサまたはデマルチプレクサ)の機能図。

【図7】図1に示した半導体装置における半導体チップ40の素子形成層42によって構成される別の例示的回路(DC−DCコンバータまたは直流電圧レギュレータ)の機能図。

【図8】本発明の別の実施形態に係る半導体装置の構成を模式的に示す断面図。

【図9】図8に示した半導体装置における半導体チップ40の再配線層44によって構成される例示的導電路構成を示す模式図。

【図10】本発明のさらに別の実施形態である半導体装置で使用可能な仲介基板の別例を模式的に示す断面図。

【発明を実施するための形態】

【0013】

本発明の実施態様として、前記第3の半導体チップの前記2,3チップ間接続端子群が、該第3の半導体チップの前記第3裏面上に配置され、前記仲介基板の前記外部接続端子群の一端子から、該仲介基板の対半導体チップ接続端子群の一端子および前記第3の半導体チップの前記対仲介基板接続端子群の一端子を経由して、該第3の半導体チップの前記再配線層に至る導電路が形成され、前記導電路が前記第3半導体素子群で構成される回路につながり、該回路により電気的に分岐されて、前記第3の半導体チップの前記第3貫通電極群のうちの複数の電極のそれぞれに電気的に連なっている、とすることができる。

【0014】

この態様は、仲介基板に隣り合う第3の半導体チップのみ、第1、第2の半導体チップとは異なりその機能面を仲介基板側に向けて配置した態様である。第3の半導体チップでは、仲介基板との接続が対半導体チップ接続端子群および対仲介基板接続端子群によりなされるが、それらの配置ピッチは比較的粗であるので、その数も比較的少ないのが自然である。そこで、少ない接続による導電路を第3の半導体チップの機能面にある回路で電気的に分岐させ、そこから、比較的配置ピッチが密であり、したがってその数も比較的多いのが自然である第3貫通電極群に電気的につないだ構成である。第3貫通電極群につながれた導電路は、以降は、第2、第1の半導体チップの、第2貫通電極群、第1貫通電極群により所望の半導体チップの機能面に電気導通することができる。

【0015】

また、実施態様として、前記第3の半導体チップの前記2,3チップ間接続端子群が、該第3の半導体チップの前記第3機能面上に配置され、前記仲介基板の前記外部接続端子群の一端子から、該仲介基板の対半導体チップ接続端子群の一端子および前記第3の半導体チップの前記対仲介基板接続端子群の一端子を経由して該第3の半導体チップの前記再配線層に至り、さらに該再配線層により電気的に分岐され、該第3の半導体チップの前記第3貫通電極群のうちの複数の電極のそれぞれに導通する導電路が形成されている、とすることもできる。

【0016】

この態様は、仲介基板に隣り合う第3の半導体チップも含めて、第1、第2の半導体チップの機能面を仲介基板の側に向けて配置した態様である。第3の半導体チップでは、仲介基板との接続が対半導体チップ接続端子群および対仲介基板接続端子群によりなされるが、それらの配置ピッチは比較的粗であるので、その数も比較的少ないのが自然である。そこで、少ない接続による導電路を第3の半導体チップの第3裏面にある再配線層で電気的に分岐させ、そこから、比較的配置ピッチが密であり、したがってその数も比較的多いのが自然である第3貫通電極群に電気的につないだ構成である。第3貫通電極群につながれた導電路は、以降は、第3の半導体チップの機能面、および第2、第1の半導体チップの、第2貫通電極群、第1貫通電極群により所望の半導体チップの機能面に電気導通することができる。

【0017】

また、実施態様として、前記第3の半導体チップの前記第3半導体素子群で構成される前記回路が、マルチプレクサまたはデマルチプレクサである、とすることができる。これは、電気的に分岐させる回路としての好例である。マルチプレクサであれば、パラレル-シリアル変換回路が挙げられ、デマルチプレクサであれば、シリアル-パラレル変換回路が挙げられる。

【0018】

また、実施態様として、前記第3の半導体チップの前記第3半導体素子群で構成される前記回路が、DC−DCコンバータまたは直流電圧レギュレータである、とすることができる。これも、電気的に分岐させる回路としての好例である。すなわち、この回路の入力側がある高い直流電圧、出力側が、それより低いいくつかの直流電圧であり、出力側の各電圧は、その電圧が必要な各半導体チップに各貫通電極群を介して送られる。

【0019】

また、実施態様として、前記導電路が、電源電位の導電路またはグラウンド電位の導電路である、とすることができる。この態様は、仲介基板に隣り合う第3の半導体チップも含めて、第1、第2の半導体チップの機能面を仲介基板の側に向けて配置した態様の場合のひとつの例である。第3の半導体チップ上の再配線層により電源の導電路、グラウンドの導電路を分けることにより、各半導体チップの電源供給路が共通に有するインピーダンスを減らすことができ、各半導体チップの安定動作上好ましい。

【0020】

また、実施態様として、前記仲介基板が、前記対半導体チップ接続端子群に属する端子の総数より少ない総数の、前記外部接続端子群に属する端子を有する、とすることができる。これは、例えば、仲介基板に、対半導体チップ接続端子群と外部接続端子群との単純な導電機能よりほかの機能を持たせ、これにより外部接続端子群のほうの端子数を減らした態様である。

【0021】

また、実施態様として、前記仲介基板が、貫通電極群の形成された、無機材料の基材を有する、とすることができる。また、前記仲介基板が、有機材料基材の多層配線板である、とすることもできる。無機材料の場合は、シリコンの基材とすることができる。対半導体チップ接続端子群と外部接続端子群との導電機能を貫通電極群により持たせるのは、構成を単純化する上で好ましい態様である。これをシリコンの基材において設けるのは、半導体製造プロセス技術を応用すれば比較的容易に実現できる。仲介基板を有機材料基材の多層配線板とする場合は、さらに安価な製造コストの期待ができる。

【0022】

また、実施態様として、前記仲介基板が、抵抗素子またはコンデンサ素子を具有している、とすることができる。仲介基板にこのような素子を具有させれば、半導体装置として付加価値の増大になる。具有させる素子として、抵抗素子であれば、ダンピング抵抗、終端抵抗、プルアップあるいはプルダウン抵抗、コンデンサ素子であれば、デカップリングコンデンサ(バイパスコンデンサ)、カップリングコンデンサなどの用途、機能が考えられる。

【0023】

以上を踏まえ、以下では本発明の実施形態を図面を参照しながら説明する。図1は、本発明の一実施形態に係る半導体装置の構成を模式的に示す断面図である。図1に示すように、この半導体装置は、積層化された4つの半導体チップ10、20、30、40(=半導体チップによる積層体;半導体チップ20が第1の半導体チップ、半導体チップ30が第2の半導体チップ、半導体チップ40が第3の半導体チップ)を有しており、この積層体の図示下側にさらに仲介基板100を設けた構成になっている。半導体チップは、さらに多層に構成させることもできるが、以下では説明簡素化のためこのような4つの場合を説明する。

【0024】

半導体チップ10は、半導体基板11、素子形成層(半導体素子群)12、配線層(配線形成層)13、貫通電極15を有する。同様に、半導体チップ20、30、40は、それぞれ、半導体基板21、31、41、素子形成層(半導体素子群)22、32、42、配線層(配線形成層)23、33、43、貫通電極25、35、45を有する。半導体チップ40のみ、さらに、配線層43上に再配線層44を有する。半導体チップ10、20、30は、図示上側面が機能面(素子、配線の集積形成がなされた面)であり、半導体チップ40のみ図示下側面が機能面になっている。なお、半導体チップ10、20、30、40の裏面(機能面とは反対側の面)上には、不図示の絶縁膜が設けられている。

【0025】

仲介基板100は、仲介基板基材101、配線層102、素子形成層103、貫通電極104を有する。仲介基板100の半導体チップ40が位置する側とは反対面上には、外部接続端子としてのはんだボール51が設けられている。この実施形態では、仲介基板100の基材101がシリコン(半導体)の場合を説明する。仲介基板100の基材としては、これに限らず、別の無機材料(例えばセラミックス)や、有機材料(例えばガラスエポキシ樹脂)のものも利用できる。なお、仲介基板100のはんだボール51が設けられた側の面上には不図示の絶縁膜が設けられている。

【0026】

半導体チップ10と同20との接続は、電気的にチップ間接続端子91によりなされ、さらにそれらの間の間隙に接着樹脂92が充填されることで、機械的かつ対環境の観点での信頼性を確保している。これらの点は、半導体チップ20と同30との間(チップ間接続端子81、接着樹脂82による)、半導体チップ30と同40との間(チップ間接続端子71、接着樹脂72による)も同様である。

【0027】

一方、半導体チップ40と仲介基板100との間には、対仲介基板接続端子61が設けられており、これによりこれら間の電気的接続がなされている。そして、半導体チップ40と仲介基板100との間の間隙に接着樹脂62が充填され、これにより、半導体チップ10、20、30、40で構成の積層体と仲介基板100との機械的かつ対環境の観点での信頼性確保が図られている。

【0028】

半導体チップ間に設けられた接続端子91、81、71の配置ピッチは、例えば、20μmから40μmと、ごく狭く設定されたものである。接続端子91、81、71は、半導体製造プロセスを適用することの一環として形成され得る。そして、接続端子91、81、71により半導体チップどうしを電気的に信頼性高く接続することは、設計や製造の素性がほぼ同一の半導体チップ10、20、30、40におけるそれらの配置の精度からして比較的容易である。

【0029】

これに対して、対仲介基板接続端子61の配置ピッチは、例えば、100μmから250μm程度になっており、これは、半導体チップ40のみ再配線層44を有し、これにより、端子として再配置を行った結果である。このように対仲介基板接続端子61の配置ピッチが比較的粗であることから、これに応ずる仲介基板100は、その最も微細な配線パターンの形成ルールが粗で済み、コストダウンを図ることができる。配置ピッチが粗の対仲介基板接続端子61を利用するこのような電気的接続は、設計や製造の素性が異なる半導体チップ40側と仲介基板100との積層接続の高信頼性化に適している。

【0030】

以下、各部の構成をさらに説明する。半導体チップ10は、半導体基板11の機能面上に素子形成層12を有し、この素子形成層12に形成された半導体素子を所望に電気的に接続するため配線層13が素子形成層12上に形成されている。これらは周知の構成である。貫通電極15は、半導体基板11を貫通して設けられた例えばCu(銅)製の縦方向の導電路であり、機能面上の配線層13と電気的導通がなされ得る。

【0031】

半導体チップ10の全厚みは例えば50μm、半導体チップ10の大きさは最大で例えば10mm角であり、貫通電極15の直径は例えば10μmから20μm、その配置ピッチは上記のように例えば20μmから40μmである。貫通電極15の配置としては、半導体チップ10の四辺に沿って、または、半導体チップ10の機能面内に設けられた回路ブロックごとの四辺に沿って、というような配置があり得る。半導体チップ10において貫通電極15の総数は、例えば1000個から10000個である。半導体チップ20、30、40においても、それらの半導体基板、素子形成層、配線層、貫通電極について同様である。

【0032】

半導体チップ40にのみ設けられた再配線層44は、仲介基板100との接続に対応する対仲介基板接続端子61を形設するための付加的な配線層である。電気的には、対仲介基板接続端子61に導通するほかに、素子形成層42の素子や貫通電極45とも導通し得る。

【0033】

チップ間接続端子91は、半導体チップ10裏面側の貫通電極15のそれぞれに対接するように、半導体チップ20の配線層23上に設けられており、その材質は例えばAu(金)やはんだ、その高さは例えば5μmから10μmである。チップ間接続端子91は、または、半導体チップ20の配線層23が含む接続パッド(不図示)のそれぞれに対接するように、半導体チップ10の裏面側の貫通電極15上に設けられていてもよい。接着樹脂92は、例えば、エポキシ樹脂(フィラーが配合されていない)である。チップ間接続端子81、接着樹脂82もそれぞれ構成的に同様である。

【0034】

チップ間接続端子71は、半導体チップ30裏面側の貫通電極35のそれぞれに対接するように、半導体チップ40の貫通電極45上に設けられており、その材質は例えば金やはんだ、その高さは例えば5μmから10μmである。チップ間接続端子71は、または、半導体チップ40裏面側の貫通電極45のそれぞれに対接するように、半導体チップ30の貫通電極35上に設けられていてもよい。接着樹脂92は、例えば、エポキシ樹脂(フィラーが配合されていない)である。

【0035】

仲介基板100は、仲介基板基材101の機能面上に素子形成層103を有し、この素子形成層103に形成された素子を所望に電気的に接続するため配線層102が素子形成層103上に形成されている。貫通電極104は、仲介基板基材101を貫通して設けられた例えばCu(銅)製の縦方向の導電路であり、機能面上の配線層102と電気的導通がなされ得る。

【0036】

仲介基板100の全厚みは例えば200μmであり、貫通電極104の直径は例えば50μm、その配置ピッチは例えば300μmである。貫通電極104の配置は、外部接続端子であるはんだボール51の配置(エリア配置)に対応して、平面的にはグリッド状の配置である。貫通電極104の総数(=はんだボール51の総数)は、例えば400個である。

【0037】

仲介基板100の素子形成層103には、この半導体装置として、付加価値の増大を図るような素子を作り込むことができる。例えば、デカップリングコンデンサ(バイパスコンデンサ)やカップリングコンデンサとして機能させるコンデンサ素子、ダンピング抵抗、終端抵抗や、プルアップまたはプルダウン抵抗として機能させる抵抗素子が挙げられる。また、素子形成層103および配線層102があることによって、外部接続端子51のそれぞれから対仲介基板接続端子61のそれぞれに至る導電路は、単純な1対1の接続であるとは限らず、外部接続端子51の総数の方が対仲介基板接続端子61の総数より少なくなることもあり得る。

【0038】

対仲介基板接続端子61は、仲介基板100の配線層102が含む対半導体チップ接続端子(不図示)のそれぞれに対接するように、半導体チップ40の再配線層44上に設けられており、その材質は例えばCu(銅)やはんだ、その高さは例えば50μm、その直径は例えば50μmから100μmである。その配置は、ピッチが既述のように例えば100μmから250μmであって例えばグリッド状に配置(エリア配置)されており、その総数は、例えば(100個程度から)500個程度である。接着樹脂62は、例えば、エポキシ樹脂(フィラーが配合されていない)である。

【0039】

次に、図1に示した半導体装置の製造方法について図2ないし図5を参照して説明する。図2、図4、図5は、図1に示した半導体装置の製造過程の一部を模式的に断面で示す工程図であり、図3は、図2に示した工程を概観する斜視図である。これらの図において図1中に示した構成要素と同一または同一相当のものには同一符号を付してある。

【0040】

図2から説明する。図2は、最初の段階として、半導体チップ10に半導体チップ20を積層、固定する工程を示している。この段階において、半導体チップ20(の機能面)上には、あらかじめ、半導体チップ10の裏面側の貫通電極15のそれぞれに対接できるようにチップ間接続端子91が形設されている。この端子91は、既述のように、半導体チップ20における半導体製造プロセスの一環として位置精度をもって形成されたものである。

【0041】

貫通電極15、25の形成方法については、すでに周知事項であり詳細を省略するが、概略として次のような工程が一般的である。すなわち、まず、エッチングによる半導体基板11、21への中途深さ穴の形成、その穴の内壁面上への絶縁膜の形成、その絶縁膜内での金属(Cu)層の成長による充填、そしてその後に金属層が露出するまで半導体基板11、21の裏面を研削する、という工程である。

【0042】

図2に示すように、あらかじめ、半導体チップ20の機能面上に、硬化前の接着樹脂92Aを全面塗布する。そして、図示の配置により、チップ間接続端子91が半導体チップ10の裏面の側の貫通電極15に電極ごとに対向してこの電極のそれぞれに電気導通するように、積層し、さらに、接着樹脂92Aを硬化させ一体化して、2つの半導体チップ10、20を有する積層体を得る。この電気的導通を確実にするため、例えば、ボンディング技術やフリップチップ接続技術と同様の、超音波による金属間接合部の生成技術を利用できる。

【0043】

この積層は、実際には、図3に示されるごとく、半導体チップ10、20に個片化される前のウエハの段階で行うことができる。図3は、既述のように図2に示した工程を概観する斜視図である。半導体チップ20に個片化される前のウエハ20Wに対して硬化前の接着樹脂92A(図3では不図示)が全面塗布され、そしてその上に、半導体チップ10に個片化される前のウエハ10Wが積層配置される。半導体チップ10、同20には、設計や製造の素性が同一のものを使用することが容易であり、このような関係から、ウエハ段階で積層すれば、数多くの半導体チップについて効率的に位置精度の確保された積層が可能である。半導体チップ10、20上の素子や電極、配線のレイアウト精度は高く、ウエハどうしで積層しても各部同時に位置合わせ精度が保てる。

【0044】

なお、すでに述べたようにチップ間接続端子91は、あらかじめ、半導体チップ10裏面の貫通電極15上に設けておくこともできる。この場合には、チップ間接続端子91を形成するため、半導体チップ10の裏面上に少しの半導体製造プロセスを適用することになる。半導体チップ10の裏面上には不図示の絶縁膜があることをすでに説明しているが、それを形成するプロセスと一連のプロセスとしてチップ間接続端子91の形成を行うことができる。このように半導体チップ10裏面の貫通電極15上にチップ間接続端子91をあらかじめ設ける場合は、これと対接するために、半導体チップ20の配線層23には対接用の端子(パッド)が設けられる。

【0045】

次に、図4を参照して説明する。図4は、3つの半導体チップ10、20、30を有する積層体に半導体チップ40を積層、固定する工程を示している。なお、3つの半導体チップ10、20、30を有する積層体を得るために、図2に示した工程により得られた2つの半導体チップ10、20を有する積層体に半導体チップ30を積層、一体化する工程については、図2における説明が援用できるので省略する。その場合の半導体チップ30の積層も、やはりウエハの段階で行うのが効率上、有用である。

【0046】

図4に示す段階において、半導体チップ40(の裏面)の貫通電極45上には、あらかじめ、半導体チップ30の裏面側の貫通電極35のそれぞれに対接できるようにチップ間接続端子71が形設されている。この端子71は、既述のように、半導体チップ40の裏面上における半導体製造プロセスの一環として位置精度をもって形成されたものである。

【0047】

そして、図4に示すように、あらかじめ、半導体チップ40の裏面上に、硬化前の接着樹脂72Aを全面塗布する。続いて、図示の配置により、チップ間接続端子71が半導体チップ30の裏面の側の貫通電極35に電極ごとに対向してこの電極のそれぞれに電気導通するように、積層し、さらに、接着樹脂72Aを硬化させ一体化して、4つの半導体チップ10、20、30、40を有する積層体を得る。この積層工程も、やはり、ウエハの段階で行うのが効率上、有用であり、上記電気的導通を確実にするため、例えば、ボンディング技術やフリップチップ接続技術と同様の、超音波による金属間接合部の生成技術を利用できる。

【0048】

また、図4に示す工程においても、チップ間接続端子71は、あらかじめ、半導体チップ30裏面の貫通電極35上に設けておくこともできる。この場合には、チップ間接続端子71を形成するため、半導体チップ30の裏面上に少しの半導体製造プロセスを適用することになる。半導体チップ30の裏面上には不図示の絶縁膜があることをすでに説明しているが、貫通電極35上へチップ間接続端子71を形成する場合は、これを、絶縁膜を形成するプロセスと一連のプロセスとして行うことができる。

【0049】

次に図5を参照して説明する。図5は、4つの半導体チップ10、20、30、40を有する積層体を仲介基板100上に取り付け固定する工程を示している。図4までに示した工程により、半導体チップ10、20、30、40を有する積層体(ウエハの積層体)を得たら、次に、このウエハをダイシングし個片化を行う。図5に示す工程は、この個片化後の積層体を用いる。なお、一方の仲介基板100については、製造効率化のため、個片化する前の多数の基板が並んで一体に形成されている基板を用いることができる。

【0050】

図5に示すように、半導体チップの積層体の半導体チップ40の再配線層44上には、あらかじめ、再配線層44と電気的導通を有して、配置の最小ピッチがチップ間接続端子71などのそれより長いピッチ長の対仲介基板接続端子61を形成する。より具体的に、対仲介基板接続端子61は、仲介基板100の配線層102が含む対半導体チップ接続端子102Tに端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置、形設される。この対仲介基板接続端子61の形設は、再配線層44の形成工程と同様の、半導体チップ40に対する付加的な工程として行うことができる。

【0051】

そして、図示の配置により、対仲介基板接続端子61が仲介基板100の配線層102が含む対半導体チップ接続端子102Tに端子ごとに対向してこの端子のそれぞれに電気導通するように、接続する。より具体的には、例えば、対半導体チップ接続端子102T上にあらかじめクリームはんだ(不図示)を塗布しておき、端子61と端子102Tとを対接した状態でこのクリームはんだをリフローする。

【0052】

なお、対仲介基板接続端子61を、図示するような凸状には再配線層44上に設けず、対半導体チップ接続端子102Tの方を、あらかじめ仲介基板100の配線層102上に凸状に設けるようにしてもよい。この場合には、凸状の対半導体チップ接続端子と対接するために、半導体チップ40の再配線層44には対接用の端子(パッド)が設けられる。

【0053】

以上のようにして半導体チップ10、20、30、40を有する積層体を仲介基板100上に取り付け、固定したら、次に、積層体と仲介基板100との間に、接着樹脂62とすべき液状の接着樹脂(フィラーが配合されていない)を例えば毛細管現象を利用して充填する。そして、全体を加熱して液状の接着樹脂を硬化させて固体化した接着樹脂62に変化させる。続いて、はんだボール51の貫通電極104上への取り付け、および仲介基板100を個片化することにより、図1に示したような半導体装置を製造することができる。

【0054】

以上説明のように、仲介基板100には、より粗いレイアウトルールを有するものを使用できる。粗いレイアウトルールによりコストダウンを図ることができ、かつ、半導体チップ10、20、30、40を有する積層体を取り付け固定する時の位置合わせも容易になるため電気的接続の信頼性も向上する。さらに、このように粗いレイアウトルールの場合、領域的な余裕から、その配線についてこれをインピーダンスのコントロールされた伝送線路として機能させる配線構造にすることが容易である。この点の付加価値増大も利点になる。

【0055】

以上の説明では、完成品として仲介基板100上に半導体チップ積層体が1つのみ取り付け固定された構成を説明したが、仲介基板上に2つ以上の積層体が横方向に並んで取り付け固定された構成もあり得る。2つの積層体が並んでいる場合のアプリケーションとしては、一方の積層体がメモリで、他方の積層体がCPUである構成が考えられる。

【0056】

次に、図1に示した半導体装置において好ましい、半導体チップ40が有する内部の回路構成について図6を参照して説明する。図6は、図1に示した半導体装置における半導体チップ40の素子形成層42によって構成される例示的回路(デマルチプレクサまたはマルチプレクサ)の機能図である。図6において、図1中に示した構成要素に対応する部分には同一符号を付してある。

【0057】

図6に示すように、半導体チップ40の素子形成層42には、その構成される素子により、例えばデマルチプレクサ4aが作り込まれている(デマルチプレクサ4aを構成するため実際には配線層43が含む配線も使用される)。そして、デマルチプレクサ4aの入力側への導電路は、対仲介基板接続端子61から、再配線層44を経て配線層43により構成される。一方、デマルチプレクサ4aの出力側は、16本の出力となって、それぞれ、配線層43、貫通電極45を経て、各半導体チップ30、20、10(実際にはさらに積層された多数の半導体チップ)に導通している。

【0058】

デマルチプレクサ4aの入力側は例えば16GHzの信号であり、その出力側は例えば1GHzの信号である。入力側のノード数がデマルチプレクサ4aにより出力側で16倍に増えるが、これらの信号を各半導体チップ30、20、10に供給するには、多数配置されている貫通電極45、35、25が利用できる。一方、デマルチプレクサ4aの入力側信号のノード数は少ないが、それに応じて少ない数の対仲介基板接続端子61で対応ができる。

【0059】

以上はデマルチプレクサ4aを例として説明したが、マルチプレクサの場合(図6で上側の16本の信号が入力信号で、下側のノードが出力信号の場合)も同様である。このように、この半導体装置の構成として、半導体チップ40の素子形成層42が有する回路としてデマルチプレクサ(シリアルパラレル変換回路)やマルチプレクサ(パラレルシリアル変換回路)を具有させることは構成上の理に適っており非常に有用である。

【0060】

次に、図7は、図1に示した半導体装置における半導体チップ40の素子形成層42によって構成される別の例示的回路(DC−DCコンバータまたは直流電圧レギュレータ)の機能図である。図7において、図1中に示した構成要素に対応する部分には同一符号を付してある。

【0061】

図7に示すように、半導体チップ40の素子形成層42には、その構成される素子により、例えばDC−DCコンバータ(または直流電圧レギュレータ、以下同)4bが作り込まれている(回路として実際には配線層43が含む配線も使用される)。そして、DC−DCコンバータの入力側への導電路は、対仲介基板接続端子61から、再配線層44を経て配線層43により構成される。一方、DC−DCコンバータ4bの出力側は、電圧の異なる例えば4本の出力となって、それぞれ、配線層43、貫通電極45を経て、各半導体チップ30、20、10(実際にはさらに積層された多数の半導体チップ)に導通している。

【0062】

このDC−DCコンバータ4bをその入出力のノード数でみると、入力側は1つのノードであり、出力側は4つのノードである。すなわち、DC−DCコンバータ4bによりノード数が4倍に増えるが、それらの出力電圧を各半導体チップ30、20、10に供給するには、多数配置されている貫通電極45、35、25を利用できる。一方、DC−DCコンバータ4bの入力側については、少ない数の対仲介基板接続端子61で対応ができる。このように、この半導体装置の構成として、半導体チップ40の素子形成層42が有する回路としてDC−DCコンバータ(直流電圧レギュレータ)4bを具有させることは構成上の理に適っており非常に有用である。

【0063】

次に、本発明の別の実施形態に係る半導体装置について図8を参照して説明する。図8は、別の実施形態に係る半導体装置の構成を模式的に示す断面図である。図8において、図1中に示した構成要素と同一のものには同一符号を付してある。その説明は特に加えるべき事項がない限り省略する。

【0064】

この実施形態の図1に示した実施形態との違いは、仲介基板100に隣り合う半導体チップ40Aとして、その機能面を図示上側に向けて配置している点である。この実施形態の場合のチップ間接続端子71や接着樹脂72については、チップ間接続端子91、接着樹脂92の場合の説明を参照することができる。そして、半導体チップ40Aは、再配線層44をその裏面側に設けている。すなわち、裏面側に再配線層44を形成するプロセスが施されている。これにより再配線層44が仲介基板100に対向する面に設けられる点で、図1に示した実施形態と同じになる。よって、再配線層44、対仲介基板接続端子61、接着樹脂62についてはすでに説明した通りである。

【0065】

次に、図8に示した半導体装置において好ましい、半導体チップ40Aが有する再配線層44の回路(導電路)構成について図9を参照して説明する。図9は、図8に示した半導体装置における半導体チップ40の再配線層44によって構成される例示的導電路構成を示す模式図である。図9において、図8中に示した構成要素に対応する部分には同一符号を付してある。

【0066】

図9に示すように、半導体チップ40の再配線層44では、その含まれる導電路により、電気的に分岐するパターンが形成されている。そして、分岐のもとの側は、対仲介基板接続端子61から接続されていて、一方、分岐先の側は例えば4本に分岐して、それぞれ、貫通電極45を経て、各半導体チップ40A(の機能面)、30、20、10(実際にはさらに積層された多数の半導体チップ)に導通している。

【0067】

すなわち、導電路の分岐により、その数は増えるが、それらを各半導体チップ40A(の機能面)、30、20、10に導通させるには、多数配置されている貫通電極45、35、25を利用できる。一方、分岐のもとの側については、少ない数の対仲介基板接続端子61で対応ができる。このように、この半導体装置の構成として、半導体チップ40Aの再配線層44が有する導電路として電気的な分岐路を具有させることは構成上の理に適っており非常に有用である。

【0068】

このような分岐路としては、電源パターンやグラウンドパターンを例示することができる。半導体チップ40A上の再配線層44により電源の導電路、グラウンドの導電路を分けることにより、各半導体チップ40A、30、20、10の電源供給路が共通に有するインピーダンスを減らすことができ、それらの半導体チップを動作安定化する上で好ましい。

【0069】

次に、本発明のさらに別の実施形態について図10を参照して説明する。図10は、本発明のさらに別の実施形態である半導体装置で使用可能な仲介基板の別例を模式的に示す断面図である。上記で説明した実施形態では、仲介基板としてシリコンの基材を有する基板を使用したものを説明したが、シリコンの基板に代えて、有機樹脂材料でできた多層配線板を利用することもできる。そこで、図10には、このような多層配線板のひとつの例を示している。このような多層配線板200を用いる場合も、図5に示した半導体チップ積層体の取り付け固定の工程においては、製造効率化のため、多層配線板200として個片化する前の多面付け基板を用いることができる。

【0070】

この多層配線板200は、図10に示すように、6層の配線層221〜226を有する、部品内蔵の多層配線板である。配線層数はこれに限られないが、以下では、この多層配線板200の構成を参考までに説明する。

【0071】

多層配線板200は、絶縁層211、同212、同213、同214、同215、配線層(配線パターン)221、同222、同223、同224、同225、同226(=合計6層)、層間接続体231、同232、同234、同235、スルーホール導電体233、受動素子部品241、はんだ251、はんだレジスト261、262を有する。

【0072】

受動素子部品241は、表面実装用のチップ部品であり、例えばチップコンデンサ、チップ抵抗である。その平面的な大きさは例えば0.6mm×0.3mmである。両端に端子を有し、その下側が配線層222による実装用ランドに対向位置している。受動素子部品241の端子と実装用ランドとははんだ251により電気的、機械的に接続されている。

【0073】

配線層221、226は、配線板としての両主面上の配線層であってランドを含んでいる。配線層221によるランドは、外部接続端子としてのランドであり、配線層226によるランドは、半導体チップの積層体との電気的接続を行うためのランドである。はんだが位置するランドの部分を除いて両主面上には、はんだ接続時に溶融したはんだをランド部分に留めかつその後は保護層として機能するはんだレジスト261、262が形成されている(厚さはそれぞれ例えば20μm程度)。ランド部分の表層には、耐腐食性の高いNi/Auのめっき層(不図示)を形成しておいてもよい。

【0074】

配線層222、223、224、225は、それぞれ、内層の配線層であり、順に、配線層221と配線層222の間に絶縁層211が、配線層222と配線層223の間に絶縁層212が、配線層223と配線層224との間に絶縁層213が、配線層224と配線層225との間に絶縁層214が、配線層225と配線層226との間に絶縁層215が、それぞれ位置しこれらの配線層221〜226を隔てている。各配線層221〜226は、例えばそれぞれ厚さ18μmの金属(銅)箔からなっている。

【0075】

各絶縁層211〜215は、絶縁層213を除き例えばそれぞれ厚さ100μm、絶縁層213のみ例えば厚さ300μmで、それぞれ例えばガラスエポキシ樹脂からなるリジッドな素材である。特に絶縁層213は、内蔵された受動素子部品241に相当する位置部分が開口部となっており、受動素子部品241を埋設するための空間を提供する。絶縁層212、214は、内蔵された受動素子部品241のための絶縁層213の上記開口部および絶縁層213のスルーホール導電体233内部の空間を埋めるように変形進入しており内部に空隙となる空間は存在しない。

【0076】

配線層221と配線層222とは、それらのパターンの面の間に挟設されかつ絶縁層211を貫通する層間接続体231により導通し得る。同様に、配線層222と配線層223とは、それらのパターンの面の間に挟設されかつ絶縁層212を貫通する層間接続体232により導通し得る。配線層223と配線層224とは、絶縁層213を貫通して設けられたスルーホール導電体233により導通し得る。配線層224と配線層225とは、それらのパターンの面の間に挟設されかつ絶縁層214を貫通する層間接続体234により導通し得る。配線層225と配線層226とは、それらのパターンの面の間に挟設されかつ絶縁層215を貫通する層間接続体235により導通し得る。

【0077】

層間接続体231、232、234、235は、それぞれ、導電性組成物のスクリーン印刷により形成される導電性バンプを由来とするものであり、その製造工程に依拠して軸方向(図1の図示で上下の積層方向)に径が変化している。その直径は、太い側で例えば200μmである。

【0078】

図10に示す多層配線板は一例であり、周知の構成の別の多層配線板を使用してもよい。特に、部品内蔵の配線板を使用することで、上記実施形態におけるシリコンの仲介基板100を使用する場合と同様に、半導体装置として、付加価値の増大を図ることができる。内蔵の部品としては、すでに述べたように、例えば、デカップリングコンデンサ(バイパスコンデンサ)やカップリングコンデンサとして機能させるコンデンサ素子、ダンピング抵抗、終端抵抗やプルアップまたはプルダウン抵抗として機能させる抵抗素子が挙げられる。

【0079】

なお、仲介基板200のような有機材料の基板を用いる場合には、半導体素子40、40Aとの間に設けられる接着樹脂62には、熱膨張率の違いを空間的に緩衝するため、フィラーを含有させた例えばエポキシ樹脂を用いるとよい。

【符号の説明】

【0080】

4a…デマルチプレクサ(またはマルチプレクサ)、4b…DC−DCコンバータ(または直流電圧レギュレータ)、10,20,30,40,40A…半導体チップ、10W,20W…ウエハ、11,21,31,41…半導体基板、12,22,32,42…素子形成層(半導体素子群)、13,23,33,43…配線層(配線形成層)、44…再配線層、15,25,35,45…貫通電極、51…はんだボール(外部接続端子)、61…対仲介基板接続端子、62…接着樹脂、71,81,91…チップ間接続端子、72,82,92…接着樹脂、72A…硬化前の接着樹脂、92A…硬化前の接着樹脂、100…仲介基板(シリコン製)、101…仲介基板基材、102…配線層、102T…対半導体チップ接続端子、103…素子形成層、104…貫通電極、200…仲介基板(有機材料製の多層配線板)、211,212,213,214,215…絶縁層、221,222,223,224,225,226…配線層(配線パターン)、231,232,234,235…層間接続体(導電性組成物印刷による導電性バンプ)、233…スルーホール導電体、241…受動素子部品、251…はんだ、261,262…はんだレジスト。

【技術分野】

【0001】

本発明は、複数の半導体チップが積層配置された半導体装置およびその製造方法に係り、特に、半導体装置としての外部接続用の端子を別の仲介基板上に有する半導体装置およびその製造方法に関する。

【背景技術】

【0002】

半導体装置としての高集積化の一環として、近年、複数の半導体チップが積層配置された構成のものが市場投入されている。例えば、特許第3896112号公報に開示されたような構成が一例である。積層配置された半導体チップどうしの電気的接続のため、半導体チップには貫通電極が形成され、これにより半導体基板を貫通する方向の電気の通り道(縦方向の配線)が確保される。貫通電極は、半導体製造プロセスにおけるレイアウトルールで形成され得るので、比較的細くかつ狭ピッチで設けることができる。

【0003】

特許第3896112号公報に開示された構成では、さらに、半導体装置としての外部接続用の端子を設けるため、半導体チップとは別の仲介基板(インターポーザ)が設けられている。この仲介基板上に設けられた外部接続端子により、半導体装置として、別の基板(マザーボードなど)上に実装が可能になっている。すなわち、仲介基板は、半導体チップが有する貫通電極の狭ピッチ配置を、基板実装に対応できる比較的広いピッチの端子に変換する機能を有している。

【0004】

上記文献では、半導体チップと仲介基板との電気的接続の詳細については言及が何らない。一般に、半導体チップと仲介基板とは設計や製造の素性が異なり、半導体チップと仲介基板との接続を半導体チップの貫通電極の狭ピッチに対応してなす場合には、接続の信頼性は半導体チップどうしの接続のようには高信頼性にならない。また、仲介基板のコストは、その最も微細な配線パターンの形成ルールに応じて決まるため、半導体チップの貫通電極の狭ピッチ配置に応じるものを用いるとすると非常に高価なものになる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3896112号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、上記した事情を考慮してなされたもので、複数の半導体チップが積層配置され、半導体装置としての外部接続用の端子を別の仲介基板上に有する半導体装置およびその製造方法において、半導体チップと仲介基板との接続の信頼性を向上しかつ半導体装置としてコストダウンを図ることができる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記の課題を解決するため、本発明の一態様である半導体装置は、第1半導体素子群および第1配線層が集積形成された第1機能面と;該第1機能面と該第1機能面に対向する第1裏面との間に貫通形成された、配置の最小ピッチが第1のピッチ長である第1貫通電極群と;を有する第1の半導体チップと、第2半導体素子群および第2配線層が集積形成された第2機能面と;前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第2機能面に配置された1,2チップ間接続端子群と;前記第2機能面と前記第2裏面との間に貫通形成された、配置の最小ピッチが第2のピッチ長である第2貫通電極群と;を有し、前記1,2チップ間接続端子群が前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、前記第1の半導体チップに対して積層配置された第2の半導体チップと、第3半導体素子群および第3配線層が集積形成された第3機能面と;前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第3機能面上にまたは該第3機能面に対向する第3裏面上に配置された2,3チップ間接続端子群と;前記第3機能面と前記第3裏面との間に貫通形成された第3貫通電極群と;前記2,3チップ間接続端子群が設けられた面とは反対の側の面上に設けられた再配線層と;該再配線層が設けられた面上に該再配線層と電気的導通を有して形成された、配置の最小ピッチが前記第2のピッチ長より長い第3のピッチ長である対仲介基板接続端子群と;を有し、前記2,3チップ間接続端子群が前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、前記第2の半導体チップに対して積層配置された第3の半導体チップと、第1の面と該第1の面に対向する第2の面とを有し;該第1の面上に、前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置された対半導体チップ接続端子群を有し;前記第2の面上に、前記対半導体チップ接続端子群に電気的に連なる外部接続端子群を有し;前記対半導体チップ接続端子群が前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気導通するように、前記第3の半導体チップに対して積層配置された仲介基板とを具備することを特徴とする。

【0008】

すなわち、下から、仲介基板、第3の半導体チップ、第2の半導体チップ、第1の半導体チップの配置の積層構造において、仲介基板と第3の半導体チップとの接続を担う対半導体チップ接続端子群および対仲介基板接続端子群の配置の最小ピッチ(上記で第3のピッチ長)が、第3の半導体チップと第2の半導体チップとの接続を担う2,3チップ間接続端子群および第2貫通電極群の配置の最小ピッチ(上記で第2のピッチ長)より長くなっている。したがって、仲介基板は、より粗いレイアウトルールを有するものを使用できる。粗いレイアウトルールによりコストダウンを図ることができ、かつ、積層形成時の位置合わせも容易になるため電気的接続の信頼性も向上する。

【0009】

また、本発明の別の態様である半導体装置の製造方法は、第1半導体素子群および第1配線層が集積形成された第1機能面と;該第1機能面と該第1機能面に対向する第1裏面との間に貫通形成された、配置の最小ピッチが第1のピッチ長である第1貫通電極群と;を有する第1の半導体チップが複数形成された第1のウエハに対して、第2半導体素子群および第2配線層が集積形成された第2機能面と;前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第2機能面に配置された1,2チップ間接続端子群と;前記第2機能面と前記第2裏面との間に貫通形成された、配置の最小ピッチが第2のピッチ長である第2貫通電極群と;を有する第2の半導体チップが複数形成された第2のウエハを、前記1,2チップ間接続端子群が前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、積層する工程と、前記第2のウエハに対して、第3半導体素子群および第3配線層が集積形成された第3機能面と;前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第3機能面上にまたは該第3機能面に対向する第3裏面上に配置された2,3チップ間接続端子群と;前記第3機能面と前記第3裏面との間に貫通形成された第3貫通電極群と;前記2,3チップ間接続端子群が設けられた面とは反対の側の面上に設けられた再配線層と;該再配線層が設けられた面上に該再配線層と電気的導通を有して形成された、配置の最小ピッチが前記第2のピッチ長より長い第3のピッチ長である対仲介基板接続端子群と;を有する第3の半導体チップが複数形成された第3のウエハを、前記2,3チップ間接続端子群が前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、積層する工程と、前記第1、第2、第3のウエハを有する積層体を、前記第1、第2、第3の半導体チップをそれぞれ1つずつ有するように個片化し、積層化半導体チップを形成する工程と、前記積層化半導体チップに対して、第1の面と該第1の面に対向する第2の面とを有し;該第1の面上に、前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置された対半導体チップ接続端子群を有し;前記第2の面上に、前記対半導体チップ接続端子群に電気的に連なる外部接続端子群を有する仲介基板を、前記対半導体チップ接続端子群が前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気導通するように、積層する工程とを具備することを特徴とする。

【0010】

この製造方法は、上記の半導体装置を製造するひとつの方法である。ここで特徴的なのは、半導体チップどうしの積層は個片化する前の状態であるウエハで行い、その後個片化して積層化半導体チップを得ている点である。半導体チップ上の素子や電極、配線のレイアウト精度は高く、ウエハどうしで積層しても位置合わせ精度が保てる。また、これによりさらに生産性を向上しコストダウンを図れる。

【発明の効果】

【0011】

本発明によれば、複数の半導体チップが積層配置され、半導体装置としての外部接続用の端子を別の仲介基板上に有する半導体装置およびその製造方法において、半導体チップと仲介基板との接続の信頼性を向上しかつ半導体装置としてコストダウンを図ることができる。

【図面の簡単な説明】

【0012】

【図1】本発明の一実施形態に係る半導体装置の構成を模式的に示す断面図。

【図2】図1に示した半導体装置の製造過程の一部を模式的に断面で示す工程図。

【図3】図2に示した工程を概観する斜視図。

【図4】図1に示した半導体装置の製造過程の別の一部を模式的に断面で示す工程図。

【図5】図1に示した半導体装置の製造過程のさらに別の一部を模式的に断面で示す工程図。

【図6】図1に示した半導体装置における半導体チップ40の素子形成層42によって構成される例示的回路(マルチプレクサまたはデマルチプレクサ)の機能図。

【図7】図1に示した半導体装置における半導体チップ40の素子形成層42によって構成される別の例示的回路(DC−DCコンバータまたは直流電圧レギュレータ)の機能図。

【図8】本発明の別の実施形態に係る半導体装置の構成を模式的に示す断面図。

【図9】図8に示した半導体装置における半導体チップ40の再配線層44によって構成される例示的導電路構成を示す模式図。

【図10】本発明のさらに別の実施形態である半導体装置で使用可能な仲介基板の別例を模式的に示す断面図。

【発明を実施するための形態】

【0013】

本発明の実施態様として、前記第3の半導体チップの前記2,3チップ間接続端子群が、該第3の半導体チップの前記第3裏面上に配置され、前記仲介基板の前記外部接続端子群の一端子から、該仲介基板の対半導体チップ接続端子群の一端子および前記第3の半導体チップの前記対仲介基板接続端子群の一端子を経由して、該第3の半導体チップの前記再配線層に至る導電路が形成され、前記導電路が前記第3半導体素子群で構成される回路につながり、該回路により電気的に分岐されて、前記第3の半導体チップの前記第3貫通電極群のうちの複数の電極のそれぞれに電気的に連なっている、とすることができる。

【0014】

この態様は、仲介基板に隣り合う第3の半導体チップのみ、第1、第2の半導体チップとは異なりその機能面を仲介基板側に向けて配置した態様である。第3の半導体チップでは、仲介基板との接続が対半導体チップ接続端子群および対仲介基板接続端子群によりなされるが、それらの配置ピッチは比較的粗であるので、その数も比較的少ないのが自然である。そこで、少ない接続による導電路を第3の半導体チップの機能面にある回路で電気的に分岐させ、そこから、比較的配置ピッチが密であり、したがってその数も比較的多いのが自然である第3貫通電極群に電気的につないだ構成である。第3貫通電極群につながれた導電路は、以降は、第2、第1の半導体チップの、第2貫通電極群、第1貫通電極群により所望の半導体チップの機能面に電気導通することができる。

【0015】

また、実施態様として、前記第3の半導体チップの前記2,3チップ間接続端子群が、該第3の半導体チップの前記第3機能面上に配置され、前記仲介基板の前記外部接続端子群の一端子から、該仲介基板の対半導体チップ接続端子群の一端子および前記第3の半導体チップの前記対仲介基板接続端子群の一端子を経由して該第3の半導体チップの前記再配線層に至り、さらに該再配線層により電気的に分岐され、該第3の半導体チップの前記第3貫通電極群のうちの複数の電極のそれぞれに導通する導電路が形成されている、とすることもできる。

【0016】

この態様は、仲介基板に隣り合う第3の半導体チップも含めて、第1、第2の半導体チップの機能面を仲介基板の側に向けて配置した態様である。第3の半導体チップでは、仲介基板との接続が対半導体チップ接続端子群および対仲介基板接続端子群によりなされるが、それらの配置ピッチは比較的粗であるので、その数も比較的少ないのが自然である。そこで、少ない接続による導電路を第3の半導体チップの第3裏面にある再配線層で電気的に分岐させ、そこから、比較的配置ピッチが密であり、したがってその数も比較的多いのが自然である第3貫通電極群に電気的につないだ構成である。第3貫通電極群につながれた導電路は、以降は、第3の半導体チップの機能面、および第2、第1の半導体チップの、第2貫通電極群、第1貫通電極群により所望の半導体チップの機能面に電気導通することができる。

【0017】

また、実施態様として、前記第3の半導体チップの前記第3半導体素子群で構成される前記回路が、マルチプレクサまたはデマルチプレクサである、とすることができる。これは、電気的に分岐させる回路としての好例である。マルチプレクサであれば、パラレル-シリアル変換回路が挙げられ、デマルチプレクサであれば、シリアル-パラレル変換回路が挙げられる。

【0018】

また、実施態様として、前記第3の半導体チップの前記第3半導体素子群で構成される前記回路が、DC−DCコンバータまたは直流電圧レギュレータである、とすることができる。これも、電気的に分岐させる回路としての好例である。すなわち、この回路の入力側がある高い直流電圧、出力側が、それより低いいくつかの直流電圧であり、出力側の各電圧は、その電圧が必要な各半導体チップに各貫通電極群を介して送られる。

【0019】

また、実施態様として、前記導電路が、電源電位の導電路またはグラウンド電位の導電路である、とすることができる。この態様は、仲介基板に隣り合う第3の半導体チップも含めて、第1、第2の半導体チップの機能面を仲介基板の側に向けて配置した態様の場合のひとつの例である。第3の半導体チップ上の再配線層により電源の導電路、グラウンドの導電路を分けることにより、各半導体チップの電源供給路が共通に有するインピーダンスを減らすことができ、各半導体チップの安定動作上好ましい。

【0020】

また、実施態様として、前記仲介基板が、前記対半導体チップ接続端子群に属する端子の総数より少ない総数の、前記外部接続端子群に属する端子を有する、とすることができる。これは、例えば、仲介基板に、対半導体チップ接続端子群と外部接続端子群との単純な導電機能よりほかの機能を持たせ、これにより外部接続端子群のほうの端子数を減らした態様である。

【0021】

また、実施態様として、前記仲介基板が、貫通電極群の形成された、無機材料の基材を有する、とすることができる。また、前記仲介基板が、有機材料基材の多層配線板である、とすることもできる。無機材料の場合は、シリコンの基材とすることができる。対半導体チップ接続端子群と外部接続端子群との導電機能を貫通電極群により持たせるのは、構成を単純化する上で好ましい態様である。これをシリコンの基材において設けるのは、半導体製造プロセス技術を応用すれば比較的容易に実現できる。仲介基板を有機材料基材の多層配線板とする場合は、さらに安価な製造コストの期待ができる。

【0022】

また、実施態様として、前記仲介基板が、抵抗素子またはコンデンサ素子を具有している、とすることができる。仲介基板にこのような素子を具有させれば、半導体装置として付加価値の増大になる。具有させる素子として、抵抗素子であれば、ダンピング抵抗、終端抵抗、プルアップあるいはプルダウン抵抗、コンデンサ素子であれば、デカップリングコンデンサ(バイパスコンデンサ)、カップリングコンデンサなどの用途、機能が考えられる。

【0023】

以上を踏まえ、以下では本発明の実施形態を図面を参照しながら説明する。図1は、本発明の一実施形態に係る半導体装置の構成を模式的に示す断面図である。図1に示すように、この半導体装置は、積層化された4つの半導体チップ10、20、30、40(=半導体チップによる積層体;半導体チップ20が第1の半導体チップ、半導体チップ30が第2の半導体チップ、半導体チップ40が第3の半導体チップ)を有しており、この積層体の図示下側にさらに仲介基板100を設けた構成になっている。半導体チップは、さらに多層に構成させることもできるが、以下では説明簡素化のためこのような4つの場合を説明する。

【0024】

半導体チップ10は、半導体基板11、素子形成層(半導体素子群)12、配線層(配線形成層)13、貫通電極15を有する。同様に、半導体チップ20、30、40は、それぞれ、半導体基板21、31、41、素子形成層(半導体素子群)22、32、42、配線層(配線形成層)23、33、43、貫通電極25、35、45を有する。半導体チップ40のみ、さらに、配線層43上に再配線層44を有する。半導体チップ10、20、30は、図示上側面が機能面(素子、配線の集積形成がなされた面)であり、半導体チップ40のみ図示下側面が機能面になっている。なお、半導体チップ10、20、30、40の裏面(機能面とは反対側の面)上には、不図示の絶縁膜が設けられている。

【0025】

仲介基板100は、仲介基板基材101、配線層102、素子形成層103、貫通電極104を有する。仲介基板100の半導体チップ40が位置する側とは反対面上には、外部接続端子としてのはんだボール51が設けられている。この実施形態では、仲介基板100の基材101がシリコン(半導体)の場合を説明する。仲介基板100の基材としては、これに限らず、別の無機材料(例えばセラミックス)や、有機材料(例えばガラスエポキシ樹脂)のものも利用できる。なお、仲介基板100のはんだボール51が設けられた側の面上には不図示の絶縁膜が設けられている。

【0026】

半導体チップ10と同20との接続は、電気的にチップ間接続端子91によりなされ、さらにそれらの間の間隙に接着樹脂92が充填されることで、機械的かつ対環境の観点での信頼性を確保している。これらの点は、半導体チップ20と同30との間(チップ間接続端子81、接着樹脂82による)、半導体チップ30と同40との間(チップ間接続端子71、接着樹脂72による)も同様である。

【0027】

一方、半導体チップ40と仲介基板100との間には、対仲介基板接続端子61が設けられており、これによりこれら間の電気的接続がなされている。そして、半導体チップ40と仲介基板100との間の間隙に接着樹脂62が充填され、これにより、半導体チップ10、20、30、40で構成の積層体と仲介基板100との機械的かつ対環境の観点での信頼性確保が図られている。

【0028】

半導体チップ間に設けられた接続端子91、81、71の配置ピッチは、例えば、20μmから40μmと、ごく狭く設定されたものである。接続端子91、81、71は、半導体製造プロセスを適用することの一環として形成され得る。そして、接続端子91、81、71により半導体チップどうしを電気的に信頼性高く接続することは、設計や製造の素性がほぼ同一の半導体チップ10、20、30、40におけるそれらの配置の精度からして比較的容易である。

【0029】

これに対して、対仲介基板接続端子61の配置ピッチは、例えば、100μmから250μm程度になっており、これは、半導体チップ40のみ再配線層44を有し、これにより、端子として再配置を行った結果である。このように対仲介基板接続端子61の配置ピッチが比較的粗であることから、これに応ずる仲介基板100は、その最も微細な配線パターンの形成ルールが粗で済み、コストダウンを図ることができる。配置ピッチが粗の対仲介基板接続端子61を利用するこのような電気的接続は、設計や製造の素性が異なる半導体チップ40側と仲介基板100との積層接続の高信頼性化に適している。

【0030】

以下、各部の構成をさらに説明する。半導体チップ10は、半導体基板11の機能面上に素子形成層12を有し、この素子形成層12に形成された半導体素子を所望に電気的に接続するため配線層13が素子形成層12上に形成されている。これらは周知の構成である。貫通電極15は、半導体基板11を貫通して設けられた例えばCu(銅)製の縦方向の導電路であり、機能面上の配線層13と電気的導通がなされ得る。

【0031】

半導体チップ10の全厚みは例えば50μm、半導体チップ10の大きさは最大で例えば10mm角であり、貫通電極15の直径は例えば10μmから20μm、その配置ピッチは上記のように例えば20μmから40μmである。貫通電極15の配置としては、半導体チップ10の四辺に沿って、または、半導体チップ10の機能面内に設けられた回路ブロックごとの四辺に沿って、というような配置があり得る。半導体チップ10において貫通電極15の総数は、例えば1000個から10000個である。半導体チップ20、30、40においても、それらの半導体基板、素子形成層、配線層、貫通電極について同様である。

【0032】

半導体チップ40にのみ設けられた再配線層44は、仲介基板100との接続に対応する対仲介基板接続端子61を形設するための付加的な配線層である。電気的には、対仲介基板接続端子61に導通するほかに、素子形成層42の素子や貫通電極45とも導通し得る。

【0033】

チップ間接続端子91は、半導体チップ10裏面側の貫通電極15のそれぞれに対接するように、半導体チップ20の配線層23上に設けられており、その材質は例えばAu(金)やはんだ、その高さは例えば5μmから10μmである。チップ間接続端子91は、または、半導体チップ20の配線層23が含む接続パッド(不図示)のそれぞれに対接するように、半導体チップ10の裏面側の貫通電極15上に設けられていてもよい。接着樹脂92は、例えば、エポキシ樹脂(フィラーが配合されていない)である。チップ間接続端子81、接着樹脂82もそれぞれ構成的に同様である。

【0034】

チップ間接続端子71は、半導体チップ30裏面側の貫通電極35のそれぞれに対接するように、半導体チップ40の貫通電極45上に設けられており、その材質は例えば金やはんだ、その高さは例えば5μmから10μmである。チップ間接続端子71は、または、半導体チップ40裏面側の貫通電極45のそれぞれに対接するように、半導体チップ30の貫通電極35上に設けられていてもよい。接着樹脂92は、例えば、エポキシ樹脂(フィラーが配合されていない)である。

【0035】

仲介基板100は、仲介基板基材101の機能面上に素子形成層103を有し、この素子形成層103に形成された素子を所望に電気的に接続するため配線層102が素子形成層103上に形成されている。貫通電極104は、仲介基板基材101を貫通して設けられた例えばCu(銅)製の縦方向の導電路であり、機能面上の配線層102と電気的導通がなされ得る。

【0036】

仲介基板100の全厚みは例えば200μmであり、貫通電極104の直径は例えば50μm、その配置ピッチは例えば300μmである。貫通電極104の配置は、外部接続端子であるはんだボール51の配置(エリア配置)に対応して、平面的にはグリッド状の配置である。貫通電極104の総数(=はんだボール51の総数)は、例えば400個である。

【0037】

仲介基板100の素子形成層103には、この半導体装置として、付加価値の増大を図るような素子を作り込むことができる。例えば、デカップリングコンデンサ(バイパスコンデンサ)やカップリングコンデンサとして機能させるコンデンサ素子、ダンピング抵抗、終端抵抗や、プルアップまたはプルダウン抵抗として機能させる抵抗素子が挙げられる。また、素子形成層103および配線層102があることによって、外部接続端子51のそれぞれから対仲介基板接続端子61のそれぞれに至る導電路は、単純な1対1の接続であるとは限らず、外部接続端子51の総数の方が対仲介基板接続端子61の総数より少なくなることもあり得る。

【0038】

対仲介基板接続端子61は、仲介基板100の配線層102が含む対半導体チップ接続端子(不図示)のそれぞれに対接するように、半導体チップ40の再配線層44上に設けられており、その材質は例えばCu(銅)やはんだ、その高さは例えば50μm、その直径は例えば50μmから100μmである。その配置は、ピッチが既述のように例えば100μmから250μmであって例えばグリッド状に配置(エリア配置)されており、その総数は、例えば(100個程度から)500個程度である。接着樹脂62は、例えば、エポキシ樹脂(フィラーが配合されていない)である。

【0039】

次に、図1に示した半導体装置の製造方法について図2ないし図5を参照して説明する。図2、図4、図5は、図1に示した半導体装置の製造過程の一部を模式的に断面で示す工程図であり、図3は、図2に示した工程を概観する斜視図である。これらの図において図1中に示した構成要素と同一または同一相当のものには同一符号を付してある。

【0040】

図2から説明する。図2は、最初の段階として、半導体チップ10に半導体チップ20を積層、固定する工程を示している。この段階において、半導体チップ20(の機能面)上には、あらかじめ、半導体チップ10の裏面側の貫通電極15のそれぞれに対接できるようにチップ間接続端子91が形設されている。この端子91は、既述のように、半導体チップ20における半導体製造プロセスの一環として位置精度をもって形成されたものである。

【0041】

貫通電極15、25の形成方法については、すでに周知事項であり詳細を省略するが、概略として次のような工程が一般的である。すなわち、まず、エッチングによる半導体基板11、21への中途深さ穴の形成、その穴の内壁面上への絶縁膜の形成、その絶縁膜内での金属(Cu)層の成長による充填、そしてその後に金属層が露出するまで半導体基板11、21の裏面を研削する、という工程である。

【0042】

図2に示すように、あらかじめ、半導体チップ20の機能面上に、硬化前の接着樹脂92Aを全面塗布する。そして、図示の配置により、チップ間接続端子91が半導体チップ10の裏面の側の貫通電極15に電極ごとに対向してこの電極のそれぞれに電気導通するように、積層し、さらに、接着樹脂92Aを硬化させ一体化して、2つの半導体チップ10、20を有する積層体を得る。この電気的導通を確実にするため、例えば、ボンディング技術やフリップチップ接続技術と同様の、超音波による金属間接合部の生成技術を利用できる。

【0043】

この積層は、実際には、図3に示されるごとく、半導体チップ10、20に個片化される前のウエハの段階で行うことができる。図3は、既述のように図2に示した工程を概観する斜視図である。半導体チップ20に個片化される前のウエハ20Wに対して硬化前の接着樹脂92A(図3では不図示)が全面塗布され、そしてその上に、半導体チップ10に個片化される前のウエハ10Wが積層配置される。半導体チップ10、同20には、設計や製造の素性が同一のものを使用することが容易であり、このような関係から、ウエハ段階で積層すれば、数多くの半導体チップについて効率的に位置精度の確保された積層が可能である。半導体チップ10、20上の素子や電極、配線のレイアウト精度は高く、ウエハどうしで積層しても各部同時に位置合わせ精度が保てる。

【0044】

なお、すでに述べたようにチップ間接続端子91は、あらかじめ、半導体チップ10裏面の貫通電極15上に設けておくこともできる。この場合には、チップ間接続端子91を形成するため、半導体チップ10の裏面上に少しの半導体製造プロセスを適用することになる。半導体チップ10の裏面上には不図示の絶縁膜があることをすでに説明しているが、それを形成するプロセスと一連のプロセスとしてチップ間接続端子91の形成を行うことができる。このように半導体チップ10裏面の貫通電極15上にチップ間接続端子91をあらかじめ設ける場合は、これと対接するために、半導体チップ20の配線層23には対接用の端子(パッド)が設けられる。

【0045】

次に、図4を参照して説明する。図4は、3つの半導体チップ10、20、30を有する積層体に半導体チップ40を積層、固定する工程を示している。なお、3つの半導体チップ10、20、30を有する積層体を得るために、図2に示した工程により得られた2つの半導体チップ10、20を有する積層体に半導体チップ30を積層、一体化する工程については、図2における説明が援用できるので省略する。その場合の半導体チップ30の積層も、やはりウエハの段階で行うのが効率上、有用である。

【0046】

図4に示す段階において、半導体チップ40(の裏面)の貫通電極45上には、あらかじめ、半導体チップ30の裏面側の貫通電極35のそれぞれに対接できるようにチップ間接続端子71が形設されている。この端子71は、既述のように、半導体チップ40の裏面上における半導体製造プロセスの一環として位置精度をもって形成されたものである。

【0047】

そして、図4に示すように、あらかじめ、半導体チップ40の裏面上に、硬化前の接着樹脂72Aを全面塗布する。続いて、図示の配置により、チップ間接続端子71が半導体チップ30の裏面の側の貫通電極35に電極ごとに対向してこの電極のそれぞれに電気導通するように、積層し、さらに、接着樹脂72Aを硬化させ一体化して、4つの半導体チップ10、20、30、40を有する積層体を得る。この積層工程も、やはり、ウエハの段階で行うのが効率上、有用であり、上記電気的導通を確実にするため、例えば、ボンディング技術やフリップチップ接続技術と同様の、超音波による金属間接合部の生成技術を利用できる。

【0048】

また、図4に示す工程においても、チップ間接続端子71は、あらかじめ、半導体チップ30裏面の貫通電極35上に設けておくこともできる。この場合には、チップ間接続端子71を形成するため、半導体チップ30の裏面上に少しの半導体製造プロセスを適用することになる。半導体チップ30の裏面上には不図示の絶縁膜があることをすでに説明しているが、貫通電極35上へチップ間接続端子71を形成する場合は、これを、絶縁膜を形成するプロセスと一連のプロセスとして行うことができる。

【0049】

次に図5を参照して説明する。図5は、4つの半導体チップ10、20、30、40を有する積層体を仲介基板100上に取り付け固定する工程を示している。図4までに示した工程により、半導体チップ10、20、30、40を有する積層体(ウエハの積層体)を得たら、次に、このウエハをダイシングし個片化を行う。図5に示す工程は、この個片化後の積層体を用いる。なお、一方の仲介基板100については、製造効率化のため、個片化する前の多数の基板が並んで一体に形成されている基板を用いることができる。

【0050】

図5に示すように、半導体チップの積層体の半導体チップ40の再配線層44上には、あらかじめ、再配線層44と電気的導通を有して、配置の最小ピッチがチップ間接続端子71などのそれより長いピッチ長の対仲介基板接続端子61を形成する。より具体的に、対仲介基板接続端子61は、仲介基板100の配線層102が含む対半導体チップ接続端子102Tに端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置、形設される。この対仲介基板接続端子61の形設は、再配線層44の形成工程と同様の、半導体チップ40に対する付加的な工程として行うことができる。

【0051】

そして、図示の配置により、対仲介基板接続端子61が仲介基板100の配線層102が含む対半導体チップ接続端子102Tに端子ごとに対向してこの端子のそれぞれに電気導通するように、接続する。より具体的には、例えば、対半導体チップ接続端子102T上にあらかじめクリームはんだ(不図示)を塗布しておき、端子61と端子102Tとを対接した状態でこのクリームはんだをリフローする。

【0052】

なお、対仲介基板接続端子61を、図示するような凸状には再配線層44上に設けず、対半導体チップ接続端子102Tの方を、あらかじめ仲介基板100の配線層102上に凸状に設けるようにしてもよい。この場合には、凸状の対半導体チップ接続端子と対接するために、半導体チップ40の再配線層44には対接用の端子(パッド)が設けられる。

【0053】

以上のようにして半導体チップ10、20、30、40を有する積層体を仲介基板100上に取り付け、固定したら、次に、積層体と仲介基板100との間に、接着樹脂62とすべき液状の接着樹脂(フィラーが配合されていない)を例えば毛細管現象を利用して充填する。そして、全体を加熱して液状の接着樹脂を硬化させて固体化した接着樹脂62に変化させる。続いて、はんだボール51の貫通電極104上への取り付け、および仲介基板100を個片化することにより、図1に示したような半導体装置を製造することができる。

【0054】

以上説明のように、仲介基板100には、より粗いレイアウトルールを有するものを使用できる。粗いレイアウトルールによりコストダウンを図ることができ、かつ、半導体チップ10、20、30、40を有する積層体を取り付け固定する時の位置合わせも容易になるため電気的接続の信頼性も向上する。さらに、このように粗いレイアウトルールの場合、領域的な余裕から、その配線についてこれをインピーダンスのコントロールされた伝送線路として機能させる配線構造にすることが容易である。この点の付加価値増大も利点になる。

【0055】

以上の説明では、完成品として仲介基板100上に半導体チップ積層体が1つのみ取り付け固定された構成を説明したが、仲介基板上に2つ以上の積層体が横方向に並んで取り付け固定された構成もあり得る。2つの積層体が並んでいる場合のアプリケーションとしては、一方の積層体がメモリで、他方の積層体がCPUである構成が考えられる。

【0056】

次に、図1に示した半導体装置において好ましい、半導体チップ40が有する内部の回路構成について図6を参照して説明する。図6は、図1に示した半導体装置における半導体チップ40の素子形成層42によって構成される例示的回路(デマルチプレクサまたはマルチプレクサ)の機能図である。図6において、図1中に示した構成要素に対応する部分には同一符号を付してある。

【0057】

図6に示すように、半導体チップ40の素子形成層42には、その構成される素子により、例えばデマルチプレクサ4aが作り込まれている(デマルチプレクサ4aを構成するため実際には配線層43が含む配線も使用される)。そして、デマルチプレクサ4aの入力側への導電路は、対仲介基板接続端子61から、再配線層44を経て配線層43により構成される。一方、デマルチプレクサ4aの出力側は、16本の出力となって、それぞれ、配線層43、貫通電極45を経て、各半導体チップ30、20、10(実際にはさらに積層された多数の半導体チップ)に導通している。

【0058】

デマルチプレクサ4aの入力側は例えば16GHzの信号であり、その出力側は例えば1GHzの信号である。入力側のノード数がデマルチプレクサ4aにより出力側で16倍に増えるが、これらの信号を各半導体チップ30、20、10に供給するには、多数配置されている貫通電極45、35、25が利用できる。一方、デマルチプレクサ4aの入力側信号のノード数は少ないが、それに応じて少ない数の対仲介基板接続端子61で対応ができる。

【0059】

以上はデマルチプレクサ4aを例として説明したが、マルチプレクサの場合(図6で上側の16本の信号が入力信号で、下側のノードが出力信号の場合)も同様である。このように、この半導体装置の構成として、半導体チップ40の素子形成層42が有する回路としてデマルチプレクサ(シリアルパラレル変換回路)やマルチプレクサ(パラレルシリアル変換回路)を具有させることは構成上の理に適っており非常に有用である。

【0060】

次に、図7は、図1に示した半導体装置における半導体チップ40の素子形成層42によって構成される別の例示的回路(DC−DCコンバータまたは直流電圧レギュレータ)の機能図である。図7において、図1中に示した構成要素に対応する部分には同一符号を付してある。

【0061】

図7に示すように、半導体チップ40の素子形成層42には、その構成される素子により、例えばDC−DCコンバータ(または直流電圧レギュレータ、以下同)4bが作り込まれている(回路として実際には配線層43が含む配線も使用される)。そして、DC−DCコンバータの入力側への導電路は、対仲介基板接続端子61から、再配線層44を経て配線層43により構成される。一方、DC−DCコンバータ4bの出力側は、電圧の異なる例えば4本の出力となって、それぞれ、配線層43、貫通電極45を経て、各半導体チップ30、20、10(実際にはさらに積層された多数の半導体チップ)に導通している。

【0062】

このDC−DCコンバータ4bをその入出力のノード数でみると、入力側は1つのノードであり、出力側は4つのノードである。すなわち、DC−DCコンバータ4bによりノード数が4倍に増えるが、それらの出力電圧を各半導体チップ30、20、10に供給するには、多数配置されている貫通電極45、35、25を利用できる。一方、DC−DCコンバータ4bの入力側については、少ない数の対仲介基板接続端子61で対応ができる。このように、この半導体装置の構成として、半導体チップ40の素子形成層42が有する回路としてDC−DCコンバータ(直流電圧レギュレータ)4bを具有させることは構成上の理に適っており非常に有用である。

【0063】

次に、本発明の別の実施形態に係る半導体装置について図8を参照して説明する。図8は、別の実施形態に係る半導体装置の構成を模式的に示す断面図である。図8において、図1中に示した構成要素と同一のものには同一符号を付してある。その説明は特に加えるべき事項がない限り省略する。

【0064】

この実施形態の図1に示した実施形態との違いは、仲介基板100に隣り合う半導体チップ40Aとして、その機能面を図示上側に向けて配置している点である。この実施形態の場合のチップ間接続端子71や接着樹脂72については、チップ間接続端子91、接着樹脂92の場合の説明を参照することができる。そして、半導体チップ40Aは、再配線層44をその裏面側に設けている。すなわち、裏面側に再配線層44を形成するプロセスが施されている。これにより再配線層44が仲介基板100に対向する面に設けられる点で、図1に示した実施形態と同じになる。よって、再配線層44、対仲介基板接続端子61、接着樹脂62についてはすでに説明した通りである。

【0065】

次に、図8に示した半導体装置において好ましい、半導体チップ40Aが有する再配線層44の回路(導電路)構成について図9を参照して説明する。図9は、図8に示した半導体装置における半導体チップ40の再配線層44によって構成される例示的導電路構成を示す模式図である。図9において、図8中に示した構成要素に対応する部分には同一符号を付してある。

【0066】

図9に示すように、半導体チップ40の再配線層44では、その含まれる導電路により、電気的に分岐するパターンが形成されている。そして、分岐のもとの側は、対仲介基板接続端子61から接続されていて、一方、分岐先の側は例えば4本に分岐して、それぞれ、貫通電極45を経て、各半導体チップ40A(の機能面)、30、20、10(実際にはさらに積層された多数の半導体チップ)に導通している。

【0067】

すなわち、導電路の分岐により、その数は増えるが、それらを各半導体チップ40A(の機能面)、30、20、10に導通させるには、多数配置されている貫通電極45、35、25を利用できる。一方、分岐のもとの側については、少ない数の対仲介基板接続端子61で対応ができる。このように、この半導体装置の構成として、半導体チップ40Aの再配線層44が有する導電路として電気的な分岐路を具有させることは構成上の理に適っており非常に有用である。

【0068】

このような分岐路としては、電源パターンやグラウンドパターンを例示することができる。半導体チップ40A上の再配線層44により電源の導電路、グラウンドの導電路を分けることにより、各半導体チップ40A、30、20、10の電源供給路が共通に有するインピーダンスを減らすことができ、それらの半導体チップを動作安定化する上で好ましい。

【0069】

次に、本発明のさらに別の実施形態について図10を参照して説明する。図10は、本発明のさらに別の実施形態である半導体装置で使用可能な仲介基板の別例を模式的に示す断面図である。上記で説明した実施形態では、仲介基板としてシリコンの基材を有する基板を使用したものを説明したが、シリコンの基板に代えて、有機樹脂材料でできた多層配線板を利用することもできる。そこで、図10には、このような多層配線板のひとつの例を示している。このような多層配線板200を用いる場合も、図5に示した半導体チップ積層体の取り付け固定の工程においては、製造効率化のため、多層配線板200として個片化する前の多面付け基板を用いることができる。

【0070】

この多層配線板200は、図10に示すように、6層の配線層221〜226を有する、部品内蔵の多層配線板である。配線層数はこれに限られないが、以下では、この多層配線板200の構成を参考までに説明する。

【0071】

多層配線板200は、絶縁層211、同212、同213、同214、同215、配線層(配線パターン)221、同222、同223、同224、同225、同226(=合計6層)、層間接続体231、同232、同234、同235、スルーホール導電体233、受動素子部品241、はんだ251、はんだレジスト261、262を有する。

【0072】

受動素子部品241は、表面実装用のチップ部品であり、例えばチップコンデンサ、チップ抵抗である。その平面的な大きさは例えば0.6mm×0.3mmである。両端に端子を有し、その下側が配線層222による実装用ランドに対向位置している。受動素子部品241の端子と実装用ランドとははんだ251により電気的、機械的に接続されている。

【0073】

配線層221、226は、配線板としての両主面上の配線層であってランドを含んでいる。配線層221によるランドは、外部接続端子としてのランドであり、配線層226によるランドは、半導体チップの積層体との電気的接続を行うためのランドである。はんだが位置するランドの部分を除いて両主面上には、はんだ接続時に溶融したはんだをランド部分に留めかつその後は保護層として機能するはんだレジスト261、262が形成されている(厚さはそれぞれ例えば20μm程度)。ランド部分の表層には、耐腐食性の高いNi/Auのめっき層(不図示)を形成しておいてもよい。

【0074】

配線層222、223、224、225は、それぞれ、内層の配線層であり、順に、配線層221と配線層222の間に絶縁層211が、配線層222と配線層223の間に絶縁層212が、配線層223と配線層224との間に絶縁層213が、配線層224と配線層225との間に絶縁層214が、配線層225と配線層226との間に絶縁層215が、それぞれ位置しこれらの配線層221〜226を隔てている。各配線層221〜226は、例えばそれぞれ厚さ18μmの金属(銅)箔からなっている。

【0075】

各絶縁層211〜215は、絶縁層213を除き例えばそれぞれ厚さ100μm、絶縁層213のみ例えば厚さ300μmで、それぞれ例えばガラスエポキシ樹脂からなるリジッドな素材である。特に絶縁層213は、内蔵された受動素子部品241に相当する位置部分が開口部となっており、受動素子部品241を埋設するための空間を提供する。絶縁層212、214は、内蔵された受動素子部品241のための絶縁層213の上記開口部および絶縁層213のスルーホール導電体233内部の空間を埋めるように変形進入しており内部に空隙となる空間は存在しない。

【0076】

配線層221と配線層222とは、それらのパターンの面の間に挟設されかつ絶縁層211を貫通する層間接続体231により導通し得る。同様に、配線層222と配線層223とは、それらのパターンの面の間に挟設されかつ絶縁層212を貫通する層間接続体232により導通し得る。配線層223と配線層224とは、絶縁層213を貫通して設けられたスルーホール導電体233により導通し得る。配線層224と配線層225とは、それらのパターンの面の間に挟設されかつ絶縁層214を貫通する層間接続体234により導通し得る。配線層225と配線層226とは、それらのパターンの面の間に挟設されかつ絶縁層215を貫通する層間接続体235により導通し得る。

【0077】

層間接続体231、232、234、235は、それぞれ、導電性組成物のスクリーン印刷により形成される導電性バンプを由来とするものであり、その製造工程に依拠して軸方向(図1の図示で上下の積層方向)に径が変化している。その直径は、太い側で例えば200μmである。

【0078】

図10に示す多層配線板は一例であり、周知の構成の別の多層配線板を使用してもよい。特に、部品内蔵の配線板を使用することで、上記実施形態におけるシリコンの仲介基板100を使用する場合と同様に、半導体装置として、付加価値の増大を図ることができる。内蔵の部品としては、すでに述べたように、例えば、デカップリングコンデンサ(バイパスコンデンサ)やカップリングコンデンサとして機能させるコンデンサ素子、ダンピング抵抗、終端抵抗やプルアップまたはプルダウン抵抗として機能させる抵抗素子が挙げられる。

【0079】

なお、仲介基板200のような有機材料の基板を用いる場合には、半導体素子40、40Aとの間に設けられる接着樹脂62には、熱膨張率の違いを空間的に緩衝するため、フィラーを含有させた例えばエポキシ樹脂を用いるとよい。

【符号の説明】

【0080】

4a…デマルチプレクサ(またはマルチプレクサ)、4b…DC−DCコンバータ(または直流電圧レギュレータ)、10,20,30,40,40A…半導体チップ、10W,20W…ウエハ、11,21,31,41…半導体基板、12,22,32,42…素子形成層(半導体素子群)、13,23,33,43…配線層(配線形成層)、44…再配線層、15,25,35,45…貫通電極、51…はんだボール(外部接続端子)、61…対仲介基板接続端子、62…接着樹脂、71,81,91…チップ間接続端子、72,82,92…接着樹脂、72A…硬化前の接着樹脂、92A…硬化前の接着樹脂、100…仲介基板(シリコン製)、101…仲介基板基材、102…配線層、102T…対半導体チップ接続端子、103…素子形成層、104…貫通電極、200…仲介基板(有機材料製の多層配線板)、211,212,213,214,215…絶縁層、221,222,223,224,225,226…配線層(配線パターン)、231,232,234,235…層間接続体(導電性組成物印刷による導電性バンプ)、233…スルーホール導電体、241…受動素子部品、251…はんだ、261,262…はんだレジスト。

【特許請求の範囲】

【請求項1】

第1半導体素子群および第1配線層が集積形成された第1機能面と;該第1機能面と該第1機能面に対向する第1裏面との間に貫通形成された、配置の最小ピッチが第1のピッチ長である第1貫通電極群と;を有する第1の半導体チップと、

第2半導体素子群および第2配線層が集積形成された第2機能面と;前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第2機能面に配置された1,2チップ間接続端子群と;前記第2機能面と前記第2裏面との間に貫通形成された、配置の最小ピッチが第2のピッチ長である第2貫通電極群と;を有し、前記1,2チップ間接続端子群が前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、前記第1の半導体チップに対して積層配置された第2の半導体チップと、

第3半導体素子群および第3配線層が集積形成された第3機能面と;前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第3機能面上にまたは該第3機能面に対向する第3裏面上に配置された2,3チップ間接続端子群と;前記第3機能面と前記第3裏面との間に貫通形成された第3貫通電極群と;前記2,3チップ間接続端子群が設けられた面とは反対の側の面上に設けられた再配線層と;該再配線層が設けられた面上に該再配線層と電気的導通を有して形成された、配置の最小ピッチが前記第2のピッチ長より長い第3のピッチ長である対仲介基板接続端子群と;を有し、前記2,3チップ間接続端子群が前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、前記第2の半導体チップに対して積層配置された第3の半導体チップと、

第1の面と該第1の面に対向する第2の面とを有し;該第1の面上に、前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置された対半導体チップ接続端子群を有し;前記第2の面上に、前記対半導体チップ接続端子群に電気的に連なる外部接続端子群を有し;前記対半導体チップ接続端子群が前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気導通するように、前記第3の半導体チップに対して積層配置された仲介基板と

を具備することを特徴とする半導体装置。

【請求項2】

前記第3の半導体チップの前記2,3チップ間接続端子群が、該第3の半導体チップの前記第3裏面上に配置され、

前記仲介基板の前記外部接続端子群の一端子から、該仲介基板の対半導体チップ接続端子群の一端子および前記第3の半導体チップの前記対仲介基板接続端子群の一端子を経由して、該第3の半導体チップの前記再配線層に至る導電路が形成され、

前記導電路が前記第3半導体素子群で構成される回路につながり、該回路により電気的に分岐されて、前記第3の半導体チップの前記第3貫通電極群のうちの複数の電極のそれぞれに電気的に連なっていること

を特徴とする請求項1記載の半導体装置。

【請求項3】

前記第3の半導体チップの前記2,3チップ間接続端子群が、該第3の半導体チップの前記第3機能面上に配置され、

前記仲介基板の前記外部接続端子群の一端子から、該仲介基板の対半導体チップ接続端子群の一端子および前記第3の半導体チップの前記対仲介基板接続端子群の一端子を経由して該第3の半導体チップの前記再配線層に至り、さらに該再配線層により電気的に分岐され、該第3の半導体チップの前記第3貫通電極群のうちの複数の電極のそれぞれに導通する導電路が形成されていること

を特徴とする請求項1記載の半導体装置。

【請求項4】

前記第3の半導体チップの前記第3半導体素子群で構成される前記回路が、マルチプレクサまたはデマルチプレクサであることを特徴とする請求項2記載の半導体装置。

【請求項5】

前記第3の半導体チップの前記第3半導体素子群で構成される前記回路が、DC−DCコンバータまたは直流電圧レギュレータであることを特徴とする請求項2記載の半導体装置。

【請求項6】

前記導電路が、電源電位の導電路またはグラウンド電位の導電路であることを特徴とする請求項3記載の半導体装置。

【請求項7】

前記仲介基板が、前記対半導体チップ接続端子群に属する端子の総数より少ない総数の、前記外部接続端子群に属する端子を有することを特徴とする請求項2記載の半導体装置。

【請求項8】

前記仲介基板が、貫通電極群の形成された、無機材料の基材を有することを特徴とする請求項2記載の半導体装置。

【請求項9】

前記仲介基板の前記基材が、シリコンであることを特徴とする請求項8記載の半導体装置

【請求項10】

前記仲介基板が、有機材料基材の多層配線板であることを特徴とする請求項2記載の半導体装置。

【請求項11】

前記仲介基板が、抵抗素子またはコンデンサ素子を具有していることを特徴とする請求項2記載の半導体装置。

【請求項12】

第1半導体素子群および第1配線層が集積形成された第1機能面と;該第1機能面と該第1機能面に対向する第1裏面との間に貫通形成された、配置の最小ピッチが第1のピッチ長である第1貫通電極群と;を有する第1の半導体チップが複数形成された第1のウエハに対して、第2半導体素子群および第2配線層が集積形成された第2機能面と;前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第2機能面に配置された1,2チップ間接続端子群と;前記第2機能面と前記第2裏面との間に貫通形成された、配置の最小ピッチが第2のピッチ長である第2貫通電極群と;を有する第2の半導体チップが複数形成された第2のウエハを、前記1,2チップ間接続端子群が前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、積層する工程と、

前記第2のウエハに対して、第3半導体素子群および第3配線層が集積形成された第3機能面と;前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第3機能面上にまたは該第3機能面に対向する第3裏面上に配置された2,3チップ間接続端子群と;前記第3機能面と前記第3裏面との間に貫通形成された第3貫通電極群と;前記2,3チップ間接続端子群が設けられた面とは反対の側の面上に設けられた再配線層と;該再配線層が設けられた面上に該再配線層と電気的導通を有して形成された、配置の最小ピッチが前記第2のピッチ長より長い第3のピッチ長である対仲介基板接続端子群と;を有する第3の半導体チップが複数形成された第3のウエハを、前記2,3チップ間接続端子群が前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、積層する工程と、

前記第1、第2、第3のウエハを有する積層体を、前記第1、第2、第3の半導体チップをそれぞれ1つずつ有するように個片化し、積層化半導体チップを形成する工程と、

前記積層化半導体チップに対して、第1の面と該第1の面に対向する第2の面とを有し;該第1の面上に、前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置された対半導体チップ接続端子群を有し;前記第2の面上に、前記対半導体チップ接続端子群に電気的に連なる外部接続端子群を有する仲介基板を、前記対半導体チップ接続端子群が前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気導通するように、積層する工程と

を具備することを特徴とする半導体装置の製造方法。

【請求項1】

第1半導体素子群および第1配線層が集積形成された第1機能面と;該第1機能面と該第1機能面に対向する第1裏面との間に貫通形成された、配置の最小ピッチが第1のピッチ長である第1貫通電極群と;を有する第1の半導体チップと、

第2半導体素子群および第2配線層が集積形成された第2機能面と;前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第2機能面に配置された1,2チップ間接続端子群と;前記第2機能面と前記第2裏面との間に貫通形成された、配置の最小ピッチが第2のピッチ長である第2貫通電極群と;を有し、前記1,2チップ間接続端子群が前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、前記第1の半導体チップに対して積層配置された第2の半導体チップと、

第3半導体素子群および第3配線層が集積形成された第3機能面と;前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第3機能面上にまたは該第3機能面に対向する第3裏面上に配置された2,3チップ間接続端子群と;前記第3機能面と前記第3裏面との間に貫通形成された第3貫通電極群と;前記2,3チップ間接続端子群が設けられた面とは反対の側の面上に設けられた再配線層と;該再配線層が設けられた面上に該再配線層と電気的導通を有して形成された、配置の最小ピッチが前記第2のピッチ長より長い第3のピッチ長である対仲介基板接続端子群と;を有し、前記2,3チップ間接続端子群が前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、前記第2の半導体チップに対して積層配置された第3の半導体チップと、

第1の面と該第1の面に対向する第2の面とを有し;該第1の面上に、前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置された対半導体チップ接続端子群を有し;前記第2の面上に、前記対半導体チップ接続端子群に電気的に連なる外部接続端子群を有し;前記対半導体チップ接続端子群が前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気導通するように、前記第3の半導体チップに対して積層配置された仲介基板と

を具備することを特徴とする半導体装置。

【請求項2】

前記第3の半導体チップの前記2,3チップ間接続端子群が、該第3の半導体チップの前記第3裏面上に配置され、

前記仲介基板の前記外部接続端子群の一端子から、該仲介基板の対半導体チップ接続端子群の一端子および前記第3の半導体チップの前記対仲介基板接続端子群の一端子を経由して、該第3の半導体チップの前記再配線層に至る導電路が形成され、

前記導電路が前記第3半導体素子群で構成される回路につながり、該回路により電気的に分岐されて、前記第3の半導体チップの前記第3貫通電極群のうちの複数の電極のそれぞれに電気的に連なっていること

を特徴とする請求項1記載の半導体装置。

【請求項3】

前記第3の半導体チップの前記2,3チップ間接続端子群が、該第3の半導体チップの前記第3機能面上に配置され、

前記仲介基板の前記外部接続端子群の一端子から、該仲介基板の対半導体チップ接続端子群の一端子および前記第3の半導体チップの前記対仲介基板接続端子群の一端子を経由して該第3の半導体チップの前記再配線層に至り、さらに該再配線層により電気的に分岐され、該第3の半導体チップの前記第3貫通電極群のうちの複数の電極のそれぞれに導通する導電路が形成されていること

を特徴とする請求項1記載の半導体装置。

【請求項4】

前記第3の半導体チップの前記第3半導体素子群で構成される前記回路が、マルチプレクサまたはデマルチプレクサであることを特徴とする請求項2記載の半導体装置。

【請求項5】

前記第3の半導体チップの前記第3半導体素子群で構成される前記回路が、DC−DCコンバータまたは直流電圧レギュレータであることを特徴とする請求項2記載の半導体装置。

【請求項6】

前記導電路が、電源電位の導電路またはグラウンド電位の導電路であることを特徴とする請求項3記載の半導体装置。

【請求項7】

前記仲介基板が、前記対半導体チップ接続端子群に属する端子の総数より少ない総数の、前記外部接続端子群に属する端子を有することを特徴とする請求項2記載の半導体装置。

【請求項8】

前記仲介基板が、貫通電極群の形成された、無機材料の基材を有することを特徴とする請求項2記載の半導体装置。

【請求項9】

前記仲介基板の前記基材が、シリコンであることを特徴とする請求項8記載の半導体装置

【請求項10】

前記仲介基板が、有機材料基材の多層配線板であることを特徴とする請求項2記載の半導体装置。

【請求項11】

前記仲介基板が、抵抗素子またはコンデンサ素子を具有していることを特徴とする請求項2記載の半導体装置。

【請求項12】

第1半導体素子群および第1配線層が集積形成された第1機能面と;該第1機能面と該第1機能面に対向する第1裏面との間に貫通形成された、配置の最小ピッチが第1のピッチ長である第1貫通電極群と;を有する第1の半導体チップが複数形成された第1のウエハに対して、第2半導体素子群および第2配線層が集積形成された第2機能面と;前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第2機能面に配置された1,2チップ間接続端子群と;前記第2機能面と前記第2裏面との間に貫通形成された、配置の最小ピッチが第2のピッチ長である第2貫通電極群と;を有する第2の半導体チップが複数形成された第2のウエハを、前記1,2チップ間接続端子群が前記第1の半導体チップの前記第1裏面の側の前記第1貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、積層する工程と、

前記第2のウエハに対して、第3半導体素子群および第3配線層が集積形成された第3機能面と;前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気的導通ができるように前記第3機能面上にまたは該第3機能面に対向する第3裏面上に配置された2,3チップ間接続端子群と;前記第3機能面と前記第3裏面との間に貫通形成された第3貫通電極群と;前記2,3チップ間接続端子群が設けられた面とは反対の側の面上に設けられた再配線層と;該再配線層が設けられた面上に該再配線層と電気的導通を有して形成された、配置の最小ピッチが前記第2のピッチ長より長い第3のピッチ長である対仲介基板接続端子群と;を有する第3の半導体チップが複数形成された第3のウエハを、前記2,3チップ間接続端子群が前記第2の半導体チップの前記第2裏面の側の前記第2貫通電極群に電極ごとに対向して該電極のそれぞれに電気導通するように、積層する工程と、

前記第1、第2、第3のウエハを有する積層体を、前記第1、第2、第3の半導体チップをそれぞれ1つずつ有するように個片化し、積層化半導体チップを形成する工程と、

前記積層化半導体チップに対して、第1の面と該第1の面に対向する第2の面とを有し;該第1の面上に、前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気的導通ができるように配置された対半導体チップ接続端子群を有し;前記第2の面上に、前記対半導体チップ接続端子群に電気的に連なる外部接続端子群を有する仲介基板を、前記対半導体チップ接続端子群が前記第3の半導体チップの前記対仲介基板接続端子群に端子ごとに対向して該端子のそれぞれに電気導通するように、積層する工程と

を具備することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−204653(P2012−204653A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2011−68505(P2011−68505)

【出願日】平成23年3月25日(2011.3.25)

【国等の委託研究の成果に係る記載事項】(出願人による申告)(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構「立体構造新機能集積回路(ドリームチップ)技術開発/多機能高密度三次元集積化技術」委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000002897)大日本印刷株式会社 (14,506)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【出願人】(000004237)日本電気株式会社 (19,353)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【出願人】(000000158)イビデン株式会社 (856)

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成23年3月25日(2011.3.25)

【国等の委託研究の成果に係る記載事項】(出願人による申告)(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構「立体構造新機能集積回路(ドリームチップ)技術開発/多機能高密度三次元集積化技術」委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000002897)大日本印刷株式会社 (14,506)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【出願人】(000004237)日本電気株式会社 (19,353)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【出願人】(000000158)イビデン株式会社 (856)

【出願人】(301021533)独立行政法人産業技術総合研究所 (6,529)

[ Back to top ]