半導体装置、及び、半導体装置の製造方法

【課題】 プローバーテストの製品への影響をさらに軽減して、より一層信頼性の高い半導体装置を提供する。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

【解決手段】 半導体装置100を、半導体基板10aと、半導体基板10aの一方の面上に形成された絶縁膜10bと、縦孔配線部30と、金属膜11と、導電性保護膜12とを備える構成とする。金属膜11は、絶縁膜10b内に形成され、縦孔配線部30と電気的に接続される。そして、導電性保護膜12は、絶縁膜10b内において金属膜11に接して形成され、かつ、金属膜11の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、半導体装置、及び、その製造方法に関し、より詳細には、半導体装置の製造途中で半導体部材の電気的性能評価を行う半導体装置、及び、その製造方法に関する。

【背景技術】

【0002】

従来、例えば、半導体装置の小型化及び高機能化を図るために、複数の半導体部材(配線基板)を積層して半導体装置を構成する。このような半導体装置では、各半導体部材間の電気的接続を得るため、各半導体部材のシリコン基板に、その厚さ方向に沿って延在した縦孔状の配線部(以下、TSV(Through Silicon Via)ともいう)を形成する。具体的には、まず、シリコン基板の厚さ方向に沿って延在した縦孔を形成し、次いで、その縦孔を画成するシリコン基板の壁面上に例えばCu等の金属材料からなる電極膜を形成する。

【0003】

上述のようなTSVを有する半導体装置では、一般に、その製造途中において、TSVを形成する前に、半導体部材の電気的性能評価(以下、プローバーテストという)を行う。プローバーテストでは、通常、電極配線の一部(パッド部)を露出させ、そのパッド部にプローブを接触させて、半導体部材の電気的性能の評価を行う。

【0004】

それゆえ、プローバーテストを行った際には、電極配線のパッド部にプローブの痕跡(以下、プローブ痕という)が残る。この場合、例えば、プローバーテスト後に行うTSVの形成工程で用いる薬液(例えばメッキ液等)が、プローブ痕に浸透して、パッド部にダメージを与えることがある。また、パッド部を露出するための開口部が設けられるので、パッド部において十分な強度が得られず、例えば、TSVの形成工程時にパッド部が変形したり、パッド部が剥離したりする場合もある。すなわち、プローバーテストの影響により、半導体装置の例えば歩留まり、信頼性等が低下することがある。

【0005】

そこで、従来、上述したプローバーテストの影響を軽減するための様々な技術が提案されている(例えば、特許文献1参照)。図23(a)及び(b)に、特許文献1で提案されている配線基板の概略構成断面図を示す。なお、図23(a)に示す例は、特許文献1で提案されている配線基板の第1の構成例であり、図23(b)に示す例は、特許文献1で提案されている配線基板の第2の構成例である。

【0006】

特許文献1の第1の構成例では、図23(a)に示すように、配線基板400は、基材401、及び、基材401の一方の面上に形成された第1絶縁部402を含む基体410を備える。そして、基体410内部には、その厚さ方向に延在した貫通孔403が形成される。また、配線基板400は、貫通孔403の一方に開口部を塞ぐように、第1絶縁部402の内部に形成された第1導電層411と、第1絶縁部402の表面に形成された第2導電層412とを備える。さらに、配線基板400は、第1導電層411と第2導電層412とを繋ぐ島状の中間層413を備える。

【0007】

また、配線基板400は、第2導電層412上に形成された第2絶縁部414を備える。そして、貫通孔403の直上に位置する第2絶縁部414の領域に、プローブの接触領域となる開口部414aを形成する。上述のように、特許文献1の第1の構成例では、プローブの接触領域となる第2絶縁部414の開口部414aの導電部を多層構造にし、これにより、上述したプローブ痕の影響を低減する。

【0008】

一方、特許文献1の第2の構成例では、図23(b)に示すように、配線基板420は、基材421、及び、基材421の一方の面上に形成された第1絶縁部422を含む基体430を備える。そして、基体430内部には、その厚さ方向に延在した貫通孔423が形成される。さらに、配線基板420は、貫通孔423の一方に開口部を塞ぐように、第1絶縁部422上に形成された導電部431と、導電部431の表面に形成された第2絶縁部432とを備える。

【0009】

そして、特許文献1の第2の構成例では、配線基板420の面内において、貫通孔423の開口領域と重ならない第2絶縁部432の領域に開口部432aが形成される。すなわち、特許文献1の第2の構成例では、配線基板420の面内において、プローブの接触領域となる導電部431の領域を、貫通孔423の開口領域と重ならない領域に配置することにより上述したプローバーテストの影響を低減する。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2007−288150号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上述のように、従来、TSVを有する半導体装置においては、その製造途中で行うプローバーテストの製品への影響を軽減するための技術が種々提案されている。しかしながら、このようなTSVを有する半導体装置では、上述したプローバーテストの製品への影響をさらに軽減して、例えば半導体装置の歩留まり、信頼性等をより一層向上させる技術の開発が望まれている。

【0012】

本開示は、上記要望に応えるためになされたものであり、本開示の目的は、プローバーテストの製品への影響をさらに軽減して、例えば歩留まり、信頼性等をより一層向上させることのできる半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本開示の半導体装置は、基材部と、縦孔配線部と、金属膜と、導電性保護膜とを備える構成とし、各部の構成を次のようにする。基材部は、半導体基板、及び、半導体基板の一方の面上に形成された絶縁膜を有し、内部に半導体基板の厚さ方向に沿って縦孔が形成される。縦孔配線部は、縦孔を画成する基材部の側壁上に形成された縦孔電極を有する。金属膜は、絶縁膜内に形成され、縦孔配線部と電気的に接続される。導電性保護膜は、絶縁膜内において金属膜に接して形成され、かつ、金属膜の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

【0014】

また、本開示の半導体装置の製造方法は、次の手順で行う。まず、半導体基板、及び、半導体基板の一方の面上に形成された絶縁膜を有する基材部の絶縁膜内に金属膜を形成する。次いで、絶縁膜内で、かつ、金属膜の膜面内の所定領域に、金属膜に接して導電性保護膜を形成する。また、絶縁膜の半導体基板の側とは反対側の表面に露出した金属膜及び導電性保護膜の一方にプローブを接触させてプローバーテストを行う。そして、プローバーテスト後に、半導体基板の厚さ方向に沿って、基材部に縦孔を形成する。

【発明の効果】

【0015】

上述のように、本開示の半導体装置及びその製造方法では、プローバーテスト時のプローブの接触領域を含む所定の領域に、金属膜に接して導電性保護膜を形成する。それゆえ、本開示によれば、上述したプローバーテストの製品への影響をさらに軽減することができ、半導体装置の例えば歩留まり、信頼性等をより一層向上させることができる。

【図面の簡単な説明】

【0016】

【図1】本開示の第1の実施形態に係る半導体装置の概略構成断面図である。

【図2】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図3】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図4】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図5】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図6】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図7】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図8】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図9】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図10】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図11】本開示の第2の実施形態に係る半導体装置の概略構成断面図である。

【図12】第2の実施形態に係る半導体装置の製造工程を説明するための図である。

【図13】第2の実施形態に係る半導体装置の製造工程を説明するための図である。

【図14】第2の実施形態に係る半導体装置の製造工程を説明するための図である。

【図15】第2の実施形態に係る半導体装置の製造工程を説明するための図である。

【図16】変形例1(変形例1−1)の半導体装置の概略構成断面図である。

【図17】変形例1(変形例1−2)の半導体装置の概略構成断面図である。

【図18】変形例2の半導体装置の製造手法を説明するための図である。

【図19】変形例2の半導体装置の製造手法を説明するための図である。

【図20】変形例3の半導体装置の概略構成断面図である。

【図21】変形例4の半導体装置の概略構成図である。

【図22】本開示に係る半導体装置を適用したカメラの概略構成図である。

【図23】TSVを有する従来の配線基板の概略構成断面図である。

【発明を実施するための形態】

【0017】

以下に、本開示の実施形態に係る半導体装置、及び、その製造手法の例を、図面を参照しながら下記の順で説明する。ただし、本開示は下記の例に限定されない。

1.第1の実施形態

2.第2の実施形態

3.各種変形例及び応用例

【0018】

<1.第1の実施形態>

[半導体装置の全体構成]

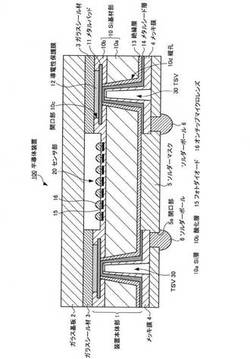

図1に、第1の実施形態に係る半導体装置の概略構成断面図を示す。なお、本実施形態では、半導体装置として、固体撮像素子(イメージセンサ)を例に挙げ説明する。また、図1には、説明を簡略化するために、センサ部及びTSV付近の構成のみを示す。

【0019】

半導体装置100は、装置本体部1と、ガラス基板2と、ガラスシール材3と、メッキ膜4と、ソルダーマスク5と、ソルダーボール6とを備える。装置本体部1の構成については、後で詳述する。

【0020】

ガラス基板2は、装置本体部1の一方の面(図1の例では上面)上に、ガラスシール材3を介して設けられる。なお、ガラスシール材3は、装置本体部1とガラス基板2とを貼り合わせるためのシール部材である。

【0021】

メッキ膜4は、装置本体部1の他方の面(図1の例では下面)上の一部に設けられる。具体的には、装置本体部1の後述するTSV30(縦孔配線部)を構成するメタルシード層14を覆うように設けられる。なお、メッキ膜4は、TSV30を構成するメタルシード層14をエッチングしてパターニングする際のマスクとしても利用される。

【0022】

ソルダーマスク5は、装置本体部1の下面、及び、メッキ膜4を覆うように設けられる。また、ソルダーマスク5には、メッキ膜4を露出するための開口部5aが設けられ、その開口部5aに、ソルダーボール6が設けられる。これにより、ソルダーボール6は、メッキ膜4を介してTSV30と電気的に接続される。なお、ソルダーボール6は、TSV30を介して出力された信号を外部の配線に出力するための接続端子である。また、ソルダーマスク5は、外部の配線をソルダーボール6に半田付けして接続する際に、半田が不要な部分に付着しないようにするためのマスクとして作用する。

【0023】

[装置本体部の構成]

装置本体部1は、Si基材部10(基材部)と、メタルパッド11(金属膜)と、導電性保護膜12と、絶縁層13と、メタルシード層14(縦孔電極)とを備える。また、装置本体部1は、外部から受光した光を電荷信号に変換する複数のフォトダイオード15と、該複数のフォトダイオード15のそれぞれ直上に設けられ、対応するフォトダイオード15に光をそれぞれ集光する複数のオンチップマイクロレンズ16とを備える。

【0024】

Si基材部10は、例えばシリコン基板等で構成されたSi層10a(半導体基板)と、該Si層10aの一方の表面(図1の例では上面)に形成された酸化層10b(絶縁膜)とを有する。なお、酸化層10bは、SiO2膜で構成され、酸化層10bには、メタルパッド11を露出させる開口部10cが設けられる。また、Si基材部10の内部には、その厚さ方向に沿って延在した縦孔10dが形成される。なお、縦孔10dは、Si層10aの他方の表面(図1の例では下面)からメタルパッド11の下面まで延在して形成される。

【0025】

また、本実施形態では、Si基材部10の酸化層10bの表面に、複数のオンチップマイクロレンズ16を配列して設け、酸化層10b内に複数のオンチップマイクロレンズ16に対応する複数のフォトダイオード15をそれぞれ形成する。これにより、被写体からの光を検出するセンサ部20が構成される。なお、図1には示さないが、センサ部20は、例えば、カラーフィルタ、各種トランジスタ、フローティングディフュージョンなども備える。

【0026】

メタルパッド11は、酸化層10b内に設けられる。この際、Si基材部10の縦孔10dのガラス基板2側の開口を塞ぐように、メタルパッド11が設けられる。なお、メタルパッド11は、例えば、Al、Cu、W、Ni、Ta等の導電性材料で形成することができる。また、メタルパッド11の厚さは、例えば、約1μm以下程度に設定することができる。

【0027】

メタルパッド11は、例えば、センサ部20から出力される信号を外部に出力するための出力電極、センサ部20に電圧を印加するための入力電極、グランド電極等の電極配線として用いられる。より具体的には、メタルパッド11は、例えば、センサ部20内に設けられた画素(不図示)を構成する選択トランジスタ(不図示)に接続される信号線の端部(BEOL:Back End Of the Line)として用いられる。

【0028】

導電性保護膜12は、酸化層10bの開口部10cに露出したメタルパッド11上(第1の領域)に形成される。なお、本実施形態では、導電性保護膜12を、半導体装置100の製造途中でプローバーテストを行う際にプローブを接触させる領域に設ける。すなわち、本実施形態では、導電性保護膜12をプローブパッドとして用いる。それゆえ、本実施形態では、プローバーテスト時にメタルパッド11を保護するため、導電性保護膜12を厚膜の金属膜で構成する。なお、導電性保護膜12の厚さは、例えば、プローブの接触圧等の条件を考慮して適宜設定されるが、できる限り厚くすることが好ましい。例えば、数μm〜数十μmの範囲で、導電性保護膜12の厚さを設定することができる。

【0029】

また、導電性保護膜12の形成材料としては、厚膜の金属膜を形成可能な導電性材料であれば、任意の材料を用いることができる。例えば、Ni、Cu、Au、Ag等の金属材料で導電性保護膜12を形成することができる。なお、本実施形態では、導電性保護膜12を一つの金属膜で構成する例を説明するが、本開示はこれに限定されず、導電性保護膜12の構成を複数の金属膜を積層した多層構造にしてもよい。

【0030】

また、本実施形態では、Si基材部10の縦孔10dを画成するSi基材部10の側壁上に、絶縁層13(SiO2層)及びメタルシード層14がこの順で積層される。なお、この際、メタルシード層14とメタルパッド11の下面とが直接接するように、絶縁層13及びメタルシード層14を形成する。本実施形態では、このように、Si基材部10の縦孔10dを画成するSi基材部10の側壁上に、絶縁層13及びメタルシード層14を設けることによりTSV30を構成する。

【0031】

TSV30は、センサ部20からメタルパッド11を介して出力される信号を、メタルシード層14、メッキ膜4及びソルダーボール6を介して、外部の配線に出力する。すなわち、本実施形態の半導体装置100では、センサ部20で検出した信号を、装置本体部1のソルダーマスク5の側から取り出す。

【0032】

[半導体装置の製造手法]

次に、本実施形態の半導体装置100の作製手法の一例を、図2〜10を参照しながら説明する。なお、図2〜10は、各工程で作製される半導体部材の概略断面図である。また、ここでは、説明を簡略化するため、装置本体部1のTSV30付近の構成の作製工程について説明する。それ以外の構成部は、例えば従来の固体撮像素子の作製手法と同様にして作製することができる。

【0033】

本実施形態では、まず、図2に示すように、Si基材部10の酸化層10b内に、メタルパッド11を形成する。なお、このメタルパッド11は、例えば従来の固体撮像素子におけるメタルパッドの作製手法と同様にして作製することができる。

【0034】

例えば、まず、Si層10a上に酸化膜(SiO2膜)を、例えばプラズマCVD(Chemical Vapor Deposition)法等の手法を用いて形成する。次いで、その酸化膜上にメタルパッド11の形成材料からなる金属膜を例えばスパッタリング法等の手法を用いて形成する。その後、金属膜をパターニングしてメタルパッド11を形成する。なお、この際、メタルパッド11上に形成する酸化層10bの後述の開口部10cのプロセスマージンを考慮して、特性上必要とされるサイズより少し大きなサイズのメタルパッド11を形成する。そして、メタルパッド11上に、例えばプラズマCVD法等の手法を用いて酸化膜を形成する。本実施形態では、このようにしてメタルパッド11を酸化層10b内に形成することができる。

【0035】

次いで、メタルパッド11上の酸化層10bの一部の領域、具体的には、導電性保護膜12の形成領域(プローブの接触領域を含む領域)をエッチングして除去する。これにより、図3に示すように、酸化層10bの導電性保護膜12の形成領域に、開口部10cが形成され、メタルパッド11が開口部10cに露出する。なお、本実施形態では、上述のように、開口部10cのプロセスマージンを考慮して、特性上必要とされるサイズより少し大きなサイズのメタルパッド11を形成する。それゆえ、開口部10cの開口面積はメタルパッド11の面積より小さくなり、メタルパッド11の外周端部付近の領域は、酸化層10bで被覆された状態になる。

【0036】

次いで、例えば、無電解メッキ法、スクリーン印刷法、スプレーコート法、スタッドバンプ形成法等の手法を用いて、図4に示すように、酸化層10bの開口部10cに露出したメタルパッド11上に、導電性保護膜12を形成する。なお、この際、本実施形態では、導電性保護膜12の表面と酸化層10bの表面とが面一となるように、導電性保護膜12を形成する。

【0037】

より具体的に説明すると、例えば、導電性保護膜12の形成手法としてスクリーン印刷法を用いた場合には、まず、導電性ペーストの充填用の孔が形成されたスクリーンを開口部10c上に配置する。次いで、導電性ペーストをスクリーン上に載せる。次いで、スキージを用いて導電性ペーストをスクリーン上で引き延ばす。これにより、スクリーンからスクリーンの孔を介して開口部10cに導電性のペーストが充填され、導電性保護膜12が形成される。

【0038】

また、例えば、導電性保護膜12の形成手法としてスプレーコート法を用いた場合には、ノズルから開口部10cに、導電性ペーストを微量のレートで吐出する。これにより、開口部10cに導電性ペーストが充填され、導電性保護膜12が形成される。

【0039】

次いで、導電性保護膜12が形成された半導体部材に対してプローバーテストを行う。具体的には、図5に示すように、プローブ50を導電性保護膜12に接触させて、半導体部材の電気的性能を評価する。なお、この際、導電性保護膜12にプローブ痕が発生するが、その下部に形成されたメタルパッド11は導電性保護膜12により保護されるので、メタルパッド11にはダメージは生じない。

【0040】

上述したプローバーテストが終了した後、図6に示すように、Si基材部10の酸化層10b、及び、導電性保護膜12上にガラスシール材3を形成する。なお、図6には示さないが、この工程では、センサ部20上にもガラスシール材3が形成される。

【0041】

次いで、図7に示すように、ガラスシール材3上にガラス基板2を載置し、ガラス基板2と、Si基材部10とをガラスシール材3を介して貼り合わせる。なお、本実施形態では、図7には示さないが、この工程において、Si層10aの酸化層10bの側とは反対側の表面(図7では下面)を研削(BGR:Back Grind)して、Si基材部10の厚さを薄くする。

【0042】

次いで、図8に示すように、ドライエッチング法により、Si層10aの下面の所定領域をエッチングして、メタルパッド11の下部(Si層10a側)に縦孔10dを形成する。この際、Si層10aの下面からメタルパッド11の下面まで延在する縦孔10dを形成し、縦孔10dの開口部にメタルパッド11の下面の一部を露出させる。なお、酸化層10bのエッチングレートとメタルパッド11のエッチングレートとの比(選択比)は高いので、メタルパッド11の下面でエッチング処理を停止させることは容易である。

【0043】

次いで、図9に示すように、Si層10aの下面上、縦孔10dを画成するSi基材部10の側壁上、及び、縦孔10dに露出したメタルパッド11の下面上に、例えばプラズマCVD法等の手法により、絶縁層13(SiO2層)を形成する。

【0044】

次いで、メタルパッド11の下面上に形成された絶縁層13の一部を除去して、縦孔10dにメタルパッド11の一部を露出させる。その後、図10に示すように、絶縁層13上、及び、露出したメタルパッド11の下面上に、例えばスパッタリング法等の手法により、メタルシード層14を形成する。これにより、メタルパッド11とメタルシード層14とが電気的に接続される。

【0045】

その後、従来の固体撮像素子の作製手法と同様にして、メッキ膜4、ソルダーマスク5、及び、ソルダーボール6を形成する。本実施形態では、このようにして、半導体装置100を作製する。

【0046】

上述のように、本実施形態の半導体装置100の製造手法では、メタルパッド11上に厚膜の導電性保護膜12を設け、その導電性保護膜12をプローブパッドとして用いる。それゆえ、本実施形態では、プローバーテスト時に発生するプローブ痕による、メタルパッド11のダメージを軽減することができる。すなわち、TSV30の形成工程で用いる薬液(例えばメッキ液等)のプローブ痕への浸透により、メタルパッド11がダメージを受けることを防止することができる。

【0047】

さらに、本実施形態は、例えば図23(a)及び(b)で説明した特許文献1で提案されている技術に対して、次のような利点が得られる。

【0048】

図23(a)及び(b)で説明した従来の配線基板では、プローブを接触させる第2導電層412又は導電部431の下部に絶縁膜(酸化膜)が設けられるので、プローバーテスト時のプローブの接触により、絶縁膜にダメージが発生する可能性がある。このように、絶縁膜にダメージが生じた場合にも、製品の例えば歩留まり、信頼性等が低下する。それに対して、本実施形態の半導体装置100では、メタルパッド11上に直接、導電性保護膜12を設けているので、プローブ50を導電性保護膜12に接触させた際に、Si基材部10の酸化層10bにダメージを与えない。

【0049】

また、上記特許文献1で提案されている第1の構成例(図23(a)参照)では、第1導電層411のプローブが接触する領域には、島状の中間層413が第1導電層411に接して設けられている。それに対して、本実施形態の半導体装置100では、プローブの接触領域を含む領域全面に渡って導電性保護膜12がメタルパッド11に接して設けられる。

【0050】

すなわち、本実施形態では、プローブの接触領域を含む領域において、メタルパッド11が導電性保護膜12に裏打ちされた構成であり、メタルパッド11及び導電性保護膜12間の接触面積は、特許文献1の第1の構成例のそれに比べて大きくなる。それゆえ、本実施形態では、上記特許文献1の第1の構成例に比べてメタルパッド11の強度を増大させることができる。この場合、導電性保護膜12を形成した後の各種工程(TSV30の形成工程も含む)において、メタルパッド11の変形や剥離を抑制することができる。

【0051】

以上のことから、本実施形態では、プローバーテストの影響をさらに軽減することができ、半導体装置100の例えば歩留まり、信頼性等をより一層向上させることができる。

【0052】

<2.第2の実施形態>

上記第1の実施形態では、メタルパッド11(メタル配線)上に、厚膜の導電性保護膜12(金属膜)を形成する例を説明したが、本開示はこれに限定されない。例えば、メタル配線を複数のメタル層からなる多層膜で構成し、その多層膜の一方の最表面側に位置するメタル層を導電性保護膜として用いてもよい。第2の実施形態では、その一例を説明する。

【0053】

[半導体装置の構成]

図11に、第2の実施形態に係る半導体装置の概略構成断面図を示す。なお、本実施形態では、上記第1の実施形態と同様に、半導体装置として、固体撮像素子(イメージセンサ)を例に挙げ説明する。また、図11には、説明を簡略化するため、本実施形態の半導体装置のTSV付近の構成のみを示す。さらに、図11に示す本実施形態の半導体装置200において、図1に示す第1の実施形態の半導体装置100と同様の構成には、同じ符号を付して示す。

【0054】

本実施形態の半導体装置200は、装置本体部201と、ガラス基板2と、ガラスシール材3とを備える。なお、図11には示さないが、半導体装置200は、上記第1の実施形態と同様に、メッキ膜、ソルダーマスク、及び、ソルダーボールを備える。また、本実施形態の半導体装置200におけるガラス基板2、及び、ガラスシール材3は、上記第1の実施形態のそれらと同様の構成である。すなわち、本実施形態において、装置本体部201以外の構成は、上記第1の実施形態の対応する構成と同様であるので、ここでは、装置本体部201の構成についてのみ説明する。

【0055】

[装置本体部の全体構成]

装置本体部201は、Si基材部10(基材部)と、メタルパッド11(金属膜)と、導電性保護膜202と、絶縁層13と、メタルシード層14(縦孔電極)とを備える。また、図11には示さないが、装置本体部201は、第1の実施形態と同様に、フォトダイオード及びオンチップマイクロレンズを含むセンサ部を備える。

【0056】

本実施形態の半導体装置200では、図11に示すように、TSV30(縦孔配線部)の上部(ガラス基板2側)に、メタルパッド11を形成し、さらに、メタルパッド11上に薄膜の導電性保護膜202を積層する。すなわち、本実施形態では、メタル配線をメタルパッド11及び導電性保護膜202の2層構造とする。

【0057】

そして、本実施形態では、Si基材部10の酸化層10b(絶縁膜)に開口部203を設け、導電性保護膜202をその開口部203に露出させる。本実施形態では、この開口部203に露出した導電性保護膜202にプローブを接触させてプローバーテストを行う。

【0058】

なお、導電性保護膜202は、メタルパッド11の形成工程に続いて形成されるので、メタルパッド11と同様の形成手法(例えばスパッタリン法)で形成される。それゆえ、第1の実施形態のように、厚膜(数十μm程度)の導電性保護膜202を形成することが難しい。そこで、本実施形態では、導電性保護膜202にプローブを接触させた際に、メタルパッド11にダメージが生じないようにするために、比較的硬度の高い導電性材料で導電性保護膜202を形成する。例えば、W、Ti、Ta等の材料で導電性保護膜202を形成することができる。

【0059】

また、図11に示す例では、導電性保護膜202を一層で構成する例を説明するが、本開示はこれに限定されない。例えば、導電性保護膜202を多層構造としてもよい。より具体的には、導電性保護膜202を、例えば、TiN膜/Ti膜、TaN膜/Ta膜等の積層膜で構成することができる。

【0060】

本実施形態において、上述のようにメタル配線を多層構造にしたこと以外の構成は、上記第1の実施形態の対応する構成と同様である。

【0061】

[半導体装置の製造手法]

次に、本実施形態の半導体装置200の作製手法の一例を、図12〜15を参照しながら説明する。なお、本実施形態の半導体装置200の作製手法では、プローバーテストまでの工程が上記第1の実施形態の半導体装置100のそれと異なるので、図12〜15には、プローバーテストまでの各工程で作製される半導体部材の概略断面図を示す。また、ここでは、説明を簡略化するため、装置本体部201のTSV30付近の構成の作製工程について説明する。それ以外の構成部は、例えば従来の固体撮像素子の作製手法と同様にして作製することができる。

【0062】

本実施形態では、まず、Si層10a上に、例えばプラズマCVD法等の手法を用いて、酸化膜204を形成する。次いで、図12に示すように、その酸化膜204上にメタルパッド11及び導電性保護膜202をこの順で形成する。

【0063】

なお、メタルパッド11及び導電性保護膜202の形成手法は任意であるが、例えば、次のようにしてメタルパッド11及び導電性保護膜202をすることができる。まず、メタルパッド11の形成材料からなる第1の金属膜、及び、導電性保護膜202の形成材料からなる第2の金属膜を、例えばスパッタリング法等の手法を用いて酸化膜204上に形成する。次いで、第1の金属膜及び第2の金属膜からなる積層膜をパターニングしてメタルパッド11及び導電性保護膜202を形成する。

【0064】

ただし、上記メタルパッド11及び導電性保護膜202の形成工程では、導電性保護膜202上に形成する後述の開口部203のプロセスマージンを考慮して、特性上必要とされるサイズより少し大きなサイズのメタルパッド11及び導電性保護膜202を形成する。

【0065】

次いで、図13に示すように、導電性保護膜202上に、例えばプラズマCVD法等の手法を用いて、酸化膜を形成してSi基材部10の酸化層10bを作製する。

【0066】

次いで、導電性保護膜202上の酸化層10bの一部の領域、具体的には、プローブの接触領域を含む領域をエッチングして除去する。これにより、図14に示すように、酸化層10bのプローブの接触領域を含む領域に開口部203が形成され、その開口部203に導電性保護膜202が露出する。なお、本実施形態では、上述のように、開口部203のプロセスマージンを考慮して、特性上必要とされるサイズより少し大きなサイズの導電性保護膜202を形成する。それゆえ、開口部203の開口面積は導電性保護膜202の面積より小さくなり、導電性保護膜202の外周端部付近の領域は、酸化層10bで被覆された状態になる。

【0067】

次いで、上記工程で作製された半導体部材に対してプローバーテストを行う。具体的には、図15に示すように、プローブ50を、導電性保護膜202を介してメタルパッド11に接触させて半導体部材の電気的性能を評価する。なお、この際、メタルパッド11は硬度の高い導電性保護膜202により保護されているので、メタルパッド11へのダメージを軽減することができる。

【0068】

上述したプローバーテストが終了した後、上記第1の実施形態と同様(図6〜10で説明した作製工程)にして半導体装置200を作製する。

【0069】

上述のように、本実施形態の半導体装置200では、プローバーテスト時にメタルパッド11が硬度の高い導電性保護膜202で保護され、かつ、プローブの接触領域を含む領域において、メタルパッド11が導電性保護膜202で裏打ちされた構成となる。それゆえ、本実施形態では、上記第1の実施形態と同様の効果が得られる。

【0070】

また、本実施形態では、メタルパッド11と同様のプロセスで導電性保護膜202を形成することができるので、工程数を少なくすることができ、より簡易に半導体装置200を作製することができる。なお、本実施形態では、上述のように、導電性保護膜202の膜厚を厚くすることは難しいので、厚膜の導電性保護膜を必要とする用途では、本実施形態より上記第1の実施形態の構成の方が優位である。

【0071】

<3.各種変形例及び応用例>

次に、上記第1及び第2の実施形態の半導体装置の各種変形例、並びに、適用例(応用例)について説明する。

【0072】

[変形例1]

上記第1及び第2の実施形態では、メタルパッド11(メタル配線)のプローブ接触側の表面に導電性保護膜を形成する例を示したが、本開示はこれに限定されず、導電性保護膜をメタルパッド11のプローブ接触側とは反対側の表面に形成してもよい。変形例1では、その構成例を説明する。

【0073】

図16及び17に、変形例1の半導体装置の概略構成を示す。図16は、第1の実施形態の半導体装置100に変形例1の構成を適用した場合の半導体装置110(変形例1−1)の概略断面構成図である。また、図17は、第2の実施形態の半導体装置200に変形例1の構成を適用した場合の半導体装置210(変形例1−2)の概略断面構成図である。

【0074】

なお、図16及び17には、説明を簡略化するため、半導体装置のTSV30付近の構成のみを示す。また、図16に示す変形例1−1の半導体装置110において、図1に示す第1の実施形態の半導体装置100と同様の構成には、同じ符号を付して示す。さらに、図17に示す変形例1−2の半導体装置210において、図11に示す第2の実施形態の半導体装置200と同様の構成には、同じ符号を付して示す。

【0075】

図16と図1との比較から明らかなように、変形例1−1の半導体装置110は、第1の実施形態の半導体装置100において、メタルパッド11と導電性保護膜12との配置を逆にした構成である。また、変形例1−1の半導体装置110では、メタルパッド11上のプローブの接触領域を含む酸化層10bの領域に、開口部111が設けられる。変形例1−1の半導体装置110において、上記構成以外の構成は、第1の実施形態の半導体装置100の対応する構成と同様である。

【0076】

また、図17と図11との比較から明らかなように、変形例1−2の半導体装置210は、第2の実施形態の半導体装置200において、メタルパッド11と導電性保護膜202との配置を逆にした構成である。そして、変形例1−2の半導体装置210におけるその他の構成は、第2の実施形態の半導体装置200の対応する構成と同様である。

【0077】

この例の半導体装置では、プローバーテスト時に、メタルパッド11に直接、プローブを接触させるので、メタルパッド11にダメージが発生する。しかしながら、この例では、メタルパッド11の下部に導電性保護膜が接して設けられているので、メタル配線の導電性が維持され、メタルパッド11のダメージの影響を軽減することができる。また、この例では、メタルパッド11の下部に導電性保護膜が接して設けられているので、プローブをメタルパッド11に接触させた際に、Si基材部10の酸化層10bにダメージを与えない。さらに、この例においても、メタルパッド11が導電性保護膜で裏打ちされた構成であるので、メタルパッド11の強度を増大させることができる。すなわち、この例においても、上記第1及び第2の実施形態と同様の効果が得られる。

【0078】

[変形例2]

上記第1の実施形態では、導電性保護膜12をメタルパッド11上に形成した(図4の工程)後、プローバーテスト(図5の工程)を行う例を説明したが、本開示はこれに限定されない。例えば、導電性保護膜12をメタルパッド11上に形成する前に、プローバーテストを行ってもよい。その半導体装置の作製手法の一例(変形例2)を、図18及び19を参照しながら説明する。なお、図18及び19は、それぞれプローバーテスト時及び導電性保護膜形成時の工程の様子を示す図である。

【0079】

この例では、まず、第1の実施形態と同様にして、メタルパッド11上に酸化層10bの開口部10cを形成して、メタルパッド11を露出させる(図2及び3の工程)。次いで、図18に示すように、開口部10cに露出したメタルパッド11にプローブ50を接触させてプローバーテストを行う。

【0080】

次いで、プローバーテスト後、例えば、無電解メッキ法、スクリーン印刷法、スプレーコート法、スタッドバンプ形成法等の手法を用いて、図19に示すように、酸化層10bの開口部10cに露出したメタルパッド11上に、導電性保護膜12を形成する。その後は、上記第1の実施形態と同様(図6〜10の工程)にして半導体装置を作製する。

【0081】

この例では、メタルパッド11に直接、プローブを接触させてプローバーテストを行うので、メタルパッド11にダメージ(プローブ痕)が発生する。しかしながら、この例では、プローバーテスト後、メタルパッド11(プローブ痕)を覆うように、導電性保護膜12をメタルパッド11に接して設ける。すなわち、プローブ痕が残るメタルパッド11の表面を導電性保護膜12で保護する。この場合、メタル配線の導電性が維持されるとともに、TSV30の形成工程で用いる薬液(例えばメッキ液等)のプローブ痕への浸透を防止することができ、メタルパッド11のダメージの影響を軽減することができる。

【0082】

さらに、この例においても、メタルパッド11が導電性保護膜12で裏打ちされた構成であるので、メタルパッド11の強度を増大させることができる。すなわち、この例においても、上記第1の実施形態と同様に、プローバーテストの影響をさらに軽減することができ、半導体装置の例えば歩留まり、信頼性等をより一層向上させることができる。

【0083】

[変形例3]

上記第1の実施形態では、TSV30の上部に、導電性保護膜12(プローブ接触領域を含む領域)を設ける例、すなわち、導電性保護膜12が、縦孔10dの開口部と対向する位置に配置される例を説明した。しかしながら、本開示はこれに限定されない。半導体装置のSi基材部10の面内において、TSV30の形成領域と導電性保護膜12の形成領域とが重ならないように、両領域を配置してもよい。変形例3では、その一構成例を説明する。

【0084】

図20に、変形例3の半導体装置120の概略構成を示す。図20は、第1の実施形態の半導体装置100に変形例3の構成を適用した場合の半導体装置120の概略断面構成図であり、ここでは説明を簡略化するため、半導体装置120のTSV30付近の構成のみを示す。また、図20に示す変形例3の半導体装置120において、図1に示す第1の実施形態の半導体装置100と同様の構成には、同じ符号を付して示す。

【0085】

図20と図1との比較から明らかなように、この例の半導体装置120では、Si基材部10の面内において、TSV30の形成領域と導電性保護膜12の形成領域とが重ならないように、両領域を配置する。そして、この例では、Si基材部10の面内において、TSV30の形成領域から導電性保護膜12の形成領域に渡る領域にメタルパッド121を形成する。この例の半導体装置120において、上記構成以外の構成は、第1の実施形態の半導体装置100の対応する構成と同様である。

【0086】

上述のように、この例の構成においても、プローブの接触領域には、導電性保護膜12がメタルパッド121に接して形成され、メタルパッド121が導電性保護膜12で裏打ちされた構成となる。それゆえ、この例の半導体装置120においても、上記第1の実施形態と同様の効果が得られる。

【0087】

なお、図20に示す例では、第1の実施形態の半導体装置100に変形例3の構成を適用した例を説明したが、本開示はこれに限定されず、例えば、第2の実施形態の半導体装置200に変形例3の構成を適用してもよい。すなわち、第2の実施形態の半導体装置200のSi基材部10の面内において、TSV30の形成領域と導電性保護膜202の形成領域とが重ならないように、両領域を配置してもよい。

【0088】

ただし、この例では、Si基材部10の面内において、TSV30の形成領域と導電性保護膜の形成領域とを互いに別の領域に形成するので、半導体装置のチップサイズが、上記第1及び第2の実施形態の半導体装置のそれに比べて大きくなる場合がある。したがって、半導体装置の小型化の観点では、上記第1及び第2の実施形態の半導体装置の方がこの例の半導体装置より優位である。

【0089】

[変形例4]

上記第2の実施形態では、例えば、W、Ti、Ta等の材料からなる比較的硬度の高い導電性保護膜202をメタルパッド11上に形成するが、このような材料で形成された導電性保護膜202の応力は大きい。それゆえ、メタルパッド11上の導電性保護膜202の形成領域が大きいと、その膜の応力により、導電性保護膜202の膜剥がれが発生する可能性がある。それゆえ、メタルパッド11上の導電性保護膜202の形成領域はできる限り小さい方が好ましい。変形例4では、その一例を説明する。

【0090】

図21(a)及び(b)に、変形例4の半導体装置におけるメタルパッド11及び導電性保護膜222の概略構成を示す。なお、図21(a)は、変形例4の半導体装置のメタルパッド11及び導電性保護膜222の概略上面図であり、図21(b)は、図21(a)中のA−A断面図である。また、図21(a)及び(b)に示す変形例4の半導体装置において、図11に示す第2の実施形態の半導体装置200と同様の構成には、同じ符号を付して示す。さらに、ここでは、説明を簡略化するため、図21(a)及び(b)には、導電性保護膜222の形成工程後の半導体部材の概略構成を示す。

【0091】

この例の半導体装置では、導電性保護膜222の形成領域を、図11に示す上記第2の実施形態の導電性保護膜202の形成領域より小さくする。例えば、導電性保護膜222の形成領域のサイズを、プローバーテスト時に必要とするプローブパッドの最小サイズに設定する。なお、図21(a)及び(b)には示さないが、この例の半導体装置において、導電性保護膜222以外の構成は、上記第2の実施形態の対応する構成と同様である。

【0092】

上述のように、この例の構成においても、プローブの接触領域を含む領域では、導電性保護膜222がメタルパッド11に接して形成され、メタルパッド11が導電性保護膜222で裏打ちされた構成となる。それゆえ、この例の半導体装置においても、上記第2の実施形態と同様の効果が得られる。さらに、この例では、比較的硬度の高い導電性保護膜222の形成領域をより小さくすることができるので、上述した導電性保護膜222の膜剥がれの発生を抑制することができる。

【0093】

[変形例5]

上記変形例4では、導電性保護膜222の膜剥がれを抑制するために、導電性保護膜222の形成領域を小さくする例を説明したが、導電性保護膜222の膜剥がれの発生を抑制する手法は、この手法に限定されない。

【0094】

例えば、導電性保護膜222を、W、Ti、Ta等の材料からなる導電性保護膜本体と、その導電性保護膜本体のメタルパッド11側の表面に設けられた密着層とで構成してもよい。この場合には、W、Ti、Ta等の材料からなる導電性保護膜本体とメタルパッド11との間に、密着層が形成されるので、導電性保護膜222の膜剥がれの発生を抑制することができる。

【0095】

[変形例6]

上記各種実施形態では、TSV30の縦孔10dがメタルパッド11を貫通しない構成例を説明したが、本開示はこれに限定されず、縦孔10dがメタルパッド11を貫通していてもよい。このような構成は、例えば、レーザーを用いて縦孔10dを形成することにより実現することができる。

【0096】

[応用例]

上記各種実施形態及び各種変形例の半導体装置は、各種電子機器に適用可能である。例えば、デジタルカメラやビデオカメラ等のカメラシステム、撮像機能を有する携帯電話、又は、撮像機能を備えた他の機器などの電子機器に、上記各種実施形態及び各種変形例を適用することができる。また、上記各種実施形態及び各種変形例で説明した本開示の技術は、MEMS(Micro Electro Mechanical Systems)にも適用可能である。

【0097】

ここでは、上記各種実施形態及び各種変形例の半導体装置を適用した電子機器として、カメラを例(応用例)に挙げ説明する。図22に、応用例に係るカメラの概略構成を示す。なお、図22には、静止画像又は動画を撮影することのできるビデオカメラの構成例を示す。

【0098】

この例のカメラ300は、固体撮像素子301と、固体撮像素子301の受光センサ(不図示)に入射光を導く光学系302と、固体撮像素子301及び光学系302間に設けられたシャッタ装置303と、固体撮像素子301を駆動する駆動回路304とを備える。さらに、カメラ300は、固体撮像素子301の出力信号を処理する信号処理回路305を備える。

【0099】

固体撮像素子301は、上述した各種実施形態及び各種変形例のいずれかの半導体装置で構成される。その他の各部の構成及び機能は、次の通りである。

【0100】

光学系(光学レンズ)302は、被写体からの像光(入射光)を固体撮像素子301の撮像面(不図示)上に結像させる。これにより、固体撮像素子301内に、一定期間、信号電荷が蓄積される。なお、光学系302は、複数の光学レンズを含む光学レンズ群で構成してもよい。また、シャッタ装置303は、入射光の固体撮像素子301への光照射期間及び遮光期間を制御する。

【0101】

駆動回路304は、固体撮像素子301及びシャッタ装置303に駆動信号を供給する。そして、駆動回路304は、供給した駆動信号により、固体撮像素子301の信号処理回路305への信号出力動作、及び、シャッタ装置303のシャッタ動作を制御する。すなわち、この例では、駆動回路304から供給される駆動信号(タイミング信号)により、固体撮像素子301から信号処理回路305への信号転送動作を行う。

【0102】

信号処理回路305は、固体撮像素子301から転送された信号に対して、各種の信号処理を施す。そして、各種信号処理が施された信号(映像信号)は、メモリなどの記憶媒体(不図示)に記憶される、又は、モニタ(不図示)に出力される。

【0103】

なお、本開示は、以下のような構成を取ることもできる。

(1)

半導体基板、及び、該半導体基板の一方の面上に形成された絶縁膜を有し、内部に該半導体基板の厚さ方向に沿って縦孔が形成された基材部と、

前記縦孔を画成する前記基材部の側壁上に形成された縦孔電極を有する縦孔配線部と、

前記絶縁膜内に形成され、前記縦孔配線部と電気的に接続された金属膜と、

前記絶縁膜内において前記金属膜に接して形成され、かつ、前記金属膜の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成された導電性保護膜と

を備える半導体装置。

(2)

前記金属膜が、前記導電性保護膜の前記半導体基板の側に設けられている

(1)に記載の半導体装置。

(3)

前記導電性保護膜が、前記金属膜の前記半導体基板の側に設けられている

(1)に記載の半導体装置。

(4)

前記導電性保護膜が、前記縦孔の開口部と対向する位置に配置されている

(1)〜(3)のいずれか一項に記載の半導体装置。

(5)

前記絶縁膜の前記プローブの接触側の表面に、前記導電性保護膜が形成された前記プローブの接触領域を含む領域より小さな開口面積の開口部が形成されている

(1)〜(4)のいずれか一項に記載の半導体装置。

(6)

前記導電性保護膜が、Au膜、Ni膜、及び、Cu膜のいずれかである

(1)〜(5)のいずれか一項に記載の半導体装置。

(7)

前記導電性保護膜が、W膜、Ti膜、TiN膜及びTi膜の積層膜、並びに、TaN膜及びTa膜の積層膜のいずれかである

(1)〜(5)のいずれか一項に記載の半導体装置。

(8)

半導体基板、及び、該半導体基板の一方の面上に形成された絶縁膜を有する基材部の該絶縁膜内に金属膜を形成するステップと、

前記絶縁膜内で、かつ、前記金属膜の膜面内の所定領域に、前記金属膜に接して導電性保護膜を形成するステップと、

前記絶縁膜の前記半導体基板の側とは反対側の表面に露出した前記金属膜及び前記導電性保護膜の一方にプローブを接触させてプローバーテストを行うステップと、

前記プローバーテスト後に、前記半導体基板の厚さ方向に沿って、前記基材部に縦孔を形成するステップと

を含む半導体装置の製造方法。

【符号の説明】

【0104】

1,201…装置本体部、2…ガラス基板、3…ガラスシール材、4…メッキ膜、5…ソルダーマスク、6…ソルダーボール、10…Si基材部、10a…Si層、10b…酸化層、10c,203…開口部、10d…縦孔、11…メタルパッド、12,202…導電性保護膜、13…絶縁層、14…メタルシード層、15…フォトダイオード、16…オンチップマイクロレンズ、20…センサ部、30…TSV、50…プローブ、100,200…半導体装置

【技術分野】

【0001】

本開示は、半導体装置、及び、その製造方法に関し、より詳細には、半導体装置の製造途中で半導体部材の電気的性能評価を行う半導体装置、及び、その製造方法に関する。

【背景技術】

【0002】

従来、例えば、半導体装置の小型化及び高機能化を図るために、複数の半導体部材(配線基板)を積層して半導体装置を構成する。このような半導体装置では、各半導体部材間の電気的接続を得るため、各半導体部材のシリコン基板に、その厚さ方向に沿って延在した縦孔状の配線部(以下、TSV(Through Silicon Via)ともいう)を形成する。具体的には、まず、シリコン基板の厚さ方向に沿って延在した縦孔を形成し、次いで、その縦孔を画成するシリコン基板の壁面上に例えばCu等の金属材料からなる電極膜を形成する。

【0003】

上述のようなTSVを有する半導体装置では、一般に、その製造途中において、TSVを形成する前に、半導体部材の電気的性能評価(以下、プローバーテストという)を行う。プローバーテストでは、通常、電極配線の一部(パッド部)を露出させ、そのパッド部にプローブを接触させて、半導体部材の電気的性能の評価を行う。

【0004】

それゆえ、プローバーテストを行った際には、電極配線のパッド部にプローブの痕跡(以下、プローブ痕という)が残る。この場合、例えば、プローバーテスト後に行うTSVの形成工程で用いる薬液(例えばメッキ液等)が、プローブ痕に浸透して、パッド部にダメージを与えることがある。また、パッド部を露出するための開口部が設けられるので、パッド部において十分な強度が得られず、例えば、TSVの形成工程時にパッド部が変形したり、パッド部が剥離したりする場合もある。すなわち、プローバーテストの影響により、半導体装置の例えば歩留まり、信頼性等が低下することがある。

【0005】

そこで、従来、上述したプローバーテストの影響を軽減するための様々な技術が提案されている(例えば、特許文献1参照)。図23(a)及び(b)に、特許文献1で提案されている配線基板の概略構成断面図を示す。なお、図23(a)に示す例は、特許文献1で提案されている配線基板の第1の構成例であり、図23(b)に示す例は、特許文献1で提案されている配線基板の第2の構成例である。

【0006】

特許文献1の第1の構成例では、図23(a)に示すように、配線基板400は、基材401、及び、基材401の一方の面上に形成された第1絶縁部402を含む基体410を備える。そして、基体410内部には、その厚さ方向に延在した貫通孔403が形成される。また、配線基板400は、貫通孔403の一方に開口部を塞ぐように、第1絶縁部402の内部に形成された第1導電層411と、第1絶縁部402の表面に形成された第2導電層412とを備える。さらに、配線基板400は、第1導電層411と第2導電層412とを繋ぐ島状の中間層413を備える。

【0007】

また、配線基板400は、第2導電層412上に形成された第2絶縁部414を備える。そして、貫通孔403の直上に位置する第2絶縁部414の領域に、プローブの接触領域となる開口部414aを形成する。上述のように、特許文献1の第1の構成例では、プローブの接触領域となる第2絶縁部414の開口部414aの導電部を多層構造にし、これにより、上述したプローブ痕の影響を低減する。

【0008】

一方、特許文献1の第2の構成例では、図23(b)に示すように、配線基板420は、基材421、及び、基材421の一方の面上に形成された第1絶縁部422を含む基体430を備える。そして、基体430内部には、その厚さ方向に延在した貫通孔423が形成される。さらに、配線基板420は、貫通孔423の一方に開口部を塞ぐように、第1絶縁部422上に形成された導電部431と、導電部431の表面に形成された第2絶縁部432とを備える。

【0009】

そして、特許文献1の第2の構成例では、配線基板420の面内において、貫通孔423の開口領域と重ならない第2絶縁部432の領域に開口部432aが形成される。すなわち、特許文献1の第2の構成例では、配線基板420の面内において、プローブの接触領域となる導電部431の領域を、貫通孔423の開口領域と重ならない領域に配置することにより上述したプローバーテストの影響を低減する。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2007−288150号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上述のように、従来、TSVを有する半導体装置においては、その製造途中で行うプローバーテストの製品への影響を軽減するための技術が種々提案されている。しかしながら、このようなTSVを有する半導体装置では、上述したプローバーテストの製品への影響をさらに軽減して、例えば半導体装置の歩留まり、信頼性等をより一層向上させる技術の開発が望まれている。

【0012】

本開示は、上記要望に応えるためになされたものであり、本開示の目的は、プローバーテストの製品への影響をさらに軽減して、例えば歩留まり、信頼性等をより一層向上させることのできる半導体装置及びその製造方法を提供することである。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本開示の半導体装置は、基材部と、縦孔配線部と、金属膜と、導電性保護膜とを備える構成とし、各部の構成を次のようにする。基材部は、半導体基板、及び、半導体基板の一方の面上に形成された絶縁膜を有し、内部に半導体基板の厚さ方向に沿って縦孔が形成される。縦孔配線部は、縦孔を画成する基材部の側壁上に形成された縦孔電極を有する。金属膜は、絶縁膜内に形成され、縦孔配線部と電気的に接続される。導電性保護膜は、絶縁膜内において金属膜に接して形成され、かつ、金属膜の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成される。

【0014】

また、本開示の半導体装置の製造方法は、次の手順で行う。まず、半導体基板、及び、半導体基板の一方の面上に形成された絶縁膜を有する基材部の絶縁膜内に金属膜を形成する。次いで、絶縁膜内で、かつ、金属膜の膜面内の所定領域に、金属膜に接して導電性保護膜を形成する。また、絶縁膜の半導体基板の側とは反対側の表面に露出した金属膜及び導電性保護膜の一方にプローブを接触させてプローバーテストを行う。そして、プローバーテスト後に、半導体基板の厚さ方向に沿って、基材部に縦孔を形成する。

【発明の効果】

【0015】

上述のように、本開示の半導体装置及びその製造方法では、プローバーテスト時のプローブの接触領域を含む所定の領域に、金属膜に接して導電性保護膜を形成する。それゆえ、本開示によれば、上述したプローバーテストの製品への影響をさらに軽減することができ、半導体装置の例えば歩留まり、信頼性等をより一層向上させることができる。

【図面の簡単な説明】

【0016】

【図1】本開示の第1の実施形態に係る半導体装置の概略構成断面図である。

【図2】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図3】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図4】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図5】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図6】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図7】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図8】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図9】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図10】第1の実施形態に係る半導体装置の製造工程を説明するための図である。

【図11】本開示の第2の実施形態に係る半導体装置の概略構成断面図である。

【図12】第2の実施形態に係る半導体装置の製造工程を説明するための図である。

【図13】第2の実施形態に係る半導体装置の製造工程を説明するための図である。

【図14】第2の実施形態に係る半導体装置の製造工程を説明するための図である。

【図15】第2の実施形態に係る半導体装置の製造工程を説明するための図である。

【図16】変形例1(変形例1−1)の半導体装置の概略構成断面図である。

【図17】変形例1(変形例1−2)の半導体装置の概略構成断面図である。

【図18】変形例2の半導体装置の製造手法を説明するための図である。

【図19】変形例2の半導体装置の製造手法を説明するための図である。

【図20】変形例3の半導体装置の概略構成断面図である。

【図21】変形例4の半導体装置の概略構成図である。

【図22】本開示に係る半導体装置を適用したカメラの概略構成図である。

【図23】TSVを有する従来の配線基板の概略構成断面図である。

【発明を実施するための形態】

【0017】

以下に、本開示の実施形態に係る半導体装置、及び、その製造手法の例を、図面を参照しながら下記の順で説明する。ただし、本開示は下記の例に限定されない。

1.第1の実施形態

2.第2の実施形態

3.各種変形例及び応用例

【0018】

<1.第1の実施形態>

[半導体装置の全体構成]

図1に、第1の実施形態に係る半導体装置の概略構成断面図を示す。なお、本実施形態では、半導体装置として、固体撮像素子(イメージセンサ)を例に挙げ説明する。また、図1には、説明を簡略化するために、センサ部及びTSV付近の構成のみを示す。

【0019】

半導体装置100は、装置本体部1と、ガラス基板2と、ガラスシール材3と、メッキ膜4と、ソルダーマスク5と、ソルダーボール6とを備える。装置本体部1の構成については、後で詳述する。

【0020】

ガラス基板2は、装置本体部1の一方の面(図1の例では上面)上に、ガラスシール材3を介して設けられる。なお、ガラスシール材3は、装置本体部1とガラス基板2とを貼り合わせるためのシール部材である。

【0021】

メッキ膜4は、装置本体部1の他方の面(図1の例では下面)上の一部に設けられる。具体的には、装置本体部1の後述するTSV30(縦孔配線部)を構成するメタルシード層14を覆うように設けられる。なお、メッキ膜4は、TSV30を構成するメタルシード層14をエッチングしてパターニングする際のマスクとしても利用される。

【0022】

ソルダーマスク5は、装置本体部1の下面、及び、メッキ膜4を覆うように設けられる。また、ソルダーマスク5には、メッキ膜4を露出するための開口部5aが設けられ、その開口部5aに、ソルダーボール6が設けられる。これにより、ソルダーボール6は、メッキ膜4を介してTSV30と電気的に接続される。なお、ソルダーボール6は、TSV30を介して出力された信号を外部の配線に出力するための接続端子である。また、ソルダーマスク5は、外部の配線をソルダーボール6に半田付けして接続する際に、半田が不要な部分に付着しないようにするためのマスクとして作用する。

【0023】

[装置本体部の構成]

装置本体部1は、Si基材部10(基材部)と、メタルパッド11(金属膜)と、導電性保護膜12と、絶縁層13と、メタルシード層14(縦孔電極)とを備える。また、装置本体部1は、外部から受光した光を電荷信号に変換する複数のフォトダイオード15と、該複数のフォトダイオード15のそれぞれ直上に設けられ、対応するフォトダイオード15に光をそれぞれ集光する複数のオンチップマイクロレンズ16とを備える。

【0024】

Si基材部10は、例えばシリコン基板等で構成されたSi層10a(半導体基板)と、該Si層10aの一方の表面(図1の例では上面)に形成された酸化層10b(絶縁膜)とを有する。なお、酸化層10bは、SiO2膜で構成され、酸化層10bには、メタルパッド11を露出させる開口部10cが設けられる。また、Si基材部10の内部には、その厚さ方向に沿って延在した縦孔10dが形成される。なお、縦孔10dは、Si層10aの他方の表面(図1の例では下面)からメタルパッド11の下面まで延在して形成される。

【0025】

また、本実施形態では、Si基材部10の酸化層10bの表面に、複数のオンチップマイクロレンズ16を配列して設け、酸化層10b内に複数のオンチップマイクロレンズ16に対応する複数のフォトダイオード15をそれぞれ形成する。これにより、被写体からの光を検出するセンサ部20が構成される。なお、図1には示さないが、センサ部20は、例えば、カラーフィルタ、各種トランジスタ、フローティングディフュージョンなども備える。

【0026】

メタルパッド11は、酸化層10b内に設けられる。この際、Si基材部10の縦孔10dのガラス基板2側の開口を塞ぐように、メタルパッド11が設けられる。なお、メタルパッド11は、例えば、Al、Cu、W、Ni、Ta等の導電性材料で形成することができる。また、メタルパッド11の厚さは、例えば、約1μm以下程度に設定することができる。

【0027】

メタルパッド11は、例えば、センサ部20から出力される信号を外部に出力するための出力電極、センサ部20に電圧を印加するための入力電極、グランド電極等の電極配線として用いられる。より具体的には、メタルパッド11は、例えば、センサ部20内に設けられた画素(不図示)を構成する選択トランジスタ(不図示)に接続される信号線の端部(BEOL:Back End Of the Line)として用いられる。

【0028】

導電性保護膜12は、酸化層10bの開口部10cに露出したメタルパッド11上(第1の領域)に形成される。なお、本実施形態では、導電性保護膜12を、半導体装置100の製造途中でプローバーテストを行う際にプローブを接触させる領域に設ける。すなわち、本実施形態では、導電性保護膜12をプローブパッドとして用いる。それゆえ、本実施形態では、プローバーテスト時にメタルパッド11を保護するため、導電性保護膜12を厚膜の金属膜で構成する。なお、導電性保護膜12の厚さは、例えば、プローブの接触圧等の条件を考慮して適宜設定されるが、できる限り厚くすることが好ましい。例えば、数μm〜数十μmの範囲で、導電性保護膜12の厚さを設定することができる。

【0029】

また、導電性保護膜12の形成材料としては、厚膜の金属膜を形成可能な導電性材料であれば、任意の材料を用いることができる。例えば、Ni、Cu、Au、Ag等の金属材料で導電性保護膜12を形成することができる。なお、本実施形態では、導電性保護膜12を一つの金属膜で構成する例を説明するが、本開示はこれに限定されず、導電性保護膜12の構成を複数の金属膜を積層した多層構造にしてもよい。

【0030】

また、本実施形態では、Si基材部10の縦孔10dを画成するSi基材部10の側壁上に、絶縁層13(SiO2層)及びメタルシード層14がこの順で積層される。なお、この際、メタルシード層14とメタルパッド11の下面とが直接接するように、絶縁層13及びメタルシード層14を形成する。本実施形態では、このように、Si基材部10の縦孔10dを画成するSi基材部10の側壁上に、絶縁層13及びメタルシード層14を設けることによりTSV30を構成する。

【0031】

TSV30は、センサ部20からメタルパッド11を介して出力される信号を、メタルシード層14、メッキ膜4及びソルダーボール6を介して、外部の配線に出力する。すなわち、本実施形態の半導体装置100では、センサ部20で検出した信号を、装置本体部1のソルダーマスク5の側から取り出す。

【0032】

[半導体装置の製造手法]

次に、本実施形態の半導体装置100の作製手法の一例を、図2〜10を参照しながら説明する。なお、図2〜10は、各工程で作製される半導体部材の概略断面図である。また、ここでは、説明を簡略化するため、装置本体部1のTSV30付近の構成の作製工程について説明する。それ以外の構成部は、例えば従来の固体撮像素子の作製手法と同様にして作製することができる。

【0033】

本実施形態では、まず、図2に示すように、Si基材部10の酸化層10b内に、メタルパッド11を形成する。なお、このメタルパッド11は、例えば従来の固体撮像素子におけるメタルパッドの作製手法と同様にして作製することができる。

【0034】

例えば、まず、Si層10a上に酸化膜(SiO2膜)を、例えばプラズマCVD(Chemical Vapor Deposition)法等の手法を用いて形成する。次いで、その酸化膜上にメタルパッド11の形成材料からなる金属膜を例えばスパッタリング法等の手法を用いて形成する。その後、金属膜をパターニングしてメタルパッド11を形成する。なお、この際、メタルパッド11上に形成する酸化層10bの後述の開口部10cのプロセスマージンを考慮して、特性上必要とされるサイズより少し大きなサイズのメタルパッド11を形成する。そして、メタルパッド11上に、例えばプラズマCVD法等の手法を用いて酸化膜を形成する。本実施形態では、このようにしてメタルパッド11を酸化層10b内に形成することができる。

【0035】

次いで、メタルパッド11上の酸化層10bの一部の領域、具体的には、導電性保護膜12の形成領域(プローブの接触領域を含む領域)をエッチングして除去する。これにより、図3に示すように、酸化層10bの導電性保護膜12の形成領域に、開口部10cが形成され、メタルパッド11が開口部10cに露出する。なお、本実施形態では、上述のように、開口部10cのプロセスマージンを考慮して、特性上必要とされるサイズより少し大きなサイズのメタルパッド11を形成する。それゆえ、開口部10cの開口面積はメタルパッド11の面積より小さくなり、メタルパッド11の外周端部付近の領域は、酸化層10bで被覆された状態になる。

【0036】

次いで、例えば、無電解メッキ法、スクリーン印刷法、スプレーコート法、スタッドバンプ形成法等の手法を用いて、図4に示すように、酸化層10bの開口部10cに露出したメタルパッド11上に、導電性保護膜12を形成する。なお、この際、本実施形態では、導電性保護膜12の表面と酸化層10bの表面とが面一となるように、導電性保護膜12を形成する。

【0037】

より具体的に説明すると、例えば、導電性保護膜12の形成手法としてスクリーン印刷法を用いた場合には、まず、導電性ペーストの充填用の孔が形成されたスクリーンを開口部10c上に配置する。次いで、導電性ペーストをスクリーン上に載せる。次いで、スキージを用いて導電性ペーストをスクリーン上で引き延ばす。これにより、スクリーンからスクリーンの孔を介して開口部10cに導電性のペーストが充填され、導電性保護膜12が形成される。

【0038】

また、例えば、導電性保護膜12の形成手法としてスプレーコート法を用いた場合には、ノズルから開口部10cに、導電性ペーストを微量のレートで吐出する。これにより、開口部10cに導電性ペーストが充填され、導電性保護膜12が形成される。

【0039】

次いで、導電性保護膜12が形成された半導体部材に対してプローバーテストを行う。具体的には、図5に示すように、プローブ50を導電性保護膜12に接触させて、半導体部材の電気的性能を評価する。なお、この際、導電性保護膜12にプローブ痕が発生するが、その下部に形成されたメタルパッド11は導電性保護膜12により保護されるので、メタルパッド11にはダメージは生じない。

【0040】

上述したプローバーテストが終了した後、図6に示すように、Si基材部10の酸化層10b、及び、導電性保護膜12上にガラスシール材3を形成する。なお、図6には示さないが、この工程では、センサ部20上にもガラスシール材3が形成される。

【0041】

次いで、図7に示すように、ガラスシール材3上にガラス基板2を載置し、ガラス基板2と、Si基材部10とをガラスシール材3を介して貼り合わせる。なお、本実施形態では、図7には示さないが、この工程において、Si層10aの酸化層10bの側とは反対側の表面(図7では下面)を研削(BGR:Back Grind)して、Si基材部10の厚さを薄くする。

【0042】

次いで、図8に示すように、ドライエッチング法により、Si層10aの下面の所定領域をエッチングして、メタルパッド11の下部(Si層10a側)に縦孔10dを形成する。この際、Si層10aの下面からメタルパッド11の下面まで延在する縦孔10dを形成し、縦孔10dの開口部にメタルパッド11の下面の一部を露出させる。なお、酸化層10bのエッチングレートとメタルパッド11のエッチングレートとの比(選択比)は高いので、メタルパッド11の下面でエッチング処理を停止させることは容易である。

【0043】

次いで、図9に示すように、Si層10aの下面上、縦孔10dを画成するSi基材部10の側壁上、及び、縦孔10dに露出したメタルパッド11の下面上に、例えばプラズマCVD法等の手法により、絶縁層13(SiO2層)を形成する。

【0044】

次いで、メタルパッド11の下面上に形成された絶縁層13の一部を除去して、縦孔10dにメタルパッド11の一部を露出させる。その後、図10に示すように、絶縁層13上、及び、露出したメタルパッド11の下面上に、例えばスパッタリング法等の手法により、メタルシード層14を形成する。これにより、メタルパッド11とメタルシード層14とが電気的に接続される。

【0045】

その後、従来の固体撮像素子の作製手法と同様にして、メッキ膜4、ソルダーマスク5、及び、ソルダーボール6を形成する。本実施形態では、このようにして、半導体装置100を作製する。

【0046】

上述のように、本実施形態の半導体装置100の製造手法では、メタルパッド11上に厚膜の導電性保護膜12を設け、その導電性保護膜12をプローブパッドとして用いる。それゆえ、本実施形態では、プローバーテスト時に発生するプローブ痕による、メタルパッド11のダメージを軽減することができる。すなわち、TSV30の形成工程で用いる薬液(例えばメッキ液等)のプローブ痕への浸透により、メタルパッド11がダメージを受けることを防止することができる。

【0047】

さらに、本実施形態は、例えば図23(a)及び(b)で説明した特許文献1で提案されている技術に対して、次のような利点が得られる。

【0048】

図23(a)及び(b)で説明した従来の配線基板では、プローブを接触させる第2導電層412又は導電部431の下部に絶縁膜(酸化膜)が設けられるので、プローバーテスト時のプローブの接触により、絶縁膜にダメージが発生する可能性がある。このように、絶縁膜にダメージが生じた場合にも、製品の例えば歩留まり、信頼性等が低下する。それに対して、本実施形態の半導体装置100では、メタルパッド11上に直接、導電性保護膜12を設けているので、プローブ50を導電性保護膜12に接触させた際に、Si基材部10の酸化層10bにダメージを与えない。

【0049】

また、上記特許文献1で提案されている第1の構成例(図23(a)参照)では、第1導電層411のプローブが接触する領域には、島状の中間層413が第1導電層411に接して設けられている。それに対して、本実施形態の半導体装置100では、プローブの接触領域を含む領域全面に渡って導電性保護膜12がメタルパッド11に接して設けられる。

【0050】

すなわち、本実施形態では、プローブの接触領域を含む領域において、メタルパッド11が導電性保護膜12に裏打ちされた構成であり、メタルパッド11及び導電性保護膜12間の接触面積は、特許文献1の第1の構成例のそれに比べて大きくなる。それゆえ、本実施形態では、上記特許文献1の第1の構成例に比べてメタルパッド11の強度を増大させることができる。この場合、導電性保護膜12を形成した後の各種工程(TSV30の形成工程も含む)において、メタルパッド11の変形や剥離を抑制することができる。

【0051】

以上のことから、本実施形態では、プローバーテストの影響をさらに軽減することができ、半導体装置100の例えば歩留まり、信頼性等をより一層向上させることができる。

【0052】

<2.第2の実施形態>

上記第1の実施形態では、メタルパッド11(メタル配線)上に、厚膜の導電性保護膜12(金属膜)を形成する例を説明したが、本開示はこれに限定されない。例えば、メタル配線を複数のメタル層からなる多層膜で構成し、その多層膜の一方の最表面側に位置するメタル層を導電性保護膜として用いてもよい。第2の実施形態では、その一例を説明する。

【0053】

[半導体装置の構成]

図11に、第2の実施形態に係る半導体装置の概略構成断面図を示す。なお、本実施形態では、上記第1の実施形態と同様に、半導体装置として、固体撮像素子(イメージセンサ)を例に挙げ説明する。また、図11には、説明を簡略化するため、本実施形態の半導体装置のTSV付近の構成のみを示す。さらに、図11に示す本実施形態の半導体装置200において、図1に示す第1の実施形態の半導体装置100と同様の構成には、同じ符号を付して示す。

【0054】

本実施形態の半導体装置200は、装置本体部201と、ガラス基板2と、ガラスシール材3とを備える。なお、図11には示さないが、半導体装置200は、上記第1の実施形態と同様に、メッキ膜、ソルダーマスク、及び、ソルダーボールを備える。また、本実施形態の半導体装置200におけるガラス基板2、及び、ガラスシール材3は、上記第1の実施形態のそれらと同様の構成である。すなわち、本実施形態において、装置本体部201以外の構成は、上記第1の実施形態の対応する構成と同様であるので、ここでは、装置本体部201の構成についてのみ説明する。

【0055】

[装置本体部の全体構成]

装置本体部201は、Si基材部10(基材部)と、メタルパッド11(金属膜)と、導電性保護膜202と、絶縁層13と、メタルシード層14(縦孔電極)とを備える。また、図11には示さないが、装置本体部201は、第1の実施形態と同様に、フォトダイオード及びオンチップマイクロレンズを含むセンサ部を備える。

【0056】

本実施形態の半導体装置200では、図11に示すように、TSV30(縦孔配線部)の上部(ガラス基板2側)に、メタルパッド11を形成し、さらに、メタルパッド11上に薄膜の導電性保護膜202を積層する。すなわち、本実施形態では、メタル配線をメタルパッド11及び導電性保護膜202の2層構造とする。

【0057】

そして、本実施形態では、Si基材部10の酸化層10b(絶縁膜)に開口部203を設け、導電性保護膜202をその開口部203に露出させる。本実施形態では、この開口部203に露出した導電性保護膜202にプローブを接触させてプローバーテストを行う。

【0058】

なお、導電性保護膜202は、メタルパッド11の形成工程に続いて形成されるので、メタルパッド11と同様の形成手法(例えばスパッタリン法)で形成される。それゆえ、第1の実施形態のように、厚膜(数十μm程度)の導電性保護膜202を形成することが難しい。そこで、本実施形態では、導電性保護膜202にプローブを接触させた際に、メタルパッド11にダメージが生じないようにするために、比較的硬度の高い導電性材料で導電性保護膜202を形成する。例えば、W、Ti、Ta等の材料で導電性保護膜202を形成することができる。

【0059】

また、図11に示す例では、導電性保護膜202を一層で構成する例を説明するが、本開示はこれに限定されない。例えば、導電性保護膜202を多層構造としてもよい。より具体的には、導電性保護膜202を、例えば、TiN膜/Ti膜、TaN膜/Ta膜等の積層膜で構成することができる。

【0060】

本実施形態において、上述のようにメタル配線を多層構造にしたこと以外の構成は、上記第1の実施形態の対応する構成と同様である。

【0061】

[半導体装置の製造手法]

次に、本実施形態の半導体装置200の作製手法の一例を、図12〜15を参照しながら説明する。なお、本実施形態の半導体装置200の作製手法では、プローバーテストまでの工程が上記第1の実施形態の半導体装置100のそれと異なるので、図12〜15には、プローバーテストまでの各工程で作製される半導体部材の概略断面図を示す。また、ここでは、説明を簡略化するため、装置本体部201のTSV30付近の構成の作製工程について説明する。それ以外の構成部は、例えば従来の固体撮像素子の作製手法と同様にして作製することができる。

【0062】

本実施形態では、まず、Si層10a上に、例えばプラズマCVD法等の手法を用いて、酸化膜204を形成する。次いで、図12に示すように、その酸化膜204上にメタルパッド11及び導電性保護膜202をこの順で形成する。

【0063】

なお、メタルパッド11及び導電性保護膜202の形成手法は任意であるが、例えば、次のようにしてメタルパッド11及び導電性保護膜202をすることができる。まず、メタルパッド11の形成材料からなる第1の金属膜、及び、導電性保護膜202の形成材料からなる第2の金属膜を、例えばスパッタリング法等の手法を用いて酸化膜204上に形成する。次いで、第1の金属膜及び第2の金属膜からなる積層膜をパターニングしてメタルパッド11及び導電性保護膜202を形成する。

【0064】

ただし、上記メタルパッド11及び導電性保護膜202の形成工程では、導電性保護膜202上に形成する後述の開口部203のプロセスマージンを考慮して、特性上必要とされるサイズより少し大きなサイズのメタルパッド11及び導電性保護膜202を形成する。

【0065】

次いで、図13に示すように、導電性保護膜202上に、例えばプラズマCVD法等の手法を用いて、酸化膜を形成してSi基材部10の酸化層10bを作製する。

【0066】

次いで、導電性保護膜202上の酸化層10bの一部の領域、具体的には、プローブの接触領域を含む領域をエッチングして除去する。これにより、図14に示すように、酸化層10bのプローブの接触領域を含む領域に開口部203が形成され、その開口部203に導電性保護膜202が露出する。なお、本実施形態では、上述のように、開口部203のプロセスマージンを考慮して、特性上必要とされるサイズより少し大きなサイズの導電性保護膜202を形成する。それゆえ、開口部203の開口面積は導電性保護膜202の面積より小さくなり、導電性保護膜202の外周端部付近の領域は、酸化層10bで被覆された状態になる。

【0067】

次いで、上記工程で作製された半導体部材に対してプローバーテストを行う。具体的には、図15に示すように、プローブ50を、導電性保護膜202を介してメタルパッド11に接触させて半導体部材の電気的性能を評価する。なお、この際、メタルパッド11は硬度の高い導電性保護膜202により保護されているので、メタルパッド11へのダメージを軽減することができる。

【0068】

上述したプローバーテストが終了した後、上記第1の実施形態と同様(図6〜10で説明した作製工程)にして半導体装置200を作製する。

【0069】

上述のように、本実施形態の半導体装置200では、プローバーテスト時にメタルパッド11が硬度の高い導電性保護膜202で保護され、かつ、プローブの接触領域を含む領域において、メタルパッド11が導電性保護膜202で裏打ちされた構成となる。それゆえ、本実施形態では、上記第1の実施形態と同様の効果が得られる。

【0070】

また、本実施形態では、メタルパッド11と同様のプロセスで導電性保護膜202を形成することができるので、工程数を少なくすることができ、より簡易に半導体装置200を作製することができる。なお、本実施形態では、上述のように、導電性保護膜202の膜厚を厚くすることは難しいので、厚膜の導電性保護膜を必要とする用途では、本実施形態より上記第1の実施形態の構成の方が優位である。

【0071】

<3.各種変形例及び応用例>

次に、上記第1及び第2の実施形態の半導体装置の各種変形例、並びに、適用例(応用例)について説明する。

【0072】

[変形例1]

上記第1及び第2の実施形態では、メタルパッド11(メタル配線)のプローブ接触側の表面に導電性保護膜を形成する例を示したが、本開示はこれに限定されず、導電性保護膜をメタルパッド11のプローブ接触側とは反対側の表面に形成してもよい。変形例1では、その構成例を説明する。

【0073】

図16及び17に、変形例1の半導体装置の概略構成を示す。図16は、第1の実施形態の半導体装置100に変形例1の構成を適用した場合の半導体装置110(変形例1−1)の概略断面構成図である。また、図17は、第2の実施形態の半導体装置200に変形例1の構成を適用した場合の半導体装置210(変形例1−2)の概略断面構成図である。

【0074】

なお、図16及び17には、説明を簡略化するため、半導体装置のTSV30付近の構成のみを示す。また、図16に示す変形例1−1の半導体装置110において、図1に示す第1の実施形態の半導体装置100と同様の構成には、同じ符号を付して示す。さらに、図17に示す変形例1−2の半導体装置210において、図11に示す第2の実施形態の半導体装置200と同様の構成には、同じ符号を付して示す。

【0075】

図16と図1との比較から明らかなように、変形例1−1の半導体装置110は、第1の実施形態の半導体装置100において、メタルパッド11と導電性保護膜12との配置を逆にした構成である。また、変形例1−1の半導体装置110では、メタルパッド11上のプローブの接触領域を含む酸化層10bの領域に、開口部111が設けられる。変形例1−1の半導体装置110において、上記構成以外の構成は、第1の実施形態の半導体装置100の対応する構成と同様である。

【0076】

また、図17と図11との比較から明らかなように、変形例1−2の半導体装置210は、第2の実施形態の半導体装置200において、メタルパッド11と導電性保護膜202との配置を逆にした構成である。そして、変形例1−2の半導体装置210におけるその他の構成は、第2の実施形態の半導体装置200の対応する構成と同様である。

【0077】

この例の半導体装置では、プローバーテスト時に、メタルパッド11に直接、プローブを接触させるので、メタルパッド11にダメージが発生する。しかしながら、この例では、メタルパッド11の下部に導電性保護膜が接して設けられているので、メタル配線の導電性が維持され、メタルパッド11のダメージの影響を軽減することができる。また、この例では、メタルパッド11の下部に導電性保護膜が接して設けられているので、プローブをメタルパッド11に接触させた際に、Si基材部10の酸化層10bにダメージを与えない。さらに、この例においても、メタルパッド11が導電性保護膜で裏打ちされた構成であるので、メタルパッド11の強度を増大させることができる。すなわち、この例においても、上記第1及び第2の実施形態と同様の効果が得られる。

【0078】

[変形例2]

上記第1の実施形態では、導電性保護膜12をメタルパッド11上に形成した(図4の工程)後、プローバーテスト(図5の工程)を行う例を説明したが、本開示はこれに限定されない。例えば、導電性保護膜12をメタルパッド11上に形成する前に、プローバーテストを行ってもよい。その半導体装置の作製手法の一例(変形例2)を、図18及び19を参照しながら説明する。なお、図18及び19は、それぞれプローバーテスト時及び導電性保護膜形成時の工程の様子を示す図である。

【0079】

この例では、まず、第1の実施形態と同様にして、メタルパッド11上に酸化層10bの開口部10cを形成して、メタルパッド11を露出させる(図2及び3の工程)。次いで、図18に示すように、開口部10cに露出したメタルパッド11にプローブ50を接触させてプローバーテストを行う。

【0080】

次いで、プローバーテスト後、例えば、無電解メッキ法、スクリーン印刷法、スプレーコート法、スタッドバンプ形成法等の手法を用いて、図19に示すように、酸化層10bの開口部10cに露出したメタルパッド11上に、導電性保護膜12を形成する。その後は、上記第1の実施形態と同様(図6〜10の工程)にして半導体装置を作製する。

【0081】

この例では、メタルパッド11に直接、プローブを接触させてプローバーテストを行うので、メタルパッド11にダメージ(プローブ痕)が発生する。しかしながら、この例では、プローバーテスト後、メタルパッド11(プローブ痕)を覆うように、導電性保護膜12をメタルパッド11に接して設ける。すなわち、プローブ痕が残るメタルパッド11の表面を導電性保護膜12で保護する。この場合、メタル配線の導電性が維持されるとともに、TSV30の形成工程で用いる薬液(例えばメッキ液等)のプローブ痕への浸透を防止することができ、メタルパッド11のダメージの影響を軽減することができる。

【0082】

さらに、この例においても、メタルパッド11が導電性保護膜12で裏打ちされた構成であるので、メタルパッド11の強度を増大させることができる。すなわち、この例においても、上記第1の実施形態と同様に、プローバーテストの影響をさらに軽減することができ、半導体装置の例えば歩留まり、信頼性等をより一層向上させることができる。

【0083】

[変形例3]

上記第1の実施形態では、TSV30の上部に、導電性保護膜12(プローブ接触領域を含む領域)を設ける例、すなわち、導電性保護膜12が、縦孔10dの開口部と対向する位置に配置される例を説明した。しかしながら、本開示はこれに限定されない。半導体装置のSi基材部10の面内において、TSV30の形成領域と導電性保護膜12の形成領域とが重ならないように、両領域を配置してもよい。変形例3では、その一構成例を説明する。

【0084】

図20に、変形例3の半導体装置120の概略構成を示す。図20は、第1の実施形態の半導体装置100に変形例3の構成を適用した場合の半導体装置120の概略断面構成図であり、ここでは説明を簡略化するため、半導体装置120のTSV30付近の構成のみを示す。また、図20に示す変形例3の半導体装置120において、図1に示す第1の実施形態の半導体装置100と同様の構成には、同じ符号を付して示す。

【0085】

図20と図1との比較から明らかなように、この例の半導体装置120では、Si基材部10の面内において、TSV30の形成領域と導電性保護膜12の形成領域とが重ならないように、両領域を配置する。そして、この例では、Si基材部10の面内において、TSV30の形成領域から導電性保護膜12の形成領域に渡る領域にメタルパッド121を形成する。この例の半導体装置120において、上記構成以外の構成は、第1の実施形態の半導体装置100の対応する構成と同様である。

【0086】

上述のように、この例の構成においても、プローブの接触領域には、導電性保護膜12がメタルパッド121に接して形成され、メタルパッド121が導電性保護膜12で裏打ちされた構成となる。それゆえ、この例の半導体装置120においても、上記第1の実施形態と同様の効果が得られる。

【0087】

なお、図20に示す例では、第1の実施形態の半導体装置100に変形例3の構成を適用した例を説明したが、本開示はこれに限定されず、例えば、第2の実施形態の半導体装置200に変形例3の構成を適用してもよい。すなわち、第2の実施形態の半導体装置200のSi基材部10の面内において、TSV30の形成領域と導電性保護膜202の形成領域とが重ならないように、両領域を配置してもよい。

【0088】

ただし、この例では、Si基材部10の面内において、TSV30の形成領域と導電性保護膜の形成領域とを互いに別の領域に形成するので、半導体装置のチップサイズが、上記第1及び第2の実施形態の半導体装置のそれに比べて大きくなる場合がある。したがって、半導体装置の小型化の観点では、上記第1及び第2の実施形態の半導体装置の方がこの例の半導体装置より優位である。

【0089】

[変形例4]

上記第2の実施形態では、例えば、W、Ti、Ta等の材料からなる比較的硬度の高い導電性保護膜202をメタルパッド11上に形成するが、このような材料で形成された導電性保護膜202の応力は大きい。それゆえ、メタルパッド11上の導電性保護膜202の形成領域が大きいと、その膜の応力により、導電性保護膜202の膜剥がれが発生する可能性がある。それゆえ、メタルパッド11上の導電性保護膜202の形成領域はできる限り小さい方が好ましい。変形例4では、その一例を説明する。

【0090】

図21(a)及び(b)に、変形例4の半導体装置におけるメタルパッド11及び導電性保護膜222の概略構成を示す。なお、図21(a)は、変形例4の半導体装置のメタルパッド11及び導電性保護膜222の概略上面図であり、図21(b)は、図21(a)中のA−A断面図である。また、図21(a)及び(b)に示す変形例4の半導体装置において、図11に示す第2の実施形態の半導体装置200と同様の構成には、同じ符号を付して示す。さらに、ここでは、説明を簡略化するため、図21(a)及び(b)には、導電性保護膜222の形成工程後の半導体部材の概略構成を示す。

【0091】

この例の半導体装置では、導電性保護膜222の形成領域を、図11に示す上記第2の実施形態の導電性保護膜202の形成領域より小さくする。例えば、導電性保護膜222の形成領域のサイズを、プローバーテスト時に必要とするプローブパッドの最小サイズに設定する。なお、図21(a)及び(b)には示さないが、この例の半導体装置において、導電性保護膜222以外の構成は、上記第2の実施形態の対応する構成と同様である。

【0092】

上述のように、この例の構成においても、プローブの接触領域を含む領域では、導電性保護膜222がメタルパッド11に接して形成され、メタルパッド11が導電性保護膜222で裏打ちされた構成となる。それゆえ、この例の半導体装置においても、上記第2の実施形態と同様の効果が得られる。さらに、この例では、比較的硬度の高い導電性保護膜222の形成領域をより小さくすることができるので、上述した導電性保護膜222の膜剥がれの発生を抑制することができる。

【0093】

[変形例5]

上記変形例4では、導電性保護膜222の膜剥がれを抑制するために、導電性保護膜222の形成領域を小さくする例を説明したが、導電性保護膜222の膜剥がれの発生を抑制する手法は、この手法に限定されない。

【0094】

例えば、導電性保護膜222を、W、Ti、Ta等の材料からなる導電性保護膜本体と、その導電性保護膜本体のメタルパッド11側の表面に設けられた密着層とで構成してもよい。この場合には、W、Ti、Ta等の材料からなる導電性保護膜本体とメタルパッド11との間に、密着層が形成されるので、導電性保護膜222の膜剥がれの発生を抑制することができる。

【0095】

[変形例6]

上記各種実施形態では、TSV30の縦孔10dがメタルパッド11を貫通しない構成例を説明したが、本開示はこれに限定されず、縦孔10dがメタルパッド11を貫通していてもよい。このような構成は、例えば、レーザーを用いて縦孔10dを形成することにより実現することができる。

【0096】

[応用例]

上記各種実施形態及び各種変形例の半導体装置は、各種電子機器に適用可能である。例えば、デジタルカメラやビデオカメラ等のカメラシステム、撮像機能を有する携帯電話、又は、撮像機能を備えた他の機器などの電子機器に、上記各種実施形態及び各種変形例を適用することができる。また、上記各種実施形態及び各種変形例で説明した本開示の技術は、MEMS(Micro Electro Mechanical Systems)にも適用可能である。

【0097】

ここでは、上記各種実施形態及び各種変形例の半導体装置を適用した電子機器として、カメラを例(応用例)に挙げ説明する。図22に、応用例に係るカメラの概略構成を示す。なお、図22には、静止画像又は動画を撮影することのできるビデオカメラの構成例を示す。

【0098】

この例のカメラ300は、固体撮像素子301と、固体撮像素子301の受光センサ(不図示)に入射光を導く光学系302と、固体撮像素子301及び光学系302間に設けられたシャッタ装置303と、固体撮像素子301を駆動する駆動回路304とを備える。さらに、カメラ300は、固体撮像素子301の出力信号を処理する信号処理回路305を備える。

【0099】

固体撮像素子301は、上述した各種実施形態及び各種変形例のいずれかの半導体装置で構成される。その他の各部の構成及び機能は、次の通りである。

【0100】

光学系(光学レンズ)302は、被写体からの像光(入射光)を固体撮像素子301の撮像面(不図示)上に結像させる。これにより、固体撮像素子301内に、一定期間、信号電荷が蓄積される。なお、光学系302は、複数の光学レンズを含む光学レンズ群で構成してもよい。また、シャッタ装置303は、入射光の固体撮像素子301への光照射期間及び遮光期間を制御する。

【0101】

駆動回路304は、固体撮像素子301及びシャッタ装置303に駆動信号を供給する。そして、駆動回路304は、供給した駆動信号により、固体撮像素子301の信号処理回路305への信号出力動作、及び、シャッタ装置303のシャッタ動作を制御する。すなわち、この例では、駆動回路304から供給される駆動信号(タイミング信号)により、固体撮像素子301から信号処理回路305への信号転送動作を行う。

【0102】

信号処理回路305は、固体撮像素子301から転送された信号に対して、各種の信号処理を施す。そして、各種信号処理が施された信号(映像信号)は、メモリなどの記憶媒体(不図示)に記憶される、又は、モニタ(不図示)に出力される。

【0103】

なお、本開示は、以下のような構成を取ることもできる。

(1)

半導体基板、及び、該半導体基板の一方の面上に形成された絶縁膜を有し、内部に該半導体基板の厚さ方向に沿って縦孔が形成された基材部と、

前記縦孔を画成する前記基材部の側壁上に形成された縦孔電極を有する縦孔配線部と、

前記絶縁膜内に形成され、前記縦孔配線部と電気的に接続された金属膜と、

前記絶縁膜内において前記金属膜に接して形成され、かつ、前記金属膜の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成された導電性保護膜と

を備える半導体装置。

(2)

前記金属膜が、前記導電性保護膜の前記半導体基板の側に設けられている

(1)に記載の半導体装置。

(3)

前記導電性保護膜が、前記金属膜の前記半導体基板の側に設けられている

(1)に記載の半導体装置。

(4)

前記導電性保護膜が、前記縦孔の開口部と対向する位置に配置されている

(1)〜(3)のいずれか一項に記載の半導体装置。

(5)

前記絶縁膜の前記プローブの接触側の表面に、前記導電性保護膜が形成された前記プローブの接触領域を含む領域より小さな開口面積の開口部が形成されている

(1)〜(4)のいずれか一項に記載の半導体装置。

(6)

前記導電性保護膜が、Au膜、Ni膜、及び、Cu膜のいずれかである

(1)〜(5)のいずれか一項に記載の半導体装置。

(7)

前記導電性保護膜が、W膜、Ti膜、TiN膜及びTi膜の積層膜、並びに、TaN膜及びTa膜の積層膜のいずれかである

(1)〜(5)のいずれか一項に記載の半導体装置。

(8)

半導体基板、及び、該半導体基板の一方の面上に形成された絶縁膜を有する基材部の該絶縁膜内に金属膜を形成するステップと、

前記絶縁膜内で、かつ、前記金属膜の膜面内の所定領域に、前記金属膜に接して導電性保護膜を形成するステップと、

前記絶縁膜の前記半導体基板の側とは反対側の表面に露出した前記金属膜及び前記導電性保護膜の一方にプローブを接触させてプローバーテストを行うステップと、

前記プローバーテスト後に、前記半導体基板の厚さ方向に沿って、前記基材部に縦孔を形成するステップと

を含む半導体装置の製造方法。

【符号の説明】

【0104】

1,201…装置本体部、2…ガラス基板、3…ガラスシール材、4…メッキ膜、5…ソルダーマスク、6…ソルダーボール、10…Si基材部、10a…Si層、10b…酸化層、10c,203…開口部、10d…縦孔、11…メタルパッド、12,202…導電性保護膜、13…絶縁層、14…メタルシード層、15…フォトダイオード、16…オンチップマイクロレンズ、20…センサ部、30…TSV、50…プローブ、100,200…半導体装置

【特許請求の範囲】

【請求項1】

半導体基板、及び、該半導体基板の一方の面上に形成された絶縁膜を有し、内部に該半導体基板の厚さ方向に沿って縦孔が形成された基材部と、

前記縦孔を画成する前記基材部の側壁上に形成された縦孔電極を有する縦孔配線部と、

前記絶縁膜内に形成され、前記縦孔配線部と電気的に接続された金属膜と、

前記絶縁膜内において前記金属膜に接して形成され、かつ、前記金属膜の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成された導電性保護膜と

を備える半導体装置。

【請求項2】

前記金属膜が、前記導電性保護膜の前記半導体基板の側に設けられている

請求項1に記載の半導体装置。

【請求項3】

前記導電性保護膜が、前記金属膜の前記半導体基板の側に設けられている

請求項1に記載の半導体装置。

【請求項4】

前記導電性保護膜が、前記縦孔の開口部と対向する位置に配置されている

請求項1に記載の半導体装置。

【請求項5】

前記絶縁膜の前記プローブの接触側の表面に、前記導電性保護膜が形成された前記プローブの接触領域を含む領域より小さな開口面積の開口部が形成されている

請求項1に記載の半導体装置。

【請求項6】

前記導電性保護膜が、Au膜、Ni膜、及び、Cu膜のいずれかである

請求項1に記載の半導体装置。

【請求項7】

前記導電性保護膜が、W膜、Ti膜、TiN膜及びTi膜の積層膜、並びに、TaN膜及びTa膜の積層膜のいずれかである

請求項1に記載の半導体装置。

【請求項8】

半導体基板、及び、該半導体基板の一方の面上に形成された絶縁膜を有する基材部の該絶縁膜内に金属膜を形成するステップと、

前記絶縁膜内で、かつ、前記金属膜の膜面内の所定領域に、前記金属膜に接して導電性保護膜を形成するステップと、

前記絶縁膜の前記半導体基板の側とは反対側の表面に露出した前記金属膜及び前記導電性保護膜の一方にプローブを接触させてプローバーテストを行うステップと、

前記プローバーテスト後に、前記半導体基板の厚さ方向に沿って、前記基材部に縦孔を形成するステップと

を含む半導体装置の製造方法。

【請求項1】

半導体基板、及び、該半導体基板の一方の面上に形成された絶縁膜を有し、内部に該半導体基板の厚さ方向に沿って縦孔が形成された基材部と、

前記縦孔を画成する前記基材部の側壁上に形成された縦孔電極を有する縦孔配線部と、

前記絶縁膜内に形成され、前記縦孔配線部と電気的に接続された金属膜と、

前記絶縁膜内において前記金属膜に接して形成され、かつ、前記金属膜の膜面において製造途中で行うプローバーテスト時のプローブの接触領域を含む領域に形成された導電性保護膜と

を備える半導体装置。

【請求項2】

前記金属膜が、前記導電性保護膜の前記半導体基板の側に設けられている

請求項1に記載の半導体装置。

【請求項3】

前記導電性保護膜が、前記金属膜の前記半導体基板の側に設けられている

請求項1に記載の半導体装置。

【請求項4】

前記導電性保護膜が、前記縦孔の開口部と対向する位置に配置されている

請求項1に記載の半導体装置。

【請求項5】

前記絶縁膜の前記プローブの接触側の表面に、前記導電性保護膜が形成された前記プローブの接触領域を含む領域より小さな開口面積の開口部が形成されている

請求項1に記載の半導体装置。

【請求項6】

前記導電性保護膜が、Au膜、Ni膜、及び、Cu膜のいずれかである

請求項1に記載の半導体装置。

【請求項7】

前記導電性保護膜が、W膜、Ti膜、TiN膜及びTi膜の積層膜、並びに、TaN膜及びTa膜の積層膜のいずれかである

請求項1に記載の半導体装置。

【請求項8】

半導体基板、及び、該半導体基板の一方の面上に形成された絶縁膜を有する基材部の該絶縁膜内に金属膜を形成するステップと、

前記絶縁膜内で、かつ、前記金属膜の膜面内の所定領域に、前記金属膜に接して導電性保護膜を形成するステップと、

前記絶縁膜の前記半導体基板の側とは反対側の表面に露出した前記金属膜及び前記導電性保護膜の一方にプローブを接触させてプローバーテストを行うステップと、

前記プローバーテスト後に、前記半導体基板の厚さ方向に沿って、前記基材部に縦孔を形成するステップと

を含む半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2012−244100(P2012−244100A)

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願番号】特願2011−115633(P2011−115633)

【出願日】平成23年5月24日(2011.5.24)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年12月10日(2012.12.10)

【国際特許分類】

【出願日】平成23年5月24日(2011.5.24)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]