半導体装置、及びその製造方法、並びに電子情報機器

【課題】シールリング構造を有し、半導体基板の一部を除去した半導体チップにおいて、シールリング構造を構成するプラグが、半導体基板を除去した部分で露出することによる耐湿性の劣化を回避する。

【解決手段】半導体ウエハを分割して得られる半導体チップ100において、半導体基板101上に形成された機能回路を含む回路形成領域Crと、該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造Shとを備え、該シールリング構造Shは、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグ104c及び105cを有し、該シールリング構造を構成する最下層の導電性プラグ104cは、該半導体基板に代わる耐湿材料層102c上に配置されている。

【解決手段】半導体ウエハを分割して得られる半導体チップ100において、半導体基板101上に形成された機能回路を含む回路形成領域Crと、該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造Shとを備え、該シールリング構造Shは、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグ104c及び105cを有し、該シールリング構造を構成する最下層の導電性プラグ104cは、該半導体基板に代わる耐湿材料層102c上に配置されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、及びその製造方法、並びに電子情報機器に関し、特に、Si基板の一部をプロセス途中で除去した構造を有する半導体装置、具体的には、裏面から光を取り込み被写体の撮像を行う、半導体素子で構成された裏面照射型CMOSイメージセンサー等の固体撮像素子としての半導体装置及びその製造方法、並びに、このような固体撮像素子を画像入力デバイスとして撮像部に用いた例えばデジタルビデオカメラ及びデジタルスチルカメラ等のデジタルカメラや、画像入力カメラ、スキャナ、ファクシミリ、カメラ付き携帯電話装置等の電子情報機器に関するものである。

【背景技術】

【0002】

従来から、半導体装置には、基板上にプラグと配線とからなるシールリング構造を耐湿構造として用いたものがある。

【0003】

図8は、このような従来の半導体装置におけるシールリング構造を説明する図であり、図8(a)は平面図、図8(b)は、図8(a)のC−C’線断面図である。

【0004】

図8(a)に示すように、半導体ウェハから切り出された半導体チップ10は、その外周に沿ってシールリング構造(以下、耐湿リングという。)12が形成され、耐湿リング12の内側に回路形成領域A1が配置されている。回路形成領域A1には、図示はしないが、ROM,RAM、ロジック、入出力回路(I/O)などのブロックが形成されている。

【0005】

また、図8(b)に示すように、耐湿リング12は、半導体チップ10の表面領域から、回路素子が形成されている基板に達する深さまで、膜厚方向に延びている。

【0006】

耐湿リング12の内側に位置する回路形成領域A1では、半導体基板(シリコン基板など)11上に、複数の層間絶縁膜14、17、18が積層され、各層において、能動素子、コンタクトプラグ、金属配線などが形成されている。

【0007】

シリコン基板11上で、素子分離領域(例えばLOCOS分離領域)13で区画される領域に、能動素子としてのトランジスタ20が形成され、シリコン基板11に、ソース・ドレイン不純物拡散領域21が形成されている。ここで、素子分離領域は、シリコン基板を部分的に酸化するLOCOS(Local Oxidation of Silicon)法で形成しているが、素子分離領域は、シリコン基板に形成した浅い溝(トレンチ)にシリコン酸化膜を埋め込むSTI(Shallow Trench Isolation)法により形成してもよい。

【0008】

シリコン基板11上に、トランジスタ20を覆って第1の層間絶縁膜14が形成されている。第1の層間絶縁膜14を貫通して、第1層コンタクトプラグ22が膜厚方向に延び、トランジスタ20のソース・ドレイン不純物拡散領域21に接続されている。

【0009】

第1の層間絶縁膜14上には、第1金属配線23が形成されている。第1金属配線23の一部は、第1層コンタクトプラグ22に接続されている。この第1金属配線23を覆って、第2の層間絶縁膜17が形成され、第2の層間絶縁膜17上に、第2金属配線25が形成されている。第2の層間絶縁膜17を貫通して、第2層コンタクトプラグ24が膜厚方向に延び、第2金属配線25と、下層の第1金属配線23とを接続している。

【0010】

第2金属配線25を覆って第3の層間絶縁膜18が形成されている。第3の層間絶縁膜18上には、最上層のメタル電極27が形成されている。メタル電極27は、第3の層間絶縁膜18を貫通する第3層コンタクトプラグ(図示せず)により、下層の第2金属配線25に接続されている。

【0011】

このような回路形成領域A1と、チップ外周に沿ったスクライブ領域(ダイシング領域)C1の間に、耐湿リング12が回路形成領域A1を囲むよう設けられている。耐湿リング12は、積層された層間絶縁膜14、17、18に含まれる、それぞれ膜厚方向に延びる第1導体リング12a、第2導体リング12c、第3導体リング12eを含む。第1導体リング12aと第2導体リング12cを接続する第1リング配線パターン12bが、第1の層間絶縁膜14上に形成されている。第2導体リング12cと第3導体リング12eを接続する第2リング配線パターン12dが、第2の層間絶縁膜17上に形成されている。

【0012】

第1導体リング12aは、シリコン基板11から第1の層間絶縁膜14の膜厚に対応する膜厚方向の寸法を有し、回路形成領域A1を囲むよう形成されている。第1導体リング12aは、回路形成領域A1の第1層コンタクトプラグ22と同じ工程で形成される。第1導体リング12aと第2導体リング12cを接続する第1リング配線パターン12bは、回路形成領域A1の第1金属配線23と同じ工程で形成される。第2導体リング12cは、第2層コンタクトプラグ24と同じ工程で形成され、第2の層間絶縁膜17の膜厚に対応する膜厚方向の寸法を有し、回路形成領域A1を囲むよう形成されている。第3導体リング12eは、第3の層間絶縁膜18の膜厚に対応する膜厚方向の寸法を有し、回路形成領域A1を囲む構造となっており、回路形成領域A1の図示しない第3層コンタクトプラグと同じ工程で形成されたものである。第2導体リング12cと第3導体リング12eを接続する第2リング配線パターン12dは、回路形成領域A1の第2金属配線25と同じ工程で形成される。

【0013】

最上層に位置する第3リング配線パターン12fは、第3導体リング12eに接続されており、回路形成領域A1のメタル電極27と同じ工程で形成されたものである。

【0014】

また、耐湿リングの最上層に位置する第3リング配線パターン12fの表面領域、及びボンディングパッド31(図9参照)の表面領域以外の領域を覆って、保護膜としてのシリコン酸化膜15及びシリコン窒化膜16が順次積層されている。

【0015】

すなわち、第3リング配線パターン12fの表面領域およびボンディングパッド31の表面領域では、シリコン酸化膜15とシリコン窒化膜16が除去され、第3リング配線パターン12f上には開口29が、また、ボンディングパット31上には開口33が形成されている。これらの開口29および31により、シリコン酸化膜15を介した回路形成領域A1への水分の通路が遮断される。

【0016】

さらに、耐湿リング12と回路形成領域A1を覆って、ポリイミド膜19が形成されている。耐湿リング12の第3リング配線パターン12fの表面は、開口29において、直接、非透水性のポリイミド膜19によって被覆される。

【0017】

この構成により、図8(b)に矢印で示すように、耐湿リング12の内側と外側をつなぐ水分の通路を遮断して、耐湿リング12の内部への水分の侵入を防止することができる。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】特開2006−261613号公報

【発明の概要】

【発明が解決しようとする課題】

【0019】

しかし、近年、特に裏面照射型撮像素子では、外部端子と接続するパッド部を露出させる開口の形成のため基板の一部を除去する構造が用いられており、この構造では、チップ周辺にはシリコン基板がなく、上述した従来型のシールリング構造では耐湿性が低下するという問題がある。

【0020】

図10は、このような裏面照射型撮像素子の断面構造を示す図である。

【0021】

図10に示すように、図8に示す回路形成領域Aに相当する領域では、シリコン基板31上に層間絶縁膜34を介して第1金属配線31bが形成され、さらに、その上に第2の層間絶縁膜37を介して第2金属配線36aが形成されている。ここで、第1金属配線31bと基板31に形成された拡散領域や電極とは第1層コンタクトプラグ34bにより接続され、第1金属配線31bと第2金属配線36aとは第2層コンタクトプラグ35bにより接続されている。

【0022】

また、この裏面照射型撮像素子における、図8に示す回路形成領域Aの外側に相当する領域では、層間絶縁膜34上に第1リング配線パターン31cが形成され、さらに、その上に第2の層間絶縁膜37を介して第2リング配線パターン36bが形成されている。ここで、第1リング配線パターン31cと第2リング配線パターン36bとは第2導体リング35cにより接続されている。

【0023】

また、これらの導体リングとリング配線パターンにより耐湿リング32が形成されており、この耐湿リング32と回路形成領域の第1金属配線31bとの間には、ボンディングパッド31aが形成されており、ボンディングパッド31aは第2層コンタクトプラグ35aにより第2金属配線36aに接続されている。また、ボンディングパッド31aにはボンディングワイヤBWが固着されている。なお、図10中、40は支持基板であり、39は耐湿性膜である。

【0024】

このような裏面照射型固体撮像素子10aの構造では、チップ周辺にはシリコン基板31がなく、シールリング構造を構成する第1導体リング34cの下端部が露出した状態となり、この結果、従来型のシールリング構造では耐湿性が低下するという問題がある。

【0025】

本発明は、上記のような問題点を解決するためになされたものであり、シールリング構造を構成するプラグが露出することによる耐湿性の劣化を回避することができる裏面照射型の固体撮像装置などの半導体装置およびその製造方法、並びにこのような固体撮像装置としての半導体装置を用いた電子情報機器を得ることを目的とする。

【課題を解決するための手段】

【0026】

本発明に係る半導体装置は、半導体ウエハを分割して半導体チップとして得られた半導体装置であって、該半導体チップは、半導体基板上に形成された機能回路を含む回路形成領域と、該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造とを備え、該シールリング構造は、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、該シールリング構造を構成する最下層の導電性プラグは、該半導体基板に代わる耐湿材料層上に配置されており、そのことにより上記目的が達成される。

【0027】

本発明は、上記半導体装置において、前記半導体基板の一部を除去した領域における、前記回路形成領域と前記シールリング構造との間の部分には、該回路形成領域の機能回路との電気的接続をとるためのボンディングパッドを構成する導電性層が配置されていることが好ましい。

【0028】

本発明は、上記半導体装置において、前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した素子分離領域上に形成されていることが好ましい。

【0029】

本発明は、上記半導体装置において、前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した多結晶シリコン層であることが好ましい。

【0030】

本発明は、上記半導体装置において、前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した窒化シリコン層であることが好ましい。

【0031】

本発明は、上記半導体装置において、該半導体チップは、多層配線構造を有しており、該シールリング構造は、該多層配線構造を構成する層間絶縁膜を貫通する導電性プラグと、該層間絶縁膜の上下に位置し、該導電性プラグにより接続された配線層とを含むことが好ましい。

【0032】

本発明は、上記半導体装置において、前記半導体チップは、被写体からの光を光電変換して撮像信号を出力する固体撮像素子であり、該固体撮像素子は、前記半導体基板の前記機能回路が形成された表面領域とは反対側の裏面側から光を入射させる裏面照射型固体撮像素子であることが好ましい。

【0033】

本発明は、上記半導体装置において、前記固体撮像素子は、CMOSイメージセンサであることが好ましい。

【0034】

本発明は、上記半導体装置において、前記固体撮像素子は、CCDイメージセンサであることが好ましい。

【0035】

本発明に係る半導体装置の製造方法は、半導体ウエハの、半導体チップとなるチップ領域に機能回路を形成するとともに、該チップ領域の周囲に、該チップ領域に該機能回路への水分の侵入が阻止されるシールリング構造を形成し、該チップ領域を半導体チップとして分割して半導体装置を製造する方法であって、該半導体ウエハを構成する半導体基板上に、該チップ領域が分離されるよう素子分離領域を形成するステップと、該チップ領域内の回路形成領域に半導体素子を形成するステップと、該半導体基板上に該絶縁膜を形成するステップと、該絶縁膜に形成した開口内に導電性プラグを形成するステップと、該絶縁膜上に配線層を形成するステップと、該半導体基板の、該シールリング構造に対向する部分の領域を除去するステップとを含み、該シールリング構造は、該絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、該半導体素子を形成するステップでは、該機能回路の電極を構成する導電材料の一部を、該素子分離領域上に耐湿材料層として形成し、該導電性プラグを形成するステップでは、該耐湿材料層上に該シールリング構造を構成する導電性プラグを形成するものであり、そのことにより上記目的が達成される。

【0036】

本発明に係る電子情報機器は、被写体の撮像を行う撮像部を備えた電子情報機器であって、該撮像部は、上述した固体撮像素子としての半導体装置を備えたものであり、そのことにより上記目的が達成される。

【0037】

次に作用について説明する。

【0038】

本発明においては、半導体ウエハを分割して半導体チップとして得られた半導体装置において、半導体基板上に形成された機能回路を含む回路形成領域と、該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造とを備え、該シールリング構造は、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、該シールリング構造を構成する最下層の導電性プラグを、該半導体基板に代わる耐湿材料層上に配置しているので、シールリング構造を有する、半導体基板の一部を除去した半導体チップにおいて、シールリング構造を構成するプラグが、半導体基板を除去した部分で露出することによる耐湿性の劣化を回避することができる。

【発明の効果】

【0039】

以上のように、本発明によれば、シリコン基板の、ボンディングための除去する部分には、この部分を除去する前に該シリコン基板上に多結晶シリコン層を形成しておくので、シールリング構造が該多結晶シリコン層上に形成されることとなり、シールリング構造を構成するプラグが露出することによる耐湿性の劣化を回避することができる効果がある。

【図面の簡単な説明】

【0040】

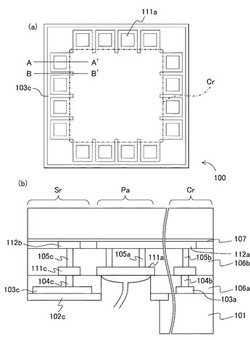

【図1】図1は、本発明の実施形態1による半導体装置を説明する図であり、図1(a)は平面図、図1(b)は、図1(a)のA−A’部分の断面図である。

【図2】図2は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図2(a))及びB−B’線部分の断面構造(図2(b))を用いて説明する図であり、半導体基板の表面に素子分離領域及び機能回路を形成する工程を示している。

【図3】図3は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図3(a))及びB−B’線部分の断面構造(図3(b))を用いて説明する図であり、半導体基板の表面に第1層絶縁膜、第1層導電性プラグ、及び第1層配線を形成する工程を示している。

【図4】図4は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図4(a))及びB−B’線部分の断面構造(図4(b))を用いて説明する図であり、半導体基板の表面に第2層絶縁膜、第2層導電性プラグ、第2層配線を形成する工程を示している。

【図5】図5は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図5(a))及びB−B’線部分の断面構造(図5(b))を用いて説明する図であり、半導体基板の表面側に支持基板を貼り付け、半導体基板の一部を除去する工程を示している。

【図6】図6は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図6(a))及びB−B’線部分の断面構造(図6(b))を用いて説明する図であり、半導体基板の裏面にボンディングパッドとなる導体層を露出させてボンディングを行う工程を示している。

【図7】図7は、本発明の実施形態2として、実施形態1の固体撮像装置を撮像部に用いた電子情報機器の概略構成例を示すブロック図である。

【図8】図8は、従来の半導体装置におけるシールリング構造を説明する図であり、図8(a)は平面図、図8(b)は、図8(a)のB−B’線断面図である。

【図9】上記従来の半導体装置におけるボンディングパッド部分の構造を示す断面図である。

【図10】図10は、上記半導体装置におけるシールリング構造を有する裏面照射型撮像素子の断面構造を示す図である。

【発明を実施するための形態】

【0041】

以下、本発明の実施形態について図面を参照しながら説明する。

【0042】

(実施形態1)

図1は、本発明の実施形態1による半導体装置を説明する図であり、図1(a)は平面図、図1(b)は、図1(a)のA−A’部分の断面図である。

【0043】

この実施形態1の半導体装置100は、半導体ウエハを分割して半導体チップ100として得られたものである。ここで、この半導体チップ100は、シリコン基板などの半導体基板101上に形成された機能回路を含む回路形成領域Crと、該回路形成領域Crの周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域Crへの水分の侵入が阻止されるよう形成されたシールリング構造Shとを備えている。

【0044】

このシールリング構造Shは、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有している。該シールリング構造Shを構成する最下層の導電性プラグ104cは、該半導体基板に代わる耐湿材料層103c上に配置されている。

【0045】

ここで、回路形成領域Crは、半導体基板101上で、絶縁材料からなる素子分離領域102cにより電気的に分離されており、この領域Crには、機能回路を構成する半導体素子が形成されている。例えば、半導体チップが裏面照射型CMOSイメージセンサである場合には、該機能回路は、図6に示すように、入射光の光電変換により信号電荷を生成する受光部PD(フォトダイオード)、受光部PDで生成された信号電荷をフォローティングディフュージョンとしての拡散領域(FD領域)101cに読み出す読み出し部Rと、FD領域101cに読み出された信号電荷を増幅する増幅部(増幅回路)Amとを有するものとなる。

【0046】

具体的には、上記受光部PDは、例えば、P型シリコン基板、あるいはN型シリコン基板に形成されたP型ウエルに形成されたN型拡散領域101dにより構成されたフォトダイオードである。また、FD領域101cはN型拡散領域であり、フォトダイオードを構成する拡散領域101dとFD領域101cとの間には、ゲート絶縁膜を介して転送電極103aが配置されている。

【0047】

また、増幅部Amは、P型シリコン基板101上の表面領域にソース領域101a及びドレイン領域101bとして形成されたN型拡散領域と、これらの領域の間の部分にゲート絶縁膜を介して形成された増幅ゲート103aとを有する増幅トランジスタを含んでいる。

【0048】

なお、増幅トランジスタの、FD領域101cに隣接する拡散領域101aは、該FD領域101cとは、素子分離領域102aにより電気的に分離されている(図6(a)及び(b))。

【0049】

ただし、このような図6(a)及び図6(b)に示す断面構造は、受光部PDの周囲の一部、つまり受光部PDを構成するフォトダイオード、読み出し部Rを構成する転送電極、FD領域101c、及び増幅部Amを構成する増幅トランジスタが並んでいる方向におけるものであり、その他の方向の断面構造、例えば、図6(a)及び図6(b)に示す断面と直交する断面の構造では、受光部PDを構成するフォトダイオード(N型拡散領域)が素子分離領域により囲まれた構造となっている。また、このような素子分離領域には、LOCOS法で形成したLOCOS分離領域やSTI法で形成したSTI分離領域ではなく、P型不純物領域を用いる場合もある。

【0050】

そして、転送電極103aには、その上に形成された絶縁膜106aを貫通する第1層コンタクトプラグ104b、第1層接続配線111b、第2層コンタクトプラグ105bを介して第2層接続配線112aに接続されている。また、この第2層接続配線112aは第2層コンタクトプラグ105aを介してボンディングパッドとしての配線層111aに接続されている。このボンディングパッド111aにはボンディングワイヤBWが固着されている。

【0051】

また、シールリング構造Shは、半導体基板101の、このシールリング構造Shに対向する部分を除去する前に半導体基板表面の素子分離領域102c上に形成した耐湿性材料層103c上に形成されている。耐湿性材料層103cとしては多結晶シリコン層が用いられる。ただし、耐湿性材料層103cは多結晶シリコン層に限定されるものではなく、耐湿性材料層103cとしてシリコン窒化膜を用いることができる。なお、多結晶シリコン層を用いた場合は、素子分離領域との密着性を高いものとすることができる。

【0052】

具体的には、シールリング構造Shは、該耐湿性材料層103cとしての多結晶シリコン膜上に形成された第1リング状シールプラグ104c、該第1リング状シールプラグ104c上に形成された第1リング状シール配線111c、該第1シール配線111c上に形成された第2リング状シールプラグ105c、及び該第2リング状シールプラグ105c上に形成された第2リング状シール配線112dを有している。

【0053】

また、ここでは、配線構造として、配線層は2層に形成されている多層配線構造を示しているが、配線構造は3層以上の多層配線構造でも単層構造でもよい。

【0054】

また、この固体撮像素子100は、CMOSイメージセンサに限定されるものではなく、CCDイメージセンサであってもよい。

【0055】

なお、プラグとしてはタングステンなどの金属材料を用い、配線としてはアルミや銅などの金属材料を用いることができ、また、層間絶縁膜などの絶縁膜にはシリコン酸化膜を用いることができる。ただし、層間絶縁膜には、シリコン酸化膜や、例えばエッチングストッパ層として用いられるシリコン酸窒化膜、シリコン窒化膜などとの積層膜を用いることができる。

【0056】

次に製造方法について説明する。

【0057】

この実施形態1では、半導体装置の製造方法の一例として、裏面照射型CMOSイメージセンサを半導体ウエハの各チップ領域に形成し、その後各チップ領域を半導体チップとして切り出す例を説明する。

【0058】

P型シリコン基板101の表面領域に素子分離領域102a及び102cを形成する。このとき、素子分離領域102aは、回路形成領域Crにおける、機能回路を構成する半導体素子間を電気的に分離する分離領域であり、また、素子分離領域102cは、シールリング構造Shが形成される領域に形成される。

【0059】

その後、回路形成領域Crでは、熱酸化などによりゲート絶縁膜を形成した後、ゲート電極材料の多結晶シリコン膜のパターニングにより、電荷読み出し部の転送電極としてのゲート電極103a、及び増幅回路としての増幅トランジスタを構成するゲート電極103bを形成する。このとき、回路形成領域Crの周辺の領域(シールリング構造Shの形成領域)では、素子分離領域102c上に、耐湿性材料層として多結晶シリコン層103cが形成される。

【0060】

なお、シールリング構造の形成領域における多結晶シリコン膜103cは、工程簡略のため、電荷読み出し部の転送電極としての多結晶シリコン膜と同一に形成しているが、別途形成してもかまわない。

【0061】

続いて、シリコン基板の各チップ領域の回路形成領域Crでは、不純物のイオン注入によりフォトダイオードを構成するN型拡散領域101b、フローティングディフュージョンとしてのN型拡散領域101c、さらに、増幅トランジスタのソース、ドレイン領域としてのN型拡散領域101a及び101bを形成する(図2(a)、(b))。

【0062】

次に、1層目の層間絶縁膜として、第1層絶縁膜106aを全面に形成し、その後、該第1層絶縁膜106aの、転送電極103a上の部分、及びシールリング構造Shを形成すべき領域に開口を選択的に形成し、それぞれの開口に第1層コンタクトプラグ104b、及び第1リング状シールプラグ104cを埋め込む(図3(a)、(b))。

【0063】

その後、転送電極103a上に配線層111bを形成するとともに、ボンディングパッドを配置する領域に、該ボンディングパッドとして配線層111aを形成し、さらに、耐湿性材料層103c上にリング状シール配線111cを形成する。

【0064】

次に、2層目の層間絶縁膜として、第2層絶縁膜106bを全面に形成し、その後、該第2層絶縁膜106aの、転送電極103a上の部分、ボンディングパッドとしての配線層111a上の部分、及びシールリング構造を形成するリング状シール配線111c上の部分に開口を選択的に形成し、それぞれの開口に、第2層コンタクトプラグ105b、第2層コンタクトプラグ105a及び第2層リング状シールプラグ105cを埋め込む(図4(a)、(b))。

【0065】

次に、第2層絶縁膜106b上に、第2層コンタクトプラグ105bに接続され、かつ、ボンディングパッドとしての配線層111a上のコンタクトプラグ105aに接続されるよう配線層112aを形成し、また、シールリング構造Shの形成領域では、リング状シールプラグ105cに接続されるようリング状シール配線112dを形成する。

【0066】

なお、ここでは、2層配線構造としているが、さらに多層の配線構造を形成する場合は、多層配線層の必要な工程だけ、プラグ、配線の形成を行う。

【0067】

また、上述したように、絶縁膜に埋め込むプラグ部材はタングステンなどの金属材料を用いることができ、埋め込む前には、予め開口内の底面及び側面に下層のチタン及び上層の窒化チタンの2層構造の膜を形成しておくことが好ましい。

【0068】

その後、最上層の絶縁膜として、該配線層112a及び112dを埋め込むよう絶縁膜106cを形成し、さらにその上に耐湿膜として窒化シリコン膜107を形成し、該耐湿膜の表面に支持基板201を貼り付ける。

【0069】

また、この実施形態では、最上層の配線層112a及び112dに耐湿膜としての窒化シリコン膜を直付けしているが、通常のプロセスでは、最上層の配線層112a及び112dを形成した後、これらの配線層を覆うよう全面にCVD法などにより酸化膜を堆積し、その後、酸化膜をその表面が平坦になるよう研磨する。このとき、この酸化膜の研磨は、最上層の配線層の表面が露出した時点で停止するのは難しいため、酸化膜が配線層112a及び112d上に若干残る状態で止める。その後、全面に耐湿膜としての窒化シリコン膜107を形成する。この場合、支持基板に貼り付ける耐湿膜の表面の平坦性が確保されるため、支持基板201との密着性を高めることができるが、シーリング構造Shとしては、最上層の配線層112a及び112dとその上の耐湿膜107との間に酸化膜が介在する構造よりは、最上層の配線層112a及び112d上に耐湿膜107が配線層としてのアルミ層と直付けされている構造の方が、高いシール効果が得られることから望ましい。

【0070】

このように支持基板201に貼り付けた後、シリコン基板の配線層を形成した表現側とは反対側の裏面に、シリコン基板が所望の膜厚になるまで研磨あるいはエッチングなどの処理を施して、シリコン基板を薄膜化し、その後、シリコン基板101の、回路形成領域Crの外側の、ボンディングパッドが配置されている部分を除去する(図5(a)、(b))。

【0071】

さらに、シリコン基板101の、ボンディングパッドとしての配線層111aが露出するよう、該シリコン基板の裏面側を選択的にエッチングする。その後、露出したボンディングパッドとしての配線層111aにボンディングワイヤBWを固着する。これにより、固体撮像素子としての半導体チップと外部の回路との接続がなされる(図6(a)、(b))。

【0072】

このように本実施形態による半導体チップ100では、シリコン基板の、ワイヤボンディングが可能となるように除去する部分には、この部分を除去する前に該シリコン基板上に多結晶シリコン層を形成しておくので、シールリング構造が該多結晶シリコン層Sh上に形成されることとなり、シールリング構造Shを構成するプラグ104cが露出することによる耐湿性の劣化を回避することができる。

【0073】

つまり、近年撮像素子に使われてきている裏面照射型撮像素子では、基板シリコンの裏面の一部を除去する工程により、レイアウトによっては、シールリング構造の下側に基板が存在しない形状となり、この結果、従来構造のシールリング構造では耐湿性を維持できない場合がある。

【0074】

これに対し、本発明の実施形態1の半導体装置100は、シリコン基板を除去する構造を持つ半導体装置、特には、裏面照射型撮像素子100において、シールリング構造Shの下地となる多結晶シリコン層103cなどを形成しているので、シリコン基板101が無くても耐湿性を維持するシールリング構造が形成可能となる。

【0075】

さらに、上記実施形態1では、特に説明しなかったが、上記実施形態1の固体撮像素子を撮像部に用いた、例えばデジタルビデオカメラ、デジタルスチルカメラなどのデジタルカメラや、画像入力カメラ、スキャナ、ファクシミリ、カメラ付き携帯電話装置などの、画像入力デバイスを有した電子情報機器について以下簡単に説明する。

(実施形態2)

図7は、本発明の実施形態2として、実施形態1の固体撮像装置を撮像部に用いた電子情報機器の概略構成例を示すブロック図である。

【0076】

図7に示す本発明の実施形態2による電子情報機器90は、本発明の上記実施形態1の半導体装置を、被写体の撮影を行う撮像部91として備えたものであり、このような撮像部による撮影により得られた高品位な画像データを記録用に所定の信号処理した後にデータ記録する記録メディアなどのメモリ部92と、この画像データを表示用に所定の信号処理した後に液晶表示画面などの表示画面上に表示する液晶表示装置などの表示部93と、この画像データを通信用に所定の信号処理をした後に通信処理する送受信装置などの通信部94と、この画像データを印刷(印字)して出力(プリントアウト)する画像出力部95とのうちの少なくともいずれかを有している。

【0077】

以上のように、本発明の好ましい実施形態を用いて本発明を例示してきたが、本発明は、この実施形態に限定して解釈されるべきものではない。本発明は、特許請求の範囲によってのみその範囲が解釈されるべきであることが理解される。当業者は、本発明の具体的な好ましい実施形態の記載から、本発明の記載および技術常識に基づいて等価な範囲を実施することができることが理解される。本明細書において引用した特許文献は、その内容自体が具体的に本明細書に記載されているのと同様にその内容が本明細書に対する参考として援用されるべきであることが理解される。

【産業上の利用可能性】

【0078】

本発明は、半導体装置、及びその製造方法、並びに電子情報機器の分野において、シールリング構造を構成するプラグが露出することによる耐湿性の劣化を回避することができる固体撮像装置などの半導体装置およびその製造方法、並びにこのような半導体装置を用いた電子情報機器を得ることができる。

【符号の説明】

【0079】

90 電子情報機器

91 撮像部

92 メモリ部

93 表示手段

94 通信手段

95 画像出力手段

100 半導体装置(半導体チップ)

101 半導体基板

101c 拡散領域(FD領域)

101d N型拡散領域

102a、102c 素子分離領域

103a 転送電極

103b 増幅ゲート

103c 耐湿性材料層

104b 第1層コンタクトプラグ

104c 第1リング状シールプラグ

105a、105b 第2層コンタクトプラグ

105c 第2リング状シールプラグ

106a、106b 絶縁膜

111a 配線層(ボンディングパッド)

111b 第1層金属配線

111c 第1リング状シール配線

112a 第2層金属配線

112b 第2リング状シール配線

113a ソース領域

113b ドレイン領域

Am 増幅部(増幅回路)

BW ボンディングワイヤ

Cr 回路形成領域

PD 受光部

R 読み出し部

Sh シールリング構造

【技術分野】

【0001】

本発明は、半導体装置、及びその製造方法、並びに電子情報機器に関し、特に、Si基板の一部をプロセス途中で除去した構造を有する半導体装置、具体的には、裏面から光を取り込み被写体の撮像を行う、半導体素子で構成された裏面照射型CMOSイメージセンサー等の固体撮像素子としての半導体装置及びその製造方法、並びに、このような固体撮像素子を画像入力デバイスとして撮像部に用いた例えばデジタルビデオカメラ及びデジタルスチルカメラ等のデジタルカメラや、画像入力カメラ、スキャナ、ファクシミリ、カメラ付き携帯電話装置等の電子情報機器に関するものである。

【背景技術】

【0002】

従来から、半導体装置には、基板上にプラグと配線とからなるシールリング構造を耐湿構造として用いたものがある。

【0003】

図8は、このような従来の半導体装置におけるシールリング構造を説明する図であり、図8(a)は平面図、図8(b)は、図8(a)のC−C’線断面図である。

【0004】

図8(a)に示すように、半導体ウェハから切り出された半導体チップ10は、その外周に沿ってシールリング構造(以下、耐湿リングという。)12が形成され、耐湿リング12の内側に回路形成領域A1が配置されている。回路形成領域A1には、図示はしないが、ROM,RAM、ロジック、入出力回路(I/O)などのブロックが形成されている。

【0005】

また、図8(b)に示すように、耐湿リング12は、半導体チップ10の表面領域から、回路素子が形成されている基板に達する深さまで、膜厚方向に延びている。

【0006】

耐湿リング12の内側に位置する回路形成領域A1では、半導体基板(シリコン基板など)11上に、複数の層間絶縁膜14、17、18が積層され、各層において、能動素子、コンタクトプラグ、金属配線などが形成されている。

【0007】

シリコン基板11上で、素子分離領域(例えばLOCOS分離領域)13で区画される領域に、能動素子としてのトランジスタ20が形成され、シリコン基板11に、ソース・ドレイン不純物拡散領域21が形成されている。ここで、素子分離領域は、シリコン基板を部分的に酸化するLOCOS(Local Oxidation of Silicon)法で形成しているが、素子分離領域は、シリコン基板に形成した浅い溝(トレンチ)にシリコン酸化膜を埋め込むSTI(Shallow Trench Isolation)法により形成してもよい。

【0008】

シリコン基板11上に、トランジスタ20を覆って第1の層間絶縁膜14が形成されている。第1の層間絶縁膜14を貫通して、第1層コンタクトプラグ22が膜厚方向に延び、トランジスタ20のソース・ドレイン不純物拡散領域21に接続されている。

【0009】

第1の層間絶縁膜14上には、第1金属配線23が形成されている。第1金属配線23の一部は、第1層コンタクトプラグ22に接続されている。この第1金属配線23を覆って、第2の層間絶縁膜17が形成され、第2の層間絶縁膜17上に、第2金属配線25が形成されている。第2の層間絶縁膜17を貫通して、第2層コンタクトプラグ24が膜厚方向に延び、第2金属配線25と、下層の第1金属配線23とを接続している。

【0010】

第2金属配線25を覆って第3の層間絶縁膜18が形成されている。第3の層間絶縁膜18上には、最上層のメタル電極27が形成されている。メタル電極27は、第3の層間絶縁膜18を貫通する第3層コンタクトプラグ(図示せず)により、下層の第2金属配線25に接続されている。

【0011】

このような回路形成領域A1と、チップ外周に沿ったスクライブ領域(ダイシング領域)C1の間に、耐湿リング12が回路形成領域A1を囲むよう設けられている。耐湿リング12は、積層された層間絶縁膜14、17、18に含まれる、それぞれ膜厚方向に延びる第1導体リング12a、第2導体リング12c、第3導体リング12eを含む。第1導体リング12aと第2導体リング12cを接続する第1リング配線パターン12bが、第1の層間絶縁膜14上に形成されている。第2導体リング12cと第3導体リング12eを接続する第2リング配線パターン12dが、第2の層間絶縁膜17上に形成されている。

【0012】

第1導体リング12aは、シリコン基板11から第1の層間絶縁膜14の膜厚に対応する膜厚方向の寸法を有し、回路形成領域A1を囲むよう形成されている。第1導体リング12aは、回路形成領域A1の第1層コンタクトプラグ22と同じ工程で形成される。第1導体リング12aと第2導体リング12cを接続する第1リング配線パターン12bは、回路形成領域A1の第1金属配線23と同じ工程で形成される。第2導体リング12cは、第2層コンタクトプラグ24と同じ工程で形成され、第2の層間絶縁膜17の膜厚に対応する膜厚方向の寸法を有し、回路形成領域A1を囲むよう形成されている。第3導体リング12eは、第3の層間絶縁膜18の膜厚に対応する膜厚方向の寸法を有し、回路形成領域A1を囲む構造となっており、回路形成領域A1の図示しない第3層コンタクトプラグと同じ工程で形成されたものである。第2導体リング12cと第3導体リング12eを接続する第2リング配線パターン12dは、回路形成領域A1の第2金属配線25と同じ工程で形成される。

【0013】

最上層に位置する第3リング配線パターン12fは、第3導体リング12eに接続されており、回路形成領域A1のメタル電極27と同じ工程で形成されたものである。

【0014】

また、耐湿リングの最上層に位置する第3リング配線パターン12fの表面領域、及びボンディングパッド31(図9参照)の表面領域以外の領域を覆って、保護膜としてのシリコン酸化膜15及びシリコン窒化膜16が順次積層されている。

【0015】

すなわち、第3リング配線パターン12fの表面領域およびボンディングパッド31の表面領域では、シリコン酸化膜15とシリコン窒化膜16が除去され、第3リング配線パターン12f上には開口29が、また、ボンディングパット31上には開口33が形成されている。これらの開口29および31により、シリコン酸化膜15を介した回路形成領域A1への水分の通路が遮断される。

【0016】

さらに、耐湿リング12と回路形成領域A1を覆って、ポリイミド膜19が形成されている。耐湿リング12の第3リング配線パターン12fの表面は、開口29において、直接、非透水性のポリイミド膜19によって被覆される。

【0017】

この構成により、図8(b)に矢印で示すように、耐湿リング12の内側と外側をつなぐ水分の通路を遮断して、耐湿リング12の内部への水分の侵入を防止することができる。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】特開2006−261613号公報

【発明の概要】

【発明が解決しようとする課題】

【0019】

しかし、近年、特に裏面照射型撮像素子では、外部端子と接続するパッド部を露出させる開口の形成のため基板の一部を除去する構造が用いられており、この構造では、チップ周辺にはシリコン基板がなく、上述した従来型のシールリング構造では耐湿性が低下するという問題がある。

【0020】

図10は、このような裏面照射型撮像素子の断面構造を示す図である。

【0021】

図10に示すように、図8に示す回路形成領域Aに相当する領域では、シリコン基板31上に層間絶縁膜34を介して第1金属配線31bが形成され、さらに、その上に第2の層間絶縁膜37を介して第2金属配線36aが形成されている。ここで、第1金属配線31bと基板31に形成された拡散領域や電極とは第1層コンタクトプラグ34bにより接続され、第1金属配線31bと第2金属配線36aとは第2層コンタクトプラグ35bにより接続されている。

【0022】

また、この裏面照射型撮像素子における、図8に示す回路形成領域Aの外側に相当する領域では、層間絶縁膜34上に第1リング配線パターン31cが形成され、さらに、その上に第2の層間絶縁膜37を介して第2リング配線パターン36bが形成されている。ここで、第1リング配線パターン31cと第2リング配線パターン36bとは第2導体リング35cにより接続されている。

【0023】

また、これらの導体リングとリング配線パターンにより耐湿リング32が形成されており、この耐湿リング32と回路形成領域の第1金属配線31bとの間には、ボンディングパッド31aが形成されており、ボンディングパッド31aは第2層コンタクトプラグ35aにより第2金属配線36aに接続されている。また、ボンディングパッド31aにはボンディングワイヤBWが固着されている。なお、図10中、40は支持基板であり、39は耐湿性膜である。

【0024】

このような裏面照射型固体撮像素子10aの構造では、チップ周辺にはシリコン基板31がなく、シールリング構造を構成する第1導体リング34cの下端部が露出した状態となり、この結果、従来型のシールリング構造では耐湿性が低下するという問題がある。

【0025】

本発明は、上記のような問題点を解決するためになされたものであり、シールリング構造を構成するプラグが露出することによる耐湿性の劣化を回避することができる裏面照射型の固体撮像装置などの半導体装置およびその製造方法、並びにこのような固体撮像装置としての半導体装置を用いた電子情報機器を得ることを目的とする。

【課題を解決するための手段】

【0026】

本発明に係る半導体装置は、半導体ウエハを分割して半導体チップとして得られた半導体装置であって、該半導体チップは、半導体基板上に形成された機能回路を含む回路形成領域と、該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造とを備え、該シールリング構造は、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、該シールリング構造を構成する最下層の導電性プラグは、該半導体基板に代わる耐湿材料層上に配置されており、そのことにより上記目的が達成される。

【0027】

本発明は、上記半導体装置において、前記半導体基板の一部を除去した領域における、前記回路形成領域と前記シールリング構造との間の部分には、該回路形成領域の機能回路との電気的接続をとるためのボンディングパッドを構成する導電性層が配置されていることが好ましい。

【0028】

本発明は、上記半導体装置において、前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した素子分離領域上に形成されていることが好ましい。

【0029】

本発明は、上記半導体装置において、前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した多結晶シリコン層であることが好ましい。

【0030】

本発明は、上記半導体装置において、前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した窒化シリコン層であることが好ましい。

【0031】

本発明は、上記半導体装置において、該半導体チップは、多層配線構造を有しており、該シールリング構造は、該多層配線構造を構成する層間絶縁膜を貫通する導電性プラグと、該層間絶縁膜の上下に位置し、該導電性プラグにより接続された配線層とを含むことが好ましい。

【0032】

本発明は、上記半導体装置において、前記半導体チップは、被写体からの光を光電変換して撮像信号を出力する固体撮像素子であり、該固体撮像素子は、前記半導体基板の前記機能回路が形成された表面領域とは反対側の裏面側から光を入射させる裏面照射型固体撮像素子であることが好ましい。

【0033】

本発明は、上記半導体装置において、前記固体撮像素子は、CMOSイメージセンサであることが好ましい。

【0034】

本発明は、上記半導体装置において、前記固体撮像素子は、CCDイメージセンサであることが好ましい。

【0035】

本発明に係る半導体装置の製造方法は、半導体ウエハの、半導体チップとなるチップ領域に機能回路を形成するとともに、該チップ領域の周囲に、該チップ領域に該機能回路への水分の侵入が阻止されるシールリング構造を形成し、該チップ領域を半導体チップとして分割して半導体装置を製造する方法であって、該半導体ウエハを構成する半導体基板上に、該チップ領域が分離されるよう素子分離領域を形成するステップと、該チップ領域内の回路形成領域に半導体素子を形成するステップと、該半導体基板上に該絶縁膜を形成するステップと、該絶縁膜に形成した開口内に導電性プラグを形成するステップと、該絶縁膜上に配線層を形成するステップと、該半導体基板の、該シールリング構造に対向する部分の領域を除去するステップとを含み、該シールリング構造は、該絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、該半導体素子を形成するステップでは、該機能回路の電極を構成する導電材料の一部を、該素子分離領域上に耐湿材料層として形成し、該導電性プラグを形成するステップでは、該耐湿材料層上に該シールリング構造を構成する導電性プラグを形成するものであり、そのことにより上記目的が達成される。

【0036】

本発明に係る電子情報機器は、被写体の撮像を行う撮像部を備えた電子情報機器であって、該撮像部は、上述した固体撮像素子としての半導体装置を備えたものであり、そのことにより上記目的が達成される。

【0037】

次に作用について説明する。

【0038】

本発明においては、半導体ウエハを分割して半導体チップとして得られた半導体装置において、半導体基板上に形成された機能回路を含む回路形成領域と、該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造とを備え、該シールリング構造は、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、該シールリング構造を構成する最下層の導電性プラグを、該半導体基板に代わる耐湿材料層上に配置しているので、シールリング構造を有する、半導体基板の一部を除去した半導体チップにおいて、シールリング構造を構成するプラグが、半導体基板を除去した部分で露出することによる耐湿性の劣化を回避することができる。

【発明の効果】

【0039】

以上のように、本発明によれば、シリコン基板の、ボンディングための除去する部分には、この部分を除去する前に該シリコン基板上に多結晶シリコン層を形成しておくので、シールリング構造が該多結晶シリコン層上に形成されることとなり、シールリング構造を構成するプラグが露出することによる耐湿性の劣化を回避することができる効果がある。

【図面の簡単な説明】

【0040】

【図1】図1は、本発明の実施形態1による半導体装置を説明する図であり、図1(a)は平面図、図1(b)は、図1(a)のA−A’部分の断面図である。

【図2】図2は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図2(a))及びB−B’線部分の断面構造(図2(b))を用いて説明する図であり、半導体基板の表面に素子分離領域及び機能回路を形成する工程を示している。

【図3】図3は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図3(a))及びB−B’線部分の断面構造(図3(b))を用いて説明する図であり、半導体基板の表面に第1層絶縁膜、第1層導電性プラグ、及び第1層配線を形成する工程を示している。

【図4】図4は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図4(a))及びB−B’線部分の断面構造(図4(b))を用いて説明する図であり、半導体基板の表面に第2層絶縁膜、第2層導電性プラグ、第2層配線を形成する工程を示している。

【図5】図5は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図5(a))及びB−B’線部分の断面構造(図5(b))を用いて説明する図であり、半導体基板の表面側に支持基板を貼り付け、半導体基板の一部を除去する工程を示している。

【図6】図6は、本発明の実施形態1による半導体装置を製造する方法を、図1(a)のA−A’線部分の断面構造(図6(a))及びB−B’線部分の断面構造(図6(b))を用いて説明する図であり、半導体基板の裏面にボンディングパッドとなる導体層を露出させてボンディングを行う工程を示している。

【図7】図7は、本発明の実施形態2として、実施形態1の固体撮像装置を撮像部に用いた電子情報機器の概略構成例を示すブロック図である。

【図8】図8は、従来の半導体装置におけるシールリング構造を説明する図であり、図8(a)は平面図、図8(b)は、図8(a)のB−B’線断面図である。

【図9】上記従来の半導体装置におけるボンディングパッド部分の構造を示す断面図である。

【図10】図10は、上記半導体装置におけるシールリング構造を有する裏面照射型撮像素子の断面構造を示す図である。

【発明を実施するための形態】

【0041】

以下、本発明の実施形態について図面を参照しながら説明する。

【0042】

(実施形態1)

図1は、本発明の実施形態1による半導体装置を説明する図であり、図1(a)は平面図、図1(b)は、図1(a)のA−A’部分の断面図である。

【0043】

この実施形態1の半導体装置100は、半導体ウエハを分割して半導体チップ100として得られたものである。ここで、この半導体チップ100は、シリコン基板などの半導体基板101上に形成された機能回路を含む回路形成領域Crと、該回路形成領域Crの周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域Crへの水分の侵入が阻止されるよう形成されたシールリング構造Shとを備えている。

【0044】

このシールリング構造Shは、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有している。該シールリング構造Shを構成する最下層の導電性プラグ104cは、該半導体基板に代わる耐湿材料層103c上に配置されている。

【0045】

ここで、回路形成領域Crは、半導体基板101上で、絶縁材料からなる素子分離領域102cにより電気的に分離されており、この領域Crには、機能回路を構成する半導体素子が形成されている。例えば、半導体チップが裏面照射型CMOSイメージセンサである場合には、該機能回路は、図6に示すように、入射光の光電変換により信号電荷を生成する受光部PD(フォトダイオード)、受光部PDで生成された信号電荷をフォローティングディフュージョンとしての拡散領域(FD領域)101cに読み出す読み出し部Rと、FD領域101cに読み出された信号電荷を増幅する増幅部(増幅回路)Amとを有するものとなる。

【0046】

具体的には、上記受光部PDは、例えば、P型シリコン基板、あるいはN型シリコン基板に形成されたP型ウエルに形成されたN型拡散領域101dにより構成されたフォトダイオードである。また、FD領域101cはN型拡散領域であり、フォトダイオードを構成する拡散領域101dとFD領域101cとの間には、ゲート絶縁膜を介して転送電極103aが配置されている。

【0047】

また、増幅部Amは、P型シリコン基板101上の表面領域にソース領域101a及びドレイン領域101bとして形成されたN型拡散領域と、これらの領域の間の部分にゲート絶縁膜を介して形成された増幅ゲート103aとを有する増幅トランジスタを含んでいる。

【0048】

なお、増幅トランジスタの、FD領域101cに隣接する拡散領域101aは、該FD領域101cとは、素子分離領域102aにより電気的に分離されている(図6(a)及び(b))。

【0049】

ただし、このような図6(a)及び図6(b)に示す断面構造は、受光部PDの周囲の一部、つまり受光部PDを構成するフォトダイオード、読み出し部Rを構成する転送電極、FD領域101c、及び増幅部Amを構成する増幅トランジスタが並んでいる方向におけるものであり、その他の方向の断面構造、例えば、図6(a)及び図6(b)に示す断面と直交する断面の構造では、受光部PDを構成するフォトダイオード(N型拡散領域)が素子分離領域により囲まれた構造となっている。また、このような素子分離領域には、LOCOS法で形成したLOCOS分離領域やSTI法で形成したSTI分離領域ではなく、P型不純物領域を用いる場合もある。

【0050】

そして、転送電極103aには、その上に形成された絶縁膜106aを貫通する第1層コンタクトプラグ104b、第1層接続配線111b、第2層コンタクトプラグ105bを介して第2層接続配線112aに接続されている。また、この第2層接続配線112aは第2層コンタクトプラグ105aを介してボンディングパッドとしての配線層111aに接続されている。このボンディングパッド111aにはボンディングワイヤBWが固着されている。

【0051】

また、シールリング構造Shは、半導体基板101の、このシールリング構造Shに対向する部分を除去する前に半導体基板表面の素子分離領域102c上に形成した耐湿性材料層103c上に形成されている。耐湿性材料層103cとしては多結晶シリコン層が用いられる。ただし、耐湿性材料層103cは多結晶シリコン層に限定されるものではなく、耐湿性材料層103cとしてシリコン窒化膜を用いることができる。なお、多結晶シリコン層を用いた場合は、素子分離領域との密着性を高いものとすることができる。

【0052】

具体的には、シールリング構造Shは、該耐湿性材料層103cとしての多結晶シリコン膜上に形成された第1リング状シールプラグ104c、該第1リング状シールプラグ104c上に形成された第1リング状シール配線111c、該第1シール配線111c上に形成された第2リング状シールプラグ105c、及び該第2リング状シールプラグ105c上に形成された第2リング状シール配線112dを有している。

【0053】

また、ここでは、配線構造として、配線層は2層に形成されている多層配線構造を示しているが、配線構造は3層以上の多層配線構造でも単層構造でもよい。

【0054】

また、この固体撮像素子100は、CMOSイメージセンサに限定されるものではなく、CCDイメージセンサであってもよい。

【0055】

なお、プラグとしてはタングステンなどの金属材料を用い、配線としてはアルミや銅などの金属材料を用いることができ、また、層間絶縁膜などの絶縁膜にはシリコン酸化膜を用いることができる。ただし、層間絶縁膜には、シリコン酸化膜や、例えばエッチングストッパ層として用いられるシリコン酸窒化膜、シリコン窒化膜などとの積層膜を用いることができる。

【0056】

次に製造方法について説明する。

【0057】

この実施形態1では、半導体装置の製造方法の一例として、裏面照射型CMOSイメージセンサを半導体ウエハの各チップ領域に形成し、その後各チップ領域を半導体チップとして切り出す例を説明する。

【0058】

P型シリコン基板101の表面領域に素子分離領域102a及び102cを形成する。このとき、素子分離領域102aは、回路形成領域Crにおける、機能回路を構成する半導体素子間を電気的に分離する分離領域であり、また、素子分離領域102cは、シールリング構造Shが形成される領域に形成される。

【0059】

その後、回路形成領域Crでは、熱酸化などによりゲート絶縁膜を形成した後、ゲート電極材料の多結晶シリコン膜のパターニングにより、電荷読み出し部の転送電極としてのゲート電極103a、及び増幅回路としての増幅トランジスタを構成するゲート電極103bを形成する。このとき、回路形成領域Crの周辺の領域(シールリング構造Shの形成領域)では、素子分離領域102c上に、耐湿性材料層として多結晶シリコン層103cが形成される。

【0060】

なお、シールリング構造の形成領域における多結晶シリコン膜103cは、工程簡略のため、電荷読み出し部の転送電極としての多結晶シリコン膜と同一に形成しているが、別途形成してもかまわない。

【0061】

続いて、シリコン基板の各チップ領域の回路形成領域Crでは、不純物のイオン注入によりフォトダイオードを構成するN型拡散領域101b、フローティングディフュージョンとしてのN型拡散領域101c、さらに、増幅トランジスタのソース、ドレイン領域としてのN型拡散領域101a及び101bを形成する(図2(a)、(b))。

【0062】

次に、1層目の層間絶縁膜として、第1層絶縁膜106aを全面に形成し、その後、該第1層絶縁膜106aの、転送電極103a上の部分、及びシールリング構造Shを形成すべき領域に開口を選択的に形成し、それぞれの開口に第1層コンタクトプラグ104b、及び第1リング状シールプラグ104cを埋め込む(図3(a)、(b))。

【0063】

その後、転送電極103a上に配線層111bを形成するとともに、ボンディングパッドを配置する領域に、該ボンディングパッドとして配線層111aを形成し、さらに、耐湿性材料層103c上にリング状シール配線111cを形成する。

【0064】

次に、2層目の層間絶縁膜として、第2層絶縁膜106bを全面に形成し、その後、該第2層絶縁膜106aの、転送電極103a上の部分、ボンディングパッドとしての配線層111a上の部分、及びシールリング構造を形成するリング状シール配線111c上の部分に開口を選択的に形成し、それぞれの開口に、第2層コンタクトプラグ105b、第2層コンタクトプラグ105a及び第2層リング状シールプラグ105cを埋め込む(図4(a)、(b))。

【0065】

次に、第2層絶縁膜106b上に、第2層コンタクトプラグ105bに接続され、かつ、ボンディングパッドとしての配線層111a上のコンタクトプラグ105aに接続されるよう配線層112aを形成し、また、シールリング構造Shの形成領域では、リング状シールプラグ105cに接続されるようリング状シール配線112dを形成する。

【0066】

なお、ここでは、2層配線構造としているが、さらに多層の配線構造を形成する場合は、多層配線層の必要な工程だけ、プラグ、配線の形成を行う。

【0067】

また、上述したように、絶縁膜に埋め込むプラグ部材はタングステンなどの金属材料を用いることができ、埋め込む前には、予め開口内の底面及び側面に下層のチタン及び上層の窒化チタンの2層構造の膜を形成しておくことが好ましい。

【0068】

その後、最上層の絶縁膜として、該配線層112a及び112dを埋め込むよう絶縁膜106cを形成し、さらにその上に耐湿膜として窒化シリコン膜107を形成し、該耐湿膜の表面に支持基板201を貼り付ける。

【0069】

また、この実施形態では、最上層の配線層112a及び112dに耐湿膜としての窒化シリコン膜を直付けしているが、通常のプロセスでは、最上層の配線層112a及び112dを形成した後、これらの配線層を覆うよう全面にCVD法などにより酸化膜を堆積し、その後、酸化膜をその表面が平坦になるよう研磨する。このとき、この酸化膜の研磨は、最上層の配線層の表面が露出した時点で停止するのは難しいため、酸化膜が配線層112a及び112d上に若干残る状態で止める。その後、全面に耐湿膜としての窒化シリコン膜107を形成する。この場合、支持基板に貼り付ける耐湿膜の表面の平坦性が確保されるため、支持基板201との密着性を高めることができるが、シーリング構造Shとしては、最上層の配線層112a及び112dとその上の耐湿膜107との間に酸化膜が介在する構造よりは、最上層の配線層112a及び112d上に耐湿膜107が配線層としてのアルミ層と直付けされている構造の方が、高いシール効果が得られることから望ましい。

【0070】

このように支持基板201に貼り付けた後、シリコン基板の配線層を形成した表現側とは反対側の裏面に、シリコン基板が所望の膜厚になるまで研磨あるいはエッチングなどの処理を施して、シリコン基板を薄膜化し、その後、シリコン基板101の、回路形成領域Crの外側の、ボンディングパッドが配置されている部分を除去する(図5(a)、(b))。

【0071】

さらに、シリコン基板101の、ボンディングパッドとしての配線層111aが露出するよう、該シリコン基板の裏面側を選択的にエッチングする。その後、露出したボンディングパッドとしての配線層111aにボンディングワイヤBWを固着する。これにより、固体撮像素子としての半導体チップと外部の回路との接続がなされる(図6(a)、(b))。

【0072】

このように本実施形態による半導体チップ100では、シリコン基板の、ワイヤボンディングが可能となるように除去する部分には、この部分を除去する前に該シリコン基板上に多結晶シリコン層を形成しておくので、シールリング構造が該多結晶シリコン層Sh上に形成されることとなり、シールリング構造Shを構成するプラグ104cが露出することによる耐湿性の劣化を回避することができる。

【0073】

つまり、近年撮像素子に使われてきている裏面照射型撮像素子では、基板シリコンの裏面の一部を除去する工程により、レイアウトによっては、シールリング構造の下側に基板が存在しない形状となり、この結果、従来構造のシールリング構造では耐湿性を維持できない場合がある。

【0074】

これに対し、本発明の実施形態1の半導体装置100は、シリコン基板を除去する構造を持つ半導体装置、特には、裏面照射型撮像素子100において、シールリング構造Shの下地となる多結晶シリコン層103cなどを形成しているので、シリコン基板101が無くても耐湿性を維持するシールリング構造が形成可能となる。

【0075】

さらに、上記実施形態1では、特に説明しなかったが、上記実施形態1の固体撮像素子を撮像部に用いた、例えばデジタルビデオカメラ、デジタルスチルカメラなどのデジタルカメラや、画像入力カメラ、スキャナ、ファクシミリ、カメラ付き携帯電話装置などの、画像入力デバイスを有した電子情報機器について以下簡単に説明する。

(実施形態2)

図7は、本発明の実施形態2として、実施形態1の固体撮像装置を撮像部に用いた電子情報機器の概略構成例を示すブロック図である。

【0076】

図7に示す本発明の実施形態2による電子情報機器90は、本発明の上記実施形態1の半導体装置を、被写体の撮影を行う撮像部91として備えたものであり、このような撮像部による撮影により得られた高品位な画像データを記録用に所定の信号処理した後にデータ記録する記録メディアなどのメモリ部92と、この画像データを表示用に所定の信号処理した後に液晶表示画面などの表示画面上に表示する液晶表示装置などの表示部93と、この画像データを通信用に所定の信号処理をした後に通信処理する送受信装置などの通信部94と、この画像データを印刷(印字)して出力(プリントアウト)する画像出力部95とのうちの少なくともいずれかを有している。

【0077】

以上のように、本発明の好ましい実施形態を用いて本発明を例示してきたが、本発明は、この実施形態に限定して解釈されるべきものではない。本発明は、特許請求の範囲によってのみその範囲が解釈されるべきであることが理解される。当業者は、本発明の具体的な好ましい実施形態の記載から、本発明の記載および技術常識に基づいて等価な範囲を実施することができることが理解される。本明細書において引用した特許文献は、その内容自体が具体的に本明細書に記載されているのと同様にその内容が本明細書に対する参考として援用されるべきであることが理解される。

【産業上の利用可能性】

【0078】

本発明は、半導体装置、及びその製造方法、並びに電子情報機器の分野において、シールリング構造を構成するプラグが露出することによる耐湿性の劣化を回避することができる固体撮像装置などの半導体装置およびその製造方法、並びにこのような半導体装置を用いた電子情報機器を得ることができる。

【符号の説明】

【0079】

90 電子情報機器

91 撮像部

92 メモリ部

93 表示手段

94 通信手段

95 画像出力手段

100 半導体装置(半導体チップ)

101 半導体基板

101c 拡散領域(FD領域)

101d N型拡散領域

102a、102c 素子分離領域

103a 転送電極

103b 増幅ゲート

103c 耐湿性材料層

104b 第1層コンタクトプラグ

104c 第1リング状シールプラグ

105a、105b 第2層コンタクトプラグ

105c 第2リング状シールプラグ

106a、106b 絶縁膜

111a 配線層(ボンディングパッド)

111b 第1層金属配線

111c 第1リング状シール配線

112a 第2層金属配線

112b 第2リング状シール配線

113a ソース領域

113b ドレイン領域

Am 増幅部(増幅回路)

BW ボンディングワイヤ

Cr 回路形成領域

PD 受光部

R 読み出し部

Sh シールリング構造

【特許請求の範囲】

【請求項1】

半導体ウエハを分割して半導体チップとして得られた半導体装置であって、

該半導体チップは、

半導体基板上に形成された機能回路を含む回路形成領域と、

該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造とを備え、

該シールリング構造は、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、

該シールリング構造を構成する最下層の導電性プラグは、該半導体基板に代わる耐湿材料層上に配置されている、半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記半導体基板の一部を除去した領域における、前記回路形成領域と前記シールリング構造との間の部分には、該回路形成領域の機能回路との電気的接続をとるためのボンディングパッドを構成する導電性層が配置されている、半導体装置。

【請求項3】

請求項1に記載の半導体装置において、

前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した素子分離領域上に形成されている、半導体装置。

【請求項4】

請求項1に記載の半導体装置において、

前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した多結晶シリコン層である、半導体装置。

【請求項5】

請求項1に記載の半導体装置において、

前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した窒化シリコン層である、半導体装置。

【請求項6】

請求項1に記載の半導体装置において、

該半導体チップは、多層配線構造を有しており、

該シールリング構造は、該多層配線構造を構成する層間絶縁膜を貫通する導電性プラグと、該層間絶縁膜の上下に位置し、該導電性プラグにより接続された配線層とを含む、半導体装置。

【請求項7】

請求項1に記載の半導体装置において、

前記半導体チップは、被写体からの光を光電変換して撮像信号を出力する固体撮像素子であり、

該固体撮像素子は、前記半導体基板の前記機能回路が形成された表面領域とは反対側の裏面側から光を入射させる裏面照射型固体撮像素子である、半導体装置。

【請求項8】

請求項7に記載の半導体装置において、

前記固体撮像素子は、CMOSイメージセンサである、半導体装置。

【請求項9】

請求項7に記載の半導体装置において、

前記固体撮像素子は、CCDイメージセンサである、半導体装置。

【請求項10】

半導体ウエハの、半導体チップとなるチップ領域に機能回路を形成するとともに、該チップ領域の周囲に、該チップ領域に該機能回路への水分の侵入が阻止されるシールリング構造を形成し、該チップ領域を半導体チップとして分割して半導体装置を製造する方法であって、

該半導体ウエハを構成する半導体基板上に、該チップ領域が分離されるよう素子分離領域を形成するステップと、

該チップ領域内の回路形成領域に半導体素子を形成するステップと、

該半導体基板上に該絶縁膜を形成するステップと、

該絶縁膜に形成した開口内に導電性プラグを形成するステップと、

該絶縁膜上に配線層を形成するステップと、

該半導体基板の、該シールリング構造に対向する部分の領域を除去するステップとを含み、

該シールリング構造は、該絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、

該半導体素子を形成するステップでは、

該機能回路の電極を構成する導電材料の一部を、該素子分離領域上に耐湿材料層として形成し、

該導電性プラグを形成するステップでは、

該耐湿材料層上に該シールリング構造を構成する導電性プラグを形成する、半導体装置の製造方法。

【請求項11】

被写体の撮像を行う撮像部を備えた電子情報機器であって、

該撮像部は、請求項7に記載の半導体装置である電子情報機器。

【請求項1】

半導体ウエハを分割して半導体チップとして得られた半導体装置であって、

該半導体チップは、

半導体基板上に形成された機能回路を含む回路形成領域と、

該回路形成領域の周囲の、該半導体基板の一部を除去した領域上に、該回路形成領域への水分の侵入が阻止されるよう形成されたシールリング構造とを備え、

該シールリング構造は、絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、

該シールリング構造を構成する最下層の導電性プラグは、該半導体基板に代わる耐湿材料層上に配置されている、半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記半導体基板の一部を除去した領域における、前記回路形成領域と前記シールリング構造との間の部分には、該回路形成領域の機能回路との電気的接続をとるためのボンディングパッドを構成する導電性層が配置されている、半導体装置。

【請求項3】

請求項1に記載の半導体装置において、

前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した素子分離領域上に形成されている、半導体装置。

【請求項4】

請求項1に記載の半導体装置において、

前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した多結晶シリコン層である、半導体装置。

【請求項5】

請求項1に記載の半導体装置において、

前記耐湿材料層は、前記半導体基板の、前記シールリング構造の配置領域に対向する部分を除去する前に、該半導体基板上に形成した窒化シリコン層である、半導体装置。

【請求項6】

請求項1に記載の半導体装置において、

該半導体チップは、多層配線構造を有しており、

該シールリング構造は、該多層配線構造を構成する層間絶縁膜を貫通する導電性プラグと、該層間絶縁膜の上下に位置し、該導電性プラグにより接続された配線層とを含む、半導体装置。

【請求項7】

請求項1に記載の半導体装置において、

前記半導体チップは、被写体からの光を光電変換して撮像信号を出力する固体撮像素子であり、

該固体撮像素子は、前記半導体基板の前記機能回路が形成された表面領域とは反対側の裏面側から光を入射させる裏面照射型固体撮像素子である、半導体装置。

【請求項8】

請求項7に記載の半導体装置において、

前記固体撮像素子は、CMOSイメージセンサである、半導体装置。

【請求項9】

請求項7に記載の半導体装置において、

前記固体撮像素子は、CCDイメージセンサである、半導体装置。

【請求項10】

半導体ウエハの、半導体チップとなるチップ領域に機能回路を形成するとともに、該チップ領域の周囲に、該チップ領域に該機能回路への水分の侵入が阻止されるシールリング構造を形成し、該チップ領域を半導体チップとして分割して半導体装置を製造する方法であって、

該半導体ウエハを構成する半導体基板上に、該チップ領域が分離されるよう素子分離領域を形成するステップと、

該チップ領域内の回路形成領域に半導体素子を形成するステップと、

該半導体基板上に該絶縁膜を形成するステップと、

該絶縁膜に形成した開口内に導電性プラグを形成するステップと、

該絶縁膜上に配線層を形成するステップと、

該半導体基板の、該シールリング構造に対向する部分の領域を除去するステップとを含み、

該シールリング構造は、該絶縁膜内に形成され、該絶縁膜の上下に位置する導電性層を接続する導電性プラグを有し、

該半導体素子を形成するステップでは、

該機能回路の電極を構成する導電材料の一部を、該素子分離領域上に耐湿材料層として形成し、

該導電性プラグを形成するステップでは、

該耐湿材料層上に該シールリング構造を構成する導電性プラグを形成する、半導体装置の製造方法。

【請求項11】

被写体の撮像を行う撮像部を備えた電子情報機器であって、

該撮像部は、請求項7に記載の半導体装置である電子情報機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−99742(P2012−99742A)

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願番号】特願2010−247872(P2010−247872)

【出願日】平成22年11月4日(2010.11.4)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願日】平成22年11月4日(2010.11.4)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]