半導体装置、及び半導体装置の作製方法

【課題】半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を提供する。またこのような半導体装置の作製方法を提供する。

【解決手段】半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこのように作製したコンタクトを用いて半導体装置を作製すればよい。

【解決手段】半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこのように作製したコンタクトを用いて半導体装置を作製すればよい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に関する。本発明は半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、半導体素子を用いた電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、デバイス素子の高密度集積化に伴い、個々の素子の微細化が必要となってきている。ここで問題となる事柄のひとつに、微細化に伴うコンタクト不良が挙げられる。

【0004】

コンタクト不良とは、配線電極と半導体装置との電気的な接続箇所(以降、コンタクトとも呼ぶ)が、接続不良を起こしたときに生じる動作不良のことである。特に、微細化技術と多層配線技術とにより、層間絶縁層に設けられた細いコンタクトホールを介して電気的接続を取る必要性が高まっている。

【0005】

半導体装置の微細化に伴う、細く、アスペクト比の高いコンタクトホールの場合、配線電極を形成する導電膜のカバレッジ不良によるコンタクトホール内での配線電極の断線や、コンタクトホール内部に導電膜が形成されるより前に、オーバーハングによりコンタクトホール上部が導電膜で塞がれて配線電極がコンタクトホール内に形成できないといった問題がある。

【0006】

これらの問題を解決するため、例えば特許文献1に示されているように、柱状のシリコン単結晶を用いて電気的接続をとる方法が考案されている。これは単結晶シリコン基板上に金などの低融点金属材料を用いたVLS(Vapor−Liquid−Solid)成長法によりシリコンの柱状単結晶を形成し、その後この柱状単結晶これに導電性を持たせるために不純物をドープし、接続電極として用いる方法である。

【0007】

また別の技術として、特許文献2に示されているように、単結晶シリコン基板上に形成したトランジスタのソース領域、及びドレイン領域を露出させるコンタクトホールを形成した後、コンタクトホール内部に不純物を含むエピタキシャルシリコン層を形成し、これを接続電極として用いる方法が考案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭61−248471号公報

【特許文献2】特開2008−130756号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、上記に代表される微細コンタクトの形成技術では、以下のような問題がある。トランジスタなどの半導体装置と配線電極との接続電極を形成する場合、接続電極として用いる柱状のシリコン層は半導体層上に形成(成膜)され、またその際に半導体層が成膜雰囲気に曝される。しかし、このような環境で柱状のシリコン層を形成すると、半導体装置の電気的特性に悪影響を及ぼす場合がある。

【0010】

例えば、同一基板上にシリコンを半導体層に用いるnチャネル型トランジスタとpチャネル型トランジスタを形成することは、従来のCMOS技術によって半導体回路を形成する上で重要である。柱状のシリコン層はこれらトランジスタのソース領域及びドレイン領域上に形成される。具体的には、nチャネル型トランジスタではn型シリコン層上に、pチャネル型トランジスタではp型シリコン層上に柱状のシリコン層が形成される。特許文献2によれば接続電極に用いる柱状のシリコン層を形成する際に、同時にリンを含むガスを添加することにより柱状のシリコン層をn型シリコンとしているが、この場合pチャネル型トランジスタでは接続電極とソース領域、又はドレイン領域との界面で、いわゆるpn接合が形成され、この電気的障壁によりコンタクト抵抗が高くなる問題がある。また、特許文献1によれば、この問題を回避するのにnチャネル型トランジスタとpチャネル型トランジスタとで柱状のシリコン層へのドープを2度に分けて行う必要が生じるが、その際、高いアスペクト比をもつ柱状のシリコン層を覆うドープマスクを形成することは困難であり、また作製工程が煩雑になる。

【0011】

また、金属酸化物半導体を半導体層としたトランジスタなどの半導体装置においては、柱状のシリコン層を形成する成膜ガス、例えばシランガス中に含まれる水素はトランジスタ特性に影響を及ぼす。酸化物半導体中の水素はバンドギャップ中のドナー準位を形成しやすいため、成膜ガス中に含まれる水素が酸化物半導体中に拡散すると、トランジスタのスイッチング特性などの電気的特性に悪影響を及ぼす。

【0012】

本発明は、この様な技術的背景を鑑みてなされたものである。したがって本発明は、半導体素子の特性を損なうことなく微細化に伴うコンタクト不良の発生が抑制された、電気的特性の良好な半導体装置と、その作製方法を提供することを課題とする。

【課題を解決するための手段】

【0013】

上記目的を達成するために、本発明の一態様では、半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、下部電極上に導電性のシリコンウィスカーを形成し、これをコンタクトにおける接続電極として用いる。

【0014】

すなわち、半導体層の上面にこれと電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこの様に作製したコンタクトを用いて半導体装置を作製すればよい。

【0015】

接続電極となるシリコンウィスカーは下部電極から成長させることが可能である。従って微細化技術に伴う、細く、アスペクト比の高いコンタクトホールであっても、上下の電極が断線することなく確実に電気的に接続することができる。

【0016】

また、半導体層のコンタクトホールと重なる部分は、金属、又は金属化合物からなる下部電極に覆われており半導体層は露出しない。この下部電極はシリコンウィスカー形成時の半導体層に対する保護膜としての機能を有するため、シリコンウィスカーの形成時において、成膜ガス、及び成膜ガスに含まれる不純物の半導体層中への浸入、及び拡散が抑制される。

【0017】

さらに、接続電極となるシリコンウィスカーに導電性を持たせるために、不純物を拡散させてn型シリコン、又はp型シリコンとする。シリコンウィスカーは下部電極である金属、又は金属化合物と接するため、これらの接合はほぼオーミック接合となり、その電気的障壁は極めて小さくなる。さらに、単純にシリコンウィスカーを低抵抗化すればよいため拡散させる不純物の種類は限定されず、このため単一のドーピング工程で形成できる。

【0018】

また、接続電極となるシリコンウィスカーと上部電極との間に、シリコンウィスカーに含まれるシリコンと上部電極に含まれる材料との反応によってシリサイド層が形成されていてもよい。シリサイド層が形成されることにより、接続電極と上部電極との接触抵抗を小さくすることができる。

【0019】

すなわち、本発明の一態様は、半導体層と、半導体層の上面と電気的に接続する下部電極と、下部電極上にコンタクトホールを備え且つ半導体層を覆う絶縁層と、導電性シリコンウィスカーを含み、且つコンタクトホールにおいて下部電極と接する接続電極と、絶縁層上に、接続電極と電気的に接続する上部電極と、を有する半導体装置である。

【0020】

このような半導体装置は、デバイスの微細化に伴う、細く、アスペクト比の高いコンタクトホールであっても、上下の電極を断線することなく確実に電気的に接続することができる。

【0021】

また本発明の一態様は、上記下部電極が、金属、又は半導体層を構成する半導体と金属とを含む金属化合物を有する半導体装置である。

【0022】

下部電極を金属、又は金属化合物とすることにより、接続電極である導電性シリコンウィスカーと下部電極との接触抵抗を小さくできるため、コンタクト抵抗の小さい半導体装置とすることができる。

【0023】

また本発明の一態様は、上記導電性シリコンウィスカーと上記上部電極との間に、シリサイド層を有する半導体装置である。

【0024】

シリコンウィスカーと上部電極との間にシリサイド層が形成されていることにより、シリコンウィスカーと上部電極との接触抵抗を小さくできるため、コンタクト抵抗の小さい半導体装置とすることができる。

【0025】

また本発明の一態様は、上記半導体装置において、上記接続電極は、二以上の導電性シリコンウィスカーを含む。

【0026】

複数のシリコンウィスカーからなるシリコンウィスカー群で接続電極を構成することにより、断線の危険性がより低くなり、コンタクト不良を低減できる。

【0027】

また、本発明の一態様は、半導体層の上面と電気的に接続する下部電極を形成し、半導体層と下部電極とを覆う絶縁層を形成し、絶縁層に、下部電極と重なるコンタクトホールを形成する。またコンタクトホールにおいて、下部電極と接し且つ導電性シリコンウィスカーを含む接続電極を形成し、絶縁層上に、接続電極と電気的に接続する上部電極を形成する、半導体装置の作製方法である。

【0028】

また、本発明の一態様は、半導体層の上面と接する金属膜を形成し、半導体層を構成する材料と金属膜を構成する材料とを含み且つ半導体層の上面に接する金属化合物層を形成した後、金属膜を除去し、続いて半導体層と金属化合物層とを覆う絶縁層を形成し、絶縁層に、金属化合物層と重なるコンタクトホールを形成し、さらにコンタクトホールにおいて、金属化合物層と接し且つ導電性シリコンウィスカーを含む接続電極を形成し、絶縁層上に、接続電極と電気的に接続する上部電極を形成する、半導体装置の作製方法である。

【0029】

このような方法で半導体装置を作製することにより、シリコンウィスカー形成時における、成膜ガス、及び成膜ガスに含まれる不純物の半導体層への浸入、及び拡散が抑制され、電気的特性の良好な半導体装置が作製できる。

【0030】

なお、本明細書等において、コンタクトとは配線電極と半導体装置との電気的な接続箇所のことを言う。またこれは、半導体装置の有する電極と、配線電極とをコンタクトホール内部に設けられた接続電極を介して電気的に接続する接続箇所をも含むこととする。

【0031】

また、本明細書等において、シリコンウィスカーとは突起(髭)状の結晶性シリコンであり、複数のシリコンウィスカーにおいて、各々の突起の伸長方向(すなわち、軸の方向)は、不揃いであってもよい。本明細書等においてシリコンウィスカーとの表記には、シリコンウィスカー群(複数のシリコンウィスカー)を含むことがある。また、本明細書等において、結晶性を有するとは、アモルファスではないことを指し、単結晶、多結晶、微結晶又は準結晶であることを含む。

【発明の効果】

【0032】

本発明によれば、半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置と、その作製方法を提供できる。

【図面の簡単な説明】

【0033】

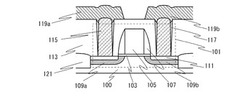

【図1】本発明の一態様の、トランジスタを説明する図。

【図2】本発明の一態様の、トランジスタの作製方法を説明する図。

【図3】本発明の一態様の、コンタクトを説明する図。

【図4】本発明の一態様の、トランジスタを説明する図。

【図5】本発明の一態様の、トランジスタの作製方法を説明する図。

【発明を実施するための形態】

【0034】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0035】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0036】

(実施の形態1)

本実施の形態では、本発明の一態様であるトランジスタの構成とその作製方法について図1乃至図3を用いて説明する。

【0037】

《トランジスタの構成例》

図1に、本実施の形態で例示するトランジスタ101の断面概略図を示す。

【0038】

トランジスタ101は半導体材料(例えばシリコンなど)を含む基板100に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられたソース領域109a、及びドレイン領域109bと、チャネル形成領域上に接して設けられたゲート絶縁層103と、ゲート絶縁層103に接し、チャネル形成領域と重畳するゲート電極層105と、を有する。ゲート電極層105の側面にはサイドウォール107が設けられ、ソース領域109a、及びドレイン領域109b上にはそれぞれ金属化合物層111が設けられている。また、金属化合物層111、ゲート絶縁層103、サイドウォール107、及びゲート電極層105を覆う層間絶縁層113が設けられており、層間絶縁層113は金属化合物層111に達するコンタクトホール117を有する。コンタクトホール117の内部には金属化合物層111に接するシリコンウィスカー115が設けられ、シリコンウィスカー115の上部はそれぞれ層間絶縁層113上に設けられたソース配線層119a、及びドレイン配線層119bと接している。

【0039】

なお、トランジスタ101は、nチャネル型のトランジスタとしても良いし、pチャネル型のトランジスタとしても良い。

【0040】

また、図1に示すように、基板100には、図示されていない隣接する半導体素子とトランジスタ101とを分離する素子分離層121が埋め込まれている。

【0041】

シリコンウィスカー115は接続電極としての機能を有し、導電性を持たせるため不純物が拡散されている。また、その下部は金属化合物層111を介してそれぞれソース領域109a及びドレイン領域109bと電気的に接続される。一方その上部はそれぞれソース配線層119a、及びドレイン配線層119bと接し、電気的に接続されている。したがって、トランジスタ101のソース領域109a、及びドレイン領域109bは、金属化合物層111及びシリコンウィスカー115を介してそれぞれソース配線層119a、又はドレイン配線層119bと電気的に接続される。

【0042】

金属化合物層111は、不純物が拡散されたソース領域109a、及びドレイン領域109bの一部から成り、ソース領域109a及びドレイン領域109bを構成する半導体と金属とが反応して低抵抗化された金属化合物で構成される。従って、金属化合物層111と接するシリコンウィスカー115の有する導電性がn型、又はp型のどちらであるかによらず、これらの接合はほぼオーミック接合となり電気的障壁が極めて小さい。さらに、ソース領域109a、及びドレイン領域109bの有する導電性がn型、又はp型のどちらであっても、シリコンウィスカー115の導電型は問われず、同一の導電型を有するシリコンウィスカー115を接続電極として用いることができる。

【0043】

なお、シリコンウィスカー115の上端と、ソース配線層119a、又はドレイン配線層119bとの界面において、金属とシリコンの反応により、シリサイドが形成されていてもよい。シリサイドが形成されると、シリコンウィスカー115と、ソース配線層119a、又はドレイン配線層119bとの接触抵抗が低減されるため、好ましい。

【0044】

《作製工程例》

次に、本発明の一態様であるトランジスタの作製方法の一例について説明する。以下ではトランジスタ101の作製方法について図2、及び図3を用いて説明する。

【0045】

まず、半導体材料を含む基板100を用意する。半導体材料を含む基板100としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができる。ここでは、半導体材料を含む基板100として、単結晶シリコン基板を用いる場合の一例について示すものとする。なお、一般に「SOI基板」は、絶縁表面上にシリコン半導体層が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が設けられた構成の基板をも含むこととする。つまり、SOI基板には、ガラス基板などの絶縁基板上に絶縁層を介して半導体層が設けられた構成も含まれるものとする。

【0046】

次に、基板100上に素子分離層121を形成する。

【0047】

基板100上に素子分離層121を形成するためのマスクとなる保護層を形成する。例えば、酸化シリコンや窒化シリコン、窒化酸化シリコンなどを材料とする絶縁膜を用いることができる。なお、この工程の前後において、トランジスタのしきい値電圧を制御するために、n型の導電性を付与する不純物元素や、p型の導電性を付与する不純物元素を基板100に添加しても良い。基板100に含まれる半導体材料がシリコンの場合、n型の導電性を付与する不純物としては、例えばリンや砒素などを用いることができる。また、p型の導電性を付与する不純物としては、例えば、ホウ素、アルミニウム、ガリウムなどを用いることができる。

【0048】

次に上記の保護層をマスクとして、保護層に覆われていない領域(露出している領域)の基板100の一部をエッチングにより除去する。これにより分離された半導体領域が形成される。当該エッチングには、ドライエッチングを用いるのが好適であるが、ウェットエッチングを用いても良い。エッチングガスやエッチング液については、被エッチング材料に応じて適宜選択することができる。

【0049】

次に、基板100全体を覆うように絶縁層を形成し、上記半導体領域に重畳する領域の当該絶縁層を選択的に除去することにより、素子分離層121を形成する。当該絶縁層は酸化シリコンや窒化シリコン、窒化酸化シリコンなどを用いて形成される。絶縁層の除去方法としては、CMP(Chemical Mechanical Polishing)などの研磨処理やエッチング処理などがあるが、そのいずれを用いても良い。なお、半導体領域の形成後、または、素子分離層121の形成後には、上記保護層を除去する。

【0050】

次に、基板100上に絶縁層を形成し、当該絶縁層上に導電材料を含む層を形成する。

【0051】

上記絶縁層は、後のゲート絶縁層103となるものであり、CVD法やスパッタリング法等を用いて得られる酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y>0))等を含む膜の単層構造または積層構造とすると良い。他に、高密度プラズマ処理や熱処理(熱酸化処理や熱窒化処理など)によって、基板100の表面を酸化、窒化することにより上記絶縁層を形成しても良い。高密度プラズマ処理は、例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素、アンモニア、窒素などとの混合ガスを用いて行うことができる。また、絶縁層の厚さは特に限定されないが、例えば1nm以上100nm以下とすることができる。

【0052】

導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、導電材料を含む多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンコート法など、各種成膜方法を用いることができる。なお、本実施の形態では、導電材料を含む層を、金属材料を用いて形成する場合の一例について示すものとする。

【0053】

その後、導電材料を含む層を選択的にエッチングして、ゲート電極層105を形成する。

【0054】

次に、サイドウォール107を形成する。サイドウォール107は、ゲート電極層105を覆うように絶縁層を形成した後に、当該絶縁層に異方性の高いエッチング処理を適用することで、自己整合的に形成することができる。

【0055】

なお、サイドウォール107を形成する際のエッチング処理により、ゲート絶縁層103となる絶縁層の、ゲート電極層105、及びサイドウォール107に覆われていない部分も同時にエッチングされ、ゲート絶縁層103も形成される。

【0056】

サイドウォール107を設けることにより、後述の不純物を添加する工程において、不純物元素が異なる濃度で添加された不純物領域を形成することができる。こうすることで短チャネル効果などの影響を抑制することができ、好ましい。なお、高集積化が要求される場合には、サイドウォールを有しない構成とすることにより、トランジスタサイズを縮小することができる。

【0057】

次に、ゲート電極層105、及びサイドウォール107をマスクとして用い、リンや砒素などの不純物を添加して、ソース領域109a、及びドレイン領域109bを形成する。なお、ここではpチャネル型のトランジスタを形成するためにホウ素やアルミニウムなどの不純物元素を添加しているが、nチャネル型のトランジスタを形成する場合には、リンや砒素などの不純物元素を添加すればよい。添加する不純物の濃度は適宜設定することができるが、半導体素子が高度に微細化される場合には、その濃度を高くすることが望ましい。なお、不純物元素の添加後には加熱処理を行い、不純物元素の活性化や不純物元素の添加時に生じる欠陥の改善等を図るのが望ましい。この加熱処理は後述するシリコンウィスカー115の形成工程と兼ねることもできる。

【0058】

この段階における断面概略図を図2(A)に示す。

【0059】

次に、金属化合物層111を形成する。

【0060】

まず、ゲート電極層105、サイドウォール107、並びにソース領域109a、及びドレイン領域109bを覆う金属層123を形成する。金属層123は、真空蒸着法やCVD法、スパッタリング法、スピンコート法などの各種成膜方法を用いて形成することができる。金属層123には、基板100を構成する半導体材料と反応して低抵抗な金属化合物を生成できる金属材料を用いる。さらに、当該金属化合物が後に形成するシリコンウィスカーを形成可能な材料を選択する。つまり、シリコンウィスカーの成長を促進する触媒として機能する金属元素を含む材料を選択することができる。例えば、シリサイドを形成する金属元素を好ましく用いることができる。例えば、チタン、ニッケル、コバルト、鉄等がある。

【0061】

次に、熱処理を施して、金属層123と半導体材料を反応させる。これにより、ソース領域109a、及びドレイン領域109bに接する金属化合物層111が形成される。なお、ゲート電極層105として多結晶シリコンなどを用いた場合は、ゲート電極層105の金属層123と接触する部分にも、金属化合物領域が形成されることとなる。

【0062】

上記熱処理としては、例えば、フラッシュランプの照射による熱処理を用いることができる。もちろん、その他の熱処理方法を用いても良いが、金属化合物の形成に係る化学反応の制御性を向上させるためには、ごく短時間の熱処理を実現できる方法を用いることが望ましい。なお、金属化合物層111は、金属材料と半導体材料との反応により形成されるものであり、十分に導電性が高められた領域である。金属化合物層111を形成することで、電気抵抗を十分に低減し、素子特性を向上させることができる。この段階の断面概略図を図2(B)に示す。

【0063】

金属化合物層111を形成した後、金属層123を除去する。

【0064】

次に、上述の工程により形成された各構成を覆うように、層間絶縁層113を形成する。層間絶縁層113は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル等の無機絶縁材料を含む膜の単層構造または積層構造とすることができる。また、後の工程の熱処理に耐えうるのであれば、ポリイミド、アクリル樹脂等の有機絶縁材料を用いて形成することもできる。層間絶縁層113となる絶縁膜を形成後、その表面をCMPやエッチング処理などによって平坦化することが好ましい。平坦化することにより、後に形成するソース配線層119a及びドレイン配線層119bなどの配線層の段切れなどの不具合を防ぐことができるため好ましい。なお、当該平坦化処理は必要でなければ工程を簡略化できるため行わなくても良い。

【0065】

続いて、層間絶縁層113に一対の金属化合物層111にまで達するコンタクトホール117を形成する。コンタクトホール117を形成する際の層間絶縁層113のエッチングには、金属化合物層111に対する層間絶縁層113のエッチングの選択比が高い方法を用いることができる。半導体素子が高度に微細化される場合には、エッチングによるコンタクトホールの広がりを抑制するため、異方性のドライエッチングを用いることが好ましい。

【0066】

次に、コンタクトホール117内にシリコンウィスカー115を形成する。

【0067】

シリコンウィスカー115は、金属化合物層111上に、熱CVD法、好ましくはLPCVD(Low Pressure Chemical Vapor Deposition)法により形成できる。LPCVD法を用いることで、シリコンウィスカー115を金属化合物層111から選択的に成長させることができる。なお、シリコンウィスカー115には、不純物として、LPCVD装置のチャンバーに起因する酸素などが含まれている場合がある。

【0068】

本実施の形態では、LPCVD法によりシリコンウィスカー115を形成する。LPCVD法は、550℃より高い温度で且つ装置、または上述の工程により形成された各構成が耐えうる温度以下、好ましくは580℃以上650℃未満の加熱をしつつ、原料としてシリコンを含む堆積性ガスを用いる。シリコンを含む堆積性ガスとしては、水素化シリコン、フッ化シリコン、または塩化シリコンなどがあり、代表的には、SiH4、Si2H6、SiF4、SiCl4、Si2Cl6などがある。なお、原料ガスに、ヘリウム、ネオン、アルゴン、キセノン等の希ガス、及び窒素、水素などの一以上を混合させても良い。

【0069】

さらに、シリコンウィスカー115に導電性を持たせるため、シリコンウィスカーの形成中に一導電型を付与する不純物元素を添加する。一導電型を付与する不純物元素のうち、LPCVD法に用いるのに適しているものとして、例えばn型の導電性を付与するにはリンや砒素などが挙げられ、他方p型の導電性を付与するにはホウ素などが挙げられる。

【0070】

シリコンウィスカー115の導電型はn型でもp型でもどちらでもよく、十分に低抵抗化していればよい。上述のようにシリコンウィスカーと接する金属化合物層111は低抵抗化された金属化合物を含んでいる。従ってシリコンウィスカーの導電型によらず、これらの接合はほぼオーミック接合となるため電気的障壁が極めて小さくなる。従って、金属化合物層111とシリコンウィスカー115との接触抵抗は小さく、またシリコンウィスカー自体も低抵抗化されているため、低抵抗なコンタクトを実現できる。

【0071】

本実施の形態では、一導電型を付与する不純物元素としてリンを用い、シリコンウィスカー115をn型の導電性シリコンとした。

【0072】

また、シリコンウィスカー115をLPCVD法などの加熱工程を含む方法で形成するため、上述のソース領域109a及びドレイン領域109bに添加した不純物元素の活性化や不純物元素の添加時に生じる欠陥の改善のための加熱処理を同時に行うことができる。

【0073】

また、シリコンウィスカー115は結晶性を有している。またその成長方向とシリコンウィスカー115を構成する結晶の結晶方位の少なくともひとつが略一致していてもよい。このようなシリコンウィスカー115とすることで、例えばアモルファスシリコンや、結晶方位に規則性のない一般的な多結晶シリコン又は微結晶シリコンなどと比べて電気伝導性に優れている。従って、このような結晶性を有するシリコンウィスカー115を用いてコンタクトを形成することにより、コンタクト抵抗の小さい良好なコンタクトを形成することができる。

【0074】

また、シリコンウィスカー115は結晶性の突起であれば、その形状は特に限定されない。例えば、円柱状、角柱状などの柱状、円錐状、角錐状などの針状でもよい。また、シリコンウィスカーの頂部は、湾曲した形状を有していても良い。また、シリコンウィスカーの直径は50nm以上コンタクトホールの径以下、好ましくは100nm以上3μm以下とする。

【0075】

また、シリコンウィスカー115とコンタクトホール117の壁面との間には隙間があってもよいし、シリコンウィスカー115によってコンタクトホール117が完全に埋まっていてもよい。隙間がある場合は、後に形成する上部電極との接触面積が大きくなるため、これらの接触抵抗を低くすることができる。また、隙間がなく完全に埋まっている場合は機械的強度が高くなるため、外力などが加わっても接触不良を起こしにくい。

【0076】

また、ひとつのコンタクトホールに複数のシリコンウィスカーからなるシリコンウィスカー群が形成されてもよい。その際、シリコンウィスカー同士が接していてもよいし、間隔があってもよい。また二以上のシリコンウィスカーが束状になっていてもよい。シリコンウィスカー群を接続電極として用いることにより、例えばひとつのシリコンウィスカーが断線したとしても、他のシリコンウィスカーにより電気的接続が保たれるため、断線の危険性がより低くなり、コンタクト不良を低減できる。

【0077】

LPCVD法を用いてコンタクトホール117内にシリコンウィスカー115を形成する際、層間絶縁層113上にはシリコンウィスカーは形成されない。しかし、層間絶縁層113上にはアモルファスシリコン、ポリシリコン、微結晶シリコンなどの薄いシリコン薄膜が成膜される場合がある。

【0078】

層間絶縁層113上に成膜された不要なシリコン薄膜をエッチングにより除去する。その際、シリコンウィスカー115と、層間絶縁層113上に形成されたシリコン薄膜との結晶性の違いに由来するエッチング速度の差を利用して、シリコンウィスカー115に対するシリコン薄膜のエッチングの選択比を大きくとれる条件でシリコン薄膜のみを除去すればよい。なお、層間絶縁層113上に該シリコン薄膜が形成されなかった場合は、この工程を省略することができる。

【0079】

この段階での断面概略図を図2(C)に示す。

【0080】

次に、ソース配線層119a、及びドレイン配線層119bを形成する。

【0081】

まず、導電膜を形成する。導電膜はアルミニウムや銅、チタン、タンタル、タングステン等の金属材料からなる膜の単層、又は積層を用いることができる。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンコート法など、各種成膜方法を用いることができる。その後、導電膜を選択的にエッチングし、ソース配線層119a、及びドレイン配線層119bを形成する。

【0082】

なお、導電膜の形成以降、この導電膜に用いる金属とシリコンウィスカー115とで反応が起こり、シリコンウィスカー115と導電膜との界面にシリサイドが形成される場合がある。シリサイドが形成されると、シリコンウィスカー115と導電膜との接触抵抗が低減されるため好ましい。

【0083】

以上の工程により、トランジスタ101が形成される。この段階での断面概略図を図2(D)に示す。

【0084】

なお、シリコンウィスカー115の形成条件により、コンタクトホール117内部のシリコンウィスカー115は様々な形状を取り得る。図3にそのシリコンウィスカー115の形状について例示する。図3(A1)、図3(B1)、図3(C1)、及び図3(D1)はコンタクトホール117の近傍を抜き出して描いた断面概略図であり、図3(A2)、図3(B2)、図3(C2)、及び図3(D2)はそれぞれ、図3(A1)、図3(B1)、図3(C1)、及び図3(D1)中の破線で示す箇所で切断した際の上面概略図である。図3(A1)及び図3(A2)に示すシリコンウィスカー115は一本の円柱状であり、コンタクトホール117の壁面との間に隙間が生じている。隙間が生じることにより、上部電極はシリコンウィスカー115の側面とも接触することができ、その結果接触面積が大きくなり、これらの接触抵抗を低くすることができる。図3(B1)及び図3(B2)ではシリコンウィスカー115によってコンタクトホール117内部が隙間なく埋まっている。従って、機械的強度が高まり、外力などが加わっても接触不良を起こしにくい。また、図3(C1)及び図3(C2)のように細い円柱状のシリコンウィスカー115がまばらに配置されていてもよい。このような構成では、より上部電極との接触面積を大きくすることができる。また、図3(D1)及び図3(D2)に示すシリコンウィスカー115は、角柱状であり、複数のシリコンウィスカー115同士が接し、シリコンウィスカー群をなしている。複数のシリコンウィスカーが接することにより、機械的強度を高めることができる。シリコンウィスカー115の形状はここに示す形状に限られるものではなく、上述のように結晶状の突起であれば様々な形状を取り得ることは言うまでもない。

【0085】

このように作製したトランジスタは、高集積化に伴う細く、アスペクト比の高いコンタクトホールに対しても、接続電極の断線などの影響がなく、良好なコンタクトを得ることができる。さらに、コンタクトホール内のシリコンウィスカーの形成時における、成膜ガス起因の不具合を受けることなく、電気的特性の良好なトランジスタを形成することができる。

【0086】

なお、高集積化に伴い多層配線を用いる場合、通常ではそれぞれの層の形成段階で接続配線を形成する必要があるが、上記のようなシリコンウィスカーを接続配線としたコンタクトの形成方法を用いることにより、二層目より上層の配線層と直接電気的に接続することが可能である。例えば二層目より上層の層間絶縁層を形成した後に、トランジスタのソース領域、又はドレイン領域上に形成された金属化合物層に到達するコンタクトホールを形成し、上述のような方法により導電性シリコンウィスカーと、配線層とを形成すればよい。

【0087】

なお、本実施の形態ではトランジスタの構成、及び作製方法を一例に挙げて説明したが、コンタクトホール底部の金属化合物からなる下部電極と接する、導電性シリコンウィスカーを接続電極としたコンタクトの形成方法は、ダイオード素子、容量素子、抵抗素子など、層間絶縁層を介した、配線の接続部を有する半導体装置であれば適用することが可能である。これらの半導体装置に適用した場合でも同様に、デバイスの高集積化に伴う細く、アスペクト比の高いコンタクトホールにおける接続電極の断線などの影響がなく、信頼性の高いコンタクトを有する半導体装置とすることができる。

【0088】

本実施の形態で例示した半導体装置の構成、および半導体装置の作製方法によれば、半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を実現できる。

【0089】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0090】

(実施の形態2)

本実施の形態では、本発明の一態様の、実施の形態1で示したものとは異なるトランジスタの構成とその作製方法について図4及び図5を用いて説明する。

【0091】

《トランジスタの構成例》

図4(A)に、本実施の形態で例示するトランジスタ201の断面概略図を示す。トランジスタ201は、酸化物半導体を半導体層とする、トップゲート構造のトランジスタのひとつである。

【0092】

トランジスタ201は、基板200上に下地層221と、チャネル形成領域を有する酸化物半導体層202と、酸化物半導体層202と接し、チャネル形成領域を挟むように設けられたソース電極層211a、及びドレイン電極層211bと、チャネル形成領域と接して設けられたゲート絶縁層203と、ゲート絶縁層203と接し、チャネル形成領域、並びにソース電極層211a及びドレイン電極層211bの向かい合う端部と重畳するゲート電極層205と、を有する。また上記構成の全てを覆う層間絶縁層213を有し、層間絶縁層213にはソース電極層211a、及びドレイン電極層211bに達するコンタクトホール217を有する。コンタクトホール217内部にはソース電極層211a又はドレイン電極層211bと接するシリコンウィスカー215が設けられ、シリコンウィスカー215の上部は、それぞれ層間絶縁層213上に設けられたソース配線層219a、又はドレイン配線層219bと接している。

【0093】

シリコンウィスカー215は実施の形態1で示したものと同様、不純物が拡散され、導電性シリコンから成る。従って、ソース電極層211a又はドレイン電極層211b(以下、まとめて下部電極とも呼ぶ)と、ソース配線層219a、又はドレイン配線層219b(以下、まとめて上部電極とも呼ぶ)とを電気的に接続する。さらに、シリコンウィスカー215と下部電極、及び上部電極との接合はほぼオーミック接合となり、電気的障壁が極めて小さい。そのため、コンタクト抵抗の小さい良好なコンタクトが形成される。

【0094】

酸化物半導体層202のコンタクトホール217の底部と重畳する領域は、ソース電極層211a、又はドレイン電極層211bで覆われている。従って、ソース電極層211a、及びドレイン電極層211bは、後述するシリコンウィスカー215の形成時における、成膜ガス等が酸化物半導体層202に直接触れることによる影響を防ぐことができる。

【0095】

なお、シリコンウィスカー215と、上部電極、及び下部電極との界面において、金属とシリコンの反応により、シリサイドが形成されていてもよい。シリサイドが形成されると、シリコンウィスカー215と、上部電極、及び下部電極との接触抵抗が低減されるため、好ましい。

【0096】

《作成工程例》

次に、本発明の一態様であるトランジスタの作製方法の一例について説明する。以下では、トランジスタ201の作製方法について図5を用いて説明する。

【0097】

まず、基板200上に、下地層221を形成する。

【0098】

基板200は材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを、基板200として用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板200として用いてもよい。

【0099】

また、基板200として、可撓性基板を用いてもよい。可撓性基板上にトランジスタを設ける場合、可撓性基板上に直接的にトランジスタを作りこんでもよいし、他の基板にトランジスタを形成した後、これを剥離し、可撓性基板に転置してもよい。なお、トランジスタを剥離し、可撓性基板に転置するためには、上記他の基板とトランジスタとの間に剥離層を形成するとよい。

【0100】

下地層221は絶縁性を有する窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜などを用いることができる。また、下地層221は13族元素及び酸素を含む材料を用いて形成することもできる。13族元素及び酸素を含む材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、及び酸化ガリウムアルミニウムのいずれか一又は複数を含む材料などがある。下地層221は、上述の材料を用いて単層構造、又は積層構造で形成することができる。また、下地層221は後に形成する酸化物半導体膜とは異なる材料を含む絶縁膜と、酸化物半導体膜と同種の成分でなる絶縁材料でなる絶縁膜との積層構造とすることがより好ましい。例えば、酸化ガリウム膜と酸化シリコン膜の積層構造や、酸化ガリウム膜と窒化シリコン膜との積層構造などを適用することができる。

【0101】

下地層221は後に形成される酸化物半導体層202と接するため、水素、水などの不純物を混入させない方法を用いて形成することが好ましい。下地層221に水素、水などの不純物が含まれると、後に成膜される酸化物半導体膜に水素、水などの不純物の浸入や、水素、水などの不純物により酸化物半導体膜中の酸素の引き抜き、などによって酸化物半導体層202のバックチャネルが低抵抗化し、寄生チャネルが形成されるおそれがある。例えば、水素、水などの不純物が除去された高純度ガスを用いた、スパッタリング法によって形成するのが好ましい。

【0102】

次に、下地層221上に酸化物半導体層202、並びにソース電極層211a、及びドレイン電極層211bを形成する。

【0103】

酸化物半導体層202に用いる材料としては、少なくともIn、Ga、Sn、Zn、Al、Mg、Hf及びランタノイドから選ばれた一種以上の元素を含有する。例えば、四元系金属酸化物であるIn−Sn−Ga−Zn−O系や、三元系金属酸化物であるIn−Ga−Zn−O系、In−Sn−Zn−O系、In−Al−Zn−O系、Sn−Ga−Zn−O系、Al−Ga−Zn−O系、Sn−Al−Zn−O系、In−Hf−Zn−O系、In−La−Zn−O系、In−Ce−Zn−O系、In−Pr−Zn−O系、In−Nd−Zn−O系、In−Sm−Zn−O系、In−Eu−Zn−O系、In−Gd−Zn−O系、In−Tb−Zn−O系、In−Dy−Zn−O系、In−Ho−Zn−O系、In−Er−Zn−O系、In−Tm−Zn−O系、In−Yb−Zn−O系、In−Lu−Zn−O系や、二元系金属酸化物であるIn−Zn−O系、Sn−Zn−O系、Al−Zn−O系、Zn−Mg−O系、Sn−Mg−O系、In−Mg−O系、In−Ga−O系や、In−O系、Sn−O系、Zn−O系の金属酸化物材料などを用いることができる。また、上記の材料にSiO2を含ませてもよい。ここで、例えば、In−Ga−Zn−O系の材料とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物層、という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。

【0104】

また、酸化物半導体層202は、化学式InMO3(ZnO)m(m>0)で表記される材料を用いた薄膜により形成することができる。ここで、Mは、Ga、Al、Mn及びCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、Ga及びAl、Ga及びMnまたはGa及びCoなどを用いることができる。

【0105】

また、酸化物半導体層202に用いる酸化物半導体膜は、スパッタリング法で成膜することができる。また希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下において成膜することができる。その際のガスは、水素、水、水酸基を有する化合物、または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0106】

なお、酸化物半導体膜を成膜後、第1の加熱処理を行ってもよい。この第1の加熱処理によって酸化物半導体膜中の過剰な水(水酸基を含む)や水素などを除去することができる。第1の加熱処理の温度は350℃以上基板の歪み点未満、好ましくは400℃以上基板の歪み点未満とすることができる。また、第1の加熱処理は窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とし、水、水素などの不純物が除去された高純度なガスの雰囲気下で行うことが望ましい。

【0107】

続いてソース電極層211a及びドレイン電極層211bに用いる金属膜を成膜する。金属膜は、後に形成するシリコンウィスカーを形成可能な材料を選択する。このような材料としては、例えばチタン、ニッケル、コバルト、鉄等がある。また、金属膜はできるだけ水素、水などの不純物が除去された高純度ガスを用いたスパッタリング法で成膜することが好ましい。

【0108】

酸化物半導体膜、及び金属膜を形成した後、これらを選択的にエッチングすることにより、島状の酸化物半導体層202、並びにソース電極層211a、及びドレイン電極層211bを形成する。

【0109】

なお、金属膜のエッチングの際に酸化物半導体層202がエッチングされ、分断することのないようにエッチング条件を最適化することが望まれる。しかしながら、金属膜のみをエッチングし、酸化物半導体層202をまったくエッチングしないという条件を得ることは難しく、金属膜のエッチングの際に酸化物半導体層202は一部のみがエッチングされ、溝部(凹部)を有する酸化物半導体層202となることもある。

【0110】

なお、酸化物半導体層202と、ソース電極層211a、及びドレイン電極層211bとの間に、導電性の層を有していてもよい。例えば酸化物半導体層との接触抵抗の低い材料を間に形成することにより、コンタクト抵抗を低減することができる。

【0111】

この段階の断面概略図を図5(A)に示す。

【0112】

次に、ゲート絶縁層203を形成する。

【0113】

ゲート絶縁層203は、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜等の単層、または積層構造とすることができる。酸化物半導体層202と接する層は酸化物絶縁層とすることが好ましい。ゲート絶縁層203の成膜方法としては、プラズマCVD法やスパッタリング法等を用いることができるが、層中に水素が多量に含まれないようにするためには、スパッタリング法で成膜することが好ましい。

【0114】

続いて、ゲート電極層205を形成する。

【0115】

ゲート電極層205を形成する導電膜の材料としては、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料、またはこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。導電膜の成膜方法としては、スパッタリング法を用いることができる。

【0116】

上記導電膜を成膜後、選択的にエッチングすることによりゲート電極層205を形成する。

【0117】

次に、上述の工程により形成された各構成を覆う層間絶縁層213を形成する。層間絶縁層213は実施の形態1で示したような材料、方法で適宜形成することができる。層間絶縁層213となる絶縁膜を成膜後、その表面をCMPやエッチング処理により平坦化することが好ましい。

【0118】

続いて、層間絶縁層213にソース電極層211a、及びドレイン電極層211bにまで達するコンタクトホール217を形成する。コンタクトホール217を形成する際の層間絶縁層213、及びゲート絶縁層203のエッチングには、ソース電極層211a、及びドレイン電極層211bに用いた金属膜に対して、層間絶縁層213及びゲート絶縁層203のエッチングの選択比が高い方法を用いることができる。また、半導体素子が高度に微細化される場合には、エッチングによるコンタクトホールの広がりを抑制するため、異方性のドライエッチングを用いることが好ましい。また、ゲート絶縁層203に対する層間絶縁層213とのエッチングの選択比の高い方法を用いて、まず層間絶縁層213をゲート絶縁層203が露出するまでエッチングし、その後ゲート絶縁層203をエッチングしてもよい。こうすることで、金属膜に対する層間絶縁層213及びゲート絶縁層203のエッチングの選択比が高くない場合でもソース電極層211a、及びドレイン電極層211bがエッチングされて消失することを抑制することができる。このような方法を適宜用いて、層間絶縁層213とゲート絶縁層203を選択的にエッチングすることにより、コンタクトホール217が形成される。

【0119】

この段階の断面概略図を図5(B)に示す。

【0120】

次に、コンタクトホール217内にシリコンウィスカー215を形成する。

【0121】

シリコンウィスカー215は、実施の形態1で示したように、熱CVD法、好ましくはLPCVD法を用いて形成する。酸化物半導体層202のコンタクトホール217と重畳する領域は、ソース電極層211a、又はドレイン電極層211bで覆われており、成膜ガスが直接酸化物半導体層に触れることなく、シリコンウィスカー215を形成することができる。従って、LPCVD法に用いる成膜ガスに水素を含む場合であっても、酸化物半導体層への水素などの不純物の浸入を防ぐことができる。また、酸化物半導体層への成膜ガス、又は成膜ガスに含まれる不純物の影響を考慮することなく、シリコンウィスカー215の成膜に最適な成膜ガスを選択することができる。

【0122】

シリコンウィスカー215の形成中、一導電性を付与する不純物元素を添加することにより、シリコンウィスカー215は導電性に導電性を持たせることができる。シリコンウィスカーの導電型はn型でもp型でもどちらでもよい。シリコンウィスカーを十分に低抵抗化することにより、上部電極、及び下部電極との接触抵抗を低減することができ、低抵抗なコンタクトを実現できる。

【0123】

このようにして形成されたシリコンウィスカー215は、実施の形態1で示したように、結晶性を有する。またその成長方向とシリコンウィスカーを構成する結晶の結晶方位の少なくともひとつが略一致していてもよい。このような結晶性を有することで、より電気伝導性に優れたシリコンウィスカーとすることができ、コンタクト抵抗の小さい良好なコンタクトを形成することができる。

【0124】

また、シリコンウィスカー215は、成膜方法、条件の違いによって実施の形態1で示したような、様々な形状を取ることができる。

【0125】

続いて、シリコンウィスカー215の形成中に層間絶縁層213上に形成された不要なシリコン薄膜を実施の形態1で示したような方法でエッチングにより除去する。なお、層間絶縁層213上に該シリコン薄膜が形成されなかった場合は、この工程を省略することができる。

【0126】

以上の工程により、コンタクトホール217内部にシリコンウィスカー215が形成される。なお、この段階の断面概略図を図5(C)に示す。

【0127】

続いて、ソース配線層219a、及びドレイン配線層219bを形成する。

【0128】

ソース配線層219a、及びドレイン配線層219bに用いる導電膜は、実施の形態1で示したような材料、方法により適宜成膜することができる。その後、導電膜を選択的にエッチングすることにより、ソース配線層219a、及びドレイン配線層219bが形成される。

【0129】

なお、シリコンウィスカー215と、上部電極、及び下部電極との界面において、金属とシリコンの反応により、シリサイドが形成されていてもよい。シリサイドが形成されると、シリコンウィスカー215と、上部電極、及び下部電極との接触抵抗が低減されるため、好ましい。

【0130】

ソース配線層219a、及びドレイン配線層219bを形成後、第2の加熱処理を行っても良い。第2の加熱処理は大気中、不活性ガス雰囲気下、または酸素雰囲気下で好ましくは100℃以上200℃以下で行うことができる。また、室温から、100℃以上200℃以下の加熱温度への昇温と、加熱温度から室温までの降温を繰り返し行っても良い。

【0131】

以上の工程により、トランジスタ201が形成される。この段階の断面概略図を図5(D)に示す。

【0132】

なお、本実施の形態では、トップゲート型のトランジスタ201の構成及び作製方法について説明したが、本発明はトランジスタの構成は特に限定されず、ボトムゲート型のトランジスタなどにも適用することができる。一例として、図4(B)にボトムゲート型のトランジスタに適用した例を示す。図4(B)に示すトランジスタ241は、逆スタガ構造と呼ばれる、ボトムゲート型のトランジスタのひとつである。トランジスタ241を作製するには、下地層221上にゲート電極層205、ゲート絶縁層203、酸化物半導体層202、ソース電極層211a及びドレイン電極層211bの順に形成し、層間絶縁層213の形成以降の工程はトランジスタ201の作製工程と同じとすればよい。

【0133】

なお、本実施の形態では、半導体層に酸化物半導体を用いたトランジスタの構成、及び作製方法について説明したが、半導体層に用いる半導体はこれに限らず、シリコンや炭化シリコンなどの単結晶半導体、多結晶半導体、シリコンゲルマニウムなどの化合物半導体などの半導体を半導体層に用いた半導体装置にも本発明は適用することができる。

【0134】

このように作製したトランジスタは、高集積化に伴う細く、アスペクト比の高いコンタクトホールに対しても、接続電極の断線などの影響がなく、信頼性の高いコンタクトを得ることができる。さらに、コンタクトホール内のシリコンウィスカーの形成時における、成膜ガス起因の不具合を受けることなく、電気的特性の良好なトランジスタを形成することができる。

【0135】

また、本実施の形態ではトランジスタの構成、及び作製方法を一例に挙げて説明したが、コンタクトホール底部の金属からなる下部電極と接する、導電性シリコンウィスカーを接続電極としたコンタクトの形成方法は、ダイオード素子、容量素子、抵抗素子など、層間絶縁層を介した、配線の接続部を有する半導体装置であれば適用することが可能である。これらの半導体装置に適用した場合でも同様に、デバイスの高集積化に伴う細く、アスペクト比の高いコンタクトホールに対して、接続電極の断線などの影響がなく、良好なコンタクトを有する半導体装置とすることができる。

【0136】

本実施の形態で例示した半導体装置の構成、および半導体装置の作製方法によれば、半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を実現できる。

【0137】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【符号の説明】

【0138】

100 基板

101 トランジスタ

103 ゲート絶縁層

105 ゲート電極層

107 サイドウォール

109a ソース領域

109b ドレイン領域

111 金属化合物層

113 層間絶縁層

115 シリコンウィスカー

117 コンタクトホール

119a ソース配線層

119b ドレイン配線層

121 素子分離層

123 金属層

200 基板

201 トランジスタ

202 半導体層

203 ゲート絶縁層

205 ゲート電極層

211a ソース電極層

211b ドレイン電極層

213 層間絶縁層

215 シリコンウィスカー

217 コンタクトホール

219a ソース配線層

219b ドレイン配線層

221 下地層

241 トランジスタ

【技術分野】

【0001】

本発明は半導体装置に関する。本発明は半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、半導体素子を用いた電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

近年、デバイス素子の高密度集積化に伴い、個々の素子の微細化が必要となってきている。ここで問題となる事柄のひとつに、微細化に伴うコンタクト不良が挙げられる。

【0004】

コンタクト不良とは、配線電極と半導体装置との電気的な接続箇所(以降、コンタクトとも呼ぶ)が、接続不良を起こしたときに生じる動作不良のことである。特に、微細化技術と多層配線技術とにより、層間絶縁層に設けられた細いコンタクトホールを介して電気的接続を取る必要性が高まっている。

【0005】

半導体装置の微細化に伴う、細く、アスペクト比の高いコンタクトホールの場合、配線電極を形成する導電膜のカバレッジ不良によるコンタクトホール内での配線電極の断線や、コンタクトホール内部に導電膜が形成されるより前に、オーバーハングによりコンタクトホール上部が導電膜で塞がれて配線電極がコンタクトホール内に形成できないといった問題がある。

【0006】

これらの問題を解決するため、例えば特許文献1に示されているように、柱状のシリコン単結晶を用いて電気的接続をとる方法が考案されている。これは単結晶シリコン基板上に金などの低融点金属材料を用いたVLS(Vapor−Liquid−Solid)成長法によりシリコンの柱状単結晶を形成し、その後この柱状単結晶これに導電性を持たせるために不純物をドープし、接続電極として用いる方法である。

【0007】

また別の技術として、特許文献2に示されているように、単結晶シリコン基板上に形成したトランジスタのソース領域、及びドレイン領域を露出させるコンタクトホールを形成した後、コンタクトホール内部に不純物を含むエピタキシャルシリコン層を形成し、これを接続電極として用いる方法が考案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭61−248471号公報

【特許文献2】特開2008−130756号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、上記に代表される微細コンタクトの形成技術では、以下のような問題がある。トランジスタなどの半導体装置と配線電極との接続電極を形成する場合、接続電極として用いる柱状のシリコン層は半導体層上に形成(成膜)され、またその際に半導体層が成膜雰囲気に曝される。しかし、このような環境で柱状のシリコン層を形成すると、半導体装置の電気的特性に悪影響を及ぼす場合がある。

【0010】

例えば、同一基板上にシリコンを半導体層に用いるnチャネル型トランジスタとpチャネル型トランジスタを形成することは、従来のCMOS技術によって半導体回路を形成する上で重要である。柱状のシリコン層はこれらトランジスタのソース領域及びドレイン領域上に形成される。具体的には、nチャネル型トランジスタではn型シリコン層上に、pチャネル型トランジスタではp型シリコン層上に柱状のシリコン層が形成される。特許文献2によれば接続電極に用いる柱状のシリコン層を形成する際に、同時にリンを含むガスを添加することにより柱状のシリコン層をn型シリコンとしているが、この場合pチャネル型トランジスタでは接続電極とソース領域、又はドレイン領域との界面で、いわゆるpn接合が形成され、この電気的障壁によりコンタクト抵抗が高くなる問題がある。また、特許文献1によれば、この問題を回避するのにnチャネル型トランジスタとpチャネル型トランジスタとで柱状のシリコン層へのドープを2度に分けて行う必要が生じるが、その際、高いアスペクト比をもつ柱状のシリコン層を覆うドープマスクを形成することは困難であり、また作製工程が煩雑になる。

【0011】

また、金属酸化物半導体を半導体層としたトランジスタなどの半導体装置においては、柱状のシリコン層を形成する成膜ガス、例えばシランガス中に含まれる水素はトランジスタ特性に影響を及ぼす。酸化物半導体中の水素はバンドギャップ中のドナー準位を形成しやすいため、成膜ガス中に含まれる水素が酸化物半導体中に拡散すると、トランジスタのスイッチング特性などの電気的特性に悪影響を及ぼす。

【0012】

本発明は、この様な技術的背景を鑑みてなされたものである。したがって本発明は、半導体素子の特性を損なうことなく微細化に伴うコンタクト不良の発生が抑制された、電気的特性の良好な半導体装置と、その作製方法を提供することを課題とする。

【課題を解決するための手段】

【0013】

上記目的を達成するために、本発明の一態様では、半導体層と電気的に接続する金属、又は金属化合物からなる下部電極を設け、下部電極上に導電性のシリコンウィスカーを形成し、これをコンタクトにおける接続電極として用いる。

【0014】

すなわち、半導体層の上面にこれと電気的に接続する金属、又は金属化合物からなる下部電極を設け、この下部電極の一部が露出するように層間絶縁層に形成されたコンタクトホール内に、接続電極となる導電性シリコンウィスカーを形成する。その後、導電性シリコンウィスカーと電気的に接続する上部電極を形成すればよい。またこの様に作製したコンタクトを用いて半導体装置を作製すればよい。

【0015】

接続電極となるシリコンウィスカーは下部電極から成長させることが可能である。従って微細化技術に伴う、細く、アスペクト比の高いコンタクトホールであっても、上下の電極が断線することなく確実に電気的に接続することができる。

【0016】

また、半導体層のコンタクトホールと重なる部分は、金属、又は金属化合物からなる下部電極に覆われており半導体層は露出しない。この下部電極はシリコンウィスカー形成時の半導体層に対する保護膜としての機能を有するため、シリコンウィスカーの形成時において、成膜ガス、及び成膜ガスに含まれる不純物の半導体層中への浸入、及び拡散が抑制される。

【0017】

さらに、接続電極となるシリコンウィスカーに導電性を持たせるために、不純物を拡散させてn型シリコン、又はp型シリコンとする。シリコンウィスカーは下部電極である金属、又は金属化合物と接するため、これらの接合はほぼオーミック接合となり、その電気的障壁は極めて小さくなる。さらに、単純にシリコンウィスカーを低抵抗化すればよいため拡散させる不純物の種類は限定されず、このため単一のドーピング工程で形成できる。

【0018】

また、接続電極となるシリコンウィスカーと上部電極との間に、シリコンウィスカーに含まれるシリコンと上部電極に含まれる材料との反応によってシリサイド層が形成されていてもよい。シリサイド層が形成されることにより、接続電極と上部電極との接触抵抗を小さくすることができる。

【0019】

すなわち、本発明の一態様は、半導体層と、半導体層の上面と電気的に接続する下部電極と、下部電極上にコンタクトホールを備え且つ半導体層を覆う絶縁層と、導電性シリコンウィスカーを含み、且つコンタクトホールにおいて下部電極と接する接続電極と、絶縁層上に、接続電極と電気的に接続する上部電極と、を有する半導体装置である。

【0020】

このような半導体装置は、デバイスの微細化に伴う、細く、アスペクト比の高いコンタクトホールであっても、上下の電極を断線することなく確実に電気的に接続することができる。

【0021】

また本発明の一態様は、上記下部電極が、金属、又は半導体層を構成する半導体と金属とを含む金属化合物を有する半導体装置である。

【0022】

下部電極を金属、又は金属化合物とすることにより、接続電極である導電性シリコンウィスカーと下部電極との接触抵抗を小さくできるため、コンタクト抵抗の小さい半導体装置とすることができる。

【0023】

また本発明の一態様は、上記導電性シリコンウィスカーと上記上部電極との間に、シリサイド層を有する半導体装置である。

【0024】

シリコンウィスカーと上部電極との間にシリサイド層が形成されていることにより、シリコンウィスカーと上部電極との接触抵抗を小さくできるため、コンタクト抵抗の小さい半導体装置とすることができる。

【0025】

また本発明の一態様は、上記半導体装置において、上記接続電極は、二以上の導電性シリコンウィスカーを含む。

【0026】

複数のシリコンウィスカーからなるシリコンウィスカー群で接続電極を構成することにより、断線の危険性がより低くなり、コンタクト不良を低減できる。

【0027】

また、本発明の一態様は、半導体層の上面と電気的に接続する下部電極を形成し、半導体層と下部電極とを覆う絶縁層を形成し、絶縁層に、下部電極と重なるコンタクトホールを形成する。またコンタクトホールにおいて、下部電極と接し且つ導電性シリコンウィスカーを含む接続電極を形成し、絶縁層上に、接続電極と電気的に接続する上部電極を形成する、半導体装置の作製方法である。

【0028】

また、本発明の一態様は、半導体層の上面と接する金属膜を形成し、半導体層を構成する材料と金属膜を構成する材料とを含み且つ半導体層の上面に接する金属化合物層を形成した後、金属膜を除去し、続いて半導体層と金属化合物層とを覆う絶縁層を形成し、絶縁層に、金属化合物層と重なるコンタクトホールを形成し、さらにコンタクトホールにおいて、金属化合物層と接し且つ導電性シリコンウィスカーを含む接続電極を形成し、絶縁層上に、接続電極と電気的に接続する上部電極を形成する、半導体装置の作製方法である。

【0029】

このような方法で半導体装置を作製することにより、シリコンウィスカー形成時における、成膜ガス、及び成膜ガスに含まれる不純物の半導体層への浸入、及び拡散が抑制され、電気的特性の良好な半導体装置が作製できる。

【0030】

なお、本明細書等において、コンタクトとは配線電極と半導体装置との電気的な接続箇所のことを言う。またこれは、半導体装置の有する電極と、配線電極とをコンタクトホール内部に設けられた接続電極を介して電気的に接続する接続箇所をも含むこととする。

【0031】

また、本明細書等において、シリコンウィスカーとは突起(髭)状の結晶性シリコンであり、複数のシリコンウィスカーにおいて、各々の突起の伸長方向(すなわち、軸の方向)は、不揃いであってもよい。本明細書等においてシリコンウィスカーとの表記には、シリコンウィスカー群(複数のシリコンウィスカー)を含むことがある。また、本明細書等において、結晶性を有するとは、アモルファスではないことを指し、単結晶、多結晶、微結晶又は準結晶であることを含む。

【発明の効果】

【0032】

本発明によれば、半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置と、その作製方法を提供できる。

【図面の簡単な説明】

【0033】

【図1】本発明の一態様の、トランジスタを説明する図。

【図2】本発明の一態様の、トランジスタの作製方法を説明する図。

【図3】本発明の一態様の、コンタクトを説明する図。

【図4】本発明の一態様の、トランジスタを説明する図。

【図5】本発明の一態様の、トランジスタの作製方法を説明する図。

【発明を実施するための形態】

【0034】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0035】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0036】

(実施の形態1)

本実施の形態では、本発明の一態様であるトランジスタの構成とその作製方法について図1乃至図3を用いて説明する。

【0037】

《トランジスタの構成例》

図1に、本実施の形態で例示するトランジスタ101の断面概略図を示す。

【0038】

トランジスタ101は半導体材料(例えばシリコンなど)を含む基板100に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられたソース領域109a、及びドレイン領域109bと、チャネル形成領域上に接して設けられたゲート絶縁層103と、ゲート絶縁層103に接し、チャネル形成領域と重畳するゲート電極層105と、を有する。ゲート電極層105の側面にはサイドウォール107が設けられ、ソース領域109a、及びドレイン領域109b上にはそれぞれ金属化合物層111が設けられている。また、金属化合物層111、ゲート絶縁層103、サイドウォール107、及びゲート電極層105を覆う層間絶縁層113が設けられており、層間絶縁層113は金属化合物層111に達するコンタクトホール117を有する。コンタクトホール117の内部には金属化合物層111に接するシリコンウィスカー115が設けられ、シリコンウィスカー115の上部はそれぞれ層間絶縁層113上に設けられたソース配線層119a、及びドレイン配線層119bと接している。

【0039】

なお、トランジスタ101は、nチャネル型のトランジスタとしても良いし、pチャネル型のトランジスタとしても良い。

【0040】

また、図1に示すように、基板100には、図示されていない隣接する半導体素子とトランジスタ101とを分離する素子分離層121が埋め込まれている。

【0041】

シリコンウィスカー115は接続電極としての機能を有し、導電性を持たせるため不純物が拡散されている。また、その下部は金属化合物層111を介してそれぞれソース領域109a及びドレイン領域109bと電気的に接続される。一方その上部はそれぞれソース配線層119a、及びドレイン配線層119bと接し、電気的に接続されている。したがって、トランジスタ101のソース領域109a、及びドレイン領域109bは、金属化合物層111及びシリコンウィスカー115を介してそれぞれソース配線層119a、又はドレイン配線層119bと電気的に接続される。

【0042】

金属化合物層111は、不純物が拡散されたソース領域109a、及びドレイン領域109bの一部から成り、ソース領域109a及びドレイン領域109bを構成する半導体と金属とが反応して低抵抗化された金属化合物で構成される。従って、金属化合物層111と接するシリコンウィスカー115の有する導電性がn型、又はp型のどちらであるかによらず、これらの接合はほぼオーミック接合となり電気的障壁が極めて小さい。さらに、ソース領域109a、及びドレイン領域109bの有する導電性がn型、又はp型のどちらであっても、シリコンウィスカー115の導電型は問われず、同一の導電型を有するシリコンウィスカー115を接続電極として用いることができる。

【0043】

なお、シリコンウィスカー115の上端と、ソース配線層119a、又はドレイン配線層119bとの界面において、金属とシリコンの反応により、シリサイドが形成されていてもよい。シリサイドが形成されると、シリコンウィスカー115と、ソース配線層119a、又はドレイン配線層119bとの接触抵抗が低減されるため、好ましい。

【0044】

《作製工程例》

次に、本発明の一態様であるトランジスタの作製方法の一例について説明する。以下ではトランジスタ101の作製方法について図2、及び図3を用いて説明する。

【0045】

まず、半導体材料を含む基板100を用意する。半導体材料を含む基板100としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができる。ここでは、半導体材料を含む基板100として、単結晶シリコン基板を用いる場合の一例について示すものとする。なお、一般に「SOI基板」は、絶縁表面上にシリコン半導体層が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が設けられた構成の基板をも含むこととする。つまり、SOI基板には、ガラス基板などの絶縁基板上に絶縁層を介して半導体層が設けられた構成も含まれるものとする。

【0046】

次に、基板100上に素子分離層121を形成する。

【0047】

基板100上に素子分離層121を形成するためのマスクとなる保護層を形成する。例えば、酸化シリコンや窒化シリコン、窒化酸化シリコンなどを材料とする絶縁膜を用いることができる。なお、この工程の前後において、トランジスタのしきい値電圧を制御するために、n型の導電性を付与する不純物元素や、p型の導電性を付与する不純物元素を基板100に添加しても良い。基板100に含まれる半導体材料がシリコンの場合、n型の導電性を付与する不純物としては、例えばリンや砒素などを用いることができる。また、p型の導電性を付与する不純物としては、例えば、ホウ素、アルミニウム、ガリウムなどを用いることができる。

【0048】

次に上記の保護層をマスクとして、保護層に覆われていない領域(露出している領域)の基板100の一部をエッチングにより除去する。これにより分離された半導体領域が形成される。当該エッチングには、ドライエッチングを用いるのが好適であるが、ウェットエッチングを用いても良い。エッチングガスやエッチング液については、被エッチング材料に応じて適宜選択することができる。

【0049】

次に、基板100全体を覆うように絶縁層を形成し、上記半導体領域に重畳する領域の当該絶縁層を選択的に除去することにより、素子分離層121を形成する。当該絶縁層は酸化シリコンや窒化シリコン、窒化酸化シリコンなどを用いて形成される。絶縁層の除去方法としては、CMP(Chemical Mechanical Polishing)などの研磨処理やエッチング処理などがあるが、そのいずれを用いても良い。なお、半導体領域の形成後、または、素子分離層121の形成後には、上記保護層を除去する。

【0050】

次に、基板100上に絶縁層を形成し、当該絶縁層上に導電材料を含む層を形成する。

【0051】

上記絶縁層は、後のゲート絶縁層103となるものであり、CVD法やスパッタリング法等を用いて得られる酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y>0))等を含む膜の単層構造または積層構造とすると良い。他に、高密度プラズマ処理や熱処理(熱酸化処理や熱窒化処理など)によって、基板100の表面を酸化、窒化することにより上記絶縁層を形成しても良い。高密度プラズマ処理は、例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素、アンモニア、窒素などとの混合ガスを用いて行うことができる。また、絶縁層の厚さは特に限定されないが、例えば1nm以上100nm以下とすることができる。

【0052】

導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、導電材料を含む多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンコート法など、各種成膜方法を用いることができる。なお、本実施の形態では、導電材料を含む層を、金属材料を用いて形成する場合の一例について示すものとする。

【0053】

その後、導電材料を含む層を選択的にエッチングして、ゲート電極層105を形成する。

【0054】

次に、サイドウォール107を形成する。サイドウォール107は、ゲート電極層105を覆うように絶縁層を形成した後に、当該絶縁層に異方性の高いエッチング処理を適用することで、自己整合的に形成することができる。

【0055】

なお、サイドウォール107を形成する際のエッチング処理により、ゲート絶縁層103となる絶縁層の、ゲート電極層105、及びサイドウォール107に覆われていない部分も同時にエッチングされ、ゲート絶縁層103も形成される。

【0056】

サイドウォール107を設けることにより、後述の不純物を添加する工程において、不純物元素が異なる濃度で添加された不純物領域を形成することができる。こうすることで短チャネル効果などの影響を抑制することができ、好ましい。なお、高集積化が要求される場合には、サイドウォールを有しない構成とすることにより、トランジスタサイズを縮小することができる。

【0057】

次に、ゲート電極層105、及びサイドウォール107をマスクとして用い、リンや砒素などの不純物を添加して、ソース領域109a、及びドレイン領域109bを形成する。なお、ここではpチャネル型のトランジスタを形成するためにホウ素やアルミニウムなどの不純物元素を添加しているが、nチャネル型のトランジスタを形成する場合には、リンや砒素などの不純物元素を添加すればよい。添加する不純物の濃度は適宜設定することができるが、半導体素子が高度に微細化される場合には、その濃度を高くすることが望ましい。なお、不純物元素の添加後には加熱処理を行い、不純物元素の活性化や不純物元素の添加時に生じる欠陥の改善等を図るのが望ましい。この加熱処理は後述するシリコンウィスカー115の形成工程と兼ねることもできる。

【0058】

この段階における断面概略図を図2(A)に示す。

【0059】

次に、金属化合物層111を形成する。

【0060】

まず、ゲート電極層105、サイドウォール107、並びにソース領域109a、及びドレイン領域109bを覆う金属層123を形成する。金属層123は、真空蒸着法やCVD法、スパッタリング法、スピンコート法などの各種成膜方法を用いて形成することができる。金属層123には、基板100を構成する半導体材料と反応して低抵抗な金属化合物を生成できる金属材料を用いる。さらに、当該金属化合物が後に形成するシリコンウィスカーを形成可能な材料を選択する。つまり、シリコンウィスカーの成長を促進する触媒として機能する金属元素を含む材料を選択することができる。例えば、シリサイドを形成する金属元素を好ましく用いることができる。例えば、チタン、ニッケル、コバルト、鉄等がある。

【0061】

次に、熱処理を施して、金属層123と半導体材料を反応させる。これにより、ソース領域109a、及びドレイン領域109bに接する金属化合物層111が形成される。なお、ゲート電極層105として多結晶シリコンなどを用いた場合は、ゲート電極層105の金属層123と接触する部分にも、金属化合物領域が形成されることとなる。

【0062】

上記熱処理としては、例えば、フラッシュランプの照射による熱処理を用いることができる。もちろん、その他の熱処理方法を用いても良いが、金属化合物の形成に係る化学反応の制御性を向上させるためには、ごく短時間の熱処理を実現できる方法を用いることが望ましい。なお、金属化合物層111は、金属材料と半導体材料との反応により形成されるものであり、十分に導電性が高められた領域である。金属化合物層111を形成することで、電気抵抗を十分に低減し、素子特性を向上させることができる。この段階の断面概略図を図2(B)に示す。

【0063】

金属化合物層111を形成した後、金属層123を除去する。

【0064】

次に、上述の工程により形成された各構成を覆うように、層間絶縁層113を形成する。層間絶縁層113は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル等の無機絶縁材料を含む膜の単層構造または積層構造とすることができる。また、後の工程の熱処理に耐えうるのであれば、ポリイミド、アクリル樹脂等の有機絶縁材料を用いて形成することもできる。層間絶縁層113となる絶縁膜を形成後、その表面をCMPやエッチング処理などによって平坦化することが好ましい。平坦化することにより、後に形成するソース配線層119a及びドレイン配線層119bなどの配線層の段切れなどの不具合を防ぐことができるため好ましい。なお、当該平坦化処理は必要でなければ工程を簡略化できるため行わなくても良い。

【0065】

続いて、層間絶縁層113に一対の金属化合物層111にまで達するコンタクトホール117を形成する。コンタクトホール117を形成する際の層間絶縁層113のエッチングには、金属化合物層111に対する層間絶縁層113のエッチングの選択比が高い方法を用いることができる。半導体素子が高度に微細化される場合には、エッチングによるコンタクトホールの広がりを抑制するため、異方性のドライエッチングを用いることが好ましい。

【0066】

次に、コンタクトホール117内にシリコンウィスカー115を形成する。

【0067】

シリコンウィスカー115は、金属化合物層111上に、熱CVD法、好ましくはLPCVD(Low Pressure Chemical Vapor Deposition)法により形成できる。LPCVD法を用いることで、シリコンウィスカー115を金属化合物層111から選択的に成長させることができる。なお、シリコンウィスカー115には、不純物として、LPCVD装置のチャンバーに起因する酸素などが含まれている場合がある。

【0068】

本実施の形態では、LPCVD法によりシリコンウィスカー115を形成する。LPCVD法は、550℃より高い温度で且つ装置、または上述の工程により形成された各構成が耐えうる温度以下、好ましくは580℃以上650℃未満の加熱をしつつ、原料としてシリコンを含む堆積性ガスを用いる。シリコンを含む堆積性ガスとしては、水素化シリコン、フッ化シリコン、または塩化シリコンなどがあり、代表的には、SiH4、Si2H6、SiF4、SiCl4、Si2Cl6などがある。なお、原料ガスに、ヘリウム、ネオン、アルゴン、キセノン等の希ガス、及び窒素、水素などの一以上を混合させても良い。

【0069】

さらに、シリコンウィスカー115に導電性を持たせるため、シリコンウィスカーの形成中に一導電型を付与する不純物元素を添加する。一導電型を付与する不純物元素のうち、LPCVD法に用いるのに適しているものとして、例えばn型の導電性を付与するにはリンや砒素などが挙げられ、他方p型の導電性を付与するにはホウ素などが挙げられる。

【0070】

シリコンウィスカー115の導電型はn型でもp型でもどちらでもよく、十分に低抵抗化していればよい。上述のようにシリコンウィスカーと接する金属化合物層111は低抵抗化された金属化合物を含んでいる。従ってシリコンウィスカーの導電型によらず、これらの接合はほぼオーミック接合となるため電気的障壁が極めて小さくなる。従って、金属化合物層111とシリコンウィスカー115との接触抵抗は小さく、またシリコンウィスカー自体も低抵抗化されているため、低抵抗なコンタクトを実現できる。

【0071】

本実施の形態では、一導電型を付与する不純物元素としてリンを用い、シリコンウィスカー115をn型の導電性シリコンとした。

【0072】

また、シリコンウィスカー115をLPCVD法などの加熱工程を含む方法で形成するため、上述のソース領域109a及びドレイン領域109bに添加した不純物元素の活性化や不純物元素の添加時に生じる欠陥の改善のための加熱処理を同時に行うことができる。

【0073】

また、シリコンウィスカー115は結晶性を有している。またその成長方向とシリコンウィスカー115を構成する結晶の結晶方位の少なくともひとつが略一致していてもよい。このようなシリコンウィスカー115とすることで、例えばアモルファスシリコンや、結晶方位に規則性のない一般的な多結晶シリコン又は微結晶シリコンなどと比べて電気伝導性に優れている。従って、このような結晶性を有するシリコンウィスカー115を用いてコンタクトを形成することにより、コンタクト抵抗の小さい良好なコンタクトを形成することができる。

【0074】

また、シリコンウィスカー115は結晶性の突起であれば、その形状は特に限定されない。例えば、円柱状、角柱状などの柱状、円錐状、角錐状などの針状でもよい。また、シリコンウィスカーの頂部は、湾曲した形状を有していても良い。また、シリコンウィスカーの直径は50nm以上コンタクトホールの径以下、好ましくは100nm以上3μm以下とする。

【0075】

また、シリコンウィスカー115とコンタクトホール117の壁面との間には隙間があってもよいし、シリコンウィスカー115によってコンタクトホール117が完全に埋まっていてもよい。隙間がある場合は、後に形成する上部電極との接触面積が大きくなるため、これらの接触抵抗を低くすることができる。また、隙間がなく完全に埋まっている場合は機械的強度が高くなるため、外力などが加わっても接触不良を起こしにくい。

【0076】

また、ひとつのコンタクトホールに複数のシリコンウィスカーからなるシリコンウィスカー群が形成されてもよい。その際、シリコンウィスカー同士が接していてもよいし、間隔があってもよい。また二以上のシリコンウィスカーが束状になっていてもよい。シリコンウィスカー群を接続電極として用いることにより、例えばひとつのシリコンウィスカーが断線したとしても、他のシリコンウィスカーにより電気的接続が保たれるため、断線の危険性がより低くなり、コンタクト不良を低減できる。

【0077】

LPCVD法を用いてコンタクトホール117内にシリコンウィスカー115を形成する際、層間絶縁層113上にはシリコンウィスカーは形成されない。しかし、層間絶縁層113上にはアモルファスシリコン、ポリシリコン、微結晶シリコンなどの薄いシリコン薄膜が成膜される場合がある。

【0078】

層間絶縁層113上に成膜された不要なシリコン薄膜をエッチングにより除去する。その際、シリコンウィスカー115と、層間絶縁層113上に形成されたシリコン薄膜との結晶性の違いに由来するエッチング速度の差を利用して、シリコンウィスカー115に対するシリコン薄膜のエッチングの選択比を大きくとれる条件でシリコン薄膜のみを除去すればよい。なお、層間絶縁層113上に該シリコン薄膜が形成されなかった場合は、この工程を省略することができる。

【0079】

この段階での断面概略図を図2(C)に示す。

【0080】

次に、ソース配線層119a、及びドレイン配線層119bを形成する。

【0081】

まず、導電膜を形成する。導電膜はアルミニウムや銅、チタン、タンタル、タングステン等の金属材料からなる膜の単層、又は積層を用いることができる。形成方法も特に限定されず、蒸着法、CVD法、スパッタリング法、スピンコート法など、各種成膜方法を用いることができる。その後、導電膜を選択的にエッチングし、ソース配線層119a、及びドレイン配線層119bを形成する。

【0082】

なお、導電膜の形成以降、この導電膜に用いる金属とシリコンウィスカー115とで反応が起こり、シリコンウィスカー115と導電膜との界面にシリサイドが形成される場合がある。シリサイドが形成されると、シリコンウィスカー115と導電膜との接触抵抗が低減されるため好ましい。

【0083】

以上の工程により、トランジスタ101が形成される。この段階での断面概略図を図2(D)に示す。

【0084】

なお、シリコンウィスカー115の形成条件により、コンタクトホール117内部のシリコンウィスカー115は様々な形状を取り得る。図3にそのシリコンウィスカー115の形状について例示する。図3(A1)、図3(B1)、図3(C1)、及び図3(D1)はコンタクトホール117の近傍を抜き出して描いた断面概略図であり、図3(A2)、図3(B2)、図3(C2)、及び図3(D2)はそれぞれ、図3(A1)、図3(B1)、図3(C1)、及び図3(D1)中の破線で示す箇所で切断した際の上面概略図である。図3(A1)及び図3(A2)に示すシリコンウィスカー115は一本の円柱状であり、コンタクトホール117の壁面との間に隙間が生じている。隙間が生じることにより、上部電極はシリコンウィスカー115の側面とも接触することができ、その結果接触面積が大きくなり、これらの接触抵抗を低くすることができる。図3(B1)及び図3(B2)ではシリコンウィスカー115によってコンタクトホール117内部が隙間なく埋まっている。従って、機械的強度が高まり、外力などが加わっても接触不良を起こしにくい。また、図3(C1)及び図3(C2)のように細い円柱状のシリコンウィスカー115がまばらに配置されていてもよい。このような構成では、より上部電極との接触面積を大きくすることができる。また、図3(D1)及び図3(D2)に示すシリコンウィスカー115は、角柱状であり、複数のシリコンウィスカー115同士が接し、シリコンウィスカー群をなしている。複数のシリコンウィスカーが接することにより、機械的強度を高めることができる。シリコンウィスカー115の形状はここに示す形状に限られるものではなく、上述のように結晶状の突起であれば様々な形状を取り得ることは言うまでもない。

【0085】

このように作製したトランジスタは、高集積化に伴う細く、アスペクト比の高いコンタクトホールに対しても、接続電極の断線などの影響がなく、良好なコンタクトを得ることができる。さらに、コンタクトホール内のシリコンウィスカーの形成時における、成膜ガス起因の不具合を受けることなく、電気的特性の良好なトランジスタを形成することができる。

【0086】

なお、高集積化に伴い多層配線を用いる場合、通常ではそれぞれの層の形成段階で接続配線を形成する必要があるが、上記のようなシリコンウィスカーを接続配線としたコンタクトの形成方法を用いることにより、二層目より上層の配線層と直接電気的に接続することが可能である。例えば二層目より上層の層間絶縁層を形成した後に、トランジスタのソース領域、又はドレイン領域上に形成された金属化合物層に到達するコンタクトホールを形成し、上述のような方法により導電性シリコンウィスカーと、配線層とを形成すればよい。

【0087】

なお、本実施の形態ではトランジスタの構成、及び作製方法を一例に挙げて説明したが、コンタクトホール底部の金属化合物からなる下部電極と接する、導電性シリコンウィスカーを接続電極としたコンタクトの形成方法は、ダイオード素子、容量素子、抵抗素子など、層間絶縁層を介した、配線の接続部を有する半導体装置であれば適用することが可能である。これらの半導体装置に適用した場合でも同様に、デバイスの高集積化に伴う細く、アスペクト比の高いコンタクトホールにおける接続電極の断線などの影響がなく、信頼性の高いコンタクトを有する半導体装置とすることができる。

【0088】

本実施の形態で例示した半導体装置の構成、および半導体装置の作製方法によれば、半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を実現できる。

【0089】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0090】

(実施の形態2)

本実施の形態では、本発明の一態様の、実施の形態1で示したものとは異なるトランジスタの構成とその作製方法について図4及び図5を用いて説明する。

【0091】

《トランジスタの構成例》

図4(A)に、本実施の形態で例示するトランジスタ201の断面概略図を示す。トランジスタ201は、酸化物半導体を半導体層とする、トップゲート構造のトランジスタのひとつである。

【0092】

トランジスタ201は、基板200上に下地層221と、チャネル形成領域を有する酸化物半導体層202と、酸化物半導体層202と接し、チャネル形成領域を挟むように設けられたソース電極層211a、及びドレイン電極層211bと、チャネル形成領域と接して設けられたゲート絶縁層203と、ゲート絶縁層203と接し、チャネル形成領域、並びにソース電極層211a及びドレイン電極層211bの向かい合う端部と重畳するゲート電極層205と、を有する。また上記構成の全てを覆う層間絶縁層213を有し、層間絶縁層213にはソース電極層211a、及びドレイン電極層211bに達するコンタクトホール217を有する。コンタクトホール217内部にはソース電極層211a又はドレイン電極層211bと接するシリコンウィスカー215が設けられ、シリコンウィスカー215の上部は、それぞれ層間絶縁層213上に設けられたソース配線層219a、又はドレイン配線層219bと接している。

【0093】

シリコンウィスカー215は実施の形態1で示したものと同様、不純物が拡散され、導電性シリコンから成る。従って、ソース電極層211a又はドレイン電極層211b(以下、まとめて下部電極とも呼ぶ)と、ソース配線層219a、又はドレイン配線層219b(以下、まとめて上部電極とも呼ぶ)とを電気的に接続する。さらに、シリコンウィスカー215と下部電極、及び上部電極との接合はほぼオーミック接合となり、電気的障壁が極めて小さい。そのため、コンタクト抵抗の小さい良好なコンタクトが形成される。

【0094】

酸化物半導体層202のコンタクトホール217の底部と重畳する領域は、ソース電極層211a、又はドレイン電極層211bで覆われている。従って、ソース電極層211a、及びドレイン電極層211bは、後述するシリコンウィスカー215の形成時における、成膜ガス等が酸化物半導体層202に直接触れることによる影響を防ぐことができる。

【0095】

なお、シリコンウィスカー215と、上部電極、及び下部電極との界面において、金属とシリコンの反応により、シリサイドが形成されていてもよい。シリサイドが形成されると、シリコンウィスカー215と、上部電極、及び下部電極との接触抵抗が低減されるため、好ましい。

【0096】

《作成工程例》

次に、本発明の一態様であるトランジスタの作製方法の一例について説明する。以下では、トランジスタ201の作製方法について図5を用いて説明する。

【0097】

まず、基板200上に、下地層221を形成する。

【0098】

基板200は材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを、基板200として用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板200として用いてもよい。

【0099】

また、基板200として、可撓性基板を用いてもよい。可撓性基板上にトランジスタを設ける場合、可撓性基板上に直接的にトランジスタを作りこんでもよいし、他の基板にトランジスタを形成した後、これを剥離し、可撓性基板に転置してもよい。なお、トランジスタを剥離し、可撓性基板に転置するためには、上記他の基板とトランジスタとの間に剥離層を形成するとよい。

【0100】

下地層221は絶縁性を有する窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜などを用いることができる。また、下地層221は13族元素及び酸素を含む材料を用いて形成することもできる。13族元素及び酸素を含む材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、及び酸化ガリウムアルミニウムのいずれか一又は複数を含む材料などがある。下地層221は、上述の材料を用いて単層構造、又は積層構造で形成することができる。また、下地層221は後に形成する酸化物半導体膜とは異なる材料を含む絶縁膜と、酸化物半導体膜と同種の成分でなる絶縁材料でなる絶縁膜との積層構造とすることがより好ましい。例えば、酸化ガリウム膜と酸化シリコン膜の積層構造や、酸化ガリウム膜と窒化シリコン膜との積層構造などを適用することができる。

【0101】

下地層221は後に形成される酸化物半導体層202と接するため、水素、水などの不純物を混入させない方法を用いて形成することが好ましい。下地層221に水素、水などの不純物が含まれると、後に成膜される酸化物半導体膜に水素、水などの不純物の浸入や、水素、水などの不純物により酸化物半導体膜中の酸素の引き抜き、などによって酸化物半導体層202のバックチャネルが低抵抗化し、寄生チャネルが形成されるおそれがある。例えば、水素、水などの不純物が除去された高純度ガスを用いた、スパッタリング法によって形成するのが好ましい。

【0102】

次に、下地層221上に酸化物半導体層202、並びにソース電極層211a、及びドレイン電極層211bを形成する。

【0103】

酸化物半導体層202に用いる材料としては、少なくともIn、Ga、Sn、Zn、Al、Mg、Hf及びランタノイドから選ばれた一種以上の元素を含有する。例えば、四元系金属酸化物であるIn−Sn−Ga−Zn−O系や、三元系金属酸化物であるIn−Ga−Zn−O系、In−Sn−Zn−O系、In−Al−Zn−O系、Sn−Ga−Zn−O系、Al−Ga−Zn−O系、Sn−Al−Zn−O系、In−Hf−Zn−O系、In−La−Zn−O系、In−Ce−Zn−O系、In−Pr−Zn−O系、In−Nd−Zn−O系、In−Sm−Zn−O系、In−Eu−Zn−O系、In−Gd−Zn−O系、In−Tb−Zn−O系、In−Dy−Zn−O系、In−Ho−Zn−O系、In−Er−Zn−O系、In−Tm−Zn−O系、In−Yb−Zn−O系、In−Lu−Zn−O系や、二元系金属酸化物であるIn−Zn−O系、Sn−Zn−O系、Al−Zn−O系、Zn−Mg−O系、Sn−Mg−O系、In−Mg−O系、In−Ga−O系や、In−O系、Sn−O系、Zn−O系の金属酸化物材料などを用いることができる。また、上記の材料にSiO2を含ませてもよい。ここで、例えば、In−Ga−Zn−O系の材料とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物層、という意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。

【0104】

また、酸化物半導体層202は、化学式InMO3(ZnO)m(m>0)で表記される材料を用いた薄膜により形成することができる。ここで、Mは、Ga、Al、Mn及びCoから選ばれた一または複数の金属元素を示す。例えば、Mとして、Ga、Ga及びAl、Ga及びMnまたはGa及びCoなどを用いることができる。

【0105】

また、酸化物半導体層202に用いる酸化物半導体膜は、スパッタリング法で成膜することができる。また希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下において成膜することができる。その際のガスは、水素、水、水酸基を有する化合物、または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0106】

なお、酸化物半導体膜を成膜後、第1の加熱処理を行ってもよい。この第1の加熱処理によって酸化物半導体膜中の過剰な水(水酸基を含む)や水素などを除去することができる。第1の加熱処理の温度は350℃以上基板の歪み点未満、好ましくは400℃以上基板の歪み点未満とすることができる。また、第1の加熱処理は窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とし、水、水素などの不純物が除去された高純度なガスの雰囲気下で行うことが望ましい。

【0107】

続いてソース電極層211a及びドレイン電極層211bに用いる金属膜を成膜する。金属膜は、後に形成するシリコンウィスカーを形成可能な材料を選択する。このような材料としては、例えばチタン、ニッケル、コバルト、鉄等がある。また、金属膜はできるだけ水素、水などの不純物が除去された高純度ガスを用いたスパッタリング法で成膜することが好ましい。

【0108】

酸化物半導体膜、及び金属膜を形成した後、これらを選択的にエッチングすることにより、島状の酸化物半導体層202、並びにソース電極層211a、及びドレイン電極層211bを形成する。

【0109】

なお、金属膜のエッチングの際に酸化物半導体層202がエッチングされ、分断することのないようにエッチング条件を最適化することが望まれる。しかしながら、金属膜のみをエッチングし、酸化物半導体層202をまったくエッチングしないという条件を得ることは難しく、金属膜のエッチングの際に酸化物半導体層202は一部のみがエッチングされ、溝部(凹部)を有する酸化物半導体層202となることもある。

【0110】

なお、酸化物半導体層202と、ソース電極層211a、及びドレイン電極層211bとの間に、導電性の層を有していてもよい。例えば酸化物半導体層との接触抵抗の低い材料を間に形成することにより、コンタクト抵抗を低減することができる。

【0111】

この段階の断面概略図を図5(A)に示す。

【0112】

次に、ゲート絶縁層203を形成する。

【0113】

ゲート絶縁層203は、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜等の単層、または積層構造とすることができる。酸化物半導体層202と接する層は酸化物絶縁層とすることが好ましい。ゲート絶縁層203の成膜方法としては、プラズマCVD法やスパッタリング法等を用いることができるが、層中に水素が多量に含まれないようにするためには、スパッタリング法で成膜することが好ましい。

【0114】

続いて、ゲート電極層205を形成する。

【0115】

ゲート電極層205を形成する導電膜の材料としては、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料、またはこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。導電膜の成膜方法としては、スパッタリング法を用いることができる。

【0116】

上記導電膜を成膜後、選択的にエッチングすることによりゲート電極層205を形成する。

【0117】

次に、上述の工程により形成された各構成を覆う層間絶縁層213を形成する。層間絶縁層213は実施の形態1で示したような材料、方法で適宜形成することができる。層間絶縁層213となる絶縁膜を成膜後、その表面をCMPやエッチング処理により平坦化することが好ましい。

【0118】

続いて、層間絶縁層213にソース電極層211a、及びドレイン電極層211bにまで達するコンタクトホール217を形成する。コンタクトホール217を形成する際の層間絶縁層213、及びゲート絶縁層203のエッチングには、ソース電極層211a、及びドレイン電極層211bに用いた金属膜に対して、層間絶縁層213及びゲート絶縁層203のエッチングの選択比が高い方法を用いることができる。また、半導体素子が高度に微細化される場合には、エッチングによるコンタクトホールの広がりを抑制するため、異方性のドライエッチングを用いることが好ましい。また、ゲート絶縁層203に対する層間絶縁層213とのエッチングの選択比の高い方法を用いて、まず層間絶縁層213をゲート絶縁層203が露出するまでエッチングし、その後ゲート絶縁層203をエッチングしてもよい。こうすることで、金属膜に対する層間絶縁層213及びゲート絶縁層203のエッチングの選択比が高くない場合でもソース電極層211a、及びドレイン電極層211bがエッチングされて消失することを抑制することができる。このような方法を適宜用いて、層間絶縁層213とゲート絶縁層203を選択的にエッチングすることにより、コンタクトホール217が形成される。

【0119】

この段階の断面概略図を図5(B)に示す。

【0120】

次に、コンタクトホール217内にシリコンウィスカー215を形成する。

【0121】

シリコンウィスカー215は、実施の形態1で示したように、熱CVD法、好ましくはLPCVD法を用いて形成する。酸化物半導体層202のコンタクトホール217と重畳する領域は、ソース電極層211a、又はドレイン電極層211bで覆われており、成膜ガスが直接酸化物半導体層に触れることなく、シリコンウィスカー215を形成することができる。従って、LPCVD法に用いる成膜ガスに水素を含む場合であっても、酸化物半導体層への水素などの不純物の浸入を防ぐことができる。また、酸化物半導体層への成膜ガス、又は成膜ガスに含まれる不純物の影響を考慮することなく、シリコンウィスカー215の成膜に最適な成膜ガスを選択することができる。

【0122】

シリコンウィスカー215の形成中、一導電性を付与する不純物元素を添加することにより、シリコンウィスカー215は導電性に導電性を持たせることができる。シリコンウィスカーの導電型はn型でもp型でもどちらでもよい。シリコンウィスカーを十分に低抵抗化することにより、上部電極、及び下部電極との接触抵抗を低減することができ、低抵抗なコンタクトを実現できる。

【0123】

このようにして形成されたシリコンウィスカー215は、実施の形態1で示したように、結晶性を有する。またその成長方向とシリコンウィスカーを構成する結晶の結晶方位の少なくともひとつが略一致していてもよい。このような結晶性を有することで、より電気伝導性に優れたシリコンウィスカーとすることができ、コンタクト抵抗の小さい良好なコンタクトを形成することができる。

【0124】

また、シリコンウィスカー215は、成膜方法、条件の違いによって実施の形態1で示したような、様々な形状を取ることができる。

【0125】

続いて、シリコンウィスカー215の形成中に層間絶縁層213上に形成された不要なシリコン薄膜を実施の形態1で示したような方法でエッチングにより除去する。なお、層間絶縁層213上に該シリコン薄膜が形成されなかった場合は、この工程を省略することができる。

【0126】

以上の工程により、コンタクトホール217内部にシリコンウィスカー215が形成される。なお、この段階の断面概略図を図5(C)に示す。

【0127】

続いて、ソース配線層219a、及びドレイン配線層219bを形成する。

【0128】

ソース配線層219a、及びドレイン配線層219bに用いる導電膜は、実施の形態1で示したような材料、方法により適宜成膜することができる。その後、導電膜を選択的にエッチングすることにより、ソース配線層219a、及びドレイン配線層219bが形成される。

【0129】

なお、シリコンウィスカー215と、上部電極、及び下部電極との界面において、金属とシリコンの反応により、シリサイドが形成されていてもよい。シリサイドが形成されると、シリコンウィスカー215と、上部電極、及び下部電極との接触抵抗が低減されるため、好ましい。

【0130】

ソース配線層219a、及びドレイン配線層219bを形成後、第2の加熱処理を行っても良い。第2の加熱処理は大気中、不活性ガス雰囲気下、または酸素雰囲気下で好ましくは100℃以上200℃以下で行うことができる。また、室温から、100℃以上200℃以下の加熱温度への昇温と、加熱温度から室温までの降温を繰り返し行っても良い。

【0131】

以上の工程により、トランジスタ201が形成される。この段階の断面概略図を図5(D)に示す。

【0132】

なお、本実施の形態では、トップゲート型のトランジスタ201の構成及び作製方法について説明したが、本発明はトランジスタの構成は特に限定されず、ボトムゲート型のトランジスタなどにも適用することができる。一例として、図4(B)にボトムゲート型のトランジスタに適用した例を示す。図4(B)に示すトランジスタ241は、逆スタガ構造と呼ばれる、ボトムゲート型のトランジスタのひとつである。トランジスタ241を作製するには、下地層221上にゲート電極層205、ゲート絶縁層203、酸化物半導体層202、ソース電極層211a及びドレイン電極層211bの順に形成し、層間絶縁層213の形成以降の工程はトランジスタ201の作製工程と同じとすればよい。

【0133】

なお、本実施の形態では、半導体層に酸化物半導体を用いたトランジスタの構成、及び作製方法について説明したが、半導体層に用いる半導体はこれに限らず、シリコンや炭化シリコンなどの単結晶半導体、多結晶半導体、シリコンゲルマニウムなどの化合物半導体などの半導体を半導体層に用いた半導体装置にも本発明は適用することができる。

【0134】

このように作製したトランジスタは、高集積化に伴う細く、アスペクト比の高いコンタクトホールに対しても、接続電極の断線などの影響がなく、信頼性の高いコンタクトを得ることができる。さらに、コンタクトホール内のシリコンウィスカーの形成時における、成膜ガス起因の不具合を受けることなく、電気的特性の良好なトランジスタを形成することができる。

【0135】

また、本実施の形態ではトランジスタの構成、及び作製方法を一例に挙げて説明したが、コンタクトホール底部の金属からなる下部電極と接する、導電性シリコンウィスカーを接続電極としたコンタクトの形成方法は、ダイオード素子、容量素子、抵抗素子など、層間絶縁層を介した、配線の接続部を有する半導体装置であれば適用することが可能である。これらの半導体装置に適用した場合でも同様に、デバイスの高集積化に伴う細く、アスペクト比の高いコンタクトホールに対して、接続電極の断線などの影響がなく、良好なコンタクトを有する半導体装置とすることができる。

【0136】

本実施の形態で例示した半導体装置の構成、および半導体装置の作製方法によれば、半導体素子の特性を損なうことなく微細化に伴うコンタクト不良を低減した、電気的特性の良好な半導体装置を実現できる。

【0137】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【符号の説明】

【0138】

100 基板

101 トランジスタ

103 ゲート絶縁層

105 ゲート電極層

107 サイドウォール

109a ソース領域

109b ドレイン領域

111 金属化合物層

113 層間絶縁層

115 シリコンウィスカー

117 コンタクトホール

119a ソース配線層

119b ドレイン配線層

121 素子分離層

123 金属層

200 基板

201 トランジスタ

202 半導体層

203 ゲート絶縁層

205 ゲート電極層

211a ソース電極層

211b ドレイン電極層

213 層間絶縁層

215 シリコンウィスカー

217 コンタクトホール

219a ソース配線層

219b ドレイン配線層

221 下地層

241 トランジスタ

【特許請求の範囲】

【請求項1】

半導体層と、

前記半導体層の上面と電気的に接続する下部電極と、

前記下部電極上にコンタクトホールを備え、且つ前記半導体層を覆う絶縁層と、

導電性シリコンウィスカーを含み、且つ前記コンタクトホールにおいて前記下部電極と接する接続電極と、

前記絶縁層上に、前記接続電極と電気的に接続する上部電極と、を有する半導体装置。

【請求項2】

前記下部電極は、金属、または前記半導体層を構成する半導体と金属とを含む金属化合物を有する、請求項1に記載の半導体装置。

【請求項3】

前記導電性シリコンウィスカーと前記上部電極との間にシリサイド層を有する、請求項1及び2のいずれか一に記載の半導体装置。

【請求項4】

前記接続電極は、二以上の導電性シリコンウィスカーを含む、請求項1乃至3のいずれか一に記載の半導体装置。

【請求項5】

半導体層の上面と電気的に接続する下部電極を形成し、

前記半導体層と前記下部電極とを覆う絶縁層を形成し、

前記絶縁層に、前記下部電極と重なるコンタクトホールを形成し、

前記コンタクトホールにおいて、前記下部電極と接し、且つ導電性シリコンウィスカーを含む接続電極を形成し、

前記絶縁層上に、前記接続電極と電気的に接続する上部電極を形成する、半導体装置の作製方法。

【請求項6】

半導体層の上面と接する金属膜を形成し、

前記半導体層を構成する材料と前記金属膜を構成する材料とを含み、且つ前記半導体層の上面に接する金属化合物層を形成し、

前記金属膜を除去し、

前記半導体層と前記金属化合物層とを覆う絶縁層を形成し、

前記絶縁層に、前記金属化合物層と重なるコンタクトホールを形成し、

前記コンタクトホールにおいて、前記金属化合物層と接し、且つ導電性シリコンウィスカーを含む接続電極を形成し、

前記絶縁層上に、前記接続電極と電気的に接続する上部電極を形成する、半導体装置の作製方法。

【請求項1】

半導体層と、

前記半導体層の上面と電気的に接続する下部電極と、

前記下部電極上にコンタクトホールを備え、且つ前記半導体層を覆う絶縁層と、

導電性シリコンウィスカーを含み、且つ前記コンタクトホールにおいて前記下部電極と接する接続電極と、

前記絶縁層上に、前記接続電極と電気的に接続する上部電極と、を有する半導体装置。

【請求項2】

前記下部電極は、金属、または前記半導体層を構成する半導体と金属とを含む金属化合物を有する、請求項1に記載の半導体装置。

【請求項3】

前記導電性シリコンウィスカーと前記上部電極との間にシリサイド層を有する、請求項1及び2のいずれか一に記載の半導体装置。

【請求項4】

前記接続電極は、二以上の導電性シリコンウィスカーを含む、請求項1乃至3のいずれか一に記載の半導体装置。

【請求項5】

半導体層の上面と電気的に接続する下部電極を形成し、

前記半導体層と前記下部電極とを覆う絶縁層を形成し、

前記絶縁層に、前記下部電極と重なるコンタクトホールを形成し、

前記コンタクトホールにおいて、前記下部電極と接し、且つ導電性シリコンウィスカーを含む接続電極を形成し、

前記絶縁層上に、前記接続電極と電気的に接続する上部電極を形成する、半導体装置の作製方法。

【請求項6】

半導体層の上面と接する金属膜を形成し、

前記半導体層を構成する材料と前記金属膜を構成する材料とを含み、且つ前記半導体層の上面に接する金属化合物層を形成し、

前記金属膜を除去し、

前記半導体層と前記金属化合物層とを覆う絶縁層を形成し、

前記絶縁層に、前記金属化合物層と重なるコンタクトホールを形成し、

前記コンタクトホールにおいて、前記金属化合物層と接し、且つ導電性シリコンウィスカーを含む接続電極を形成し、

前記絶縁層上に、前記接続電極と電気的に接続する上部電極を形成する、半導体装置の作製方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−33905(P2012−33905A)

【公開日】平成24年2月16日(2012.2.16)

【国際特許分類】

【出願番号】特願2011−141995(P2011−141995)

【出願日】平成23年6月27日(2011.6.27)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成24年2月16日(2012.2.16)

【国際特許分類】

【出願日】平成23年6月27日(2011.6.27)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]