半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

【発明の詳細な説明】

【技術分野】

【0001】

半導体装置及び半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

半導体薄膜を用いてトランジスタ(薄膜トランジスタ(TFT)ともいう)を構成する技術が注目されている。該トランジスタは集積回路(IC)や画像表示装置(表示装置)のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

【0004】

酸化物半導体を用いたトランジスタとしては、より高機能な半導体装置への応用のために、より高い電気特性が求められている。酸化物半導体を用いたトランジスタにおいて、高い電気特性を目的として、アルミニウム反応法を用いて低抵抗なソース領域及びドレイン領域を形成する技術などが報告がされている(例えば、非特許文献1参照。)。

【0005】

例えば、トランジスタの活性層として、インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む非晶質酸化物を用いたトランジスタが開示されている(特許文献1参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−165528号公報

【非特許文献】

【0007】

【非特許文献1】N.Morosawa, Yoshihiro Ohshima,Mitsuo Morooka, Toshiaki Arai, Tatsuya Sasaoka, 「A Novel Self−Aligned Top−Gate Oxide TFT for AM−OLED Displays」、SID 11 DIGEST pp479−482

【発明の概要】

【発明が解決しようとする課題】

【0008】

トランジスタのオン特性(例えば、オン電流や電界効果移動度)が向上すると、半導体装置において入力信号に対する高速応答、高速駆動が可能になり、より高性能な半導体装置が実現できる。一方、半導体装置の低消費電力化には、トランジスタのオフ電流が十分低いことが求められる。このように、トランジスタに求められる電気特性は用途や目的に合わせて様々であり、該電気特性をより精度よく制御することは有益である。

【0009】

酸化物半導体をチャネル形成領域に用いたトランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供することを課題の一つとする。

【0010】

トランジスタは、ゲート電圧が0Vにできるだけ近い正のしきい値電圧でチャネルが形成されることが望ましい。トランジスタのしきい値電圧がマイナスであると、ゲート電圧が0Vでもソース電極とドレイン電極の間に電流が流れる、所謂ノーマリーオンとなりやすい。LSIやCPUやメモリにおいては、回路を構成するトランジスタの電気特性が重要であり、この電気特性が半導体装置の消費電力を左右する。特に、トランジスタの電気特性のうち、しきい値電圧(Vth)が重要である。電界効果移動度が高くとも、しきい値電圧がマイナスであると、回路として制御することが困難である。負の電圧状態でもチャネルが形成されてドレイン電流が流れるトランジスタは、半導体装置の集積回路に用いるトランジスタとしては不向きである。

【0011】

また、材料や作製条件によっては、作製されたトランジスタがノーマリーオフとならない場合であっても、ノーマリーオフの特性に近づけることが重要であり、しきい値電圧がマイナスである、所謂ノーマリーオンであっても、トランジスタのしきい値をゼロに近づける構成およびその作製方法を提供することも課題の一つとする。

【0012】

また、より高性能な半導体装置を実現するため、トランジスタのオン特性(例えば、オン電流や電界効果移動度)を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供することも課題の一つとする。

【0013】

上記のように、用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供することを課題の一とする。

【課題を解決するための手段】

【0014】

半導体層、ソース電極層及びドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。

【0015】

酸化物半導体積層を第1の酸化物半導体層及び第2の酸化物半導体層の積層構造とする場合、第1の酸化物半導体層及び第2の酸化物半導体層は、それぞれの有するエネルギーギャップが異なればよく、その積層順は限定されず、ゲート絶縁膜と接する方をエネルギーギャップが大きい層としてもよいし、エネルギーギャップが小さい層としてもよい。

【0016】

具体的には、酸化物半導体積層において、一方の酸化物半導体層のエネルギーギャップを3eV以上とし、他方の酸化物半導体層のエネルギーギャップを3eV未満とする。なお、本明細書において、「エネルギーギャップ」という用語は、「バンドギャップ」や、「禁制帯幅」と同じ意味で用いている。

【0017】

酸化物半導体積層を3層以上の積層構造とする場合、すべての酸化物半導体層同士が異なるエネルギーギャップを有する構造であってもよいし、ほぼ同じエネルギーギャップを有する酸化物半導体層を複数酸化物半導体積層中に用いてもよい。

【0018】

例えば、酸化物半導体積層を第1の酸化物半導体層、第2の酸化物半導体層、及び第3の酸化物半導体層の積層構造において、第2の酸化物半導体層のエネルギーギャップを第1の酸化物半導体層及び第3の酸化物半導体層のエネルギーギャップより小さくする。または、第2の酸化物半導体層の電子親和力を、第1の酸化物半導体層及び第3の酸化物半導体層の電子親和力よりも大きくする。この場合、第1の酸化物半導体層及び第3の酸化物半導体層のエネルギーギャップと電子親和力とは同等とすることができる。エネルギーギャップの小さい第2の酸化物半導体層を、エネルギーギャップの大きい第1の酸化物半導体層及び第3の酸化物半導体層により挟む構造とすることによって、よりトランジスタのオフ電流(リーク電流)を低減する効果が得られる。ここで、電子親和力とは真空準位と酸化物半導体の伝導帯とのエネルギー差を表す。

【0019】

酸化物半導体層を用いたトランジスタにおいて、該酸化物半導体層のエネルギーギャップは、トランジスタの電気特性に影響を与える。例えば、酸化物半導体層を用いたトランジスタにおいて、酸化物半導体層のエネルギーギャップが小さいと、オン特性(例えば、オン電流や電界効果移動度)が向上し、一方、酸化物半導体層のエネルギーギャップが大きいと、オフ電流が低減できる。

【0020】

単層の酸化物半導体層では該酸化物半導体層のエネルギーギャップの大きさで、トランジスタの電気特性はほぼ決定してしまうため、所望の電気的特性をトランジスタに付与することは難しい。

【0021】

異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層を用いることによって、トランジスタの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタに付与することが可能となる。

【0022】

従って、高機能、高信頼性、又は低消費電力など、種々の目的に応じた半導体装置を提供することができる。

【0023】

本明細書で開示する発明の構成の一形態は、エネルギーギャップが異なる第1の酸化物半導体層及び第2の酸化物半導体層を含む酸化物半導体積層と、酸化物半導体積層上にソース電極層及びドレイン電極層と、ソース電極層及びドレイン電極層上にゲート絶縁膜と、ゲート絶縁膜上に酸化物半導体積層と重なるゲート電極層とを有する半導体装置である。

【0024】

本明細書で開示する発明の構成の一形態は、第1の酸化物半導体層、第2の酸化物半導体層、及び第3の酸化物半導体層を順に含む酸化物半導体積層と、酸化物半導体積層上にソース電極層及びドレイン電極層と、ソース電極層及びドレイン電極層上にゲート絶縁膜と、ゲート絶縁膜上に酸化物半導体積層と重なるゲート電極層とを有し、第2の酸化物半導体層は、第1の酸化物半導体層及び第3の酸化物半導体層のエネルギーギャップより小さいエネルギーギャップを有する半導体装置である。

【0025】

上記構成において、酸化物半導体積層は島状であり、ソース電極層及びドレイン電極層は酸化物半導体積層の側面(端部)に接して形成することができる。この場合、酸化物半導体積層の側面(端部)には第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層の側面(端部)が露出しているので、第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層はソース電極層及びドレイン電極層と接する構成となる。

【0026】

本明細書で開示する発明の構成の一形態は、酸化物絶縁膜上にエネルギーギャップが異なる2層の酸化物半導体層を含む酸化物半導体積層を形成し、酸化物半導体積層上にソース電極層及びドレイン電極層を形成し、ソース電極層及びドレイン電極層を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極層を形成する半導体装置の作製方法である。

【0027】

本明細書で開示する発明の構成の一形態は、酸化物絶縁膜上にエネルギーギャップが異なる酸化物半導体膜を積層し、酸化物半導体膜の積層上にマスクを形成し、マスクを用いて酸化物半導体膜の積層をエッチング加工して酸化物半導体積層を形成し、酸化物半導体積層上にソース電極層及びドレイン電極層を形成し、ソース電極層及びドレイン電極層を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極層を形成する半導体装置の作製方法である。

【0028】

また、ゲート電極層をマスクとして酸化物半導体積層にドーパントを導入し、自己整合的にチャネル形成領域を挟んでチャネル形成領域より抵抗が低く、ドーパントを含む低抵抗領域を形成してもよい。ドーパントは、酸化物半導体積層の導電率を変化させる不純物である。ドーパントの導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。

【0029】

チャネル長方向にチャネル形成領域を挟んで低抵抗領域を含む酸化物半導体積層を有することにより、該トランジスタはオン特性(例えば、オン電流及び電界効果移動度)が高く、高速動作、高速応答が可能となる。

【0030】

また、酸化物半導体層(酸化物半導体膜)に水素若しくは水分を放出させる加熱処理(脱水化又は脱水素化処理)を行ってもよい。例えば上記構成において、マスクを形成する前に、積層された酸化物半導体膜中に含まれる水素若しくは水分を放出させる加熱処理を行うことが好ましい。

【0031】

また、脱水化又は脱水素化処理によって、酸化物半導体を構成する主成分材料である酸素が同時に脱離して減少してしまうおそれがある。酸化物半導体膜において、酸素が脱離した箇所では酸素欠損が存在し、該酸素欠損に起因してトランジスタの電気的特性変動を招くドナー準位が生じてしまう。

【0032】

よって、脱水化又は脱水素化処理を行った酸化物半導体層(酸化物半導体膜)に、酸素を供給することが好ましい。酸化物半導体層(酸化物半導体膜)へ酸素を供給することにより、膜中の酸素欠損を補填することができる。

【0033】

例えば、酸素の供給源となる酸素を多く(過剰に)含む酸化物絶縁膜を酸化物半導体層(酸化物半導体膜)と接して設けることによって、該酸化物絶縁膜から酸化物半導体層(酸化物半導体膜)へ酸素を供給することができる。上記構成において、脱水化又は脱水素化処理として加熱処理を行った酸化物半導体層(酸化物半導体膜)及び酸化物絶縁膜を少なくとも一部が接した状態で加熱処理を行うことによって酸化物半導体層(酸化物半導体膜)への酸素の供給を行ってもよい。

【0034】

また、脱水化又は脱水素化処理を行った酸化物半導体層(酸化物半導体膜)に、酸素(少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む)を導入して膜中に酸素を供給してもよい。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。

【0035】

さらに、好ましくはトランジスタに設けられる酸化物半導体層(酸化物半導体膜)は、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている膜とするとよい。この場合、酸素の含有量は、酸化物半導体の化学量論的組成比を超える程度とする。あるいは、酸素の含有量は、単結晶の場合の酸素の量を超える程度とする。酸化物半導体の格子間に酸素が存在する場合もある。

【0036】

水素若しくは水分を酸化物半導体から除去し、不純物が極力含まれないように高純度化し、酸素を供給して酸素欠損を補填することによりI型(真性)の酸化物半導体、又はI型(真性)に限りなく近い酸化物半導体とすることができる。そうすることにより、酸化物半導体のフェルミ準位(Ef)を真性フェルミ準位(Ei)と同じレベルにまですることができる。よって、該酸化物半導体膜をトランジスタに用いることで、酸素欠損に起因するトランジスタのしきい値電圧Vthのばらつき、しきい値電圧のシフトΔVthを低減することができる。

【0037】

本発明の一形態は、トランジスタ若しくはトランジスタを含んで構成される回路を有する半導体装置に関する。例えば、酸化物半導体でチャネル形成領域が形成される、トランジスタ若しくはトランジスタを含んで構成される回路を有する半導体装置に関する。例えば、LSIや、CPUや、電源回路に搭載されるパワーデバイスや、メモリ、サイリスタ、コンバータ、イメージセンサなどを含む半導体集積回路、液晶表示パネルに代表される電気光学装置や発光素子を有する発光表示装置を部品として搭載した電子機器に関する。

【発明の効果】

【0038】

異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層を用いることによって、トランジスタの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタに付与することが可能となる。

【0039】

従って、高機能、高信頼性、又は低消費電力など、種々の目的に応じた半導体装置を提供することができる。

【図面の簡単な説明】

【0040】

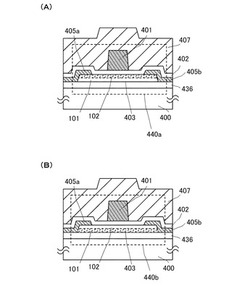

【図1】半導体装置の一形態を説明する図。

【図2】半導体装置及び半導体装置の作製方法の一形態を説明する図。

【図3】半導体装置の一形態を説明する図。

【図4】半導体装置の一形態を説明する図及びエネルギーバンド図。

【図5】半導体装置及び半導体装置の作製方法の一形態を説明する図。

【図6】半導体装置及び半導体装置の作製方法の一形態を説明する図。

【図7】半導体装置の一形態を説明する図。

【図8】半導体装置の一形態を説明する図。

【図9】半導体装置の一形態を説明する図。

【図10】半導体装置の一形態を説明する図。

【図11】電子機器を示す図。

【図12】イオン化ポテンシャルを示す図。

【図13】エネルギーバンド図を示す図。

【図14】実施例のサンプルのTEM写真図およびその模式図。

【発明を実施するための形態】

【0041】

以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。ただし、本明細書に開示する発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本明細書に開示する発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0042】

(実施の形態1)

本実施の形態では、半導体装置及び半導体装置の作製方法の一形態を、図1及び図3を用いて説明する。本実施の形態では、半導体装置の一例として酸化物半導体膜を有するトランジスタを示す。

【0043】

トランジスタはチャネル形成領域が1つ形成されるシングルゲート構造でも、2つ形成されるダブルゲート構造もしくは3つ形成されるトリプルゲート構造であってもよい。また、チャネル領域の上下にゲート絶縁膜を介して配置された2つのゲート電極層を有する、デュアルゲート型でもよい。

【0044】

図1(A)(B)に示すトランジスタ440a、トランジスタ440bは、トップゲート構造を有するプレーナ型のトランジスタの例である。

【0045】

図1(A)(B)に示すように、トランジスタ440a、トランジスタ440bは、酸化物絶縁膜436が設けられた基板400上に、エネルギーギャップの異なる第1の酸化物半導体層101及び第2の酸化物半導体層102を含む酸化物半導体積層403、ソース電極層405a、ドレイン電極層405b、ゲート絶縁膜402、ゲート電極層401を有する。トランジスタ440a、トランジスタ440b上には、絶縁膜407が形成されている。

【0046】

なお、図1において、第1の酸化物半導体層101と第2の酸化物半導体層102の界面を点線で図示しているが、これは酸化物半導体積層403を模式的に示したものである。材料や成膜条件や加熱処理によっては、第1の酸化物半導体層101と第2の酸化物半導体層102との界面が不明確になる場合もある。不明確になる場合、異なる複数の酸化物半導体層の混合領域又は混合層とよぶことのできる箇所が形成されることもある。これは本明細書の他の図面においても同様である。

【0047】

酸化物半導体積層403において、第1の酸化物半導体層101及び第2の酸化物半導体層102は、それぞれの有するエネルギーギャップが異なればよく、その積層順は限定されない。

【0048】

具体的には、酸化物半導体積層403において、一方の酸化物半導体層のエネルギーギャップを3eV以上とし、他方の酸化物半導体層のエネルギーギャップを3eV未満とする。

【0049】

図1(A)に示すトランジスタ440aは、第1の酸化物半導体層101より第2の酸化物半導体層102の方が、エネルギーギャップが大きい例である。本実施の形態では、トランジスタ440aにおける第1の酸化物半導体層101としてIn−Sn−Zn系酸化物膜(エネルギーギャップ2.6eV〜2.9eV、代表的には2.8eV)、第2の酸化物半導体層102としてはIn−Ga−Zn系酸化物(IGZOとも表記する)膜(エネルギーギャップ3.0eV〜3.4eV、代表的には3.2eV)を用いる。

【0050】

一方、図1(B)に示すトランジスタ440bは、第1の酸化物半導体層101より第2の酸化物半導体層102の方が、該エネルギーギャップが小さい例である。本実施の形態では、トランジスタ440bにおける第1の酸化物半導体層101としてIn−Ga−Zn系酸化物膜(エネルギーギャップ3.2eV)、第2の酸化物半導体層102としてはIn−Sn−Zn系酸化物膜(エネルギーギャップ2.8eV)を用いる。

【0051】

このように、酸化物半導体積層403において、第1の酸化物半導体層101及び第2の酸化物半導体層102は、ゲート絶縁膜402と接する方をエネルギーギャップが大きい層としてもよいし、エネルギーギャップが小さい層としてもよい。

【0052】

図4(A)に酸化物半導体積層403として第1の酸化物半導体層101、第2の酸化物半導体層102、及び第3の酸化物半導体層103の3層構造の積層を用いたトランジスタ480aを示す。

【0053】

トランジスタ480aは、酸化物絶縁膜436が設けられた基板400上に、第1の酸化物半導体層101、第2の酸化物半導体層102、及び第3の酸化物半導体層103を含む酸化物半導体積層403、ソース電極層405a、ドレイン電極層405b、ゲート絶縁膜402、ゲート電極層401を有する。トランジスタ480a上には、絶縁膜407が形成されている。

【0054】

なお、図4において、第1の酸化物半導体層101と、第2の酸化物半導体層102の界面を点線で図示しているが、これは酸化物半導体積層403を模式的に示したものである。材料や成膜条件や加熱処理によっては、第1の酸化物半導体層101と、第2の酸化物半導体層102との界面が不明確になる場合もある。不明確になる場合、異なる複数の酸化物半導体層の混合領域又は混合層とよぶことのできる箇所が形成されることもある。なお、第2の酸化物半導体層102と、第3の酸化物半導体層103の界面も同様である。

【0055】

トランジスタ480aの酸化物半導体積層403において、第1の酸化物半導体層101、第2の酸化物半導体層102、及び第3の酸化物半導体層103のエネルギーギャップは全て同じではなく、少なくとも2種類の異なる値のエネルギーギャップを含む。

【0056】

酸化物半導体積層403を3層以上の積層構造とする場合、すべての酸化物半導体層同士が異なるエネルギーギャップを有する構造であってもよいし、ほぼ同じエネルギーギャップを有する酸化物半導体層を複数酸化物半導体積層403中に用いてもよい。

【0057】

酸化物半導体積層403(第1の酸化物半導体層101、第2の酸化物半導体層102、第3の酸化物半導体層103)に用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0058】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0059】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn系酸化物、Sn−Zn系酸化物、Al−Zn系酸化物、Zn−Mg系酸化物、Sn−Mg系酸化物、In−Mg系酸化物、In−Ga系酸化物、三元系金属の酸化物であるIn−Ga−Zn系酸化物、In−Al−Zn系酸化物、In−Sn−Zn系酸化物、Sn−Ga−Zn系酸化物、Al−Ga−Zn系酸化物、Sn−Al−Zn系酸化物、In−Hf−Zn系酸化物、In−La−Zn系酸化物、In−Ce−Zn系酸化物、In−Pr−Zn系酸化物、In−Nd−Zn系酸化物、In−Sm−Zn系酸化物、In−Eu−Zn系酸化物、In−Gd−Zn系酸化物、In−Tb−Zn系酸化物、In−Dy−Zn系酸化物、In−Ho−Zn系酸化物、In−Er−Zn系酸化物、In−Tm−Zn系酸化物、In−Yb−Zn系酸化物、In−Lu−Zn系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn系酸化物、In−Hf−Ga−Zn系酸化物、In−Al−Ga−Zn系酸化物、In−Sn−Al−Zn系酸化物、In−Sn−Hf−Zn系酸化物、In−Hf−Al−Zn系酸化物を用いることができる。

【0060】

なお、ここで、例えば、In−Ga−Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0061】

また、酸化物半導体として、InMO3(ZnO)m(m>0、且つ、mは整数でない)で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、In2SnO5(ZnO)n(n>0、且つ、nは整数)で表記される材料を用いてもよい。

【0062】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子比のIn−Ga−Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子比のIn−Sn−Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

【0063】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0064】

例えば、In−Sn−Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn系酸化物でも、バルク内欠陥密度を低くすることにより移動度を上げることができる。

【0065】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物の組成の近傍であるとは、a、b、cが、(a−A)2+(b−B)2+(c−C)2≦r2を満たすことをいい、rは、例えば、0.05とすればよい。他の酸化物でも同様である。

【0066】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0067】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0068】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0069】

Raとは、JIS B 0601:2001(ISO4287:1997)で定義されている算術平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」で表現でき、数式(1)にて定義される。

【0070】

【数1】

【0071】

なお、上記において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)の4点で表される四角形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0072】

酸化物半導体積層403の第1の酸化物半導体層101、第2の酸化物半導体層102、第3の酸化物半導体層103として、結晶を含み、結晶性を有する酸化物半導体層(結晶性酸化物半導体層)を用いることができる。結晶性酸化物半導体層内の結晶は、結晶軸の方向が無秩序な状態でも、一定の配向性を有する状態であってもよい。

【0073】

例えば、結晶性酸化物半導体層として、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を用いることができる。

【0074】

表面に概略垂直なc軸を有している結晶を含む酸化物半導体層は、単結晶構造ではなく、非晶質構造でもない構造であり、c軸配向を有した結晶性酸化物半導体(C Axis Aligned Crystalline Oxide Semiconductor; CAAC−OSともいう)膜である。

【0075】

CAAC−OS膜は、完全な単結晶ではなく、完全な非晶質でもない。CAAC−OS膜は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであることが多い。また、透過型電子顕微鏡(TEM:Transmission Electron Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界に起因する電子移動度の低下が抑制される。

【0076】

CAAC−OS膜に含まれる結晶部は、c軸がCAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−5°以上5°以下の範囲も含まれることとする。

【0077】

なお、CAAC−OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC−OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

【0078】

CAAC−OS膜に含まれる結晶部のc軸は、CAAC−OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0079】

CAAC−OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

【0080】

CAAC−OS膜を得る方法としては、3つ挙げられる。1つ目は、成膜温度を200℃以上500℃以下として酸化物半導体層の成膜を行い、表面に概略垂直にc軸配向させる方法である。2つ目は、膜厚を薄く成膜した後、200℃以上700℃以下の加熱処理を行い、表面に概略垂直にc軸配向させる方法である。3つ目は、一層目の膜厚を薄く成膜した後、200℃以上700℃以下の加熱処理を行い、2層目の成膜を行い、表面に概略垂直にc軸配向させる方法である。

【0081】

第1の酸化物半導体層101、第2の酸化物半導体層102、第3の酸化物半導体層103の膜厚は、1nm以上100nm以下(好ましくは5nm以上30nm以下)とし、スパッタリング法、MBE(Molecular Beam Epitaxy)法、CVD法、パルスレーザ堆積法、ALD(Atomic Layer Deposition)法等を適宜用いて作製することができる。また、第1の酸化物半導体層101、第2の酸化物半導体層102、第3の酸化物半導体層103は、スパッタリングターゲット表面に対し、概略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜してもよい。

【0082】

酸化物半導体層を用いたトランジスタにおいて、該酸化物半導体層のエネルギーギャップは、トランジスタの電気特性に影響を与える。例えば、酸化物半導体層を用いたトランジスタにおいて、酸化物半導体層のエネルギーギャップが小さいと、オン特性(例えば、オン電流や電界効果移動度)が向上し、一方、酸化物半導体層のエネルギーギャップが大きいと、オフ電流が低減できる。

【0083】

異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層403を用いることによって、トランジスタ440a、トランジスタ440b、トランジスタ480aの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタ440a、トランジスタ440b、トランジスタ480aに付与することが可能となる。

【0084】

例えば、図4(A)に示すトランジスタ480aの酸化物半導体積層403において、第2の酸化物半導体層102のエネルギーギャップを第1の酸化物半導体層101及び第3の酸化物半導体層103のエネルギーギャップより小さくする。この場合、第1の酸化物半導体層101及び第3の酸化物半導体層103のエネルギーギャップはほぼ同じとすることができる。

【0085】

図4(C)に、図4(A)における膜厚方向(E1−E2間)のエネルギーバンド図を示す。トランジスタ480aでは、図4(C)に示すエネルギーバンド図となるように、第1の酸化物半導体層101、第2の酸化物半導体層102、及び第3の酸化物半導体層103の材料を選択することが好ましい。ただし、伝導帯に埋め込みチャネルが形成されれば十分な効果が得られるため、必ずしも図4(C)のように伝導帯と価電子帯の両方に凹部を有するエネルギーバンド図に限定しなくともよく、例えば伝導帯のみに凹部を有するエネルギーバンド図が得られる構成としてもよい。

【0086】

例えば、トランジスタ480aにおける第1の酸化物半導体層101としてIn−Ga−Zn系酸化物膜(エネルギーギャップ3.2eV)、第2の酸化物半導体層102としてはIn−Sn−Zn系酸化物膜(エネルギーギャップ2.8eV)、第3の酸化物半導体層103としてIn−Ga−Zn系酸化物膜(エネルギーギャップ3.2eV)を用いる。

【0087】

また、3層積層の酸化物半導体積層403としては、トランジスタ480aにおける第1の酸化物半導体層101としてIn−Ga−Zn系酸化物膜、第2の酸化物半導体層102としてはIn−Zn系酸化物膜、第3の酸化物半導体層103としてIn−Ga−Zn系酸化物膜の積層、第1の酸化物半導体層101としてGa−Zn系酸化物膜、第2の酸化物半導体層102としてはIn−Sn−Zn系酸化物膜、第3の酸化物半導体層103としてGa−Zn系酸化物膜の積層、又は第1の酸化物半導体層101としてGa−Zn系酸化物膜、第2の酸化物半導体層102としてはIn−Zn系酸化物膜、第3の酸化物半導体層103としてGa−Zn系酸化物膜の積層などを用いることができる。

【0088】

エネルギーギャップの小さい第2の酸化物半導体層102を、エネルギーギャップの大きい第1の酸化物半導体層101及び第3の酸化物半導体層103により挟む構造とすることによって、よりトランジスタ480aのオフ電流(リーク電流)を低減する効果が得られる。

【0089】

図2(A)乃至(E)にトランジスタ440aを用いて、作製方法の一例を示す。

【0090】

まず、基板400上に酸化物絶縁膜436を形成する。

【0091】

基板400に使用することができる基板に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することもでき、これらの基板上に半導体素子が設けられたものを、基板400として用いてもよい。

【0092】

また、基板400として、可撓性基板を用いて半導体装置を作製してもよい。可撓性を有する半導体装置を作製するには、可撓性基板上に酸化物半導体積層403を含むトランジスタ440aを直接作製してもよいし、他の作製基板に酸化物半導体積層403を含むトランジスタ440aを作製し、その後可撓性基板に剥離、転置してもよい。なお、作製基板から可撓性基板に剥離、転置するために、作製基板と酸化物半導体積層を含むトランジスタ440aとの間に剥離層を設けるとよい。

【0093】

酸化物絶縁膜436としては、プラズマCVD法又はスパッタリング法等により、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ハフニウム、酸化ガリウム、又はこれらの混合材料を用いて形成することができる。

【0094】

酸化物絶縁膜436は、単層でも積層でもよい。本実施の形態では酸化物絶縁膜436としてスパッタリング法を用いて形成する酸化シリコン膜を用いる。

【0095】

また、酸化物絶縁膜436と基板400との間に窒化物絶縁膜を設けてもよい。窒化物絶縁膜は、プラズマCVD法又はスパッタリング法等により、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム、又はこれらの混合材料を用いて形成することができる。

【0096】

次に、酸化物絶縁膜436上に第1の酸化物半導体膜191及び第2の酸化物半導体膜192からなる酸化物半導体膜の積層493を形成する(図2(A)参照)。

【0097】

酸化物絶縁膜436は、酸化物半導体膜の積層493(酸化物半導体積層403)と接するため、膜中(バルク中)に少なくとも化学量論論的組成比を超える量の酸素が存在することが好ましい。例えば、酸化物絶縁膜436として、酸化シリコン膜を用いる場合には、SiO2+α(ただし、α>0)とする。このような酸化物絶縁膜436を用いることで、酸化物半導体膜の積層493(酸化物半導体積層403)に酸素を供給することができ、特性を良好にすることができる。酸化物半導体膜の積層493(酸化物半導体積層403)へ酸素を供給することにより、膜中の酸素欠損を補填することができる。

【0098】

例えば、酸素の供給源となる酸素を多く(過剰に)含む酸化物絶縁膜436を酸化物半導体膜の積層493(酸化物半導体積層403)と接して設けることによって、該酸化物絶縁膜436から酸化物半導体膜の積層493(酸化物半導体積層403)へ酸素を供給することができる。酸化物半導体膜の積層493(酸化物半導体積層403)及び酸化物絶縁膜436を少なくとも一部が接した状態で加熱処理を行うことによって酸化物半導体膜の積層493(酸化物半導体積層403)への酸素の供給を行ってもよい。

【0099】

酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)の形成工程において、酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)に水素、又は水がなるべく含まれないようにするために、酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)の成膜の前処理として、スパッタリング装置の予備加熱室で酸化物絶縁膜436が形成された基板を予備加熱し、基板及び酸化物絶縁膜436に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。

【0100】

酸化物絶縁膜436において酸化物半導体膜の積層493(酸化物半導体積層403)が接して形成される領域に、平坦化処理を行ってもよい。平坦化処理としては、特に限定されないが、研磨処理(例えば、化学的機械研磨(Chemical Mechanical Polishing:CMP)法)、ドライエッチング処理、プラズマ処理を用いることができる。

【0101】

プラズマ処理としては、例えば、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行うことができる。逆スパッタリングとは、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。逆スパッタリングを行うと、酸化物絶縁膜436の表面に付着している粉状物質(パーティクル、ごみともいう)を除去することができる。

【0102】

平坦化処理として、研磨処理、ドライエッチング処理、プラズマ処理は複数回行ってもよく、それらを組み合わせて行ってもよい。また、組み合わせて行う場合、工程順も特に限定されず、酸化物絶縁膜436表面の凹凸状態に合わせて適宜設定すればよい。

【0103】

なお、第1の酸化物半導体膜191及び第2の酸化物半導体膜192は、成膜時に酸素が多く含まれるような条件(例えば、酸素100%の雰囲気下でスパッタリング法により成膜を行うなど)で成膜して、酸素を多く含む(好ましくは酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている)膜とすることが好ましい。

【0104】

なお、本実施の形態において、第1の酸化物半導体膜191を、スパッタリング法で作製するためのターゲットとしては、例えば、組成比として、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、または20:45:35などとなる酸化物ターゲットを用いて、In−Sn−Zn−O膜を成膜する。

【0105】

なお、本実施の形態において、第2の酸化物半導体膜192を、スパッタリング法で作製するためのターゲットとしては、例えば、組成比として、In2O3:Ga2O3:ZnO=1:1:2[mol比]の酸化物ターゲットを用い、In−Ga−Zn系酸化物膜を成膜する。また、このターゲットの材料及び組成に限定されず、例えば、In2O3:Ga2O3:ZnO=1:1:1[mol比]の金属酸化物ターゲットを用いてもよい。

【0106】

また、金属酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜とすることができる。

【0107】

第1の酸化物半導体膜191及び第2の酸化物半導体膜192を、成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0108】

減圧状態に保持された成膜室内に基板を保持する。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板400上に酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)を成膜する。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H2O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)に含まれる不純物の濃度を低減できる。

【0109】

また、酸化物絶縁膜436と酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)とを大気に解放せずに連続的に形成することが好ましい。酸化物絶縁膜436と酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)とを大気に曝露せずに連続して形成すると、酸化物絶縁膜436表面に水素や水分などの不純物が吸着することを防止することができる。

【0110】

CAAC−OS膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa−b面から劈開し、a−b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、CAAC−OS膜を成膜することができる。

【0111】

また、CAAC−OS膜を成膜するために、以下の条件を適用することが好ましい。

【0112】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度(水素、水、二酸化炭素および窒素など)を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が−80℃以下、好ましくは−100℃以下である成膜ガスを用いる。

【0113】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を100℃以上740℃以下、好ましくは200℃以上500℃以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。

【0114】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

【0115】

スパッタリング用ターゲットの一例として、In−Ga−Zn−O化合物ターゲットについて以下に示す。

【0116】

InOX粉末、GaOY粉末およびZnOZ粉末を所定のmol数比で混合し、加圧処理後、1000℃以上1500℃以下の温度で加熱処理をすることで多結晶であるIn−Ga−Zn−O化合物ターゲットとする。なお、X、YおよびZは任意の正数である。ここで、所定のmol数比は、例えば、InOX粉末、GaOY粉末およびZnOZ粉末が、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3または3:1:2のmol数比である。なお、粉末の種類、およびその混合する比率は、作製するスパッタリング用ターゲットによって適宜変更すればよい。

【0117】

酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)をフォトリソグラフィ工程により島状の酸化物半導体積層403(第1の酸化物半導体層101及び第2の酸化物半導体層102)に加工する(図2(B)参照)。

【0118】

また、島状の酸化物半導体積層403を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0119】

なお、酸化物半導体膜のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。例えば、酸化物半導体膜のウェットエッチングに用いるエッチング液としては、燐酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO07N(関東化学社製)を用いてもよい。

【0120】

本実施の形態では、第1の酸化物半導体膜191及び第2の酸化物半導体膜192を同じマスクによりエッチング加工して形成するため、第1の酸化物半導体層101及び第2の酸化物半導体層102は側面の端部が一致した同形状の酸化物半導体層となる。酸化物半導体積層403において、第1の酸化物半導体層101及び第2の酸化物半導体層102の側面(端部)は露出している。

【0121】

また、酸化物半導体積層403(酸化物半導体膜の積層493)に、過剰な水素(水や水酸基を含む)を除去(脱水化または脱水素化)するための加熱処理を行ってもよい。加熱処理の温度は、300℃以上700℃以下、または基板の歪み点未満とする。加熱処理は減圧下又は窒素雰囲気下などで行うことができる。例えば、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体積層403(酸化物半導体膜の積層493)に対して窒素雰囲気下450℃において1時間の加熱処理を行う。

【0122】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0123】

例えば、加熱処理として、650℃〜700℃の高温に加熱した不活性ガス中に基板を入れ、数分間加熱した後、基板を不活性ガス中から出すGRTAを行ってもよい。

【0124】

なお、加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0125】

また、加熱処理で酸化物半導体積層403(酸化物半導体膜の積層493)を加熱した後、同じ炉に高純度の酸素ガス、高純度の一酸化二窒素ガス、又は超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で−55℃)以下、好ましくは1ppm以下、より好ましくは10ppb以下の空気)を導入してもよい。酸素ガスまたは一酸化二窒素ガスに、水、水素などが含まれないことが好ましい。または、熱処理装置に導入する酸素ガスまたは一酸化二窒素ガスの純度を、6N以上好ましくは7N以上(即ち、酸素ガスまたは一酸化二窒素ガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。酸素ガス又は一酸化二窒素ガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体積層403(酸化物半導体膜の積層493)を高純度化及び電気的にI型(真性)化することができる。

【0126】

なお、脱水化又は脱水素化のための加熱処理は、酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)の形成後、絶縁膜407の形成前であれば、トランジスタ440aの作製工程においてどのタイミングで行ってもよい。例えば、酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)の形成後、又は島状の酸化物半導体積層403(第1の酸化物半導体層101及び第2の酸化物半導体層102)の形成後に行うことができる。

【0127】

また、脱水化又は脱水素化のための加熱処理は、複数回行ってもよく、他の加熱処理と兼ねてもよい。例えば、第1の酸化物半導体膜191形成後と、第2の酸化物半導体膜192形成後に2回加熱処理を行ってもよい。

【0128】

脱水化又は脱水素化のための加熱処理を、酸化物半導体積層403(第1の酸化物半導体層101及び第2の酸化物半導体層102)として島状に加工される前、酸化物半導体膜の積層493(第1の酸化物半導体膜191及び第2の酸化物半導体膜192)が酸化物絶縁膜436を覆った状態で行うと、酸化物絶縁膜436に含まれる酸素が加熱処理によって放出されるのを防止することができるため好ましい。

【0129】

次いで、酸化物半導体積層403上に、ソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)となる導電膜を形成する。該導電膜は後の加熱処理に耐えられる材料を用いる。ソース電極層、及びドレイン電極層に用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タングステン膜)等を用いることができる。また、Al、Cuなどの金属膜の下側又は上側の一方または双方にTi、Mo、Wなどの高融点金属膜またはそれらの金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タングステン膜)を積層させた構成としても良い。また、ソース電極層、及びドレイン電極層に用いる導電膜としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ(In2O3―SnO2)、酸化インジウム酸化亜鉛(In2O3―ZnO)またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

【0130】

フォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層405a、ドレイン電極層405bを形成した後、レジストマスクを除去する。本実施の形態では、ソース電極層405a、ドレイン電極層405bとして膜厚10nmのタングステン膜を形成する。このようにソース電極層405a、ドレイン電極層405bの膜厚が薄いと、上に形成されるゲート絶縁膜402の被覆性が良好となる他、低抵抗領域を形成するために酸化物半導体積層403へドーパントを導入する場合、ソース電極層405a、ドレイン電極層405bを通過してソース電極層405a、ドレイン電極層405b下の酸化物半導体積層403にもドーパントを導入することができる。

【0131】

酸化物半導体積層403において、第1の酸化物半導体層101及び第2の酸化物半導体層102の側面(端部)は露出しているため、ソース電極層405a、ドレイン電極層405bは、第1の酸化物半導体層101及び第2の酸化物半導体層102の側面の一部に接するように形成される。

【0132】

次いで、酸化物半導体積層403、ソース電極層405a、及びドレイン電極層405bを覆うゲート絶縁膜402を形成する(図2(C)参照)。

【0133】

なお、ゲート絶縁膜402の被覆性を向上させるために、酸化物半導体積層403、ソース電極層405a、及びドレイン電極層405b表面にも上記平坦化処理を行ってもよい。特にゲート絶縁膜402として膜厚の薄い絶縁膜を用いる場合、酸化物半導体積層403、ソース電極層405a、及びドレイン電極層405b表面の平坦性が良好であることが好ましい。

【0134】

ゲート絶縁膜402の膜厚は、1nm以上20nm以下とし、スパッタリング法、MBE法、CVD法、パルスレーザ堆積法、ALD法等を適宜用いることができる。また、ゲート絶縁膜402は、スパッタリングターゲット表面に対し、概略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜してもよい。

【0135】

ゲート絶縁膜402としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。ゲート絶縁膜402は、酸化物半導体積層403と接する部分において酸素を含むことが好ましい。特に、ゲート絶縁膜402は、膜中(バルク中)に少なくとも化学量論論的組成比を超える量の酸素が存在することが好ましく、例えば、ゲート絶縁膜402として、酸化シリコン膜を用いる場合には、SiO2+α(ただし、α>0)とする。本実施の形態では、ゲート絶縁膜402として、SiO2+α(ただし、α>0)である酸化シリコン膜を用いる。この酸化シリコン膜をゲート絶縁膜402として用いることで、酸化物半導体積層403に酸素を供給することができ、特性を良好にすることができる。さらに、ゲート絶縁膜402は、作製するトランジスタのサイズやゲート絶縁膜402の段差被覆性を考慮して形成することが好ましい。

【0136】

また、ゲート絶縁膜402の材料として酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(HfSixOyx>0、y>0))、窒素が添加されたハフニウムシリケート(HfSiOxNy(x>0、y>0))、ハフニウムアルミネート(HfAlxOy(x>0、y>0))、酸化ランタンなどのhigh−k材料を用いることでゲートリーク電流を低減できる。さらに、ゲート絶縁膜402は、単層構造としても良いし、積層構造としても良い。

【0137】

そして、ゲート電極層401をプラズマCVD法又はスパッタリング法等により、ゲート絶縁膜402上に形成する。ゲート電極層401は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極層401としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。ゲート電極層401は、単層構造としてもよいし、積層構造としてもよい。

【0138】

また、ゲート電極層401の材料は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることもできる。

【0139】

また、ゲート絶縁膜402と接するゲート電極層401の一層として、窒素を含む金属酸化物、具体的には、窒素を含むIn−Ga−Zn−O膜や、窒素を含むIn−Sn−O膜や、窒素を含むIn−Ga−O膜や、窒素を含むIn−Zn−O膜や、窒素を含むSn−O膜や、窒素を含むIn−O膜や、金属窒化膜(InN、SnNなど)を用いることができる。これらの膜は5電子ボルト、好ましくは5.5電子ボルト以上の仕事関数を有し、ゲート電極層として用いた場合、トランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

【0140】

以上の工程で、本実施の形態のトランジスタ440aが作製される(図2(D)参照)。異なるエネルギーギャップを有する複数の酸化物半導体層(第1の酸化物半導体層101及び第2の酸化物半導体層102)を用いた酸化物半導体積層403を用いることによって、トランジスタ440a、440bの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタ440a、440bに付与することが可能となる。

【0141】

次いで、酸化物半導体積層403、ソース電極層405a、ドレイン電極層405b、ゲート絶縁膜402、ゲート電極層401上に絶縁膜407を形成する(図2(E)参照)。

【0142】

絶縁膜407は、プラズマCVD法、スパッタリング法、又は蒸着法等により成膜することができる。絶縁膜407は、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、又は酸化ガリウム膜などの無機絶縁膜などを用いることができる。

【0143】

また、絶縁膜407として、酸化アルミニウム膜、酸化ハフニウム膜、酸化マグネシウム膜、酸化ジルコニウム膜、酸化ランタン膜、酸化バリウム膜、又は金属窒化物膜(例えば、窒化アルミニウム膜)も用いることができる。

【0144】

絶縁膜407は、単層でも積層でもよく、例えば酸化シリコン膜及び酸化アルミニウム膜の積層を用いることができる。

【0145】

絶縁膜407は、スパッタリング法など、絶縁膜407に水、水素等の不純物を混入させない方法を適宜用いて形成することが好ましい。また、絶縁膜407において、酸化物半導体積層403に接する絶縁膜は、酸素を過剰に含む膜とすると、酸化物半導体積層403への酸素の供給源となるために好ましい。

【0146】

本実施の形態では、絶縁膜407として膜厚100nmの酸化シリコン膜を、スパッタリング法を用いて成膜する。酸化シリコン膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガスと酸素の混合雰囲気下において行うことができる。

【0147】

酸化物半導体膜の成膜時と同様に、絶縁膜407の成膜室内の残留水分を除去するためには、吸着型の真空ポンプ(クライオポンプなど)を用いることが好ましい。クライオポンプを用いて排気した成膜室で成膜した絶縁膜407に含まれる不純物の濃度を低減できる。また、絶縁膜407の成膜室内の残留水分を除去するための排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。

【0148】

絶縁膜407を、成膜する際に用いるスパッタガスとしては、水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0149】

また、図3(B)に示すように、トランジスタ440d上に層間絶縁膜として設ける絶縁膜として、トランジスタ440dと絶縁膜407の間に絶縁膜416を形成し、層間絶縁膜を積層構造としてもよい。絶縁膜416は絶縁膜407と同様な材料及び方法を用いて形成することができる。例えば、絶縁膜416として酸化アルミニウム膜を用い、絶縁膜407として酸化シリコン膜を用いることで、トランジスタ440d上に設ける絶縁膜として、酸化アルミニウム膜と酸化シリコン膜との積層を用いることができる。なお、トランジスタ440dは、ゲート絶縁膜402を、ゲート電極層401をマスクとしてエッチング加工し、酸化物半導体積層403の一部を露出させ、酸化物半導体積層403の一部と絶縁膜416とを接するように設ける例である。

【0150】

酸化物半導体積層403上に設けられる絶縁膜407、絶縁膜416として用いることのできる酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を通過させない遮断効果(ブロック効果)が高い。

【0151】

従って、酸化アルミニウム膜は、作製工程中及び作製後において、変動要因となる水素、水分などの不純物の酸化物半導体積層403への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体積層403からの放出を防止する保護膜として機能する。

【0152】

また、トランジスタ起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。平坦化絶縁膜としては、ポリイミド、アクリル、ベンゾシクロブテン系樹脂、等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low−k材料)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁膜を形成してもよい。

【0153】

また、絶縁膜407にソース電極層405a、ドレイン電極層405bに達する開口を形成し、開口にソース電極層405a、ドレイン電極層405bと電気的に接続する配線層を形成してもよい。配線層を用いて他のトランジスタと接続させ、様々な回路を構成することができる。

【0154】

ソース電極層405a、ドレイン電極層405bはソース電極層405a、ドレイン電極層405bに達する開口を形成する際のエッチング工程により、一部オーバーエッチングされることがある。ソース電極層及びドレイン電極層を積層構造とし、開口形成時のエッチングストッパーとしても機能する導電膜をソース電極層及びドレイン電極層として設けることができる。

【0155】

図3(A)で示すように、トランジスタ440cはソース電極層及びドレイン電極層を積層構造とする例であり、ソース電極層としてソース電極層404a及びソース電極層405a、ドレイン電極層としてドレイン電極層404b及びドレイン電極層405bが積層されている。トランジスタ440cのように、ゲート絶縁膜402、絶縁膜407、及びソース電極層405a、ドレイン電極層405bにソース電極層404a、ドレイン電極層404bに達する開口を形成し、開口にソース電極層404a、ドレイン電極層404bと電気的に接続する配線層465a、配線層465bを形成してもよい。

【0156】

トランジスタ440cにおいて、ソース電極層404a、ドレイン電極層404bは開口形成時においてエッチングストッパーとしても機能する。ソース電極層404a、ドレイン電極層404bとしてはタングステン膜や窒化タンタル膜など、ソース電極層405a、ドレイン電極層405bとしては銅膜やアルミニウム膜などをそれぞれ用いることができる。ソース電極層404a及びソース電極層405a、ドレイン電極層404b及びドレイン電極層405bの積層における膜厚を、5nm以上15nm以下程度とすると、ゲート絶縁膜402の被覆性を良好とすることができる。

【0157】

配線層465a、配線層465bはゲート電極層401、ソース電極層405a、ドレイン電極層405bと同様の材料及び方法を用いて形成することができる。例えば、配線層465a、配線層465bとして窒化タンタル膜と銅膜との積層、又は窒化タンタル膜とタングステン膜との積層などを用いることができる。

【0158】

また、ゲート電極層401の側面に側壁絶縁層を設けてもよい。側壁絶縁層は、ゲート電極層401を覆う絶縁膜を形成した後、これをRIE(Reactive ion etching:反応性イオンエッチング)法による異方性のエッチングによって絶縁膜を加工し、ゲート電極層401の側壁に自己整合的に側壁絶縁層を形成すればよい。ここで、絶縁膜について特に限定はないが、例えば、TEOS(Tetraethyl−Ortho−Silicate)若しくはシラン等と、酸素若しくは亜酸化窒素等とを反応させて形成した段差被覆性のよい酸化シリコンを用いることができる。絶縁膜は熱CVD、プラズマCVD、常圧CVD、バイアスECRCVD、スパッタリング等の方法によって形成することができる。また、低温酸化(LTO:Low Temperature Oxidation)法により形成する酸化シリコンを用いてもよい。

【0159】

高純度化され、酸素欠損が補填された酸化物半導体積層403は、水素、水などの不純物が十分に除去されており、酸化物半導体積層403中の水素濃度は5×1019atoms/cm3以下、好ましくは5×1018atoms/cm3以下である。なお、酸化物半導体積層403中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)で測定されるものである。

【0160】

本実施の形態を用いて作製した、高純度化し、酸素欠損を補填する酸素を過剰に含む酸化物半導体積層403を用いたトランジスタ440aは、オフ状態における電流値(オフ電流値)を、チャネル幅1μm当たり室温にて100zA/μm(1zA(ゼプトアンペア)は1×10−21A)以下、好ましくは10zA/μm以下、より好ましくは1zA/μm以下、さらに好ましくは100yA/μm以下レベルにまで低くすることができる。

【0161】

以上のように、高機能、高信頼性、又は低消費電力など、種々の目的に応じた半導体装置を提供することができる。

【0162】

(実施の形態2)

本実施の形態では、半導体装置及び半導体装置の作製方法の他の一形態を、図5を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0163】

本実施の形態では、開示する発明に係る半導体装置の作製方法において、脱水化又は脱水素化処理を行った酸化物半導体積層に、酸素(少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む)を導入して膜中に酸素を供給する例を示す。

【0164】

脱水化又は脱水素化処理によって、酸化物半導体を構成する主成分材料である酸素が同時に脱離して減少してしまうおそれがある。酸化物半導体積層において、酸素が脱離した箇所では酸素欠損が存在し、該酸素欠損に起因してトランジスタの電気特性変動を招くドナー準位が生じてしまう。

【0165】

よって、脱水化又は脱水素化処理を行った酸化物半導体積層に、酸素を供給することが好ましい。酸化物半導体積層へ酸素を供給することにより、膜中の酸素欠損を補填することができる。該酸化物半導体積層をトランジスタに用いることで、酸素欠損に起因するトランジスタのしきい値電圧Vthのばらつき、しきい値電圧のシフトΔVthを低減することができる。また、しきい値電圧をプラスシフトさせ、トランジスタをノーマリーオフ化することもできる。

【0166】

図5(A)は、図2(C)と対応しており、酸化物絶縁膜436が設けられた基板400上に、エネルギーギャップの異なる第1の酸化物半導体層101及び第2の酸化物半導体層102を含む酸化物半導体積層403、ソース電極層405a、ドレイン電極層405b、ゲート絶縁膜402が形成されている。

【0167】

次に、酸化物半導体積層403に酸素431(少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む)を導入して、第1の酸化物半導体層101及び第2の酸化物半導体層102を含む酸化物半導体積層403に酸素過剰領域111、112を形成する(図5(B)参照)。

【0168】

なお、酸素過剰領域111、112は、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が、少なくとも一部含まれている領域とする。酸素過剰領域111、112に供給された酸素431によって、第1の酸化物半導体層101及び第2の酸化物半導体層102を含む酸化物半導体積層403中に存在する酸素欠損を補填することができる。

【0169】

酸素過剰領域111、112を有する酸化物半導体積層403、ゲート絶縁膜402上にゲート電極層401を形成し、トランジスタ430を作製する(図5(C)参照)。

【0170】

脱水化又は脱水素化処理を行った酸化物半導体積層403に、酸素を導入して膜中に酸素を供給することによって、酸化物半導体積層403を高純度化し、I型(真性)化することができる。高純度化し、I型(真性)化した酸化物半導体積層403を有するトランジスタ430は、電気特性変動が抑制されており、電気的に安定である。

【0171】

酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。

【0172】

酸素の導入工程は、酸化物半導体積層403に酸素導入する場合、酸化物半導体積層403に直接導入してもよいし、ゲート絶縁膜402や絶縁膜407などの他の膜を通過して酸化物半導体積層403へ導入してもよい。酸素を他の膜を通過して導入する場合は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いればよいが、酸素を露出された酸化物半導体積層403へ直接導入する場合は、プラズマ処理なども用いることができる。

【0173】

酸化物半導体積層403への酸素の導入は、脱水化又は脱水素化処理を行った後であればよく、特に限定されない。また、上記脱水化又は脱水素化処理を行った酸化物半導体積層403への酸素の導入は複数回行ってもよい。

【0174】

例えば、実施の形態1において、酸化物半導体積層403への酸素の導入は、露出した酸化物半導体膜の積層493、又は酸化物半導体積層403に対して、ソース電極層405a、ドレイン電極層405b形成後、ゲート絶縁膜402形成後、ゲート電極層401形成後、(絶縁膜416形成後)、絶縁膜407形成後に行うことができる。

【0175】

また、酸化物半導体積層403中の酸素過剰領域111、112において、酸素の導入工程によって導入された酸素濃度を1×1018atoms/cm3以上5×1021atoms/cm3以下とするのが好ましい。

【0176】

なお、酸化物半導体において、酸素は主たる成分材料の一つである。このため、酸化物半導体積層403中の酸素濃度を、SIMS(Secondary Ion Mass Spectrometry)などの方法を用いて、正確に見積もることは難しい。つまり、酸化物半導体積層403に酸素が意図的に添加されたか否かを判別することは困難であるといえる。

【0177】

ところで、酸素には17Oや18Oといった同位体が存在し、自然界におけるこれらの存在比率はそれぞれ酸素原子全体の0.037%、0.204%程度であることが知られている。つまり、酸化物半導体積層403中にこれらの同位体を意図的に添加した場合、これら同位体の濃度は、SIMSなどの方法によって見積もることができ、これらの濃度を測定することで、酸化物半導体積層403中の酸素濃度をより正確に見積もることが可能な場合がある。よって、これらの濃度を測定することで、酸化物半導体積層403に意図的に酸素が添加されたか否かを判別しても良い。

【0178】

また、酸化物半導体膜へ酸素を導入した後、加熱処理を行うことが好ましい。

【0179】

本実施の形態のトランジスタ430のように、酸素を直接酸化物半導体積層403へ導入する場合は、酸化物半導体積層403と接する酸化物絶縁膜436、ゲート絶縁膜402を、必ずしも酸素を多くに含む膜とする必要はない。導入した酸素が再度酸化物半導体積層403から脱離しないように、また、水素、水などの水素を含む不純物が酸化物半導体積層403へ再度混入しないように、酸素、水素、水などの水素を含む不純物に対して遮断効果(ブロック効果)が高い膜を絶縁膜407として設けることが好ましい。例えば、水素、水分などの不純物、及び酸素の両方に対して遮断効果(ブロック効果)が高い酸化アルミニウム膜などを用いるとよい。

【0180】

もちろん、酸化物半導体膜と接する酸化物絶縁膜436、ゲート絶縁膜402を、酸素を多く含む膜とし、さらに酸素を直接酸化物半導体積層403に導入し、複数の酸素供給方法を行ってもよい。

【0181】

また、本実施の形態では酸化物半導体積層403への酸素導入を例として説明するが、酸素の導入は酸化物半導体積層403と接するゲート絶縁膜402、酸化物絶縁膜436、絶縁膜416や、絶縁膜407などに行ってもよい。酸化物半導体積層403と接するゲート絶縁膜402、酸化物絶縁膜436、絶縁膜416や、絶縁膜407に酸素を導入し、酸素過剰とすることによって、酸化物半導体積層403への酸素の供給を行うことができる。

【0182】

以上のように、安定した電気特性を有する酸化物半導体積層を用いた半導体装置を提供することができる。よって、信頼性の高い半導体装置を提供することができる。

【0183】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0184】

(実施の形態3)

本実施の形態では、半導体装置及び半導体装置の作製方法の他の一形態を、図6を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0185】

本実施の形態では、開示する発明に係る半導体装置の作製方法において、酸化物半導体積層に低抵抗領域を形成する例である。低抵抗領域は、酸化物半導体積層へ導電率を変化させる不純物(ドーパントともいう)を導入して形成することができる。

【0186】

図6(A)は、図2(D)と対応しており、酸化物絶縁膜436が設けられた基板400上に、エネルギーギャップの異なる第1の酸化物半導体層101及び第2の酸化物半導体層102を含む酸化物半導体積層403、ソース電極層405a、ドレイン電極層405b、ゲート絶縁膜402、ゲート電極層401が形成されている。

【0187】

次に、ゲート電極層401をマスクとして、酸化物半導体積層403に、ゲート絶縁膜402、ソース電極層405a、及びドレイン電極層405bを通過してドーパント421を選択的に導入し、低抵抗領域121a、121b、122a、122bを形成する。

【0188】

本実施の形態では、ソース電極層405a、及びドレイン電極層405bを薄膜とするため、ソース電極層405a、及びドレイン電極層405b下の酸化物半導体積層403にもドーパント421が導入され、低抵抗領域121a、121b、122a、122bが形成される例を示す。

【0189】

ソース電極層405a、及びドレイン電極層405bの膜厚や、ドーパント421の導入条件によっては、ソース電極層405a、及びドレイン電極層405b下の酸化物半導体積層403にはドーパント421が導入されない場合、導入されても濃度が低くソース電極層405a、又はドレイン電極層405b下以外の低抵抗領域と比べて抵抗が高い領域となる場合もある。また、ドーパント421の導入条件によっては、第1の酸化物半導体層101のみ、第2の酸化物半導体層102のみにドーパント421が導入され、低抵抗領域が形成される場合、第1の酸化物半導体層101と第2の酸化物半導体層102においてドーパントの濃度分布が存在する場合がある。

【0190】

ドーパント421は、酸化物半導体積層403の導電率を変化させる不純物である。ドーパント421としては、15族元素(代表的にはリン(P)、砒素(As)、およびアンチモン(Sb))、ホウ素(B)、アルミニウム(Al)、窒素(N)、アルゴン(Ar)、ヘリウム(He)、ネオン(Ne)、インジウム(In)、フッ素(F)、塩素(Cl)、チタン(Ti)、及び亜鉛(Zn)のいずれかから選択される一以上を用いることができる。

【0191】

ドーパント421は、注入法により、絶縁膜407、ソース電極層405a、及びドレイン電極層405bを通過して、酸化物半導体積層403に導入する。ドーパント421の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。その際には、ドーパント421の単体のイオンあるいはフッ化物、塩化物のイオンを用いると好ましい。

【0192】

ドーパント421の導入工程は、加速電圧、ドーズ量などの注入条件、また通過させる絶縁膜407の膜厚を適宜設定して制御すればよい。本実施の形態では、ドーパント421としてホウ素を用いて、イオン注入法でホウ素イオンの注入を行う。なお、ドーパント421のドーズ量は1×1013ions/cm2以上5×1016ions/cm2以下とすればよい。

【0193】

低抵抗領域におけるドーパント421の濃度は、5×1018/cm3以上1×1022/cm3以下であることが好ましい。

【0194】

ドーパント421を導入する際に、基板400を加熱しながら行ってもよい。

【0195】

なお、酸化物半導体積層403にドーパント421を導入する処理は、複数回行ってもよく、ドーパントの種類も複数種用いてもよい。

【0196】

また、ドーパント421の導入処理後、加熱処理を行ってもよい。加熱条件としては、温度300℃以上700℃以下、好ましくは300℃以上450℃以下で1時間、酸素雰囲気下で行うことが好ましい。また、窒素雰囲気下、減圧下、大気(超乾燥エア)下で加熱処理を行ってもよい。

【0197】

酸化物半導体積層403を結晶性酸化物半導体膜とした場合、ドーパント421の導入により、一部非晶質化する場合がある。この場合、ドーパント421の導入後に加熱処理を行うことによって、酸化物半導体積層403の結晶性を回復することができる。

【0198】

よって酸化物半導体積層403において、チャネル形成領域121cを挟んで低抵抗領域121a、121bが設けられた第1の酸化物半導体層101と、チャネル形成領域122cを挟んで低抵抗領域122a、122bが設けられた第2の酸化物半導体層102とが形成される。

【0199】

以上の工程で、本実施の形態のトランジスタ420が作製される(図6(B)参照)。

【0200】

また、実施の形態1で示したトランジスタ440dのように、ゲート絶縁膜402がゲート電極層401をマスクにしてエッチングされており、酸化物半導体積層403が一部露出され、絶縁膜416と接するトランジスタにおいて、ドーパントを導入し、低抵抗領域を形成したトランジスタ425を図3(C)に示す。

【0201】

トランジスタ425は、ゲート電極層401をマスクとしてドーパントを導入し、チャネル形成領域121c、122cを挟んで、低抵抗領域121a、121b、122a、122bを形成して作製される。また、ドーパントを導入する際に通過するソース電極層、ドレイン電極層にもドーパントが導入される場合がある。トランジスタ425は、ドーパントがソース電極層及びドレイン電極層にも導入され、ドーパントを含むソース電極層415a、ドーパントを含むドレイン電極層415bとなる例である。

【0202】

チャネル長方向にチャネル形成領域121cを挟んで低抵抗領域121a、121bが設けられた第1の酸化物半導体層101と、チャネル形成領域122cを挟んで低抵抗領域122a、122bが設けられた第2の酸化物半導体層102とを含む酸化物半導体積層403を有することにより、トランジスタ420及びトランジスタ425はオン特性(例えば、オン電流及び電界効果移動度)が高く、高速動作、高速応答が可能となる。

【0203】

また、実施の形態2で示した酸素過剰領域を有するトランジスタ430にドーパントを導入し、低抵抗領域を形成したトランジスタ423を図6(C)に示す。

【0204】

トランジスタ423は、図5(C)のトランジスタ430のように、酸素過剰領域111を含む第1の酸化物半導体層101、及び酸素過剰領域112を含む第2の酸化物半導体層102を有する酸化物半導体積層が設けられたトランジスタにおいて、ゲート電極層401をマスクとしてドーパントを導入し、酸素を過剰に含むチャネル形成領域121c、122cを挟んで、ドーパント及び過剰な酸素を含む低抵抗領域121d、121e、122d、122eと、ドーパントを含む低抵抗領域121a、121b、122a、122bを形成して作製される。

【0205】

チャネル長方向にチャネル形成領域121cを挟んで低抵抗領域121d、121e、121a、121bが設けられた第1の酸化物半導体層101と、チャネル形成領域122cを挟んで低抵抗領域122d、122e、122a、122bが設けられた第2の酸化物半導体層102とを含む酸化物半導体積層403を有することにより、該トランジスタ423はオン特性(例えば、オン電流及び電界効果移動度)が高く、高速動作、高速応答が可能となる。

【0206】

また、実施の形態1で示したトランジスタ480aのように、酸化物半導体積層403が3層構造のトランジスタにおいて、酸素及びドーパントを導入し、酸素過剰領域及び低抵抗領域を形成したトランジスタ480bを図4(B)に示す。

【0207】

トランジスタ480bは、第1の酸化物半導体層101、第2の酸化物半導体層102、及び第3の酸化物半導体層103を含む酸化物半導体積層403に酸素を導入して酸素過剰領域を形成し、ゲート電極層401形成後、ゲート電極層401をマスクとしてドーパントを導入し、酸素を過剰に含むチャネル形成領域121c、122c、123cを挟んで、ドーパント及び過剰な酸素を含む低抵抗領域121d、121e、122d、122e、123d、123eと、ドーパントを含む低抵抗領域121a、121b、122a、122b、123a、123bを形成して作製される。

【0208】

チャネル長方向にチャネル形成領域121cを挟んで低抵抗領域121d、121e、121a、121bが設けられた第1の酸化物半導体層101と、チャネル形成領域122cを挟んで低抵抗領域122d、122e、122a、122bが設けられた第2の酸化物半導体層102と、チャネル形成領域123cを挟んで低抵抗領域123d、123e、123a、123bが設けられた第3の酸化物半導体層103とを含む酸化物半導体積層403を有することにより、該トランジスタ480bはオン特性(例えば、オン電流及び電界効果移動度)が高く、高速動作、高速応答が可能となる。

【0209】

トランジスタ420、トランジスタ423、トランジスタ425、トランジスタ480bにおいて、低抵抗領域121a、121b、122a、122bはソース領域、又はドレイン領域として機能させることができる。低抵抗領域121a、121b、122a、122bを設けることによって、低抵抗領域121a、121b、122a、122bの間に形成されるチャネル形成領域121c、122cに加わる電界を緩和させることができる。また、低抵抗領域121a、121b、122a、122bにおいて酸化物半導体積層403とソース電極層405a及びドレイン電極層405bとを電気的に接続させることによって、酸化物半導体積層403とソース電極層405a及びドレイン電極層405bとの接触抵抗を低減することができる。従って、トランジスタ420、トランジスタ423の電気特性を向上させることができる。

【0210】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0211】

(実施の形態4)

実施の形態1乃至3のいずれかで一例を示したトランジスタを用いて表示機能を有する半導体装置(表示装置ともいう)を作製することができる。また、トランジスタを含む駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

【0212】

図7(A)において、第1の基板4001上に設けられた画素部4002を囲むようにして、シール材4005が設けられ、第2の基板4006によって封止されている。図7(A)においては、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された走査線駆動回路4004、信号線駆動回路4003が実装されている。また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、FPC(Flexible printed circuit)4018a、4018bから供給されている。

【0213】

図7(B)(C)において、第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。よって画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、表示素子と共に封止されている。図7(B)(C)においては、第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路4003が実装されている。図7(B)(C)においては、別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、FPC4018から供給されている。

【0214】

また図7(B)(C)においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装してもよいし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装してもよい。

【0215】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG(Chip On Glass)方法、ワイヤボンディング方法、或いはTAB(Tape Automated Bonding)方法などを用いることができる。図7(A)は、COG方法により信号線駆動回路4003、走査線駆動回路4004を実装する例であり、図7(B)は、COG方法により信号線駆動回路4003を実装する例であり、図7(C)は、TAB方法により信号線駆動回路4003を実装する例である。

【0216】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。

【0217】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源(照明装置含む)を指す。また、コネクター、例えばFPCもしくはTABテープもしくはTCPが取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG方式によりIC(集積回路)が直接実装されたモジュールも全て表示装置に含むものとする。

【0218】

また第1の基板上に設けられた画素部及び走査線駆動回路は、トランジスタを複数有しており、実施の形態1乃至3のいずれかで一例を示したトランジスタを適用することができる。

【0219】

表示装置に設けられる表示素子としては液晶素子(液晶表示素子ともいう)、発光素子(発光表示素子ともいう)、を用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL(Electro Luminescence)、有機EL等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

【0220】

半導体装置の一形態について、図7及び図8を用いて説明する。図8は、図7(B)のM−Nにおける断面図に相当する。

【0221】

図7及び図8で示すように、半導体装置は接続端子電極4015及び端子電極4016を有しており、接続端子電極4015及び端子電極4016はFPC4018が有する端子と異方性導電膜4019を介して、電気的に接続されている。

【0222】

接続端子電極4015は、第1の電極層4030と同じ導電膜から形成され、端子電極4016は、トランジスタ4010、4011のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

【0223】

また第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004は、トランジスタを複数有しており、図7及び図8では、画素部4002に含まれるトランジスタ4010と、走査線駆動回路4004に含まれるトランジスタ4011とを例示している。図8(A)では、トランジスタ4010、4011上には絶縁膜4020が設けられ、図8(B)ではさらに、絶縁膜4021が設けられている。なお、絶縁膜4023は下地膜として機能する絶縁膜である。

【0224】

トランジスタ4010、トランジスタ4011としては、実施の形態1乃至3のいずれかで示したトランジスタを適用することができる。本実施の形態では、実施の形態1で示したトランジスタ440aと同様な構造を有するトランジスタを適用する例を示す。

【0225】

トランジスタ4010及びトランジスタ4011は、半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を有するトランジスタである。異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層を用いることによって、トランジスタの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタ4010及びトランジスタ4011に付与することが可能となる。

【0226】

よって、図7及び図8で示す本実施の形態の半導体装置として、高機能、高信頼性、又は低消費電力など、種々の目的に応じた半導体装置を提供することができる。

【0227】

画素部4002に設けられたトランジスタ4010は表示素子と電気的に接続し、表示パネルを構成する。表示素子は表示を行うことができれば特に限定されず、様々な表示素子を用いることができる。

【0228】

図8(A)に表示素子として液晶素子を用いた液晶表示装置の例を示す。図8(A)において、表示素子である液晶素子4013は、第1の電極層4030、第2の電極層4031、及び液晶層4008を含む。なお、液晶層4008を挟持するように配向膜として機能する絶縁膜4032、4033が設けられている。第2の電極層4031は第2の基板4006側に設けられ、第1の電極層4030と第2の電極層4031とは液晶層4008を介して積層する構成となっている。

【0229】

また4035は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、液晶層4008の膜厚(セルギャップ)を制御するために設けられている。なお球状のスペーサを用いていてもよい。

【0230】

表示素子として、液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料(液晶組成物)は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

【0231】

また、液晶層4008に、配向膜を用いないブルー相を発現する液晶組成物を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は、液晶及びカイラル剤を混合させた液晶組成物を用いて発現させることができる。また、ブルー相が発現する温度範囲を広げるために、ブルー相を発現する液晶組成物に重合性モノマー及び重合開始剤などを添加し、高分子安定化させる処理を行って液晶層を形成することもできる。ブルー相を発現する液晶組成物は、応答速度が短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。よって液晶表示装置の生産性を向上させることが可能となる。酸化物半導体膜を用いるトランジスタは、静電気の影響によりトランジスタの電気的な特性が著しく変動して設計範囲を逸脱する恐れがある。よって酸化物半導体膜を用いるトランジスタを有する液晶表示装置にブルー相を発現する液晶組成物を用いることはより効果的である。

【0232】

また、液晶材料の固有抵抗は、1×109Ω・cm以上であり、好ましくは1×1011Ω・cm以上であり、さらに好ましくは1×1012Ω・cm以上である。なお、本明細書における固有抵抗の値は、20℃で測定した値とする。

【0233】

液晶表示装置に設けられる保持容量の大きさは、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間の間電荷を保持できるように設定される。保持容量の大きさは、トランジスタのオフ電流等を考慮して設定すればよい。本明細書に開示する酸化物半導体膜を有するトランジスタを用いることにより、各画素における液晶容量に対して1/3以下、好ましくは1/5以下の容量の大きさを有する保持容量を設ければ充分である。

【0234】

本明細書に開示する酸化物半導体膜を用いたトランジスタは、オフ状態における電流値(オフ電流値)を低く制御することができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

【0235】

また、本明細書に開示する酸化物半導体膜を用いたトランジスタは、電界効果移動度を高く制御することができるため、高速駆動が可能である。例えば、このような高速駆動が可能なトランジスタを液晶表示装置に用いることで、画素部のスイッチングトランジスタと、駆動回路部に使用するドライバートランジスタを同一基板上に形成することができる。すなわち、別途駆動回路として、シリコンウェハ等により形成された半導体装置を用いる必要がないため、半導体装置の部品点数を削減することができる。また、画素部においても、高速駆動が可能なトランジスタを用いることで、高画質な画像を提供することができる。よって、半導体装置として高信頼化も達成できる。

【0236】

液晶表示装置には、TN(Twisted Nematic)モード、IPS(In−Plane−Switching)モード、FFS(Fringe Field Switching)モード、ASM(Axially Symmetric aligned Micro−cell)モード、OCB(Optical Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モードなどを用いることができる。

【0237】

また、ノーマリーブラック型の液晶表示装置、例えば垂直配向(VA)モードを採用した透過型の液晶表示装置としてもよい。垂直配向モードとしては、いくつか挙げられるが、例えば、MVA(Multi−Domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASV(Advanced Super View)モードなどを用いることができる。また、VA型の液晶表示装置にも適用することができる。VA型の液晶表示装置とは、液晶表示パネルの液晶分子の配列を制御する方式の一種である。VA型の液晶表示装置は、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。また、画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれ別の方向に分子を倒すよう工夫されているマルチドメイン化あるいはマルチドメイン設計といわれる方法を用いることができる。

【0238】

また、表示装置において、ブラックマトリクス(遮光層)、偏光部材、位相差部材、反射防止部材などの光学部材(光学基板)などは適宜設ける。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

【0239】

また、画素部における表示方式は、プログレッシブ方式やインターレース方式等を用いることができる。また、カラー表示する際に画素で制御する色要素としては、RGB(Rは赤、Gは緑、Bは青を表す)の三色に限定されない。例えば、RGBW(Wは白を表す)、又はRGBに、イエロー、シアン、マゼンタ等を一色以上追加したものがある。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。ただし、開示する発明はカラー表示の表示装置に限定されるものではなく、モノクロ表示の表示装置に適用することもできる。

【0240】

また、表示装置に含まれる表示素子として、エレクトロルミネッセンスを利用する発光素子を適用することができる。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

【0241】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

【0242】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー−アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

【0243】

発光素子は発光を取り出すために少なくとも一対の電極の一方が透光性であればよい。そして、基板上にトランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、どの射出構造の発光素子も適用することができる。

【0244】

図8(B)に表示素子として発光素子を用いた発光装置の例を示す。表示素子である発光素子4513は、画素部4002に設けられたトランジスタ4010と電気的に接続している。なお発光素子4513の構成は、第1の電極層4030、電界発光層4511、第2の電極層4031の積層構造であるが、示した構成に限定されない。発光素子4513から取り出す光の方向などに合わせて、発光素子4513の構成は適宜変えることができる。

【0245】

隔壁4510は、有機絶縁材料、又は無機絶縁材料を用いて形成する。特に感光性の樹脂材料を用い、第1の電極層4030上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0246】

電界発光層4511は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでもよい。

【0247】

発光素子4513に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層4031及び隔壁4510上に保護膜を形成してもよい。保護膜としては、窒化シリコン膜、窒化酸化シリコン膜、DLC膜等を形成することができる。また、第1の基板4001、第2の基板4006、及びシール材4005によって封止された空間には充填材4514が設けられ密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

【0248】

充填材4514としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。例えば充填材として窒素を用いればよい。

【0249】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板(楕円偏光板を含む)、位相差板(λ/4板、λ/2板)、カラーフィルタなどの光学フィルムを適宜設けてもよい。また、偏光板又は円偏光板に反射防止膜を設けてもよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

【0250】

また、表示装置として、電子インクを駆動させる電子ペーパーを提供することも可能である。電子ペーパーは、電気泳動表示装置(電気泳動ディスプレイ)も呼ばれており、紙と同じ読みやすさ、他の表示装置に比べ低消費電力、薄くて軽い形状とすることが可能という利点を有している。

【0251】

電気泳動表示装置は、様々な形態が考えられ得るが、プラスの電荷を有する第1の粒子と、マイナスの電荷を有する第2の粒子とを含むマイクロカプセルが溶媒または溶質に複数分散されたものであり、マイクロカプセルに電界を印加することによって、マイクロカプセル中の粒子を互いに反対方向に移動させて一方側に集合した粒子の色のみを表示するものである。なお、第1の粒子または第2の粒子は染料を含み、電界がない場合において移動しないものである。また、第1の粒子の色と第2の粒子の色は異なるもの(無色を含む)とする。

【0252】

このように、電気泳動表示装置は、誘電定数の高い物質が高い電界領域に移動する、いわゆる誘電泳動的効果を利用したディスプレイである。

【0253】

上記マイクロカプセルを溶媒中に分散させたものが電子インクと呼ばれるものであり、この電子インクはガラス、プラスチック、布、紙などの表面に印刷することができる。また、カラーフィルタや色素を有する粒子を用いることによってカラー表示も可能である。

【0254】

なお、マイクロカプセル中の第1の粒子および第2の粒子は、導電体材料、絶縁体材料、半導体材料、磁性材料、液晶材料、強誘電性材料、エレクトロルミネセント材料、エレクトロクロミック材料、磁気泳動材料から選ばれた一種の材料、またはこれらの複合材料を用いればよい。

【0255】

また、電子ペーパーとして、ツイストボール表示方式を用いる表示装置も適用することができる。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を表示素子に用いる電極層である第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を生じさせての球形粒子の向きを制御することにより、表示を行う方法である。

【0256】

なお、図7及び図8において、第1の基板4001、第2の基板4006としては、ガラス基板の他、可撓性を有する基板も用いることができ、例えば透光性を有するプラスチック基板などを用いることができる。プラスチックとしては、FRP(Fiberglass−Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルムまたはアクリル樹脂フィルムを用いることができる。また、透光性が必要でなければ、アルミニウムやステンレスなどの金属基板(金属フィルム)を用いてもよい。例えば、アルミニウムホイルをPVFフィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。

【0257】

本実施の形態では、絶縁膜4020として酸化アルミニウム膜を用いる。

【0258】

酸化物半導体膜上に絶縁膜4020として設けられた酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を透過させない遮断効果(ブロック効果)が高い。

【0259】

従って、酸化アルミニウム膜は、作製工程中及び作製後において、変動要因となる水素、水分などの不純物の酸化物半導体膜への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体膜からの放出を防止する保護膜として機能する。

【0260】

また、平坦化絶縁膜として機能する絶縁膜4021は、アクリル、ポリイミド、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁膜を形成してもよい。

【0261】

絶縁膜4021の形成法は、特に限定されず、その材料に応じて、スパッタリング法、SOG法、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法等)、印刷法(スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーター等を用いることができる。

【0262】

表示装置は光源又は表示素子からの光を透過させて表示を行う。よって光が透過する画素部に設けられる基板、絶縁膜、導電膜などの薄膜はすべて可視光の波長領域の光に対して透光性とする。

【0263】

表示素子に電圧を印加する第1の電極層及び第2の電極層(画素電極層、共通電極層、対向電極層などともいう)においては、取り出す光の方向、電極層が設けられる場所、及び電極層のパターン構造によって透光性、反射性を選択すればよい。

【0264】

第1の電極層4030、第2の電極層4031は、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物、グラフェンなどの透光性を有する導電性材料を用いることができる。

【0265】

また、第1の電極層4030、第2の電極層4031はタングステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。

【0266】

また、第1の電極層4030、第2の電極層4031として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆるπ電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはアニリン、ピロールおよびチオフェンの2種以上からなる共重合体若しくはその誘導体などがあげられる。

【0267】

また、トランジスタは静電気などにより破壊されやすいため、駆動回路保護用の保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

【0268】

以上のように実施の形態1乃至3のいずれかで示したトランジスタを適用することで、様々な機能を有する半導体装置を提供することができる。

【0269】

(実施の形態5)

実施の形態1乃至3のいずれかで一例を示したトランジスタを用いて、対象物の情報を読み取るイメージセンサ機能を有する半導体装置を作製することができる。

【0270】

図9(A)に、イメージセンサ機能を有する半導体装置の一例を示す。図9(A)はフォトセンサの等価回路であり、図9(B)はフォトセンサの一部を示す断面図である。

【0271】

フォトダイオード602は、一方の電極がフォトダイオードリセット信号線658に、他方の電極がトランジスタ640のゲートに電気的に接続されている。トランジスタ640は、ソース又はドレインの一方がフォトセンサ基準信号線672に、ソース又はドレインの他方がトランジスタ656のソース又はドレインの一方に電気的に接続されている。トランジスタ656は、ゲートがゲート信号線659に、ソース又はドレインの他方がフォトセンサ出力信号線671に電気的に接続されている。

【0272】

なお、本明細書における回路図において、酸化物半導体膜を用いるトランジスタと明確に判明できるように、酸化物半導体膜を用いるトランジスタの記号には「OS」と記載している。図9(A)において、トランジスタ640、トランジスタ656は実施の形態1乃至3に示したトランジスタが適用でき、酸化物半導体膜を用いるトランジスタである。本実施の形態では、実施の形態1で示したトランジスタ440aと同様な構造を有するトランジスタを適用する例を示す。

【0273】

図9(B)は、フォトセンサにおけるフォトダイオード602及びトランジスタ640に示す断面図であり、基板601(TFT基板)上に、センサとして機能するフォトダイオード602及びトランジスタ640が設けられている。フォトダイオード602、トランジスタ640の上には接着層608を用いて基板613が設けられている。

【0274】

トランジスタ640上には絶縁膜631、絶縁膜632、層間絶縁膜633、層間絶縁膜634が設けられている。フォトダイオード602は、層間絶縁膜633上に設けられ、層間絶縁膜633上に形成した電極層641と、層間絶縁膜634上に設けられた電極層642との間に、層間絶縁膜633側から順に第1半導体膜606a、第2半導体膜606b、及び第3半導体膜606cを積層した構造を有している。

【0275】

電極層641は、層間絶縁膜634に形成された導電層643と電気的に接続し、電極層642は電極層641を介して導電層645と電気的に接続している。導電層645は、トランジスタ640のゲート電極層と電気的に接続しており、フォトダイオード602はトランジスタ640と電気的に接続している。

【0276】

ここでは、第1半導体膜606aとしてp型の導電型を有する半導体膜と、第2半導体膜606bとして高抵抗な半導体膜(I型半導体膜)、第3半導体膜606cとしてn型の導電型を有する半導体膜を積層するpin型のフォトダイオードを例示している。

【0277】

第1半導体膜606aはp型半導体膜であり、p型を付与する不純物元素を含むアモルファスシリコン膜により形成することができる。第1半導体膜606aの形成には13族の不純物元素(例えばボロン(B))を含む半導体材料ガスを用いて、プラズマCVD法により形成する。半導体材料ガスとしてはシラン(SiH4)を用いればよい。または、Si2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4等を用いてもよい。また、不純物元素を含まないアモルファスシリコン膜を形成した後に、拡散法やイオン注入法を用いて該アモルファスシリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合にアモルファスシリコン膜を形成する方法としては、LPCVD法、気相成長法、又はスパッタリング法等を用いればよい。第1半導体膜606aの膜厚は10nm以上50nm以下となるよう形成することが好ましい。

【0278】

第2半導体膜606bは、I型半導体膜(真性半導体膜)であり、アモルファスシリコン膜により形成する。第2半導体膜606bの形成には、半導体材料ガスを用いて、アモルファスシリコン膜をプラズマCVD法により形成する。半導体材料ガスとしては、シラン(SiH4)を用いればよい。または、Si2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4等を用いてもよい。第2半導体膜606bの形成は、LPCVD法、気相成長法、スパッタリング法等により行ってもよい。第2半導体膜606bの膜厚は200nm以上1000nm以下となるように形成することが好ましい。

【0279】

第3半導体膜606cは、n型半導体膜であり、n型を付与する不純物元素を含むアモルファスシリコン膜により形成する。第3半導体膜606cの形成には、15族の不純物元素(例えばリン(P))を含む半導体材料ガスを用いて、プラズマCVD法により形成する。半導体材料ガスとしてはシラン(SiH4)を用いればよい。または、Si2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4等を用いてもよい。また、不純物元素を含まないアモルファスシリコン膜を形成した後に、拡散法やイオン注入法を用いて該アモルファスシリコン膜に不純物元素を導入してもよい。イオン注入法等により不純物元素を導入した後に加熱等を行うことで、不純物元素を拡散させるとよい。この場合にアモルファスシリコン膜を形成する方法としては、LPCVD法、気相成長法、又はスパッタリング法等を用いればよい。第3半導体膜606cの膜厚は20nm以上200nm以下となるよう形成することが好ましい。

【0280】

また、第1半導体膜606a、第2半導体膜606b、及び第3半導体膜606cは、アモルファス半導体ではなく、多結晶半導体を用いて形成してもよいし、微結晶(セミアモルファス半導体(Semi Amorphous Semiconductor:SAS))半導体を用いて形成してもよい。

【0281】

微結晶半導体は、ギブスの自由エネルギーを考慮すれば非晶質と単結晶の中間的な準安定状態に属するものである。すなわち、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する。柱状または針状結晶が基板表面に対して法線方向に成長している。微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す520cm−1よりも低波数側に、シフトしている。即ち、単結晶シリコンを示す520cm−1とアモルファスシリコンを示す480cm−1の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手(ダングリングボンド)を終端するため水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性が増し良好な微結晶半導体膜が得られる。

【0282】

この微結晶半導体膜は、周波数が数十MHz〜数百MHzの高周波プラズマCVD法、または周波数が1GHz以上のマイクロ波プラズマCVD装置により形成することができる。代表的には、SiH4、Si2H6、SiH2Cl2、SiHCl3、SiCl4、SiF4などの珪素を含む化合物を水素で希釈して形成することができる。また、珪素を含む化合物(例えば水素化珪素)及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの珪素を含む化合物(例えば水素化珪素)に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。さらには、シリコンを含む気体中に、CH4、C2H6等の炭化物気体、GeH4、GeF4等のゲルマニウム化気体、F2等を混入させてもよい。

【0283】

また、光電効果で発生した正孔の移動度は電子の移動度に比べて小さいため、pin型のフォトダイオードはp型の半導体膜側を受光面とする方がよい特性を示す。ここでは、pin型のフォトダイオードが形成されている基板601の面からフォトダイオード602が受ける光を電気信号に変換する例を示す。また、受光面とした半導体膜側とは逆の導電型を有する半導体膜側からの光は外乱光となるため、電極層は遮光性を有する導電膜を用いるとよい。また、n型の半導体膜側を受光面として用いることもできる。

【0284】

絶縁膜632、層間絶縁膜633、層間絶縁膜634としては、絶縁性材料を用いて、その材料に応じて、スパッタリング法、プラズマCVD法、SOG法、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法等)、印刷法(スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーター、カーテンコーター、ナイフコーター等を用いて形成することができる。

【0285】

本実施の形態では、絶縁膜631として酸化アルミニウム膜を用いる。絶縁膜631はスパッタリング法やプラズマCVD法によって形成することができる。

【0286】

酸化物半導体膜上に絶縁膜631として設けられた酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を透過させない遮断効果(ブロック効果)が高い。

【0287】

従って、酸化アルミニウム膜は、作製工程中及び作製後において、変動要因となる水素、水分などの不純物の酸化物半導体膜への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体膜からの放出を防止する保護膜として機能する。

【0288】

絶縁膜632としては、無機絶縁材料としては、酸化シリコン層、酸化窒化シリコン層、酸化アルミニウム層、又は酸化窒化アルミニウム層などの酸化物絶縁膜、窒化シリコン層、窒化酸化シリコン層、窒化アルミニウム層、又は窒化酸化アルミニウム層などの窒化物絶縁膜の単層、又は積層を用いることができる。

【0289】

層間絶縁膜633、634としては、表面凹凸を低減するため平坦化絶縁膜として機能する絶縁膜が好ましい。層間絶縁膜633、634としては、例えばポリイミド、アクリル樹脂、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂等の、耐熱性を有する有機絶縁材料を用いることができる。また上記有機絶縁材料の他に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等の単層、又は積層を用いることができる。

【0290】

フォトダイオード602に入射する光を検出することによって、被検出物の情報を読み取ることができる。なお、被検出物の情報を読み取る際にバックライトなどの光源を用いることができる。

【0291】

以上のように、半導体層として異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層を用いることによって、トランジスタの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタに付与することが可能となる。よって、該トランジスタを用いることで、高機能、高信頼性、又は低消費電力など、種々の目的に応じた半導体装置を提供することができる。

【0292】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0293】

(実施の形態6)

実施の形態1乃至3のいずれかで一例を示したトランジスタは、複数のトランジスタを積層する集積回路を有する半導体装置に好適に用いることができる。本実施の形態では、半導体装置の一例として、記憶媒体(メモリ素子)の例を示す。

【0294】

実施の形態では、単結晶半導体基板に作製された第1のトランジスタであるトランジスタ140と絶縁膜を介してトランジスタ140の上方に半導体膜を用いて作製された第2のトランジスタであるトランジスタ162を含む半導体装置を作製する。実施の形態1乃至3のいずれかで一例を示したトランジスタは、トランジスタ162に好適に用いることができる。本実施の形態では、トランジスタ162として実施の形態1で示したトランジスタ440aと同様な構造を有するトランジスタを用いる例を示す。

【0295】

積層するトランジスタ140、トランジスタ162の半導体材料、及び構造は、同一でもよいし異なっていてもよい。本実施の形態は、記憶媒体(メモリ素子)の回路に好適な材料及び構造のトランジスタをそれぞれ用いる例である。

【0296】

図10は、半導体装置の構成の一例である。図10(A)には、半導体装置の断面を、図10(B)には、半導体装置の平面を、それぞれ示す。ここで、図10(A)は、図10(B)のC1−C2およびD1−D2における断面に相当する。また、図10(C)には、上記半導体装置をメモリ素子として用いる場合の回路図の一例を示す。図10(A)および図10(B)に示される半導体装置は、下部に第1の半導体材料を用いたトランジスタ140を有し、上部に第2の半導体材料を用いたトランジスタ162を有する。本実施の形態では、第1の半導体材料を酸化物半導体以外の半導体材料とし、第2の半導体材料を酸化物半導体とする。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いるのが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

【0297】

図10における半導体装置を図10(A)乃至(C)を用いて説明する。

【0298】

トランジスタ140は、半導体材料(例えば、シリコンなど)を含む基板185に設けられたチャネル形成領域116と、チャネル形成領域116を挟むように設けられた不純物領域120と、不純物領域120に接する金属化合物領域124と、チャネル形成領域116上に設けられたゲート絶縁膜108と、ゲート絶縁膜108上に設けられたゲート電極110とを有する。

【0299】

半導体材料を含む基板185は、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができる。なお、一般に「SOI基板」は、絶縁表面上にシリコン半導体膜が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体膜が設けられた構成の基板も含む。つまり、「SOI基板」が有する半導体膜は、シリコン半導体膜に限定されない。また、SOI基板には、ガラス基板などの絶縁基板上に絶縁膜を介して半導体膜が設けられた構成のものが含まれるものとする。

【0300】

SOI基板の作製方法としては、鏡面研磨ウェハーに酸素イオンを注入した後、高温加熱することにより、表面から一定の深さに酸化層を形成させるとともに、表面層に生じた欠陥を消滅させて作る方法、水素イオン照射により形成された微小ボイドの熱処理による成長を利用して半導体基板を劈開する方法や、絶縁表面上に結晶成長により単結晶半導体膜を形成する方法等を用いることができる。

【0301】

例えば、単結晶半導体基板の一つの面からイオンを添加して、単結晶半導体基板の一つの面から一定の深さに脆弱化層を形成し、単結晶半導体基板の一つの面上、又は素子基板上のどちらか一方に絶縁膜を形成する。単結晶半導体基板と素子基板を、絶縁膜を挟んで重ね合わせた状態で、脆弱化層に亀裂を生じさせ、単結晶半導体基板を脆弱化層で分離する熱処理を行い、単結晶半導体基板より半導体膜として単結晶半導体膜を素子基板上に形成する。上記方法を用いて作製されたSOI基板も好適に用いることができる。

【0302】

基板185上にはトランジスタ140を囲むように素子分離絶縁層106が設けられている。なお、高集積化を実現するためには、図10に示すようにトランジスタ140がサイドウォールとなる側壁絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ140の特性を重視する場合には、ゲート電極110の側面にサイドウォールとなる側壁絶縁層を設け、不純物濃度が異なる領域を含む不純物領域120を設けてもよい。

【0303】

単結晶半導体基板を用いたトランジスタ140は、高速動作が可能である。このため、当該トランジスタを読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。トランジスタ140を覆うように絶縁膜を2層形成する。トランジスタ162および容量素子164の形成前の処理として、該絶縁膜2層にCMP処理を施して、平坦化した絶縁膜128、絶縁膜130を形成し、同時にゲート電極110の上面を露出させる。

【0304】

絶縁膜128、絶縁膜130は、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜を用いることができる。絶縁膜128、絶縁膜130は、プラズマCVD法又はスパッタリング法等を用いて形成することができる。

【0305】

また、ポリイミド、アクリル樹脂、ベンゾシクロブテン系樹脂、等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low−k材料)等を用いることができる。有機材料を用いる場合、スピンコート法、印刷法などの湿式法によって絶縁膜128、絶縁膜130を形成してもよい。

【0306】

なお、絶縁膜130において、半導体膜と接する膜は酸化シリコン膜を用いる。

【0307】

本実施の形態では、絶縁膜128としてスパッタリング法により膜厚50nmの酸化窒化シリコン膜を形成し、絶縁膜130としてスパッタリング法により膜厚550nmの酸化シリコン膜を形成する。

【0308】

CMP処理により十分に平坦化した絶縁膜130上にエネルギーギャップの異なる酸化半導体膜を積層する。本実施の形態では、酸化物半導体膜の積層としてスパッタリング法により、絶縁膜130上にIn−Sn−Zn系酸化物及びIn−Ga−Zn系酸化物層を順に積層する。

【0309】

次に酸化物半導体膜の積層を選択的にエッチングして島状の酸化物半導体積層144を形成する。酸化物半導体積層144上にソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bを形成する。

【0310】

酸化物半導体膜上にゲート絶縁膜146、ゲート電極層148を形成する。ゲート電極層148は、導電層を形成した後に、当該導電層を選択的にエッチングすることによって形成することができる。

【0311】

ゲート絶縁膜146として、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ハフニウム膜、又は酸化ガリウム膜、酸化アルミニウム膜を形成することができる。

【0312】

ゲート電極層148、ソース電極またはドレイン電極142a、ソース電極またはドレイン電極142bに用いることのできる導電層は、スパッタリング法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて形成することができる。また、導電層の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。Mn、Mg、Zr、Be、Nd、Scのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

【0313】

導電層は、単層構造であってもよいし、2層以上の積層構造としてもよい。例えば、チタン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された2層構造、窒化チタン膜上にチタン膜が積層された2層構造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。なお、導電層を、チタン膜や窒化チタン膜の単層構造とする場合には、テーパー形状を有するソース電極またはドレイン電極142a、およびソース電極またはドレイン電極142bへの加工が容易であるというメリットがある。

【0314】

次に、酸化物半導体積層144、ゲート絶縁膜146、ゲート電極層148上に、絶縁膜150を形成する。本実施の形態では、絶縁膜150として酸化アルミニウム膜を形成する。

【0315】

酸化物半導体積層144上に絶縁膜150として設けられた酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を通過させない遮断効果(ブロック効果)が高い。

【0316】

従って、酸化アルミニウム膜は、作製工程中及び作製後において、変動要因となる水素、水分などの不純物の酸化物半導体積層144への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体積層144からの放出を防止する保護膜として機能する。

【0317】

また、絶縁膜150上に積層して別途絶縁膜を形成してもよい。

【0318】

絶縁膜としては、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜、酸化ハフニウム膜、又は酸化ガリウム膜を用いることができる。

【0319】

絶縁膜150上において、ソース電極またはドレイン電極142aと重畳する領域に電極層153を形成する。

【0320】

次にトランジスタ162、及び電極層153上に、絶縁膜152を形成する。絶縁膜152は、スパッタリング法やCVD法などを用いて形成することができる。また、酸化シリコン、酸化窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。また、ポリイミド、アクリル、ベンゾシクロブテン系樹脂、等の有機材料を用いることができ、上記有機材料には塗布法、印刷法、インクジェット法などの湿式法を用いることができる。

【0321】

次に、ゲート絶縁膜146、絶縁膜150、及び絶縁膜152に、ソース電極またはドレイン電極142bにまで達する開口を形成する。当該開口の形成は、マスクなどを用いた選択的なエッチングにより行われる。

【0322】

その後、上記開口にソース電極またはドレイン電極142bに接する配線156を形成する。なお、図10(A)にはソース電極またはドレイン電極142bと配線156との接続箇所は図示していない。

【0323】

配線156は、スパッタリング法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて導電層を形成した後、当該導電層をエッチング加工することによって形成される。また、導電層の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。Mn、Mg、Zr、Be、Nd、Scのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。詳細は、ソース電極またはドレイン電極142aなどと同様である。

【0324】

以上の工程でトランジスタ162及び容量素子164が形成される。本実施の形態では、トランジスタ162は、エネルギーギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層144を有するトランジスタである。半導体層として異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層144を用いることによって、トランジスタ162の電気特性をより精度よく制御することができ、所望の電気特性をトランジスタ162に付与することが可能となる。また、本実施の形態においては、酸化物半導体積層144を高純度化し、酸素欠損を補填する酸素を過剰に含む酸化物半導体積層とする。よって、トランジスタ162は、オフ電流を低減され、電気特性変動が抑制されており、電気的に安定である。容量素子164は、ソース電極またはドレイン電極142a、酸化物半導体積層144、ゲート絶縁膜146、および電極層153、で構成される。

【0325】

なお、図10の容量素子164では、ゲート絶縁膜146と絶縁膜150を積層させることにより、ソース電極またはドレイン電極142aと、電極層153との間の絶縁性を十分に確保することができる。もちろん、十分な容量を確保するために、絶縁膜150を有しない構成の容量素子164を採用してもよい。また、絶縁膜を有する構成の容量素子164を採用してもよい。さらに、容量が不要の場合は、容量素子164を設けない構成とすることも可能である。

【0326】

図10(C)には、上記半導体装置をメモリ素子として用いる場合の回路図の一例を示す。図10(C)において、トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、トランジスタ140のゲート電極と、は電気的に接続されている。また、第1の配線(1st Line:ソース線とも呼ぶ)とトランジスタ140のソース電極とは、電気的に接続され、第2の配線(2nd Line:ビット線とも呼ぶ)とトランジスタ140のドレイン電極とは、電気的に接続されている。また、第3の配線(3rd Line:第1の信号線とも呼ぶ)とトランジスタ162のソース電極またはドレイン電極の他方とは、電気的に接続され、第4の配線(4th Line:第2の信号線とも呼ぶ)と、トランジスタ162のゲート電極とは、電気的に接続されている。そして、第5の配線(5th Line:ワード線とも呼ぶ)と、容量素子164の電極の他方は電気的に接続されている。

【0327】

酸化物半導体を用いたトランジスタ162は、オフ電流が極めて小さいという特徴を有しているため、トランジスタ162をオフ状態とすることで、トランジスタ162のソース電極またはドレイン電極の一方と、容量素子164の電極の一方と、トランジスタ140のゲート電極とが電気的に接続されたノード(以下、ノードFG)の電位を極めて長時間にわたって保持することが可能である。そして、容量素子164を有することにより、ノードFGに与えられた電荷の保持が容易になり、また、保持された情報の読み出しが容易になる。

【0328】

半導体装置に情報を記憶させる場合(書き込み)は、まず、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位が、ノードFGに供給され、ノードFGに所定量の電荷が蓄積される。ここでは、異なる二つの電位レベルを与える電荷(以下、ロー(Low)レベル電荷、ハイ(High)レベル電荷という)のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、ノードFGが浮遊状態となるため、ノードFGには所定の電荷が保持されたままの状態となる。以上のように、ノードFGに所定量の電荷を蓄積及び保持させることで、メモリセルに情報を記憶させることができる。

【0329】

トランジスタ162のオフ電流は極めて小さく制御されているため、ノードFGに供給された電荷は長時間にわたって保持される。したがって、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となり、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

【0330】

記憶された情報を読み出す場合(読み出し)は、第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、ノードFGに保持された電荷量に応じて、トランジスタ140は異なる状態をとる。一般に、トランジスタ140をnチャネル型とすると、ノードFGにHighレベル電荷が保持されている場合のトランジスタ140の見かけのしきい値Vth_Hは、ノードFGにLowレベル電荷が保持されている場合のトランジスタ140の見かけのしきい値Vth_Lより低くなるためである。ここで、見かけのしきい値とは、トランジスタ140を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位をVth_HとVth_Lの中間の電位V0とすることにより、ノードFGに保持された電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位がV0(>Vth_H)となれば、トランジスタ140は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位がV0(<Vth_L)となっても、トランジスタ140は「オフ状態」のままである。このため、第5の配線の電位を制御して、トランジスタ140のオン状態またはオフ状態を読み出す(第2の配線の電位を読み出す)ことで、記憶された情報を読み出すことができる。

【0331】

また、記憶させた情報を書き換える場合においては、上記の書き込みによって所定量の電荷を保持したノードFGに、新たな電位を供給することで、ノードFGに新たな情報に係る電荷を保持させる。具体的には、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位(新たな情報に係る電位)が、ノードFGに供給され、ノードFGに所定量の電荷が蓄積される。その後、第4の配線の電位をトランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、ノードFGには、新たな情報に係る電荷が保持された状態となる。すなわち、ノードFGに第1の書き込みによって所定量の電荷が保持された状態で、第1の書き込みと同様の動作(第2の書き込み)を行うことで、記憶させた情報を上書きすることが可能である。

【0332】

本実施の形態で示すトランジスタ162は、エネルギーギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を有し、オフ電流が十分に低くなるよう制御されたトランジスタである。このようなトランジスタを用いることで、極めて長期にわたり記憶内容を保持することが可能な半導体装置が得られる。

【0333】

以上のように、異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層を用いることによって、トランジスタの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタに付与することが可能となる。よって、高機能、高信頼性、又は低消費電力など、種々の目的に応じた半導体装置を提供することができる。

【0334】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0335】

(実施の形態7)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態で説明した半導体装置を具備する電子機器の例について説明する。上記実施の形態で説明した半導体装置を具備することによって、高機能、高信頼性、又は低消費電力など、種々の目的に応じた品質を付与された電子機器を提供することができる。

【0336】

図11(A)は、ノート型のパーソナルコンピュータであり、本体3001、筐体3002、表示部3003、キーボード3004などによって構成されている。実施の形態1乃至6のいずれかで示した半導体装置を表示部3003に適用することにより、高性能及び高信頼性なノート型のパーソナルコンピュータとすることができる。

【0337】

図11(B)は、携帯情報端末(PDA)であり、本体3021には表示部3023と、外部インターフェイス3025と、操作ボタン3024等が設けられている。また操作用の付属品としてスタイラス3022がある。実施の形態1乃至6のいずれかで示した半導体装置を表示部3023に適用することにより、より高性能及び高信頼性な携帯情報端末(PDA)とすることができる。

【0338】

図11(C)は、電子書籍の一例を示している。例えば、電子書籍は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

【0339】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705および表示部2707は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすることで、例えば右側の表示部(図11(C)では表示部2705)に文章を表示し、左側の表示部(図11(C)では表示部2707)に画像を表示することができる。実施の形態1乃至6のいずれかで示した半導体装置を表示部2705、表示部2707に適用することにより、高性能及び高信頼性な電子書籍とすることができる。表示部2705として半透過型、又は反射型の液晶表示装置を用いる場合、比較的明るい状況下での使用も予想されるため、太陽電池を設け、太陽電池による発電、及びバッテリーでの充電を行えるようにしてもよい。なおバッテリーとしては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

【0340】

また、図11(C)では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍は、電子辞書としての機能を持たせた構成としてもよい。

【0341】

また、電子書籍は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0342】

図11(D)は、携帯電話であり、筐体2800及び筐体2801の二つの筐体で構成されている。筐体2801には、表示パネル2802、スピーカー2803、マイクロフォン2804、ポインティングデバイス2806、カメラ用レンズ2807、外部接続端子2808などを備えている。また、筐体2800には、携帯電話の充電を行う太陽電池セル2810、外部メモリスロット2811などを備えている。また、アンテナは筐体2801内部に内蔵されている。実施の形態1乃至6のいずれかで示した半導体装置を表示パネル2802に適用することにより、高性能及び高信頼性な携帯電話とすることができる。

【0343】

また、表示パネル2802はタッチパネルを備えており、図11(D)には映像表示されている複数の操作キー2805を点線で示している。なお、太陽電池セル2810で出力される電圧を各回路に必要な電圧に昇圧するための昇圧回路も実装している。

【0344】

表示パネル2802は、使用形態に応じて表示の方向が適宜変化する。また、表示パネル2802と同一面上にカメラ用レンズ2807を備えているため、テレビ電話が可能である。スピーカー2803及びマイクロフォン2804は音声通話に限らず、テレビ電話、録音、再生などが可能である。さらに、筐体2800と筐体2801は、スライドし、図11(D)のように展開している状態から重なり合った状態とすることができ、携帯に適した小型化が可能である。

【0345】

外部接続端子2808はACアダプタ及びUSBケーブルなどの各種ケーブルと接続可能であり、充電及びパーソナルコンピュータなどとのデータ通信が可能である。また、外部メモリスロット2811に記録媒体を挿入し、より大量のデータ保存及び移動に対応できる。

【0346】

また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってもよい。

【0347】

図11(E)は、デジタルビデオカメラであり、本体3051、表示部(A)3057、接眼部3053、操作スイッチ3054、表示部(B)3055、バッテリー3056などによって構成されている。実施の形態1乃至6のいずれかで示した半導体装置を表示部(A)3057、表示部(B)3055に適用することにより、高性能及び高信頼性なデジタルビデオカメラとすることができる。

【0348】

図11(F)は、テレビジョン装置の一例を示している。テレビジョン装置は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することが可能である。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。実施の形態1乃至6のいずれかで示した半導体装置を表示部9603に適用することにより、高性能及び高信頼性なテレビジョン装置とすることができる。

【0349】

テレビジョン装置の操作は、筐体9601が備える操作スイッチや、別体のリモコン操作機により行うことができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

【0350】

なお、テレビジョン装置は、受信機やモデムなどを備えた構成とする。受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

【0351】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【実施例1】

【0352】

本実施例では、第1の酸化物半導体層上に、第1の酸化物半導体層のエネルギーギャップよりも小さい第2の酸化物半導体層を形成し、さらに第2の酸化物半導体層上に第3の酸化物半導体層を形成したサンプルを作製し、そのサンプルのイオン化ポテンシャルの測定を行い、その結果に基づきエネルギーバンド図を計算した。本明細書において、イオン化ポテンシャルの値は、バンドギャップと電子親和力を加算した値であり、バンドギャップの値は、材料の単膜のエリプソで測定して得られる値を用いる。

【0353】

サンプルは、単結晶シリコン基板上に膜厚5nmのIGZO膜、膜厚5nmのIn−Sn−Zn系酸化物膜、膜厚5nmのIGZO膜を積層成膜した。それぞれの成膜条件は、スパッタリング法を用いて基板温度300℃、酸素雰囲気(酸素100%)下で成膜を行った。ターゲットは、In:Ga:Zn=1:1:1[原子数比]の酸化物ターゲットを用い、IGZO膜を成膜する。また、In−Sn−Zn系酸化物膜は、In:Sn:Zn=2:1:3[原子数比]の酸化物ターゲットを用いる。

【0354】

また、基板を石英基板として、同じ成膜条件で積層成膜して得られたサンプルの断面を撮影したTEM写真が図14(A)である。なお、模式図を図14(B)に示す。図14(B)において、酸化物半導体層の界面を点線で図示しているが、模式的に示したものである。材料や成膜条件や加熱処理によっては、各酸化物半導体層との界面が不明確になる場合もある。図14(A)を撮影したサンプルは、石英基板1000上に膜厚5nmの第1のIGZO膜1001、膜厚5nmのIn−Sn−Zn系酸化物膜1002、膜厚5nmの第2のIGZO膜1003を積層成膜したものであり、In−Sn−Zn系酸化物膜とIGZO膜の界面が確認できる。また、図14(A)では、第2のIGZO膜1003と、In−Sn−Zn系酸化物膜1002は、結晶を含んでおり、c軸配向を有した結晶性酸化物半導体(CAAC)であることが確認できる。また、図14(A)において第1のIGZO膜1001は非晶質構造である。なお、図14(A)では、3層のうち、2層が結晶構造を有している酸化物半導体膜となっているが特に限定されず、第2のIGZO膜1003のみが結晶構造を有してもよいし、3層全てが結晶構造を有してもよいし、3層全て非晶質構造であってもよい。

【0355】

サンプルの表面からスパッタリングしながら紫外線光電子分光分析(UPS:Ultraviolet Photoelectron Spctroscopy)によるイオン化ポテンシャルを測定した結果を図12に示す。

【0356】

図12において、横軸はサンプル表面からのスパッタリング時間を表し、縦軸はイオン化ポテンシャルを表している。なお、IGZO膜とIn−Sn−Zn系酸化物膜のスパッタレートは等しいと仮定して試料の境界を表示している。この図12から、IGZO膜に挟まれたIn−Sn−Zn系酸化物膜でイオン化ポテンシャルが低下することがわかる。なお、イオン化ポテンシャルは真空準位から価電子帯までのエネルギー差を表す。

【0357】

イオン化ポテンシャルの値からエリプソで測定したバンドギャップを引くことで伝導帯のエネルギーを算出し、この積層膜のバンド構造を作成した。ただし、IGZO膜とIn−Sn−Zn系酸化物膜のバンドギャップはそれぞれ3.2eV、2.8eVとした。その結果が図13になる。図13には、図4(C)に示したエネルギーバンド図のように埋め込みチャネルが形成されていることがわかる。

【0358】

本実施例では、第1の酸化物半導体層及び第3の酸化物半導体層としてIGZO膜を用い、第1の酸化物半導体層及び第3の酸化物半導体層よりも大きいイオン化ポテンシャルを有し、且つ、小さいエネルギーギャップを有する第2の酸化物半導体層としてIn−Sn−Zn系酸化物膜を用いた積層は、図13または図4(C)に示すエネルギーバンド図で表すことができることを確認した。第1の酸化物半導体層、第2の酸化物半導体層、及び第3の酸化物半導体層の材料の組み合わせは、特に限定されず、図13または図4(C)に示すエネルギーバンド図となるように、実施者が用いる材料のエネルギーギャップを考慮して適宜材料を選択し、組み合わせればよく、例えば、第1の酸化物半導体層及び第3の酸化物半導体層としてIGZO膜を用い、第2の酸化物半導体層としてインジウム亜鉛酸化物膜を用いた積層を用いてもよい。

【符号の説明】

【0359】

101 酸化物半導体層

102 酸化物半導体層

103 酸化物半導体層

106 素子分離絶縁層

108 ゲート絶縁膜

110 ゲート電極

111 酸素過剰領域

112 酸素過剰領域

116 チャネル形成領域

120 不純物領域

121a 低抵抗領域

121b 低抵抗領域

121c チャネル形成領域

121d 低抵抗領域

121e 低抵抗領域

122a 低抵抗領域

122b 低抵抗領域

122c チャネル形成領域

122d 低抵抗領域

122e 低抵抗領域

123a 低抵抗領域

123b 低抵抗領域

123c チャネル形成領域

123d 低抵抗領域

123e 低抵抗領域

124 金属化合物領域

128 絶縁膜

130 絶縁膜

140 トランジスタ

142a ドレイン電極

142b ドレイン電極

144 酸化物半導体積層

146 ゲート絶縁膜

148 ゲート電極層

150 絶縁膜

152 絶縁膜

153 電極層

156 配線

162 トランジスタ

164 容量素子

185 基板

191 酸化物半導体膜

192 酸化物半導体膜

400 基板

401 ゲート電極層

402 ゲート絶縁膜

403 酸化物半導体積層

404a ソース電極層

404b ドレイン電極層

405a ソース電極層

405b ドレイン電極層

407 絶縁膜

415a ソース電極層

415b ドレイン電極層

416 絶縁膜

420 トランジスタ

421 ドーパント

423 トランジスタ

425 トランジスタ

430 トランジスタ

431 酸素

436 酸化物絶縁膜

440a トランジスタ

440b トランジスタ

440c トランジスタ

440d トランジスタ

465a 配線層

465b 配線層

480a トランジスタ

480b トランジスタ

493 積層

601 基板

602 フォトダイオード

606a 半導体膜

606b 半導体膜

606c 半導体膜

608 接着層

613 基板

631 絶縁膜

632 絶縁膜

633 層間絶縁膜

634 層間絶縁膜

640 トランジスタ

641 電極層

642 電極層

643 導電層

645 導電層

656 トランジスタ

658 フォトダイオードリセット信号線

659 ゲート信号線

671 フォトセンサ出力信号線

672 フォトセンサ基準信号線

1000 石英基板

1001 IGZO膜

1002 In−Sn−Zn系酸化物膜

1003 IGZO膜

2701 筐体

2703 筐体

2705 表示部

2707 表示部

2711 軸部

2721 電源

2723 操作キー

2725 スピーカ

2800 筐体

2801 筐体

2802 表示パネル

2803 スピーカー

2804 マイクロフォン

2805 操作キー

2806 ポインティングデバイス

2807 カメラ用レンズ

2808 外部接続端子

2810 太陽電池セル

2811 外部メモリスロット

3001 本体

3002 筐体

3003 表示部

3004 キーボード

3021 本体

3022 スタイラス

3023 表示部

3024 操作ボタン

3025 外部インターフェイス

3051 本体

3053 接眼部

3054 操作スイッチ

3056 バッテリー

4001 基板

4002 画素部

4003 信号線駆動回路

4004 走査線駆動回路

4005 シール材

4006 基板

4008 液晶層

4010 トランジスタ

4011 トランジスタ

4013 液晶素子

4015 接続端子電極

4016 端子電極

4018 FPC

4019 異方性導電膜

4020 絶縁膜

4021 絶縁膜

4023 絶縁膜

4030 電極層

4031 電極層

4032 絶縁膜

4033 絶縁膜

4510 隔壁

4511 電界発光層

4513 発光素子

4514 充填材

9601 筐体

9603 表示部

9605 スタンド

【技術分野】

【0001】

半導体装置及び半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

半導体薄膜を用いてトランジスタ(薄膜トランジスタ(TFT)ともいう)を構成する技術が注目されている。該トランジスタは集積回路(IC)や画像表示装置(表示装置)のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

【0004】

酸化物半導体を用いたトランジスタとしては、より高機能な半導体装置への応用のために、より高い電気特性が求められている。酸化物半導体を用いたトランジスタにおいて、高い電気特性を目的として、アルミニウム反応法を用いて低抵抗なソース領域及びドレイン領域を形成する技術などが報告がされている(例えば、非特許文献1参照。)。

【0005】

例えば、トランジスタの活性層として、インジウム(In)、ガリウム(Ga)、及び亜鉛(Zn)を含む非晶質酸化物を用いたトランジスタが開示されている(特許文献1参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006−165528号公報

【非特許文献】

【0007】

【非特許文献1】N.Morosawa, Yoshihiro Ohshima,Mitsuo Morooka, Toshiaki Arai, Tatsuya Sasaoka, 「A Novel Self−Aligned Top−Gate Oxide TFT for AM−OLED Displays」、SID 11 DIGEST pp479−482

【発明の概要】

【発明が解決しようとする課題】

【0008】

トランジスタのオン特性(例えば、オン電流や電界効果移動度)が向上すると、半導体装置において入力信号に対する高速応答、高速駆動が可能になり、より高性能な半導体装置が実現できる。一方、半導体装置の低消費電力化には、トランジスタのオフ電流が十分低いことが求められる。このように、トランジスタに求められる電気特性は用途や目的に合わせて様々であり、該電気特性をより精度よく制御することは有益である。

【0009】

酸化物半導体をチャネル形成領域に用いたトランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供することを課題の一つとする。

【0010】

トランジスタは、ゲート電圧が0Vにできるだけ近い正のしきい値電圧でチャネルが形成されることが望ましい。トランジスタのしきい値電圧がマイナスであると、ゲート電圧が0Vでもソース電極とドレイン電極の間に電流が流れる、所謂ノーマリーオンとなりやすい。LSIやCPUやメモリにおいては、回路を構成するトランジスタの電気特性が重要であり、この電気特性が半導体装置の消費電力を左右する。特に、トランジスタの電気特性のうち、しきい値電圧(Vth)が重要である。電界効果移動度が高くとも、しきい値電圧がマイナスであると、回路として制御することが困難である。負の電圧状態でもチャネルが形成されてドレイン電流が流れるトランジスタは、半導体装置の集積回路に用いるトランジスタとしては不向きである。

【0011】

また、材料や作製条件によっては、作製されたトランジスタがノーマリーオフとならない場合であっても、ノーマリーオフの特性に近づけることが重要であり、しきい値電圧がマイナスである、所謂ノーマリーオンであっても、トランジスタのしきい値をゼロに近づける構成およびその作製方法を提供することも課題の一つとする。

【0012】

また、より高性能な半導体装置を実現するため、トランジスタのオン特性(例えば、オン電流や電界効果移動度)を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供することも課題の一つとする。

【0013】

上記のように、用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供することを課題の一とする。

【課題を解決するための手段】

【0014】

半導体層、ソース電極層及びドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。

【0015】

酸化物半導体積層を第1の酸化物半導体層及び第2の酸化物半導体層の積層構造とする場合、第1の酸化物半導体層及び第2の酸化物半導体層は、それぞれの有するエネルギーギャップが異なればよく、その積層順は限定されず、ゲート絶縁膜と接する方をエネルギーギャップが大きい層としてもよいし、エネルギーギャップが小さい層としてもよい。

【0016】

具体的には、酸化物半導体積層において、一方の酸化物半導体層のエネルギーギャップを3eV以上とし、他方の酸化物半導体層のエネルギーギャップを3eV未満とする。なお、本明細書において、「エネルギーギャップ」という用語は、「バンドギャップ」や、「禁制帯幅」と同じ意味で用いている。

【0017】

酸化物半導体積層を3層以上の積層構造とする場合、すべての酸化物半導体層同士が異なるエネルギーギャップを有する構造であってもよいし、ほぼ同じエネルギーギャップを有する酸化物半導体層を複数酸化物半導体積層中に用いてもよい。

【0018】

例えば、酸化物半導体積層を第1の酸化物半導体層、第2の酸化物半導体層、及び第3の酸化物半導体層の積層構造において、第2の酸化物半導体層のエネルギーギャップを第1の酸化物半導体層及び第3の酸化物半導体層のエネルギーギャップより小さくする。または、第2の酸化物半導体層の電子親和力を、第1の酸化物半導体層及び第3の酸化物半導体層の電子親和力よりも大きくする。この場合、第1の酸化物半導体層及び第3の酸化物半導体層のエネルギーギャップと電子親和力とは同等とすることができる。エネルギーギャップの小さい第2の酸化物半導体層を、エネルギーギャップの大きい第1の酸化物半導体層及び第3の酸化物半導体層により挟む構造とすることによって、よりトランジスタのオフ電流(リーク電流)を低減する効果が得られる。ここで、電子親和力とは真空準位と酸化物半導体の伝導帯とのエネルギー差を表す。

【0019】

酸化物半導体層を用いたトランジスタにおいて、該酸化物半導体層のエネルギーギャップは、トランジスタの電気特性に影響を与える。例えば、酸化物半導体層を用いたトランジスタにおいて、酸化物半導体層のエネルギーギャップが小さいと、オン特性(例えば、オン電流や電界効果移動度)が向上し、一方、酸化物半導体層のエネルギーギャップが大きいと、オフ電流が低減できる。

【0020】

単層の酸化物半導体層では該酸化物半導体層のエネルギーギャップの大きさで、トランジスタの電気特性はほぼ決定してしまうため、所望の電気的特性をトランジスタに付与することは難しい。

【0021】

異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層を用いることによって、トランジスタの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタに付与することが可能となる。

【0022】

従って、高機能、高信頼性、又は低消費電力など、種々の目的に応じた半導体装置を提供することができる。

【0023】

本明細書で開示する発明の構成の一形態は、エネルギーギャップが異なる第1の酸化物半導体層及び第2の酸化物半導体層を含む酸化物半導体積層と、酸化物半導体積層上にソース電極層及びドレイン電極層と、ソース電極層及びドレイン電極層上にゲート絶縁膜と、ゲート絶縁膜上に酸化物半導体積層と重なるゲート電極層とを有する半導体装置である。

【0024】

本明細書で開示する発明の構成の一形態は、第1の酸化物半導体層、第2の酸化物半導体層、及び第3の酸化物半導体層を順に含む酸化物半導体積層と、酸化物半導体積層上にソース電極層及びドレイン電極層と、ソース電極層及びドレイン電極層上にゲート絶縁膜と、ゲート絶縁膜上に酸化物半導体積層と重なるゲート電極層とを有し、第2の酸化物半導体層は、第1の酸化物半導体層及び第3の酸化物半導体層のエネルギーギャップより小さいエネルギーギャップを有する半導体装置である。

【0025】

上記構成において、酸化物半導体積層は島状であり、ソース電極層及びドレイン電極層は酸化物半導体積層の側面(端部)に接して形成することができる。この場合、酸化物半導体積層の側面(端部)には第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層の側面(端部)が露出しているので、第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層はソース電極層及びドレイン電極層と接する構成となる。

【0026】

本明細書で開示する発明の構成の一形態は、酸化物絶縁膜上にエネルギーギャップが異なる2層の酸化物半導体層を含む酸化物半導体積層を形成し、酸化物半導体積層上にソース電極層及びドレイン電極層を形成し、ソース電極層及びドレイン電極層を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極層を形成する半導体装置の作製方法である。

【0027】

本明細書で開示する発明の構成の一形態は、酸化物絶縁膜上にエネルギーギャップが異なる酸化物半導体膜を積層し、酸化物半導体膜の積層上にマスクを形成し、マスクを用いて酸化物半導体膜の積層をエッチング加工して酸化物半導体積層を形成し、酸化物半導体積層上にソース電極層及びドレイン電極層を形成し、ソース電極層及びドレイン電極層を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極層を形成する半導体装置の作製方法である。

【0028】

また、ゲート電極層をマスクとして酸化物半導体積層にドーパントを導入し、自己整合的にチャネル形成領域を挟んでチャネル形成領域より抵抗が低く、ドーパントを含む低抵抗領域を形成してもよい。ドーパントは、酸化物半導体積層の導電率を変化させる不純物である。ドーパントの導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。

【0029】

チャネル長方向にチャネル形成領域を挟んで低抵抗領域を含む酸化物半導体積層を有することにより、該トランジスタはオン特性(例えば、オン電流及び電界効果移動度)が高く、高速動作、高速応答が可能となる。

【0030】

また、酸化物半導体層(酸化物半導体膜)に水素若しくは水分を放出させる加熱処理(脱水化又は脱水素化処理)を行ってもよい。例えば上記構成において、マスクを形成する前に、積層された酸化物半導体膜中に含まれる水素若しくは水分を放出させる加熱処理を行うことが好ましい。

【0031】

また、脱水化又は脱水素化処理によって、酸化物半導体を構成する主成分材料である酸素が同時に脱離して減少してしまうおそれがある。酸化物半導体膜において、酸素が脱離した箇所では酸素欠損が存在し、該酸素欠損に起因してトランジスタの電気的特性変動を招くドナー準位が生じてしまう。

【0032】

よって、脱水化又は脱水素化処理を行った酸化物半導体層(酸化物半導体膜)に、酸素を供給することが好ましい。酸化物半導体層(酸化物半導体膜)へ酸素を供給することにより、膜中の酸素欠損を補填することができる。

【0033】

例えば、酸素の供給源となる酸素を多く(過剰に)含む酸化物絶縁膜を酸化物半導体層(酸化物半導体膜)と接して設けることによって、該酸化物絶縁膜から酸化物半導体層(酸化物半導体膜)へ酸素を供給することができる。上記構成において、脱水化又は脱水素化処理として加熱処理を行った酸化物半導体層(酸化物半導体膜)及び酸化物絶縁膜を少なくとも一部が接した状態で加熱処理を行うことによって酸化物半導体層(酸化物半導体膜)への酸素の供給を行ってもよい。

【0034】

また、脱水化又は脱水素化処理を行った酸化物半導体層(酸化物半導体膜)に、酸素(少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む)を導入して膜中に酸素を供給してもよい。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。

【0035】

さらに、好ましくはトランジスタに設けられる酸化物半導体層(酸化物半導体膜)は、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている膜とするとよい。この場合、酸素の含有量は、酸化物半導体の化学量論的組成比を超える程度とする。あるいは、酸素の含有量は、単結晶の場合の酸素の量を超える程度とする。酸化物半導体の格子間に酸素が存在する場合もある。

【0036】

水素若しくは水分を酸化物半導体から除去し、不純物が極力含まれないように高純度化し、酸素を供給して酸素欠損を補填することによりI型(真性)の酸化物半導体、又はI型(真性)に限りなく近い酸化物半導体とすることができる。そうすることにより、酸化物半導体のフェルミ準位(Ef)を真性フェルミ準位(Ei)と同じレベルにまですることができる。よって、該酸化物半導体膜をトランジスタに用いることで、酸素欠損に起因するトランジスタのしきい値電圧Vthのばらつき、しきい値電圧のシフトΔVthを低減することができる。

【0037】

本発明の一形態は、トランジスタ若しくはトランジスタを含んで構成される回路を有する半導体装置に関する。例えば、酸化物半導体でチャネル形成領域が形成される、トランジスタ若しくはトランジスタを含んで構成される回路を有する半導体装置に関する。例えば、LSIや、CPUや、電源回路に搭載されるパワーデバイスや、メモリ、サイリスタ、コンバータ、イメージセンサなどを含む半導体集積回路、液晶表示パネルに代表される電気光学装置や発光素子を有する発光表示装置を部品として搭載した電子機器に関する。

【発明の効果】

【0038】

異なるエネルギーギャップを有する複数の酸化物半導体層を用いた酸化物半導体積層を用いることによって、トランジスタの電気特性をより精度よく制御することができ、所望の電気特性をトランジスタに付与することが可能となる。

【0039】

従って、高機能、高信頼性、又は低消費電力など、種々の目的に応じた半導体装置を提供することができる。

【図面の簡単な説明】

【0040】

【図1】半導体装置の一形態を説明する図。

【図2】半導体装置及び半導体装置の作製方法の一形態を説明する図。

【図3】半導体装置の一形態を説明する図。

【図4】半導体装置の一形態を説明する図及びエネルギーバンド図。

【図5】半導体装置及び半導体装置の作製方法の一形態を説明する図。

【図6】半導体装置及び半導体装置の作製方法の一形態を説明する図。

【図7】半導体装置の一形態を説明する図。

【図8】半導体装置の一形態を説明する図。

【図9】半導体装置の一形態を説明する図。

【図10】半導体装置の一形態を説明する図。

【図11】電子機器を示す図。

【図12】イオン化ポテンシャルを示す図。

【図13】エネルギーバンド図を示す図。

【図14】実施例のサンプルのTEM写真図およびその模式図。

【発明を実施するための形態】

【0041】

以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。ただし、本明細書に開示する発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本明細書に開示する発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0042】

(実施の形態1)