半導体装置、表示装置及びに電子機器

【課題】電源線の電位を一行ずつ変化させながら、かつ大きな電流を供給するためには、大きな電流を制御できるスイッチを配置する必要がある。そのため、回路のトランジスタサイズを大きくしなければならないという問題がある。トランジスタサイズを大きくすると、トランジスタでの消費電力が大きくなってしまう。そこで、表示素子へ電流を供給する電源線の電位を一行ずつ変化させずに、信号書き込み動作時に表示素子へ電流が流れてしまうのを防ぐことが可能な表示装置を提供することを課題とする。

【解決手段】トランジスタに所定の電流を流してトランジスタのゲートソース間電圧を設定する際、トランジスタのソース端子に接続された負荷に電流がながれないようにするため、トランジスタのゲート端子の電位を調整する。そのため、トランジスタのゲート端子の接続された配線とトランジスタのドレイン端子の接続された配線とを異なる電位にする。

【解決手段】トランジスタに所定の電流を流してトランジスタのゲートソース間電圧を設定する際、トランジスタのソース端子に接続された負荷に電流がながれないようにするため、トランジスタのゲート端子の電位を調整する。そのため、トランジスタのゲート端子の接続された配線とトランジスタのドレイン端子の接続された配線とを異なる電位にする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は負荷に供給する電流をトランジスタで制御する機能を設けた半導体装置に係り、信号によって輝度が変化する電流駆動型表示素子で形成された画素や、その画素を駆動させる信号線駆動回路や走査線駆動回路を含む表示装置に関する。また、その駆動方法に関する。また、その表示装置を表示部に有する電子機器に関する。

【背景技術】

【0002】

液晶などの表示素子で形成した表示装置である液晶ディスプレイ(LCD)が広く普及している。しかし、近年、画素を発光ダイオード(LED)などの表示素子で形成した、いわゆる自発光型の表示装置、つまり、発光装置が注目を浴びている。このような自発光型の表示装置に用いられる表示素子としては、有機発光ダイオード(OLED(Organic Light Emitting Diode)、有機EL素子、エレクトロルミネッセンス(Electro Luminescence:EL)素子などとも言う)が注目を集めており、ELディスプレイなどに用いられるようになってきている。OLEDなどの表示素子は自発光型であるため、液晶ディスプレイに比べて画素の視認性が高く、バックライトが不要で応答速度が速い等の利点がある。なお、表示素子の輝度は、そこを流れる電流値によって制御されるものが多い。

【0003】

このような表示装置の階調を表現する駆動方式として、アナログ階調方式とデジタル階調方式がある。デジタル階調方式はデジタル制御で表示素子をオンオフさせ、階調を表現している。デジタル階調方式の場合、画素毎の輝度の均一性に優れているが、発光・非発光の2状態しかないため、このままでは、2階調しか表現できない。そこで、別の手法を組み合わせて、多階調化を図ることが行われている。多階調化のための手法としては、画素の発光面積に重みをつけてその選択により階調表示を行う面積階調方式と、発光時間に重みをつけてその選択により階調表示を行う時間階調方式とがある。そして、デジタル階調方式の場合には、高精細化にも適している時間階調法が用いられることが多い。一方、アナログ方式には、表示素子の発光強度をアナログ制御する方式と表示素子の発光時間をアナログ制御する方式がある。アナログ階調方式においては表示素子の発光強度をアナログ制御する方式がよく用いられている。そして、発光強度をアナログ制御する方式としては、画素毎の薄膜トランジスタ(以下TFTともいう)の特性のバラツキの影響を受けにくい電流入力電流駆動方式が用いられることが多い。

【0004】

そして、単極性、つまりPチャネル型またはNチャネル型のいずれか一つの極性のトランジスタで構成される電流入力電流駆動型の画素が特許文献1や非特許文献1に開示されている。

【特許文献1】特開2004−021219号公報

【非特許文献1】Tomoyuki Shirasaki、他7名、”Full−color Polymer AM−OLED using Ink−jet and a−Si TFT Technologies”、SOCIETY FOR INFORMATION DISPLAY 2004 INTERNATIONAL SYMPOSIUM DIGEST OF TECHNICAL PAPERS、P1516〜P1519

【発明の開示】

【発明が解決しようとする課題】

【0005】

特許文献1や非特許文献1では、表示素子に電流を供給する電源線の電位を一行ずつ変化させ、画素への信号書き込み時に表示素子へ電流が流れてしまうのを防いでいる。なぜなら、信号書き込み動作時に表示素子に電流が流れてしまうと、正しい信号が画素に入力できなくなってしまう。そのため、表示不良を起こしてしまう。

【0006】

ところで、電源線からは発光素子へ大きな電流を供給する必要がある。よって、電源線の電位を一行ずつ変化させながら、かつ大きな電流を供給するためには、大きな電流を制御できるスイッチを配置する必要がある。そのため、回路のトランジスタサイズを大きくしなければならないという問題がある。トランジスタサイズを大きくすると、トランジスタでの消費電力が大きくなってしまう。

【0007】

また、非特許文献1や特許文献1のような従来の構成では、信号書き込み動作時には表示素子を駆動するトランジスタは、Vds=Vgsとなり、発光動作時にはVds>Vgsとなる。よって、トランジスタの飽和領域での定電流特性(電流のフラット性)が悪くなると、信号書き込み動作時と発光動作時とで電流値が大きく異なってしまう。

【0008】

そこで本発明は、表示素子へ電流を供給する電源線の電位を一行ずつ変化させずに、信号書き込み動作時に表示素子へ電流が流れてしまうのを防ぐことが可能な表示装置を提供することを課題とする。

【課題を解決するための手段】

【0009】

本発明は、トランジスタに所定の電流を流してトランジスタのゲートソース間電圧を設定する際、トランジスタのソース端子に接続された負荷に電流がながれないようにするため、トランジスタのゲート端子の電位を調整する。そのため、トランジスタのゲート端子に接続された配線とトランジスタのドレイン端子に接続された配線とを異なる電位にする。

【0010】

つまり、トランジスタのゲート端子の電位をトランジスタのドレイン端子の電位より高く又は低くすることにより、トランジスタのソース端子の電位を調整し、負荷に電流が流れないようにする。

【0011】

以下に具体的な構成を示す。

【0012】

本発明の半導体装置は、トランジスタと、第1のスイッチと、第2のスイッチと、容量素子と、第1の配線と、第2の配線と、第3の配線と、負荷と、を有し、トランジスタは、第1端子が第1のスイッチを介して第1の配線と接続され、第2端子が第2の配線と接続され、ゲート端子が第2のスイッチを介して第3の配線と接続され、容量素子はトランジスタのゲート端子と第1端子との間に接続され、負荷はトランジスタの第1端子に接続されている。

【0013】

また、本発明の半導体装置は、上記構成において、第2の配線及び第3の配線には所定の電位が入力されていることを特徴とする半導体装置。

【0014】

また、本発明の半導体装置は、トランジスタと、第1のスイッチと、第2のスイッチと、容量素子と、第1の配線と、第2の配線と、第3の配線と、負荷と、を有し、トランジスタは、第1端子が第1のスイッチを介して第1の配線と接続され、第2端子が第2の配線と接続され、ゲート端子が第2のスイッチを介して第3の配線と接続され、容量素子はトランジスタのゲート端子と第1端子との間に接続され、負荷はトランジスタの第1端子に接続され、第3の配線の電位は第2の配線の電位よりも低い。

【0015】

また、本発明の半導体装置は、トランジスタと、第1のスイッチと、第2のスイッチと、容量素子と、第1の配線と、第2の配線と、第3の配線と、負荷と、を有し、トランジスタは、第1端子が第1のスイッチを介して第1の配線と接続され、第2端子が第2の配線と接続され、ゲート端子が第2のスイッチを介して第3の配線と接続され、容量素子はトランジスタのゲート端子と第1端子との間に接続され、負荷はトランジスタの第1端子に接続され、第2の配線及び第3の配線には所定の電位が入力され、第1のスイッチ及び第2のスイッチがオンし、且つ第1の配線に電流が流れるとき、トランジスタには電流が流れ、負荷には電流が流れず、第1のスイッチ及び第2のスイッチがオフすると、前記トランジスタ及び前記負荷に電流が流れる。

【0016】

また、本発明の半導体装置は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、負荷と、を有し、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が第3の配線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が第1の配線に接続され、第1端子が第2の配線と接続され、第3のトランジスタは、ゲート端子が第1の配線に接続され、第2端子が第4の配線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、負荷は第1のトランジスタの第1端子に接続されている。

【0017】

また、本発明の半導体装置は、上記構成において、第3の配線及び第4の配線には所定の電位が入力されている。

【0018】

また、本発明の半導体装置は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、負荷と、を有し、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が第3の配線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が第1の配線に接続され、第1端子が第2の配線と接続され、第3のトランジスタは、ゲート端子が第1の配線に接続され、第2端子が第4の配線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、負荷は第1のトランジスタの第1端子に接続され、第4の配線の電位は第3の配線の電位よりも低い。

【0019】

また、本発明の半導体装置は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、負荷と、を有し、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が第3の配線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が第1の配線に接続され、第1端子が第2の配線と接続され、第3のトランジスタは、ゲート端子が第1の配線に接続され、第2端子が第4の配線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、負荷は第1のトランジスタの第1端子に接続され、第1の配線に入力される信号により第2のトランジスタ及び第3のトランジスタがオンし、且つ第1の配線に電流が流れるとき、第1のトランジスタには電流が流れ、負荷には電流が流れず、第2のトランジスタ及び第3のトランジスタがオフすると、前記第1のトランジスタ及び前記負荷に電流が流れる。

【0020】

また、本発明の表示装置は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、画素電極と対向電極との間に発光層を有する発光素子と、を有し、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が第3の配線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が第1の配線に接続され、第1端子が第2の配線と接続され、第3のトランジスタは、ゲート端子が第1の配線に接続され、第2端子が第4の配線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、発光素子は画素電極が第1のトランジスタの第1端子に接続されている。

【0021】

また、本発明の表示装置は、上記構成において、第3の配線及び第4の配線には所定の電位が入力されている。

【0022】

また、本発明の表示装置は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、画素電極と対向電極との間に発光層を有する発光素子と、を有し、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が第3の配線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が第1の配線に接続され、第1端子が第2の配線と接続され、第3のトランジスタは、ゲート端子が第1の配線に接続され、第2端子が第4の配線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、発光素子は画素電極が第1のトランジスタの第1端子に接続され、第4の配線の電位は第3の配線の電位よりも低い。

【0023】

また、本発明の表示装置は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、画素電極と対向電極との間に発光層を有する発光素子と、を有し、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が第3の配線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が第1の配線に接続され、第1端子が第2の配線と接続され、第3のトランジスタは、ゲート端子が第1の配線に接続され、第2端子が第4の配線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、発光素子は画素電極が第1のトランジスタの第1端子に接続され、第1の配線に入力される信号により第2のトランジスタ及び第3のトランジスタがオンし、且つ第1の配線に電流が流れるとき、第1のトランジスタには電流が流れ、発光素子には電流が流れず、第2のトランジスタ及び第3のトランジスタがオフすると、前記第1のトランジスタ及び前記発光素子に電流が流れる。

【0024】

また、本発明の表示装置は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、第3の配線と、第4の配線と、画素電極と対向電極との間に発光層を有する発光素子と、を有し、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が第3の配線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が第1の配線に接続され、第1端子が第2の配線と接続され、第3のトランジスタは、ゲート端子が第1の配線に接続され、第2端子が第4の配線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、発光素子は画素電極が第1のトランジスタの第1端子に接続され、第4の配線の電位は対向電極の電位と等しい。

【0025】

また、本発明の表示装置は、走査線駆動回路と、信号線駆動回路と、画素部と、を有し、画素部には、走査線駆動回路から伸張して配置された複数の走査線と、信号線駆動回路から伸張して配置された複数の信号線と、走査線と信号線とに対応してマトリクスに配置された複数の画素と、を備え、画素は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、走査線と、信号線と、電源線と、バイアス線と、画素電極と対向電極との間に発光層を有する発光素子と、を備え、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が電源線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が走査線に接続され、第1端子が信号線と接続され、第3のトランジスタは、ゲート端子が走査線に接続され、第2端子がバイアス線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、発光素子は画素電極が第1のトランジスタの第1端子に接続されている。

【0026】

また、本発明の表示装置は、走査線駆動回路と、信号線駆動回路と、画素部と、を有し、画素部には、走査線駆動回路から伸張して配置された複数の走査線と、信号線駆動回路から伸張して配置された複数の信号線と、走査線と信号線とに対応してマトリクスに配置された複数の画素と、を備え、画素は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、走査線と、信号線と、電源線と、バイアス線と、画素電極と対向電極との間に発光層を有する発光素子と、を備え、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が電源線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が走査線に接続され、第1端子が信号線と接続され、第3のトランジスタは、ゲート端子が走査線に接続され、第2端子がバイアス線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、発光素子は画素電極が第1のトランジスタの第1端子に接続され、バイアス線の電位は電源線の電位よりも低い。

【0027】

また、本発明の表示装置は、走査線駆動回路と、信号線駆動回路と、画素部と、を有し、画素部には、走査線駆動回路から伸張して配置された複数の走査線と、信号線駆動回路から伸張して配置された複数の信号線と、走査線と信号線とに対応してマトリクスに配置された複数の画素と、を備え、画素は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、走査線と、信号線と、電源線と、バイアス線と、画素電極と対向電極との間に発光層を有する発光素子と、を備え、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が電源線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が走査線に接続され、第1端子が信号線と接続され、第3のトランジスタは、ゲート端子が走査線に接続され、第2端子がバイアス線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、走査線に入力される信号により第2のトランジスタ及び第3のトランジスタがオンし、且つ信号線に信号電流が流れるとき、第1のトランジスタには電流が流れ、発光素子には電流が流れず、第2のトランジスタ及び第3のトランジスタがオフすると、前記第1のトランジスタ及び前記発光素子に電流が流れる。

【0028】

また、本発明の表示装置は、走査線駆動回路と、信号線駆動回路と、画素部と、を有し、画素部には、走査線駆動回路から伸張して配置された複数の走査線と、信号線駆動回路から伸張して配置された複数の信号線と、走査線と信号線とに対応してマトリクスに配置された複数の画素と、を備え、画素は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、走査線と、信号線と、電源線と、バイアス線と、画素電極と対向電極との間に発光層を有する発光素子と、を備え、第1のトランジスタは、第1端子が第2のトランジスタの第2端子と接続され、第2端子が電源線と接続され、ゲート端子が第3のトランジスタの第1端子と接続され、第2のトランジスタは、ゲート端子が走査線に接続され、第1端子が信号線と接続され、第3のトランジスタは、ゲート端子が走査線に接続され、第2端子がバイアス線に接続され、容量素子は第1のトランジスタのゲート端子と第1端子との間に接続され、発光素子は画素電極が第1のトランジスタの第1端子に接続され、バイアス線の電位は対向電極の電位と等しい。

【0029】

また、本発明の表示装置は、上記構成において、第1のトランジスタ、第2のトランジスタ及び第3のトランジスタがNチャネル型トランジスタである。

【0030】

また、本発明の表示装置は、上記構成において、Nチャネル型トランジスタの半導体層に非晶質半導体膜が用いられている。

【0031】

なお、本発明に示すスイッチは、様々な形態のものを用いることができ、一例として、電気的スイッチや機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されず、様々なものを用いることができる。例えば、トランジスタでもよいし、ダイオード(PNダイオード、PINダイオード、ショットキーダイオード、ダイオード接続のトランジスタなど)でもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性(導電型)は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設けているものやマルチゲート構造にしているもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源(Vss、GND、0Vなど)に近い状態で動作する場合はNチャネル型を、反対に、ソース端子の電位が、高電位側電源(Vddなど)に近い状態で動作する場合はPチャネル型を用いることが望ましい。なぜなら、ゲートソース間電圧の絶対値を大きくできるため、スイッチとして、動作しやすいからである。なお、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。CMOS型のスイッチにすると、スイッチを介して出力する電圧(つまりスイッチへの入力電圧)が、出力電圧に対して、高かったり、低かったりして、状況が変化する場合においても、適切に動作させることが出来る。

【0032】

なお、本発明において、接続されているとは、電気的に接続されている場合と直接接続されている場合とを含むものとする。したがって、本発明が開示する構成において、所定の接続関係に加え、その間に電気的な接続を可能とする他の素子(例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど)が配置されていてもよい。あるいは、間に他の素子を挟まずに、直接接続されて、配置されていてもよい。なお、電気的な接続を可能とする他の素子を間に介さずに接続されていて、直接接続されている場合のみを含む場合であって、電気的に接続されている場合を含まない場合には、直接接続されている、と記載するものとする。なお、電気的に接続されている、と記載する場合は、電気的に接続されている場合と直接接続されている場合とを含むものとする。

【0033】

なお、表示素子は、様々な形態を用いることが出来る。例えば、EL素子(有機EL素子、無機EL素子又は有機物材料び無機材料を含むEL素子)、電子放出素子、液晶素子、電子インク、光回折素子、放電素子、微少鏡面素子(DMD:Digital Micromirror Device)、圧電素子、カーボンナノチューブなど、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いたELパネル方式の表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッションディスプレイ(FED:Field Emission Display)やSED方式平面型ディスプレイ(SED:Surface−conduction Electron−emitter Disply)など、液晶素子を用いた液晶パネル方式の表示装置としては液晶ディスプレイ、電子インクを用いたデジタルペーパー方式の表示装置としては電子ペーパー、光回折素子を用いた表示装置としてはグレーティングライトバルブ(GLV)方式のディスプレイ、放電素子を用いたPDP(Plazma Display Panel)方式のディスプレイとしてはプラズマディスプレイ、微少鏡面素子を用いたDMDパネル方式の表示装置としてはデジタル・ライト・プロセッシング(DLP)方式の表示装置、圧電素子を用いた表示装置としては圧電セラミックディスプレイ、カーボンナノチューブを用いた表示装置としてはナノ放射ディスプレイ(NED:Nano Emissive Display)、などがある。

【0034】

なお、本発明において、トランジスタは、様々な形態のトランジスタを適用させることが出来る。よって、適用可能なトランジスタの種類に限定はない。したがって、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ(TFT)、半導体基板やSOI基板を用いて形成されるMOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、ZnO、a−InGaZnOなどの化合物半導体を用いたトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、トランジスタが配置されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、石英基板、プラスチック基板、紙基板、セロファン基板、石材基板、ステンレス・スチル基板、ステンレス・スチル・ホイルを有する基板などに配置することが出来る。また、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板上に配置するようにしてもよい。

【0035】

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート本数が2本以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値を大きくしたり、空乏層ができやすくなってサブスレッショルド係数(S値)をよくしたりすることができる。また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれていてもよいし、並列に接続されていてもよいし、直列に接続されていてもよい。また、チャネル(もしくはその一部)にソース電極やドレイン電極が重なっていてもよい。チャネル(もしくはその一部)にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。

【0036】

なお、すでに述べたように、本発明におけるトランジスタは、様々なタイプを用いることができ、様々な基板上に形成させることができる。したがって、回路の全てが、ガラス基板上に形成されていてもよいし、プラスチック基板に形成されていてもよいし、単結晶基板に形成されていてもよいし、SOI基板上に形成されていてもよいし、どのような基板上に形成されていてもよい。回路の全てが形成されていることにより、部品点数を減らしてコストを低減したり、回路部品との接続点数を減らして信頼性を向上させたりすることができる。あるいは、回路の一部が、ある基板に形成されており、回路の別の一部が、別の基板に形成されていてもよい。つまり、回路の全てが同じ基板上に形成されていなくてもよい。例えば、回路の一部は、ガラス基板上にトランジスタを用いて形成し、回路の別の一部は、単結晶基板上に形成し、そのICチップをCOG(Chip On Glass)で接続してガラス基板上に配置してもよい。あるいは、そのICチップをTAB(Tape Auto Bonding)やプリント基板を用いてガラス基板と接続してもよい。このように、回路の一部が同じ基板に形成されていることにより、部品点数を減らしてコストを低減したり、回路部品との接続点数を減らして信頼性を向上させたりすることができる。また、駆動電圧が高い部分や駆動周波数が高い部分は、消費電力が大きくなってしまうので、そのような部分は同じ基板に形成しないようにすれば、消費電力の向上を防ぐことができる。

【0037】

なお、本発明においては、一画素とは、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R(赤)G(緑)B(青)の色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。なお、色要素は、三色に限定されず、それ以上でもよく、例えば、RGBW(Wは白)や、RGBに、イエロー、シアン、マゼンダを追加したものなどがある。また、別の例としては、1つの色要素について、複数の領域を用いて明るさを制御する場合は、その領域一つ分を一画素とする。よって、一例としては、面積階調を行う場合、一つの色要素につき、明るさを制御する領域が複数あり、その全体で階調を表現するわけであるが、明るさを制御する領域の一つ分を一画素とする。よって、その場合は、一つの色要素は、複数の画素で構成されることとなる。また、その場合、画素によって、表示に寄与する領域の大きさが異なっている場合がある。また、一つの色要素につき複数ある、明るさを制御する領域において、つまり、一つの色要素を構成する複数の画素において、各々に供給する信号を僅かに異ならせるようにして、視野角を広げるようにしてもよい。

【0038】

なお、本発明において、画素は、マトリクス状に配置(配列)されている場合を含んでいる。ここで、画素がマトリクスに配置(配列)されているとは、縦縞と横縞を組み合わせたいわゆる格子状にストライプ配置されている場合を含んでいる。そして、三色の色要素(例えばRGB)でフルカラー表示を行う場合に、三つの色要素のドットがいわゆるデルタ配置されている場合も含むものとする。さらに、ベイヤー配置されている場合も含んでいる。なお、色要素は、三色に限定されず、それ以上でもよく、色要素のドット毎にその発光領域の大きさが異なっていてもよい。

【0039】

なお、トランジスタとは、それぞれ、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有する。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソースまたはドレインであるかを限定することが困難である。そこで、本発明においては、ソース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある。その場合、一例としては、それぞれを第1端子、第2端子と表記する場合がある。

【0040】

なお、ゲートとは、ゲート電極とゲート配線(ゲート線またはゲート信号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言う。ゲート電極とは、チャネル領域やLDD(Lightly Doped Drain)領域などを形成する半導体と、ゲート絶縁膜を介してオーバーラップしている部分の導電膜のことを言う。ゲート配線とは、各画素のゲート電極の間を接続したり、ゲート電極と別の配線とを接続したりするための配線のことを言う。

【0041】

ただし、ゲート電極としても機能し、ゲート配線としても機能するような部分も存在する。そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。つまり、ゲート電極とゲート配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているゲート配線とオーバーラップしてチャネル領域がある場合、その領域はゲート配線として機能しているが、ゲート電極としても機能していることになる。よって、そのような領域は、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

【0042】

また、ゲート電極と同じ材料で形成され、ゲート電極とつながっている領域も、ゲート電極と呼んでも良い。同様に、ゲート配線と同じ材料で形成され、ゲート配線とつながっている領域も、ゲート配線と呼んでも良い。このような領域は、厳密な意味では、チャネル領域とオーバーラップしていなかったり、別のゲート電極と接続させる機能を有してなかったりする場合がある。しかし、製造マージンなどの関係で、ゲート電極やゲート配線と同じ材料で形成され、ゲート電極やゲート配線とつながっている領域がある。よって、そのような領域もゲート電極やゲート配線と呼んでも良い。

【0043】

また、例えば、マルチゲートのトランジスタにおいて、1つのトランジスタのゲート電極と、別のトランジスタのゲート電極とは、ゲート電極と同じ材料で形成された導電膜で接続される場合が多い。そのような領域は、ゲート電極とゲート電極とを接続させるための領域であるため、ゲート配線と呼んでも良いが、マルチゲートのトランジスタを1つのトランジスタであると見なすことも出来るため、ゲート電極と呼んでも良い。つまり、ゲート電極やゲート配線と同じ材料で形成され、それらとつながって配置されているものは、ゲート電極やゲート配線と呼んでも良い。

また、例えば、ゲート電極とゲート配線とを接続してさせている部分の導電膜も、ゲート電極と呼んでも良いし、ゲート配線と呼んでも良い。

【0044】

なお、ゲート端子とは、ゲート電極の領域や、ゲート電極と電気的に接続されている領域について、その一部分のことを言う。

【0045】

なお、ソースとは、ソース領域とソース電極とソース配線(ソース線またはソース信号線等とも言う)とを含んだ全体、もしくは、それらの一部のことを言う。ソース領域とは、P型不純物(ボロンやガリウムなど)やN型不純物(リンやヒ素など)が多く含まれる半導体領域のことを言う。従って、少しだけP型不純物やN型不純物が含まれる領域、いわゆる、LDD(Lightly Doped Drain)領域は、ソース領域には含まれない。ソース電極とは、ソース領域とは別の材料で形成され、ソース領域と電気的に接続されて配置されている部分の導電層のことを言う。ただし、ソース電極は、ソース領域も含んでソース電極と呼ぶこともある。ソース配線とは、各画素のソース電極の間を接続したり、ソース電極と別の配線とを接続したりするための配線のことを言う。

【0046】

しかしながら、ソース電極としても機能し、ソース配線としても機能するような部分も存在する。そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。つまり、ソース電極とソース配線とが、明確に区別できないような領域も存在する。例えば、延伸して配置されているソース配線とオーバーラップしてソース領域がある場合、その領域はソース配線として機能しているが、ソース電極としても機能していることになる。よって、そのような領域は、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

【0047】

また、ソース電極と同じ材料で形成され、ソース電極とつながっている領域や、ソース電極とソース電極とを接続する部分も、ソース電極と呼んでも良い。また、ソース領域とオーバーラップしている部分も、ソース電極と呼んでも良い。同様に、ソース配線と同じ材料で形成され、ソース配線とつながっている領域も、ソース配線と呼んでも良い。このような領域は、厳密な意味では、別のソース電極と接続させる機能を有していたりすることがない場合がある。しかし、製造マージンなどの関係で、ソース電極やソース配線と同じ材料で形成され、ソース電極やソース配線とつながっている領域がある。よって、そのような領域もソース電極やソース配線と呼んでも良い。

【0048】

また、例えば、ソース電極とソース配線とを接続してさせている部分の導電膜も、ソース電極と呼んでも良いし、ソース配線と呼んでも良い。

【0049】

なお、ソース端子とは、ソース領域や、ソース電極や、ソース電極と電気的に接続されている領域について、その一部分のことを言う。

【0050】

なお、ドレインについては、ソースと同様である。

【0051】

なお、本発明において、半導体装置とは半導体素子(トランジスタやダイオードなど)を含む回路を有する装置をいう。また、半導体特性を利用することで機能しうる装置全般でもよい。また、表示装置とは、表示素子(液晶素子や発光素子など)を有する装置のことを言う。なお、基板上に液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が形成された表示パネル本体のことでもよい。さらに、フレキシブルプリントサーキット(FPC)やプリント配線基盤(PWB)が取り付けられたもの(ICや抵抗素子や容量素子やインダクタやトランジスタなど)も含んでもよい。さらに、偏光板や位相差板などの光学シートを含んでいても良い。さらに、バックライト(導光板やプリズムシートや拡散シートや反射シートや光源(LEDや冷陰極管など)を含んでいても良い)を含んでいても良い。また、発光装置とは、特にEL素子やFEDで用いる素子などの自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有している表示装置をいう。

【0052】

なお、本発明において、ある物の上に形成されている、あるいは、〜上に形成されている、というように、〜の上に、あるいは、〜上に、という記載については、ある物の上に直接接していることに限定されない。直接接してはいない場合、つまり、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上に(もしくは層A上に)、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層(例えば層Cや層Dなど)が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。また、〜の上方に、という記載についても同様であり、ある物の上に直接接していることに限定されず、間に別のものが挟まっている場合も含むものとする。従って例えば、層Aの上方に、層Bが形成されている、という場合は、層Aの上に直接接して層Bが形成されている場合と、層Aの上に直接接して別の層(例えば層Cや層Dなど)が形成されていて、その上に直接接して層Bが形成されている場合とを含むものとする。なお、〜の下に、あるいは、〜の下方に、の場合についても、同様であり、直接接している場合と、接していない場合とを含むこととする。

【発明の効果】

【0053】

本発明は、表示素子へ電流を供給する電源線の電位を一行ずつ変化させずに、信号書き込み動作時に表示素子へ電流が流れてしまうのを防ぐことが可能な表示装置を提供することができる。

【発明を実施するための最良の形態】

【0054】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

【0055】

本発明は、EL素子などを有する画素だけでなく、電流源を有する様々なアナログ回路に適用することが出来る。そこでまず、本実施の形態では、本発明の基本原理について述べる。

【0056】

まず、図21に、本発明の基本原理に基づく半導体装置の構成について示す。トランジスタ2101、第1のスイッチ2102、第2のスイッチ2103、容量素子2104、負荷2105、第1の配線2106、第2の配線2107及び第3の配線2108を有する。なお、トランジスタ2101はNチャネル型トランジスタである。

【0057】

まず、半導体装置の接続構造について説明する。

【0058】

トランジスタ2101は、第1端子(ソース端子又はドレイン端子)が負荷2105に接続され、第2端子(ソース端子又はドレイン端子)が第2の配線2107に接続され、ゲート端子が第2のスイッチ2103を介して第3の配線2108と接続されている。つまり、第2のスイッチ2103がオンしているとき、トランジスタ2101のゲート端子と第3の配線2108とが導通しており、第2のスイッチ2103がオフしているとき、トランジスタ2101のゲート端子と第3の配線2108とが非導通となっている。

【0059】

また、トランジスタ2101の第1端子は、第1のスイッチ2102を介して第1の配線2106と接続されている。つまり、第1のスイッチ2102がオンしているとき、トランジスタ2101の第1端子と第1の配線2106とが導通しており、第1のスイッチ2102がオフしているとき、トランジスタ2101の第1端子と第1の配線2106とが非導通となっている。

【0060】

また、トランジスタ2101のゲート端子と第1端子の間に容量素子2104が接続されている。つまり、容量素子2104の第1電極がトランジスタ2101のゲート端子に接続され、第2電極がトランジスタ2101の第1端子に接続されている。なお、容量素子2104は、配線や活性層や電極等により絶縁膜を挟んだ構成のものでもいいし、トランジスタ2101のゲート容量を用いて省略することもできる。

【0061】

なお、第2の配線2107や、第3の配線2108にはそれぞれ所定の電位が入力されている。

【0062】

続いて半導体装置の動作について説明する。

【0063】

設定動作時には第1のスイッチ2102及び第2のスイッチ2103をオンにする。

【0064】

すると、容量素子2104に電荷が蓄積され、トランジスタ2101に電流が流れる。このとき流れる電流は第1の配線2106に設定された電流である。

【0065】

そして、容量素子2104への電荷の蓄積が完了したら、第1のスイッチ2102と第2のスイッチ2103をオフにする。すると、トランジスタ2101のゲートソース間電圧が容量素子2104で保持される。また、このとき第3の配線2108の電位を調整することにより負荷2105には電流を流れなくすることができる。

【0066】

なお、このときのトランジスタ2101のゲートソース間電圧は、第1の配線2106に流れる電流と同じだけの電流をトランジスタ2101に流すための電圧となる。

【0067】

そして、出力動作時には、第1のスイッチ2102と第2のスイッチ2103をオフにする。すると、トランジスタ2101のゲート端子はフローティングとなる。そして、トランジスタ2101のゲートソース間電圧は容量素子2104で保持されている。よって、設定動作時に第1の配線2106に流れた電流が、第2の配線2107からトランジスタ2101を介して負荷2105に流れる。

【0068】

このとき、トランジスタ2101の第1端子がソース端子であり、第1端子の電位が高くなる。そしてトランジスタ2101のドレイン・ソース間電圧は設定動作時よりも小さくなる。しかし、トランジスタ2101を飽和領域で動作させるので、設定動作時に第1の配線2106に流れた電流とほぼ等しい電流を負荷2105に流すことができる。

【0069】

なお、トランジスタ2101にはNチャネル型トランジスタを用いているが、Pチャネル型トランジスタであってもよい。その場合には電流の向きは逆方向となる。

【0070】

(実施の形態1)

本実施の形態において、本発明を画素に適用した場合の基本的な画素構成を説明する。

【0071】

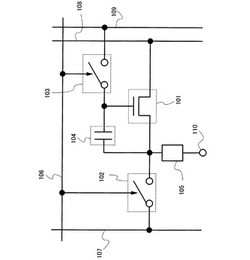

本実施の形態に示す画素は、トランジスタ101、第1のスイッチ102、第2のスイッチ103、容量素子104、表示素子105、第1の配線106、第2の配線107、第3の配線108及び第4の配線109を有する。なお、トランジスタ101はNチャネル型のトランジスタである。

【0072】

まず、画素の接続構造について説明する。

【0073】

トランジスタ101は、第1端子(ソース端子又はドレイン端子)が表示素子105の画素電極に接続され、第2端子(ソース端子又はドレイン端子)が第3の配線108に接続され、ゲート端子が第2のスイッチ103を介して第4の配線109と接続されている。つまり、第2のスイッチ103がオンしているとき、トランジスタ101のゲート端子と第4の配線109とが導通しており、第2のスイッチ103がオフしているとき、トランジスタ101のゲート端子と第4の配線109とが非導通となっている。

【0074】

また、トランジスタ101の第1端子は、第1のスイッチ102を介して第2の配線107と接続されている。つまり、第1のスイッチ102がオンしているとき、トランジスタ101の第1端子と第2の配線107とが導通しており、第1のスイッチ102がオフしているとき、トランジスタ101の第1端子と第2の配線107とが非導通となっている。

【0075】

また、トランジスタ101のゲート端子と第1端子の間に容量素子104が接続されている。つまり、容量素子104の第1電極がトランジスタ101のゲート端子に接続され、第2電極がトランジスタ101の第1端子に接続されている。なお、容量素子104は、配線や活性層や電極等により絶縁膜を挟んだ構成のものでもいいし、トランジスタ101のゲート容量を用いて省略することもできる。

【0076】

なお、表示素子105の対向電極110や、第3の配線108や第4の配線109にはそれぞれ所定の電位が入力されている。

【0077】

また、第1の配線106に信号を入力することにより、第1のスイッチ102と第2のスイッチ103のオンオフが制御される。

【0078】

また、第2の配線107には、画素の階調にしたがった信号が入力される。この信号は、ビデオ信号に相当し、信号電流が第2の配線107に流れる。

【0079】

なお、第1のスイッチ102と第2のスイッチ103にはトランジスタを適用することができる。よって、第1のスイッチ102と第2のスイッチ103にNチャネル型のトランジスタを適用した場合について図2に示す。なお、図1の構成と共通するところは共通の符号を用いてその説明を省略する。

【0080】

第1のスイッチングトランジスタ201が第1のスイッチ102に相当し、第2のスイッチングトランジスタ202が第2のスイッチ103に相当する。

【0081】

第1のスイッチングトランジスタ201はゲート端子が第1の配線106に接続され、第1端子(ソース端子又はドレイン端子)が第2の配線107に接続され、第2端子(ソース端子又はドレイン端子)が表示素子105の画素電極及びトランジスタ101の第1端子と接続されている。よって、第1の配線106に入力される信号がHレベルのときに第1のスイッチングトランジスタ201はオンし、第1の配線106に入力される信号がLレベルのときに第1のスイッチングトランジスタ201はオフする。

【0082】

また、第2のスイッチングトランジスタ202はゲート端子が第1の配線106に接続され、第1端子(ソース端子又はドレイン端子)がトランジスタ101のゲート端子に接続され、第2端子(ソース端子又はドレイン端子)が第4の配線109と接続されている。よって、第1の配線106に入力される信号がHレベルのときに第2のスイッチングトランジスタ202はオンし、第1の配線106に入力される信号がLレベルのときに第2のスイッチングトランジスタ202はオフする。

【0083】

続いて、本実施の形態に示す画素の動作について図3(A)、(B)、(C)を用いて説明する。なお、図1と図2の画素の動作は同様であるため、図3では図2の画素構成を用いて説明している。

【0084】

なお、第2の配線107に接続された電流源301は、この画素に書き込む信号電流Idataを設定する。そして、第2の配線107は電流源301を介して配線302と接続されている。配線302には、所定の電位が入力されている。ここで、第3の配線108に入力する電位をV3、第4の配線109に入力する電位をV4、配線302に入力する電位をV5、対向電極110に入力する電位をVcomとする。そして、電位の関係は少なくとも、V3>Vcom>V5とする。また、V4=Vcomであれば、図48に示すように第4の配線109と表示素子105の対向電極110とを第5の配線4801で接続してもよい。

【0085】

なお、画素の動作には、画素へ信号の書き込みを行う信号書き込み動作と、画素に書き込まれた信号にしたがった階調の発光をする発光動作がある。図3(A)、及び図3(B)は、共に信号書き込み動作を説明する図であり、図3(C)は発光動作を説明する図である。

【0086】

まず、信号書き込み動作時の過渡状態について図3(A)を用いて説明する。第1の配線106に入力する信号をHレベルにして、第1のスイッチングトランジスタ201と第2のスイッチングトランジスタ202をオンにする。すると、図3(A)のように電流が流れる。つまり、電流の経路は、第4の配線109から第2のスイッチングトランジスタ202を介して容量素子104に電流が流れ込む第1経路と、第3の配線108からトランジスタ101に電流が流れる第2経路とがある。そして、第1経路に流れる電流Icと第2経路に流れる電流Itrは、トランジスタ101の第1端子と容量素子104の第2電極との接続部で合流する。そして、信号電流Idataとして第1のスイッチングトランジスタ201及び電流源301を介して配線302に流れる。つまり、Ic+Itr=Idataとなる。

【0087】

やがて、容量素子104へは電流が流れなくなる。このとき、信号書き込み動作時の定常状態となり、図3(B)のように電流が流れる。そして、第3の配線108からトランジスタ101に流れる電流Itrが、信号電流Idataと等しくなっている。つまり、トランジスタ101のゲートソース間電圧Vgsは、トランジスタ101に信号電流Idataを流すのに必要な電圧となっている。そして、このトランジスタ101のゲートソース間電圧Vgs分の電荷が容量素子104に蓄積されている。

【0088】

なお、このときのトランジスタ101のゲート端子の電位をVa、第1端子の電位をVbとすると、Vgs=(Va−Vb)である。そして、表示素子105の順方向しきい値電圧VELthとしたとき、(Vb−Vcom)<VELthとなるようにすると信号書き込み動作時に表示素子105へ電流を流さなくすることができる。そのため、第4の配線109に入力する電位V4は、V3>V4>V5となるようにするとよい。また、V4=Vcomとすることにより、画素へ必要な電源数を減らすことができる。また、信号書き込み時に表示素子105へ逆方向バイアスを印加することができる。

【0089】

なお、逆方向バイアスを表示素子105に印加しても、正常な表示素子105には電流は流れない(若しくは流れたとしても微少な電流である)。一方、表示素子105に短絡箇所が有る場合には、その短絡箇所に電流が流れる。そして、短絡箇所を絶縁化する。よって、表示不良を改善することができる。

【0090】

続いて、発光動作について図3(C)を用いて説明する。第1の配線106に入力する信号をLレベルにして、第1のスイッチングトランジスタ201と第2のスイッチングトランジスタ202とをオフにする。すると、図3(C)のように電流が流れる。このとき、第2のスイッチングトランジスタ202がオフしているため、容量素子104は、トランジスタ101に信号電流Idataを流すのに必要なゲートソース間電圧Vgsを保持する。よって、トランジスタ101に信号電流Idataとほぼ等しい電流が流れる。

【0091】

なお、このときのトランジスタ101のゲート端子の電位をVa’、第1端子の電位をVb’とすると、Vgs=(Va’−Vb’)である。なぜなら、Vb’>Vbとなるが、容量素子104はゲートソース間電圧Vgsを保持しているため、Vb’が上昇するとともにVa’も上昇するからである。

【0092】

なお、第1の配線106に入力するHレベルの信号の電位をV1(H)、Lレベルの信号の電位をV1(L)とすると次のような電位にすることが望ましい。また、第1のスイッチングトランジスタ201のしきい値電圧をVth1、第2のスイッチングトランジスタ202のしきい値電圧をVth2とする。

【0093】

図3(B)で示したように、表示素子105の画素電極の電位はVbとなっても、第1のスイッチングトランジスタ201をオンにしておく必要がある。そのためV1(H)>Vb+Vth1とする。また、第2のスイッチングトランジスタ202をオンにしておくためV1(H)>V4+Vth2とする。具体的には、例えば、V4=Vcomのときには、V1(H)はVcomより1〜8V高い電位であるとよい。

【0094】

また、図3(C)で示したように、第1のスイッチングトランジスタ201がオフするためには、V1(L)<(Vb+Vth1)とする。つまり、他の画素へ信号電流の書き込みを行っているときに、第2の配線107の電位はVbとなるため、この電位になったときにも選択しない画素は第1のスイッチングトランジスタ201がオフしている必要があるからである。また、第2のスイッチングトランジスタ202がオフにしておくため、V1(L)<(V4+Vth2)とする。具体的には、例えば、V4=Vcomのときには、V1(L)はVcomより1〜8V低い電位であるとよい。

【0095】

なお、第3の配線108と第4の配線109とは、それぞれV3、V4の電位が供給されているが、常に同じ電位のまま保たれている必要はない。例えば信号書き込み動作と発光動作とで、電位が異なっていても、正常に動作する場合は、問題ない。

【0096】

あるいは、信号書き込み動作毎に第4の配線109に供給する電位を変動させる構成であってもよい。特に信号書き込み動作時に電流源301によって設定される電流が大きいときに第4の配線109に供給する電位を上昇させることにより、電流源301に接続された配線302に供給する電位を低くしすぎなくても正常な動作を行うことができるため好適である。すなわち、信号書き込み動作時に第4の配線109に供給する電位を変動させることにより、第4の配線109に供給する電位が固定されている場合よりも第3の配線108と配線302との電位差を小さくしても、正常に動作させることができる。なお第4の配線109に供給する電位は、信号書き込み動作時に電流源301よって設定される電流の大きさに応じて変化させてもよい。例えば信号書き込み動作時に電流源301によって設定される電流が大きいときは、第4の配線109に供給する電位を高くして、信号書き込み動作時に電流源301によって設定される電流の大きさが小さいときは、第4の配線109に供給する電位を低くすることにより、信号書き込み動作時に表示素子105に電流が漏れてしまうことを防止しつつ、第3の配線108と配線302との電位差を小さくすることができる。

【0097】

なお、配線302と対向電極110とは、それぞれ所定の電位が供給されているが、常に同じ電位のまま保たれている必要はない。信号書き込み動作と出力動作とで、電位が異なっていても、正常に動作する場合は、問題ない。

【0098】

よって、本実施の形態に示した画素構成によれば信号書き込み動作時のトランジスタのゲート端子の電位を制御することにより、信号書き込み動作時に表示素子へ電流が流れてしまうのを防ぐことができる。

【0099】

なお、図2に示した画素構成によれば、Nチャネル型のトランジスタのみで画素を構成することができるため、製造工程の簡略化を図ることができる。また、画素を構成するトランジスタの半導体層にアモルファス半導体やセミアモルファス半導体(若しくは微結晶半導体ともいう)などを用いることができる。例えば、アモルファス半導体として、アモルファスシリコン(a−Si:H)が挙げられる。よって、さらなる製造工程の簡略化を図ることが可能である。したがって、製造コストの削減や歩留まりの向上を図ることができる。

【0100】

また、本発明の構成によれば、信号書き込み動作時にVds>Vgsにすることができる。そして、信号書き込み動作時と発光動作時とでVdsの変動を小さくすることができ、トランジスタ101の飽和領域での定電流特性(電流のフラット性)が悪くても、信号書き込み動作時と発光動作時との電流値をほぼ等しくすることができる。特に、トランジスタ101の半導体層に非晶質半導体膜(例えばアモルファスシリコン)を用いると飽和領域での定電流特性(電流のフラット性)が悪くなってしまう場合がある。よって、トランジスタ101の半導体層に非晶質半導体膜を用いている場合に本発明の構成を適用すれば表示不良を防止することができる。

【0101】

また、図2に示したトランジスタ101にはソースドレイン端子間に大きな電圧が印加されるため、第1のスイッチングトランジスタ201や第2のスイッチングトランジスタ202よりもチャネル長を長くするとよい。又は、トランジスタ101として図16に示すようにマルチゲートトランジスタを適用してもよい。こうすることにより、トランジスタの耐圧が大きくなり、トランジスタが破壊されるのを防止することができる。

【0102】

また、図2に示したトランジスタ101で制御された電流を表示素子105へ流すため、トランジスタ101は大きなオン電流を流す能力が必要である。よって、トランジスタ101は、第1のスイッチングトランジスタ201や第2のスイッチングトランジスタ202よりもチャネル幅を大きくしてもよい。又は、トランジスタ101として図17のトランジスタ1701に示すように複数のトランジスタを並列に接続した構成であってもよい。

【0103】

続いて、本発明の画素を有する表示装置について図4を用いて説明する。

【0104】

表示装置は、信号線駆動回路401、走査線駆動回路402及び画素部403を有し、画素部403には、信号線駆動回路401から列方向に伸張して配置された複数の信号線S1〜Snと、走査線駆動回路402から行方向に伸張して配置された複数の走査線G1〜Gmと、信号線S1〜Snと走査線G1〜Gmとに対応してマトリクスに配置された複数の画素404と、を有する。また、信号線S1〜Snと平行に電源線P1〜Pnと、バイアス線B1〜Bnとを有している。そして、各画素404は、それぞれ、信号線Sj(信号線S1〜Snのうちいずれか一)、走査線Gi(走査線G1〜Gmのうちいずれか一)、電源線Pj(電源線P1〜Pn)のうちいずれか一)、及びバイアス線Bj(バイアス線B1〜Bnのうちいずれか一)と接続されている。

【0105】

なお、走査線Giは図1の第1の配線106に相当し、信号線Sjは図1の第2の配線107に相当し、電源線Pjは図1の第3の配線108に相当し、バイアス線Bjは図1の第4の配線109に相当する。

【0106】

走査線駆動回路402から出力される信号により走査線G1〜Gmを一つずつ選択する。そして、選択された走査線に接続されている画素404に信号を書き込む。このとき、それぞれの画素の階調に対応した信号電流が各信号線S1〜Snに流れる。

【0107】

信号の書き込みを終えると別の走査線を選択し、その走査線に接続されている画素404へ信号の書き込みを行う。信号の書き込みを終えた画素は、発光動作に移り、その画素へ書き込まれた信号にしたがって発光する。こうして、次々と画素404へ信号の書き込みを行い、全ての画素404へ信号の書き込みを行う。

【0108】

なお、図4に示した表示装置の構成は一例であって本発明はこれに限定されない。つまり、電源線P1〜Pnやバイアス線B1〜Bnは信号線S1〜Snと平行に配置されていなくてもよく、走査線G1〜Gmに平行に配置されていてもいいし、電源線やバイアス線のそれぞれが格子状に配置されていてもいい。しかし、画素部403に複数の色要素を有している場合には、図4のように配置するのが好ましい。

【0109】

つまり、図46に示すように、図1の画素における第4の配線109を第1の配線106と平行に配置してもよい。また、その場合には、図47に示すように、図4におけるバイアス線B1〜Bnに相当するバイアス線B1〜Bmを走査線G1〜Gmと平行に配置する。そして、このバイアス線B1〜Bmは電位を変動することができるようにしてもよい。つまり、走査させるようにしてもよい。その場合に走査線G1〜Gmを走査する走査線駆動回路402とは別にバイアス線駆動回路を設けても良い。

【0110】

また、画素部403に複数の色要素を有している場合には、それぞれの色要素となる画素毎に接続される電源線やバイアス線の電位をかえてもよい。また、それぞれの色要素となる画素毎に画素電極の大きさが異なっていてもよい。つまり、色要素となる画素毎に発光面積がことなっていてもよい。こうすることにより、特にフルカラー表示のときの表示素子として、異なる色のEL素子を用いた場合、色のバランスや、EL素子の劣化の進行を調整することが可能となる。

【0111】

また、本発明の画素は、図1の構成に限られない。信号書き込み動作時に図19(A)のように接続され、発光動作時に図19(B)のように接続されていればよい。つまり、信号書き込み動作時には、トランジスタ101は、ゲート端子が第4の配線109に接続され、第1端子が第2の配線107に接続され、第2端子が第3の配線108に接続されていればよい。また、発光動作時には、トランジスタ101は、ゲート端子がどこにも導通していなく、第1端子が表示素子105の画素電極と接続され、第2端子が第3の配線108と接続されていればよい。

【0112】

よって、図1に示した画素において、第1のスイッチ102と第2のスイッチ103のオンオフを別々に制御するため、別途配線を設けても良い。つまり、図5に示すように、第1のスイッチ102のオンオフを制御する第1の配線106とは別に第2のスイッチ103のオンオフを制御する第5の配線501を設けてもよい。なお、この場合には、信号書き込み動作が完了したら、第1のスイッチ102と第2のスイッチ103とを同時にオフにするか、第2のスイッチ103を第1のスイッチ102より先にオフにする。第1のスイッチ102がオフした後も第2のスイッチ103がオンしているとトランジスタ101を介して容量素子104に蓄積した電荷が放電してしまうからである。

【0113】

また、図5に示す構成の場合において、V4=Vcomであれば、図49に示すように第4の配線109と表示素子105の対向電極110とを第6の配線4901で接続してもよい。

【0114】

また、図1や図2の画素において、第4の配線109を他の行の画素の第1の配線106で代用することができる。つまり、その場合には、図4に示す表示装置のバイアス線B1〜Bnを省略することができる。一例として、図2の画素の第4の配線109を省略し、隣の行の画素の第1の配線106で代用した場合の構成を図13に示す。

【0115】

また、図14に示すように、図5の画素の第1のスイッチ102、第2のスイッチ103にNチャネル型トランジスタである第1のスイッチングトランジスタ201、第2のスイッチングトランジスタ202をそれぞれ適用し、第4の配線109を他の行の画素の第5の配線501で代用することもできる。

【0116】

また、図15に示すように、図5の画素の第1のスイッチ102及び第2のスイッチ103にNチャネル型トランジスタである第1のスイッチングトランジスタ201、第2のスイッチングトランジスタ202をそれぞれ適用し、第4の配線109を他の行の画素の第1の配線106で代用することもできる。

【0117】

また、図20に示すように、図1の画素の第1のスイッチ102及び第2のスイッチ103にPチャネル型トランジスタである第1のスイッチングトランジスタ2001、第2のスイッチングトランジスタ2002をそれぞれ適用し、第3の配線108を他の行の画素の第1の配線106で代用することもできる。

【0118】

(実施の形態2)

トランジスタを用いて画素を構成する場合の問題の一つとして、画素間のトランジスタ特性のバラツキがある。このトランジスタ特性のバラツキは表示ムラとして認識されてしまう。

【0119】

そこで、本実施の形態では、本発明の画素において、使用するトランジスタ(オンにするトランジスタ)を期間毎に切り替えることにより、トランジスタ特性を時間的に平均化し、表示ムラを認識されにくくすることが可能とした場合について説明する。

【0120】

本実施の形態の画素を図6に示す。

【0121】

本実施の形態の画素は、第1のトランジスタ601、第2のトランジスタ611、第1のスイッチ602、第2のスイッチ603、第3のスイッチ612、第4のスイッチ613、容量素子604、表示素子605、第1の配線606、第2の配線607、第3の配線608及び第4の配線609を有する。なお、第1のトランジスタ601及び第2のトランジスタ611はNチャネル型のトランジスタである。

【0122】

まず、画素の接続構造について説明する。

【0123】

第1のトランジスタ601は、第1端子(ソース端子又はドレイン端子)が表示素子605の画素電極に接続され、第2端子(ソース端子又はドレイン端子)が第3のスイッチ612を介して第3の配線608に接続され、ゲート端子が第2のスイッチ603を介して第4の配線609と接続されている。つまり、第3のスイッチ612がオンしているとき、第1のトランジスタ601の第2端子と第3の配線608とが導通しており、第3のスイッチ612がオフしているとき、第1のトランジスタ601の第2端子と第3の配線608とが非導通となっている。また、第2のスイッチ603がオンしているとき、第1のトランジスタ601のゲート端子と第4の配線609とが導通しており、第2のスイッチ603がオフしているとき、第1のトランジスタ601のゲート端子と第4の配線609とが非導通となっている。

【0124】

また同様に、第2のトランジスタ611が第1のトランジスタ601と並列に接続されている。つまり、第2のトランジスタ611は、第1端子(ソース端子又はドレイン端子)が表示素子605の画素電極に接続され、第2端子(ソース端子又はドレイン端子)が第4のスイッチ613を介して第3の配線608に接続され、ゲート端子が第2のスイッチ603を介して第4の配線609と接続されている。つまり、第4のスイッチ613がオンしているとき、第2のトランジスタ611の第2端子と第3の配線608とが導通しており、第4のスイッチ613がオフしているとき、第2のトランジスタ611の第2端子と第3の配線608とが非導通となっている。また、第2のスイッチ603がオンしているとき、第2のトランジスタ611のゲート端子と第4の配線609とが導通しており、第2のスイッチ603がオフしているとき、第2のトランジスタ611のゲート端子と第4の配線609とが非導通となっている。

【0125】

また、第1のトランジスタ601の第1端子及び第2のトランジスタ611の第1端子は、第1のスイッチ602を介して第2の配線607と接続されている。つまり、第1のスイッチ602がオンしているとき、第1のトランジスタ601の第1端子及び第2のトランジスタ611の第1端子と、第2の配線607とが導通しており、第1のスイッチ602がオフしているとき、第1のトランジスタ601の第1端子及び第2のトランジスタ611の第1端子と、第2の配線607とが非導通となっている。

【0126】

また、第1のトランジスタ601のゲート端子と第2のトランジスタ611のゲート端子とは接続され、第1のトランジスタ601のゲート端子及び第2のトランジスタ611のゲート端子と、第1のトランジスタ601の第1端子及び第2のトランジスタ611の第1端子との間に容量素子604が接続されている。つまり、容量素子604の第1電極が第1のトランジスタ601のゲート端子及び第2のトランジスタ611のゲート端子に接続され、第2電極が第1のトランジスタ601の第1端子及び第2のトランジスタ611の第1端子に接続されている。なお、容量素子604は、配線や活性層や電極等により絶縁膜を挟んだ構成のものでもいいし、第1のトランジスタ601のゲート容量や第2のトランジスタ611のゲート容量を用いて省略することもできる。

【0127】

なお、表示素子605の対向電極610や、第3の配線608や第4の配線609にはそれぞれ所定の電位が入力されている。

【0128】

また、第1の配線606に信号を入力することにより、第1のスイッチ602と第2のスイッチ603のオンオフが制御される。

【0129】

また、第2の配線607には、画素の階調にしたがった信号が入力される。この信号は、ビデオ信号に相当し、信号電流が配線607に流れる。

【0130】

なお、第1のスイッチ602、第2のスイッチ603、第3のスイッチ612及び第4のスイッチ613にはトランジスタを適用することができる。よって、第1のスイッチ602と第2のスイッチ603にNチャネル型のトランジスタを適用することもできる。

【0131】

続いて、図6の画素の動作について説明する。

【0132】

なお、画素の動作には、画素へ信号の書き込みを行う信号書き込み動作と、画素に書き込まれた信号にしたがった階調の発光をする発光動作がある。そして、本実施の形態に示す画素は、使用するトランジスタ(オンにするトランジスタ)を、ある期間の信号書き込み動作時及び発光動作時と、別の期間の信号書き込み動作時及び発光動作時とで切り替える。

【0133】

図7(A)は、ある期間の信号書き込み動作を説明する図であり、図7(B)はそのときの発光動作を説明する図である。また、図7(C)は、別の期間の信号書き込み動作を説明する図であり、図7(D)はそのときの発光動作を説明する図である。なお、第2の配線607に接続された電流源701は、この画素に書き込む信号電流を設定する。そして、第2配線607は電流源701を介して配線702と接続されている。配線702には、所定の電位が入力されている。ここで、第3の配線608に入力する電位をV3、第4の配線609に入力する電位をV4、配線702に入力する電位をV5、対向電極610に入力する電位をVcomとする。そして、電位の関係は少なくとも、V3>Vcom>V5とする。

【0134】

また、図7(A)は、ある期間の信号書き込み動作時の定常状態となったときの画素の状態と、そのときの電流の流れを示している。第1のスイッチ602と第2のスイッチ603と第4のスイッチ613がオンし、第3のスイッチ612がオフしている。このときは、第2のトランジスタ611を使用している。つまり、電流源701によって設定された信号電流Idataが第3の配線608から第4のスイッチ613を介して第2のトランジスタ611に流れている。つまり、このとき、第2のトランジスタ611は信号電流Idataが流れるだけのゲートソース間電圧となっており、その電圧分の電荷が容量素子604に蓄積されている。

【0135】

よって、発光動作時は第1のスイッチ602と第2のスイッチ603と第3のスイッチ612がオフし、第4のスイッチ613がオンし、図7(B)に示すように電流が流れる。つまり、第3の配線608から第4のスイッチ613及び第2のトランジスタ611を介して表示素子605に電流が流れる。この電流は信号電流Idataと概略等しいものとなる。

【0136】

しかし、第2のトランジスタ611のドレイン・ソース間電圧が信号書き込み動作時と発光動作時とで異なるので、第2のトランジスタ611に流れる電流の大きさもわずかな違いが生じてしまう。そして、画素毎に第2のトランジスタ611の特性のバラツキがあると、表示ムラとして認識されてしまう。

【0137】

そこで、別の期間においては、信号書き込み動作時に、第1のスイッチ602と第2のスイッチ603と第3のスイッチ612とをオンにし、第4のスイッチ613をオフにする。図7(C)はこの期間の定常状態となったときの画素の状態と、そのときの電流の流れを示している。このときは、第1のトランジスタ601を使用している。つまり、電流源701によって設定された信号電流Idataが第3の配線608から第3のスイッチ612を介して第1のトランジスタ601に流れている。つまり、このとき、第1のトランジスタ601は信号電流Idataが流れるだけのゲートソース間電圧となっており、その電圧分の電荷が容量素子604に蓄積されている。

【0138】

よって、発光動作時は第1のスイッチ602と第2のスイッチ603と第4のスイッチ613がオフし、第3のスイッチ612がオンし、図7(D)に示すように電流が流れる。つまり、第3の配線608から第3のスイッチ612及び第1のトランジスタ601を介して表示素子605に電流が流れる。この電流は信号電流Idataと概略等しいものとなる。

【0139】

このように、使用するトランジスタを期間毎に切り替えることによって、トランジスタの特性を時間的に平均化することができる。よって、表示ムラを低減することができる。

【0140】

また、本実施の形態に示す画素には別の駆動方法を適用することもできる。例えば、信号書き込み動作時には大きな信号電流で書き込み、発光動作時に表示素子に流す電流を小さくする。そのような駆動法について以下に説明する。

【0141】

図8(A)は、信号書き込み動作を説明する図であり、図8(B)は発光動作を説明する図である。

【0142】

また、図8(A)は、信号書き込み動作時の定常状態となったときの画素の状態と、そのときの電流の流れを示している。第1のスイッチ602、第2のスイッチ603、第3のスイッチ612及び第4のスイッチ613がオンしている。図8(A)のように電流が流れる。つまり、電流の経路は、第3の配線608から第3のスイッチ612を介して第1のトランジスタ601に電流が流れる第1経路と、第3の配線608から第4のスイッチ613を介して第2のトランジスタ611に電流が流れる第2経路とがある。そして、第1経路に流れる電流I1と第2経路に流れる電流I2は、第1のトランジスタ601の第1端子と第2のトランジスタ611の第1端子との接続部で合流する。そして、信号電流Idataとして第1のスイッチ602及び電流源701を介して配線702に流れる。つまり、I1+I2=Idataとなる。

【0143】

発光動作について図8(B)を用いて説明する。第1のスイッチ602、第2のスイッチ603、及び第4のスイッチ613をオフにし、第3のスイッチ612をオンにする。すると、図8(B)のように電流が流れる。このとき、第2のスイッチ603がオフしているため、容量素子604は、第1のトランジスタ601と第2のトランジスタ611に流れる電流が信号電流Idataとなるのに必要なゲートソース間電圧Vgsを保持している。よって、トランジスタ601を介して表示素子605に電流が流れる。本構成によれば、この電流を調整することができる。

【0144】

ここで、トランジスタのチャネル長L、チャネル幅Wとする。すると、トランジスタが飽和領域で動作するとき、ゲートソース間電圧が一定であれば、一般的にトランジスタに流れる電流値はW/Lに比例する。つまり、チャネル幅Wに比例し、チャネル長Lに反比例する。

【0145】

よって、第1のトランジスタ601のチャネル幅W1、第2のトランジスタ611のチャネル幅W2とし、これらのトランジスタのチャネル長を等しいとする。そして、図8(A)において電流の流れている第1のトランジスタ601と第2のトランジスタ611とを一つのトランジスタであると仮定すると、チャネル幅(W1+W2)、チャネル長Lとみなすことができる。そして、図8(B)においては、第1のトランジスタ601にのみ電流が流れており、そのトランジスタはチャネル幅W1、チャネル長Lとなっている。したがって、発光動作のときには、Idata×(W1/(W1+W2))の電流を表示素子605に流すことができる。

【0146】

このように、第1のトランジスタ601や第2のトランジスタ611のチャネル幅やチャネル長を調整することにより、信号書き込み動作に流す信号電流より小さい電流を表示素子605に流すことができる。

【0147】

また、チャネル幅W1とチャネル幅W2とを等しくして、ある期間毎において、発光動作のとき使用するトランジスタを切り替えることにより、トランジスタの特性を時間的に平均化することもできる。

【0148】

また、信号書き込み動作時と、発光動作時に使用するトランジスタを切り替えることにより、信号書き込み動作時と、発光動作時に使用するトランジスタのチャネル幅Wとチャネル長Lとの比W/Lを調整して表示素子へ流す電流の大きさを調整してもよい。

【0149】

つまり、信号書き込み動作時には、図9(A)に示すように、第1のスイッチ602、第2のスイッチ603及び第4のスイッチ613をオンにし、第3のスイッチ612をオフにする。そして、第3の配線608から第4のスイッチ613を介して第2のトランジスタ611に信号電流Idataを流す。そして、発光動作時には、第1のスイッチ602、第2のスイッチ603及び第4のスイッチ613をオフにし、第3のスイッチ612をオンにする。すると、第1のトランジスタ601には、Idata×(W1/W2)の電流が流れる。なお、このときW1<W2であれば発光動作時に表示素子605に流す電流をIdataより小さくすることができる。

【0150】

このように、信号書き込み動作時に大きな電流で書き込むことにより、信号電流の流れる経路において、寄生容量が形成されていたとしても素早く信号の書き込みを行うことができるため、表示不良を防止することができる。

【0151】

なお、発光動作に表示素子に流す電流を、信号書き込み動作に流す信号電流より小さくする場合について説明したが、場合によっては、逆に、発光動作に表示素子に流す電流を信号電流より大きくしてもよい。例えば、信号書き込み動作時に第1のトランジスタ601又は第2のトランジスタ611のいずれかに電流を流すようにし、発光動作時には、第1のトランジスタ601及び第2のトランジスタ611の両方に電流を流すようにしてもよい。また、図9において、W1>W2であれば発光動作時に表示素子605に流す電流をIdataより大きくすることができる。

【0152】

また、本実施の形態の画素において、プリチャージ動作を行ってもよい。そのときの動作を図10を用いて説明する。この場合には、電流源701は第5のスイッチ1003を介して第2の配線607と接続されている。また、第2の配線607はさらに第6のスイッチ1004とプリチャージ用電流源1001を介して配線1002と接続されている。なお、プリチャージ用電流源1001は電流源701より大きな電流を設定することができるものを用いる。また、配線1002には、所定の電位が入力されている。この配線702と配線1002は共通の配線を用いてもいいし、別の配線であってもよい。

【0153】

まず、図10(A)はプリチャージ動作時において定常状態となったときの画素の状態と、そのときの電流の流れを示している。第1のスイッチ602、第2のスイッチ603、第3のスイッチ612、第4のスイッチ613及び第6のスイッチ1004をオンにし、第5のスイッチ1003をオフにする。すると、プリチャージ用電流源1001により設定される電流が、第3の配線608から第3のスイッチ612を介して第1のトランジスタ601と、第3の配線608から第4のスイッチ613を介して第2のトランジスタ611とに流れる。こうして、容量素子604に電荷を蓄積しておく。

【0154】

そして、設定動作時には、第1のスイッチ602、第2のスイッチ603、第3のスイッチ612及び第5のスイッチ1003をオンにし、第4のスイッチ613及び第6のスイッチ1004をオフにする。すると、定常状態には、図10(B)のように電流が流れる。つまり、第3の配線608から第1のトランジスタ601に電流源701によって設定された信号電流Idataが流れる。そして、第1のトランジスタ601に信号電流Idataを流すのに必要なゲートソース間電圧分の電荷が容量素子604に蓄積される。

【0155】

なお、プリチャージ用電流源1001に流す電流、第1のトランジスタ601のチャネル長L1及びチャネル幅W1、並びに第2のトランジスタ611のチャネル長L2及びチャネル幅W2などを適宜定めることにより、プリチャージ動作時と、設定動作時に容量素子604に蓄積する電荷をほぼ等しいものにすることができ、素早く信号電流を画素へ書き込むことができるようになる。

【0156】

なお、図10では、プリチャージ動作時に第1のトランジスタ601及び第2のトランジスタ611に電流を流すようにしたが、いずれか一方にのみ流すようにしてもよい。そして、設定動作時には、他方のトランジスタに電流を流すようにしてもよい。

【0157】

なお、上述したように、第1のトランジスタ601の第2端子と第3の配線608との間に第3のスイッチ612、第2のトランジスタ611の第2端子と第3の配線608との間に第4のスイッチ613が接続されている構成に限られず、図18に示すような構成であってもよい。つまり、第1のトランジスタ601は、第1端子(ソース端子又はドレイン端子)が第3のスイッチ1801を介して表示素子605の画素電極に接続され、第2端子(ソース端子又はドレイン端子)が第3の配線608に接続されている。つまり、第3のスイッチ1801がオンしているとき、第1のトランジスタ601の第1端子と表示素子605の画素電極とが導通しており、第3のスイッチ1801がオフしているとき、第1のトランジスタ601の第1端子と表示素子605の画素電極とが非導通となっている。また同様に、第2のトランジスタ611が第1のトランジスタ601と並列に接続されている。つまり、第2のトランジスタ611は、第1端子(ソース端子又はドレイン端子)が第4のスイッチ1802を介して表示素子605の画素電極に接続され、第2端子(ソース端子又はドレイン端子)が第3の配線608に接続されている。つまり、第4のスイッチ1802がオンしているとき、第2のトランジスタ611の第1端子と表示素子605の画素電極とが導通しており、第4のスイッチ1802がオフしているとき、第2のトランジスタ611の第1端子と表示素子605の画素電極とが非導通となっている。

【0158】

なお、本実施の形態においても、信号書き込み動作時に、電流を流すトランジスタのゲート端子を所定の電位にすることができることから、表示素子の画素電極の電位と対向電極との電位差が、表示素子の順方向しきい値電圧以下にすることができるため、信号書き込み動作時に表示素子へ電流を流さないようにすることができる。

【0159】

また、本実施の形態においても、第1のスイッチ602や、第2のスイッチ603や、第3のスイッチ612や、第4のスイッチ613をNチャネル型のトランジスタにすることにより、単極性のトランジスタで画素を構成することができるため、製造工程の簡略化を図ることができる。よって、製造コストの削減や歩留まりの向上を図ることができる。また。Nチャネル型のトランジスタのみで画素を構成することができることから、画素を構成するトランジスタの半導体層にアモルファス半導体やセミアモルファス半導体(若しくは微結晶半導体ともいう)などを用いることができる。例えば、アモルファス半導体として、アモルファスシリコン(a−Si:H)が挙げられる。よって、さらなる製造工程の簡略化を図ることが可能である。したがって、製造コストの削減や歩留まりの向上を図ることができる。

【0160】

(実施の形態3)

本実施の形態では、本発明の画素を構成するトランジスタにPチャネル型トランジスタを適用した場合について図11を用いて説明する。

【0161】

本実施の形態に示す画素は、トランジスタ1101、第1のスイッチングトランジスタ1102、第2のスイッチングトランジスタ1103、容量素子1104、表示素子1105、第1の配線1106、第2の配線1107、第3の配線1108及び第4の配線1109を有する。なお、トランジスタ1101、第1のスイッチングトランジスタ1102及び第2のスイッチングトランジスタ1103はPチャネル型のトランジスタである。

【0162】

まず、画素の接続構造について説明する。

【0163】

トランジスタ1101は、第1端子(ソース端子又はドレイン端子)が表示素子1105の画素電極に接続され、第2端子(ソース端子又はドレイン端子)が第3の配線1108に接続され、ゲート端子が第2のスイッチングトランジスタ1103を介して第4の配線1109と接続されている。つまり、第2のスイッチングトランジスタ1103がオンしているとき、トランジスタ1101のゲート端子と第4の配線1109とが導通しており、第2のスイッチングトランジスタ1103がオフしているとき、トランジスタ1101のゲート端子と第4の配線1109とが非導通となっている。第2のスイッチングトランジスタ1103はゲート端子が第1の配線1106に接続され、第1端子(ソース端子又はドレイン端子)がトランジスタ1101のゲート端子に接続され、第2端子(ソース端子又はドレイン端子)が第4の配線1109と接続されている。よって、第1の配線1106に入力される信号がHレベルのときに第2のスイッチングトランジスタ1103はオンし、第1の配線1106に入力される信号がLレベルのときに第2のスイッチングトランジスタ1103はオフする。

【0164】

また、トランジスタ1101の第1端子は、第1のスイッチングトランジスタ1102を介して第2の配線1107と接続されている。つまり、第1のスイッチングトランジスタ1102がオンしているとき、トランジスタ1101の第1端子と第2の配線1107とが導通しており、第1のスイッチングトランジスタ1102がオフしているとき、トランジスタ1101の第1端子と第2の配線1107とが非導通となっている。第1のスイッチングトランジスタ1102はゲート端子が第1の配線1106に接続され、第1端子(ソース端子又はドレイン端子)が第2の配線1107に接続され、第2端子(ソース端子又はドレイン端子)が表示素子1105の画素電極及びトランジスタ1101の第1端子と接続されている。よって、第1の配線1106に入力される信号がHレベルのときに第1のスイッチングトランジスタ1102はオンし、第1の配線1106に入力される信号がLレベルのときに第1のスイッチングトランジスタ1102はオフする。

【0165】

また、トランジスタ1101のゲート端子と第1端子の間に容量素子1104が接続されている。つまり、容量素子1104の第1電極がトランジスタ1101のゲート端子に接続され、第2電極がトランジスタ1101の第1端子に接続されている。なお、容量素子1104は、配線や活性層や電極等により絶縁膜を挟んだ構成のものでもいいし、トランジスタ1101のゲート容量を用いて省略することもできる。

【0166】

なお、表示素子1105の対向電極1110や、第3の配線1108や第4の配線1109にはそれぞれ所定の電位が入力されている。

【0167】

また、第1の配線1106に信号を入力することにより、第1のスイッチングトランジスタ1102と第2のスイッチングトランジスタ1103のオンオフが制御される。

【0168】

また、第2の配線1107には、画素の階調にしたがった信号が入力される。この信号は、ビデオ信号に相当し、信号電流が第2の配線1107に流れる。

【0169】

続いて、本実施の形態に示す画素の動作について図12(A)、(B)、(C)を用いて説明する。

【0170】

なお、第2の配線1107に接続された電流源1201は、この画素に書き込む信号電流Idataを設定する。そして、第2の配線1107は電流源1201を介して配線1202と接続されている。配線1202には、所定の電位が入力されている。ここで、第3の配線1108に入力する電位をV3、第4の配線1109に入力する電位をV4、配線1202に入力する電位をV5、対向電極1110に入力する電位をVcomとする。そして、電位の関係は少なくとも、V3<Vcom<V5とする。

【0171】

なお、画素の動作には、画素へ信号の書き込みを行う信号書き込み動作と、画素に書き込まれた信号にしたがった階調の発光をする発光動作がある。図12(A)、及び図12(B)は、共に信号書き込み動作を説明する図であり、図12(C)は発光動作を説明する図である。

【0172】

まず、信号書き込み動作時の過渡状態について図12(A)を用いて説明する。第1の配線1106に入力する信号をLレベルにして、第1のスイッチングトランジスタ1102と第2のスイッチングトランジスタ1103をオンにする。すると、図12(A)のように電流が流れる。つまり、電流源1201で設定される電流Idataが、容量素子1104と、トランジスタ1101とに流れる。つまり、容量素子1104には電流Ic、トランジスタ1101には電流Itrの電流が流れるとすると、Ic+Itr=Idataとなる。

【0173】

やがて、容量素子1104へは電流が流れなくなる。このとき、信号書き込み動作時の定常状態となり、図12(B)のように電流が流れる。そして、トランジスタ1101に流れる電流Itrが、信号電流Idataと等しくなっている。つまり、トランジスタ1101のゲートソース間電圧Vgsは、トランジスタ1101に信号電流Idataを流すのに必要な電圧となっている。そして、このトランジスタ1101のゲートソース間電圧Vgs分の電荷が容量素子1104に蓄積されている。

【0174】

なお、このときのトランジスタ1101のゲート端子の電位をVa、第1端子の電位をVbとすると、Vgs=(Va−Vb)である。そして、表示素子1105の順方向しきい値電圧VELthとしたとき、(Vcom−Vb)<VELthとなるようにすると信号書き込み動作時に表示素子1105へ電流を流さなくすることができる。そのため、第4の配線1109に入力する電位V4は、V3<V4<V5となるようにするとよい。また、V4=Vcomとすることにより、画素へ必要な電源数を減らすことができる。また、信号書き込み時に表示素子1105へ逆方向バイアスを印加することができる。

【0175】

なお、逆方向バイアスを表示素子1105に印加しても、正常な表示素子1105には電流は流れない(若しくは流れたとしても微少な電流である)。一方、表示素子1105に短絡箇所が有る場合には、その短絡箇所に電流が流れる。そして、短絡箇所を絶縁化する。よって、表示不良を改善することができる。

【0176】

続いて、発光動作について図12(C)を用いて説明する。第1の配線1106に入力する信号をHレベルにして、第1のスイッチングトランジスタ1102と第2のスイッチングトランジスタ1103とをオフにする。すると、図12(C)のように電流が流れる。このとき、第2のスイッチングトランジスタ1102がオフしているため、容量素子1104は、トランジスタ1101に信号電流Idataを流すのに必要なゲートソース間電圧Vgsを保持する。よって、トランジスタ1101に信号電流Idataとほぼ等しい電流が流れる。

【0177】

なお、このときのトランジスタ1101のゲート端子の電位をVa’、第1端子の電位をVb’とすると、Vgs=(Va’−Vb’)である。なぜなら、Vb’>Vbとなるが、容量素子1104はゲートソース間電圧Vgsを保持しているため、Vb’が上昇するとともにVa’も上昇するからである。

【0178】

なお、第1の配線1106に入力するLレベルの信号の電位をV1(L)、Hレベルの信号の電位をV1(H)とすると次のような電位にすることが望ましい。なお、第1のスイッチングトランジスタ1102のしきい値電圧をVth1、第2のスイッチングトランジスタ1103のしきい値電圧をVth2とする。

【0179】

図12(B)で示したように、表示素子1105の画素電極の電位はVbとなっても、第1のスイッチングトランジスタ1102をオンにしておく必要がある。そのためV1(L)<Vb+Vth1とする。また、第2のスイッチングトランジスタ1103をオンにしておくためV1(L)<V4+Vth2とする。具体的には、例えば、V4=Vcomのときには、V1(L)はVcomより1〜8V低い電位であるとよい。

【0180】

また、図12(C)で示したように、第1のスイッチングトランジスタ1102がオフするためには、V1(H)>(Vb+Vth1)とする。つまり、他の画素へ信号電流の書き込みを行っているときに、第2の配線1107の電位はVbとなるため、この電位になったときにも選択しない画素は第1のスイッチングトランジスタ1102がオフしている必要があるからである。また、第2のスイッチングトランジスタ1103がオフにしておくため、V1(H)>(V4+Vth2)とする。具体的には、例えば、V4=Vcomのときには、V1(H)はVcomより1〜8V高い電位であるとよい。

【0181】

よって、本実施の形態に示した画素構成によれば、信号書き込み動作時のトランジスタのゲート端子の電位を制御することにより、信号書き込み動作時に表示素子へ電流が流れてしまうのを防ぐことができる。

【0182】

また、図12に示した画素構成によれば、Pチャネル型のトランジスタのみで画素を構成することができるため、製造工程の簡略化を図ることができる。

【0183】

また、本発明の構成によれば、信号書き込み動作時に|Vds|>|Vgs|にすることができ、信号書き込み動作時と発光動作時とでVdsの変動を小さくすることができ、トランジスタ1101の飽和領域での定電流特性(電流のフラット性)が悪くても、信号書き込み動作時と発光動作時との電流値をほぼ等しくすることができる。特に、トランジスタ1101の半導体層に非晶質半導体膜(例えばアモルファスシリコン)を用いると飽和領域での定電流特性(電流のフラット性)が悪くなってしまう場合がある。よって、トランジスタ1101の半導体層に非晶質半導体膜を用いている場合に本発明の構成を適用すれば表示不良を防止することができる。

【0184】

(実施の形態4)

本実施の形態では、特に信号書き込み動作時と発光動作時のトランジスタのソースドレイン間電圧を小さくするための駆動方法を説明する。

【0185】

図1の画素を用いて説明する。画素の接続構造については、実施の形態1で説明したのでここではその説明を省略する。

【0186】

本実施の形態においては、信号書き込み動作時において、発光動作時よりも対向電極110の電位を高くする。そのときの対向電極110の電位は、信号書き込み動作時に表示素子105に順方向電流が流れないような電位であればよく、第3の配線108と同じでもいいし、第3の配線108よりも高い電位であってもよい。

【0187】

さらに、信号書き込み動作時には、第1の配線106に信号を入力して第1のスイッチ102と第2のスイッチ103とをオンにする。そして、第2の配線107に流れる信号電流Idataがトランジスタ101に流れるようになるだけのゲートソース間電圧分の電荷を容量素子104に蓄積する。

【0188】

なお、このとき、トランジスタ101のゲート端子の接続された第4の配線109の電位を所定の電位にしておく。

【0189】

次に、発光動作時には、第1の配線106に信号を入力して第1のスイッチ102と第2のスイッチ103とをオフにする。また、対向電極110の電位を信号書き込み動作時よりも低くする。

【0190】

すると、容量素子104はトランジスタ101に信号電流Idataが流れるだけのゲートソース間電圧を保持しているので、トランジスタ101に信号電流Idataとほぼ等しい電流が流れる。そして、その電流が表示素子105に流れる。

【0191】

このときの表示素子105の画素電極の電位は、対向電極110の電位よりも高くなる。つまり、トランジスタ101のソース端子の電位は対向電極110の電位よりも高くなる。

【0192】

よって、書き込み動作時にトランジスタ101のゲート端子に入力する電位を供給する第4の配線109の電位と、発光動作時に表示素子105の対向電極110に入力する電位とを適宜設定することにより、信号書き込み動作時と発光動作時のトランジスタ101の第1端子の電位の変動を小さくすることができる。つまり、トランジスタ101の第2端子の電位には所定の電位が入力されていることから、トランジスタ101の第1端子の電位を制御することにより、信号書き込み動作時と発光動作時において、トランジスタ101のドレイン・ソース間電圧の変動を小さくすることができる。

【0193】

よって、トランジスタ101の飽和領域での定電流特性(電流のフラット性)が悪くなっても、信号書き込み動作時と発光動作時とで電流値の変動を小さくすることができるので、表示ムラを低減することができる。特に、画素のトランジスタの半導体層に非晶質半導体(例えばアモルファスシリコン)を用いている場合に定電流特性(電流のフラット性)が悪くなることが多いので、本実施の形態の駆動方法を適用すれば表示不良を防止することができる。

【0194】

また、信号電流の大きさに合わせて画素の列毎に、第4の配線109に入力する電位を設定するのであれば、信号書き込み動作時と発光動作時とでトランジスタ101のドレイン・ソース間電圧の変動をより減らすことができる。よって、トランジスタ101を線形領域で動作させてもよい。

【0195】

(実施の形態5)

本実施の形態では、本発明の画素の適用可能な表示装置の駆動方法の一形態について図40に示すタイミングチャートを用いて説明する。また、そのときの駆動方法が適用可能な本発明の画素構成について説明する。

【0196】

横方向は時間経過を表し、縦方向は走査線の走査行数を表している。

【0197】

画像表示を行うとき、書き込み動作と発光動作とが繰り返し行われる。一画面(1フレーム)分の書き込み動作と発光動作を行う期間を1フレーム期間という。1フレーム分の信号の処理について特に限定はないが、画像をみる人がちらつき(フリッカ)を感じないように少なくとも1秒間に60回程度とすることが好ましい。

【0198】

本実施の形態の表示装置は書き込み動作によって、画素毎の階調に従ったビデオ信号が画素に書き込まれる。つまりアナログの信号が画素に書き込まれる。このビデオ信号は信号電流である。

【0199】

そして、発光期間において、そのビデオ信号を保持することによって階調を表現する。ここで、本実施の形態の画素を有する表示装置は、消去動作により、画素に書き込まれた信号を消去する。すると、次のフレーム期間までは消去期間が設けられる。つまり、黒表示が挿入されることにより残像が見えにくくなる。こうして、動画特性の向上を図ることができる。

【0200】

本実施の形態の駆動方法が適用可能な画素構成について説明する。そのため、本実施の形態の画素としては、走査することにより画素を強制的に非点灯にする手段を有していればよい。そのような手段としては、例えば図1に示す画素であれば、第3の配線108からトランジスタ101を介して表示素子105の対向電極110までの間の電流の経路を非導通にすればよい。

【0201】

そのためには大きく分けて二つの方法がある、一つ目の方法としては、第3の配線108からトランジスタ101を介して表示素子105の対向電極110までの間の電流の経路に新たにスイッチを設ける。そして、画素の一行ずつ走査してそのスイッチをオフにすることにより、第3の配線108からトランジスタ101を介して表示素子105の対向電極110までの間の電流の経路を非導通にする。

【0202】

そのような構成の一例を図42に示す。なお、図1の画素と共通するところは共通の符号を用いてその説明を省略する。

【0203】

図42の構成では、図1の構成において、トランジスタ101の第2端子と第3の配線108との間に第3のスイッチ4201が接続されている。そして、第3のスイッチ4201のオンオフは第5の配線4202に入力される信号によって制御される。なお、スイッチを設ける箇所は図42の構成に限られず、トランジスタ101の第1端子と表示素子105の画素電極との接続点をノード4203とすると、ノード4203とトランジスタ101の第1端子との間にスイッチを接続してもいいし、ノード4203と表示素子105の画素電極との間にスイッチを接続してもいい。

【0204】

また、二つ目の方法としては、画素の一行ずつ走査してトランジスタ101を強制的にオフにする。そのため、容量素子104に蓄積した電荷を放電する手段を有しているか、または、トランジスタ101のゲート端子に電位を入力する手段を有している必要がある。

【0205】

まず、容量素子104に蓄積した電荷を放電する手段を有している画素の一例を図38に示す。なお、図1の画素と共通するところは共通の符号を用いてその説明を省略する。図38では、容量素子104と並列に第3のスイッチ3801が接続されている。そして、第3のスイッチ3801のオンオフは第5の配線3802に入力される信号によって制御される。つまり、第3のスイッチ3801がオンするとトランジスタ101のゲートと第1端子間が短絡する。すると、容量素子104で保持されていたトランジスタ101のゲートソース間電圧を0Vにすることができる。こうして、トランジスタ101をオフにすることができる。

【0206】

なお、図5の構成や図49の構成によっても画素の一行ずつ走査して容量素子104に蓄積した電荷を放電することができる。その場合には、第5の配線501に供給する信号により第2のスイッチ103をオンにする。第1のスイッチ102をオフにした状態で第2のスイッチ103をオンにすると、トランジスタ101を介して容量素子104に蓄積された電荷を放電し、トランジスタ101をオフにすることができる。

【0207】

また、トランジスタ101のゲート端子に電位を入力する手段を有している画素の一例を図39に示す。なお、図1の画素と共通するところは共通の符号を用いてその説明を省略する。図39では、トランジスタ101のゲート端子と第5の配線3902との間に整流素子3901を接続する。なお、整流素子3901は、トランジスタ101のゲート端子から第5の配線3902に電流が流れる方向を順方向電流とするように接続されている。第5の配線3902はトランジスタ101を強制的にオフにするときだけLレベルの信号が入力され、それ以外はHレベルの信号を入力する。すると、第5の配線3902がHレベルのときには、整流素子3901には電流が流れず、Lレベルになるとトランジスタ101から第5の配線3902へ電流が流れる。そして、トランジスタ101のゲート端子の電位は第5の配線3902のLレベルの電位から整流素子3901の順方向しきい値電圧分高い電位となる。このときトランジスタ101を介して容量素子104の第2電極にも電荷が蓄積される。そして、トランジスタ101の第1端子の電位も高くなる。こうしてトランジスタ101を強制的にオフにすることができる。

【0208】

また、ゲート端子に電位を入力する手段を有している画素の他の例として、図5の画素構成でもよい。その場合には、第5の配線501に信号を入力して第2のスイッチ103をオンにすれば、トランジスタ101を介して容量素子104の第2電極に電荷が蓄積され、トランジスタ101はオフする。

【0209】

また、ゲート端子に電位を入力する手段を有している画素の他の例を図41に示す。なお、図1の画素と共通するところは共通の符号を用いてその説明を省略する。図41では、トランジスタ101のゲート端子と表示素子105の対向電極110との間に第3のスイッチ4101が接続されている。第3のスイッチ4101と表示素子105の対向電極110とは配線4103で接続されている。なお、第3のスイッチ4101のオンオフは第5の配線4102に信号を入力することにより制御する。第5の配線4102に信号を入力して第3のスイッチ4101をオンにすれば、トランジスタ101を介して容量素子104の電荷が放電され、トランジスタ101はオフする。

【0210】

なお、図41のような画素を有する表示パネルの断面構造について図43を用いて説明する。

【0211】

基板4301上に下地膜4302を有している。基板4301としてはガラス基板、石英基板、プラスチック基板、セラミックス基板等の絶縁性基板、金属基板、半導体基板等を用いることができる。下地膜4302はCVD法やスパッタ法により形成することができる。例えばSiH4、N2O、NH3を原料に用いたCVD法により形成した酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を適用することができる。また、これらの積層を用いても良い。なお、下地膜4302は基板4301から不純物が半導体層に拡散することを防ぐために設けるものであり、基板4301にガラス基板や石英基板を用いている場合には下地膜4302は設けなくてもよい。

【0212】

下地膜4302上に島状の半導体層を有する。半導体層にはN型のチャネルが形成されるチャネル形成領域4303、ソース領域又はドレイン領域となる不純物領域4304、低濃度不純物領域(LDD領域)4305が形成されている。そして、チャネル形成領域4303上にゲート絶縁膜4306を介してゲート電極4307を有している。ゲート絶縁膜4306としてはCVD法やスパッタ法により形成される酸化珪素膜、窒化珪素膜、酸化窒化珪素膜等を用いることができる。また、ゲート電極4307としてはアルミニウム(Al)膜、銅(Cu)膜、アルミニウム又は銅を主成分とする薄膜、クロム(Cr)膜、タンタル(Ta)膜、窒化タンタル(TaN)膜、チタン(Ti)膜、タングステン(W)膜、モリブデン(Mo)膜等を用いることができる。

【0213】

ゲート電極4307の脇にはサイドウォール4322が形成されている。ゲート電極4307を覆うようにシリコン化合物、例えば、酸化シリコン膜、窒化シリコン膜若しくは酸化窒化シリコン膜を形成した後、エッチバックしてサイドウォール4322を形成することができる。

【0214】

なお、LDD領域4305はサイドウォール4322の下部に位置している。つまり、自己整合的にLDD領域4305が形成されている。なお、サイドウォール4322は、LDD領域4305を自己整合的に形成するために設けているのであって、必ずしも設けなくともよい。

【0215】

ゲート電極4307、サイドウォール4322およびゲート絶縁膜4306上には第1の層間絶縁膜を有している。第1の層間絶縁膜は下層に無機絶縁膜4318、上層に樹脂膜4308を有している。無機絶縁膜4318としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜又はこれらを積層した膜を用いることができる。樹脂膜4308としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

【0216】

第1の層間絶縁膜上には、第1の電極4309、第2の電極4324、第3の電極4320及び第4の電極4321を有し、第1の電極4309はコンタクトホールを介して不純物領域4304と電気的に接続されている。また、第2の電極4324はコンタクトホールを介して不純物領域4304と電気的に接続されている。また、第3の電極4320はコンタクトホールを介してゲート電極4307と電気的に接続されている。また、第4の電極4321は、コンタクトホールを介して不純物領域4304と電気的に接続されている。そして、第3の電極4320と第4の電極4321とは電気的に接続されている。第1の電極4309及び第2の電極4324としては、チタン(Ti)膜やアルミニウム(Al)膜や銅(Cu)膜やTiを含むアルミニウム膜をなどを用いることができる。なお、第1の電極4309、第2の電極4324、第3の電極4320及び第4の電極4321と同じ層に信号線などの配線を設ける場合には低抵抗な銅を用いるとよい。

【0217】

第1の電極4309、第2の電極4324、第3の電極4320、第4の電極4321および第1の層間絶縁膜上に第2の層間絶縁膜4310を有する。第2の層間絶縁膜4310としては、無機絶縁膜や、樹脂膜、又はこれらの積層を用いることができる。無機絶縁膜としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜又はこれらを積層した膜を用いることができる。樹脂膜としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

【0218】

第2の層間絶縁膜4310上には画素電極4311および配線4319を有している。画素電極4311および配線4319は同じ材料により形成されている。つまり、同じ層に同時に形成されている。画素電極4311や配線4319に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、窒化チタン(TiN)膜、クロム(Cr)膜、タングステン(W)膜、亜鉛(Zn)膜、プラチナ(Pt)膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。光を反射する金属膜を用いることで光を透過させない陽極を形成することができる。

【0219】

画素電極4311および配線4319の端部を覆うように絶縁物4312を有する。

例えば、絶縁物4312としては、ポジ型の感光性アクリル樹脂膜を用いることができる。

【0220】

画素電極4311上に有機化合物を含む層4313が形成され、有機化合物を含む層4313の一部は絶縁物4312上に重なっている。なお、有機化合物を含む層4313は、配線4319上には形成されていない。

【0221】

有機化合物を含む層4313、絶縁物4312および配線4319上に対向電極4314を有している。対向電極4314に用いる材料としては、仕事関数の小さい材料を用いることが望ましい。例えば、アルミニウム(Al)、銀(Ag)、リチウム(Li)、カルシウム(Ca)、若しくはこれらの合金又は、MgAg、MgIn、AlLi、CaF2、若しくはCa3N2などの金属薄膜を用いることができる。こうして薄い金属薄膜を用いることで光を透過させることが可能な陰極を形成することができる。

【0222】

対向電極4314と画素電極4311とにより有機化合物を含む層4313が挟まれた領域では発光素子4316が形成されている。

【0223】

また、絶縁物4312により有機化合物を含む層4313が隔離されている領域では、接合部4317が形成され、対向電極4314と配線4319とが接している。よって、配線4319が対向電極4314の補助電極として機能し、対向電極4314を低抵抗化することができる。よって、対向電極4314の膜厚を薄くすることができ、透過率を高くすることができる。したがって、発光素子4316から得られる光を上面から取り出す上面射出構造において、より高い輝度を得ることができる。

【0224】

なお、対向電極4314をより低抵抗化するため、金属薄膜と透明導電膜(例えば、ITO(インジウムスズ酸化物)、インジウム亜鉛酸化物(IZO)、酸化亜鉛(ZnO)等)との積層を用いてもよい。こうして薄い金属薄膜と、透明性を有する透明導電膜を用いることによっても光を透過させることが可能な陰極を形成することができる。

【0225】

つまり、トランジスタ4315が図41の画素のトランジスタ101であり、トランジスタ4323が図41の画素の第3のスイッチ4101の機能を果たすトランジスタである。また、対向電極4314が図41の画素における表示素子105の対向電極110である。また、配線4319が図41の画素における配線4103である。

【0226】

また、図43を用いて説明した構造の表示パネルは他の画素構造を有する場合にも適用することができる。例えば、トランジスタ4315が図48のトランジスタ101又は図49のトランジスタ101、トランジスタ4323が図48の第2のスイッチ103の機能を果たすトランジスタ又は図49の第2のスイッチ103として機能するトランジスタである。なお、電極4324が図48の第4の配線109又は図49の第4の配線109とし、配線4319が図48の第5の配線4801又は図49の第6の配線4901としてもよいし、配線4319が図48の第4の配線109及び第5の配線4801の機能を果たす配線、又は図49の第4の配線109及び第6の配線4901の機能を果たす配線としてもよい。

【0227】

なお、図43で説明した構造の表示パネルは対向電極4314の膜を薄くすることができ、上面から射出する光の透光性がよい。よって、上面からの輝度が高くすることができる。また、対向電極4314と配線4319を接続することにより、対向電極4314及び配線4319を低抵抗化することができる。よって、消費電力の低減を図ることができる。

【0228】

また、図2の画素構成を有する表示装置によっても、トランジスタ101を強制的にオフにすることが可能である。その場合の駆動方法を以下において説明する。

【0229】

図44に示すように、1水平期間を2つに分割する。ここでは、前半が書き込み時間、後半が消去時間として説明する。そして、分割された水平期間内で、各々の走査線を選択し、そのときに対応する信号を信号線に入力する。例えば、ある1水平期間において、前半はi行目を選択し、後半はj行目を選択する。すると、1水平期間において、あたかも同時に2行分を選択したかのように動作させることが可能となる。つまり、それぞれの1水平期間の前半の書き込み時間を用いて、書き込み時間Tb1〜Tb4に信号線から画素へビデオ信号を書き込む。そして、このときの1水平期間の後半の消去時間には画素を選択しない。また、別の1水平期間の後半の消去時間を用いて消去時間Teに信号線から画素へ消去信号を入力する。このときの1水平期間の前半の書き込み時間には画素を選択しない。このようにすることによって、開口率の高い画素を有する表示装置を提供することができ、歩留まりの向上を図ることができる。

【0230】

このような画素を有する表示装置の一例を図45に示す。信号線駆動回路4501、第1の走査線駆動回路4502、第2の走査線駆動回路4505、画素部4503を有し、画素部4503には画素4504が走査線G1〜Gmと信号線S1〜Snに対応してマトリクスに配置されている。第1の走査線駆動回路に4502には、パルス出力回路4506を有し、走査線G1〜Gmのそれぞれとパルス出力回路4506との間にスイッチ4508が接続されている。また、第2の走査線駆動回路に4505には、パルス出力回路4507を有し、走査線G1〜Gmのそれぞれとパルス出力回路4507との間にスイッチ4509が接続されている。

【0231】

なお、走査線Gi(走査線G1〜Gmのいずれか一)は図2の第1の配線106に相当し、信号線Sj(信号線S1〜Snのうちいずれか一)は図2の第2の配線107に相当する。

【0232】

第1の走査線駆動回路4502には、クロック信号(G_CLK)、クロック反転信号(G_CLKB)、スタートパルス信号(G_SP)、制御信号(WE)などの信号が入力される。そして、それらの信号にしたがって、選択する画素行の第1の走査線Gi(第1の走査線G1〜Gmのうちいずれか一)に画素を選択する信号を出力する。なお、このときの信号は図37のタイミングチャートに示すように1水平期間の前半に出力されるパルスである。そして、制御信号(WE)によってスイッチ4508のオンオフが制御され、パルス出力回路4506と走査線G1〜Gmとを導通又は非導通にすることができる。

【0233】

第2の走査線駆動回路4505には、クロック信号(R_CLK)、クロック反転信号(R_CLKB)、スタートパルス信号(R_SP)、制御信号(WE’)などの信号が入力される。そして、それらの信号にしたがって、選択する画素行の第2の走査線Ri(第2の走査線R1〜Rmのうちいずれか一)に信号を出力する。なお、このときの信号は図37のタイミングチャートに示すように1水平期間の後半に出力されるパルスである。そして、制御信号(WE’)によってスイッチ4509のオンオフが制御され、パルス出力回路4507と走査線G1〜Gmとを導通又は非導通にすることができる。なお、スイッチ4508とスイッチ4509とは一方が導通のとき他方は非導通となる。

【0234】

また、信号線駆動回路4501には、クロック信号(S_CLK)、クロック反転信号(S_CLKB)、スタートパルス信号(S_SP)、ビデオ信号(Digital Video Data)、制御信号(WE)などの信号が入力される。そして、それらの信号にしたがって、各信号線S1〜Snへそれぞれ各列の画素に応じたビデオ信号を出力する。

【0235】

よって、信号線S1〜Snに入力されたビデオ信号は、第1の走査線駆動回路4502から走査線Gi(走査線G1〜Gmのうちいずれか一)に入力された信号によって選択された画素行の各列の画素4504に書き込まれる。そして、各走査線G1〜Gmにより各画素行が選択され、全ての画素4504に各画素4504に対応したビデオ信号が書き込まれる。そして、各画素4504は書き込まれたビデオ信号のデータを一定期間保持する。各画素4504は、ビデオ信号のデータを一定期間保持することによって、点灯又は非点灯の状態を維持することができる。

【0236】

また、第2の走査線駆動回路4505から走査線Gi(走査線G1〜Gmのうちいずれか一)に入力された信号によって選択された画素行の各列の画素4504には、画素を非点灯とする信号(消去信号ともいう)が信号線S1〜Snから書き込まれる。そして、各走査線G1〜Gmにより各画素行を選択することで、非点灯期間を設定することができる。例えば、第2の走査線駆動回路4505から走査線Giに入力された信号によってi行目の画素が選択される時間は、信号線S1〜Snを、図2の画素の第4の配線109の電位と同じ電位とする。なお、このとき信号線S1〜Snをフローティングにしてもよい。

【0237】

したがって、本発明の表示装置によれば、ある画素行に着目して、その画素行にすでに入力されている信号が、これから入力しようとしている信号と同じであれば、その画素行には信号を入力しないようにすることができるので、走査線や信号線の充放電の回数を減らすことができ、消費電力の低減を図ることができる。

【0238】

(実施の形態6)

本実施の形態では、実施の形態1、実施の形態2及び実施の形態3で示した画素構成を有する表示パネルの構成について図22(a)、(b)を用いて説明する。

【0239】

なお、図22(a)は、表示パネルを示す上面図、図22(b)は図22(a)をA−A’で切断した断面図である。点線で示された信号線駆動回路2201、画素部2202、第1の走査線駆動回路2203、第2の走査線駆動回路2206を有する。また、封止基板2204、シール材2205を有し、シール材2205で囲まれた内側は、空間2207になっている。

【0240】

なお、配線2208は第1の走査線駆動回路2203、第2の走査線駆動回路2206及び信号線駆動回路2201に入力される信号を伝送するための配線であり、外部入力端子となるFPC(フレキシブルプリントサーキット)2209からビデオ信号、クロック信号、スタート信号等を受け取る。FPC2209と表示パネルとの接続部上にはICチップ(メモリ回路や、バッファ回路などが形成された半導体チップ)2219がCOG(Chip On Glass)等で実装されている。なお、ここではFPCしか図示されていないが、このFPCにはプリント配線基盤(PWB)が取り付けられていても良い。本明細書における表示装置とは、表示パネル本体だけでなく、それにFPCもしくはPWBが取り付けられた状態をも含むものとする。また、ICチップなどが実装されたものを含むものとする。

【0241】

次に、断面構造について図22(b)を用いて説明する。基板2210上には画素部2202とその周辺駆動回路(第1の走査線駆動回路2203、第2の走査線駆動回路2206及び信号線駆動回路2201)が形成されているが、ここでは、信号線駆動回路2201と、画素部2202が示されている。

【0242】

なお、信号線駆動回路2201はNチャネル型TFT2220やNチャネル型TFT2221のように単極性のトランジスタで構成されている。なお、画素構成には図2や図13や図14や図15の画素構成を適用することにより単極性のトランジスタで画素を構成することができる。よって、周辺駆動回路をNチャネル型トランジスタで構成すれば単極性表示パネルを作製することができる。もちろん、単極性のトランジスタだけでなくPチャネル型トランジスタも用いてCMOS回路を形成しても良い。また、本実施の形態では、基板上に周辺駆動回路を一体形成した表示パネルを示すが、必ずしもその必要はなく、周辺駆動回路の全部若しくは一部をICチップなどに形成し、COGなどで実装しても良い。その場合には駆動回路は単極性にする必要がなくPチャネル型トランジスタを組み合わせて用いることができる。

【0243】

また、画素部2202はTFT2211と、TFT2212とを有している。なお、TFT2212のソース電極は第1の電極(画素電極)2213と接続されている。また、第1の電極2213の端部を覆って絶縁物2214が形成されている。ここでは、ポジ型の感光性アクリル樹脂膜を用いることにより形成する。

【0244】

また、カバレッジを良好なものとするため、絶縁物2214の上端部または下端部に曲率を有する曲面が形成されるようにする。例えば、絶縁物2214の材料としてポジ型の感光性アクリルを用いた場合、絶縁物2214の上端部のみに曲率半径(0.2μm〜3μm)を有する曲面を持たせることが好ましい。また、絶縁物2214として、感光性の光によってエッチャントに不溶解性となるネガ型、或いは光によってエッチャントに溶解性となるポジ型のいずれも使用することができる。

【0245】

第1の電極2213上には、有機化合物を含む層2216、および第2の電極(対向電極)2217がそれぞれ形成されている。ここで、陽極として機能する第1の電極2213に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウムスズ酸化物)膜、インジウム亜鉛酸化物(IZO)膜、窒化チタン膜、クロム膜、タングステン膜、Zn膜、Pt膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。

【0246】

また、有機化合物を含む層2216は、蒸着マスクを用いた蒸着法、またはインクジェット法によって形成される。有機化合物を含む層2216には、元素周期律第4族金属錯体をその一部に用いることとし、その他、組み合わせて用いることのできる材料としては、低分子系材料であっても高分子系材料であっても良い。また、有機化合物を含む層に用いる材料としては、通常、有機化合物を単層もしくは積層で用いる場合が多いが、本実施の形態においては、有機化合物からなる膜の一部に無機化合物を用いる構成も含めることとする。さらに、公知の三重項材料を用いることも可能である。

【0247】

さらに、有機化合物を含む層2216上に形成される、陰極として機能する第2の電極2217に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、またはCa3N2)を用いればよい。なお、有機化合物を含む層2216で生じた光が第2の電極2217を透過させる場合には、第2の電極2217として、膜厚を薄くした金属薄膜と、透明導電膜(ITO(インジウムスズ酸化物)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)、酸化亜鉛(ZnO)等)との積層を用いるのが良い。

【0248】

さらにシール材2205で封止基板2204を基板2210と貼り合わせることにより、基板2210、封止基板2204、およびシール材2205で囲まれた空間2207に発光素子2218が備えられた構造になっている。なお、空間2207には、不活性気体(窒素やアルゴン等)が充填される場合の他、シール材2205で充填される構成も含むものとする。

【0249】

なお、シール材2205にはエポキシ系樹脂を用いるのが好ましい。また、これらの材料はできるだけ水分や酸素を透過しない材料であることが望ましい。また、封止基板2204に用いる材料としてガラス基板や石英基板の他、FRP(Fiberglass−Reinforced Plastics)、PVF(ポリビニルフロライド)、マイラー、ポリエステルまたはアクリル等からなるプラスチック基板を用いることができる。

【0250】

以上のようにして、本発明の画素構成を有する表示パネルを得ることができる。なお、上述した構成は一例であって本発明の表示パネルの構成はこれに限定されない。

【0251】

図22示すように、信号線駆動回路2201、画素部2202、第1の走査線駆動回路2203及び第2の走査線駆動回路2206を一体形成することで、表示装置の低コスト化が図れる。また、この場合において、信号線駆動回路2201、画素部2202、第1の走査線駆動回路2203及び第2の走査線駆動回路2206に用いられるトランジスタを単極性とすることで作製工程の簡略化が図れるためさらなる低コスト化が図れる。

【0252】

なお、表示パネルの構成としては、図22(a)に示したように信号線駆動回路2201、画素部2202、第1の走査線駆動回路2203及び第2の走査線駆動回路2206を一体形成した構成に限られず、信号線駆動回路2201に相当する図28に示す信号線駆動回路2801をICチップ上に形成して、COG等で表示パネルに実装した構成としても良い。なお、図28(a)の基板2800、画素部2802、第1の走査線駆動回路2803、第2の走査線駆動回路2804、FPC2805、ICチップ2806、ICチップ2807、封止基板2808、シール材2809は図22(a)の基板2210、画素部2202、第1の走査線駆動回路2203、第2の走査線駆動回路2206、FPC2209、ICチップ2219、ICチップ2222、封止基板2204、シール材2205に相当する。

【0253】

つまり、駆動回路の高速動作が要求される信号線駆動回路のみを、CMOS等を用いてICチップに形成し、低消費電力化を図る。また、ICチップはシリコンウエハ等の半導体チップとすることで、より高速動作且つ低消費電力化を図れる。

【0254】

そして、第2の走査線駆動回路2803や第1の走査線駆動回路2804を画素部2802と一体形成することで、低コスト化が図れる。そして、この第2の走査線駆動回路2803、第1の走査線駆動回路2804及び画素部2802は単極性のトランジスタで構成することでさらなる低コスト化が図れる。画素部2802の有する画素の構成としては実施の形態1、2、3及び4で示した画素を適用することができる。

【0255】

こうして、高精細な表示装置の低コスト化が図れる。また、FPC2805と基板2800との接続部において機能回路(メモリやバッファ)が形成されたICチップを実装することで基板面積を有効利用することができる。

【0256】

また、図22(a)の信号線駆動回路2201、第1の走査線駆動回路2203及び第2の走査線駆動回路2206に相当する図28(b)の信号線駆動回路2811、第1の走査線駆動回路2814及び第2の走査線駆動回路2813をICチップ上に形成して、COG等で表示パネルに実装した構成としても良い。この場合には高精細な表示装置をより低消費電力にすることが可能である。よって、より消費電力が少ない表示装置とするためには、画素部に用いられるトランジスタの半導体層にはポリシリコンを用いることが望ましい。なお、図28(b)の基板2810、画素部2812、第FPC2815、ICチップ2816、ICチップ2817、封止基板2818、シール材2822は図22(a)の基板2210、画素部2202、FPC2209、ICチップ2219、ICチップ2222、封止基板2204、シール材2205に相当する。

【0257】

また、画素部2812のトランジスタの半導体層にアモルファスシリコンを用いることにより低コスト化を図ることができる。さらに、大型の表示パネルを作製することも可能となる。

【0258】

また、画素の行方向及び列方向に第2の走査線駆動回路、第1の走査線駆動回路及び信号線駆動回路を設けなくても良い。例えば、図29(a)に示すようにICチップ上に形成された周辺駆動回路2901が図28(b)に示す、第1の走査線駆動回路2814、第2の走査線駆動回路2813及び信号線駆動回路2811の機能を有するようにしても良い。なお、図29(a)の基板2900、画素部2902、第FPC2904、ICチップ2905、ICチップ2906、封止基板2907、シール材2908は図22(a)の基板2210、画素部2202、FPC2209、ICチップ2219、ICチップ2222、封止基板2204、シール材2205に相当する。

【0259】

なお、図29(a)の表示装置の配線の接続を説明する模式図を図29(b)に示す。基板2910、周辺駆動回路2911、画素部2912、FPC2913、FPC2914有する。FPC2913より周辺駆動回路2911に外部からの信号及び電源電位が入力される。そして、周辺駆動回路2911からの出力は、画素部2912の有する画素に接続された行方向及び列方向の配線に入力される。

【0260】

さらに、発光素子2218に適用可能な発光素子の例を図23(a)、(b)に示す。つまり、実施の形態1、実施の形態2、実施の形態3、実施の形態4及び本実施の形態で示した画素に適用可能な発光素子の構成について図23(a)、(b)を用いて説明する。

【0261】

図23(a)の発光素子は、基板2301の上に陽極2302、正孔注入材料からなる正孔注入層2303、その上に正孔輸送材料からなる正孔輸送層2304、発光層2305、電子輸送材料からなる電子輸送層2306、電子注入材料からなる電子注入層2307、そして陰極2308を積層させた素子構造である。ここで、発光層2305は、一種類の発光材料のみから形成されることもあるが、2種類以上の材料から形成されてもよい。また本発明の素子の構造は、この構造に限定されない。

【0262】

また、図23(a)で示した各機能層を積層した積層構造の他、高分子化合物を用いた素子、発光層に三重項励起状態から発光する三重項発光材料を利用した高効率素子など、バリエーションは多岐にわたる。ホールブロック層によってキャリヤの再結合領域を制御し、発光領域を二つの領域にわけることによって得られる白色発光素子などにも応用可能である。

【0263】

図23(a)に示す本発明の素子作製方法は、まず、陽極2302(ITO)を有する基板2301に正孔注入材料、正孔輸送材料、発光材料を順に蒸着する。次に電子輸送材料、電子注入材料を蒸着し、最後に陰極2308を蒸着で形成する。

【0264】

次に、正孔注入材料、正孔輸送材料、電子輸送材料、電子注入材料、発光材料の材料に好適な材料を以下に列挙する。

【0265】

正孔注入材料としては、有機化合物であればポルフィリン系の化合物や、フタロシアニン(以下「H2Pc」と記す)、銅フタロシアニン(以下「CuPc」と記す)などが有効である。また、使用する正孔輸送材料よりもイオン化ポテンシャルの値が小さく、かつ、正孔輸送機能をもつ材料であれば、これも正孔注入材料として使用できる。導電性高分子化合物に化学ドーピングを施した材料もあり、ポリスチレンスルホン酸(以下「PSS」と記す)をドープしたポリエチレンジオキシチオフェン(以下「PEDOT」と記す)や、ポリアニリンなどが挙げられる。また、絶縁体の高分子化合物も陽極の平坦化の点で有効であり、ポリイミド(以下「PI」と記す)がよく用いられる。さらに、無機化合物も用いられ、金や白金などの金属薄膜の他、酸化アルミニウム(以下「アルミナ」と記す)の超薄膜などがある。

【0266】

正孔輸送材料として最も広く用いられているのは、芳香族アミン系(すなわち、ベンゼン環−窒素の結合を有するもの)の化合物である。広く用いられている材料として、4,4’−ビス(ジフェニルアミノ)−ビフェニル(以下、「TAD」と記す)や、その誘導体である4,4’−ビス[N−(3−メチルフェニル)−N−フェニル−アミノ]−ビフェニル(以下、「TPD」と記す)、4,4’−ビス[N−(1−ナフチル)−N−フェニル−アミノ]−ビフェニル(以下、「α−NPD」と記す)がある。4,4’,4”−トリス(N,N− ジフェニル−アミノ)−トリフェニルアミン(以下、「TDATA」と記す)、4,4’,4”−トリス[N−(3−メチルフェニル)−N− フェニル−アミノ]−トリフェニルアミン(以下、「MTDATA」と記す)などのスターバースト型芳香族アミン化合物が挙げられる。

【0267】

電子輸送材料としては、金属錯体がよく用いられ、先に述べたAlq、BAlq、トリス(4−メチル−8−キノリノラト)アルミニウム(以下、「Almq」と記す)、ビス(10−ヒドロキシベンゾ[h]−キノリナト)ベリリウム(以下、「BeBq」と記す)などのキノリン骨格またはベンゾキノリン骨格を有する金属錯体などがある。また、ビス[2−(2−ヒドロキシフェニル)−ベンゾオキサゾラト]亜鉛(以下、「Zn(BOX)2」と記す)、ビス[2−(2−ヒドロキシフェニル)−ベンゾチアゾラト]亜鉛(以下、「Zn(BTZ)2」と記す)などのオキサゾール系、チアゾール系配位子を有する金属錯体もある。さらに、金属錯体以外にも、2−(4−ビフェニリル)−5−(4−tert−ブチルフェニル)−1,3,4−オキサジアゾール(以下、「PBD」と記す)、OXD−7などのオキサジアゾール誘導体、TAZ、3−(4−tert−ブチルフェニル)−4−(4−エチルフェニル)−5−(4−ビフェニリル)−23、4−トリアゾール(以下、「p−EtTAZ」と記す)などのトリアゾール誘導体、バソフェナントロリン(以下、「BPhen」と記す)、BCPなどのフェナントロリン誘導体が電子輸送性を有する。

【0268】

電子注入材料としては、上で述べた電子輸送材料を用いることができる。その他に、フッ化カルシウム、フッ化リチウム、フッ化セシウムなどの金属ハロゲン化物や、酸化リチウムなどのアルカリ金属酸化物のような絶縁体の、超薄膜がよく用いられる。また、リチウムアセチルアセトネート(以下、「Li(acac)」と記す)や8−キノリノラト−リチウム(以下、「Liq」と記す)などのアルカリ金属錯体も有効である。

【0269】

発光材料としては、先に述べたAlq、Almq、BeBq、BAlq、Zn(BOX)2、Zn(BTZ)2などの金属錯体の他、各種蛍光色素が有効である。蛍光色素としては、青色の4,4’−ビス(2,2 − ジフェニル−ビニル)−ビフェニルや、赤橙色の4−(ジシアノメチレン)−2−メチル−6−(p−ジメチルアミノスチリル)−4H−ピランなどがある。また、三重項発光材料も可能であり、白金ないしはイリジウムを中心金属とする錯体が主体である。三重項発光材料として、トリス(2−フェニルピリジン)イリジウム、ビス(2−(4’−トリル)ピリジナト−N,C2’)アセチルアセトナトイリジウム(以下「acacIr(tpy)2」と記す)、 2,3,7,8,12,13,17,18−オクタエチル−21H,23Hポルフィリン−白金などが知られている。

【0270】

以上で述べたような各機能を有する材料を、各々組み合わせ、高信頼性の発光素子を作製することができる。

【0271】

また、実施の形態3で示した図11の画素の場合には図23(b)に示すように図23(a)とは逆の順番に層を形成した発光素子を用いることができる。つまり、基板2311の上に陰極2318、電子注入材料からなる電子注入層2317、その上に電子輸送材料からなる電子輸送層2316、発光層2315、正孔輸送材料からなる正孔輸送層2314、正孔注入材料からなる正孔注入層2313、そして陽極2312を積層させた素子構造である。

【0272】

また、発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上にTFT及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本発明の画素構成はどの射出構造の発光素子にも適用することができる。

【0273】

上面射出構造の発光素子について図24(a)を用いて説明する。

【0274】

基板2400上に駆動用TFT2401が形成され、駆動用TFT2401のソース電極に接して第1の電極2402が形成され、その上に有機化合物を含む層2403と第2の電極2404が形成されている。

【0275】

また、第1の電極2402は発光素子の陽極である。そして第2の電極2404は発光素子の陰極である。つまり、第1の電極2402と第2の電極2404とで有機化合物を含む層2403が挟まれているところが発光素子となる。

【0276】

また、ここで、陽極として機能する第1の電極2402に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、窒化チタン膜、クロム膜、タングステン膜、Zn膜、Pt膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。光を反射する金属膜を用いることで光を透過させない陽極を形成することができる。

【0277】

また、陰極として機能する第2の電極2404に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、またはCa3N2)からなる金属薄膜と、透明導電膜(ITO(インジウムスズ酸化物)、インジウム亜鉛酸化物(IZO)、酸化亜鉛(ZnO)等)との積層を用いるのが良い。こうして薄い金属薄膜と、透明性を有する透明導電膜を用いることで光を透過させることが可能な陰極を形成することができる。

【0278】

こうして、図24(a)の矢印に示すように発光素子からの光を上面に取り出すことが可能になる。つまり、図22の表示パネルに適用した場合には、封止基板2204側に光が射出することになる。従って上面射出構造の発光素子を表示装置に用いる場合には封止基板2204は光透過性を有する基板を用いる。

【0279】

また、光学フィルムを設ける場合には、封止基板2204に光学フィルムを設ければよい。

【0280】

なお、実施の形態3の図11の画素構成の場合には、第1の電極2402を陰極として機能するMgAg、MgIn、AlLi等の仕事関数の小さい材料からなる金属膜を用いることができる。そして、第2の電極2404にはITO(インジウムスズ酸化物)膜、インジウム亜鉛酸化物(IZO)などの透明導電膜を用いることができる。よって、この構成によれば、上面射出の透過率を高くすることができる。

【0281】

また、下面射出構造の発光素子について図24(b)を用いて説明する。射出構造以外は図24(a)と同じ構造の発光素子であるため同じ符号を用いて説明する。

【0282】

ここで、陽極として機能する第1の電極2402に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウムスズ酸化物)膜、インジウム亜鉛酸化物(IZO)膜などの透明導電膜を用いることができる。透明性を有する透明導電膜を用いることで光を透過させることが可能な陽極を形成することができる。

【0283】

また、陰極として機能する第2の電極2404に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、またはCa3N2)からなる金属膜を用いることができる。こうして、光を反射する金属膜を用いることで光が透過しない陰極を形成することができる。

【0284】

こうして、図24(b)の矢印に示すように発光素子からの光を下面に取り出すことが可能になる。つまり、図22の表示パネルに適用した場合には、基板2210側に光が射出することになる。従って下面射出構造の発光素子を表示装置に用いる場合には基板2210は光透過性を有する基板を用いる。

【0285】

また、光学フィルムを設ける場合には、基板2210に光学フィルムを設ければよい。

【0286】

両面射出構造の発光素子について図24(c)を用いて説明する。射出構造以外は図24(a)と同じ構造の発光素子であるため同じ符号を用いて説明する。

【0287】

ここで、陽極として機能する第1の電極2402に用いる材料としては、仕事関数の大きい材料を用いることが望ましい。例えば、ITO(インジウムスズ酸化物)膜、インジウム亜鉛酸化物(IZO)膜などの透明導電膜を用いることができる。透明性を有する透明導電膜を用いることで光を透過させることが可能な陽極を形成することができる。

【0288】

また、陰極として機能する第2の電極2404に用いる材料としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF2、またはCa3N2)からなる金属薄膜と、透明導電膜(ITO(インジウムスズ酸化物)、酸化インジウム酸化亜鉛合金(In2O3―ZnO)、酸化亜鉛(ZnO)等)との積層を用いるのが良い。こうして薄い金属薄膜と、透明性を有する透明導電膜を用いることで光を透過させることが可能な陰極を形成することができる。

【0289】

こうして、図24(c)の矢印に示すように発光素子からの光を両面に取り出すことが可能になる。つまり、図22の表示パネルに適用した場合には、基板2210側と封止基板2204側に光が射出することになる。従って両面射出構造の発光素子を表示装置に用いる場合には基板2210および封止基板2204は、ともに光透過性を有する基板を用いる。

【0290】

また、光学フィルムを設ける場合には、基板2210および封止基板2204の両方に光学フィルムを設ければよい。

【0291】

また、白色の発光素子とカラーフィルターを用いてフルカラー表示を実現する表示装置にも本発明を適用することが可能である。

【0292】

図25に示すように、基板2500上に下地膜2502が形成され、その上に駆動用TFT2501が形成され、駆動用TFT2501のソース電極に接して第1の電極2503が形成され、その上に有機化合物を含む層2504と第2の電極2505が形成されている。

【0293】

また、第1の電極2503は発光素子の陽極である。そして第2の電極2505は発光素子の陰極である。つまり、第1の電極2503と第2の電極2505とで有機化合物を含む層2504が挟まれているところが発光素子となる。図25の構成では白色光を発光する。そして、発光素子の上部に赤色のカラーフィルター2506R、緑色のカラーフィルター2506G、青色のカラーフィルター2506Bを設けられており、フルカラー表示を行うことができる。また、これらのカラーフィルターを隔離するブラックマトリクス(BMともいう)2507が設けられている。

【0294】

上述した発光素子の構成は組み合わせて用いることができ、本発明の画素構成を有する表示装置に適宜用いることができる。また、上述した表示パネルの構成や、発光素子は例示であり、もちろん本発明の画素構成は他の構成の表示装置に適用することもできる。

【0295】

次に、表示パネルの画素部の部分断面図を示す。

【0296】

まず、トランジスタの半導体層に結晶性半導体膜(ポリシリコン(p−Si:H)膜)を用いた場合について図26及び図27を用いて説明する。

【0297】

ここで、半導体層は、例えば基板上にアモルファスシリコン(a−Si)膜を公知の成膜法で形成する。なお、アモルファスシリコン膜に限定する必要はなく、非晶質構造を含む半導体膜(微結晶半導体膜を含む)であれば良い。さらに非晶質シリコンゲルマニウム膜などの非晶質構造を含む化合物半導体膜でも良い。

【0298】

そして、アモルファスシリコン膜をレーザ結晶化法や、RTAやファーネスアニール炉を用いた熱結晶化法や、結晶化を助長する金属元素を用いた熱結晶化法などとにより結晶化させる。もちろん、これらを組み合わせて行っても良い。

【0299】

上述した結晶化によって、非晶質半導体膜に部分的に結晶化された領域が形成される。

【0300】

さらに、部分的に結晶性が高められた結晶性半導体膜を所望の形状にパターニングして、結晶化された領域から島状の半導体膜(一続きの半導体膜を分離して複数の膜にした各々の膜をいう)を形成する。この半導体膜をトランジスタの半導体層に用いる。なお、パターニングとは、膜を形状加工することをいい、フォトリソグラフィー技術によって膜のパターンを形成すること(例えば、感光性アクリルにコンタクトホールを形成することや、感光性アクリルをスペーサとなるように形状加工することも含む)や、フォトリソグラフィー技術によってマスクパターンを形成し、当該マスクパターンを用いてエッチング加工を行うことなどをいう。

【0301】

図26に示すように、基板26101上に下地膜26102が形成され、その上に半導体層が形成されている。半導体層は駆動トランジスタ26118のチャネル形成領域26103及びソース又はドレイン領域となる不純物領域26105、並びに容量素子26119の下部電極となるチャネル形成領域26106、低濃度不純物領域26107及び不純物領域26108を有する。なお、チャネル形成領域26103及びチャネル形成領域26106にはチャネルドープが行われていても良い。

【0302】

基板はガラス基板、石英基板、セラミック基板、プラスチック基板などを用いることができる。また、下地膜26102としては、窒化アルミ(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

【0303】

半導体層上にはゲート絶縁膜26109を介してゲート電極26110及び容量素子の上部電極26111が形成されている。

【0304】

駆動トランジスタ26118及び容量素子26119を覆って層間絶縁膜26112が形成され、層間絶縁膜26112上にコンタクトホールを介して配線26113が不純物領域26105と接している。配線26113に接して画素電極26114が形成され、画素電極26114の端部及び配線26113を覆って層間絶縁物26115が形成されている。ここでは、ポジ型の感光性アクリル樹脂膜を用いることにより形成する。そして、画素電極26114上に有機化合物を含む層26116及び対向電極26117が形成され、画素電極26114と対向電極26117とで有機化合物を含む層26116が挟まれた領域では発光素子26120が形成されている。

【0305】

また、図26(b)に示すように、容量素子26119の下部電極の一部を構成する低濃度不純物領域のうち、上部電極26111と重なるような低濃度不純物領域26202を設けても良い。つまり、容量素子26119の下部電極はチャネル形成領域26201、低濃度不純物領域26202、低濃度不純物領域26107、不純物領域26108で構成される。なお、図26(a)と共通するところは共通の符号を用い、説明は省略する。

【0306】

また、図27(a)に示すように、駆動トランジスタ26118の不純物領域26105と接する配線26113と同じ層に形成された第2の上部電極26301を有していても良い。なお、図26(a)と共通するところは共通の符号を用い、説明は省略する。第2の上部電極26301と上部電極26111とで層間絶縁膜26112を挟みこみ、第2の容量素子を構成している。また、第2の上部電極26301は不純物領域26108と接しているため、上部電極26111とチャネル形成領域26106とでゲート絶縁膜26109を挟みこんで構成される第1の容量素子と、上部電極26111と第2の上部電極26301とで層間絶縁膜26112を挟みこんで構成される第2の容量素子と、が並列に接続され、第1の容量素子と第2の容量素子からなる容量素子26302を構成している。この容量素子26302の容量は第1の容量素子と第2の容量素子の容量を加算した合成容量であるため、小さい面積で大きな容量の容量素子を形成することができる。つまり、本発明の画素構成の容量素子として用いるとより開口率の向上が図れる。

【0307】

また、図27(b)に示すような容量素子の構成としても良い。基板27101上に下地膜27102が形成され、その上に半導体層が形成されている。半導体層は駆動トランジスタ27118のチャネル形成領域27103及びソース又はドレイン領域となる不純物領域27105を有する。なお、チャネル形成領域27103はチャネルドープが行われていても良い。

【0308】

基板はガラス基板、石英基板、セラミック基板、プラスチック基板などを用いることができる。また、下地膜27102としては、窒化アルミ(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

【0309】

半導体層上にはゲート絶縁膜27106を介してゲート電極27107及び第1の電極27108が形成されている。

【0310】

駆動トランジスタ27118及び第1の電極27108を覆って第1の層間絶縁膜27109が形成され、第1の層間絶縁膜27109上にコンタクトホールを介して配線27110が不純物領域27105と接している。また、配線27110と同じ材料からなる同層の第2の電極27111が形成される。

【0311】

さらに、配線27110及び第2の電極27111を覆うように第2の層間絶縁膜27112が形成され、第2の層間絶縁膜27112上にコンタクトホールを介して、配線27110と接して画素電極27113が形成されている。また、画素電極27113のと同じ材料からなる同層の第3の電極27114が形成されている。ここで、第1の電極27108、第2の電極27111及び第3の電極27114からなる容量素子27119が形成される。

【0312】

画素電極27113の端部と第3の電極27114を覆って絶縁物27115が形成され、絶縁物27115及び第3の電極27114上に有機化合物を含む層27116及び対向電極27117が形成され、画素電極27113と対向電極27117とで有機化合物を含む層27116が挟まれた領域では発光素子27120が形成されている。

【0313】

上述したように、結晶性半導体膜を半導体層に用いたトランジスタの構成は図26及び図27に示したような構成が挙げられる。なお、図26及び図27に示したトランジスタの構造はトップゲートの構造のトランジスタの一例である。つまり、トランジスタはP型でもN型でもよい。N型の場合には、LDD領域はゲート電極と重なっていても良いし、ゲート電極と重なっていなくても良いし、又はLDD領域の一部の領域が重なっていてもよい。さらに、ゲート電極はテーパー形状でもよく、ゲート電極のテーパー部の下部にLDD領域が自己整合的に設けられていても良い。また、ゲート電極は二つに限られず三以上のマルチゲート構造でも良いし、一つのゲート電極でも良い。

【0314】

本発明の画素を構成するトランジスタの半導体層(チャネル形成領域やソース領域やドレイン領域など)に結晶性半導体膜を用いることで、例えば、図4における走査線駆動回路402及び信号線駆動回路401を画素部403と一体形成することが容易になる。

【0315】

また、半導体層にポリシリコン(p−Si)を用いたトランジスタの構成として、基板と半導体層の間にゲート電極が挟まれた構造、つまり、半導体層の下にゲート電極が位置するボトムゲートのトランジスタを適用した表示パネルの部分断面を図30(a)に示す。

【0316】

基板3001上に下地膜3002が形成されている。さらに下地膜3002上にゲート電極3003が形成されている。また、ゲート電極と同層に同じ材料からなる第1の電極3004が形成されている。ゲート電極3003の材料にはリンが添加された多結晶シリコンを用いることができる。多結晶シリコンの他に、金属とシリコンの化合物であるシリサイドでもよい。

【0317】

また、ゲート電極3003及び第1の電極3004を覆うようにゲート絶縁膜3005が形成されている。ゲート絶縁膜3005としては酸化珪素膜や窒化珪素膜などが用いられる。

【0318】

また、ゲート絶縁膜3005上に、半導体層が形成されている。半導体層は駆動トランジスタ3022のチャネル形成領域3006、LDD領域3007及びソース又はドレイン領域となる不純物領域3008、並びに容量素子3023の第2の電極となるチャネル形成領域3009、LDD領域3010及び不純物領域3011を有する。なお、チャネル形成領域3006及びチャネル形成領域3009はチャネルドープが行われていても良い。

【0319】

基板はガラス基板、石英基板、セラミック基板、プラスチック基板などを用いることができる。また、下地膜3002としては、窒化アルミ(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

【0320】

半導体層を覆って第1の層間絶縁膜3012が形成され、第1の層間絶縁膜3012上にコンタクトホールを介して配線3013が不純物領域3008と接している。また、配線3013と同層に同じ材料で第3の電極3014が形成されている。第1の電極3004、第2の電極、第3の電極3014によって容量素子3023が構成されている。

【0321】

また、第1の層間絶縁膜3012には開口部3015が形成されている。駆動トランジスタ3022、容量素子3023及び開口部3015を覆うように第2の層間絶縁膜3016が形成され、第2の層間絶縁膜3016上にコンタクトホールを介して、画素電極3017が形成されている。また、画素電極3017の端部を覆って絶縁物3018が形成されている。例えば、ポジ型の感光性アクリル樹脂膜を用いることができる。そして、画素電極3017上に有機化合物を含む層3019及び対向電極3020が形成され、画素電極3017と対向電極3020とで有機化合物を含む層3019が挟まれた領域では発光素子3021が形成されている。そして、発光素子3021の下部に開口部3015が位置している。つまり、発光素子3021からの発光を基板側から取り出すときには開口部3015を有するため透過率を高めることができる。

【0322】

また、図30(a)において画素電極3017と同層に同じ材料を用いて第4の電極3024を形成して、図30(b)のような構成としてもよい。すると、第1の電極3004、第2の電極、第3の電極3014及び第4の電極3024によって構成される容量素子3025を形成することができる。

【0323】

次に、トランジスタの半導体層にアモルファスシリコン(a−Si:H)膜を用いた場合について説明する。図31にはトップゲートのトランジスタ、図32及び図30にはボトムゲートのトランジスタの場合について示す。

【0324】

アモルファスシリコンを半導体層に用いた順スタガ構造のトランジスタの断面を図31(a)に示す。に示すように、基板3101上に下地膜3102が形成されている。さらに下地膜3102上に画素電極3103が形成されている。また、画素電極3103と同層に同じ材料からなる第1の電極3104が形成されている。

【0325】

基板はガラス基板、石英基板、セラミック基板、プラスチック基板などを用いることができる。また、下地膜3102としては、窒化アルミ(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

【0326】

また、下地膜3102上に配線3105及び配線3106が形成され、画素電極3103の端部が配線3105で覆われている。配線3105及び配線3106の上部にN型の導電型を有するN型半導体層3107及びN型半導体層3108が形成されている。また、配線3106と配線3105の間であって、下地膜3102上に半導体層3109が形成されている。そして、半導体層3109の一部はN型半導体層3107及びN型半導体層3108上にまで延長されている。なお、この半導体層はアモルファスシリコン(a−Si:H)、微結晶半導体(μ−Si:H)等の非結晶性を有する半導体膜で形成されている。また、半導体層3109上にゲート絶縁膜3110が形成されている。また、ゲート絶縁膜3110と同層の同じ材料からなる絶縁膜3111が第1の電極3104上にも形成されている。なお、ゲート絶縁膜3110としては酸化珪素膜や窒化珪素膜などが用いられる。

【0327】

また、ゲート絶縁膜3110上に、ゲート電極3112が形成されている。また、ゲート電極と同層に同じ材料でなる第2の電極3113が第1の電極3120上に絶縁膜3111を介して形成されている。第1の電極3104及び第2の電極3113で絶縁膜3111を挟まれた容量素子3119が形成されている。また、画素電極3103の端部、駆動トランジスタ3118及び容量素子3119を覆い、絶縁物3114が形成されている。

【0328】

絶縁物3114及びその開口部に位置する画素電極3103上に有機化合物を含む層3115及び対向電極3116が形成され、画素電極3103と対向電極3116とで有機化合物を含む層3115が挟まれた領域では発光素子3117が形成されている。

【0329】

また、図31(a)に示す第1の電極3104を図31(b)に示すように第1の電極3120で形成してもよい。第1の電極3120は配線3105及び3106と同層の同一材料で形成されている。

【0330】

また、アモルファスシリコンを半導体層に用いたボトムゲート構造のトランジスタを用いた表示パネルの部分断面を図32に示す。

【0331】

基板3201上に下地膜3202が形成されている。さらに下地膜3202上にゲート電極3203が形成されている。また、ゲート電極と同層に同じ材料からなる第1の電極3204が形成されている。ゲート電極3203の材料にはリンが添加された多結晶シリコンを用いることができる。多結晶シリコンの他に、金属とシリコンの化合物であるシリサイドでもよい。

【0332】

また、ゲート電極3203及び第1の電極3204を覆うようにゲート絶縁膜3205が形成されている。ゲート絶縁膜3205としては酸化珪素膜や窒化珪素膜などが用いられる。

【0333】

また、ゲート絶縁膜3205上に、半導体層3206が形成されている。また、半導体層3206と同層に同じ材料からなる半導体層3207が形成されている。

【0334】

基板はガラス基板、石英基板、セラミック基板、プラスチック基板などを用いることができる。また、下地膜3202としては、窒化アルミ(AlN)や酸化珪素(SiO2)、酸化窒化珪素(SiOxNy)などの単層やこれらの積層を用いることができる。

【0335】

半導体層3206上にはN型の導電性を有するN型半導体層3208、3209が形成され、半導体層3207上にはN型半導体層3210が形成されている。

【0336】

N型半導体層3208、3209上にはそれぞれ配線3211、3212が形成され、N型半導体層3210上には配線3211及び3212と同層の同一材料からなる導電層3213が形成されている。

【0337】

半導体層3207、N型半導体層3210及び導電層3213からなる第2の電極が構成される。なお、この第2の電極と第1の電極3204でゲート絶縁膜3205を挟み込んだ構造の容量素子3220が形成されている。

【0338】

また、配線3211の一方の端部は延在し、その延在した配線3211上部に接して画素電極3214が形成されている。

【0339】

また、画素電極3214の端部、駆動トランジスタ3219及び容量素子3220を覆うように絶縁物3215が形成されている。

【0340】

画素電極3214及び絶縁物3215上には有機化合物を含む層3216及び対向電極3217が形成され、画素電極3214と対向電極3217とで有機化合物を含む層3216が挟まれた領域では発光素子3218が形成されている。

【0341】

容量素子の第2の電極の一部となる半導体層3207及びN型半導体層3210は設けなくても良い。つまり第2の電極は導電層3213とし、第1の電極3204と導電層3213でゲート絶縁膜が挟まれた構造の容量素子としてもよい。

【0342】

なお、図32(a)において、配線3211を形成する前に画素電極3214を形成することで、図32(b)に示すような、画素電極3214からなる第2の電極3221と第1の電極3204でゲート絶縁膜3205が挟まれた構造の容量素子3222を形成することができる。

【0343】

なお、図32では、逆スタガ型のチャネルエッチ構造のトランジスタについて示したが、もちろんチャネル保護構造のトランジスタでも良い。チャネル保護構造のトランジスタの場合について、図33(a)、(b)を用いて説明する。

【0344】

図33(a)に示すチャネル保護型構造のトランジスタは図32(a)に示したチャネルエッチ構造の駆動トランジスタ3219の半導体層3206のチャネルが形成される領域上にエッチングのマスクとなる絶縁物3301が設けられている点が異なり、他の共通しているところは共通の符号を用いている。

【0345】

また、同様に、図33(b)に示すチャネル保護型構造のトランジスタは図32(b)に示したチャネルエッチ構造の駆動トランジスタ3219の半導体層3206のチャネルが形成される領域上にエッチングのマスクとなる絶縁物3301が設けられている点が異なり、他の共通しているところは共通の符号を用いている。

【0346】

本発明の画素を構成するトランジスタの半導体層(チャネル形成領域やソース領域やドレイン領域など)に非晶質半導体膜を用いることで、製造コストを削減することができる。例えば、図2に示す画素構成を用いることで非晶質半導体膜を適用することが可能である。

【0347】

なお、本発明の画素構成の適用することができるトランジスタの構造や、容量素子の構造は上述した構成に限られず、さまざまな構成のトランジスタの構造や、容量素子の構造のものを用いることができる。

【0348】

(実施の形態7)

本発明の表示装置は様々な電子機器に適用することができる。具体的には電子機器の表示部に適用することができる。そのような電子機器として、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。

【0349】

図34(A)はディスプレイであり、筐体34001、支持台34002、表示部34003、スピーカー部34004、ビデオ入力端子34005等を含む。本発明の画素構成を有する表示装置を表示部34003に用いることができる。なお、ディスプレイは、パーソナルコンピュータ用、テレビジョン放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。本発明の画素構成を有する表示装置を表示部34003に用いたディスプレイは、消費電力を抑えつつ、表示不良を防止することができる。また、低コスト化を図ることも可能である。

【0350】

近年、ディスプレイの大型化のニーズが強くなっている。そして、ディスプレイの大型化に伴い価格の上昇が問題となっている、よって、いかに製造コストの削減を図り、高品質な製品を少しでも低価格に抑えるかが課題となる。

【0351】

例えば、図2や図11などの画素構成を表示パネルの画素部に用いることで、単極性のトランジスタからなる表示パネルを提供することができる。よって、工程数を減らし製造コストを削減することができる。

【0352】

また、図22(a)に示すように画素部と周辺の駆動回路を一体形成することにより、単極性のトランジスタからなる回路で構成された表示パネルを形成することができる。

【0353】

また、画素部を構成する回路のトランジスタの半導体層に非晶質半導体(例えばアモルファスシリコン(a−Si:H))を用いることで、工程を簡略化し、さらなるコストダウンが図れる。この場合には図28(b)や図29(a)に示したように、画素部の周辺の駆動回路をICチップ上に形成し、COG等で表示パネルに実装する良い。このように、非晶質半導体を用いることでディスプレイの大型化が容易になる。

【0354】

図34(B)はカメラであり、本体34101、表示部34102、受像部34103、操作キー34104、外部接続ポート34105、シャッター34106等を含む。

【0355】

近年、デジタルカメラなどの高性能化に伴い、生産競争は激化している。そして、いかに高性能なものを低価格に抑えるかが重要となる。本発明の画素構成を有する表示装置を表示部34102に用いたデジタルカメラは、消費電力を抑えつつ、表示不良を防止することができる。また、低コスト化を図ることも可能である。

【0356】

例えば、図2や図11の画素構成を画素部に用いることで、単極性のトランジスタからなる画素部を形成することができる。また、図28(a)に示すように、動作速度の高い信号線駆動回路はICチップ上に形成し、比較的動作速度の低い走査線駆動回路を画素部と共に単極性のトランジスタで構成される回路で一体形成することで、高性能化を実現し、低コスト化を図ることができる。また、画素部と、画素部と共に一体形成する走査線駆動回路に用いられるトランジスタの半導体層に非晶質半導体、例えばアモルファスシリコンを適用することでさらなる低コスト化が図れる。

【0357】

図34(C)はコンピュータであり、本体34201、筐体34202、表示部34203、キーボード34204、外部接続ポート34205、ポインティングマウス34206等を含む。本発明の画素構成を有する表示装置を表示部34203に用いたコンピュータは、消費電力を抑えつつ、表示不良を防止することができる。また、低コスト化を図ることも可能である。

【0358】

図34(D)はモバイルコンピュータであり、本体34301、表示部34302、スイッチ34303、操作キー34304、赤外線ポート34305等を含む。本発明の画素構成を有する表示装置を表示部34302に用いたモバイルコンピュータは、消費電力を抑えつつ、表示不良を防止することができる。また、低コスト化を図ることも可能である。

【0359】

図34(E)は記録媒体を備えた携帯型の画像再生装置(具体的にはDVD再生装置)であり、本体34401、筐体34402、表示部A34403、表示部B34404、記録媒体(DVD等)読み込み部34405、操作キー34406、スピーカー部34407等を含む。表示部A34403は主として画像情報を表示し、表示部B34404は主として文字情報を表示することができる。本発明の画素構成を有する表示装置を表示部A34403や表示部B34404に用いた画像再生装置は、消費電力を抑えつつ、表示不良を防止することができる。また、低コスト化を図ることも可能である。

【0360】

図34(F)はゴーグル型ディスプレイであり、本体34501、表示部34502、アーム部34503を含む。本発明の画素構成を有する表示装置を表示部34502に用いたゴーグル型ディスプレイは、消費電力を抑えつつ、表示不良を防止することができる。また、低コスト化を図ることも可能である。

【0361】

図34(G)はビデオカメラであり、本体34601、表示部34602、筐体34603、外部接続ポート34604、リモコン受信部34605、受像部34606、バッテリー34607、音声入力部34608、操作キー34609、接眼部34610等を含む。本発明の画素構成を有する表示装置を表示部34602に用いたビデオカメラは、消費電力を抑えつつ、表示不良を防止することができる。また、低コスト化を図ることも可能である。

【0362】

図34(H)は携帯電話機であり、本体34701、筐体34702、表示部34703、音声入力部34704、音声出力部34705、操作キー34706、外部接続ポート34707、アンテナ34708等を含む。

【0363】

近年、携帯電話機はゲーム機能やカメラ機能、電子マネー機能等を搭載し、高付加価値の携帯電話機のニーズが強くなっている。さらに、ディスプレイも高精細なものが求められている。本発明の画素構成を有する表示装置を表示部34703に用いた携帯電話機は、消費電力を抑えつつ、表示不良を防止することができる。また、画素の開口率が高く高詳細な表示が可能となる。また、低コスト化を図ることも可能である。

【0364】

例えば、図2の画素構成を画素部に用いることで、画素の開口率を向上させることができる。具体的には、発光素子を駆動する駆動トランジスタにNチャネル型のトランジスタを用いることで開口率が向上する。よって、高精細な表示部を有する携帯電話機を提供することができる。

【0365】

また、開口率が向上することから、図24(c)に示すような両面射出構造の表示装置を表示部に有し、付加価値が高く、高精細な表示部を有する携帯電話を提供することができる。

【0366】

このように多機能化し、携帯電話機は使用頻度が高まる一方で、一回の充電により長時間使用できることが要求される。

【0367】

例えば、図28(b)や図29(a)に示すように周辺駆動回路をICチップ上に形成し、CMOS等を用いることにより低消費電力化を図ることが可能である。

【0368】

このように本発明は、あらゆる電子機器に適用することが可能である。

【0369】

(実施の形態8)

本実施の形態において、本発明の画素構成を用いた表示装置を表示部に有する携帯電話の構成例について図37を用いて説明する。

【0370】

表示パネル3710はハウジング3700に脱着自在に組み込まれる。ハウジング3700は表示パネル3710のサイズに合わせて、形状や寸法を適宜変更することができる。表示パネル3710を固定したハウジング3700はプリント基板3701に嵌入されモジュールとして組み立てられる。

【0371】

表示パネル3710はFPC3711を介してプリント基板3701に接続される。プリント基板3701には、スピーカ3702、マイクロフォン3703、送受信回路3704、CPU及びコントローラなどを含む信号処理回路3705が形成されている。このようなモジュールと、入力手段3706、バッテリ3707を組み合わせ、筐体3709に収納する。表示パネル3710の画素部は筐体3709に形成された開口窓から視認できように配置する。

【0372】

表示パネル3710は、画素部と一部の周辺駆動回路(複数の駆動回路のうち動作周波数の低い駆動回路)を基板上にTFTを用いて一体形成し、一部の周辺駆動回路(複数の駆動回路のうち動作周波数の高い駆動回路)をICチップ上に形成し、そのICチップをCOG(Chip On Glass)で表示パネル3710に実装しても良い。あるいは、そのICチップをTAB(Tape Auto Bonding)やプリント基板を用いてガラス基板と接続してもよい。なお、一部の周辺駆動回路を基板上に画素部と一体形成し、他の周辺駆動回路を形成したICチップをCOG等で実装した表示パネルの構成は図28(a)に一例を示してある。このような構成とすることで、表示装置の低消費電力化を図り、携帯電話機の一回の充電による使用時間を長くすることができる。また、携帯電話機の低コスト化を図ることができる。

【0373】

また、画素部には実施の形態1乃至4で示した画素構成を適宜適用することができる。

【0374】

例えば、実施の形態1で示した図2の画素構成や実施の形態3で示した図11の画素構成を適用することで、低コスト化を実現するため画素部及び画素部と一体形成する周辺駆動回路を単極性のトランジスタで構成して製造工程の削減を図ることができる。

【0375】

また、さらに消費電力の低減を図るため、図28(b)や図29(a)に示すように、基板上にTFTを用いて画素部を形成し、全ての周辺駆動回路をICチップ上に形成し、そのICチップをCOG(Chip On Glass)などで表示パネルに実装しても良い。そして、画素部には、図2の画素構成を用い、非晶質半導体膜をトランジスタの半導体層に用いることで製造コストの削減を図ることができる。

【0376】

また、本実施例に示した構成は携帯電話の一例であって、本発明の画素構成はこのような構成の携帯電話に限られず様々な構成の携帯電話に適用することができる。

【0377】

(実施の形態9)

図35は表示パネル3501と、回路基板3502を組み合わせたELモジュールを示している。表示パネル3501は画素部3503、走査線駆動回路3504及び信号線駆動回路3505を有している。回路基板3502には、例えば、コントロール回路3506や信号分割回路3507などが形成されている。表示パネル3501と回路基板3502は接続配線3508によって接続されている。接続配線にはFPC等を用いることができる。

【0378】

表示パネル3501は、画素部と一部の周辺駆動回路(複数の駆動回路のうち動作周波数の低い駆動回路)を基板上にTFTを用いて一体形成し、一部の周辺駆動回路(複数の駆動回路のうち動作周波数の高い駆動回路)をICチップ上に形成し、そのICチップをCOG(Chip On Glass)などで表示パネル3501に実装するとよい。あるいは、そのICチップをTAB(Tape Auto Bonding)やプリント基板を用いて表示パネル3501に実装しても良い。なお、一部の周辺駆動回路を基板上に画素部と一体形成し、他の周辺駆動回路を形成したICチップをCOG等で実装した構成は図28(a)に一例を示してある。

【0379】

また、画素部には実施の形態1乃至4で示した画素構成を適宜適用することができる。

【0380】

例えば、実施の形態1で示した図2の画素構成や実施の形態3で示した図11の画素構成を適用することで、低コスト化を実現するため画素部及び画素部と一体形成する周辺駆動回路を単極性のトランジスタで構成して製造工程の削減を図ることができる。

【0381】