半導体装置、表示装置及び電子機器

【課題】表示装置において、表示素子に電流を供給するトランジスタの特性が画素ごとにばらつくことによって生ずる輝度ムラが、表示装置の画質向上の足かせとなっていた。

【解決手段】ソース信号線より画素に入力される映像信号は、表示素子に電流を供給するためのトランジスタをダイオード接続とし、当該ダイオード接続されたトランジスタのゲートに所望の電位が印加される。ここで、ダイオード接続したトランジスタにおいて、そのソース・ドレイン間には、トランジスタのしきい値電圧に応じた電位差を取得する。その結果、駆動用トランジスタのゲート電極には、映像信号にしきい値電圧に応じた電位差のオフセットをかけた電位を印加することができる。

【解決手段】ソース信号線より画素に入力される映像信号は、表示素子に電流を供給するためのトランジスタをダイオード接続とし、当該ダイオード接続されたトランジスタのゲートに所望の電位が印加される。ここで、ダイオード接続したトランジスタにおいて、そのソース・ドレイン間には、トランジスタのしきい値電圧に応じた電位差を取得する。その結果、駆動用トランジスタのゲート電極には、映像信号にしきい値電圧に応じた電位差のオフセットをかけた電位を印加することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トランジスタを有する半導体装置の構成に関する。本発明はまた、ガラス、

プラスチック等の絶縁体上に作製される薄膜トランジスタ(以後、TFTと表記する)を有

する半導体装置を含むアクティブマトリクス型発光装置の構成に関する。また、このよう

な発光装置を用いた電子機器に関する。

【背景技術】

【0002】

近年、エレクトロルミネッセンス(Electro Luminescence:EL)素子等を始めとした

発光素子を用いた表示装置の開発が活発化している。発光素子は、自らが発光するために

視認性が高く、液晶表示装置(LCD)等において必要なバックライトを必要としないため

に薄型化に適しているとともに、視野角にほとんど制限が無い。

【0003】

ここで、EL素子とは、電場を加えることで発生するルミネッセンスが得られる発光層

を有する素子を指す。この発光層においては、一重項励起状態から基底状態に戻る際の発

光(蛍光)と、三重項励起状態から基底状態に戻る際の発光(燐光)とがあるが、本発明にお

いて、発光装置とは、上述したいずれの発光形態であっても良い。

【0004】

EL素子は、一対の電極(陽極と陰極)間に発光層が挟まれる形で構成され、通常、積層

構造をとっている。代表的には、「陽極/正孔輸送層/発光層/電子輸送層/陰極」とい

う積層構造が挙げられる。また、これ以外にも、陽極と陰極との間に、「正孔注入層/正

孔輸送層/発光層/電子輸送層」または「正孔注入層/正孔輸送層/発光層/電子輸送層

/電子注入層」の順に積層する構造がある。

本発明の発光装置に用いるEL素子の構造としては、上述の構造のいずれを採用していて

も良い。また、発光層に対して蛍光性色素等をドーピングしても良い。

【0005】

本明細書においては、EL素子において、陽極と陰極との間に設けられる全ての層を総

称してEL層と呼ぶ。よって、上述の正孔注入層、正孔輸送層、発光層、電子輸送層、電

子注入層は、全てEL素子に含まれ、陽極、EL層、および陰極で構成される発光素子を

EL素子と呼ぶ。

【0006】

図20に、一般的な発光装置における画素の構成を示す。なお、代表的な発光装置とし

て、EL表示装置を例とする。図20に示した画素は、ソース信号線2001、ゲート信

号線2002、スイッチング用TFT2003、駆動用TFT2004、容量手段200

5、EL素子2006、電流供給線2007、電源線2008を有している。

【0007】

各部の接続関係について説明する。ここで、TFTはゲート、ソース、ドレインの3端

子を有するが、ソース、ドレインに関しては、TFTの構造上、明確に区別が出来ない。

よって、素子間の接続について説明する際は、ソース、ドレインのうち一方を第1の電極

、他方を第2の電極と表記する。TFTのON、OFFについて、各端子の電位等(ある

TFTのゲート・ソース間電圧等)について説明が必要な際には、ソース、ドレイン等と

表記する。

【0008】

また、本明細書において、TFTがONしているとは、TFTのゲート・ソース間電圧

がそのしきい値電圧を超え、ソース、ドレイン間が導通している状態をいい、TFTがO

FFしているとは、TFTのゲート・ソース間電圧がそのしきい値電圧を下回り、ソース

、ドレイン間が導通していない(非導通となっている)状態をいう。ただし、TFTにお

いてはオフリーク電流が存在するが、その大きさはオン電流に比べて小さいので、ここで

はオフリーク電流のみが流れる状態もまたOFFしている状態に含むものとする。

【0009】

スイッチング用TFT2003のゲート電極は、ゲート信号線2002に接続され、第

1の電極はソース信号線2001に接続され、第2の電極は駆動用TFT2004のゲー

ト電極に接続されている。駆動用TFT2004の第1の電極は、電流供給線2007に

接続され、第2の電極はEL素子2006の第1の電極に接続されている。EL素子20

06の第2の電極は、電源線2008に接続されている。電流供給線2007と、電源線

2008とは、互いに電位差を有している。また、駆動用TFT2004のゲート・ソー

ス間電圧を保持するために、駆動用TFT2004のゲート電極と第1の電極との間に容

量手段2005を設けても良い。

【0010】

ゲート信号線2002にパルスが入力されてスイッチング用TFT2003がONする

と、ソース信号線2001に出力されてきている映像信号は、駆動用TFT2004のゲ

ート電極へと入力される。入力された映像信号の電位に従って、駆動用TFT2004の

ゲート・ソース間電圧が決定し、駆動用TFT2004のソース・ドレイン間を流れる電

流(以下、ドレイン電流と表記)が決定する。

この電流はEL素子2006に供給されて発光する。

【0011】

ところで、多結晶シリコン(ポリシリコン 以下P−Si)で形成されたTFTは、非晶

質シリコン(アモルファスシリコン 以下A−Si)で形成されたTFTよりも電界効果移

動度が高く、ON電流が大きいため、発光装置に用いるトランジスタとしてより適してい

る。

【0012】

反面、ポリシリコンで形成されたTFTは、結晶粒界における欠陥に起因して、その電

気的特性にばらつきが生じやすいといった問題点を有している。

【0013】

図20に示した画素において、画素を構成するTFTのしきい値電圧が画素ごとにばら

つくと、同じ映像信号を入力した場合にも、それに応じてTFTのドレイン電流の大きさ

が異なってくるため、EL素子2006の輝度がばらつく。よってアナログ階調の場合、

問題となっていた。

【0014】

最近、このような問題に鑑みて、TFTのしきい値電圧のばらつきを補正することの出

来るものが提案されている。そのうちの1例としては、図22に示すような構成が挙げら

れる(特許文献1参照)。

【0015】

図22に示した画素は、ソース信号線2201、第1〜第3のゲート信号線2202〜

2204、TFT2205〜2208、容量手段2209(C2)、2210(C1)、電流供

給線2212、EL素子2211を有する。

【0016】

TFT2205のゲート電極は、第1のゲート信号線2202に接続され、第1の電極

は、ソース信号線2201に接続され、第2の電極は、容量手段2209の第1の電極に

接続されている。容量手段2209の第2の電極は、容量手段2210の第1の電極に接

続され、容量手段2210の第2の電極は、電流供給線2212に接続されている。TF

T2206のゲート電極は、容量手段2209の第2の電極および容量手段2210の第

1の電極に接続され、第1の電極は、電流供給線2212に接続され、第2の電極は、T

FT2207の第1の電極およびTFT2208の第1の電極に接続されている。TFT

2207のゲート電極は、第2のゲート信号線2203に接続され、第2の電極は、容量

手段2209の第2の電極および容量手段2210の第1の電極に接続されている。TF

T2208のゲート電極は、第3のゲート信号線2204に接続され、第2の電極は、E

L素子2211の第1の電極に接続されている。EL素子2211の第2の電極には、電

源線2213に接続され、電流供給線2212とは互いに電位差を有する。

【0017】

図22(B)および図23(A)〜(F)を用いて、動作について説明する。図22(B)は、

ソース信号線2201、第1〜第3のゲート信号線2202〜2204に入力される映像

信号およびパルスのタイミングを示しており、図23に示す各動作にあわせて、I〜VIII

の区間に分割している。また、図22に示した画素の一例では、4つのTFTを用いて構

成され、その極性は全てPチャネル型である。よって、ゲート電極にLレベルが入力され

てONし、Hレベルが入力されてOFFするものとする。また、ソース信号線2201に

入力される映像信号は、ここでは入力される期間のみを示すためパルスで示しているが、

アナログ階調方式の場合は、所定のアナログ電位をとる。

【0018】

まず、第1のゲート信号線2202がLレベルとなり、TFT2205がONする(区

間I)。続いて第2、第3のゲート信号線2203、2204がLレベルとなり、TFT2

207、2208がONする。ここで、図23(A)に示すように、容量手段2209、2

210に電荷が貯まり、容量手段2210が保持する電圧が、TFT2206のしきい値

電圧(Vth)を上回ったところで、TFT2206がONする(区間II)。

【0019】

続いて、第3のゲート信号線2204がHレベルとなって、TFT2208がOFFす

る。すると、容量手段2209、2210に貯まっていた電荷が再び移動し、容量手段2

210に保持される電圧は、やがてVthに等しくなる。このとき、図23(B)にも示すよ

うに、電流供給線2212、ソース信号線2201の電位はいずれもVDDであるので、容

量手段2209においても、保持されている電圧はVthに等しくなる。よって、やがてT

FT2206はOFFする。

【0020】

前述のように、容量手段2209、2210に保持されている電圧がVthに等しくなっ

たところで、第2のゲート信号線2203がHレベルとなり、TFT2207がOFFす

る(区間IV)。この動作により、図23(C)に示すように、容量手段2209においてVt

hが保持される。

【0021】

このとき、容量手段2210(C1)に保持されている電荷Q1については、式(1)のような

関係が成立する。同時に、容量手段2209(C2)に保持されている電荷Q2においては、

式(2)のような関係が成立する。

【0022】

【数1】

【0023】

【数2】

【0024】

続いて、図23(D)に示すように、映像信号の入力が行われる(区間V)。ソース信号線

2201に映像信号が出力されて、その電位はVDDから映像信号の電位VData(ここでは

、TFT2206がPチャネル型であるので、VDD>VDataとする。)となる。このとき

の、TFT2206のゲート電極の電位をVPとし、このノードにおける電荷をQとする

と、容量手段2209、2210とを含めた電荷保存則により、式(3)、(4)のような関

係が成立する。

【0025】

【数3】

【0026】

【数4】

【0027】

式(1)〜(4)より、TFT2206のゲート電極の電位VPは、式(5)で表される。

【0028】

【数5】

【0029】

よって、TFT2206のゲート・ソース間電圧VGSは、式(6)で表される。

【0030】

【数6】

【0031】

式(6)右辺には、Vthの項が含まれる。すなわち、ソース信号線2201より入力され

る映像信号には、その画素におけるTFT2206のしきい値電圧が上乗せされて容量手

段2209、2210によって保持される。

【0032】

映像信号の入力が完了すると、第1のゲート信号線2202がHレベルとなって、TF

T2205がOFFする(区間VI)。その後、ソース信号線は所定の電位に戻る(区間VII

)。以上の動作によって、映像信号の画素への書き込み動作が完了する(図23(E))。

【0033】

続いて、第3のゲート信号線2204がLレベルとなり、TFT2208がONし、E

L素子2211に図23(F)に示すように電流が流れることによってEL素子2211が

発光する。このときEL素子2211に流れる電流の値は、TFT2206のゲート・ソ

ース間電圧に従ったものであり、TFT2206を流れるドレイン電流IDSは、式(7)で

表される。

【0034】

【数7】

【0035】

式(7)より、TFT2206のドレイン電流IDSには、しきい値電圧Vthの値に依存し

ないことがわかる。よって、TFT2206のしきい値電圧がばらついた場合にも、画素

ごとにその値を補正して映像信号に上乗せすることにより、映像信号の電位VDataに従っ

た電流がEL素子2211に流れることがわかる。

【先行技術文献】

【特許文献】

【0036】

【特許文献1】国際公開番号99−48403号パンフレット(P25、Fig3、Fig4)

【発明の概要】

【発明が解決しようとする課題】

【0037】

しかし、前述の構成の場合、容量手段2209、2210の容量値がばらついた場合には

、TFT2206のドレイン電流IDSがばらついてしまうことになる。そこで、本発明に

おいては、容量値のばらつきの影響を受けることのない構成によって、TFTのしきい値

電圧のばらつきを補正することの出来る半導体装置を画素に用いた発光装置を提供するこ

とを目的とする。

【課題を解決するための手段】

【0038】

本発明の動作原理を、図29を用いて説明する。図29(A)(B)のような回路を考

える。スイッチ素子2901、2903、2911、2913は、それぞれSignal1、Si

gnal2によって制御される素子であり、TFT等によってON、OFFが出来るもので良

い。ここで、単一方向にのみ電流が流れる素子を、整流性素子と定義する。整流性素子と

しては、ダイオードや、ゲート・ドレイン間を接続(このような接続をダイオード接続と

表記する)したTFTが挙げられる。

【0039】

図29(A)(B)に示すように、スイッチ素子2901、2911、整流性素子29

02、2912、スイッチ素子2903、2913を接続した回路を考える。

【0040】

ここで、回路の一端より、ある信号が入力され、回路の他端は、ある一定電位が与えら

れているとする。図29(A)の場合、入力される信号をVX、一定電位をVSS(≦VX−

|VthP|:VthPはTFTのしきい値電圧)とし、図29(B)の場合、入力される信号

をVX、一定電位をVDD(≧VX+|VthN|:VthNはTFTのしきい値電圧)とする。

【0041】

今、図29(C)においてiで示される期間で、スイッチ素子2903、2913が導

通する。すると、図29(A)において、整流性素子(ここでは整流性素子にダイオード

接続TFTを用いたものとする。)であるTFT2902のドレイン電極およびゲート電

極の電位が低下する。図29(B)においては、TFT2912の第2の電極およびゲー

ト電極の電位が上昇する。整流性素子2902、2912のいずれも、両電極間の電圧が

しきい値電圧の絶対値を上回るため、TFT2902、2912はともにONする。ただ

しこのとき、スイッチ素子2901、2911は共にOFFしており、電流は流れない。

【0042】

その後、図29(C)においてiiで示される期間で、スイッチ素子2901、2903

、2911、2913が導通する。この期間で、TFT2902、2912のゲート・ソ

ース間電圧はそれぞれ、VSS−VX、VDD−VXとなり、それぞれのTFTのしきい値電圧

の絶対値を上回り、VX→VSSへ、VDD→VXへ電流が流れる。

【0043】

続いて、図29(C)においてiiiで示される期間で、スイッチ素子2901、291

1が導通し、かつスイッチ素子2903、2913が非導通となる。このとき、TFT2

902、2912のソース電位はVXである。今、TFT2902、2912のゲート・

ソース間電圧はそのしきい値電圧の絶対値を上回っており、TFT2902、2912は

ON状態であるため、電流が流れつづける。

これにより、TFT2902のドレイン電位は上昇し、TFT2912のドレイン電位は

下降する。やがて、TFT2902、2912のゲート・ソース間電圧は、そのしきい値

電圧に等しくなり、TFT2902、2912はともにOFFする。このとき、TFT2

902、2912のドレイン電位はそれぞれ、VX−|VthP|、VX+|VthN|となる。つ

まり、TFT2902、2912によって、入力される信号の電位VXに、それぞれのし

きい値電圧を上乗せする動作が行われる。TFT2902、2912のゲート電極の電位

をそれぞれ、VG2902、VG2912とすると、上記の動作において、VG2902、VG2912はそれ

ぞれ、図29(D)に示すような電位をとる。

【0044】

本発明においては、ソース信号線より画素に入力される映像信号は、図29(A)(B

)において2902、2912で示したような、ゲート・ドレイン間を接続したTFTを

経て、EL素子に電流を供給するためのTFTのゲート電極に所望の電位が印加される。

ここで、ゲート・ドレイン間を接続したTFTにおいて、そのソース・ドレイン間には、

TFTのしきい値電圧に等しい電位差が生ずる。よって、駆動用TFTのゲート電極には

、映像信号にしきい値電圧分だけオフセットをかけた電位を印加するようにする。

【0045】

なお、TFT2902、2912は、図29(E)に示すように、それぞれダイオード

2922、2932を用いても良い。

【0046】

また、スイッチ素子2903、2913についても、図29(F)に示すように、ダイ

オード2923、2933を用い、図29(C)における区間iiiの動作で、VDDもしく

はVSSの電位を変化させることによってVG2902、VG2912に同様の振る舞いをさせること

も出来る。

【0047】

ここで用いるダイオードには、通常のPN接合を有するダイオードの他、前述のダイオ

ード接続TFTを用いても良い。

【0048】

また、スイッチ素子2901、2911は共に省略しても良い。つまり、整流性素子2

902、2912の第1の電極に、信号VXが入力されても良い。

【0049】

ここでは、発光装置におけるTFTのしきい値電圧のばらつきを補正し、EL素子の輝

度ばらつきを低減することを課題とし、それに対する解決方法として述べているが、本発

明の動作原理は、発光装置におけるTFTのしきい値電圧のばらつきを補正するためだけ

にとどまらず、他の電子回路にももちろん応用が可能である。

【0050】

また、本発明におけるトランジスタとしては、主としてTFTを用いて構成したものを例

として挙げているが、単結晶トランジスタ又は有機物を利用したトランジスタでもよい。

例えば、単結晶トランジスタとしては、SOI技術を用いて形成されたトランジスタとす

ることができる。また、薄膜トランジスタとしては、活性層として多結晶半導体を用いた

ものでも、非晶質半導体を用いたものでもよい。例えば、ポリシリコンを用いたTFTや

、アモルファスシリコンを用いたTFTとすることができる。その他、バイポーラトラン

ジスタや、カーボンナノチューブ等により形成されたトランジスタを用いても良い。

【0051】

本発明の構成を以下に記す。

【0052】

本発明の半導体装置は、 スイッチ素子と、整流性素子とを有し、 前記整流性素子の

第1の電極には、第1の信号V1が入力され、第2の電極は、前記スイッチ素子の第1の

電極と電気的に接続され、 前記スイッチ素子の第2の電極には、ある電位Vが与えられ

る半導体装置であって、 前記整流性素子の第2の電極より、前記信号V1から前記整流

性素子のしきい値電圧Vthだけオフセットした信号V2を得ることを特徴としている。

【0053】

本発明の半導体装置は、 第1および第2のスイッチ素子と、整流性素子とを有し、

前記第1のスイッチ素子の第1の電極には、第1の信号V1が入力され、第2の電極は、

前記整流性素子の第1の電極と電気的に接続され、 前記整流性素子の第2の電極は、前

記第2のスイッチ素子の第1の電極と電気的に接続され、 前記第2のスイッチ素子の第

2の電極には、ある電位Vが与えられる半導体装置であって、 前記整流性素子の第2の

電極より、前記信号V1から前記整流性素子のしきい値電圧Vthだけオフセットした信

号V2を得ることを特徴としている。

【0054】

本発明の半導体装置は、 第1および第2の整流性素子とを有し、 前記第1の整流性

素子の第1の電極には、第1の信号V1が入力され、第2の電極は、前記第2の整流性素

子の第1の電極と電気的に接続され、 前記第2の整流性素子の第2の電極には、ある電

位Vが与えられる半導体装置であって、 前記第1の整流性素子の第2の電極より、前記

信号V1から前記第1の整流性素子のしきい値電圧Vthだけオフセットした信号V2を得

ることを特徴としている。

【0055】

本発明の半導体装置は、 前記整流性素子とは、ゲート・ドレイン間を接続したトラン

ジスタを用いてなり、 前記トランジスタの極性がNチャネル型であり、しきい値電圧が

Vthであるとき、 V1+Vth<V、かつV2=V1+Vthを満たし、 前記トラン

ジスタの極性がNチャネル型であり、しきい値電圧がVthであるとき、 V1>V+|V

th|、かつV2=V1−|Vth|を満たすことを特徴としている。

【0056】

本発明の半導体装置は、 前記整流性素子とは、ダイオードを用いてなり、 前記ダイ

オードのしきい値電圧がVthであるとき、 V1>V+Vth、かつV2=V1−|Vth

|もしくは、 V1<V−|Vth|、かつV2=V1+Vthを満たすことを特徴としている

。

【0057】

本発明の半導体装置は、 発光素子を備えた画素を有する半導体装置であって、 前記

画素は、 ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1乃至

第4のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極は、

前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気的

に接続され、第2の電極は、前記第2のトランジスタの第1の電極と電気的に接続され、

前記第2のトランジスタのゲート電極は、前記第2のトランジスタの第2の電極と、前

記第3のトランジスタの第1の電極と、前記第4のトランジスタのゲート電極と電気的に

接続され、 前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気的

に接続され、 前記第4のトランジスタの第1の電極は、前記電流供給線と電気的に接続

され、第2の電極は、前記発光素子の第1の電極と電気的に接続されていることを特徴と

している。

【0058】

本発明の半導体装置は、 発光素子を備えた画素を有する半導体装置であって、 前記

画素は、 ソース信号線と、ゲート信号線と、電流供給線と、第1乃至第4のトランジス

タと、発光素子とを有し、 前記第1のトランジスタのゲート電極は、前記ゲート信号線

と電気的に接続され、第1の電極は、前記ソース信号線と電気的に接続され、第2の電極

は、前記第2のトランジスタの第1の電極と電気的に接続され、 前記第2のトランジス

タのゲート電極は、前記第2のトランジスタの第2の電極と、前記第3のトランジスタの

第1の電極と、前記第4のトランジスタのゲート電極と電気的に接続され、 前記第3の

トランジスタのゲート電極は、前記画素より少なくとも1行前に走査される行の画素の有

するゲート信号線と電気的に接続され、 前記第4のトランジスタの第1の電極は、前記

電流供給線と電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接

続されていることを特徴としている。

【0059】

本発明の半導体装置は、 発光素子を備えた画素を有する半導体装置であって、 前記

画素は、 ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1乃至

第4のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極は、

前記第1のゲート信号線と電気的に接続され、第1の電極は、前記第2のトランジスタの

ゲート電極および第1の電極と電気的に接続され、第2の電極は、前記第3のトランジス

タの第1の電極と、前記第4のトランジスタのゲート電極と電気的に接続され、 前記第

2のトランジスタの第2の電極は、前記ソース信号線と電気的に接続され、 前記第3の

トランジスタのゲート電極は、前記第2のゲート信号線と電気的に接続され、 前記第4

のトランジスタの第1の電極は、前記電流供給線と電気的に接続され、第2の電極は、前

記発光素子の第1の電極と電気的に接続されていることを特徴としている。

【0060】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1

乃至第4のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極

は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記第2のトランジス

タのゲート電極と、前記第2のトランジスタの第1の電極と、前記第3のトランジスタの

第1の電極と電気的に接続され、第2の電極は、前記第4のトランジスタのゲート電極と

電気的に接続され、 前記第3のトランジスタのゲート電極は、前記第2のゲート信号線

と電気的に接続され、 前記第4のトランジスタの第1の電極は、前記電流供給線と電気

的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続されていること

を特徴としている。

【0061】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、ゲート信号線と、電流供給線と、第1乃至第4のトラン

ジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極は、前記第1のゲ

ート信号線と電気的に接続され、第1の電極は、前記第2のトランジスタのゲート電極と

、前記第2のトランジスタの第1の電極と、前記第3のトランジスタの第1の電極と電気

的に接続され、第2の電極は、前記第4のトランジスタのゲート電極と電気的に接続され

、 前記第3のトランジスタのゲート電極は、前記画素より少なくとも1行前に走査され

る行の画素の有するゲート信号線と電気的に接続され、 前記第4のトランジスタの第1

の電極は、前記電流供給線と電気的に接続され、第2の電極は、前記発光素子の第1の電

極と電気的に接続されていることを特徴としている。

【0062】

本発明の半導体装置は、 前記第3のトランジスタの第2の電極は、リセット用電源線

と電気的に接続されていることを特徴としている。

【0063】

本発明の半導体装置は、 前記第3のトランジスタの第2の電極は、前記画素と異なる

行において走査されるいずれかの画素が有するゲート信号線のうちいずれか1本と電気的

に接続されていることを特徴としている。

【0064】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1

乃至第4のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極

は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電

気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極および、前記第3

のトランジスタの第1の電極と電気的に接続され、 前記第2のトランジスタのゲート電

極は、前記第2のトランジスタの第2の電極と、前記第3のトランジスタの第2の電極と

、前記第4のトランジスタのゲート電極と電気的に接続され、 前記第4のトランジスタ

の第1の電極は、前記電流供給線と電気的に接続され、第2の電極は、前記発光素子の第

1の電極と電気的に接続されていることを特徴としている。

【0065】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1

乃至第3のトランジスタと、容量手段と、発光素子とを有し、 前記第1のトランジスタ

のゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソー

ス信号線と電気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と電

気的に接続され、 前記第2のトランジスタのゲート電極は、前記第2のトランジスタの

第2の電極および、前記第3のトランジスタのゲート電極と電気的に接続され、 前記第

3のトランジスタの第1の電極は、前記電流供給線と電気的に接続され、第2の電極は、

前記発光素子の第1の電極と電気的に接続され、 前記容量手段の第1の電極は、前記第

3のトランジスタのゲート電極と電気的に接続され、第2の電極は、前記第2のゲート信

号線と電気的に接続されていることを特徴としている。

【0066】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1

乃至第3のトランジスタと、ダイオードと、発光素子とを有し、 前記第1のトランジス

タのゲート電極は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソ

ース信号線と電気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と

電気的に接続され、 前記第2のトランジスタのゲート電極は、前記第2のトランジスタ

の第2の電極および、前記第3のトランジスタのゲート電極と電気的に接続され、 前記

第3のトランジスタの第1の電極は、前記電流供給線と電気的に接続され、第2の電極は

、前記発光素子の第1の電極と電気的に接続され、 前記ダイオードの第1の電極は、前

記第3のトランジスタのゲート電極と電気的に接続され、第2の電極は、前記第2のゲー

ト信号線と電気的に接続され、 前記第2のゲート信号線の電位を変化させたとき、前記

第1の電極から前記第2の電極、もしくは前記第2の電極から前記第1の電極のいずれか

一方向にのみ電流を生ずることを特徴としている。

【0067】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃

至第5のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極は

、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気

的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と電気的に接続され

、 前記第2のトランジスタのゲート電極は、前記第2のトランジスタの第2の電極と、

前記第3のトランジスタの第1の電極と、前記第4のトランジスタのゲート電極と電気的

に接続され、 前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気

的に接続され、 前記第4のトランジスタの第1の電極は、前記電流供給線と電気的に接

続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、 前記第5のト

ランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第1の電極は

、前記電流供給線と電気的に接続され、第2の電極は、前記第4のトランジスタのゲート

電極と電気的に接続され、 前記第5のトランジスタが導通することによって、前記第4

のトランジスタのゲート・ソース間電圧を0とすることを特徴としている。

【0068】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、第1および第2のゲート信号線と、電流供給線と、第1

乃至第5のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極

は、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電

気的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と電気的に接続さ

れ、 前記第2のトランジスタのゲート電極は、前記第2のトランジスタの第2の電極と

、前記第3のトランジスタの第1の電極と、前記第4のトランジスタのゲート電極と電気

的に接続され、 前記第3のトランジスタのゲート電極は、前記画素より少なくとも1行

前に走査される行の画素の有する前記第1のゲート信号線と電気的に接続され、 前記第

4のトランジスタの第1の電極は、前記電流供給線と電気的に接続され、第2の電極は、

前記発光素子の第1の電極と電気的に接続され、 前記第5のトランジスタのゲート電極

は、前記第2のゲート信号線と電気的に接続され、第1の電極は、前記電流供給線と電気

的に接続され、第2の電極は、前記第4のトランジスタのゲート電極と電気的に接続され

、 前記第5のトランジスタが導通することによって、前記第4のトランジスタのゲート

・ソース間電圧を0とすることを特徴としている。

【0069】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃

至第5のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極は

、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気

的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と電気的に接続され

、 前記第2のトランジスタのゲート電極は、前記第2のトランジスタの第2の電極と、

前記第3のトランジスタの第1の電極と、前記第4のトランジスタのゲート電極と電気的

に接続され、 前記第3のトランジスタのゲート電極は、前記第2のゲート信号線と電気

的に接続され、 前記第4のトランジスタの第1の電極は、前記電流供給線と電気的に接

続され、第2の電極は、前記第5のトランジスタの第1の電極と電気的に接続され、 前

記第5のトランジスタのゲート電極は、前記第3のゲート信号線と電気的に接続され、第

2の電極は、前記発光素子の第2の電極と電気的に接続され、 前記第5のトランジスタ

が非導通となることにより、前記電流供給線から前記発光素子に供給される電流を遮断す

ることを特徴としている。

【0070】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号線と、第1乃至第3のゲート信号線と、電流供給線と、第1乃

至第5のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極は

、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気

的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と電気的に接続され

、 前記第2のトランジスタのゲート電極は、前記第2のトランジスタの第2の電極と、

前記第3のトランジスタの第1の電極と、前記第4のトランジスタのゲート電極と電気的

に接続され、 前記第3のトランジスタのゲート電極は、前記画素より少なくとも1行前

に走査される行の画素の有する前記第1のゲート信号線と電気的に接続され、 前記第4

のトランジスタの第1の電極は、前記電流供給線と電気的に接続され、第2の電極は、前

記第5のトランジスタの第1の電極と電気的に接続され、 前記第5のトランジスタのゲ

ート電極は、前記第3のゲート信号線と電気的に接続され、第2の電極は、前記発光素子

の第2の電極と電気的に接続され、 前記第5のトランジスタが非導通となることにより

、前記電流供給線から前記発光素子に供給される電流を遮断することを特徴としている。

【0071】

本発明の半導体装置は、 前記第3のトランジスタの第2の電極は、リセット用電源線

と電気的に接続されていることを特徴としている。

【0072】

本発明の半導体装置は、 前記第3のトランジスタの第2の電極は、前記画素を除くい

ずれかの行において走査されるいずれかの画素が有するゲート信号線のうちいずれか1本

と電気的に接続されていることを特徴としている。

【0073】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号と、第1および第2のゲート信号線と、電流供給線と、第1乃

至第5のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極は

、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気

的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と電気的に接続され

、 前記第2のトランジスタのゲート電極は、前記第2のトランジスタの第2の電極と、

前記第3のトランジスタの第1の電極と、前記第4のトランジスタのゲート電極と電気的

に接続され、 前記第3のトランジスタのゲート電極は、前記画素の1行前に走査される

行の画素の有する前記第1のゲート信号線と電気的に接続され、第2の電極は、前記第2

のゲート信号線と電気的に接続され、 前記第4のトランジスタの第1の電極は、前記電

流供給線と電気的に接続され、第2の電極は、前記第5のトランジスタの第1の電極と電

気的に接続され、 前記第5のトランジスタのゲート電極は、前記第2のゲート信号線と

電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、 前

記第5のトランジスタが非導通となることにより、前記電流供給線から前記発光素子に供

給される電流を遮断することを特徴としている。

【0074】

本発明の半導体装置は、 発光素子が備えられた画素を有する半導体装置であって、

前記画素は、 ソース信号と、第1および第2のゲート信号線と、電流供給線と、第1乃

至第5のトランジスタと、発光素子とを有し、 前記第1のトランジスタのゲート電極は

、前記第1のゲート信号線と電気的に接続され、第1の電極は、前記ソース信号線と電気

的に接続され、第2の電極は、前記第2のトランジスタの第1の電極と電気的に接続され

、 前記第2のトランジスタのゲート電極は、前記第2のトランジスタの第2の電極と、

前記第3のトランジスタの第1の電極と、前記第4のトランジスタのゲート電極と電気的

に接続され、 前記第3のトランジスタのゲート電極は、前記画素の1行前に走査される

行の画素の有する前記第1のゲート信号線と電気的に接続され、第2の電極は、前記第1

のゲート信号線と電気的に接続され、 前記第4のトランジスタの第1の電極は、前記電

流供給線と電気的に接続され、第2の電極は、前記第5のトランジスタの第1の電極と電

気的に接続され、 前記第5のトランジスタのゲート電極は、前記第2のゲート信号線と

電気的に接続され、第2の電極は、前記発光素子の第1の電極と電気的に接続され、 前

記第5のトランジスタが非導通となることにより、前記電流供給線から前記発光素子に供

給される電流を遮断することを特徴としている。

【0075】

本発明の半導体装置は、 前記半導体装置は、保持容量手段を有し、前記保持容量手段

の第1の電極は、前記第1のトランジスタの第2の電極と電気的に接続され、第2の電極

には、一定電位が与えられ、前期第1のトランジスタの第2の電極における電位を保持す

ることを特徴としている。

【0076】

本発明の半導体装置は、 前記半導体装置は、保持容量手段を有し、前記保持容量手段

の第1の電極は、前記第4のトランジスタのゲート電極と電気的に接続され、第2の電極

には、一定電位が与えられ、前期第4のトランジスタのゲート電極に印加される電位を保

持することを特徴としている。

【0077】

本発明の半導体装置は、 スイッチ素子と、整流性素子とを有し、 前記整流性素子の

第1の電極には、第1の信号V1が入力され、第2の電極は、前記スイッチ素子の第1の

電極と電気的に接続され、 前記スイッチ素子の第2の電極には、ある電位Vが与えられ

る半導体装置の駆動方法であって、 前記スイッチ素子を導通して、前記整流性素子の第

2の電極の電位をVとする第1のステップと、 前記第1のステップから、前記スイッチ

素子を非導通とし、前記整流性素子の両電極間の電圧を、前記整流性素子のしきい値電圧

Vthに収束させる第2のステップと、 前記しきい値電圧Vthを保持し、前記整流性

素子の第2の電極より、前記信号V1から前記しきい値電圧Vthだけオフセットした信

号V2を得る第3のステップとを有することを特徴としている。

【0078】

本発明の半導体装置は、 第1および第2のスイッチ素子と、整流性素子とを有し、

前記第1のスイッチ素子の第1の電極には、第1の信号V1が入力され、第2の電極は、

前記整流性素子の第1の電極と電気的に接続され、 前記整流性素子の第2の電極は、前

記第2のスイッチ素子の第1の電極と電気的に接続され、 前記第2のスイッチ素子の第

2の電極には、ある電位Vが与えられる半導体装置の駆動方法であって、 前記第2のス

イッチ素子を導通して、前記整流性素子の第2の電極の電位をVとする第1のステップと

、 前記第1のステップから、さらに前記第1のスイッチ素子を導通して、前記整流性素

子第1の電極の電位をV1とする第2のステップと、 前記第2のステップから、前記第

2のスイッチを非導通とし、前記整流性素子の両電極間の電圧を、前記整流性素子のしき

い値電圧Vthに収束させる第3のステップと、 前記第3のステップから、さらに第1

のスイッチを非導通とし、前記しきい値電圧Vthを保持し、前記整流性素子の第2の電

極より、前記信号V1から前記しきい値電圧Vthだけオフセットした信号V2を得る第4

のステップとを有することを特徴としている。

【0079】

本発明の半導体装置は、 第1および第2の整流性素子とを有し、 前記第1の整流性

素子の第1の電極には、第1の信号V1が入力され、第2の電極は、前記第2の整流性素

子の第1の電極と電気的に接続され、 前記第2の整流性素子の第2の電極には、ある電

位Vが与えられる半導体装置の駆動方法であって、 前記第1の整流性素子のしきい値電

圧をVthとし、 V1>(V−|Vth|)のとき、前記第2の整流性素子の第2の電極

の電位をV→V0(V0>V)とし、前記第2の整流性素子を流れる電流を遮断する第1の

ステップと、 前記第1の整流性素子の第2の電極より、前記信号V1から前記しきい値

電圧Vthだけオフセットした信号V2を得る第2のステップとを有することを特徴とし

ている。

【0080】

本発明の半導体装置は、 前記整流性素子とは、ゲート・ドレイン間を接続したトラン

ジスタを用いてなり、 前記トランジスタの極性がNチャネル型であり、しきい値電圧が

Vthであるとき、 V1+|Vth|<V、かつV2=V1+Vthを満たし、 前記トラ

ンジスタの極性がPチャネル型であり、しきい値電圧がVthであるとき、 V1>V+

Vth、かつV2=V1−|Vth|を満たすことを特徴としている。

【0081】

本発明の半導体装置は、 前記整流性素子とは、ダイオードを用いてなり、 前記ダイ

オードのしきい値電圧がVthであるとき、 V1>V+Vth、かつV2=V1−|Vth

|もしくは、 V1<V−|Vth|、かつV2=V1+Vthを満たすことを特徴としている

。

【発明の効果】

【0082】

本発明によると、容量手段の容量値等のばらつきの影響等を受けることなく、正常にT

FTのしきい値電圧のばらつきを補正することが出来る。さらに、図22、23に示した

ように、発光装置に応用する場合、従来例では1水平期間内に行う動作が多かったのに対

して、本発明はより簡単な動作原理に基づいており、動作タイミングも簡単なため、回路

の高速動作が可能となり、特にデジタル階調方式と時間階調方式とを組み合わせた方法に

よって表示を行う際に、よりビット数の高い映像信号を用いて高品質な映像の表示が可能

となる。

【図面の簡単な説明】

【0083】

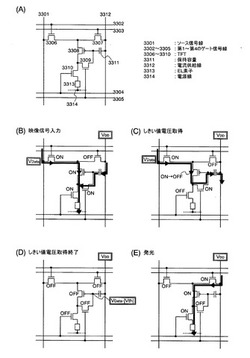

【図1】本発明の一実施形態を示す図。

【図2】図1に示した構成による動作を説明する図。

【図3】本発明の一実施形態およびその動作を説明する図。

【図4】本発明の一実施形態およびその動作を説明する図。

【図5】本発明の一実施形態およびその動作を説明する図。

【図6】本発明の一実施形態およびその動作を説明する図。

【図7】本発明の一実施形態およびその動作を説明する図。

【図8】本発明の一実施形態を示す図。

【図9】本発明の一実施形態およびその動作を説明する図。

【図10】本発明の一実施形態およびその動作を説明する図。

【図11】図9に示した構成による動作のタイミングを示す図。

【図12】図10に示した構成による動作のタイミングを示す図。

【図13】発光装置の作製工程を説明する図。

【図14】発光装置の作製工程を説明する図。

【図15】発光装置の作製工程を説明する図。

【図16】本発明の一実施形態およびその動作を説明する図。

【図17】図16に示した構成による動作を説明する図。

【図18】本発明の一実施形態およびその動作を説明する図。

【図19】図18に示した構成による動作を説明する図。

【図20】一般的な発光装置の画素の構成を示す図。

【図21】デジタル階調方式と時間階調方式とを組み合わせた方法による動作を説明する図。

【図22】TFTのしきい値電圧の補正を行う画素の構成の一例を示す図。

【図23】図22に示した構成による動作を説明する図。

【図24】アナログ信号方式による発光装置の概要を説明する図。

【図25】図24にて用いるソース信号線駆動回路およびゲート信号線駆動回路の構成例を示す図。

【図26】デジタル信号方式による発光装置の概要を説明する図。

【図27】図26にて用いるソース信号線駆動回路の構成例を示す図。

【図28】D−FFを用いた一般的なシフトレジスタによるパルス幅調整の例を示す図。

【図29】本発明の動作原理を説明する図。

【図30】発光装置の上面図および断面図。

【図31】本発明が適用可能な電子機器の例を示す図。

【図32】本発明の実施形態とは異なる構成例および動作を説明する図。

【図33】本発明の実施形態とは異なる構成例および動作を説明する図。

【図34】本発明の実施形態とは異なる構成例および動作を説明する図。

【図35】本発明の実施形態とは異なる構成例および動作を説明する図。

【図36】本発明の実施形態とは異なる構成例および動作を説明する図。

【図37】本発明の実施形態とは異なる構成例および動作を説明する図。

【図38】本発明の実施形態とは異なる構成例および動作を説明する図。

【図39】本発明の実施形態とは異なる構成例および動作を説明する図。

【図40】本発明の実施形態とは異なる構成例および動作を説明する図。

【図41】本発明のしきい値電圧の補正原理を用いて電流源回路を構成する例を示す図。

【図42】本発明のしきい値電圧の補正原理を用いて電流源回路を構成する例を示す図。

【図43】本発明のしきい値電圧の補正原理を用いて電流源回路を構成する例を示す図。

【図44】本発明のしきい値電圧の補正原理を用いて電流源回路を構成する例を示す図。

【発明を実施するための形態】

【0084】

[実施の形態1]

図1(A)に、本発明の第1の実施形態を示す。ソース信号線101、第1、第2のゲー

ト信号線102、103、TFT104〜107、EL素子109、電流供給線110、

リセット用電源線111、電源線112を有する。さらに、映像信号を保持するための容

量手段108を設けても良い。

【0085】

TFT104のゲート電極は、第1のゲート信号線102に接続され、第1の電極は、

ソース信号線101に接続され、第2の電極は、TFT105の第1の電極に接続されて

いる。TFT105のゲート電極と第2の電極とは互いに接続され、TFT106の第1

の電極および、TFT107のゲート電極に接続されている。TFT106のゲート電極

は、第2のゲート信号線103に接続され、第2の電極は、リセット用電源線111に接

続されている。TFT107の第1の電極は、電流供給線110に接続され、第2の電極

は、EL素子109の第1の電極に接続されている。EL素子109の第2の電極は、電

源線112に接続され、電流供給線110とは互いに電位差を有している。容量手段10

8を設ける場合には、TFT107のゲート電極と、電流供給線110等の定電位を得ら

れる部位との間に設ければ良い。また、TFT104の第2の電極と、電流供給線110

等の定電位との間に設けても良いし、保持容量の値を大きくしたい場合等には、両方に設

けても良い。

【0086】

図1(B)は、第1、第2のゲート信号線に入力するパルスのタイミングを示している。

図1(B)および図2を用いて、動作について説明する。なお、ここではTFT104、1

06はNチャネル型として構成しているので、ゲート信号線の電位がHレベルのときにT

FTがONし、LレベルのときにTFTがOFFするものとしているが、TFT104、

106は単にスイッチング素子として機能するものであり、その極性は問わない。

【0087】

今、ソース信号線101の電位がVDD、電流供給線の電位がVDD、リセット用電源線の

電位がVReset(<VDD−|Vth|)であるとし、TFT105については、ゲート(G)、ソ

ース(S)、ドレイン(D)を図2(A)のように定義する。まず、第2のゲート信号線103

にパルスが入力されてTFT106がONする。よって、図2(A)に示すように、TFT

105のドレイン電位が低下して、TFT105のゲート・ソース間電圧VGS<0となり

、さらにしきい値電圧Vthの絶対値を上回って、TFT105がONする。同時に、TF

T107のゲート・ソース間電圧もまたしきい値電圧の絶対値を上回るため、ONする。

【0088】

続いて、TFT106がOFFし、第1のゲート信号線102にパルスが入力されてT

FT104がONする。ここで、ソース信号線には映像信号が出力されてきており、その

電位がVData(VReset<VData<VDD)となっているため、TFT105のソース電位が

VDataへと上昇する。すると、TFT105を経て、TFT107のゲート電極の電位、

すなわちTFT105のゲート電極の電位も上昇する。その電位がVData−|Vth|となっ

たところで、TFT105のゲート・ソース間電圧がそのしきい値電圧に等しくなるので

、TFT105がOFFし、TFT107のゲート電極の電位、すなわちTFT105の

ゲート電極の電位の上昇が停止する(図2(B))。

【0089】

続いて、TFT104がOFFし、発光期間に移る。今、TFT107のゲート電極に

は、所望の映像信号の電位に、しきい値電圧を上乗せした電位が印加されており、図2(

C)に示すように、それに見合った電流が電流供給線110よりTFT107を経てEL

素子109に流れ、発光する。ところで、実際には、図2(A)の初期化の段階でTFT1

07のゲート電極には、しきい値電圧の絶対値を上回る電位が印加されてONし、最大輝

度で発光しているが、第1、第2のゲート信号線が選択される期間は、実際の発光期間に

比べて十分に短く、いかなる場合にも同様に発光するため、相対的な輝度のばらつきに影

響することはない。

【0090】

以上のような動作によって、画素の制御を行う。このとき、TFT107を流れるドレ

イン電流IDSは、式(8)にて表される。

【0091】

【数8】

【0092】

仮に画面内の画素において、TFTのしきい値電圧のばらつきが生じた場合にも、1つ

の画素を構成するTFT、具体的にはTFT105、107のしきい値電圧が等しければ

、その項は相殺され、IDSはしきい値電圧の項を含まなくなる。つまり、しきい値電圧に

関係なく、IDSを決定することが出来、しきい値電圧のばらつきの影響を排除することが

出来る。

【0093】

[実施の形態2]

前述のアナログ階調方式とは異なる駆動方式として、TFTのしきい値電圧等がON電

流に影響しにくい領域を用いて、EL素子を輝度100%、0%の2つの状態のみで駆動

するデジタル階調方式が提案されている。この方式では、白、黒の2階調しか表現出来な

いため、時間階調方式等と組み合わせて多階調化を実現している。

【0094】

デジタル階調方式と時間階調方式とを組み合わせた方法を用いる場合の半導体装置の画

素の構成は、図21(A)に示したようなものがある。スイッチング用TFT2104、駆

動用TFT2105に加え、消去用TFT2106を用いることによって、発光時間の長

さを細かく制御することが可能となっている。

【0095】

デジタル階調方式と時間階調方式とを組み合わせた場合、図21(B)に示すように、1

フレーム期間を複数のサブフレーム期間に分割する。各サブフレーム期間は、図21(C)

に示すように、アドレス(書き込み)期間と、サステイン(発光)期間と、消去期間とを有す

る。表示ビット数に応じた数のサブフレーム期間を設け、各サブフレーム期間におけるサ

ステイン(発光)期間の長さを、2(n-1):2(n-2):・・・:2:1とし、各サステイン(

発光)期間でEL素子の発光、もしくは非発光の選択をし、EL素子が発光している合計

期間の長さの差を利用して階調表現を行う。発光している期間が長ければ輝度が高く、短

ければ輝度が低くなる。なお、図21においては4ビット階調の例を示しており、1フレ

ーム期間は4つのサブフレーム期間に分割され、サステイン(発光)期間の組み合わせに

よって、24=16階調を表現出来る。

【0096】

時間階調方式を用いて多階調化を図る場合、下位ビットのサステイン(発光)期間の長さ

がより短くなるため、サステイン(発光)期間の終了後、直ちに次のアドレス期間を開始し

ようとすると、異なるサブフレーム期間のアドレス(書き込み)期間が重複する期間が生ず

る。その場合、ある画素に入力される映像信号が、同時に異なる画素にも入力されてしま

うため、正常な表示が出来なくなる。消去期間は、このような問題を解決するために設け

られており、図21(B)に示すように、Ts3の後、およびTs4の後で、異なる2つの

アドレス(書き込み)期間が重複しないように設けられる。よって、サステイン(発光)期間

が十分に長く、異なる2つのアドレス(書き込み)期間の重複が生ずる心配の無いSF1、

SF2においては、消去期間は設けられていない。

【0097】

図9(A)は、実施の形態1において示した構成の画素に、第3のゲート信号線913、

消去用TFT914を追加し、デジタル階調方式と時間階調方式とを組み合わせた方法を

用いるものである。消去用TFT914のゲート電極は、第3のゲート信号線913に接

続され、第1の電極は、TFT907のゲート電極に接続され、第2の電極は、電流供給

線910に接続されている。また、映像信号を保持するために、容量手段908を設ける

場合には、TFT907のゲート電極と、電流供給線910等の定電位を得られる部位と

の間に設ければ良い。また、TFT904の第2の電極と、電流供給線910等の定電位

との間に設けても良いし、保持容量の値を大きくしたい場合等には、両方に設けても良い

。

【0098】

初期化および映像信号の入力の動作は、実施の形態1にて示したものと同様である。な

お、初期化および映像信号の入力を行っている期間は、消去用TFT914はOFFして

いる。

【0099】

ここで、サステイン(発光)期間から消去期間における動作について、図9および図11

を用いて説明する。図11(A)は、図21(A)に示したものと同様であり、1フレーム期

間は、図11(B)に示すように、4つのサブフレーム期間を有する。サステイン(発光)

期間が短いサブフレーム期間SF3、SF4においては、それぞれ消去期間Te3、Te

4を有している。ここでは、SF3での動作を例として説明する。

【0100】

映像信号の入力が終了した後、図9(B)に示すように、TFT907のゲート・ソース

間電圧に応じた電流がEL素子909に流れて発光する。その後、当該サステイン(発光)

期間の終了するタイミングに達すると、第3のゲート信号線913にパルスが入力されて

消去用TFT914がONし、図9(C)に示すように、TFT907のゲート・ソース

間電圧を0とする。よってTFT907がOFFし、EL素子909への電流が遮断され

、強制的にEL素子909は非発光となる。

【0101】

これらの動作をタイミングチャートとして、図11(C)に示した。サステイン(発光

)期間Ts3の後、第3のゲート信号線913にパルスが入力されてEL素子909が非

発光となってから、次に第2のゲート信号線903にパルスが入力されて、初期化が始ま

るまでの期間が消去期間Te3となる。

【0102】

本実施形態にて用いている消去用TFT914は、他の実施形態における構成と組み合

わせて用いることも出来る。

【0103】

[実施の形態3]

実施の形態2において、消去期間においての動作は、TFT907のゲート・ソース間

電圧を0としてOFFさせることによって、EL素子909への電流の供給を遮断してい

る。この他の方法を用いた例を図10(A)に示す。実施の形態2においては、消去用T

FT914はTFT907のゲート電極と、電流供給線910との間に設けられていたの

に対し、本実施形態においては、消去用TFT914は、TFT907とEL素子909

との間に設けられている。

【0104】

初期化および映像信号の入力の動作については、実施の形態1と同様である。

消去用TFT914は、サステイン(発光)期間のみONしている。初期化、映像信号の

入力、および消去期間においてはOFFし、EL素子909への電流を遮断する。

【0105】

実施の形態2と動作面で異なる点としては、実施の形態2の場合は、一度消去用TFT

914をONし、TFT907のゲート・ソース間電圧を0とすれは、以後はEL素子9

09が発光しないため、図11に示すように、消去期間の開始するタイミングで、短いパ

ルスを入力すれば良いが、本実施形態においては、消去用TFTは、サステイン期間を通

じてONしている必要があるため、第3のゲート信号線913には、図12に示すように

、サステイン(発光)期間と同じ長さのパルスを入力する。

【0106】

このようなパルスを生成するのには、特別な回路は必要とせず、図28(A)

に示すような、クロックドインバータ2802、インバータ2803等からなるD−フリ

ップフロップ回路2801を複数段用いてなるシフトレジスタを用いて、外部より入力す

るスタートパルスの長さを変更することによって、図28(B)に示すように、出力され

るパルスの長さを変更して生成すれば良い。サステイン(発光)期間に合わせるための微

調整は、パルス幅調整回路等を用いて容易に行うことが出来る。

【0107】

なお、図9および図10において、消去用TFT914はNチャネル型TFTを用い、

第3のゲート信号線がHレベルのときにONし、LレベルのときにOFFするが、特にそ

の極性は問わない。

【0108】

本実施形態にて用いている消去用TFT914は、他の実施形態における構成と組み合

わせて用いることも出来る。

【0109】

[実施の形態4]

実施の形態1に示した構成において、1画素を駆動するのに用いる信号線および電源線

は、ソース信号線、第1および第2のゲート信号線、電流供給線、リセット用電源線であ

る。実施の形態2、3においては、さらに第3のゲート信号線を用いて消去用TFTの制

御を行う。図20に示した従来の構成や、図21に示した消去用TFTを有する構成と比

較しても、画素部において配線の占める面積が大きく、開口率が低下するのは明らかであ

る。

【0110】

そこで、本実施形態においては、図16に示すような構成の画素を用いる。図16(A

)に示すように、ソース信号線1601、第1、第2のゲート信号線1603、1604

、TFT1605〜1609、容量手段1610、EL素子1611、電流供給線161

2等を有する。配線数は1画素あたり4本となっている。

【0111】

図16(A)に示した画素が、i行目の画素であるとして、構成について説明する。T

FT1605のゲート電極は、i行目の第1のゲート信号線1603に接続され、第1の

電極は、ソース信号線1601に接続され、第2の電極は、TFT1606の第1の電極

に接続されている。TFT1606のゲート電極と第2の電極とは互いに接続され、TF

T1607の第1の電極および、TFT1608のゲート電極に接続されている。TFT

1607のゲート電極は、i−1行目のゲート信号線1602に接続され、第2の電極は

、第2のゲート信号線1604に接続されている。TFT1608の第1の電極は、電流

供給線1612に接続され、第2の電極は、TFT1609の第1の電極に接続されてい

る。TFT1609のゲート電極は、i行目の第2のゲート信号線1604に接続され、

第2の電極は、EL素子1611の第1の電極に接続されている。EL素子1611の第

2の電極は、電源線1613に接続され、電流供給線1612とは互いに電位差を有する

。容量手段1610は、TFT1608のゲート電極を含むノードと、電流供給線161

2との間に接続され、サステイン(発光)期間中に、TFT1608のゲート電極に印加

される電位を保持するものである。

【0112】

動作について、図16、図17を用いて説明する。なお、ここでは、TFT1605、

1607、1609はいずれもNチャネル型TFTを用い、ゲート電極にHレベルのパル

スが入力されてONし、Lレベルが入力されてOFFするものとして説明する。ここで、

TFT1609にNチャネル型TFTを用いているのは、TFT1607をONして初期

化を行う際、i行目の第2のゲート信号線がLレベルである必要があり、かつこのときT

FT1609がOFFしている必要があるためである。

【0113】

今、ソース信号線1601の電位がVDD、電流供給線の電位がVDD、ゲート信号線がL

レベルにあるときの電位がVReset(<VDD−|Vth|)であるとし、TFT1606につい

ては、ゲート(G)、ソース(S)、ドレイン(D)を図17(A)のように定義する。

【0114】

i−1行目の第1のゲート信号線1602が選択されているとき、すなわちi−1行目

において映像信号の入力が行われているとき、i行目の画素においては、TFT1607

がONする。このとき、i行目の第2のゲート信号線1604はLレベルであるので、図

17(A)に示すように、TFT1608のゲート電極の電位が下がる。これによりTF

T1608のゲート電極の電位が初期化される。

【0115】

i−1行目において、映像信号の入力が終了すると、i−1行目の第1のゲート信号線

1602はLレベルとなり、TFT1607がOFFする。一方、i行目の第1のゲート

信号線1603が選択されてHレベルとなり、TFT1605がONして、i行目におい

て映像信号が入力される。映像信号の電位がVData(ただしVData+Vth<VDD)である

とき、TFT1606のソース・ドレイン間電圧はVthに等しく、TFT1608のゲー

ト電極の電位は、(VData−Vth)

となる。このとき、i+1行目においては、前述と同様に初期化が行われている(図17

(B))。

【0116】

映像信号の入力が終了し、i行目においてはサステイン(発光)期間に移る。

i行目の第2のゲート信号線1604にHレベルのパルスが入力されて、TFT1609

がONし、図17(C)に示すように、EL素子には、TFT1608のゲート・ソース

間電圧に応じた電流が流れて発光する。

【0117】

本実施形態の特徴は、ある行の初期化を行うためのTFT1607の制御に、前行のゲ

ート信号線選択パルスを利用する点と、選択されていないゲート信号線が一定電位である

ことを利用し、リセット用の電源線として利用している点にある。このような構成とする

ことによって、信号線の本数を最小限に留めて高開口率を得、かつ実施の形態2と同様の

動作を行う構成が実現する。

【0118】

なお、TFT1607の第2の電極は、第2のゲート信号線1604に接続されている

が、TFT1607がONするタイミングにおいてLレベルとなっている信号線であれば

、他の信号線でも良い。また、TFT1607は、i−1行目の第1のゲート信号線によ

って制御されているが、i行目よりも前の行であれば、他の行でも良い。

【0119】

[実施の形態5]

実施の形態4においては、TFT1609はNチャネル型としていたが、これは初期化

に用いたTFT1607のソース・ドレインの一端が、i行目の第2のゲート信号線16

04に接続されていたためであったことは前述の通りである。

ところで、画素内では、開口率を高くするため、あるいはTFTの特性にばらつきが生じ

にくくするためには、できるだけ近接配置することが望ましい。そこで、図18(A)に

示すように、TFT1809をPチャネル型とし、TFT1808とより近接して配置で

きる構成とする。

【0120】

このとき、初期化に用いるTFT1807の接続が一部変更される。TFT1807の

ゲート電極は、i−1行目の第1のゲート信号線に接続され、第1の電極は、TFT18

08のゲート電極に接続されている。これは、前述のように、初期化の際にはTFT18

07がONして、TFT1808のゲート電極の電位を下げなければならない。よって、

TFT1807のソース・ドレインの一端の接続先は、その期間ではLレベルとなってい

る必要がある。TFT1809をPチャネル型としたことによって、i行目の画素で初期

化を行っている期間の、i行目の第2のゲート信号線1804の電位はHレベルであるた

めに用いることが出来ない。よってその接続先を、i行目の第1のゲート信号線1802

とした。

【0121】

回路の動作については、図19(A)〜(C)に示すが、i行目の第2のゲート信号線

1804のHレベルとLレベルの電位が反転している点を除き、実施の形態4と同様であ

るので、ここでは詳細な説明は省略する。TFT1809は、そのON、OFFによって

EL素子への電流供給経路の導通もしくは非導通の選択を行うためのスイッチング素子と

して用いているため、動作上、その極性は問わない。よって、実施の形態4および本実施

形態に関しては、実際の回路レイアウト等の事情によって、適宜選択すれば良い。

【0122】

なお、TFT1807の第2の電極は、第2のゲート信号線1803に接続されている

が、TFT1807がONするタイミングにおいてLレベルとなっている信号線であれば

、他の信号線でも良い。また、TFT1807は、i−1行目の第1のゲート信号線によ

って制御されているが、i行目よりも前の行であれば、他の行でも良い。

【0123】

[実施の形態6]

実施の形態1にて示した構成の接続を一部変更したものを図3(A)に示す。

実施の形態1においては、図1に示したように、ゲート・ドレイン間を接続したTFT1

05は、TFT104の第2の電極と、TFT107のゲート電極との間に設けられてい

たが、本実施形態の構成によると、ゲート・ドレイン間を接続したTFT305は、ソー

ス信号線301と、TFT304の第1の電極との間に設けられている。また、映像信号

を保持するために、容量手段308等を設ける場合には、TFT304の第2の電極と、

電流供給線310等の定電位との間に設ければ良い。

【0124】

図3(B)〜(D)を用いて、動作について説明する。なお、ここではTFT304、

306はNチャネル型として構成しているので、ゲート信号線の電位がHレベルのときに

TFTがONし、LレベルのときにTFTがOFFするものとしているが、TFT304

、306は単にスイッチング素子として機能するものであり、その極性は問わない。

【0125】

今、ソース信号線301の電位がVDD、電流供給線の電位がVDD、リセット用電源線の

電位がVReset(<VDD−|Vth|)であるとし、TFT305については、ゲート(G)、ソ

ース(S)、ドレイン(D)を図3(B)のように定義する。

【0126】

まず、第2のゲート信号線303にパルスが入力されてTFT306がONする。TF

T306がONしている間に、第1のゲート信号線302にパルスが入力されてTFT3

04がONする。すると、図3(B)に示すように、TFT305のドレイン電位が低下し

て、TFT305のゲート・ソース間電圧VGS<0となり、さらにしきい値電圧Vthの絶

対値を上回って、TFT305がONする。

ここで、TFT306は、TFT305がONして前述の動作が行われ、TFT305が

ONした瞬間、速やかにOFFするようにする。TFT305、306が両方ともONし

ている状態が長く続くと、やがてTFT305がONし、ソース信号線301−リセット

用電源線311間に電流パスが生ずるため、TFT307のゲート電極の電位が低くなら

ない場合があるためである。同時に、TFT307のゲート・ソース間電圧もまたしきい

値電圧の絶対値を上回るため、ONする。

【0127】

続いて、映像信号の入力が行われる。ソース信号線301には映像信号が出力されてき

ており、その電位がVData(VReset<VData<VDD)となっているため、TFT305の

ソース電位がVDataへと上昇する。すると、TFT305、304を経て、TFT307

のゲート電極の電位も上昇する。その電位がVData−|Vth|となったところで、TFT3

05のゲート・ソース間電圧がそのしきい値電圧に等しくなるので、TFT305がOF

Fし、TFT307のゲート電極の電位も停止する(図3(C))。

【0128】

続いて、発光期間に移る。TFT307がONした時点で発光が始まるが、映像信号が

入力された後、TFT307のゲート電位が(VData−Vth)となって初めて、それに応

じた電流が電流供給線310よりTFT307を経てEL素子309に流れ、発光する。

【0129】

[実施の形態7]

実施の形態6にて示した構成の接続を一部変更したものを図4(A)に示す。

実施の形態6においては、図3(A)に示したように、TFT304は、TFT305の

第2の電極と、TFT306の第1の電極との間に設けられていたが、本実施形態の構成

によると、TFT404は、TFT406の第1の電極と、TFT407のゲート電極と

の間に設けられている。また、映像信号を保持するために、容量手段408を設ける場合

には、TFT407のゲート電極と、電流供給線410等の定電位を得られる部位との間

に設ければ良い。また、TFT405の第2の電極と、電流供給線410等の定電位との

間に設けても良いし、保持容量の値を大きくしたい場合等には、両方に設けても良い。

【0130】

図4(B)〜(D)を用いて、動作について説明する。なお、ここではTFT404、

406はNチャネル型として構成しているので、ゲート信号線の電位がHレベルのときに

TFTがONし、LレベルのときにTFTがOFFするものとしているが、TFT404

、406は単にスイッチング素子として機能するものであり、その極性は問わない。

【0131】

今、ソース信号線401の電位がVDD、電流供給線の電位がVDD、リセット用電源線の

電位がVReset(<VDD−|Vth|)であるとし、TFT405については、ゲート(G)、ソ

ース(S)、ドレイン(D)を図4(B)のように定義する。

【0132】

まず、第1、第2のゲート信号線402、403にパルスが入力されてTFT404、

406がONする。すると、図4(B)に示すように、TFT405のドレイン電位が低

下して、TFT405のゲート・ソース間電圧VGS<0となり、さらにしきい値電圧Vth

の絶対値を上回って、TFT405がONする。これにより、初期化が完了する。なお、

ここではTFT404はOFFしていても構わない。

【0133】

続いて、映像信号の入力が行われる。第2のゲート信号線403がLレベルとなってT

FT406がOFFし、第1のゲート信号線402がHレベルとなってTFT404がO

Nする。よって、TFT407のゲート・ソース間電圧もまたしきい値電圧の絶対値を上

回ってONする。今、ソース信号線の電位はVDDからVDataとなっており、それに伴って

TFT407のゲート電極に印加される電位は、(VData−Vth)に落ち着く。

【0134】

続いて、発光期間に移る。TFT407がONした時点で発光が始まるが、映像信号が

入力された後、TFT407のゲート電位が(VData−Vth)となって初めて、所望の電

流がEL素子409に流れる。同時に、第1のゲート信号線がLレベルとなってTFT4

04がOFFする。

【0135】

[実施の形態8]

実施の形態1〜7においては、映像信号が入力される前の初期化には、あるTFTを用

いて行っている。図5(A)は、TFTの代わりにダイオード507を用いる。ダイオー

ド507の第1の電極は、TFT505のゲート電極および第2の電極に接続され、第2

の電極は、第2のゲート信号線503に接続されている。また、映像信号を保持するため

に、容量手段508を設ける場合には、TFT506のゲート電極と、電流供給線510

等の定電位を得られる部位との間に設ければ良い。また、TFT504の第2の電極と、

電流供給線510等の定電位との間に設けても良いし、保持容量の値を大きくしたい場合

等には、両方に設けても良い。

【0136】

実施の形態1と異なる点は、初期化の際の動作のみである。ここでは、映像信号の入力

および発光動作についての説明は省略し、図5(B)を用いて、初期化の際の動作につい

て説明する。

【0137】

初期状態において、第2のゲート信号線503は、Hレベルにしておく。初期化のタイ

ミングで、第2のゲート信号線503の電位を下げると、ダイオードには順バイアスがか

かり、電位の高い方から低い方、つまり、図5(B)に示すように電流が生じ、TFT5

05、506のゲート電位が低下する。やがてTFT505、506のしきい値電圧Vth

の絶対値を、TFT505、506のゲート・ソース間電圧が上回ると、TFT505が

ONする。その後、映像信号の入力が行われるときには、第2のゲート信号線503は、

再びHレベルに戻しておく。その後、映像信号が入力されるが、ダイオード507には、

常に逆バイアスがかかっている状態であり、電流は生じない。

【0138】

以後、実施の形態1と同様にして、EL素子509に所望の電流が流れ、発光する。

【0139】

図5(C)は、ダイオード507に代わって容量手段557を設けた例を示している。

容量手段557の第1の電極は、TFT555のゲート電極および第2の電極と、TFT

556のゲート電極に接続され、第2の電極は、第2のゲート信号線553に接続されて

いる。この場合も、動作は図5(B)と同様であり、初期状態において、第2のゲート信

号線553をHレベルにしておき、初期化のタイミングで、第2のゲート信号線553の

電位を下げる。このとき、TFT554がOFFしているので、容量手段557の第2の

電極は浮遊状態であり、容量手段557の第1の電極の電位が低下すると、容量結合によ

って、第2の電極の電位、すなわちTFT555、556のゲート電極の電位も低下する

。やがてTFT555、556のしきい値電圧Vthの絶対値を、TFT555、556の

ゲート・ソース間電圧が上回ると、TFT555、556がONする。

【0140】

その後、TFT554がONして、映像信号の入力が行われる。第2のゲート信号線5

53は、今Lレベルとなっているが、映像信号が入力されている間、すなわちTFT55

4がONしている間にHレベルにしておけば良い。

【0141】

以後、実施の形態1と同様にして、EL素子559に所望の電流が流れ、発光する。

【0142】

本実施形態の構成によると、図1(A)においては初期化に用いるゲート信号線と、リ

セット用電源線とを必要としたのに対し、初期化に用いるゲート信号線(図5においては

、第2のゲート信号線503、553)のみで動作が可能である。よって画素部に必要な

配線を1本減らすことが出来、高開口率化に寄与する。

【0143】

[実施の形態9]

実施の形態1にて示した構成の接続を一部変更したものを図6(A)に示す。

実施の形態1においては、図1に示したように、TFT106の第2の電極は、リセット

用電源線111に接続されているのに対し、本実施形態においては、図6(A)に示すよ

うに、i行目の画素においては、i+1行目の第1のゲート信号線に接続されている。各

動作は全て実施の形態1と同様である。i行目の初期化を行うときには、i+1行目はま

だゲート信号線が選択されておらず、Lレベルとなっている。ゲート信号線選択パルスが

入力されていない期間、ゲート信号線が一定電位となることから、図6(B)に示すよう

に、i+1行目のゲート信号線をリセット用電源線として共用する。このようにして、実

施の形態8と同様に、リセット用電源線を省略することが出来る。

【0144】

この場合、共用するゲート信号線は、選択されていない状態でLレベルとなっている必

要がある。よって、当該ゲート信号線に入力されるパルスによって制御されるTFT、す

なわちTFT605は、Nチャネル型とする。

【0145】

本実施形態の構成は、他の実施形態とも組み合わせることが可能である。例えば、図9

、図10等に示したように、消去用のゲート信号線を追加する場合など、TFT906を

本実施形態に従って接続することで、リセット用電源線911を省略することが可能であ

る。

【0146】

また、映像信号を保持するために、容量手段609を設ける場合には、TFT608の

ゲート電極と、電流供給線611等の定電位を得られる部位との間に設ければ良い。また

、TFT605の第2の電極と、電流供給線611等の定電位との間に設けても良いし、

保持容量の値を大きくしたい場合等には、両方に設けても良い。

【0147】

[実施の形態10]

実施の形態9と同様、実施の形態1にて示した構成の接続を一部変更したものを図7(

A)に示す。実施の形態1においては、図1に示したように、TFT106の第2の電極

は、リセット用電源線111に接続されているのに対し、本実施形態においては、TFT

704の第2の電極に接続されている。また、映像信号を保持するために、容量手段70

8を設ける場合には、TFT707のゲート電極と、電流供給線710等の定電位を得ら

れる部位との間に設ければ良い。また、TFT704の第2の電極と、電流供給線710

等の定電位との間に設けても良いし、保持容量の値を大きくしたい場合等には、両方に設

けても良い。

【0148】

図7(B)〜(E)を用いて、動作について説明する。図7(B)〜(D)は初期化〜

発光に至るまでの回路の動作を示すものであり、図7(E)は、第1、第2のゲート信号

線702、703および、ソース信号線701のそれぞれの電位について示したものであ

る。図7(E)中、iと示してある期間が初期化(図7(B))、iiと示してある期間が

映像信号の入力(図7(C))、iiiと示してある期間が発光期間(図7(D))である

。

【0149】

まず、第1,第2のゲート信号線702、703がHレベルとなり、TFT704、7

06がONする。このとき、ソース信号線701の電位は、図7(E)

に示すようにVResetとしておく。この電位は、映像信号よりもさらにTFT705のし

きい値電圧の分だけ低い電位もしくはそれ以下の電位としておく。すると、図7(B)に

示すように、TFT705、707のゲート電極の電位が低くなり、TFT707のしき

い値電圧の絶対値を上回ったところで、TFT707がONする。TFT705に関して

は、図7(B)から明らかなように、ゲート・ソース間電圧が0となっているため、OF

Fしている。

【0150】

続いて、第2のゲート信号線703がLレベルとなってTFT706がOFFし、ソー

ス信号線の電位がVResetからVDataとなって映像信号の入力が開始される。ここで、VR

eset+|Vth|<VDataであるから、TFT705のゲート・ソース間電圧はしきい値電圧

の絶対値を上回り、ONする。よって映像信号は、図7(C)に示されるように、TFT

707のゲート電極に、しきい値電圧が上乗せされて印加される。

【0151】

続いて、第1のゲート信号線702がLレベルとなってTFT704がOFFし、発光

期間に移る。今、TFT707のゲート電極には、映像信号VDataに、しきい値電圧Vth

が上乗せされて印加されており、それに応じた電流がEL素子709に供給されて発光す

る。

【0152】

また、TFT706の第2の電極は、今、TFT704の第2の電極に接続されている

が、ソース信号線701に接続し、TFT707のゲート電極とソース信号線との間に設

けるようにしても同様のタイミングによって動作が可能である。

【0153】

[実施の形態11]

本発明において、映像信号を保持するために容量手段を用いて良いことは前述のとおり

である。容量手段の配置例としては、実施の形態1などに示したとおり、図8(A)に示

すように、TFT804と電流供給線810等の定電位との間に設け、TFT805のソ

ース電位を保持する形としても良いし、図8(B)のように、TFT807のゲート電極

と、電流供給線810等の定電位との間に設け、TFT807のゲート電極の電位を保持

する形としても良い。なお、容量手段の接続先は、電流供給線に限らず、一定の電位を持

ったノードに接続すれば電位の保持が出来るので、その場所は問わない。

【0154】

以下に、本発明の実施例について記載する。

【実施例1】

【0155】

本実施例においては、映像信号にアナログ映像信号を用いて表示を行う発光装置の構成

について説明する。図24(A)に、発光装置の構成例を示す。基板2401上に、複数の

画素がマトリクス状に配置された画素部2402を有し、画素部周辺には、ソース信号線

駆動回路2403および、第1、第2のゲート信号線駆動回路2404、2405を有し

ている。図24(A)においては、2組のゲート信号線駆動回路を用い、図1に示した画素

における第1、第2のゲート信号線をそれぞれ制御するものである。

【0156】

ソース信号線駆動回路2403、第1、第2のゲート信号線駆動回路2404、240

5に入力される信号は、フレキシブルプリント基板(Flexible Print Circuit:FPC)2

406を介して外部より供給される。

【0157】

図24(B)に、ソース信号線駆動回路の構成例を示す。これは、映像信号にアナログ映

像信号を用いて表示を行うためのソース信号線駆動回路であり、シフトレジスタ2411

、バッファ2412、サンプリング回路2413を有している。特に図示していないが、

必要に応じてレベルシフタ等を追加しても良い。

【0158】

ソース信号線駆動回路の動作について説明する。図25(A)に、より詳細な構成を示し

たので、そちらを参照する。

【0159】

シフトレジスタ2501は、フリップフロップ回路(FF)2502等を複数段用いてな

り、クロック信号(S−CLK)、クロック反転信号(S−CLKb)、スタートパルス(S

−SP)が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが

出力される。

【0160】

シフトレジスタ2501より出力されたサンプリングパルスは、バッファ2503等を

通って増幅された後、サンプリング回路へと入力される。サンプリング回路2504は、

サンプリングスイッチ(SW)2505を複数段用いてなり、サンプリングパルスが入力さ

れるタイミングに従って、ある列で映像信号のサンプリングを行う。具体的には、サンプ

リングスイッチにサンプリングパルスが入力されると、サンプリングスイッチ2505が

ONし、そのときに映像信号が有する電位が、サンプリングスイッチを介して各々のソー

ス信号線へと出力される。

【0161】

続いて、ゲート信号線駆動回路の動作について説明する。図24(C)に示した、第1、

第2のゲート信号線駆動回路2404、2405についての詳細な構成の一例を図25(

B)に示した。第1のゲート信号線駆動回路は、シフトレジスタ回路2511、バッファ

2512を有し、クロック信号(G−CLK1)、クロック反転信号(G−CLKb1)、ス

タートパルス(G−SP1)に従って駆動される。第2のゲート信号線駆動回路2405も

構成は同様で良い。また、図24(A)においては、第1、第2のゲート信号線駆動回路

2404、2405は、画素部2402を挟んで対称配置しているが、一方に並列して配

置しても良い。

【0162】

シフトレジスタ〜バッファの動作については、ソース信号線駆動回路の場合と同様であ

る。バッファによって増幅された選択パルスは、それぞれのゲート信号線を選択する。第

1のゲート信号線駆動回路によって、第1のゲート信号線G11、G21、・・・、Gm1が順

次選択され、第2のゲート信号線駆動回路によって、第2のゲート信号線G12、G22、・

・・、Gm2が順次選択される。図示していないが、第3のゲート信号線駆動回路について

も第1、第2のゲート信号線駆動回路と同様であり、第3のゲート信号線G13、G23、・

・・、Gm3が順次選択される。選択された行において、実施形態にて説明した手順により

、画素に映像信号が書き込まれて発光する。

【0163】

なお、ここではシフトレジスタの一例として、D−フリップフロップを複数段用いてな

るものを図示したが、デコーダ等によって、信号線を選択出来るような構成としていても

良い。

【実施例2】

【0164】

本実施例においては、映像信号にデジタル映像信号を用いて表示を行う発光装置の構成

について説明する。図26(A)に、発光装置の構成例を示す。基板2601上に、複数の

画素がマトリクス状に配置された画素部2602を有し、画素部周辺には、ソース信号線

駆動回路2603および、第1、第2のゲート信号線駆動回路2604、2605を有し

ている。図26(A)においては、2組のゲート信号線駆動回路を用い、図1に示した画素

における第1、第2のゲート信号線をそれぞれ制御するものである。

【0165】

ソース信号線駆動回路2603、第1、第2のゲート信号線駆動回路2604、260

5に入力される信号は、フレキシブルプリント基板(Flexible Print Circuit:FPC)2

606を介して外部より供給される。

【0166】

図26(B)に、ソース信号線駆動回路の構成例を示す。これは、映像信号にデジタル映

像信号を用いて表示を行うためのソース信号線駆動回路であり、シフトレジスタ2611

、第1のラッチ回路2612、第2のラッチ回路2613、D/A変換回路2614を有

している。特に図示していないが、必要に応じてレベルシフタ等を追加しても良い。

【0167】

第1、第2のゲート信号線駆動回路2604、2605については、実施例1にて示し

たものと同様で良いので、ここでは図示および説明を省略する。

【0168】

ソース信号線駆動回路の動作について説明する。図27(A)に、より詳細な構成を示し

たので、そちらを参照する。

【0169】

シフトレジスタ2701は、フリップフロップ回路(FF)2710等を複数段用いてな

り、クロック信号(S−CLK)、クロック反転信号(S−CLKb)、スタートパルス(S

−SP)が入力される。これらの信号のタイミングに従って、順次サンプリングパルスが

出力される。

【0170】

シフトレジスタ2701より出力されたサンプリングパルスは、第1のラッチ回路27

02に入力される。第1のラッチ回路2702には、デジタル映像信号が入力されており

、サンプリングパルスが入力されるタイミングに従って、各段でデジタル映像信号を保持

していく。ここでは、デジタル映像信号は3ビット入力されており、各ビットの映像信号

を、それぞれの第1のラッチ回路において保持する。1つのサンプリングパルスによって

、ここでは3つの第1のラッチ回路が並行して動作する。

【0171】

第1のラッチ回路2702において、最終段までデジタル映像信号の保持が完了すると

、水平帰線期間中に、第2のラッチ回路2703にラッチパルス(Latch Puls

e)が入力され、第1のラッチ回路2702に保持されていたデジタル映像信号は、一斉

に第2のラッチ回路2703に転送される。その後、第2のラッチ回路2703に保持さ

れたデジタル映像信号は、1行分が同時に、D/A変換回路2704へと入力される。

【0172】

第2のラッチ回路2703に保持されたデジタル映像信号がD/A変換回路2704に

入力されている間、シフトレジスタ2701においては再びサンプリングパルスが出力さ

れる。以後、この動作を繰り返し、1フレーム分の映像信号の処理を行う。

【0173】

D/A変換回路2704においては、入力されるデジタル映像信号をデジタル−アナロ

グ変換し、アナログ電圧を有する映像信号としてソース信号線に出力する。

【0174】

前記の動作が、1水平期間内に、全段にわたって同時に行われる。よって、全てのソー

ス信号線に映像信号が出力される。

【0175】

なお、実施例1においても述べたとおり、シフトレジスタの代わりにデコーダ等を用い

て、信号線を選択出来るような構成としていても良い。

【実施例3】

【0176】

実施例2においては、デジタル映像信号はD/A変換回路によってデジタル−アナログ

変換を受け、画素に書き込まれるが、本発明の発光装置は、時間階調方式によって階調表

現を行うことも出来る。この場合には、図27(B)に示すように、D/A変換回路を必要

とせず、階調表現は、EL素子の発光時間の長短によって制御されるので、各ビットの映

像信号を並列処理する必要がないため、第1および第2のラッチ回路も1ビット分で良い

。このとき、デジタル映像信号は、各ビットが直列に入力され、順次ラッチ回路に保持さ

れ、画素に書き込まれる。

勿論、必要ビット数分だけのラッチ回路を並列配置していても構わない。

【実施例4】

【0177】

本明細書ではCMOS回路で構成される駆動回路と、スイッチング用TFT及び駆動用

TFTを有する画素部とが同一基板上に形成された基板を便宜上アクティブマトリクス基

板と呼ぶ。そして本実施例では前記アクティブマトリクス基板の作製工程について図13

、図14を用いて説明する。

【0178】

基板5000は、石英基板、シリコン基板、金属基板又はステンレス基板の表面に絶縁

膜を形成したものを用いる。また本作製工程の処理温度に耐えうる耐熱性を有するプラス

チック基板を用いても良い。本実施例ではバリウムホウケイ酸ガラス、アルミノホウケイ

酸ガラス等のガラスからなる基板5000を用いた。

【0179】

次いで、基板5000上に酸化珪素膜、窒化珪素膜又は酸化窒化珪素膜などの絶縁膜か

ら成る下地膜5001を形成する。本実施例の下地膜5001は2層構造で形成したが、

前記絶縁膜の単層構造又は前記絶縁膜を2層以上積層させた構造であっても良い。

【0180】

本実施例では、下地膜5001の1層目として、プラズマCVD法を用いて、SiH4

、NH3、及びN2Oを反応ガスとして成膜される窒化酸化珪素膜5001aを10〜20

0nm(好ましくは50〜100nm)の厚さに形成する。本実施例では、窒化酸化珪素膜50

01aを50nmの厚さに形成した。次いで下地膜5001の2層目として、プラズマCV

D法を用いて、SiH4及びN2Oを反応ガスとして成膜される酸化窒化珪素膜5001b

を50〜200nm(好ましくは100〜150nm)の厚さに形成する。本実施例では、酸化

窒化珪素膜5001bを100nmの厚さに形成した。

【0181】

続いて、下地膜5001上に半導体層5002〜5005を形成する。半導体層500

2〜5005は公知の手段(スパッタ法、LPCVD法、プラズマCVD法等)により25

〜80nm(好ましくは30〜60nm)の厚さで半導体膜を成膜する。次いで前記半導体膜を

公知の結晶化法(レーザ結晶化法、RTA又はファーネスアニール炉を用いる熱結晶化法

、結晶化を助長する金属元素を用いる熱結晶化法等)を用いて結晶化させる。そして、得

られた結晶質半導体膜を所望の形状にパターニングして半導体層5002〜5005を形

成する。なお前記半導体膜としては、非晶質半導体膜、微結晶半導体膜、結晶質半導体膜

、又は非晶質珪素ゲルマニウム膜などの非晶質構造を有する化合物半導体膜などを用いて

も良い。

【0182】

本実施例では、プラズマCVD法を用いて、膜厚55nmの非晶質珪素膜を成膜した。そ

して、ニッケルを含む溶液を非晶質珪素膜上に保持させ、この非晶質珪素膜に脱水素化(

500℃、1時間)を行った後、熱結晶化(550℃、4時間)を行って結晶質珪素膜を形

成した。その後、フォトリソグラフィ法を用いたパターニング処理によって半導体層50

02〜5005を形成した。

【0183】

なおレーザ結晶化法で結晶質半導体膜を作製する場合のレーザは、連続発振またはパル

ス発振の気体レーザ又は固体レーザを用いれば良い。前者の気体レーザとしては、エキシ

マレーザ、YAGレーザ、YVO4レーザ、YLFレーザ、YAlO3レーザ、ガラスレー

ザ、ルビーレーザ、Ti:サファイアレーザ等を用いることができる。また後者の固体レ

ーザとしては、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmがドーピングされた

YAG、YVO4、YLF、YAlO3などの結晶を使ったレーザを用いることができる。

当該レーザの基本波はドーピングする材料によって異なり、1μm前後の基本波を有する

レーザ光が得られる。基本波に対する高調波は、非線形光学素子を用いることで得ること

ができる。なお非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためには、連続発振

が可能な固体レーザを用い、基本波の第2高調波〜第4高調波を適用するのが好ましい。

代表的には、Nd:YVO4レーザー(基本波1064nm)の第2高調波(532nm)や第3高

調波(355nm)を適用する。

【0184】

また出力10Wの連続発振のYVO4レーザから射出されたレーザ光は、非線形光学素

子により高調波に変換する。さらに、共振器の中にYVO4結晶と非線形光学素子を入れ

て、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状ま

たは楕円形状のレーザ光に成形して、被処理体に照射する。このときのエネルギー密度は

0.01〜100MW/cm2程度(好ましくは0.1〜10MW/cm2)が必要である。そして、

10〜2000cm/s程度の速度でレーザ光に対して相対的に半導体膜を移動させて照射

する。

【0185】

また上記のレーザを用いる場合には、レーザ発振器から放射されたレーザビームを光学

系で線状に集光して、半導体膜に照射すると良い。結晶化の条件は適宜設定されるが、エ

キシマレーザを用いる場合はパルス発振周波数300Hzとし、レーザーエネルギー密度を

100〜700mJ/cm2(代表的には200〜300mJ/cm2)とすると良い。またYAGレー

ザを用いる場合には、その第2高調波を用いてパルス発振周波数1〜300Hzとし、レー

ザーエネルギー密度を300〜1000mJ/cm2(代表的には350〜500mJ/cm2)とする

と良い。そして幅100〜1000μm(好ましくは幅400μm)で線状に集光したレーザ

光を基板全面に渡って照射し、このときの線状ビームの重ね合わせ率(オーバーラップ率)

を50〜98%として行っても良い。

【0186】

しかしながら本実施例では、結晶化を助長する金属元素を用いて非晶質珪素膜の結晶化

を行ったため、前記金属元素が結晶質珪素膜中に残留している。そのため、前記結晶質珪

素膜上に50〜100nmの非晶質珪素膜を形成し、加熱処理(RTA法やファーネスアニ

ール炉を用いた熱アニール等)を行って、該非晶質珪素膜中に前記金属元素を拡散させ、

前記非晶質珪素膜は加熱処理後にエッチングを行って除去する。その結果、前記結晶質珪

素膜中の金属元素の含有量を低減または除去することができる。

【0187】

なお半導体層5002〜5005を形成した後、TFTのしきい値電圧を制御するため

に微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。

【0188】

次いで、半導体層5002〜5005を覆うゲート絶縁膜5006を形成する。ゲート

絶縁膜5006はプラズマCVD法やスパッタ法を用いて、膜厚を40〜150nmとして

珪素を含む絶縁膜で形成する。本実施例では、ゲート絶縁膜5006としてプラズマCV

D法により酸化窒化珪素膜を115nmの厚さに形成した。勿論、ゲート絶縁膜5006は

酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造と

して用いても良い。

【0189】

なおゲート絶縁膜5006として酸化珪素膜を用いる場合には、プラズマCVD法でT

EOS(Tetraethyl Orthosilicate)とO2とを混合し、反応圧力40Pa、基板温度300

〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成

しても良い。上記の工程により作製される酸化珪素膜は、その後400〜500℃の熱ア

ニールによって、ゲート絶縁膜5006として良好な特性を得ることができる。

【0190】

次いで、ゲート絶縁膜5006上に膜厚20〜100nmの第1の導電膜5007と、膜

厚100〜400nmの第2の導電膜5008とを積層形成する。本実施例では、膜厚30

nmのTaN膜からなる第1の導電膜5007と、膜厚370nmのW膜からなる第2の導電

膜5008を積層形成した。

【0191】

本実施例では、第1の導電膜5007であるTaN膜はスパッタ法で形成し、Taのタ

ーゲットを用いて、窒素を含む雰囲気内でスパッタ法で形成した。また第2の導電膜50

08であるW膜は、Wのターゲットを用いたスパッタ法で形成した。その他に6フッ化タ

ングステン(WF6)を用いる熱CVD法で形成することもできる。いずれにしてもゲート

電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下

にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができる

が、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従っ

て、本実施例では、高純度のW(純度99.9999%)のターゲットを用いたスパッタ法

で、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成する

ことにより、抵抗率9〜20μΩcmを実現することができた。

【0192】

なお本実施例では、第1の導電膜5007をTaN膜、第2の導電膜5008をW膜と

したが、第1の導電膜5007及び第2の導電膜5008を構成する材料は特に限定され

ない。第1の導電膜5007及び第2の導電膜5008は、Ta、W、Ti、Mo、Al

、Cu、Cr、Ndから選択された元素、または前記元素を主成分とする合金材料若しく

は化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶珪素

膜に代表される半導体膜やAgPdCu合金で形成してもよい。

【0193】

次いで、フォトリソグラフィ法を用いてレジストからなるマスク5009を形成し、電

極及び配線を形成するための第1のエッチング処理を行う。第1のエッチング処理では第

1及び第2のエッチング条件で行う。(図13(B))

【0194】

本実施例では第1のエッチング条件として、ICP(Inductively Coupled Plasma:誘

導結合型プラズマ)エッチング法を用い、エッチング用ガスにCF4とCl2とO2とを用い

、それぞれのガス流量比を25:25:10sccmとし、1.0Paの圧力でコイル型の電極

に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッチングを行っ

た。基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に

負の自己バイアス電圧を印加した。

そしてこの第1のエッチング条件によりW膜をエッチングして第1の導電層5007の端

部をテーパー形状とした。

【0195】

続いて、レジストからなるマスク5009を除去せずに第2のエッチング条件に変更し

、エッチング用ガスにCF4とCl2とを用い、それぞれのガス流量比を30:30sccmと

し、1.0Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入して

プラズマを生成して15秒程度のエッチングを行った。基板側(試料ステージ)にも20W

のRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加した。第2

のエッチング条件では第1の導電層5007及び第2の導電層5008とも同程度にエッ

チングを行った。なお、ゲート絶縁膜5006上に残渣を残すことなくエッチングするた

めには、10〜20%程度の割合でエッチング時間を増加させると良い。

【0196】

上記の第1のエッチング処理では、レジストからなるマスクの形状を適したものとする

ことにより、基板側に印加するバイアス電圧の効果により第1の導電層5007及び第2

の導電層5008の端部がテーパー形状となる。こうして、第1のエッチング処理により

第1の導電層5007と第2の導電層5008から成る第1の形状の導電層5010〜5

014を形成した。ゲート絶縁膜5006においては、第1の形状の導電層5010〜5

014で覆われない領域が20〜50nm程度エッチングされたため、膜厚が薄くなった領

域が形成された。

【0197】

次いで、レジストからなるマスク5009を除去せずに第2のエッチング処理を行う。

(図13(C))第2のエッチング処理では、エッチングガスにSF6とCl2とO2を用い、

それぞれのガス流量比を24:12:24(sccm)とし、1.3Paの圧力でコイル側

の電力に700WのRF(13.56MHz)電力を投入してプラズマを生成して25秒程度のエッ

チングを行った。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質

的に負の自己バイアス電圧を印加した。こうして、W膜を選択的にエッチングして、第2

の形状の導電層5015〜5019を形成した。このとき、第1の導電層5015a〜5

019aは、ほとんどエッチングされない。

【0198】

そして、レジストからなるマスク5009を除去せずに第1のドーピング処理を行い、

半導体層5002〜5005にN型を付与する不純物元素を低濃度に添加する。第1のド

ーピング処理はイオンドープ法又はイオン注入法で行えば良い。イオンドープ法の条件は

ドーズ量を1×1013〜5×1014atoms/cm2とし、加速電圧を40〜80keVとして行う

。本実施例ではドーズ量を5.0×1013atoms/cm2とし、加速電圧を50keVとして行っ

た。N型を付与する不純物元素としては、15族に属する元素を用いれば良く、代表的に

はリン(P)又は砒素(As)を用いられるが、本実施例ではリン(P)を用いた。この場合、

第2の形状の導電層5015〜5019がN型を付与する不純物元素に対するマスクとな

って、自己整合的に第1の不純物領域(N--領域)5020〜5023を形成した。そして

第1の不純物領域5020〜5023には1×1018〜1×1020atoms/cm3の濃度範囲

でN型を付与する不純物元素が添加された。

【0199】

続いてレジストからなるマスク5009を除去した後、新たにレジストからなるマスク

5024を形成して、第1のドーピング処理よりも高い加速電圧で第2のドーピング処理

を行う。イオンドープ法の条件はドーズ量を1×1013〜3×1015atoms/cm2とし、加

速電圧を60〜120keVとして行う。本実施例では、ドーズ量を3.0×1015atoms/c

m2とし、加速電圧を65keVとして行った。第2のドーピング処理は第2の導電層501

5b〜5018bを不純物元素に対するマスクとして用い、第1の導電層5015a〜5

018aのテーパー部の下方の半導体層に不純物元素が添加されるようにドーピングを行

う。

【0200】

上記の第2のドーピング処理を行った結果、第1の導電層と重なる第2の不純物領域(

N−領域、Lov領域)5026には1×1018〜5×1019atoms/cm3の濃度範囲でN型を付

与する不純物元素を添加された。また第3の不純物領域(N+領域)5025、5028に

は1×1019〜5×1021atoms/cm3の濃度範囲でN型を付与する不純物元素を添加された

。また、第1、第2のドーピング処理を行った後、半導体層5002〜5005において

、不純物元素が全く添加されない領域又は微量の不純物元素が添加された領域が形成され

た。本実施例では、不純物元素が全く添加されない領域又は微量の不純物元素が添加され

た領域をチャネル領域5027、5030とよぶ。また前記第1のドーピング処理により

形成された第1の不純物領域(N--領域)5020〜5023のうち、第2のドーピング処

理においてレジスト5024で覆われていた領域が存在するが、本実施例では、引き続き

第1の不純物領域(N--領域、LDD領域)5029とよぶ。

【0201】

なお本実施例では、第2のドーピング処理のみにより、第2の不純物領域(N−領域)5

026及び第3の不純物領域(N+領域)5025、5028を形成したが、これに限定さ

れない。ドーピング処理を行う条件を適宜変えて、複数回のドーピング処理で形成しても

良い。

【0202】

次いで図14(A)に示すように、レジストからなるマスク5024を除去した後、新た

にレジストからなるマスク5031を形成する。その後、第3のドーピング処理を行う。

第3のドーピング処理により、Pチャネル型TFTの活性層となる半導体層に、前記第1

の導電型とは逆の導電型を付与する不純物元素が添加された第4の不純物領域(P+領域)

5032、5034及び第5の不純物領域(P−領域)5033、5035を形成する。

【0203】

第3のドーピング処理では、第2の導電層5016b、5018bを不純物元素に対す

るマスクとして用いる。こうして、P型を付与する不純物元素を添加し、自己整合的に第

4の不純物領域(P+領域)5032、5034及び第5の不純物領域(P−領域)5033

、5035を形成する。

【0204】

本実施例では、第4の不純物領域5032、5034及び第5の不純物領域5033、

5035はジボラン(B2H6)を用いたイオンドープ法で形成する。イオンドープ法の条件

としては、ドーズ量を1×1016atoms/cm2とし、加速電圧を80keVとした。

【0205】

なお、第3のドーピング処理の際には、Nチャネル型TFTを形成する半導体層はレジ

ストからなるマスク5031によって覆われている。

【0206】

ここで、第1及び2のドーピング処理によって、第4の不純物領域(P+領域)5032

、5034及び第5の不純物領域(P−領域)5033、5035にはそれぞれ異なる濃度

でリンが添加されている。しかし、第4の不純物領域(P+領域)5032、5034及び

第5の不純物領域(P−領域)5033、5035のいずれの領域においても、第3のドー

ピング処理によって、P型を付与する不純物元素の濃度が1×1019〜5×1021atoms/

cm3となるようにドーピング処理される。こうして、第4の不純物領域(P+領域)503

2、5034及び第5の不純物領域(P−領域)5033、5035は、Pチャネル型TF

Tのソース領域およびドレイン領域として問題なく機能する。

【0207】

なお本実施例では、第3のドーピング処理のみにより、第4の不純物領域(P+領域)5

032、5034及び第5の不純物領域(P−領域)5033、5035を形成したが、こ

れに限定されない。ドーピング処理を行う条件を適宜変えて、複数回のドーピング処理で

形成しても良い。

【0208】

次いで図14(B)に示すように、レジストからなるマスク5031を除去して第1の層

間絶縁膜5036を形成する。この第1の層間絶縁膜5036としては、プラズマCVD

法またはスパッタ法を用い、厚さを100〜200nmとして珪素を含む絶縁膜で形成する

。本実施例では、プラズマCVD法により膜厚100nmの酸化窒化珪素膜を形成した。勿

論、第1の層間絶縁膜5036は酸化窒化珪素膜に限定されるものでなく、他の珪素を含

む絶縁膜を単層または積層構造として用いても良い。

【0209】

次いで、図14(C)に示すように、加熱処理(熱処理)を行って、半導体層の結晶性の回

復、半導体層に添加された不純物元素の活性化を行う。この加熱処理はファーネスアニー

ル炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が1ppm以下、好ま

しくは0.1ppm以下の窒素雰囲気中で400〜700℃で行えばよく、本実施例では4

10℃、1時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザアニ

ール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

【0210】

また、第1の層間絶縁膜5036を形成する前に加熱処理を行っても良い。ただし、第

1の導電層5015a〜5019a及び、第2の導電層5015b〜5019bを構成す

る材料が熱に弱い場合には、本実施例のように配線等を保護するため第1の層間絶縁膜5

036(珪素を主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で熱処理を行うこと

が好ましい。

【0211】

上記の様に、第1の層間絶縁膜5036(珪素を主成分とする絶縁膜、例えば窒化珪素

膜)を形成した後に熱処理することにより、活性化処理と同時に、半導体層の水素化も行

うことができる。水素化の工程では、第1の層間絶縁膜5036に含まれる水素により半

導体層のダングリングボンドが終端される。

【0212】

なお、活性化処理のための加熱処理とは別に、水素化のための加熱処理を行っても良い

。

【0213】

ここで、第1の層間絶縁膜5036の存在に関係なく、半導体層を水素化することもで

きる。水素化の他の手段として、プラズマにより励起された水素を用いる手段(プラズマ

水素化)や、3〜100%の水素を含む雰囲気中において、300〜450℃で1〜12

時間の加熱処理を行う手段でも良い。

【0214】

次いで、第1の層間絶縁膜5036上に、第2の層間絶縁膜5037を形成する。第2

の層間絶縁膜5037としては、無機絶縁膜を用いることができる。例えば、CVD法に

よって形成された酸化珪素膜や、SOG(Spin On Glass)法によって塗布された酸化珪素

膜等を用いることができる。また、第2の層間絶縁膜5037として、有機絶縁膜を用い

ることができる。例えば、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アク

リル等の膜を用いることができる。

また、アクリル膜と酸化窒化珪素膜の積層構造を用いても良い。

【0215】

本実施例では、膜厚1.6μmのアクリル膜を形成した。第2の層間絶縁膜5037によ

って、基板上5000に形成されたTFTによる凹凸を緩和し、平坦化することができる

。特に、第2の層間絶縁膜5037は平坦化の意味合いが強いので、平坦性に優れた膜が

好ましい。

【0216】

次いで、ドライエッチングまたはウエットエッチングを用い、第2の層間絶縁膜503

7、第1の層間絶縁膜5036、およびゲート絶縁膜5006をエッチングし、第3の不

純物領域5025、5028、第4の不純物領域5032、5034に達するコンタクト

ホールを形成する。

【0217】

次いで、透明導電膜からなる画素電極5038を形成する。透明導電膜としては、酸化

インジウムと酸化スズの化合物(Indium Tin Oxide:ITO)、酸化インジウムと酸化亜鉛

の化合物、酸化亜鉛、酸化スズ、酸化インジウム等を用いることができる。また、前記透

明導電膜にガリウムを添加したものを用いてもよい。

画素電極がEL素子の陽極に相当する。

【0218】

本実施例では、ITOを110nm厚さで成膜、その後パターニングし、画素電極503

8形成した。

【0219】

次いで、各不純物領域とそれぞれ電気的に接続される配線5039〜5045を形成す

る。なお本実施例では、配線5039〜5045は、膜厚100nmのTi膜と、膜厚35

0nmのAl膜と、膜厚100nmのTi膜との積層膜をスパッタ法で連続形成し、所望の形

状にパターニングして形成する。

【0220】

もちろん、三層構造に限らず、単層構造でもよいし、二層構造でもよいし、四層以上の

積層構造にしてもよい。また配線の材料としては、AlとTiに限らず、他の導電膜を用

いても良い。例えば、TaN膜上にAlやCuを形成し、さらにTi膜を形成した積層膜

をパターニングして配線を形成してもよい。

【0221】

こうして、画素部のNチャネル型TFTのソース領域またはドレイン領域の一方は、配

線5042によってソース信号線(5019aと5019bの積層)と電気的に接続され、

もう一方は、配線5043によって画素部のPチャネル型TFTのゲート電極と電気的に

接続される。また、画素部のPチャネル型TFTのソース領域またはドレイン領域の一方

は、配線5044によって38と電気的に接続されている。ここで、画素電極5038上

の一部と、配線5044の一部を重ねて形成することによって、配線5044と画素電極

5038の電気的接続をとっている。

【0222】

以上の工程により図14(D)に示すように、Nチャネル型TFTとPチャネル型TFT

からなるCMOS回路を有する駆動回路部と、スイッチング用TFT、駆動用TFTとを

有する画素部を同一基板上に形成することができる。

【0223】

駆動回路部のNチャネル型TFTは、ゲート電極の一部を構成する第1の導電層501

5aと重なる低濃度不純物領域5026(Lov領域)、ソース領域またはドレイン領域とし

て機能する高濃度不純物領域5025とを有している。このNチャネル型TFTと配線5

040で接続されCMOS回路を形成するPチャネル型TFTは、ゲート電極の一部を構

成する第1の導電層5016aと重なる低濃度不純物領域5033(Lov領域)、ソース領

域またはドレイン領域として機能する高濃度不純物領域5032とを有している。

【0224】

画素部において、Nチャネル型のスイッチング用TFTは、ゲート電極の外側に形成さ

れる低濃度不純物領域5029(Loff領域)、ソース領域またはドレイン領域として機能

する高濃度不純物領域5028とを有している。また画素部において、Pチャネル型の駆

動用TFTは、ゲート電極の一部を構成する第1の導電層5018aと重なる低濃度不純

物領域5035(Lov領域)、ソース領域またはドレイン領域として機能する高濃度不純物

領域5034とを有している。

【0225】

次いで、第3の層間絶縁膜5046を形成する。第3の層間絶縁膜としては、無機絶縁

膜や有機絶縁膜を用いることができる。無機絶縁膜としては、CVD法によって形成され

た酸化珪素膜や、SOG(Spin On Glass)法によって塗布された酸化珪素膜、あるいは、

スパッタ法によって形成された窒化酸化珪素膜等を用いることができる。また、有機絶縁

膜としては、アクリル樹脂膜等を用いることができる。

【0226】

第2の層間絶縁膜5037と第3の層間絶縁膜5046の組み合わせの例を以下に挙げ

る。

【0227】

第2の層間絶縁膜5037として、アクリルとスパッタ法によって形成された窒化酸化

珪素膜の積層膜を用い、第3の層間絶縁膜5046として、スパッタ法によって形成され

た窒化酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜5037として、

SOG法によって形成した酸化珪素膜を用い、第3の層間絶縁膜5046としてもSOG

法によって形成した酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜50

37として、SOG法によって形成した酸化珪素膜とプラズマCVD法によって形成した

酸化珪素膜の積層膜を用い、第3の層間絶縁膜5046としてプラズマCVD法によって

形成した酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜5037として

、アクリルを用い、第3の層間絶縁膜5046としてもアクリルを用いる組み合わせがあ

る。また、第2の層間絶縁膜5037として、アクリルとプラズマCVD法によって形成

した酸化珪素膜の積層膜を用い、第3の層間絶縁膜5046としてプラズマCVD法によ

って形成した酸化珪素膜を用いる組み合わせがある。また、第2の層間絶縁膜5037と

して、プラズマCVD法によって形成した酸化珪素膜を用い、第3の層間絶縁膜5046

としてアクリルを用いる組み合わせがある。

【0228】

第3の層間絶縁膜5046の画素電極5038に対応する位置に開口部を形成する。第

3の層間絶縁膜は、バンクとして機能する。開口部を形成する際、ウエットエッチング法

を用いることで容易にテーパー形状の側壁とすることが出来る。開口部の側壁が十分にな

だらかでないと段差に起因するEL層の劣化が顕著な問題となってしまうため、注意が必

要である。

【0229】

第3の層間絶縁膜中に、カーボン粒子や金属粒子を添加し、抵抗率を下げ、静電気の発

生を抑制してもよい。この際、抵抗率は、1×106〜1×1012Ωm(好ましくは、1×

108〜1×1010Ωm)となるように、カーボン粒子や金属粒子の添加量を調節すればよ

い。

【0230】

次いで、第3の層間絶縁膜5046の開口部において露出している画素電極5038上

に、EL層5047を形成する。

【0231】

EL層5047としては、公知の有機発光材料や無機発光材料を用いることができる。

【0232】

有機発光材料としては、低分子系有機発光材料、高分子系有機発光材料、中分子系有機

材料を自由に用いることができる。なお、本明細書中においては、中分子系有機発光材料

とは、昇華性を有さず、かつ、分子数が20以下または連鎖する分子の長さが10μm以

下の有機発光材料を示すものとする。

【0233】

EL層5047は通常、積層構造である。代表的には、「正孔輸送層/発光層/電子輸

送層」という積層構造が挙げられる。また他にも、陽極上に正孔注入層/正孔輸送層/発

光層/電子輸送層、または正孔注入層/正孔輸送層/発光層/電子輸送層/電子注入層の

順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。

【0234】

本実施例では蒸着法により低分子系有機発光材料を用いてEL層5047を形成してい

る。具体的には、正孔注入層として20nm厚の銅フタロシアニン(CuPc)膜を設け、そ

の上に発光層として70nm厚のトリス−8−キノリノラトアルミニウム錯体(Alq3)膜

を設けた積層構造としている。Alq3にキナクリドン、ペリレンもしくはDCM1とい

った蛍光色素を添加することで発光色を制御することができる。

【0235】

なお、図14(D)では一画素しか図示していないが、複数の色、例えば、R(赤)、G(

緑)、B(青)の各色に対応したEL層5047を作り分ける構成とすることができる。

【0236】

また、高分子系有機発光材料を用いる例として、正孔注入層として20nmのポリチオフ

ェン(PEDOT)膜をスピン塗布法により設け、その上に発光層として100nm程度のパ

ラフェニレンビニレン(PPV)膜を設けた積層構造によってEL層5047を構成しても

良い。なお、PPVのπ共役系高分子を用いると、赤色から青色まで発光波長を選択でき

る。また、電子輸送層や電子注入層として炭化珪素等の無機材料を用いることも可能であ

る。

【0237】

なお、EL層5047は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層

等が、明確に区別された積層構造を有するものに限定されない。つまり、EL層5047

は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等を構成する材料が、混

合した層を有する構造であってもよい。

【0238】

例えば、電子輸送層を構成する材料(以下、電子輸送材料と表記する)と、発光層を構成

する材料(以下、発光材料と表記する)とによって構成される混合層を、電子輸送層と発光

層との間に有する構造のEL層5047であってもよい。

【0239】

次に、EL層5047の上には導電膜からなる画素電極5048が設けられる。本実施

例の場合、導電膜としてアルミニウムとリチウムとの合金膜を用いる。

勿論、公知のMgAg膜(マグネシウムと銀との合金膜)を用いても良い。画素電極504

8がEL素子の陰極に相当する。陰極材料としては、周期表の1族もしくは2族に属する

元素からなる導電膜もしくはそれらの元素を添加した導電膜を自由に用いることができる

。

【0240】

画素電極5048まで形成された時点でEL素子が完成する。なお、EL素子とは、画

素電極(陽極)5038、EL層5047及び画素電極(陰極)5048で形成された素子を

指す。

【0241】

EL素子を完全に覆うようにしてパッシベーション膜5049を設けることは有効であ

る。パッシベーション膜5049としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜

を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いることができる

。

【0242】

カバレッジの良い膜をパッシベーション膜5049として用いることが好ましく、炭素

膜、特にDLC(ダイヤモンドライクカーボン)膜を用いることは有効である。DLC膜は

室温から100℃以下の温度範囲で成膜可能であるため、耐熱性の低いEL層5047の

上方にも容易に成膜することができる。また、DLC膜は酸素に対するブロッキング効果

が高く、EL層5047の酸化を抑制することが可能である。そのため、EL層5047

が酸化するといった問題を防止できる。

【0243】

なお、第3の層間絶縁膜5046を形成した後、パッシベーション膜5049を形成す

るまでの工程をマルチチャンバー方式(またはインライン方式)の成膜装置を用いて、大気

解放せずに連続的に処理することは有効である。

【0244】

なお、実際には図14(D)の状態まで完成したら、さらに外気に曝されないように、気

密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィル

ム等)や透光性のシーリング材でパッケージング(封入)することが好ましい。その際、シ

ーリング材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配

置したりするとEL素子の信頼性が向上する。

【0245】

また、パッケージング等の処理により気密性を高めたら、基板5000上に形成された

素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクタ(フレキ

シブルプリントサーキット:FPC)を取り付けて製品として完成する。

【0246】

また、本実施例で示す工程に従えば、発光装置の作製に必要なフォトマスクの数を抑え

ることが出来る。その結果、工程を短縮し、製造コストの低減及び歩留まりの向上に寄与

することが出来る。

【実施例5】

【0247】

本実施例では、実施例4に示した構成とは異なる構成のアクティブマトリクス基板の作

製工程について図15を用いて説明する。

【0248】

なお、図15(A)までの工程は、実施例4において、図13(A)〜(D)、図14(A)に

示した工程と同様である。ただし、画素部を構成する駆動用TFTは、ゲート電極の外側

に形成される低濃度不純物領域(Loff領域)を有する、Nチャネル型のTFTである点が

異なる。この駆動用TFTにおいては、実施例4に示したように、レジストによるマスク

を用いて、ゲート電極の外側に低濃度不純物領域(Loff領域)を形成すれば良い。

【0249】

図13及び図14と同じ部分は同じ符号を用いて示し、説明は省略する。

【0250】

図15(A)に示すように、第1の層間絶縁膜5101を形成する。この第1の層間絶縁

膜5101としては、プラズマCVD法またはスパッタ法を用い、厚さを100〜200

nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚10

0nmの酸化窒化珪素膜を形成した。勿論、第1の層間絶縁膜5101は酸化窒化珪素膜に

限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い

。

【0251】

次いで、図15(B)に示すように、加熱処理(熱処理)を行って、半導体層の結晶性の回

復、半導体層に添加された不純物元素の活性化を行う。この加熱処理はファーネスアニー

ル炉を用いる熱アニール法で行う。熱アニール法としては、酸素濃度が1ppm以下、好ま

しくは0.1ppm以下の窒素雰囲気中で400〜700℃で行えばよく、本実施例では4

10℃、1時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザアニ

ール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。

【0252】

また、第1の層間絶縁膜5101を形成する前に加熱処理を行っても良い。ただし、第

1の導電層5015a〜5019a及び、第2の導電層5015b〜5019bが熱に弱

い場合には、本実施例のように配線等を保護するため第1の層間絶縁膜5101(珪素を

主成分とする絶縁膜、例えば窒化珪素膜)を形成した後で熱処理を行うことが好ましい。

【0253】

上記の様に、第1の層間絶縁膜5101(珪素を主成分とする絶縁膜、例えば窒化珪素

膜)を形成した後に熱処理することにより、活性化処理と同時に、半導体層の水素化も行

うことができる。水素化の工程では、第1の層間絶縁膜5101に含まれる水素により半

導体層のダングリングボンドが終端される。

【0254】

なお、活性化処理のための加熱処理とは別に、水素化のための加熱処理を行っても良い

。

【0255】

ここで、第1の層間絶縁膜5101の存在に関係なく、半導体層を水素化することもで

きる。水素化の他の手段として、プラズマにより励起された水素を用いる手段(プラズマ

水素化)や、3〜100%の水素を含む雰囲気中において、300〜450℃で1〜12

時間の加熱処理を行う手段でも良い。

【0256】

以上の工程により、Nチャネル型TFTとPチャネル型TFTからなるCMOS回路を

有する駆動回路部と、スイッチング用TFT、駆動用TFTとを有する画素部を同一基板

上に形成することができる。

【0257】

次いで、第1の層間絶縁膜5101上に、第2の層間絶縁膜5102を形成する。第2

の層間絶縁膜5102としては、無機絶縁膜を用いることができる。例えば、CVD法に

よって形成された酸化珪素膜や、SOG(Spin On Glass)法によって塗布された酸化珪素

膜等を用いることができる。また、第2の層間絶縁膜5102として、有機絶縁膜を用い

ることができる。例えば、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アク

リル等の膜を用いることができる。

また、アクリル膜と酸化珪素膜の積層構造を用いても良いし、アクリル膜とスパッタ法で

形成した窒化酸化珪素膜の積層構造を用いても良い。

【0258】

次いで、ドライエッチングまたはウエットエッチングを用い、第1の層間絶縁膜510

1、第2の層間絶縁膜5102及びゲート絶縁膜5006をエッチングし、駆動回路部及

び画素部を構成する各TFTの不純物領域(第3の不純物領域(N+領域)及び第4の不純

物領域(P+領域))に達するコンタクトホールを形成する。

【0259】

次いで、各不純物領域とそれぞれ電気的に接続される配線5103〜5109を形成す

る。なお本実施例では、配線5103〜5109は、膜厚100nmのTi膜と、膜厚35

0nmのAl膜と、膜厚100nmのTi膜との積層膜をスパッタ法で連続形成し、所望の形

状にパターニングして形成する。

【0260】

もちろん、三層構造に限らず、単層構造でもよいし、二層構造でもよいし、四層以上の

積層構造にしてもよい。また配線の材料としては、AlとTiに限らず、他の導電膜を用

いても良い。例えば、TaN膜上にAlやCuを形成し、さらにTi膜を形成した積層膜

をパターニングして配線を形成してもよい。

【0261】

画素部のスイッチング用TFTのソース領域またはドレイン領域の一方は、配線510

6によってソース配線(5019aと5019bの積層)と電気的に接続され、もう一方は

、配線5107によって画素部の駆動用TFTのゲート電極と電気的に接続される。

【0262】

次いで図15(C)に示すように、第3の層間絶縁膜5110を形成する。第3の層間絶

縁膜5110としては、無機絶縁膜や有機絶縁膜を用いることができる。無機絶縁膜とし

ては、CVD法によって形成された酸化珪素膜や、SOG(Spin On Glass)法によって塗

布された酸化珪素膜等を用いることができる。また、有機絶縁膜としては、アクリル樹脂

膜等を用いることができる。また、アクリル膜とスパッタ法で形成した窒化酸化珪素膜の

積層構造を用いても良い。

【0263】

第3の層間絶縁膜5110によって、基板上5000に形成されたTFTによる凹凸を

緩和し、平坦化することができる。特に、第3の層間絶縁膜5110は平坦化の意味合い

が強いので、平坦性に優れた膜が好ましい。

【0264】

次いで、ドライエッチングまたはウエットエッチングを用い、第3の層間絶縁膜511

0に、配線5108に達するコンタクトホールを形成する。

【0265】

次いで、導電膜をパターニングして画素電極5111を形成する。本実施例の場合、導

電膜としてアルミニウムとリチウムとの合金膜を用いる。勿論、公知のMgAg膜(マグ

ネシウムと銀との合金膜)を用いても良い。画素電極5111がEL素子の陰極に相当す

る。陰極材料としては、周期表の1族もしくは2族に属する元素からなる導電膜もしくは

それらの元素を添加した導電膜を自由に用いることができる。

【0266】

画素電極5111は、第3の層間絶縁膜5110に形成されたコンタクトホールによっ

て、配線5108と電気的な接続がとられる。こうして、画素電極5111は、駆動用T

FTのソース領域またはドレイン領域の一方と、電気的に接続される。

【0267】

次いで図15(D)に示すように、各画素間のEL層を塗り分けるために、土手5112

を形成する。土手5112としては、無機絶縁膜や有機絶縁膜を用いて形成する。無機絶

縁膜としては、スパッタ法によって形成された窒化酸化珪素膜、CVD法によって形成さ

れた酸化珪素膜、あるいは、SOG法によって塗布された酸化珪素膜等を用いることがで

きる。また、有機絶縁膜としては、アクリル樹脂膜等を用いることができる。

【0268】

ここで、土手5112を形成する際、ウエットエッチング法を用いることで容易にテー

パー形状の側壁とすることが出来る。土手5112の側壁が十分になだらかでないと段差

に起因するEL層の劣化が顕著な問題となってしまうため、注意が必要である。

【0269】

なお、画素電極5111と配線5108を電気的に接続する際に、第3の層間絶縁膜5

110に形成したコンタクトホールの部分にも、土手5112を形成する。こうして、コ

ンタクトホール部分の凹凸による、画素電極の凹凸を土手5112によって埋めることに

より、段差に起因するEL層の劣化を防いでいる。

【0270】

第3の層間絶縁膜5110と土手5112の組み合わせの例を以下に挙げる。

【0271】

第3の層間絶縁膜5110として、アクリルとスパッタ法によって形成された窒化酸化

珪素膜の積層膜を用い、土手5112として、スパッタ法によって形成された窒化酸化珪

素膜を用いる組み合わせがある。また、第3の層間絶縁膜5110として、SOG法によ

って形成した酸化珪素膜を用い、土手5112としてもSOG法によって形成した酸化珪

素膜を用いる組み合わせがある。また第3の層間絶縁膜5110として、SOG法によっ

て形成した酸化珪素膜とプラズマCVD法によって形成した酸化珪素膜の積層膜を用い、

土手5112としてプラズマCVD法によって形成した酸化珪素膜を用いる組み合わせが

ある。また、第3の層間絶縁膜5110として、アクリルを用い、土手5112としても

アクリルを用いる組み合わせがある。また、第3の層間絶縁膜5110として、アクリル

とプラズマCVD法によって形成した酸化珪素膜の積層膜を用い、土手5112としてプ

ラズマCVD法によって形成した酸化珪素膜を用いる組み合わせがある。また、第3の層

間絶縁膜5110として、プラズマCVD法によって形成した酸化珪素膜を用い、土手5

112としてアクリルを用いる組み合わせがある。

【0272】

土手5112中に、カーボン粒子や金属粒子を添加し、抵抗率を下げ、静電気の発生を

抑制してもよい。この際、抵抗率は、1×106〜1×1012Ωm(好ましくは、1×108

〜1×1010Ωm)となるように、カーボン粒子や金属粒子の添加量を調節すればよい。

【0273】

次いで、土手5112に囲まれた、露出している画素電極5111上に、EL層511

3を形成する。

【0274】

EL層5113としては、公知の有機発光材料や無機発光材料を用いることができる。

【0275】

有機発光材料としては、低分子系有機発光材料、高分子系有機発光材料、中分子系有機

材料を自由に用いることができる。なお、本明細書中においては、中分子系有機発光材料

とは、昇華性を有さず、かつ、分子数が20以下または連鎖する分子の長さが10μm以

下の有機発光材料を示すものとする。

【0276】

EL層5113は通常、積層構造である。代表的には、「正孔輸送層/発光層/電子輸

送層」という積層構造が挙げられる。また他にも、陰極上に電子輸送層/発光層/正孔輸

送層/正孔注入層、または電子注入層/電子輸送層/発光層/正孔輸送層/正孔注入層の

順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。

【0277】

本実施例では蒸着法により低分子系有機発光材料を用いてEL層5113を形成してい

る。具体的には、発光層として70nm厚のトリス−8−キノリノラトアルミニウム錯体(

Alq3)膜を設け、その上に、正孔注入層として20nm厚の銅フタロシアニン(CuPc)

膜を設けた積層構造としている。Alq3にキナクリドン、ペリレンもしくはDCM1と

いった蛍光色素を添加することで発光色を制御することができる。

【0278】

なお、図15(D)では一画素しか図示していないが、複数の色、例えば、R(赤)、G(

緑)、B(青)の各色に対応したEL層5113を作り分ける構成とすることができる。

【0279】

また、高分子系有機発光材料を用いる例として、正孔注入層として20nmのポリチオフ

ェン(PEDOT)膜をスピン塗布法により設け、その上に、発光層として100nm程度の

パラフェニレンビニレン(PPV)膜を設けた積層構造によってEL層5113を構成して

も良い。なお、PPVのπ共役系高分子を用いると、赤色から青色まで発光波長を選択で

きる。また、電子輸送層や電子注入層として炭化珪素等の無機材料を用いることも可能で

ある。

【0280】

なお、EL層5113は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層

等が、明確に区別された積層構造を有するものに限定されない。つまり、EL層5113

は、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等を構成する材料が、混

合した層を有する構造であってもよい。

【0281】

例えば、電子輸送層を構成する材料(以下、電子輸送材料と表記する)と、発光層を構成

する材料(以下、発光材料と表記する)とによって構成される混合層を、電子輸送層と発光

層との間に有する構造のEL層5113であってもよい。

【0282】

次に、EL層5113の上には、透明導電膜からなる画素電極5114を形成する。透

明導電膜としては、酸化インジウムと酸化スズの化合物(ITO)、酸化インジウムと酸化

亜鉛の化合物、酸化亜鉛、酸化スズ、酸化インジウム等を用いることができる。また、前

記透明導電膜にガリウムを添加したものを用いてもよい。画素電極5114がEL素子の

陽極に相当する。

【0283】

画素電極5114まで形成された時点でEL素子が完成する。なお、EL素子とは、画

素電極(陰極)5111、EL層5113及び画素電極(陽極)5114で形成されたダイオ

ードを指す。

【0284】

本実施例では、画素電極5114が透明導電膜によって形成されているため、EL素子

が発した光は、基板5000とは逆側に向かって放射される。また、第3の層間絶縁膜5

110によって、配線5106〜5109が形成された層とは別の層に、画素電極511

1を形成している。そのため、実施例4に示した構成と比較して、開口率を上げることが

できる。

【0285】

EL素子を完全に覆うようにして保護膜(パッシベーション膜)5115を設けることは

有効である。保護膜5115としては、炭素膜、窒化珪素膜もしくは窒化酸化珪素膜を含

む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層で用いることができる。

【0286】

なお本実施例のように、EL素子が発した光が画素電極5114側から放射される場合

、保護膜5115としては、光を透過する膜を用いる必要がある。

【0287】

なお、土手5112を形成した後、保護膜5115を形成するまでの工程をマルチチャ

ンバー方式(またはインライン方式)の成膜装置を用いて、大気解放せずに連続的に処理す

ることは有効である。

【0288】

なお、実際には図15(D)の状態まで完成したら、さらに外気に曝されないように、気

密性が高く、脱ガスの少ない保護フィルム(ラミネートフィルム、紫外線硬化樹脂フィル

ム等)等のシーリング材でパッケージング(封入)することが好ましい。その際、シーリン

グ材の内部を不活性雰囲気にしたり、内部に吸湿性材料(例えば酸化バリウム)を配置した

りするとEL素子の信頼性が向上する。

【0289】

また、パッケージング等の処理により気密性を高めたら、基板5000上に形成された

素子又は回路から引き回された端子と外部信号端子とを接続するためのコネクタ(フレキ

シブルプリントサーキット:FPC)を取り付けて製品として完成する。

【実施例6】

【0290】

本実施例では、本発明を用いて発光装置を作製した例について、図30を用いて説明す

る。

【0291】

図30は、TFTが形成された素子基板をシーリング材によって封止することによって

形成された発光装置の上面図であり、図30(B)は、図30(A)のA−A’における断面

図、図30(C)は図30(A)のB−B’における断面図である。

【0292】

基板4001上に設けられた画素部4002と、ソース信号線駆動回路4003と、第

1及び第2のゲート信号線駆動回路4004a、4004bとを囲むようにして、シール

材4009が設けられている。また画素部4002と、ソース信号線駆動回路4003と

、第1及び第2のゲート信号線駆動回路4004a、4004bとの上にシーリング材4

008が設けられている。よって画素部4002と、ソース信号線駆動回路4003と、

第1及び第2のゲート信号線駆動回路4004a、4004bとは、基板4001とシー

ル材4009とシーリング材4008とによって、充填材4210で密封されている。

【0293】

また基板4001上に設けられた画素部4002と、ソース信号線駆動回路4003と

、第1及び第2のゲート信号線駆動回路4004a、4004bとは、複数のTFTを有

している。図30(B)では代表的に、下地膜4010上に形成された、ソース信号線駆動

回路4003に含まれるTFT(但し、ここではNチャネル型TFTとPチャネル型TF

Tを図示する)4201及び画素部4002に含まれるTFT4202を図示した。

【0294】

TFT4201及び4202上には層間絶縁膜(平坦化膜)4301が形成され、その上

にTFT4202のドレインと電気的に接続する画素電極(陽極)4203が形成される。

画素電極4203としては仕事関数の大きい透明導電膜が用いられる。透明導電膜として

は、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化

亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガ

リウムを添加したものを用いても良い。

【0295】

そして、画素電極4203の上には絶縁膜4302が形成され、絶縁膜4302は画素

電極4203の上に開口部が形成されている。この開口部において、画素電極4203の

上には有機発光層4204が形成される。有機発光層4204は公知の有機発光材料また

は無機発光材料を用いることができる。また、有機発光材料には低分子系(モノマー系)材

料と高分子系(ポリマー系)材料があるがどちらを用いても良い。

【0296】

有機発光層4204の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。

また、有機発光層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入

層を自由に組み合わせて積層構造または単層構造とすれば良い。

【0297】

有機発光層4204の上には遮光性を有する導電膜(代表的にはアルミニウム、銅もし

くは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜)からなる陰極420

5が形成される。また、陰極4205と有機発光層4204の界面に存在する水分や酸素

は極力排除しておくことが望ましい。従って、有機発光層4204を窒素または希ガス雰

囲気で形成し、酸素や水分に触れさせないまま陰極4205を形成するといった工夫が必

要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用い

ることで上述のような成膜を可能とする。そして陰極4205は所定の電圧が与えられて

いる。

【0298】

以上のようにして、画素電極(陽極)4203、有機発光層4204及び陰極4205か

らなる発光素子4303が形成される。そして発光素子4303を覆うように、絶縁膜4

302上に保護膜4209が形成されている。保護膜4209は、発光素子4303に酸

素や水分等が入り込むのを防ぐのに効果的である。

【0299】

4005aは電源線に接続された引き回し配線であり、TFT4202の第1の電極に

接続されている。引き回し配線4005aはシール材4009と基板4001との間を通

り、異方導電性フィルム4300を介してFPC4006が有するFPC用配線4301

に電気的に接続される。

【0300】

シーリング材4008としては、ガラス材、金属材(代表的にはステンレス材)、セラミ

ックス材、プラスチック材(プラスチックフィルムも含む)を用いることができる。プラス

チック材としては、FRP(Fiberglass‐Reinforced‐Plastics)板、PVF(ポリビニル

フルオライド)フィルム、マイラーフィルム、ポリエステルフィルムまたはアクリル樹脂

フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやマイラー

フィルムで挟んだ構造のシートを用いることもできる。

【0301】

但し、発光素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でな

ければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまた

はアクリルフィルムのような透明物質を用いる。

【0302】

また、充填材4210としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化

樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、

ポリイミド、エポキシ樹脂、シリコン樹脂、PVB(ポリビニルブチラル)またはEVA(

エチレンビニルアセテート)を用いることができる。

本実施例では充填材として窒素を用いた。

【0303】

また充填材4210を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる

物質にさらしておくために、シーリング材4008の基板4001側の面に凹部4007

を設けて吸湿性物質または酸素を吸着しうる物質4207を配置する。そして、吸湿性物

質または酸素を吸着しうる物質4207が飛び散らないように、凹部カバー材4208に

よって吸湿性物質または酸素を吸着しうる物質4207は凹部4007に保持されている

。なお凹部カバー材4208は目の細かいメッシュ状になっており、空気や水分は通し、

吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物

質または酸素を吸着しうる物質4207を設けることで、発光素子4303の劣化を抑制

できる。

【0304】

図30(C)に示すように、画素電極4203が形成されると同時に、引き回し配線40

05a上に接するように導電性膜4203aが形成される。

【0305】

また、異方導電性フィルム4300は導電性フィラー4300aを有している。基板4

001とFPC4006とを熱圧着することで、基板4001上の導電性膜4203aと

FPC4006上のFPC用配線4301とが、導電性フィラー4300aによって電気

的に接続される。

【実施例7】

【0306】

本発明において、三重項励起子からの燐光を発光に利用できる有機発光材料を用いるこ

とで、外部発光量子効率を飛躍的に向上させることができる。これにより、発光素子の低

消費電力化、長寿命化、および軽量化が可能になる。

【0307】

ここで、三重項励起子を利用し、外部発光量子効率を向上させた報告を示す。

(T.Tsutsui, C.Adachi, S.Saito, Photochemical Processes in Organized Molecular S

ystems, ed.K.Honda, (Elsevier Sci.Pub., Tokyo,1991) p.437.)

【0308】

上記の論文により報告された有機発光材料(クマリン色素)の分子式を以下に示す。

【0309】

【化1】

【0310】

(M.A.Baldo, D.F.O’Brien, Y.You, A.Shoustikov, S.Sibley, M.E.Thompson, S.R.For

rest, Nature 395 (1998) p.151.)

【0311】

上記の論文により報告された有機発光材料(Pt錯体)の分子式を以下に示す。

【0312】

【化2】

【0313】

(M.A.Baldo, S.Lamansky, P.E.Burrrows, M.E.Thompson, S.R.Forrest, Appl.Phys.Let

t.,75 (1999) p.4.) (T.Tsutsui, M.-J.Yang, M.Yahiro, K.Nakamura, T.Watanabe, T.ts

uji, Y.Fukuda, T.Wakimoto, S.Mayaguchi, Jpn.Appl.Phys., 38 (12B) (1999) L1502.)

【0314】

上記の論文により報告された有機発光材料(Ir錯体)の分子式を以下に示す。

【0315】

【化3】

【0316】

以上のように三重項励起子からの燐光発光を利用できれば原理的には一重項励起子から

の蛍光発光を用いる場合より3〜4倍の高い外部発光量子効率の実現が可能となる。

【実施例8】

【0317】

本明細書でこれまでに示してきた構成では、駆動用TFTにはPチャネル型TFTを用

いていたが、本発明は駆動用TFTにNチャネル型TFTを用いた場合の構成にも適用が

可能である。図32(A)に構成を示す。

【0318】

駆動用TFT3209はNチャネル型であり、この場合、ソース領域はEL素子32

12の陽極と接続されている側であり、ドレイン領域は、電流供給線3211と接続され

ている側となる。そこで、容量手段3210は、駆動用TFT3209のゲート・ソース

間の電圧を保持出来るようなノードに設ける。よって、容量手段3210は、図32(A

)に示したノードの他、駆動用TFT3209のゲート電極とソース領域との間に設けて

も良い。

【0319】

動作について説明する。まず、図32(B)に示すように、TFT3207をONし、

TFT3206のドレイン領域の電位を高くしておく。続いて、図32(C)に示すよう

に、TFT3205がONし、映像信号の入力が行われる。ここで、TFT3206のソ

ース・ドレイン間電圧が、そのしきい値電圧に等しくなったところで、TFT3206が

OFFし、図32(D)に示すような状態となる。TFT3206のソース領域の電位は

VDataであるので、TFT3206のドレイン領域の電位、すなわち駆動用TFT320

9のゲート電極の電位は、VData+Vthとなる。

【0320】

続いて、TFT3208がOFFすると、電流供給線から駆動用TFT3209を介し

て流れていた電流は、EL素子3212に流れ、発光する。よって、隣接画素において、

駆動用TFT3209のしきい値電圧がばらついたとしても、そのばらつきに関係なく、

TFT3206のソース・ドレイン間電圧、つまりしきい値電圧が映像信号に上乗せされ

るため、駆動用TFT3209のゲート・ソース間電圧は隣接画素ごとにばらつくことが

ない。

【0321】

さらに、図32に示した構成でEL素子3212が発光によって劣化した場合、陽極−

陰極間の電圧が上昇する。これにより、通常であれば駆動用TFT3209のソース領域

の電位が上昇し、結果として発光時のゲート・ソース間電圧が小さくなってしまうという

問題が考えられるが、本実施例で示した構成によると、図32(C)〜(D)における、

映像信号の入力時において、TFT3208がONすることによって、駆動用TFT32

09のソース領域の電位は、電源線3214の電位に固定される。よって前述のように、

容量手段3210が、駆動用TFT3209のゲート・ソース間電圧を保持しており、駆

動用TFT3209のソース領域の電位が変化しても、ゲート・ソース間電圧が小さくな

ることがないため、経時的な輝度低下を抑えることが出来る。

【0322】

なお、本実施例において、ダイオード接続されたTFT3206と、駆動用TFT32

09はNチャネル型としている。他のTFTは、ON・OFFのみの制御を行うスイッチ

素子として用いているので、その極性は問わない。

【0323】

また、駆動用TFTがPチャネル型である場合と同様、配線を共有としても良い。例え

ば、TFT3207を制御しているゲート信号線3203は、前段のゲート信号線と共有

しても良い。また、電源線3214についても、図32(C)

(D)に示した動作を行っている期間中、一定電位であれば良く、選択されている当行を

除くいずれかのゲート信号線と共有が可能である。また、電源線3213、3214は共

通としても良い。

【0324】

また、消去期間を設ける場合にも、駆動用TFTがPチャネル型の場合と同様、TFT

を追加するなどして、任意の期間でEL素子3212への電流供給を遮断する手段を設け

ても良い。

【実施例9】

【0325】

本実施例においては、ダイオード接続による電圧効果を利用した、異なる回路構成例に

ついて説明する。

【0326】

図33(A)に、一構成例を示す。本実施例の構成によると、TFT3308は、その

ゲート電極とドレイン領域との間にTFT3309を有し、TFT3309がONしてい

るとき、TFT3308はダイオード接続されたTFTとして振る舞い、TFT3309

がOFFしているとき、EL素子3313への電流供給の制御を行う駆動用TFTとして

振る舞う。

【0327】

動作について説明する。まず、図33(B)に示すように、TFT3306がONし、

映像信号VDataが入力される。さらに、TFT3309、3310がONし、TFT33

08はダイオード接続されたTFTとして振る舞う。続いて、TFT3310がOFFす

ると、図33(C)に示すように電荷が移動する。やがて、TFT3308のソース・ド

レイン間電圧、つまりTFT3308のゲート・ソース間電圧がしきい値電圧に等しくな

ったところで、図33(D)に示すようにTFT3308はOFFする。

【0328】

続いて、TFT3307、TFT3310がONする。TFT3307がONすること

によって、TFT3308のソース領域の電位は、VDataからVDDへと上昇する。よって

、TFT3308のゲート・ソース間電圧がしきい値電圧を上回ってONし、図33(E

)に示すように、EL素子3313に電流が流れて発光する。

【0329】

以上のような行程により、隣接画素間でTFT3308のしきい値電圧がばらついても

、あらかじめ駆動用TFT3308のゲート・ソース間にしきい値電圧分の電位差を作っ

ておくことが出来るため、駆動用TFT3308のゲート・ソース間電圧は隣接画素ごと

にばらつくことがない。さらに、これまでの実施例においては、ダイオード接続されたT

FTのしきい値電圧を、映像信号に上乗せすることによって、別の駆動用TFTのゲート

電極に入力するといった手法でしきい値電圧のばらつきの補正を行ってきた。ただし、こ

の手法によると、ダイオード接続されたTFTと、駆動用TFTのしきい値電圧がばらつ

いてしまった場合、満足な補正が行えない。これに対し、図33(A)に示した本実施例

の構成によると、ダイオード接続によってしきい値電圧を取得するTFTと、駆動用TF

Tとは同一のTFTを用いている。よって、近接したTFTにおいてしきい値電圧のばら

つきが生じたとしても、自らのしきい値電圧をそのまま補正に用いるので、しきい値電圧

の補正がいかなる場合でも正常に行われる。

【0330】

また、TFT3310はデジタル時間階調方式による駆動方式を適用した際、消去用T

FTとしても用いることが出来る。また、消去用TFTの位置は、任意のタイミングでE

L素子への電流供給を遮断出来る位置であれば、その位置を問わない。

【0331】

また、図34(A)(B)に示すように、TFTを制御するためのゲート信号線を、複数

のTFTで共有しても良い。例えば、図33(A)において、TFT3306とTFT3

307とは、互いに逆のタイミングでON・OFFが制御されるので、図34(A)に示

すように、一方の極性を他方の極性と逆のものとし、同一のゲート信号線3402によっ

て制御することが出来る。同様に、図33(A)において、TFT3306とTFT33

09とは同一のタイミングでON・OFFが制御されている。よって図34(B)に示す

ように、同一のゲート信号線3452によって制御することが出来る。もちろん、図34

(A)(B)に示した構成を組み合わせて用いても良い。

【0332】

ここでも、TFT3409、3459は、消去用TFTとしても用いることが出来る。

【実施例10】