半導体装置、電子デバイス及び電子デバイスの製造方法

【課題】対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めるための半導体装置を提供する。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

【解決手段】半導体基板2の上方に形成される第1絶縁膜15と、第1絶縁膜15内に形成される導電パターン19と、第1絶縁膜15上に形成される第2絶縁膜21と、第2絶縁膜21内に形成され、導電パターン19に接続されるビアプラグ24と、記ビアプラグ24の上に接続され、開口部25aを有する電極パッド25と、第2絶縁膜21内でビアプラグ24の周辺に形成される内部空間21aとを有し、電極パッド25上面及び開口部25a内には外部の突起状電極58が接続される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置、電子デバイス及び電子デバイスの製造方法に関する。

【背景技術】

【0002】

半導体装置同士を電気的に接続したり、半導体装置を回路基板上に実装したりするため、互いに向き合って配置されるパッド、バンプ等を接合させている。

【0003】

基板上の金バンプをチップ上の接合パッドに接合するために、チップ側の接合パッドの上に中間部材を重ねて形成する構造が知られている。その中間部材は、内面にテーパ状段差を有し、中央に貫通孔を有するガラス基材等から形成されている。

【0004】

そのような構造では、基板上の金バンプをチップ上の中間部材の貫通孔に通して接合パッドに接触させ、さらに重荷と熱をかけている。これにより、金バンプと接合パッドが接合され、さらに中間部材内に金バンプが広がるので、接合された金バンプと接合パッドの水平方向の荷重による位置変異が中間部材により防止される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−184070号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記のような中間部材を有するチップ構造によれば、基板上の金バンプがチップ上の中間部材の貫通孔から僅かにでも外れると、金バンプが中間部材を押圧して破損させるおそれがある。従って、金バンプと中間部材は高い精度の位置合わせが要求される。

【0007】

また、金バンプの体積が大きい場合には、溶融した金バンプが中間部材の貫通孔から溢れて横に流れるおそれがある。従って、金バンプの体積を高い精度で形成する必要がある。

【0008】

さらに、接合パッドとバンプの接続のためには加熱処理が必要となるので、その加熱温度が高い場合にはチップ内に形成される半導体素子や配線に損傷を与えるおそれがある。

【0009】

本発明の目的は、対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めることができる半導体装置、電子デバイス及び電子デバイスの製造方法を提供することにある。

【課題を解決するための手段】

【0010】

1つの観点によれば、半導体基板の上方に形成される第1絶縁膜と、前記第1絶縁膜内に形成される導電パターンと、前記第1絶縁膜上に形成される第2絶縁膜と、前記第2絶縁膜内に形成され、前記導電パターンに接続されるビアプラグと、前記ビアプラグの上に接続され、開口部を有する電極パッドと、前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、を有する半導体装置が提供される。

別の観点によれば、第1基板の上方に形成される第1絶縁膜と、前記第1絶縁膜内に形成される導電パターンと、前記第1絶縁膜の上方に形成され、前記導電パターンに電気的に接続され、開口部を有する電極パッドと、第2基板の上方と下方のいずれかに形成され、前記電極パッドの上面と前記開口部内に接合される突起状電極と、を有する電子デバイ

スが提供される。

さらに別の観点によれば、1基板の上方に形成され、開口部を有する電極パッドを、第2基板の上方と下方のいずれかに形成された突起状電極に対向させる工程と、前記第1基板と前記第2基板を互いに近づく方向に押圧し、前記突起状電極を前記電極パッドに接合させる工程と、を有する電子デバイスの製造方法が提供される。

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない、と理解される。

【発明の効果】

【0011】

電極パッドに開口部を形成しているので、電極パッドに別の素子の突起状電極を押圧して接続すると、電極パッドの上面と開口部内に突起状電極を接合することができる。このため、電極パッドと突起状電極にズレが生じても、開口部内に突起状電極がめり込むことに変わりがないので、接続部分の水平強度を高く保持できる。しかも、突起状電極を開口部内に入り込ませることにより、突起状電極が横方向に溢れることを防止することができる。

【図面の簡単な説明】

【0012】

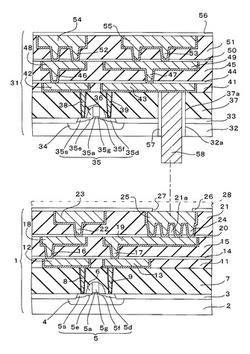

【図1】図1は、第1実施形態に係る電子デバイスを形成するための第1、第2の半導体装置の接続前の状態の一例を示す断面図である。

【図2】図2は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の電極パッドの一例を示す斜視断面図である。

【図3】図3は、第1実施形態に係る電子デバイスの一例を示す断面図である。

【図4】図4(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第1の平面図及び断面図である。

【図5】図5(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第2の平面図及び断面図である。

【図6】図6(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第3の平面図及び断面図である。

【図7】図7(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第4の平面図及び断面図である。

【図8】図8(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第5の平面図及び断面図である。

【図9】図9(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第6の平面図及び断面図である。

【図10】図10(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第7の平面図及び断面図である。

【図11】図11(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第8の平面図及び断面図である。

【図12】図12(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第9の平面図及び断面図である。

【図13】図13は、第2実施形態に係る電子デバイスに含まれる第1、第2の半導体装置の接続前の状態の一例を示す断面である。

【図14】図14は、第2実施形態に係る電子デバイスの一例を示す断面図である。

【図15】図15は、第3実施形態に係る電子デバイスに含まれる第1、第2の半導体装置の接続前の状態の一例示す断面である。

【図16】図16は、第3実施形態に係る電子デバイスの一例を示す断面図である。

【図17】図17(a)、(b)は、第4実施形態に係る電子デバイスに含まれる半導体装置の一例を示す断面図である。

【図18】図18は、第5実施形態に係る電子デバイスに含まれる半導体装置の一例を示す断面図である。

【発明を実施するための最良の形態】

【0013】

以下に、図面を参照して好ましい実施形態を説明する。図面において、同様の構成要素には同じ参照番号が付されている。

【0014】

(第1の実施の形態)

図1は、第1実施形態に係る電子デバイスに含まれる第1、第2の半導体装置を互いに接続する前の状態の一例を示す断面図である。

【0015】

第1の半導体装置1は半導体基板、例えばシリコン基板2を有し、シリコン基板2の表面にはPウエル4を囲む素子分離絶縁層3が形成されている。また、Pウエル4内とその上の領域にはn型MOSトランジスタ5が形成されている。

【0016】

n型MOSトランジスタ5は、Pウエル4上にゲート絶縁膜5aを介して形成されるゲート電極5gと、ゲート電極5gの両側領域のシリコン基板2内に形成されたn型ソース/ドレイン領域5s、5dとを有している。また、n型ソース/ドレイン領域5s、5dのうちゲート電極5g寄りの領域にはn型エクステンション領域5e、5fが形成されている。ゲート電極5gの側壁には絶縁性サイドウォール6が形成されている。

【0017】

図1においては、n型MOSトランジスタ5が1つ例示されているが、複数形成されてもよい。また、シリコン基板2には、p型MOSトランジスタ(不図示)、その他の素子が併せて形成されてもよい。

【0018】

n型MOSトランジスタ5、素子分離絶縁層3及びシリコン基板2の上には、第1層間絶縁膜7が形成されている。また、第1層間絶縁膜7内には、n型MOSトランジスタ5のソース/ドレイン領域5s、5dのそれぞれに接続される第1、第2のコンタクトプラグ8、9が形成されている。

【0019】

第1の層間絶縁膜7の上には、第2層間絶縁膜11が形成されている。第2層間絶縁膜11内には、第1、第2のコンタクトプラグ8、9のそれぞれに個別に接続される第1、第2の配線12、13が形成されている。第1、第2の配線12、13はダマシン構造を有している。

【0020】

第1、第2の配線12、13及び第2層間絶縁膜11の上には、第1の金属バリア絶縁膜14、第3層間絶縁膜15が順に形成されている。第3層間絶縁膜15内の下部には、第1の金属バリア絶縁膜14を貫通して第1、第2の配線12、13に個別に接続される第1、第2のビアプラグ16、17が形成されている。さらに、第3層間絶縁膜15内の上部には第1、第2のビアプラグ16、17のそれぞれに個別に接続される第3、第4の配線18、19が形成されている。第4の配線19である導電パターンには、後述の電極パッド25が形成される領域に重なる領域が広く形成されている。

【0021】

第1のビアプラグ16と第3の配線18は一体的に形成されるデュアルダマシン構造を有している。同様に、第2のビアプラグ17と第4の配線19もデュアルダマシン構造を有している。

【0022】

第3、第4の配線18、19及び第3層間絶縁膜15の上には、第2の金属バリア絶縁膜20と第4層間絶縁膜21が順に形成されている。第4層間絶縁膜21内の下部には、第2の金属バリア絶縁膜20を貫通して第3の配線18に達する第3のビアプラグ22が形成されている。さらに、第4層間絶縁膜21内の上部には、第3のビアプラグ22に繋

がる第5の配線23が形成されている。第3のビアプラグ22と第5の配線23はデュアルダマシン構造を有している。

【0023】

さらに、第4層間絶縁膜21内の下部には、第2の金属バリア絶縁層20を貫通して第4の配線19に達する複数の第4のビアプラグ24が形成されている。第4のビアプラグ24は少なくとも1つであってもよい。また、第4層間絶縁膜21内の上部には、第4のビアプラグ24に接続される金属製の電極パッド25が形成されている。第4のビアプラグ24及び電極パッド25は一体的に形成されるデュアルダマシン構造を有している。

【0024】

電極パッド25において、図2に例示するように、第4のビアプラグ24の周囲にはマトリクス状の複数の開口部25aが上下方向に貫通して形成されている。さらに、電極パッド25の下であって第4のビアプラグ24の周囲には、電極パッド25の開口25aに繋がる格子状の内部空間21aが形成されている。電極パッド25及び第4のビアプラグ24の形成方法については後述する。なお、開口部25aは1つ形成されてもよい。

【0025】

次に、第2の半導体装置31について説明する。

第2の半導体装置31は半導体基板、例えばシリコン基板32を有している。シリコン基板32内には、シリコン基板32の表面に形成される素子分離絶縁層33、例えばシリコン酸化層に囲まれるPウエル34が形成されている。また、Pウエル34内とその上の領域にはn型MOSトランジスタ35が形成されている。

【0026】

n型MOSトランジスタ35は、Pウエル34上にゲート絶縁膜35aを介して形成されるゲート電極35gを有し、ゲート電極35gは、ゲート絶縁膜35g上に形成されたポリシリコン膜をパターニングすることにより形成成される。

【0027】

Pウエル34内には、ゲート電極35gをマスクに使用する不純物イオン注入によりn型エクステンション領域35e、35fが形成されている。さらに、ゲート電極35gの側壁には絶縁性サイドウォール36が形成されている。また、ゲート電極35g、サイドウォール36をマスクに使用するイオン注入により、Pウエル34内にはn型ソース/ドレイン領域35s、35dが形成されている。

【0028】

図1に例示する第2の半導体装置31おいては、n型MOSトランジスタ35が1つ例示されているが、複数形成されてもよい。また、シリコン基板32には、p型MOSトランジスタ(不図示)、その他の素子が形成されてもよい。

【0029】

n型MOSトランジスタ35及びシリコン基板32の上には、第1層間絶縁膜37として例えばシリコン酸化膜が気相成長(CVD)法により形成されている。また、第1層間絶縁膜37内には、n型MOSトランジスタ35のn型ソース/ドレイン領域35s、35dのそれぞれに達する第1、第2のコンタクトプラグ38、39が形成されている。

【0030】

第1の層間絶縁膜37の上には、第2層間絶縁膜41として例えばシリコン酸化膜がCVD法により形成されている。第2層間絶縁膜41の中には、第1、第2のコンタクトプラグ38、39のそれぞれに個別に接続される第1、第2の配線42、43が形成されている。第1、第2の配線42、43のそれぞれは、チタン、タンタルの積層構造を有するバリア層とその上に形成される銅の主導体膜を有するダマシン構造に形成されている。

【0031】

第1、第2の配線42、43と第2層間絶縁膜41の上には、第1の金属バリア絶縁膜44と第3層間絶縁膜45が順に形成されている。第1の金属バリア絶縁膜44として、例えばシリコン窒化膜がCVD法により形成され、第3層間絶縁膜45として例えばシリコン酸化膜がCVD法により形成されている。

【0032】

第3層間絶縁膜45内の下部には、第1の金属拡散防止絶縁膜44を貫通して第1、第2の配線42、43のそれぞれに接続される第1、第2のビアホールが形成されている。さらに、第3層間絶縁膜45内の上部には、第1、第2のビアホールに個別に重なる第3、第4の配線溝が形成されている。

【0033】

第1のビアホール内と第3の配線溝内にはそれぞれ第1のビアプラグ46と第3の配線48が形成されている。第1のビアプラグ46及び第3の配線48は、バリアメタル層と主導体層を有するデュアルダマシン構造に形成されている。同様に、第2のビアホール内と第4の配線溝内にはそれぞれ第2のビアプラグ47と第4の配線49が形成され、第2のビアプラグ47及び第4の配線49はデュアルダマシン構造を有している。この場合、バリアメタル層としてチタンとタンタルの積層構造が形成され、主導体層として例えば銅層が形成される。

【0034】

第3、第4の配線48、49及び第3層間絶縁膜45の上には第2の金属バリア絶縁膜50と第4層間絶縁膜51が順に形成されている。第2の金属バリア絶縁膜50として、例えばシリコン窒化膜がCVD法により形成され、第3層間絶縁膜45として例えばシリコン酸化膜がCVD法により形成されている。

【0035】

第4層間絶縁膜51内の下部には、第2の金属拡散防止絶縁膜50を貫通して第3、第4の配線48、49のそれぞれに個別に達する第3、第4のビアホールが形成されている。さらに、第4層間絶縁膜51内の上部には、第3、第4のビアホールのそれぞれに繋がる第5、第6の配線溝が形成されている。第3、第4のビアホールのそれぞれの中には第3、第4のビアプラグ52、53が形成され、さらに、第5、第6の配線溝のそれぞれの中には第5、第6の配線54、55が形成されている。

第5、第6の配線54、55及び第4層間絶縁膜51の上には、カバー絶縁膜56として例えばシリコン窒化膜がCVD法により形成されている。

【0036】

互いに接続される互いに接続される第3のビアプラグ52及び第5の配線54と、互いに接続される第4のビアプラグ53と第6の配線55は、それぞれデュアルダマシン構造を有している。デュアルダマシン構造のバリアメタル層としてチタンとタンタルの積層構造が形成され、主導体層として例えば銅層が形成される。

【0037】

シリコン基板32内であって第2の配線43の下方には基板側ビアホール32aが形成されている。また、第1層間絶縁膜37内には基板側ビアホール32aに繋がる一層目のビアホール37aが形成されている。基板側ビアホール32a及び一層目のビアホール37aの内周面には金属拡散防止用の絶縁保護膜57、例えばシリコン窒化膜が形成されている。

【0038】

基板側ビアホール32aは、例えばドライエッチング、ウェットエッチング、レーザドリルリング等を利用して形成される。また、第5のビアホール37aは、例えば保護絶縁膜57を形成した後に、基板側ホール32aを通して第1層間絶縁膜37をエッチングすることにより形成される。

【0039】

さらに、基板側ビアホール32a及び第5のビアホール37a内には、絶縁保護膜57に囲まれる突起状電極58が第2の配線43の下面からシリコン基板32の下方に突出して形成されている。突起状電極58は、例えば、直径が約5μm以上に形成され、シリコン基板32の下面から例えば約1μmの量で突出されている。

【0040】

以上のような構造を有する第1の半導体装置1と第2の半導体装置31は次の方法によ

り接続される。

【0041】

まず、第1の半導体装置1の上面の全体にスペーサ絶縁膜28として例えばエポキシ、ポリイミド等の有機樹脂を例えば約200nmの厚さに塗布する。これにより、第1の半導体装置1と第2の半導体装置31の間に空孔が発生することが防止される。この場合、スペーサ絶縁膜28のうち電極パッド25の上に開口を形成する。

【0042】

続いて、突起状電極58を電極パッド25の直上に配置した状態で、第1の半導体装置1の上面と第2の半導体装置31の下面を対向させる。さらに、第1の半導体装置1と第2の半導体装置31を近づけて荷重を加えると、図3に例示するように、突起状電極58がスペーサ絶縁膜28を貫通し、続いて図2に例示する電極パッド25に接続し、さらに開口25a内にめり込む。これにより、突起状電極58と電極パッド25は、電極パッド25の面方向と厚さ方向に接合する。この場合、加熱の処理をせずに良好な接続が得られる。なお、加熱処理してもよい。

【0043】

また、突起状電極58を電極パッド25に接合する際に、少なくとも突起状電極58は変形して電極パッド25の開口部25a内に入り込む。さらに、余分な荷重がかかって、突起状電極58が開口部25aの下から内部空間21a内にはみ出させることができるので、電極パッド25の上面での横方向への広がりやはみ出しを抑制することができる。従って、突起状電極58の体積の誤差を開口部25a、内部空間21aによって吸収することができる。

【0044】

以上により、突起状電極58と電極パッド25の位置合わせが僅かにずれても、突起状電極58は電極パッド25の開口部25a内に入り込むので、電極パッド25と突起状電極58の接続部分の水平強度を高めることができる。

【0045】

次に、第1の半導体装置1の形成方法を図4〜図12に基づいて説明する。図4〜図12のそれぞれにおいて、(a)には平面の一例を示し、(b)には(a)のI−I線から見た側断面の一例を示している。

まず、図4に例示する構造を形成するまでの工程を説明する。

【0046】

図4(b)に示すように、シリコン基板2の素子分離領域に素子分離溝を形成した後に素子分離溝内にシリコン酸化膜を埋め込むことにより、素子分離絶縁層3としてシャロートレンチアイソレーションを形成する。なお、素子分離絶縁層3はLOCOS法により形成されてもよい。その後に、素子形成領域にp型不純物イオン、例えばホウ素イオンを注入することによりPウエル4を形成する。

【0047】

その後に、シリコン基板2及び素子分離絶縁層3の上にゲート絶縁膜5a、ポリシリコン膜をCVD法により順に形成した後にそれらの膜をパターニングし、Pウエル4上にストライプ状に残されたポリシリコン膜をゲート電極5gとして使用する。さらに、ゲート電極5g及び素子分離絶縁層3をマスクにしてPウエル4内にn型不純物イオン、例えばリンイオンを注入してn型エクステンション領域5e、5fを形成する。

【0048】

さらに、シリコン基板2上に例えばシリコン酸化膜をCVD法により形成し、これを垂直方向に異方性ドライエッチングすることによりゲート電極5gの側壁に絶縁性サイドウォール6を形成する。その後に、ゲート電極5g、絶縁性サイドウォール6及び素子分離絶縁層3をマスクにしてPウエル4内にn型不純物イオンを注入する。これにより、ゲート電極5gの両側のPウエル4内にn型ソース/ドレイン領域5s、5dを形成する。以上によりn型MOSトランジスタ5の基本的な構造が形成される。

【0049】

その後に、シリコン基板2及びn型MOSトランジスタ5の上に第1層間絶縁膜7としてシリコン酸化膜をプラズマ気相成長(PCVD)法により形成する。さらに、第1層間絶縁膜7をパターニングすることにより、ソース/ドレイン領域5s、5dに達する第1、第2のコンタクトホール7a、7bを形成する。その後に、第1、第2のコンタクトホール7a、7b内面に例えば窒化チタン膜を形成し、さらに第1、第2のコンタクトホール7a、7b内にタングステンを埋め込む。これにより、第1、第2のコンタクトホール7a、7b内のそれぞれに第1、第2のコンタクトプラグ8、9が形成される。この場合、第1層間絶縁膜7上に形成された窒化チタン膜、タングステン膜は、例えば化学機械研磨(CMP)法により除去される。

【0050】

次に、第1層間絶縁膜7の上に第2層間絶縁膜11として例えば酸化シリコン膜等をPCVD法により形成する。続いて、第2層間絶縁膜11をパターニングすることにより、第1、第2のコンタクトプラグ8、9のそれぞれに一部が重なる第1、第2の配線溝11a、11bを形成し、それぞれの配線溝11a、11b内に、タンタル、窒化チタンの積層構造のバリアメタル層と銅の主導体層を順に形成する。第2層間絶縁膜11上のバリアメタル層及び主導体層はCMP法により除去される。第1、第2の配線溝11a、11b内にそれぞれ残されたバリアメタル層と主導体層はそれぞれダマシン構造の第1、第2の配線12、13として使用される。

【0051】

次に、第1、第2の配線12、13及び第2層間絶縁膜11の上に第1の金属バリア絶縁膜14、第3層間絶縁膜15をPCVD法により順に形成する。第1の金属バリア絶縁膜14として例えばシリコン窒化膜をPCVD法により形成する。また、第3層間絶縁膜としてシリコン酸化膜をPCVD法により形成する。

【0052】

第3層間絶縁膜15及び第1の金属バリア絶縁膜14をパターニングして、第1、第2の配線12、13に達する深さの第1、第2のビアホール15a、15bを形成する。その後、第1、第2のビアホール15a、15bのそれぞれに一部が重なる第3、第4の配線溝15c、15dを第3層間絶縁膜15の上部に形成する。続いて、第1、第2のビアホール15a、15b、第3、第4の配線溝15c、15d内に、タンタル、窒化チタンの積層構造のバリアメタル層と銅の主導体層を順に形成する。

【0053】

続いて、第3層間絶縁膜15上のバリアメタル層、主導体層をCMP法により除去する。これにより、第1のビアホール15a及び第3の配線溝15c内のバリアメタル層と主導体層をデュアルダマシン構造の第1のビアプラグ16、第3の配線18として使用する。さらに、第2のビアホール15b及び第4の配線溝15d内のバリアメタル層と主導体層をデュアルダマシン構造の第2のビアプラグ17、第4の配線19として使用する。

【0054】

第4の配線19は、図4(a)に示すように、後の工程で形成される電極パッド25と同じ又はそれ以上の面積で重なるパッド部19aを有している。パッド部19aは、例えば1辺が10μm以上の四角形の平面形状を有している。

【0055】

次に、第3、第4の配線18、19及び第3層間絶縁膜15の上に第2の金属バリア絶縁膜20、第4層間絶縁膜21を順に形成する。第2の金属バリア絶縁膜20として例えばシリコン窒化膜をPCVD法により形成し、さらに、第4層間絶縁膜21としてシリコン酸化膜をPCVD法により1450nm〜1550nmの厚さに形成する。さらに、第4層間絶縁膜21上に、下地絶縁膜29として窒化シリコン膜をPCVD法により45nm〜55nmの厚さに形成する。

【0056】

次に、図5(a)、(b)に示す構造を形成するまでの工程を説明する。

まず、下地絶縁膜29上に第1フォトレジスト61を塗布し、これを露光、現像するこ

とにより、第3の配線23に重なる位置に第3のビア用開口61aを形成するとともに、第4の配線19のパッド部19aの上に複数の第4のビア用開口61bを形成する。第3、第4のビア用開口61a、61bのそれぞれは、例えば350nm〜450nmの直径を有している。

フォトレジストとして、本実施形態において、例えば、有機ポリマー、架橋剤、光酸発生剤を含む化学増幅レジストを使用する。

【0057】

次に、図6(a)、(b)に示す構造を形成するまでの工程を説明する。

まず、第1フォトレジスト61をマスクに使用し、第3、第4のビア用開口61a、61bを通してプラズマエッチングにより下地絶縁膜29、第4層間絶縁膜21をエッチングする。エッチング用の反応ガスとして、例えばCO、Ar、C4F8を含むガスを使用する。

【0058】

これにより、第1フォトレジスト61の第3、第4のビア用開口61a、61bのそれぞれの下には、開口径が300nm〜400nmの大きさの第3、第4のビアホール21d、21eが形成される。その後に、第1フォトレジスト61を除去する。これにより、第3、第4のビアホール21d、21eは、第3、第4の配線18、19の一部に重なる位置に形成される。続いて、残存した第1フォトレジスト61を除去する。

【0059】

その後に、図7(b)に示すように、下地絶縁膜29上と第3、第4ビアホール21d、21e内に第2フォトレジスト62を塗布し、さらに、第2フォトレジスト62を露光、現像する。これにより、第2フォトレジスト62において、第3のビアホール21dに一部が重なる第5の配線溝用開口部62aを形成するとともに、図7(a)、(b)に示すように、第4のビアホール21eを含む領域にメッシュ状のパッド用開口部62bを形成する。パッド用開口部62bの平面状の外形は、一辺が400nm以上の四角形に形成されている。

【0060】

これにより、第5の配線溝用開口部62aからは、第2フォトレジスト62に埋め込まれた第3ビアホール21dの上端が露出する。また、第2フォトレジスト62のパッド用開口部62bの中では、第2フォトレジスト62に埋め込まれた複数の第4のビアホール21eの上端が露出するとともに、複数の第4ビアホール21eに挟まれる領域のそれぞれに島状レジスト62cが形成される。

【0061】

次に、図8(a)、(b)に示すように、第5の配線溝用開口部62a、パッド用開口部62bを通して下地絶縁膜29をエッチングし、さらに第4層間絶縁膜21を途中の深さまでエッチングする。これにより、第4層間絶縁膜21内において、第3のビアホール21dに一部が重なる第5の配線溝21fが形成され、さらに複数の第4のビアホール21eに一部が重なるメッシュ状のパッド用溝21gが形成される。第5の配線溝21f、パッド用溝21gの深さは、例えば上面から700nm〜800nmとする。

【0062】

この場合、第2のフォトレジスト62が残存しないエッチング条件とし、第3、第4のビアホール21d、21eを通して第2の金属バリア絶縁膜20をエッチングし、第3、第4の配線18、19の一部を露出させる。また、島状のレジスト62cの下の第4層間絶縁膜21及び下地絶縁膜29は突起21tとして残される。

【0063】

続いて、図9(a)、(b)に示すように、下地絶縁膜29及び第4層間絶縁膜21の表面と第3、第4のビアホール21d、21e、第5の配線溝21f及びパッド用溝21gの内面の上にバリアメタル膜63を例えば40nm〜50nmの厚さに形成する。バリアメタル膜63とし、例えばチタンとタンタルをスパッタ法により順に形成する。続いて、バリアメタル膜63上に銅膜64を電解メッキ処理により2000nm〜2500nm

の厚さに形成する。電解メッキの前にバリアメタル膜63の上に薄い銅シード層を形成してもよい。

【0064】

次に、砥粒、分散剤、キレート材を含むスラリーが供給された研磨パッド(不図示)に銅膜64上面を押し当てながら、例えばシリコン基板2を回転させて銅膜64、バリアメタル膜63及び下地絶縁膜29を順に研磨する。これにより、図10(a)、(b)に示すように、銅膜64、バリアメタル膜63、下地絶縁膜29を第4層間絶縁膜21の上面上から除去する。さらに研磨を続けて、第4層間絶縁膜21を上面から45nm〜55nmの深さまで削り込み、第4層間絶縁膜21、銅膜64及びバリアメタル膜63の上面を平坦化する。

【0065】

これにより、第3、第4のビアホール21d、21e内の銅膜64、バリアメタル膜63はそれぞれ第3、第4のビアプラグ22、24となり、また、第5の配線溝21f内の銅膜64、バリアメタル膜63は第5の配線23として使用される。さらに、パッド用溝21g内の銅膜64、バリアメタル膜63は電極パッド25として使用される。

【0066】

図2に例示したように、電極パッド25の平面形状はメッシュ状になり、内部から第4層間絶縁膜21の複数の島状の突起21tの上面が露出する。また、電極パッド25の銅膜24、バリアメタル膜23のそれぞれは第4のビアプラグ24と一体になってデュアルダマシン構造となる。同様に、第3のビアプラグ22及び第5の配線23もデュアルダマシン構造となる。

【0067】

この後に、図11(a)、(b)に示すように、第5の配線23、電極パッド25及び第4層間絶縁膜21の上に、窒化シリコン、炭化シリコンなどからなる保護絶縁膜26をPCVD法により65nm〜75nmの厚さに形成する。

【0068】

その後に、保護絶縁膜26上に第3フォトレジスト66を塗布し、これを露光、現像することにより、電極パッド25の上に開口66aを形成する。開口66aは、電極パッド25の外周縁部を覆うことにより、電極パッド25の平面形状よりも狭く形成してもよい。

【0069】

続いて、図12(a)、(b)に示すように、第3のフォトレジスト66の開口66aを通して保護絶縁膜26をエッチングすることにより、電極パッド25を露出する開口部27を形成する。保護絶縁膜26のエッチングは、例えばフッ酸、リン酸を用いるウェットエッチング法、又は、フッ素含有ガスを用いるプラズマエッチング法を使用し、電極パッド25の銅膜に対してエッチング選択比が高くなる条件とする。

【0070】

これにより、電極パッド25内に現れる複数の島状の突起21tもエッチングされて複数箇所に開口25aが形成され、さらに、それらの開口25aを通して第4のビアプラグ24の周囲の第4層間絶縁膜21もエッチングされる。これにより、電極パッド25の下に内部空間21aが形成される。

【0071】

保護絶縁膜26をエッチングする際に、第4層間絶縁膜21のエッチングレートが遅い条件を選択する場合には、保護絶縁膜26に開口部27を形成した後に緩衝フッ酸溶液を用いて第4層間絶縁膜21を等方性エッチングする。この後に、第3のフォトレジスト65を溶剤により除去することにより、図1に例示した第1の半導体装置1が形成される。

【0072】

(第2の実施の形態)

図13は、第2実施形態に係る電子デバイスに含まれる第1、第2の半導体装置を互いに接続する前の状態の一例を示す断面図である。図13において、図1と同一符号は同一

要素を示している。

【0073】

図13において、第1の半導体装置1は、第1実施形態に示した構造を有し、また、第2の半導体装置71は、第1実施形態に示す第2の半導体装置31と外部端子を除いてほぼ同じ構造を有している。

【0074】

第2の半導体装置71に含まれるシリコン基板32には、第1実施形態と同様に、基板側ビアホール32aが形成され、基板側ビアホール32aの上の第1層間絶縁膜37には第5のビアホール37aが形成されている。互いに重ねて形成される第5のビアホール37aと基板側ビアホール32aの内周面には、金属拡散防止用の絶縁保護膜57、例えばシリコン窒化膜が形成されている。

【0075】

基板側ビアホール32aは、例えばドライエッチング、ウェットエッチング、レーザドリルリング等を利用して形成される。また、第5のビアホール37aは、例えば基板側ホール32aを通して第1層間絶縁膜37を垂直方向に異方性エッチングすることにより形成される。

【0076】

さらに、基板側ビアホール32a及び第5のビアホール37a内には、絶縁保護膜57に囲まれる基板側ビアプラグ68が第2の配線43の下面からシリコン基板32の裏面に達する高さに形成されている。基板側ビアプラグ68は、例えば、直径が約5μm以上に形成されている。

【0077】

シリコン基板32の下面には、基板側ビアプラグ68の下面に接続される表面配線66が形成され、表面配線66のパッド領域の上には、突起状電極の一種であるバンプ67が接合されている。バンプ67として、例えば、鉛、スズ、ニッケル、金、銀、銅等、又はそれらの合金などの金属が使用される。

【0078】

そのような構造の第2の半導体装置71のバンプ67と第1の半導体装置1の電極パッド25を接続する際には次の方法による。

【0079】

まず、第1の半導体装置1の上面の全体にスペーサ絶縁膜28として例えばエポキシ、ポリイミド等の有機樹脂を約200nmの厚さに塗布する。スペーサ絶縁膜28には、電極パッド25を露出する開口を形成する。これにより、第1の半導体装置1と第2の半導体装置71の間に空孔が発生することが防止される。

【0080】

続いて、バンプ67を電極パッド25の直上に位置させるために、第1の半導体装置1の上面と第2の半導体装置71の下面を対向させ、スペーサ絶縁膜28を介して合わせる。さらに、第2の半導体装置71から第1の半導体装置1に向けて相対的に荷重を加えると、図14に例示するように、バンプ67がスペーサ絶縁膜28を貫通し、続いて電極パッド25に接続する。

【0081】

これにより、バンプ67と電極パッド25は、電極パッド25の面方向と厚さ方向に接合する。この場合、加熱の処理をせずに良好な接続が得られる。なお、加熱処理してもよい。

【0082】

また、バンプ67が電極パッド25にめり込む際に、少なくともバンプ67が変形して電極パッド25の開口部25a内に入り込む。これにより、バンプ67と電極パッド25の位置合わせがわずかにずれても、電極パッド25とバンプ67の接合の水平強度を高めることができる。さらに、バンプ67の体積に形成誤差が生じても、バンプ67が開口部25a、内部空間21a内に入り込むので、電極パッド25の上面での広がりやはみ出し

、或いは接合不足を解消することができる。

【0083】

(第3の実施の形態)

図15は、第3実施形態に係る電子デバイスに含まれる第1、第2の半導体装置を互いに接続する前の状態の一例を示す断面図である。図15において、図1と同一符号は同一要素を示している。

【0084】

図15において、第1の半導体装置1は第1実施形態に示したと同じ構造を有し、また、第2の半導体装置72は、第1実施形態に示す第2の半導体装置31と外部端子を除いてほぼ同じ構造を有している。ただし、第2の半導体装置72は、図1とは上下の向きが反対になる状態に記載されている。

【0085】

第2の半導体装置72の第5、第6の配線54、55及び第4層間絶縁膜51の上には、第5層間絶縁膜74として例えば炭化酸化シリコン膜がCVD法により形成されている。また、第5層間絶縁膜74内には、第6の配線55に接続されるビアプラグ75が形成されている。ビアプラグ75は、例えばチタン、窒化チタンのバリアメタル膜上にタングステン膜が形成される構造を有している。

【0086】

第5層間絶縁膜74の上には、ビアプラグ75上面に接続されるアルミニウムの最上配線76が形成されている。また、最上配線76及び第5層間絶縁膜74の上にはカバー保護膜56としてシリコン窒化膜がCVD法により形成されている。また、カバー保護膜56のうちビアプラグ75の上方には、最上配線76の一部に重なる開口が形成されている。最上配線76上にはカバー保護膜56の開口を通してバンプ77が接合されている。バンプ77として、例えば、鉛、スズ、ニッケル、金、銀、銅等の金属が使用される。

【0087】

そのような構造の第2の半導体装置72のバンプ77と第1の半導体装置1の電極パッド25を接続する際には次の方法による。

【0088】

まず、第1の半導体装置1の上面の全体にスペーサ絶縁膜28として例えばエポキシ、ポリイミド等の有機樹脂を約200nmの厚さに塗布する。これにより、第1の半導体装置1と第2の半導体装置72の間に空孔が発生することが防止される。さらにスペーサ絶縁膜28には、電極パッド25を露出する開口部を形成する。

【0089】

続いて、バンプ77を電極パッド25の直上に位置させた状態で、第1の半導体装置1の上面と第2の半導体装置72の上面を対向させ。さらに、第2の半導体装置72から第1の半導体装置1の方向に相対的に荷重を加えると、図16に例示するように、バンプ77がスペーサ絶縁膜28を貫通し、続いて電極パッド25に接続する。

【0090】

これにより、バンプ77と電極パッド25は、電極パッド25の面方向と厚さ方向に接合する。この場合、加熱の処理をせずに良好な接続が得られる。なお、加熱処理してもよい。

【0091】

また、バンプ77が電極パッド25にめり込む際に、少なくともバンプ77が変形して電極パッド25の開口部25a内に入り込む。これにより、バンプ77と電極パッド25の位置合わせがわずかにずれても、電極パッド25とバンプ77の接合の水平強度を高めることができる。さらに、バンプ77の体積に形成誤差が生じても、バンプ77が開口部25a、内部空間21a内に入り込むので、電極パッド25の上面での広がりやはみ出し、或いは接合不足を解消することができる。

【0092】

(第4の実施の形態)

図17(a)は、第4実施形態に係る電子デバイスに使用される半導体装置の電極パッド及びその周辺の一例を示す平面図、図17(b)は、第4実施形態に係る電子デバイスに使用される第1の半導体装置の一例であって図17(a)のI−I線に沿う断面図である。図17(a)、(b)において、図1と同じ符号は同じ要素を示している。

【0093】

図17(a)、(b)に示す第4層間絶縁膜21内において、電極パッド25の周囲には間隔をおいて平面形状が環状のガード溝21hが形成され、さらに、ガード溝21h内にはダマシン構造のガードリングパターン69が形成されている。なお、環状の金属膜であるカードリング69は、電極パッドの周囲に間隔をおいて幾重にも横方向に広がる多重位置に形成されてもよい。

【0094】

ガード溝21hは、第1実施形態の説明で例示した図8における配線溝21gと同時に形成される。さらに、ガード溝21h内には、図9、図10に例示するバリアメタル層63と主導体層64が埋め込まれ、それらの層63、64はCMPにより残されてガードリングパターン69となる。

【0095】

以上のように、ガードリングパターン69を電極パッド25の周囲に設けることにより、第1の半導体装置1と上記実施形態の第2の半導体装置31、71、72を接続するために、電極パッド25に接続用突起58又はバンプ67、77を押圧する。その際、電極パッド25に加わる応力により第4層間絶縁膜21にクラックが発生したとしても、クラックの拡散はガードリングパターン69により防止される。従って、第1の半導体装置1の損傷を防止できる。

【0096】

(第5の実施の形態)

図18は、第5実施形態に係る電子デバイスに使用される半導体装置の一例を示す断面図である。なお、図18において、図1と同じ符号は同じ要素を示している。

【0097】

シリコン基板2の上方の第4層間絶縁膜21内には、第1実施形態と同様に、デュアルダマシン構造を有する第3のビアプラグ22及び第5の配線23と、デュアルダマシン構造を有する第4のビアプラグ24及び電極パッド25が形成されている。

【0098】

第5、第6の配線23、25及び第4層間絶縁膜21の上には、第3の金属用バリア絶縁膜80と第5層間絶縁膜81が順にPCVD法により形成されている。第3の金属バリア用絶縁膜80として例えばシリコン窒化膜を形成し、第5層間絶縁膜81としてシリコン酸化膜が形成される。

【0099】

第5層間絶縁膜81内の下部には第3の金属用バリア絶縁層80を貫通して第5の配線23に達する複数の第5のビアプラグ82が形成され、さらに第5層間絶縁膜81内の上部には第5のビアプラグ82に接続される第6の配線83が形成されている。第5のビアプラグ82は、電極パッド25の下のビアプラグ24に重なる位置に形成されている。第5のビアプラグ82と第6の配線83は、第3のビアプラグ22及び第5の配線23と同様に、デュアルダマシン構造を有している。

【0100】

また、第5層間絶縁膜81内の下部には第3の金属用バリア絶縁層80を貫通して電極パッド25に達する第6のビアプラグ84が形成され、さらに第5層間絶縁膜81内の上部には第6のビアプラグ84に接続される上側電極パッド85が形成されている。第6のビアプラグ84と上側電極パッド85は、図2に例示する第4のビアプラグ24及び電極パッド25と同様に、デュアルダマシン構造を有している。

【0101】

さらに、上側電極パッド85のうち複数の第6のビアプラグ84に挟まれる領域の上に

は上下方向に貫通する開口部85aが形成されている。さらに、電極パッド25の上であって第6のビアプラグ84の周囲には、上側電極パッド85の開口部85aに繋がる格子状の内部空間81aが形成されている。なお、上側電極パッド85の周辺にも第4実施形態に記載のガードリングを形成してもよい。

【0102】

以上のような本実施形態における第1の半導体装置1においては、電極パッド25の上に同一構造又は類似構造の上側電極パッド85を重ねて形成している。これにより、電極パッド25及び上側電極パッド85の開口部25a、85a及び内部空間81a、21aによって電極パッド領域の空間が広くなるので、上記実施形態の接続用突起58又はバンプ67、77を受け入れる容量が多くなる。

【0103】

また、第1〜第4実施形態と同様に、接続用突起58等と上側電極パッド85を接合する際に、僅かなズレが生じても開口部25a、85a内に接続用突起58等を入り込ませることができ、水平方向の接合強度が高まる。さらに、バンプ67、77又は接続用突起58の突出量が多くても内部空間21a、81a内に入り込ませることにより側方へのはみ出しを防止することができる。

【0104】

ところで、上記の各実施形態では、第1の半導体装置1に接続するデバイスとして第2の半導体装置31、71、72について説明したが、プリント基板に突起電極を設けたプリント基板を電極パッド25、85に接合させてもよい。また、上記の各実施形態における電極パッド25、85の開口部25a、85aは少なくとも1つあればよい。

【0105】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができると理解される。

【0106】

次に、実施形態を付記する。

(付記1)半導体基板の上方に形成される第1絶縁膜と、前記第1絶縁膜内に形成される導電パターンと、前記第1絶縁膜上に形成される第2絶縁膜と、前記第2絶縁膜内に形成され、前記導電パターンに接続されるビアプラグと、前記ビアプラグの上に接続され、開口部を有する電極パッドと、前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、を有する半導体装置。

(付記2)前記ビアプラグと前記電極パッドは一体に形成されている付記1に記載の半導体装置。

(付記3)前記電極パッドの周囲に間隔をおいて形成されるガードリングを有する付記1又は2に記載の半導体装置。

(付記4)前記電極パッドと前記導電パターンの間に形成され、開口部を有する下側の電極パッドを含む付記1乃至付記3のいずれか1つに記載の半導体装置。

(付記5)第1基板の上方に形成される第1絶縁膜と、前記第1絶縁膜内に形成される導電パターンと、前記第1絶縁膜の上方に形成され、前記導電パターンに電気的に接続され、開口部を有する電極パッドと、第2基板の上方と下方のいずれかに形成され、前記電極パッドの上面と前記開口部内に接合される突起状電極と、を有する電子デバイス。

(付記6)前記第1絶縁膜上に形成される第2絶縁膜と、前記第2絶縁膜内に形成され、前記電極パッドの下面側と前記導電パターンに接続されるビアプラグと、前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、を有する付記5に記載の電子デバイス。

(付記7)前記突起状電極が前記内部空間内に入り込む構造を有する付記6に記載の電子

デバイス。

(付記8)前記突起状電極はバンプである付記5乃至付記7のいずれか1つに記載の電子デバイス。

(付記9)第1基板の上方に形成され、開口部を有する電極パッドを、第2基板の上方と下方のいずれかに形成された突起状電極に対向させる工程と、前記第1基板と前記第2基板を互いに近づく方向に押圧し、前記突起状電極を前記電極パッドに接合させる工程と、を有する電子デバイスの製造方法。

【符号の説明】

【0107】

1 半導体装置

2 シリコン基板

5 n型MOSトランジスタ

8、9 コンタクトプラグ

7、11、15、21 層間絶縁膜

21a 内部空間

14、20 金属バリア絶縁膜

12、13、18、19、23 配線

16、17、22、24 ビアプラグ

25 電極パッド

25a 開口部

31 半導体装置

32 シリコン基板

35 n型MOSトランジスタ

38、39 コンタクトプラグ

37、41、45、51、81 層間絶縁膜

44、50、80 金属バリア絶縁膜

42、43、48、49、54、55、83 配線

46、47、52、53、82、84 ビアプラグ

58、85 突起状電極

67、77 バンプ

69 ガードリングパターン

【技術分野】

【0001】

本発明は、半導体装置、電子デバイス及び電子デバイスの製造方法に関する。

【背景技術】

【0002】

半導体装置同士を電気的に接続したり、半導体装置を回路基板上に実装したりするため、互いに向き合って配置されるパッド、バンプ等を接合させている。

【0003】

基板上の金バンプをチップ上の接合パッドに接合するために、チップ側の接合パッドの上に中間部材を重ねて形成する構造が知られている。その中間部材は、内面にテーパ状段差を有し、中央に貫通孔を有するガラス基材等から形成されている。

【0004】

そのような構造では、基板上の金バンプをチップ上の中間部材の貫通孔に通して接合パッドに接触させ、さらに重荷と熱をかけている。これにより、金バンプと接合パッドが接合され、さらに中間部材内に金バンプが広がるので、接合された金バンプと接合パッドの水平方向の荷重による位置変異が中間部材により防止される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−184070号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記のような中間部材を有するチップ構造によれば、基板上の金バンプがチップ上の中間部材の貫通孔から僅かにでも外れると、金バンプが中間部材を押圧して破損させるおそれがある。従って、金バンプと中間部材は高い精度の位置合わせが要求される。

【0007】

また、金バンプの体積が大きい場合には、溶融した金バンプが中間部材の貫通孔から溢れて横に流れるおそれがある。従って、金バンプの体積を高い精度で形成する必要がある。

【0008】

さらに、接合パッドとバンプの接続のためには加熱処理が必要となるので、その加熱温度が高い場合にはチップ内に形成される半導体素子や配線に損傷を与えるおそれがある。

【0009】

本発明の目的は、対向するバンプ、パッド等を良好に接続し、接続部分の水平強度を高めることができる半導体装置、電子デバイス及び電子デバイスの製造方法を提供することにある。

【課題を解決するための手段】

【0010】

1つの観点によれば、半導体基板の上方に形成される第1絶縁膜と、前記第1絶縁膜内に形成される導電パターンと、前記第1絶縁膜上に形成される第2絶縁膜と、前記第2絶縁膜内に形成され、前記導電パターンに接続されるビアプラグと、前記ビアプラグの上に接続され、開口部を有する電極パッドと、前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、を有する半導体装置が提供される。

別の観点によれば、第1基板の上方に形成される第1絶縁膜と、前記第1絶縁膜内に形成される導電パターンと、前記第1絶縁膜の上方に形成され、前記導電パターンに電気的に接続され、開口部を有する電極パッドと、第2基板の上方と下方のいずれかに形成され、前記電極パッドの上面と前記開口部内に接合される突起状電極と、を有する電子デバイ

スが提供される。

さらに別の観点によれば、1基板の上方に形成され、開口部を有する電極パッドを、第2基板の上方と下方のいずれかに形成された突起状電極に対向させる工程と、前記第1基板と前記第2基板を互いに近づく方向に押圧し、前記突起状電極を前記電極パッドに接合させる工程と、を有する電子デバイスの製造方法が提供される。

発明の目的および利点は、請求の範囲に具体的に記載された構成要素および組み合わせによって実現され達成される。前述の一般的な説明および以下の詳細な説明は、典型例および説明のためのものであって、本発明を限定するためのものではない、と理解される。

【発明の効果】

【0011】

電極パッドに開口部を形成しているので、電極パッドに別の素子の突起状電極を押圧して接続すると、電極パッドの上面と開口部内に突起状電極を接合することができる。このため、電極パッドと突起状電極にズレが生じても、開口部内に突起状電極がめり込むことに変わりがないので、接続部分の水平強度を高く保持できる。しかも、突起状電極を開口部内に入り込ませることにより、突起状電極が横方向に溢れることを防止することができる。

【図面の簡単な説明】

【0012】

【図1】図1は、第1実施形態に係る電子デバイスを形成するための第1、第2の半導体装置の接続前の状態の一例を示す断面図である。

【図2】図2は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の電極パッドの一例を示す斜視断面図である。

【図3】図3は、第1実施形態に係る電子デバイスの一例を示す断面図である。

【図4】図4(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第1の平面図及び断面図である。

【図5】図5(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第2の平面図及び断面図である。

【図6】図6(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第3の平面図及び断面図である。

【図7】図7(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第4の平面図及び断面図である。

【図8】図8(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第5の平面図及び断面図である。

【図9】図9(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第6の平面図及び断面図である。

【図10】図10(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第7の平面図及び断面図である。

【図11】図11(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第8の平面図及び断面図である。

【図12】図12(a)、(b)は、第1実施形態に係る電子デバイスに含まれる第1の半導体装置の製造工程の一例を示す第9の平面図及び断面図である。

【図13】図13は、第2実施形態に係る電子デバイスに含まれる第1、第2の半導体装置の接続前の状態の一例を示す断面である。

【図14】図14は、第2実施形態に係る電子デバイスの一例を示す断面図である。

【図15】図15は、第3実施形態に係る電子デバイスに含まれる第1、第2の半導体装置の接続前の状態の一例示す断面である。

【図16】図16は、第3実施形態に係る電子デバイスの一例を示す断面図である。

【図17】図17(a)、(b)は、第4実施形態に係る電子デバイスに含まれる半導体装置の一例を示す断面図である。

【図18】図18は、第5実施形態に係る電子デバイスに含まれる半導体装置の一例を示す断面図である。

【発明を実施するための最良の形態】

【0013】

以下に、図面を参照して好ましい実施形態を説明する。図面において、同様の構成要素には同じ参照番号が付されている。

【0014】

(第1の実施の形態)

図1は、第1実施形態に係る電子デバイスに含まれる第1、第2の半導体装置を互いに接続する前の状態の一例を示す断面図である。

【0015】

第1の半導体装置1は半導体基板、例えばシリコン基板2を有し、シリコン基板2の表面にはPウエル4を囲む素子分離絶縁層3が形成されている。また、Pウエル4内とその上の領域にはn型MOSトランジスタ5が形成されている。

【0016】

n型MOSトランジスタ5は、Pウエル4上にゲート絶縁膜5aを介して形成されるゲート電極5gと、ゲート電極5gの両側領域のシリコン基板2内に形成されたn型ソース/ドレイン領域5s、5dとを有している。また、n型ソース/ドレイン領域5s、5dのうちゲート電極5g寄りの領域にはn型エクステンション領域5e、5fが形成されている。ゲート電極5gの側壁には絶縁性サイドウォール6が形成されている。

【0017】

図1においては、n型MOSトランジスタ5が1つ例示されているが、複数形成されてもよい。また、シリコン基板2には、p型MOSトランジスタ(不図示)、その他の素子が併せて形成されてもよい。

【0018】

n型MOSトランジスタ5、素子分離絶縁層3及びシリコン基板2の上には、第1層間絶縁膜7が形成されている。また、第1層間絶縁膜7内には、n型MOSトランジスタ5のソース/ドレイン領域5s、5dのそれぞれに接続される第1、第2のコンタクトプラグ8、9が形成されている。

【0019】

第1の層間絶縁膜7の上には、第2層間絶縁膜11が形成されている。第2層間絶縁膜11内には、第1、第2のコンタクトプラグ8、9のそれぞれに個別に接続される第1、第2の配線12、13が形成されている。第1、第2の配線12、13はダマシン構造を有している。

【0020】

第1、第2の配線12、13及び第2層間絶縁膜11の上には、第1の金属バリア絶縁膜14、第3層間絶縁膜15が順に形成されている。第3層間絶縁膜15内の下部には、第1の金属バリア絶縁膜14を貫通して第1、第2の配線12、13に個別に接続される第1、第2のビアプラグ16、17が形成されている。さらに、第3層間絶縁膜15内の上部には第1、第2のビアプラグ16、17のそれぞれに個別に接続される第3、第4の配線18、19が形成されている。第4の配線19である導電パターンには、後述の電極パッド25が形成される領域に重なる領域が広く形成されている。

【0021】

第1のビアプラグ16と第3の配線18は一体的に形成されるデュアルダマシン構造を有している。同様に、第2のビアプラグ17と第4の配線19もデュアルダマシン構造を有している。

【0022】

第3、第4の配線18、19及び第3層間絶縁膜15の上には、第2の金属バリア絶縁膜20と第4層間絶縁膜21が順に形成されている。第4層間絶縁膜21内の下部には、第2の金属バリア絶縁膜20を貫通して第3の配線18に達する第3のビアプラグ22が形成されている。さらに、第4層間絶縁膜21内の上部には、第3のビアプラグ22に繋

がる第5の配線23が形成されている。第3のビアプラグ22と第5の配線23はデュアルダマシン構造を有している。

【0023】

さらに、第4層間絶縁膜21内の下部には、第2の金属バリア絶縁層20を貫通して第4の配線19に達する複数の第4のビアプラグ24が形成されている。第4のビアプラグ24は少なくとも1つであってもよい。また、第4層間絶縁膜21内の上部には、第4のビアプラグ24に接続される金属製の電極パッド25が形成されている。第4のビアプラグ24及び電極パッド25は一体的に形成されるデュアルダマシン構造を有している。

【0024】

電極パッド25において、図2に例示するように、第4のビアプラグ24の周囲にはマトリクス状の複数の開口部25aが上下方向に貫通して形成されている。さらに、電極パッド25の下であって第4のビアプラグ24の周囲には、電極パッド25の開口25aに繋がる格子状の内部空間21aが形成されている。電極パッド25及び第4のビアプラグ24の形成方法については後述する。なお、開口部25aは1つ形成されてもよい。

【0025】

次に、第2の半導体装置31について説明する。

第2の半導体装置31は半導体基板、例えばシリコン基板32を有している。シリコン基板32内には、シリコン基板32の表面に形成される素子分離絶縁層33、例えばシリコン酸化層に囲まれるPウエル34が形成されている。また、Pウエル34内とその上の領域にはn型MOSトランジスタ35が形成されている。

【0026】

n型MOSトランジスタ35は、Pウエル34上にゲート絶縁膜35aを介して形成されるゲート電極35gを有し、ゲート電極35gは、ゲート絶縁膜35g上に形成されたポリシリコン膜をパターニングすることにより形成成される。

【0027】

Pウエル34内には、ゲート電極35gをマスクに使用する不純物イオン注入によりn型エクステンション領域35e、35fが形成されている。さらに、ゲート電極35gの側壁には絶縁性サイドウォール36が形成されている。また、ゲート電極35g、サイドウォール36をマスクに使用するイオン注入により、Pウエル34内にはn型ソース/ドレイン領域35s、35dが形成されている。

【0028】

図1に例示する第2の半導体装置31おいては、n型MOSトランジスタ35が1つ例示されているが、複数形成されてもよい。また、シリコン基板32には、p型MOSトランジスタ(不図示)、その他の素子が形成されてもよい。

【0029】

n型MOSトランジスタ35及びシリコン基板32の上には、第1層間絶縁膜37として例えばシリコン酸化膜が気相成長(CVD)法により形成されている。また、第1層間絶縁膜37内には、n型MOSトランジスタ35のn型ソース/ドレイン領域35s、35dのそれぞれに達する第1、第2のコンタクトプラグ38、39が形成されている。

【0030】

第1の層間絶縁膜37の上には、第2層間絶縁膜41として例えばシリコン酸化膜がCVD法により形成されている。第2層間絶縁膜41の中には、第1、第2のコンタクトプラグ38、39のそれぞれに個別に接続される第1、第2の配線42、43が形成されている。第1、第2の配線42、43のそれぞれは、チタン、タンタルの積層構造を有するバリア層とその上に形成される銅の主導体膜を有するダマシン構造に形成されている。

【0031】

第1、第2の配線42、43と第2層間絶縁膜41の上には、第1の金属バリア絶縁膜44と第3層間絶縁膜45が順に形成されている。第1の金属バリア絶縁膜44として、例えばシリコン窒化膜がCVD法により形成され、第3層間絶縁膜45として例えばシリコン酸化膜がCVD法により形成されている。

【0032】

第3層間絶縁膜45内の下部には、第1の金属拡散防止絶縁膜44を貫通して第1、第2の配線42、43のそれぞれに接続される第1、第2のビアホールが形成されている。さらに、第3層間絶縁膜45内の上部には、第1、第2のビアホールに個別に重なる第3、第4の配線溝が形成されている。

【0033】

第1のビアホール内と第3の配線溝内にはそれぞれ第1のビアプラグ46と第3の配線48が形成されている。第1のビアプラグ46及び第3の配線48は、バリアメタル層と主導体層を有するデュアルダマシン構造に形成されている。同様に、第2のビアホール内と第4の配線溝内にはそれぞれ第2のビアプラグ47と第4の配線49が形成され、第2のビアプラグ47及び第4の配線49はデュアルダマシン構造を有している。この場合、バリアメタル層としてチタンとタンタルの積層構造が形成され、主導体層として例えば銅層が形成される。

【0034】

第3、第4の配線48、49及び第3層間絶縁膜45の上には第2の金属バリア絶縁膜50と第4層間絶縁膜51が順に形成されている。第2の金属バリア絶縁膜50として、例えばシリコン窒化膜がCVD法により形成され、第3層間絶縁膜45として例えばシリコン酸化膜がCVD法により形成されている。

【0035】

第4層間絶縁膜51内の下部には、第2の金属拡散防止絶縁膜50を貫通して第3、第4の配線48、49のそれぞれに個別に達する第3、第4のビアホールが形成されている。さらに、第4層間絶縁膜51内の上部には、第3、第4のビアホールのそれぞれに繋がる第5、第6の配線溝が形成されている。第3、第4のビアホールのそれぞれの中には第3、第4のビアプラグ52、53が形成され、さらに、第5、第6の配線溝のそれぞれの中には第5、第6の配線54、55が形成されている。

第5、第6の配線54、55及び第4層間絶縁膜51の上には、カバー絶縁膜56として例えばシリコン窒化膜がCVD法により形成されている。

【0036】

互いに接続される互いに接続される第3のビアプラグ52及び第5の配線54と、互いに接続される第4のビアプラグ53と第6の配線55は、それぞれデュアルダマシン構造を有している。デュアルダマシン構造のバリアメタル層としてチタンとタンタルの積層構造が形成され、主導体層として例えば銅層が形成される。

【0037】

シリコン基板32内であって第2の配線43の下方には基板側ビアホール32aが形成されている。また、第1層間絶縁膜37内には基板側ビアホール32aに繋がる一層目のビアホール37aが形成されている。基板側ビアホール32a及び一層目のビアホール37aの内周面には金属拡散防止用の絶縁保護膜57、例えばシリコン窒化膜が形成されている。

【0038】

基板側ビアホール32aは、例えばドライエッチング、ウェットエッチング、レーザドリルリング等を利用して形成される。また、第5のビアホール37aは、例えば保護絶縁膜57を形成した後に、基板側ホール32aを通して第1層間絶縁膜37をエッチングすることにより形成される。

【0039】

さらに、基板側ビアホール32a及び第5のビアホール37a内には、絶縁保護膜57に囲まれる突起状電極58が第2の配線43の下面からシリコン基板32の下方に突出して形成されている。突起状電極58は、例えば、直径が約5μm以上に形成され、シリコン基板32の下面から例えば約1μmの量で突出されている。

【0040】

以上のような構造を有する第1の半導体装置1と第2の半導体装置31は次の方法によ

り接続される。

【0041】

まず、第1の半導体装置1の上面の全体にスペーサ絶縁膜28として例えばエポキシ、ポリイミド等の有機樹脂を例えば約200nmの厚さに塗布する。これにより、第1の半導体装置1と第2の半導体装置31の間に空孔が発生することが防止される。この場合、スペーサ絶縁膜28のうち電極パッド25の上に開口を形成する。

【0042】

続いて、突起状電極58を電極パッド25の直上に配置した状態で、第1の半導体装置1の上面と第2の半導体装置31の下面を対向させる。さらに、第1の半導体装置1と第2の半導体装置31を近づけて荷重を加えると、図3に例示するように、突起状電極58がスペーサ絶縁膜28を貫通し、続いて図2に例示する電極パッド25に接続し、さらに開口25a内にめり込む。これにより、突起状電極58と電極パッド25は、電極パッド25の面方向と厚さ方向に接合する。この場合、加熱の処理をせずに良好な接続が得られる。なお、加熱処理してもよい。

【0043】

また、突起状電極58を電極パッド25に接合する際に、少なくとも突起状電極58は変形して電極パッド25の開口部25a内に入り込む。さらに、余分な荷重がかかって、突起状電極58が開口部25aの下から内部空間21a内にはみ出させることができるので、電極パッド25の上面での横方向への広がりやはみ出しを抑制することができる。従って、突起状電極58の体積の誤差を開口部25a、内部空間21aによって吸収することができる。

【0044】

以上により、突起状電極58と電極パッド25の位置合わせが僅かにずれても、突起状電極58は電極パッド25の開口部25a内に入り込むので、電極パッド25と突起状電極58の接続部分の水平強度を高めることができる。

【0045】

次に、第1の半導体装置1の形成方法を図4〜図12に基づいて説明する。図4〜図12のそれぞれにおいて、(a)には平面の一例を示し、(b)には(a)のI−I線から見た側断面の一例を示している。

まず、図4に例示する構造を形成するまでの工程を説明する。

【0046】

図4(b)に示すように、シリコン基板2の素子分離領域に素子分離溝を形成した後に素子分離溝内にシリコン酸化膜を埋め込むことにより、素子分離絶縁層3としてシャロートレンチアイソレーションを形成する。なお、素子分離絶縁層3はLOCOS法により形成されてもよい。その後に、素子形成領域にp型不純物イオン、例えばホウ素イオンを注入することによりPウエル4を形成する。

【0047】

その後に、シリコン基板2及び素子分離絶縁層3の上にゲート絶縁膜5a、ポリシリコン膜をCVD法により順に形成した後にそれらの膜をパターニングし、Pウエル4上にストライプ状に残されたポリシリコン膜をゲート電極5gとして使用する。さらに、ゲート電極5g及び素子分離絶縁層3をマスクにしてPウエル4内にn型不純物イオン、例えばリンイオンを注入してn型エクステンション領域5e、5fを形成する。

【0048】

さらに、シリコン基板2上に例えばシリコン酸化膜をCVD法により形成し、これを垂直方向に異方性ドライエッチングすることによりゲート電極5gの側壁に絶縁性サイドウォール6を形成する。その後に、ゲート電極5g、絶縁性サイドウォール6及び素子分離絶縁層3をマスクにしてPウエル4内にn型不純物イオンを注入する。これにより、ゲート電極5gの両側のPウエル4内にn型ソース/ドレイン領域5s、5dを形成する。以上によりn型MOSトランジスタ5の基本的な構造が形成される。

【0049】

その後に、シリコン基板2及びn型MOSトランジスタ5の上に第1層間絶縁膜7としてシリコン酸化膜をプラズマ気相成長(PCVD)法により形成する。さらに、第1層間絶縁膜7をパターニングすることにより、ソース/ドレイン領域5s、5dに達する第1、第2のコンタクトホール7a、7bを形成する。その後に、第1、第2のコンタクトホール7a、7b内面に例えば窒化チタン膜を形成し、さらに第1、第2のコンタクトホール7a、7b内にタングステンを埋め込む。これにより、第1、第2のコンタクトホール7a、7b内のそれぞれに第1、第2のコンタクトプラグ8、9が形成される。この場合、第1層間絶縁膜7上に形成された窒化チタン膜、タングステン膜は、例えば化学機械研磨(CMP)法により除去される。

【0050】

次に、第1層間絶縁膜7の上に第2層間絶縁膜11として例えば酸化シリコン膜等をPCVD法により形成する。続いて、第2層間絶縁膜11をパターニングすることにより、第1、第2のコンタクトプラグ8、9のそれぞれに一部が重なる第1、第2の配線溝11a、11bを形成し、それぞれの配線溝11a、11b内に、タンタル、窒化チタンの積層構造のバリアメタル層と銅の主導体層を順に形成する。第2層間絶縁膜11上のバリアメタル層及び主導体層はCMP法により除去される。第1、第2の配線溝11a、11b内にそれぞれ残されたバリアメタル層と主導体層はそれぞれダマシン構造の第1、第2の配線12、13として使用される。

【0051】

次に、第1、第2の配線12、13及び第2層間絶縁膜11の上に第1の金属バリア絶縁膜14、第3層間絶縁膜15をPCVD法により順に形成する。第1の金属バリア絶縁膜14として例えばシリコン窒化膜をPCVD法により形成する。また、第3層間絶縁膜としてシリコン酸化膜をPCVD法により形成する。

【0052】

第3層間絶縁膜15及び第1の金属バリア絶縁膜14をパターニングして、第1、第2の配線12、13に達する深さの第1、第2のビアホール15a、15bを形成する。その後、第1、第2のビアホール15a、15bのそれぞれに一部が重なる第3、第4の配線溝15c、15dを第3層間絶縁膜15の上部に形成する。続いて、第1、第2のビアホール15a、15b、第3、第4の配線溝15c、15d内に、タンタル、窒化チタンの積層構造のバリアメタル層と銅の主導体層を順に形成する。

【0053】

続いて、第3層間絶縁膜15上のバリアメタル層、主導体層をCMP法により除去する。これにより、第1のビアホール15a及び第3の配線溝15c内のバリアメタル層と主導体層をデュアルダマシン構造の第1のビアプラグ16、第3の配線18として使用する。さらに、第2のビアホール15b及び第4の配線溝15d内のバリアメタル層と主導体層をデュアルダマシン構造の第2のビアプラグ17、第4の配線19として使用する。

【0054】

第4の配線19は、図4(a)に示すように、後の工程で形成される電極パッド25と同じ又はそれ以上の面積で重なるパッド部19aを有している。パッド部19aは、例えば1辺が10μm以上の四角形の平面形状を有している。

【0055】

次に、第3、第4の配線18、19及び第3層間絶縁膜15の上に第2の金属バリア絶縁膜20、第4層間絶縁膜21を順に形成する。第2の金属バリア絶縁膜20として例えばシリコン窒化膜をPCVD法により形成し、さらに、第4層間絶縁膜21としてシリコン酸化膜をPCVD法により1450nm〜1550nmの厚さに形成する。さらに、第4層間絶縁膜21上に、下地絶縁膜29として窒化シリコン膜をPCVD法により45nm〜55nmの厚さに形成する。

【0056】

次に、図5(a)、(b)に示す構造を形成するまでの工程を説明する。

まず、下地絶縁膜29上に第1フォトレジスト61を塗布し、これを露光、現像するこ

とにより、第3の配線23に重なる位置に第3のビア用開口61aを形成するとともに、第4の配線19のパッド部19aの上に複数の第4のビア用開口61bを形成する。第3、第4のビア用開口61a、61bのそれぞれは、例えば350nm〜450nmの直径を有している。

フォトレジストとして、本実施形態において、例えば、有機ポリマー、架橋剤、光酸発生剤を含む化学増幅レジストを使用する。

【0057】

次に、図6(a)、(b)に示す構造を形成するまでの工程を説明する。

まず、第1フォトレジスト61をマスクに使用し、第3、第4のビア用開口61a、61bを通してプラズマエッチングにより下地絶縁膜29、第4層間絶縁膜21をエッチングする。エッチング用の反応ガスとして、例えばCO、Ar、C4F8を含むガスを使用する。

【0058】

これにより、第1フォトレジスト61の第3、第4のビア用開口61a、61bのそれぞれの下には、開口径が300nm〜400nmの大きさの第3、第4のビアホール21d、21eが形成される。その後に、第1フォトレジスト61を除去する。これにより、第3、第4のビアホール21d、21eは、第3、第4の配線18、19の一部に重なる位置に形成される。続いて、残存した第1フォトレジスト61を除去する。

【0059】

その後に、図7(b)に示すように、下地絶縁膜29上と第3、第4ビアホール21d、21e内に第2フォトレジスト62を塗布し、さらに、第2フォトレジスト62を露光、現像する。これにより、第2フォトレジスト62において、第3のビアホール21dに一部が重なる第5の配線溝用開口部62aを形成するとともに、図7(a)、(b)に示すように、第4のビアホール21eを含む領域にメッシュ状のパッド用開口部62bを形成する。パッド用開口部62bの平面状の外形は、一辺が400nm以上の四角形に形成されている。

【0060】

これにより、第5の配線溝用開口部62aからは、第2フォトレジスト62に埋め込まれた第3ビアホール21dの上端が露出する。また、第2フォトレジスト62のパッド用開口部62bの中では、第2フォトレジスト62に埋め込まれた複数の第4のビアホール21eの上端が露出するとともに、複数の第4ビアホール21eに挟まれる領域のそれぞれに島状レジスト62cが形成される。

【0061】

次に、図8(a)、(b)に示すように、第5の配線溝用開口部62a、パッド用開口部62bを通して下地絶縁膜29をエッチングし、さらに第4層間絶縁膜21を途中の深さまでエッチングする。これにより、第4層間絶縁膜21内において、第3のビアホール21dに一部が重なる第5の配線溝21fが形成され、さらに複数の第4のビアホール21eに一部が重なるメッシュ状のパッド用溝21gが形成される。第5の配線溝21f、パッド用溝21gの深さは、例えば上面から700nm〜800nmとする。

【0062】

この場合、第2のフォトレジスト62が残存しないエッチング条件とし、第3、第4のビアホール21d、21eを通して第2の金属バリア絶縁膜20をエッチングし、第3、第4の配線18、19の一部を露出させる。また、島状のレジスト62cの下の第4層間絶縁膜21及び下地絶縁膜29は突起21tとして残される。

【0063】

続いて、図9(a)、(b)に示すように、下地絶縁膜29及び第4層間絶縁膜21の表面と第3、第4のビアホール21d、21e、第5の配線溝21f及びパッド用溝21gの内面の上にバリアメタル膜63を例えば40nm〜50nmの厚さに形成する。バリアメタル膜63とし、例えばチタンとタンタルをスパッタ法により順に形成する。続いて、バリアメタル膜63上に銅膜64を電解メッキ処理により2000nm〜2500nm

の厚さに形成する。電解メッキの前にバリアメタル膜63の上に薄い銅シード層を形成してもよい。

【0064】

次に、砥粒、分散剤、キレート材を含むスラリーが供給された研磨パッド(不図示)に銅膜64上面を押し当てながら、例えばシリコン基板2を回転させて銅膜64、バリアメタル膜63及び下地絶縁膜29を順に研磨する。これにより、図10(a)、(b)に示すように、銅膜64、バリアメタル膜63、下地絶縁膜29を第4層間絶縁膜21の上面上から除去する。さらに研磨を続けて、第4層間絶縁膜21を上面から45nm〜55nmの深さまで削り込み、第4層間絶縁膜21、銅膜64及びバリアメタル膜63の上面を平坦化する。

【0065】

これにより、第3、第4のビアホール21d、21e内の銅膜64、バリアメタル膜63はそれぞれ第3、第4のビアプラグ22、24となり、また、第5の配線溝21f内の銅膜64、バリアメタル膜63は第5の配線23として使用される。さらに、パッド用溝21g内の銅膜64、バリアメタル膜63は電極パッド25として使用される。

【0066】

図2に例示したように、電極パッド25の平面形状はメッシュ状になり、内部から第4層間絶縁膜21の複数の島状の突起21tの上面が露出する。また、電極パッド25の銅膜24、バリアメタル膜23のそれぞれは第4のビアプラグ24と一体になってデュアルダマシン構造となる。同様に、第3のビアプラグ22及び第5の配線23もデュアルダマシン構造となる。

【0067】

この後に、図11(a)、(b)に示すように、第5の配線23、電極パッド25及び第4層間絶縁膜21の上に、窒化シリコン、炭化シリコンなどからなる保護絶縁膜26をPCVD法により65nm〜75nmの厚さに形成する。

【0068】

その後に、保護絶縁膜26上に第3フォトレジスト66を塗布し、これを露光、現像することにより、電極パッド25の上に開口66aを形成する。開口66aは、電極パッド25の外周縁部を覆うことにより、電極パッド25の平面形状よりも狭く形成してもよい。

【0069】

続いて、図12(a)、(b)に示すように、第3のフォトレジスト66の開口66aを通して保護絶縁膜26をエッチングすることにより、電極パッド25を露出する開口部27を形成する。保護絶縁膜26のエッチングは、例えばフッ酸、リン酸を用いるウェットエッチング法、又は、フッ素含有ガスを用いるプラズマエッチング法を使用し、電極パッド25の銅膜に対してエッチング選択比が高くなる条件とする。

【0070】

これにより、電極パッド25内に現れる複数の島状の突起21tもエッチングされて複数箇所に開口25aが形成され、さらに、それらの開口25aを通して第4のビアプラグ24の周囲の第4層間絶縁膜21もエッチングされる。これにより、電極パッド25の下に内部空間21aが形成される。

【0071】

保護絶縁膜26をエッチングする際に、第4層間絶縁膜21のエッチングレートが遅い条件を選択する場合には、保護絶縁膜26に開口部27を形成した後に緩衝フッ酸溶液を用いて第4層間絶縁膜21を等方性エッチングする。この後に、第3のフォトレジスト65を溶剤により除去することにより、図1に例示した第1の半導体装置1が形成される。

【0072】

(第2の実施の形態)

図13は、第2実施形態に係る電子デバイスに含まれる第1、第2の半導体装置を互いに接続する前の状態の一例を示す断面図である。図13において、図1と同一符号は同一

要素を示している。

【0073】

図13において、第1の半導体装置1は、第1実施形態に示した構造を有し、また、第2の半導体装置71は、第1実施形態に示す第2の半導体装置31と外部端子を除いてほぼ同じ構造を有している。

【0074】

第2の半導体装置71に含まれるシリコン基板32には、第1実施形態と同様に、基板側ビアホール32aが形成され、基板側ビアホール32aの上の第1層間絶縁膜37には第5のビアホール37aが形成されている。互いに重ねて形成される第5のビアホール37aと基板側ビアホール32aの内周面には、金属拡散防止用の絶縁保護膜57、例えばシリコン窒化膜が形成されている。

【0075】

基板側ビアホール32aは、例えばドライエッチング、ウェットエッチング、レーザドリルリング等を利用して形成される。また、第5のビアホール37aは、例えば基板側ホール32aを通して第1層間絶縁膜37を垂直方向に異方性エッチングすることにより形成される。

【0076】

さらに、基板側ビアホール32a及び第5のビアホール37a内には、絶縁保護膜57に囲まれる基板側ビアプラグ68が第2の配線43の下面からシリコン基板32の裏面に達する高さに形成されている。基板側ビアプラグ68は、例えば、直径が約5μm以上に形成されている。

【0077】

シリコン基板32の下面には、基板側ビアプラグ68の下面に接続される表面配線66が形成され、表面配線66のパッド領域の上には、突起状電極の一種であるバンプ67が接合されている。バンプ67として、例えば、鉛、スズ、ニッケル、金、銀、銅等、又はそれらの合金などの金属が使用される。

【0078】

そのような構造の第2の半導体装置71のバンプ67と第1の半導体装置1の電極パッド25を接続する際には次の方法による。

【0079】

まず、第1の半導体装置1の上面の全体にスペーサ絶縁膜28として例えばエポキシ、ポリイミド等の有機樹脂を約200nmの厚さに塗布する。スペーサ絶縁膜28には、電極パッド25を露出する開口を形成する。これにより、第1の半導体装置1と第2の半導体装置71の間に空孔が発生することが防止される。

【0080】

続いて、バンプ67を電極パッド25の直上に位置させるために、第1の半導体装置1の上面と第2の半導体装置71の下面を対向させ、スペーサ絶縁膜28を介して合わせる。さらに、第2の半導体装置71から第1の半導体装置1に向けて相対的に荷重を加えると、図14に例示するように、バンプ67がスペーサ絶縁膜28を貫通し、続いて電極パッド25に接続する。

【0081】

これにより、バンプ67と電極パッド25は、電極パッド25の面方向と厚さ方向に接合する。この場合、加熱の処理をせずに良好な接続が得られる。なお、加熱処理してもよい。

【0082】

また、バンプ67が電極パッド25にめり込む際に、少なくともバンプ67が変形して電極パッド25の開口部25a内に入り込む。これにより、バンプ67と電極パッド25の位置合わせがわずかにずれても、電極パッド25とバンプ67の接合の水平強度を高めることができる。さらに、バンプ67の体積に形成誤差が生じても、バンプ67が開口部25a、内部空間21a内に入り込むので、電極パッド25の上面での広がりやはみ出し

、或いは接合不足を解消することができる。

【0083】

(第3の実施の形態)

図15は、第3実施形態に係る電子デバイスに含まれる第1、第2の半導体装置を互いに接続する前の状態の一例を示す断面図である。図15において、図1と同一符号は同一要素を示している。

【0084】

図15において、第1の半導体装置1は第1実施形態に示したと同じ構造を有し、また、第2の半導体装置72は、第1実施形態に示す第2の半導体装置31と外部端子を除いてほぼ同じ構造を有している。ただし、第2の半導体装置72は、図1とは上下の向きが反対になる状態に記載されている。

【0085】

第2の半導体装置72の第5、第6の配線54、55及び第4層間絶縁膜51の上には、第5層間絶縁膜74として例えば炭化酸化シリコン膜がCVD法により形成されている。また、第5層間絶縁膜74内には、第6の配線55に接続されるビアプラグ75が形成されている。ビアプラグ75は、例えばチタン、窒化チタンのバリアメタル膜上にタングステン膜が形成される構造を有している。

【0086】

第5層間絶縁膜74の上には、ビアプラグ75上面に接続されるアルミニウムの最上配線76が形成されている。また、最上配線76及び第5層間絶縁膜74の上にはカバー保護膜56としてシリコン窒化膜がCVD法により形成されている。また、カバー保護膜56のうちビアプラグ75の上方には、最上配線76の一部に重なる開口が形成されている。最上配線76上にはカバー保護膜56の開口を通してバンプ77が接合されている。バンプ77として、例えば、鉛、スズ、ニッケル、金、銀、銅等の金属が使用される。

【0087】

そのような構造の第2の半導体装置72のバンプ77と第1の半導体装置1の電極パッド25を接続する際には次の方法による。

【0088】

まず、第1の半導体装置1の上面の全体にスペーサ絶縁膜28として例えばエポキシ、ポリイミド等の有機樹脂を約200nmの厚さに塗布する。これにより、第1の半導体装置1と第2の半導体装置72の間に空孔が発生することが防止される。さらにスペーサ絶縁膜28には、電極パッド25を露出する開口部を形成する。

【0089】

続いて、バンプ77を電極パッド25の直上に位置させた状態で、第1の半導体装置1の上面と第2の半導体装置72の上面を対向させ。さらに、第2の半導体装置72から第1の半導体装置1の方向に相対的に荷重を加えると、図16に例示するように、バンプ77がスペーサ絶縁膜28を貫通し、続いて電極パッド25に接続する。

【0090】

これにより、バンプ77と電極パッド25は、電極パッド25の面方向と厚さ方向に接合する。この場合、加熱の処理をせずに良好な接続が得られる。なお、加熱処理してもよい。

【0091】

また、バンプ77が電極パッド25にめり込む際に、少なくともバンプ77が変形して電極パッド25の開口部25a内に入り込む。これにより、バンプ77と電極パッド25の位置合わせがわずかにずれても、電極パッド25とバンプ77の接合の水平強度を高めることができる。さらに、バンプ77の体積に形成誤差が生じても、バンプ77が開口部25a、内部空間21a内に入り込むので、電極パッド25の上面での広がりやはみ出し、或いは接合不足を解消することができる。

【0092】

(第4の実施の形態)

図17(a)は、第4実施形態に係る電子デバイスに使用される半導体装置の電極パッド及びその周辺の一例を示す平面図、図17(b)は、第4実施形態に係る電子デバイスに使用される第1の半導体装置の一例であって図17(a)のI−I線に沿う断面図である。図17(a)、(b)において、図1と同じ符号は同じ要素を示している。

【0093】

図17(a)、(b)に示す第4層間絶縁膜21内において、電極パッド25の周囲には間隔をおいて平面形状が環状のガード溝21hが形成され、さらに、ガード溝21h内にはダマシン構造のガードリングパターン69が形成されている。なお、環状の金属膜であるカードリング69は、電極パッドの周囲に間隔をおいて幾重にも横方向に広がる多重位置に形成されてもよい。

【0094】

ガード溝21hは、第1実施形態の説明で例示した図8における配線溝21gと同時に形成される。さらに、ガード溝21h内には、図9、図10に例示するバリアメタル層63と主導体層64が埋め込まれ、それらの層63、64はCMPにより残されてガードリングパターン69となる。

【0095】

以上のように、ガードリングパターン69を電極パッド25の周囲に設けることにより、第1の半導体装置1と上記実施形態の第2の半導体装置31、71、72を接続するために、電極パッド25に接続用突起58又はバンプ67、77を押圧する。その際、電極パッド25に加わる応力により第4層間絶縁膜21にクラックが発生したとしても、クラックの拡散はガードリングパターン69により防止される。従って、第1の半導体装置1の損傷を防止できる。

【0096】

(第5の実施の形態)

図18は、第5実施形態に係る電子デバイスに使用される半導体装置の一例を示す断面図である。なお、図18において、図1と同じ符号は同じ要素を示している。

【0097】

シリコン基板2の上方の第4層間絶縁膜21内には、第1実施形態と同様に、デュアルダマシン構造を有する第3のビアプラグ22及び第5の配線23と、デュアルダマシン構造を有する第4のビアプラグ24及び電極パッド25が形成されている。

【0098】

第5、第6の配線23、25及び第4層間絶縁膜21の上には、第3の金属用バリア絶縁膜80と第5層間絶縁膜81が順にPCVD法により形成されている。第3の金属バリア用絶縁膜80として例えばシリコン窒化膜を形成し、第5層間絶縁膜81としてシリコン酸化膜が形成される。

【0099】

第5層間絶縁膜81内の下部には第3の金属用バリア絶縁層80を貫通して第5の配線23に達する複数の第5のビアプラグ82が形成され、さらに第5層間絶縁膜81内の上部には第5のビアプラグ82に接続される第6の配線83が形成されている。第5のビアプラグ82は、電極パッド25の下のビアプラグ24に重なる位置に形成されている。第5のビアプラグ82と第6の配線83は、第3のビアプラグ22及び第5の配線23と同様に、デュアルダマシン構造を有している。

【0100】

また、第5層間絶縁膜81内の下部には第3の金属用バリア絶縁層80を貫通して電極パッド25に達する第6のビアプラグ84が形成され、さらに第5層間絶縁膜81内の上部には第6のビアプラグ84に接続される上側電極パッド85が形成されている。第6のビアプラグ84と上側電極パッド85は、図2に例示する第4のビアプラグ24及び電極パッド25と同様に、デュアルダマシン構造を有している。

【0101】

さらに、上側電極パッド85のうち複数の第6のビアプラグ84に挟まれる領域の上に

は上下方向に貫通する開口部85aが形成されている。さらに、電極パッド25の上であって第6のビアプラグ84の周囲には、上側電極パッド85の開口部85aに繋がる格子状の内部空間81aが形成されている。なお、上側電極パッド85の周辺にも第4実施形態に記載のガードリングを形成してもよい。

【0102】

以上のような本実施形態における第1の半導体装置1においては、電極パッド25の上に同一構造又は類似構造の上側電極パッド85を重ねて形成している。これにより、電極パッド25及び上側電極パッド85の開口部25a、85a及び内部空間81a、21aによって電極パッド領域の空間が広くなるので、上記実施形態の接続用突起58又はバンプ67、77を受け入れる容量が多くなる。

【0103】

また、第1〜第4実施形態と同様に、接続用突起58等と上側電極パッド85を接合する際に、僅かなズレが生じても開口部25a、85a内に接続用突起58等を入り込ませることができ、水平方向の接合強度が高まる。さらに、バンプ67、77又は接続用突起58の突出量が多くても内部空間21a、81a内に入り込ませることにより側方へのはみ出しを防止することができる。

【0104】

ところで、上記の各実施形態では、第1の半導体装置1に接続するデバイスとして第2の半導体装置31、71、72について説明したが、プリント基板に突起電極を設けたプリント基板を電極パッド25、85に接合させてもよい。また、上記の各実施形態における電極パッド25、85の開口部25a、85aは少なくとも1つあればよい。

【0105】

ここで挙げた全ての例および条件的表現は、発明者が技術促進に貢献した発明および概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例および条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神および範囲から逸脱することなく、それに対して種々の変更、置換および変形を施すことができると理解される。

【0106】

次に、実施形態を付記する。

(付記1)半導体基板の上方に形成される第1絶縁膜と、前記第1絶縁膜内に形成される導電パターンと、前記第1絶縁膜上に形成される第2絶縁膜と、前記第2絶縁膜内に形成され、前記導電パターンに接続されるビアプラグと、前記ビアプラグの上に接続され、開口部を有する電極パッドと、前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、を有する半導体装置。

(付記2)前記ビアプラグと前記電極パッドは一体に形成されている付記1に記載の半導体装置。

(付記3)前記電極パッドの周囲に間隔をおいて形成されるガードリングを有する付記1又は2に記載の半導体装置。

(付記4)前記電極パッドと前記導電パターンの間に形成され、開口部を有する下側の電極パッドを含む付記1乃至付記3のいずれか1つに記載の半導体装置。

(付記5)第1基板の上方に形成される第1絶縁膜と、前記第1絶縁膜内に形成される導電パターンと、前記第1絶縁膜の上方に形成され、前記導電パターンに電気的に接続され、開口部を有する電極パッドと、第2基板の上方と下方のいずれかに形成され、前記電極パッドの上面と前記開口部内に接合される突起状電極と、を有する電子デバイス。

(付記6)前記第1絶縁膜上に形成される第2絶縁膜と、前記第2絶縁膜内に形成され、前記電極パッドの下面側と前記導電パターンに接続されるビアプラグと、前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、を有する付記5に記載の電子デバイス。

(付記7)前記突起状電極が前記内部空間内に入り込む構造を有する付記6に記載の電子

デバイス。

(付記8)前記突起状電極はバンプである付記5乃至付記7のいずれか1つに記載の電子デバイス。

(付記9)第1基板の上方に形成され、開口部を有する電極パッドを、第2基板の上方と下方のいずれかに形成された突起状電極に対向させる工程と、前記第1基板と前記第2基板を互いに近づく方向に押圧し、前記突起状電極を前記電極パッドに接合させる工程と、を有する電子デバイスの製造方法。

【符号の説明】

【0107】

1 半導体装置

2 シリコン基板

5 n型MOSトランジスタ

8、9 コンタクトプラグ

7、11、15、21 層間絶縁膜

21a 内部空間

14、20 金属バリア絶縁膜

12、13、18、19、23 配線

16、17、22、24 ビアプラグ

25 電極パッド

25a 開口部

31 半導体装置

32 シリコン基板

35 n型MOSトランジスタ

38、39 コンタクトプラグ

37、41、45、51、81 層間絶縁膜

44、50、80 金属バリア絶縁膜

42、43、48、49、54、55、83 配線

46、47、52、53、82、84 ビアプラグ

58、85 突起状電極

67、77 バンプ

69 ガードリングパターン

【特許請求の範囲】

【請求項1】

半導体基板の上方に形成される第1絶縁膜と、

前記第1絶縁膜内に形成される導電パターンと、

前記第1絶縁膜上に形成される第2絶縁膜と、

前記第2絶縁膜内に形成され、前記導電パターンに接続されるビアプラグと、

前記ビアプラグの上に接続され、開口部を有する電極パッドと、

前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、

を有する半導体装置。

【請求項2】

第1基板の上方に形成される第1絶縁膜と、

前記第1絶縁膜内に形成される導電パターンと、

前記第1絶縁膜の上方に形成され、前記導電パターンに電気的に接続され、開口部を有する電極パッドと、

第2基板の上方と下方のいずれかに形成され、前記電極パッドの上面と前記開口部内に接合される突起状電極と、

を有する電子デバイス。

【請求項3】

前記第1絶縁膜上に形成される第2絶縁膜と、

前記第2絶縁膜内に形成され、前記電極パッドの下面側と前記導電パターンに接続されるビアプラグと、

前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、

を有する請求項2に記載の電子デバイス。

【請求項4】

第1基板の上方に形成され、開口部を有する電極パッドを、第2基板の上方と下方のいずれかに形成された突起状電極に対向させる工程と、

前記第1基板と前記第2基板を互いに近づく方向に押圧し、前記突起状電極を前記電極パッドに接合させる工程と、

を有する電子デバイスの製造方法。

【請求項1】

半導体基板の上方に形成される第1絶縁膜と、

前記第1絶縁膜内に形成される導電パターンと、

前記第1絶縁膜上に形成される第2絶縁膜と、

前記第2絶縁膜内に形成され、前記導電パターンに接続されるビアプラグと、

前記ビアプラグの上に接続され、開口部を有する電極パッドと、

前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、

を有する半導体装置。

【請求項2】

第1基板の上方に形成される第1絶縁膜と、

前記第1絶縁膜内に形成される導電パターンと、

前記第1絶縁膜の上方に形成され、前記導電パターンに電気的に接続され、開口部を有する電極パッドと、

第2基板の上方と下方のいずれかに形成され、前記電極パッドの上面と前記開口部内に接合される突起状電極と、

を有する電子デバイス。

【請求項3】

前記第1絶縁膜上に形成される第2絶縁膜と、

前記第2絶縁膜内に形成され、前記電極パッドの下面側と前記導電パターンに接続されるビアプラグと、

前記第2絶縁膜内で前記ビアプラグの周辺に形成される内部空間と、

を有する請求項2に記載の電子デバイス。

【請求項4】

第1基板の上方に形成され、開口部を有する電極パッドを、第2基板の上方と下方のいずれかに形成された突起状電極に対向させる工程と、

前記第1基板と前記第2基板を互いに近づく方向に押圧し、前記突起状電極を前記電極パッドに接合させる工程と、

を有する電子デバイスの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−190961(P2012−190961A)

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願番号】特願2011−52535(P2011−52535)

【出願日】平成23年3月10日(2011.3.10)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年10月4日(2012.10.4)

【国際特許分類】

【出願日】平成23年3月10日(2011.3.10)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]