半導体装置およびその作製法

【課題】チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、窒化物半導体を用いた導体装置およびその作製法を提供すること。

【解決手段】ソース電極1にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側へテロ接合構造、および、ドレイン電極3にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるドレイン側へテロ接合構造が形成され、それぞれのへテロ接合構造が、InN系チャネル層半導体(#)と接し、それぞれのへテロ接合構造において、ヘテロ接合界面近傍のみに伝導電子が局在し、ヘテロ接合界面の垂直方向位置が、InN系チャネル層半導体(#)の層内位置に存在することを特徴とする半導体装置を構成する。

【解決手段】ソース電極1にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側へテロ接合構造、および、ドレイン電極3にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるドレイン側へテロ接合構造が形成され、それぞれのへテロ接合構造が、InN系チャネル層半導体(#)と接し、それぞれのへテロ接合構造において、ヘテロ接合界面近傍のみに伝導電子が局在し、ヘテロ接合界面の垂直方向位置が、InN系チャネル層半導体(#)の層内位置に存在することを特徴とする半導体装置を構成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその作製法に関し、特に、高温・高出力・高耐圧の超高周波化合物半導体電界効果トランジスタとその作製法に関する。

【背景技術】

【0002】

窒化物半導体を用いた電界効果トランジスタ(Field Effect Transistor: FET)あるいはヘテロ構造FET(Heterostructure FET: HFET)は、次世代の高温・高出力・高耐圧の超高周波トランジスタとして非常に有望であり、実用化に向けて現在盛んに研究が行われている。しかし、現在行われているほとんどの研究開発は、チャネル層半導体としてGaN(あるいはGa組成の大きいAlGaN)を用いた、GaN系HFETに関するものであり(参考文献1)、チャネル層半導体として、GaNに比べて電子移動度および最大電子速度が高く、したがって、より高速動作が期待できる、InN系半導体(InN、および、一般にIn組成の大きいInGaN、InAlN、あるいはInAlGaN)を用いた、InN系FETあるいはHFETに関しての研究はほとんど報告されておらず、現在、トランジスタ動作の実現や特性の実証がまさにこれからの研究課題となっている。

【0003】

InN系FETあるいはHFETが、理論的にはGaN系FETあるいはHFETを凌ぐ高速動作が期待されながら(参考文献2)、その作製やトランジスタ動作がほとんど報告されていない理由のひとつは、InN結晶には一般に高濃度の残留背景電子(〜1018 cm-3)が存在するため(参考文献3)、トランジスタ動作に必須となるピンチオフ特性(ゲートに正電圧を印加することによってドレイン電流をゼロにする(ピンチオフ)ことができる特性)が得られないことである。この問題を解決するためには、残留背景電子濃度を低減することが直接的な方法であり、実際、このような目的で多くの研究がなされているが、今現在、問題が解決されるには至っていない。

【0004】

そこでこのような状況のもと、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、新しいトランジスタ構造を開発することによって、高性能のInN系FETあるいはHFETを実現することが強く望まれていた。

【0005】

なお、下記非特許文献1は、AlGaN/GaN HFETの実用化研究の報告(文献表題のHeterojunction FETはHFETに同じ)であり、非特許文献2は、InNの電子輸送特性に関する理論的検討の報告で、電子デバイス材料として、InNが、GaNを凌駕する、優れた電子輸送特性を有することを報告しており、非特許文献3は、InN結晶に高濃度の残留電子(〜1018 cm-3)が存在することを報告する文献である。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】Y. Okamoto et. al., Trans. on Microwave Theory and Tech. 52, 2536 (2004).

【非特許文献2】S. K. O’Leary et al., J. of Appl. Phys. 83, 826 (1998).

【非特許文献3】L. F. J. Piper et. al., Appl. Phys. Lett. 88, 252109 (2006).

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、上記の要望に鑑みてなされたものであり、本発明が解決しようとする課題は、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる半導体装置およびその作製法を提供することにある。

【課題を解決するための手段】

【0008】

本発明においては、上記課題を解決するために、請求項1に記載のように、

窒化物半導体を用いた電界効果トランジスタであり、ゲート電極の下方に存在するチャネル層半導体として、InN系半導体であるInN、InGaN、InAlNあるいはInAlGaNが用いられている半導体装置において、ソース電極にオーミック接触するオーミック領域障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側窒化物半導体へテロ接合構造、および、ドレイン電極にオーミック接触するオーミック領域障壁層半導体と前記オーミック領域チャネル層半導体とから形成されるドレイン側窒化物半導体へテロ接合構造が形成され、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とにおいて、それぞれ、ヘテロ接合界面近傍のみに伝導電子が局在し、前記ソース側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置と前記ドレイン側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置とが、前記チャネル層半導体の層内位置に存在することを特徴とする半導体装置を構成する。

【0009】

また、本発明においては、請求項2に記載のように、

請求項1に記載の半導体装置において、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、組成傾斜を設けた窒化物半導体層を介して前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記チャネル層半導体との間、および、前記ドレイン側窒化物半導体へテロ接合構造と前記チャネル層半導体との間に伝導帯不連続が生じていないことを特徴とする半導体装置を構成する。

【0010】

また、本発明においては、請求項3に記載のように、

請求項1に記載の半導体装置を作製する半導体装置の作製法であって、基板上に、ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造とを部分として含む積層構造をエピタキシャル結晶成長法により形成する成長工程と、該成長工程後に、チャネル層半導体を形成する位置にある前記積層構造の部分を、ドライ・エッチング法により削除するエッチング工程と、該エッチング工程後に、チャネル層半導体を、エピタキシャル結晶成長法により形成する再成長工程とを有することを特徴とする半導体装置の作製法を構成する。

【0011】

また、本発明においては、請求項4に記載のように、

請求項2に記載の半導体装置を作製する半導体装置の作製法であって、基板上に、ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造とを部分として含む積層構造をエピタキシャル結晶成長法により形成する成長工程と、該成長工程後に、チャネル層半導体および組成傾斜を設けた窒化物半導体層を形成する位置にある前記積層構造の部分を、ドライ・エッチング法により削除するエッチング工程と、該エッチング工程後に、組成傾斜を設けた窒化物半導体層およびチャネル層半導体を、エピタキシャル結晶成長法により形成する再成長工程とを有することを特徴とする半導体装置の作製法を構成する。

【発明の効果】

【0012】

本発明に係る半導体装置、その作製法においては、ソース側窒化物半導体へテロ接合構造と、ドレイン側窒化物半導体へテロ接合構造とによってInN系チャネル層半導体を挟み、両へテロ接合構造において、それぞれ、ヘテロ接合界面近傍のみに伝導電子が局在し、テロ接合界面の垂直方向位置が、前記チャネル層半導体の層内位置に存在するようにし、それによって、InN系FETあるいはHFETにおいて、InN系半導体チャネル層において高濃度の残留背景電子が存在する場合にも、ピンチオフ特性が得られる、高性能のInN系FETあるいはHFETを実現することが可能となる。

【0013】

また、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、組成傾斜を設けた窒化物半導体層を介して前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記チャネル層半導体との間、および、前記ドレイン側窒化物半導体へテロ接合構造と前記チャネル層半導体との間に伝導帯不連続が生じていないようにすることによって、FET動作時の電気抵抗が低減され、素子特性が高性能化される。

【図面の簡単な説明】

【0014】

【図1】窒化物半導体を用いたFETの模式図である。

【図2】図1に示される窒化物半導体を用いたFETにおいて、ゲート電極とチャネル半導体との間に絶縁膜(絶縁ゲート膜)の挿入されているMIS構造FETの模式図である。

【図3】図2に示されるMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図4】残留背景電子濃度の高いInN系窒化物半導体をチャネル層半導体として用いた、MIS構造FETの基本的な構造を模式的に示す図である。

【図5】図4に示されるInN系チャネル層半導体を用いたMIS構造FETにおいて、ピンチオフ動作を得るために、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

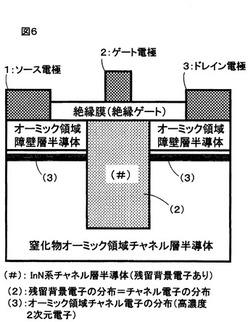

【図6】本発明による、InN系チャネル層半導体を用いたMIS構造FETの層構造を模式的に示す図である。

【図7】図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図8】図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETを改良した、本発明による改良型のMIS構造FETを模式的に示す図である。

【図9】図8に示される、本発明による改良型の、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図10】実施例3における、InN系チャネル層半導体を用いたFETを示す図である。

【図11】実施例4における、InN系チャネル層半導体を用いたFETを示す図である。

【図12】実施例5における、InN系チャネル層半導体を用いたFETを示す図である。

【図13】本実施例5のInN系MIS構造HFETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図14】実施例6における、InN系チャネル層半導体を用いたFETを示す図である。

【図15】実施例7における、InN系チャネル層半導体を用いたFETを示す図である。

【図16】実施例8における、InN系チャネル層半導体を用いたFETを示す図である。

【発明を実施するための形態】

【0015】

本発明によれば、チャネル層半導体として用いられるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、本発明によるトランジスタ構造の作用を、図1から図9を用いて説明する。また、本発明によるトランジスタ構造の作製法を説明する。

【0016】

本発明による作用を説明するためのトランジスタ構造として、ここでは、窒化物半導体を用いた電界効果トランジスタ(Field Effect Transistor: FET)において、ゲート電極とチャネル半導体との間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS: Metal-Insulator-Semiconductor))のFET(MIS構造FET)を用いる。その理由は、(i) MIS構造が一般にゲート耐圧が高く、高いゲート電圧の印加が可能であり、したがって、ピンチオフ動作を得るのに有利であること、また、(ii) ヘテロ構造を有するヘテロ構造電界効果トランジスタ(Heterostructure Field Effect Transistor: HFET)に比べて、窒化物半導体のヘテロ構造を有しないFETは、より単純な構造ゆえに一般性があること、であるが、本発明によるトランジスタ構造の作用は、MIS構造でないFET、MIS構造でないHFET、およびMIS構造のHFET、においても全く同様である。詳細は実施例で示す。

【0017】

図1は、窒化物半導体を用いたFETの模式図で、窒化物チャネル層半導体、ソース電極1、ゲート電極2、ドレイン電極3の構成が示されており、同時に、チャネル層半導体の表面近傍の、典型的には層厚10-200 nmの領域(1)に、不純物ドーピングやイオン注入が施され、当該の層領域にチャネル電子が分布している様子が示されている。ここで、チャネル電子が分布している当該の層領域以外の領域は、背景残留電子の存在しない高抵抗の半導体層である。また、チャネル層半導体としては、典型的にはGaNが想定される。

【0018】

図2は、図1に示される窒化物半導体を用いたFETにおいて、ゲート電極2とチャネル半導体との間に絶縁膜(絶縁ゲート膜)の挿入されているMIS構造FETの模式図で、図1と同様のチャネル電子の分布の様子が示されている。図2の構造は、図1の構造に比べて、ゲートリーク電流が低減され、また、ゲート耐圧が増大された構造である。

【0019】

図2に示されるMIS構造FETにおいて、トランジスタ動作において必須のピンチオフ動作(正のゲート電圧を印加することによってドレイン電流をゼロにする(ピンチオフ)動作)について説明する。

【0020】

図3は、図2に示されるMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したもので、ゲート電極2下においては、ゲート電極2の負電位によって形成される電界によってチャネル電子が排除され、チャネル電子が存在しなくなる(すなわち電子濃度がゼロとなる)様子が示されている。したがって、図3の状況においては、ドレイン電圧を印加してもドレイン電流は流れない。これが、ピンチオフ動作が実現される状況である。

【0021】

このようにピンチオフ動作が実現されるのは、チャネル電子の分布幅(垂直方向のチャネル電子の分布厚)が小さく、チャネル電子の分布が、ゲートの電位によって形成される電界の作用が及ぶ、十分小さい領域に限られていることによるものである。

【0022】

次に、InN系半導体の代表であるInNの残留背景電子について述べる。InNが、現状の結晶成長技術において、他の窒化物半導体と大きく異なる点は、残留背景電子濃度が高く、不純物ドーピングを施さない場合においても、高抵抗のInN結晶が得られていない点である。すなわち、InNを、MBE法(MBE: Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE: Metal Organic Vapor Phase Epitaxy)等の結晶成長法によって成長する場合、成長初期の残留背景電子濃度は〜1019 cm-3以上と極めて高く、成長を続行してInN膜厚を増大するにしたがって残留背景電子濃度が徐々に低下するものの、膜厚0.2-0.3 μm程度のInNにおいては残留背景電子濃度は5×1018 cm-3以上、膜厚1 μm程度のInNにおいても1×1018 cm-3以上と残留背景電子濃度が高く、さらに、成長時間の観点からは実用性の乏しい10 μm程度以上の厚膜InNにおいても、電子デバイス応用には不適合な5×1017 cm-3以上の高濃度の残留背景電子が存在する(非特許文献3)。

【0023】

このように、InNは、100 nm以下の膜厚では〜1019 cm-3程度の極めて高濃度の残留背景電子が存在し、5×1018 cm-3程度の残留背景電子濃度を得るためにも、0.2-0.3 μm以上の膜厚の成長が必要であり、また、10 μm程度以上の厚膜InNにおいても、電子デバイス応用に適合する低い残留背景電子濃度が得られない、という、デバイス応用上不利な特徴を有する。一般に、InN系窒化物半導体、すなわち、InNにGa、Al、あるいはその両方が加わった、InGaN、InAlN、あるいはInAlGaNも、同様の特徴を持ち得る。

【0024】

図4は、上述の特徴を有する、すなわち、残留背景電子濃度の高いInN系窒化物半導体をチャネル層半導体として用いた、MIS構造FETの基本的な構造を模式的に示したもので、InN系チャネル層半導体、絶縁膜(絶縁ゲート膜)、ソース電極1、ゲート電極2、ドレイン電極3とともに、電極に電圧印加を行わない状態での電子分布が模式的に示されており、InN層全体に残留電子が存在する様子が示されている。(ただし、残留背景電子濃度の層厚方向の分布は、簡単のため図1においては表現されていない。)

図4に示されるInN系チャネル層半導体を用いたMIS構造FETにおいては、ピンチオフ動作が得られないことを説明する。

【0025】

図5は、図4に示されるInN系チャネル層半導体を用いたMIS構造FETにおいて、ピンチオフ動作を得るために、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したもので、ゲート電極2近傍において、ゲート電極2の負電位によって形成される電界によってチャネル電子が排除されて電子が空乏する領域は存在するものの、大きな負のゲート電圧の印加によって、その電子空乏領域がソース電極1あるいはドレイン電極3にまで達するような状況であっても、電子空乏領域の下には、残留背景電子がチャネル電子として存在している様子が示されている。したがって、図5の状況においては、ドレイン電圧を印加すればドレイン電流が流れ、ピンチオフ動作は得られない。これが、従来技術によるInN系チャネル層半導体を用いたMIS構造FETの動作である。

【0026】

図6は、本発明による、InN系チャネル層半導体を用いたMIS構造FETの層構造を模式的に示したもので、ゲート電極2の下方に存在するチャネル層半導体として、InN系半導体が用いられていると同時に、ソース電極1およびドレイン電極3が形成されているオーミック領域において、窒化物障壁層半導体(オーミック領域障壁層半導体)と窒化物チャネル層半導体(オーミック領域チャネル層半導体)とから構成される窒化物半導体へテロ構造(オーミック領域へテロ構造)が形成されており、当該のオーミック領域へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する様子が示されている。ここで、前記のオーミック領域へテロ構造は、オーミック領域チャネル層半導体として、オーミック領域障壁層半導体よりもバンドギャップの小さい窒化物半導体を用いることにより、形成することが可能である。典型的には、オーミック領域障壁層半導体としてAlGaN、オーミック領域チャネル層半導体としてGaNを用いることが可能である。また、図6においては、InN系チャネル層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、本発明において、前記の両半導体層の表面位置が一致している必要は全くない。また、図6においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。

【0027】

図7は、図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したものである。InN系チャネル層半導体の領域においては、ゲート電極2の負電位によって形成される電界によってチャネル電子が排除される結果、電子が空乏する領域が存在し、その下方には、残留背景電子がチャネル電子として存在するが、一方、オーミック領域へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する様子が示されている。ここで、前記の当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在するため、InN系チャネル層半導体の領域に存在するチャネル電子(残留背景電子)と、オーミック領域チャネル電子(高濃度2次元電子)とは、電気的に接触していない。したがって、図7の状況においては、ドレイン電圧を印加してもドレイン電流は流れない。すなわち、図6に示される本発明により、ピンチオフ動作が実現される。このようにして、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる。

【0028】

図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETは、下記の方法により作製することが可能である。すなわち、(i)オーミック領域へテロ構造の層構造を、MBE法あるいはMOVPE法などの結晶成長法によって、結晶成長基板の全領域に成長し、その後、(ii) InN系チャネル層半導体を形成する領域に存在する、オーミック領域障壁層半導体、およびオーミック領域チャネル層半導体の一部を、ドライエッチング法等の通常のエッチング法によって所定の深さまで削除し、その後、(iii) InN系チャネル層半導体を形成する領域に、MBE法あるいはMOVPE法などの結晶成長法によって、選択的に、InN系チャネル層半導体を再成長し、その後、(iv) MIS構造FETの通常の作製プロセスによって、図6に示されるMIS構造FETを作製することが可能である。

【0029】

図8は、図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETを改良した、本発明による改良型のMIS構造FETを模式的に示したもので、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)が挿入されている様子が示されている。

【0030】

図8には、当該の窒化物組成傾斜半導体層の、InN系チャネル層半導体近傍の領域においても、残留背景電子が存在している様子も示されている。今、典型的な構造として、InN系チャネル層半導体としてInN、オーミック領域障壁層半導体としてAlGaN、オーミック領域チャネル層半導体としてGaNを用いた場合に、窒化物組成傾斜半導体層としてInxGa1-xN(0≦x≦1)を用いて、In組成xを、オーミック領域チャネル層半導体であるGaN側のx=0からInN系チャネル層半導体であるInN側のx=1まで連続的に変化させることにより、図8の構造が得られる。

【0031】

図8においては、InN系チャネル層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、本発明において、前記の両半導体層の表面位置が一致している必要は全くない。また、図8においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。

【0032】

図8に示される、本発明による改良型の、InN系チャネル層半導体を用いたMIS構造FETの改良点を以下に記す。図6に示される構造においては、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に一般に存在する、伝導帯不連続が、FETの動作時、すなわち、ドレイン電流が流れる際に、前記の両半導体層間でのチャネル電子輸送においてエネルギー障壁となり、これが、FET動作にとって不利な、電気抵抗の要因になる。しかし、図8に示される、本発明による改良型の構造においては、窒化物組成傾斜半導体層によって当該の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。

【0033】

図9は、図8に示される、本発明による改良型の、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したものである。図9に示されている状況は、図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示した、図7に示されている状況と全く同様であり、したがって、図9の状況においても、ドレイン電圧を印加してもドレイン電流は流れない。すなわち、図8に示される本発明においても、ピンチオフ動作が実現される。また同時に、図8に示される、本発明による改良型の構造においては、前述の説明のように、窒化物組成傾斜半導体層によって当該の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。

【0034】

図8に示される、本発明による改良型の、InN系チャネル層半導体を用いたMIS構造FETの作製は、図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETの作製方法に準じた、下記の方法により行うことが可能である。すなわち、(i)オーミック領域へテロ構造の層構造を、MBE法あるいはMOVPE法などの結晶成長法によって、結晶成長基板の全領域に成長し、その後、(ii) 窒化物組成傾斜半導体層およびInN系チャネル層半導体を形成する領域に存在する、オーミック領域障壁層半導体、およびオーミック領域チャネル層半導体の一部を、ドライエッチング法等の通常のエッチング法によって所定の深さまで削除し、その後、(iii) 窒化物組成傾斜半導体層およびInN系チャネル層半導体を形成する領域に、MBE法あるいはMOVPE法などの結晶成長法によって、選択的に、窒化物組成傾斜半導体層およびInN系チャネル層半導体を再成長し、その後、(iv) MIS構造FETの通常の作製プロセスによって、図8に示されるMIS構造FETを作製することが可能である。ここで、上記(iii)の窒化物組成傾斜半導体層の再成長においては、結晶成長条件の制御によって、通常の縦方向成長と同時に、横方向成長も実現することが可能であり、したがって、図8に示されている、横方向の層構造を有する、窒化物組成傾斜半導体層の層構造を形成することが可能である。

【0035】

以上で、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、本発明によるトランジスタ構造の作用が、その作製法とともに、すべて示された。

【0036】

窒化物半導体を用いた電界効果トランジスタ(Field Effect Transistor: FET)あるいはヘテロ構造電界効果トランジスタ(Heterostructure Field Effect Transistor: HFET)において、ゲート電極の下方に存在するチャネル層半導体として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系FETあるいはHFETにおいて、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、InN系FETあるいはHFETが実現される。

【実施例1】

【0037】

図6に示される、InN系チャネル層半導体を用いたMIS構造FET。すわなち、ゲート電極2の下方に存在するチャネル層半導体として、InN系半導体(図中、(#)で示す)が用いられていると同時に、ソース電極1およびドレイン電極3が形成されているオーミック領域において、オーミック領域障壁層半導体と窒化物オーミック領域チャネル層半導体とから構成される窒化物半導体へテロ構造(ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造)が形成されており、当該の窒化物半導体へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する構造。

【0038】

すなわち、この構造において、ソース電極1にオーミック接触するオーミック領域障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側窒化物半導体へテロ接合構造、および、ドレイン電極3にオーミック接触するオーミック領域障壁層半導体と前記オーミック領域チャネル層半導体とから形成されるドレイン側窒化物半導体へテロ接合構造が形成され、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とにおいて、それぞれ、ヘテロ接合界面近傍のみに伝導電子が局在し、前記ソース側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置と前記ドレイン側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置とが、前記チャネル層半導体の層内位置に存在している。

【0039】

図6においては、InN系チャネル層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、前記の両半導体層の表面位置が一致している必要は全くない。また、図6においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。

【0040】

本実施例1の具体的な構造は、上記の特徴を有する図6において、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-x22N(0≦xM2<xM1≦1.0)が用いられている構造である。図6における絶縁膜(絶縁ゲート)としては、SiO2、Si3N4、AlN、Al2O3、ZrO2、HfO2、その他、いかなる絶縁膜を用いることも可能である。

【0041】

本実施例として、下記の構造を有するMIS構造FETを、下記の製造方法によって作製した。

【0042】

まず、オーミック領域チャネル層半導体としてGaN、オーミック領域障壁層半導体として層厚15 nmのAl0.3Ga0.7Nを用いたAl0.3Ga0.7N/GaNヘテロ構造を、MBE法あるいはMOVPE法等の結晶成長法によってサファイア基板上の全領域に成長した(成長工程)。

【0043】

次に、図6におけるInN系チャネル層半導体の領域において、すなわち、オーミック領域以外の全領域において、オーミック領域障壁層半導体である層厚15 nmのAl0.3Ga0.7N、およびその下方の層厚200 nmのGaNをドライエッチング法等の通常の半導体エッチング法により削除した(エッチング工程)。

【0044】

その後、この領域に、MBE法あるいはMOVPE法などの結晶成長法によって、選択的に、InN系チャネル層半導体として層厚215 nmのInNを再成長した(再成長工程)。ここで、選択的な再成長は、SiO2等の絶縁膜を選択成長マスクとして用いる等の方法により可能である。その後、絶縁ゲート膜として層厚10 nmのSi3N4を用いたMIS構造FETを、通常のMIS構造FETの作製プロセスにより作製した。このようにして作製した、InN系チャネル層半導体を用いたMIS構造FETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。

【0045】

ここで、本実施例のMIS構造FETが、サファイア基板上の他、SiC(シリコンカーバイド)基板上あるいはSi(シリコン)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、図6に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0046】

また、本実施例においては、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)が用いられているが、InN系チャネル層半導体としてInNやInGaNの他、InxAl1-xN(0<x≦1.0)、あるいはInxAlYGa1-x-YN(0<x≦1、0≦Y≦1)が用いられている場合も、図6に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0047】

また、本実施例においては、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-xM2N(0≦Mx2<xM1≦1.0)が用いられているが、オーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、InxAl1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、オーミック領域障壁層半導体のバンドギャップがオーミック領域チャネル層半導体のそれよりも大きい、という条件のもとで、AlN/AlGaN、AlGaN/AlGaN、AlGaN/GaNの他、AlGaN/InN、AlGaN/InGaN、InAlN/InN、InAlN/InGaN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなオーミック領域へテロ構造を構成することが可能であり、当該へテロ構造のオーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてこれらの半導体が用いられている場合も、図6に示される本発明による特徴を有する限り、すべて本発明の範囲内である。

【実施例2】

【0048】

図8に示される、InN系チャネル層半導体を用いたMIS構造FET。本実施例2は、実施例1の改良型である。すわなち、ゲート電極2の下方に存在するチャネル層半導体として、InN系半導体が用いられていると同時に、ソース電極1およびドレイン電極3が形成されているオーミック領域において、オーミック領域障壁層半導体とオーミック領域チャネル層半導体とから構成される窒化物半導体へテロ構造(ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造)が形成されており、当該の窒化物半導体へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する構造において、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)が挿入されている構造である。すなわち、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、組成傾斜を設けた窒化物半導体層を介して前記チャネル層半導体と接している構造である。

【0049】

図8においては、InN系チャネル層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、本発明において、前記の両半導体層の表面位置が一致している必要は全くない。また、図8においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。図8には、当該の窒化物組成傾斜半導体層の、InN系チャネル層半導体近傍の領域においても、残留背景電子が存在している様子も示されている。

【0050】

本実施例2の、実施例1と比較した場合の改良点を以下に記す。図6に示される実施例1の構造においては、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に一般に存在する、伝導帯不連続が、FETの動作時、すなわち、ドレイン電流が流れる際に、前記の両半導体層間でのチャネル電子輸送においてエネルギー障壁となり、これが、FET動作にとって不利な、電気抵抗の要因になる。しかし、図8に示される本実施例2の構造においては、窒化物組成傾斜半導体層によって当該の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。本実施例2を実施例1と比較すると、本実施例2は層構造がより複雑になるために、実施例1に比べてより高度な結晶成長技術が必要とされるという、不利な点が存在するものの、実施例1に比べて素子特性が高性能化されるという、有利な点を有する。

【0051】

本実施例2の具体的な構造は、上記の特徴を有する図8において、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-x22N(0≦xM2<xM1≦1.0)が用いられており、かつ、InN系チャネル層半導体InxCGa1-xCN(0<xC≦1.0)と、オーミック領域チャネル層半導体AlxM1Ga1-xM1N(0<xM1≦1.0)との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)InxAlYGa1-x-YN(xおよびYは層内で連続的に変化、0≦x≦1、0≦Y≦1)が挿入されている構造である。図8における絶縁膜(絶縁ゲート)としては、SiO2、Si3N4、AlN、Al2O3、ZrO2、HfO2、その他、いかなる絶縁膜を用いることも可能である。

【0052】

本実施例として、下記の構造を有するMIS構造FETを、下記の製造方法によって作製した。

【0053】

まず、オーミック領域チャネル層半導体としてGaN、オーミック領域障壁層半導体として層厚15 nmのAl0.3Ga0.7Nを用いたAl0.3Ga0.7N/GaNヘテロ構造を、MBE法あるいはMOVPE法等の結晶成長法によってサファイア基板上の全領域に成長した(成長工程)。

【0054】

次に、図8における窒化物組成傾斜半導体層およびInN系チャネル層半導体の領域において、すなわち、オーミック領域以外の全領域において、オーミック領域障壁層半導体である層厚15 nmのAl0.3Ga0.7N、およびその下方の層厚200 nmのGaNをドライエッチング法等の通常の半導体エッチング法により削除した(エッチング工程)。

【0055】

その後、この領域に、縦方向層厚10 nmの組成傾斜InGaNを、初期In組成0、最終In組成1.0なる線形変化の組成傾斜InGaN層として、MBE法あるいはMOVPE法等の結晶成長法により再成長を行った。この際の結晶成長条件においては、当該の組成傾斜InGaN層の横方向層厚は5 nmであった。前記の組成傾斜InGaN層の再成長に引き続き、InN系チャネル層半導体として層厚205 nmのInNを再成長した(再成長工程)。ここで、選択的な再成長は、SiO2等の絶縁膜を選択成長マスクとして用いる等の方法により可能である。その後、絶縁ゲート膜として層厚10 nmのSi3N4を用いたMIS構造FETを、通常のMIS構造FETの作製プロセスにより作製した。このようにして作製した、InN系チャネル層半導体を用いたMIS構造FETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、本実施例2のドレイン電流が、実施例1のドレイン電流の約1.5倍になることが確認された。

【0056】

ここで、本実施例のMIS構造FETが、サファイア基板上の他、SiC(シリコンカーバイド)基板上あるいはSi(シリコン)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、図8に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0057】

また、本実施例においては、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)が用いられているが、InN系チャネル層半導体としてInNやInGaNの他、InxAl1-xN(0<x≦1.0)、あるいはInxAlYGa1-x-YN(0<x≦1、0≦Y≦1)が用いられている場合も、図8に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0058】

また、本実施例においては、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-xM2N(0≦Mx2<xM1≦1.0)が用いられているが、オーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、InxAl1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、オーミック領域障壁層半導体のバンドギャップがオーミック領域チャネル層半導体のそれよりも大きい、という条件のもとで、AlN/AlGaN、AlGaN/AlGaN、AlGaN/GaNの他、AlGaN/InN、AlGaN/InGaN、InAlN/InN、InAlN/InGaN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなオーミック領域へテロ構造を構成することが可能であり、当該へテロ構造のオーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてこれらの半導体が用いられている場合も、図8に示される本発明による特徴を有する限り、すべて本発明の範囲内である。この際には、図8における組成傾斜半導体層としてInxAlYGa1-x-YN(xおよびYは層内で連続的に変化、0≦x≦1、0≦Y≦1)を用いることにより、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、伝導帯不連続が生じないように、組成傾斜を設けることが可能である。

【実施例3】

【0059】

図10に示される、InN系チャネル層半導体を用いたFET。本実施例3は、図6に示される実施例1において、ゲート絶縁膜が用いられていない、すなわち、MIS構造ではない、通常のFETである。図10には、図6と同様に、チャネル電子の分布の様子が示されている。本実施例3のFETは、実施例1のMIS構造FETに比べて、ゲートリーク電流が大きく、また、ゲート耐圧が小さい、という不利な点を有するが、一方、ゲート絶縁膜を用いていないため、素子作製プロセスがより簡便であるという、有利な点を有する。

【0060】

本実施例3として、実施例1において絶縁ゲート膜を堆積せずに、ゲート電極2を形成したFETを、すわなち、ゲート絶縁膜が用いられていないという点以外は実施例1と全く同じ構造のFETを、実施例1と全く同様の作製方法によって作製した。このようにして作製した、InN系チャネル層半導体を用いたFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、実施例1と比べると、ゲートリーク電流が増大し、ゲート耐圧も低減したものの、より簡便な素子作製プロセスにより、高性能のInN系FETが実現されることが確認された。

【0061】

本実施例3は、ゲート絶縁膜が用いられていないという点以外は、実施例1と全く同様であるため、本実施例3における、結晶成長基板、構成される半導体層、および、その他に関する請求範囲は、実施例1に準ずるものとする。

【実施例4】

【0062】

図11に示される、InN系チャネル層半導体を用いたFET。本実施例4は、図8に示される実施例2において、ゲート絶縁膜が用いられていない、すなわち、MIS構造ではない、通常のFETである。図11には、図8と同様に、チャネル電子の分布の様子が示されている。本実施例4のFETは、実施例2のMIS構造FETに比べて、ゲートリーク電流が大きく、また、ゲート耐圧が小さい、という不利な点を有するが、一方、ゲート絶縁膜を用いていないため、素子作製プロセスがより簡便であるという、有利な点を有する。また、本実施例4のFETを、実施例3のFETと比較すると、実施例2の実施例1に対する比較と全く同様に、窒化物組成傾斜半導体層の設置によって、InN系チャネル層半導体とオーミック領域チャネル層半導体との間の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。このように、本実施例4は層構造がより複雑になるために、実施例3に比べて作製により手間がかかるという不利な点が存在するものの、実施例1に比べて素子特性が高性能化されるという、有利な点を有する。

【0063】

本実施例4として、実施例2において絶縁ゲート膜を堆積せずに、ゲート電極2を形成したFETを、すわなち、ゲート絶縁膜が用いられていないという点以外は実施例2と全く同じ構造のFETを、実施例2と全く同様の作製方法によって作製した。このようにして作製した、InN系チャネル層半導体を用いたFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、実施例2と比べると、ゲートリーク電流が増大し、ゲート耐圧も低減したものの、より簡便な素子作製プロセスにより、高性能のInN系FETが実現されることが確認された。

【0064】

本実施例4は、ゲート絶縁膜が用いられていないという点以外は、実施例2と全く同様であるため、本実施例2における、結晶成長基板、組成傾斜層その他の構成される半導体層、および、その他に関する請求範囲は、実施例2に準ずるものとする。

【実施例5】

【0065】

図12に示される、ゲート電極2の形成されるチャネル領域において、窒化物障壁層半導体(チャネル領域障壁層半導体(#1))およびInN系チャネル層半導体とから構成される、InN系チャネル層半導体へテロ構造を用いた、InN系MIS構造へテロ構造FET(HFET)において、チャネル領域障壁層半導体およびInN系チャネル層半導体とから構成される、InN系チャネル層半導体へテロ構造を用いた、InN系MIS構造へテロ構造FET(HFET)において、ソース電極1およびドレイン電極3が形成されているオーミック領域において、窒化物障壁層半導体(オーミック領域障壁層半導体)と窒化物チャネル層半導体(オーミック領域チャネル層半導体)とから構成される窒化物半導体へテロ構造(オーミック領域へテロ構造)が形成されており、当該のオーミック領域へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、オーミック領域ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する、すわなち、チャネル領域へテロ界面の垂直位置よりも下方(同位置を含む)に存在する構造。図12に示される本実施例5の構造は、図6に示される実施例1の構造において、チャネル領域において、単層のInN系チャネル層半導体が用いられている、InN系FETではなく、チャネル領域障壁層半導体とInN系チャネル層半導体とから構成される、InN系チャネル層半導体へテロ構造が用いられている、InN系MIS構造へテロ構造FET(HFET)である。チャネル領域へテロ構造のInN系チャネル層半導体においては、図12に模式的に示されているように、InNの背景残留電子に加えて、当該へテロ界面の近傍には、高濃度の伝導電子(チャネル領域チャネル電子(高濃度2次元電子))が存在する。

【0066】

図13は、図12に示される本実施例5のInN系MIS構造HFETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したもので、図7に示される実施例1のInN系MIS構造FETにおける、対応する状況におけるチャネル電子の分布の様子と全く同様の状況が実現される様子が示されており、したがって、図12に示される本実施例5のInN系MIS構造HFETにおいて、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となることが模式的に示されている。

【0067】

本実施例が示されている図12においては、チャネル領域障壁層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、前記の両半導体層の表面位置が一致している必要は全くない。また、図12においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。

【0068】

本実施例5を、実施例1と比較した場合、本実施例5においては、チャネル領域においてヘテロ構造を形成する必要があり、したがって、より高度な結晶成長技術が必要とされるという、不利な点が存在するものの、チャネル領域へテロ構造におけるチャネル領域チャネル電子(高濃度2次元電子)の存在によって、チャネル抵抗が低減し、その結果、実施例1に比べて素子特性が高性能化される、という有利な点を有する。

【0069】

本実施例5の具体的な構造は、上記の特徴を有する図12において、チャネル領域障壁層半導体としてInxAl1-xN(0≦x<1.0)、InN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)(バンドギャップはInxAl1-xN(0≦x<1.0)のそれよりも小さいとする)、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-x22N(0≦xM2<xM1≦1.0)が用いられている構造である。図12における絶縁膜(絶縁ゲート)としては、SiO2、Si3N4、AlN、Al2O3、ZrO2、HfO2、その他、いかなる絶縁膜を用いることも可能である。

【0070】

本実施例として、下記の構造を有するMIS構造HFETを、下記の製造方法によって作製した。まず、オーミック領域チャネル層半導体としてGaN、オーミック領域障壁層半導体として層厚15 nmのAl0.3Ga0.7Nを用いたAl0.3Ga0.7N/GaNヘテロ構造を、MBE法あるいはMOVPE法等の結晶成長法によってサファイア基板上の全領域に成長した。次に、図12におけるInN系チャネル層半導体の領域において、すなわち、オーミック領域以外の全領域において、オーミック領域障壁層半導体である層厚15 nmのAl0.3Ga0.7N、およびその下方の層厚200 nmのGaNをドライエッチング法等の通常の半導体エッチング法により削除し、その後、この領域に、MBE法あるいはMOVPE法などの結晶成長法によって、選択的に、InN系チャネル層半導体として層厚205 nmのInN、および、チャネル領域障壁層半導体として層厚10 nmのInl0.2Al0.8Nを、再成長した。ここで、選択的な再成長は、SiO2等の絶縁膜を選択成長マスクとして用いる等の方法により可能である。その後、絶縁ゲート膜として層厚10 nmのSi3N4を用いたMIS構造FETを、通常のMIS構造FETの作製プロセスにより作製した。このようにして作製した、InN系チャネル層半導体を用いたMIS構造FETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、本実施例5のドレイン電流が、実施例1のドレイン電流の約2倍になることが確認された。

【0071】

ここで、本実施例のMIS構造FETが、サファイア基板上の他、SiC(シリコンカーバイド)基板上あるいはSi(シリコン)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、図12に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0072】

また、本実施例においては、チャネル領域障壁層半導体としてInxAl1-xN(0≦x<1.0)、InN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)(バンドギャップはInxAl1-xN(0≦x<1.0)のそれよりも小さいとする)が用いられているが、チャネル領域障壁層半導体およびチャネル領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、チャネル領域障壁層半導体のバンドギャップがチャネル領域チャネル層半導体のそれよりも大きい、という条件のもとで、InAlN/InGaN、InAlN/InN、AlN/InGaNの他、AlGaN/InN、AlGaN/InGaN、InGaN/InN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなチャネル領域へテロ構造を構成することが可能であり、当該へテロ構造のチャネル領域障壁層半導体およびチャネル領域チャネル層半導体としてこれらの半導体が用いられている場合も、図12に示される本発明による特徴を有する限り、すべて本発明の範囲内である。

【実施例6】

【0073】

図14に示される、InN系チャネル層半導体を用いたMIS構造HFET。本実施例6は、実施例5の改良型である。すわなち、ゲート電極2の形成されているチャネル領域において、窒化物障壁層半導体(チャネル領域障壁層半導体)およびInN系チャネル層半導体とから構成される、InN系チャネル層半導体へテロ構造が形成されていると同時に、ソース電極1およびドレイン電極3が形成されているオーミック領域において、窒化物障壁層半導体(オーミック領域障壁層半導体)と窒化物チャネル層半導体(オーミック領域チャネル層半導体)とから構成される窒化物半導体へテロ構造(オーミック領域へテロ構造)が形成されており、当該のオーミック領域へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する構造において、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)が挿入されている構造である。

【0074】

図12においては、チャネル領域障壁層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、本発明において、前記の両半導体層の表面位置が一致している必要は全くない。また、図12においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。図12には、当該の窒化物組成傾斜半導体層の、InN系チャネル層半導体近傍の領域においても、残留背景電子が存在している様子も示されている。

【0075】

本実施例6の、実施例5と比較した場合の改良点は、実施例2の、実施例1と比較した場合の改良点と全く同じである。すわなち、図12に示される実施例5の構造においては、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に一般に存在する、伝導帯不連続が、FETの動作時、すなわち、ドレイン電流が流れる際に、前記の両半導体層間でのチャネル電子輸送においてエネルギー障壁となり、これが、FET動作にとって不利な、電気抵抗の要因になる。しかし、図14に示される本実施例6の構造においては、窒化物組成傾斜半導体層によって当該の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。本実施例6を実施例5と比較すると、本実施例6は層構造がより複雑になるために、実施例5に比べてより高度な結晶成長技術が必要とされるという、不利な点が存在するものの、実施例5に比べて素子特性が高性能化されるという、有利な点を有する。

【0076】

本実施例6の具体的な構造は、上記の特徴を有する図14において、チャネル領域障壁層半導体としてInxAl1-xN(0≦x<1.0)、InN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)(バンドギャップはInxAl1-xN(0≦x<1.0)のそれよりも小さいとする)、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-x22N(0≦xM2<xM1≦1.0)が用いられており、かつ、InN系チャネル層半導体InxCGa1-xCN(0<xC≦1.0)と、オーミック領域チャネル層半導体AlxM1Ga1-xM1N(0<xM1≦1.0)との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)InxAlYGa1-x-YN(xおよびYは層内で連続的に変化、0≦x≦1、0≦Y≦1)が挿入されている構造である。図8における絶縁膜(絶縁ゲート)としては、SiO2、Si3N4、AlN、Al2O3、ZrO2、HfO2、その他、いかなる絶縁膜を用いることも可能である。

【0077】

本実施例として、下記の構造を有するMIS構造HFETを、下記の製造方法によって作製した。まず、オーミック領域チャネル層半導体としてGaN、オーミック領域障壁層半導体として層厚15 nmのAl0.3Ga0.7Nを用いたAl0.3Ga0.7N/GaNヘテロ構造を、MBE法あるいはMOVPE法等の結晶成長法によってサファイア基板上の全領域に成長した。次に、図8における窒化物組成傾斜半導体層およびInN系チャネル層半導体の領域において、すなわち、オーミック領域以外の全領域において、オーミック領域障壁層半導体である層厚15 nmのAl0.3Ga0.7N、およびその下方の層厚200 nmのGaNをドライエッチング法等の通常の半導体エッチング法により削除した。その後、この領域に、縦方向層厚10 nmの組成傾斜InGaNを、初期In組成0、最終In組成1.0なる線形変化の組成傾斜InGaN層として、MBE法あるいはMOVPE法等の結晶成長法により再成長を行った。この際の結晶成長条件においては、当該の組成傾斜InGaN層の横方向層厚は5 nmであった。前記の組成傾斜InGaN層の再成長に引き続き、InN系チャネル層半導体として層厚205 nmのInN、および、チャネル領域障壁層半導体として層厚10 nmのInl0.2Al0.8Nを、再成長した。ここで、選択的な再成長は、SiO2等の絶縁膜を選択成長マスクとして用いる等の方法により可能である。その後、絶縁ゲート膜として層厚10 nmのSi3N4を用いたMIS構造HFETを、通常のMIS構造HFETの作製プロセスにより作製した。このようにして作製した、InN系チャネル層半導体を用いたMIS構造HFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、本実施例6のドレイン電流が、実施例5のドレイン電流の約1.5倍になることが確認された。

【0078】

ここで、本実施例のMIS構造HFETが、サファイア基板上の他、SiC(シリコンカーバイド)基板上あるいはSi(シリコン)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、図8に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0079】

また、本実施例においては、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)が用いられているが、InN系チャネル層半導体としてInNやInGaNの他、InxAl1-xN(0<x≦1.0)、あるいはInxAlYGa1-x-YN(0<x≦1、0≦Y≦1)が用いられている場合も、図8に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0080】

また、本実施例においては、チャネル領域障壁層半導体としてInxAl1-xN(0≦x<1.0)、InN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)(バンドギャップはInxAl1-xN(0≦x<1.0)のそれよりも小さいとする)が用いられているが、チャネル領域障壁層半導体およびチャネル領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、チャネル領域障壁層半導体のバンドギャップがチャネル領域チャネル層半導体のそれよりも大きい、という条件のもとで、InAlN/InGaN、InAlN/InN、AlN/InGaNの他、AlGaN/InN、AlGaN/InGaN、InGaN/InN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなチャネル領域へテロ構造を構成することが可能であり、当該へテロ構造のチャネル領域障壁層半導体およびチャネル領域チャネル層半導体としてこれらの半導体が用いられている場合も、図14に示される本発明による特徴を有する限り、すべて本発明の範囲内である。

【0081】

また、本実施例においては、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-xM2N(0≦Mx2<xM1≦1.0)が用いられているが、オーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、InxAl1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、オーミック領域障壁層半導体のバンドギャップがオーミック領域チャネル層半導体のそれよりも大きい、という条件のもとで、AlN/AlGaN、AlGaN/AlGaN、AlGaN/GaNの他、AlGaN/InN、AlGaN/InGaN、InAlN/InN、InAlN/InGaN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなオーミック領域へテロ構造を構成することが可能であり、当該へテロ構造のオーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてこれらの半導体が用いられている場合も、図14に示される本発明による特徴を有する限り、すべて本発明の範囲内である。この際には、図14における組成傾斜半導体層としてInxAlYGa1-x-YN(xおよびYは層内で連続的に変化、0≦x≦1、0≦Y≦1)を用いることにより、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、伝導帯不連続が生じないように、組成傾斜を設けることが可能である。

【実施例7】

【0082】

図15に示される、InN系チャネル層半導体を用いたHFET。本実施例7は、図12に示される実施例5において、ゲート絶縁膜が用いられていない、すなわち、MIS構造ではない、通常のHFETである。図15には、図12と同様に、チャネル電子の分布の様子が示されている。本実施例7のHFETは、実施例5のMIS構造HFETに比べて、ゲートリーク電流が大きく、また、ゲート耐圧が小さい、という不利な点を有するが、一方、ゲート絶縁膜を用いていないため、素子作製プロセスがより簡便であるという、有利な点を有する。

【0083】

本実施例7として、実施例5において絶縁ゲート膜を堆積せずに、ゲート電極2を形成したFETを、すわなち、ゲート絶縁膜が用いられていないという点以外は実施例5と全く同じ構造のHFETを、実施例5と全く同様の作製方法によって作製した。このようにして作製した、InN系チャネル層半導体を用いたHFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系HFETが実現された。また、実施例5と比べると、ゲートリーク電流が増大し、ゲート耐圧も低減したものの、より簡便な素子作製プロセスにより、高性能のInN系HFETが実現されることが確認された。

【0084】

本実施例7は、ゲート絶縁膜が用いられていないという点以外は、実施例5と全く同様であるため、本実施例5における、結晶成長基板、構成される半導体層、および、その他に関する請求範囲は、実施例5に準ずるものとする。

【実施例8】

【0085】

図16に示される、InN系チャネル層半導体を用いたHFET。本実施例8は、図14に示される実施例6において、ゲート絶縁膜が用いられていない、すなわち、MIS構造ではない、通常のHFETである。図11には、図8と同様に、チャネル電子の分布の様子が示されている。本実施例8のFETは、実施例6のMIS構造HFETに比べて、ゲートリーク電流が大きく、また、ゲート耐圧が小さい、という不利な点を有するが、一方、ゲート絶縁膜を用いていないため、素子作製プロセスがより簡便であるという、有利な点を有する。また、本実施例8のHFETを、実施例7のHFETと比較すると、実施例6の実施例5に対する比較と全く同様に、窒化物組成傾斜半導体層の設置によって、InN系チャネル層半導体とオーミック領域チャネル層半導体との間の伝導帯不連続が解消されるため、HFET動作時の電気抵抗が低減され、素子特性が高性能化される。このように、本実施例8は層構造がより複雑になるために、実施例7に比べて作製により手間がかかるという不利な点が存在するものの、実施例7に比べて素子特性が高性能化されるという、有利な点を有する。

【0086】

本実施例8として、実施例6において絶縁ゲート膜を堆積せずに、ゲート電極2を形成したHFETを、すわなち、ゲート絶縁膜が用いられていないという点以外は実施例6と全く同じ構造のHFETを、実施例6と全く同様の作製方法によって作製した。このようにして作製した、InN系チャネル層半導体を用いたHFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、実施例6と比べると、ゲートリーク電流が増大し、ゲート耐圧も低減したものの、より簡便な素子作製プロセスにより、高性能のInN系FETが実現されることが確認された。

【0087】

本実施例8は、ゲート絶縁膜が用いられていないという点以外は、実施例6と全く同様であるため、本実施例6における、結晶成長基板、組成傾斜層その他の構成される半導体層、および、その他に関する請求範囲は、実施例6に準ずるものとする。

【符号の説明】

【0088】

1:ソース電極、2:ゲート電極、3:ドレイン電極。

【技術分野】

【0001】

本発明は、半導体装置およびその作製法に関し、特に、高温・高出力・高耐圧の超高周波化合物半導体電界効果トランジスタとその作製法に関する。

【背景技術】

【0002】

窒化物半導体を用いた電界効果トランジスタ(Field Effect Transistor: FET)あるいはヘテロ構造FET(Heterostructure FET: HFET)は、次世代の高温・高出力・高耐圧の超高周波トランジスタとして非常に有望であり、実用化に向けて現在盛んに研究が行われている。しかし、現在行われているほとんどの研究開発は、チャネル層半導体としてGaN(あるいはGa組成の大きいAlGaN)を用いた、GaN系HFETに関するものであり(参考文献1)、チャネル層半導体として、GaNに比べて電子移動度および最大電子速度が高く、したがって、より高速動作が期待できる、InN系半導体(InN、および、一般にIn組成の大きいInGaN、InAlN、あるいはInAlGaN)を用いた、InN系FETあるいはHFETに関しての研究はほとんど報告されておらず、現在、トランジスタ動作の実現や特性の実証がまさにこれからの研究課題となっている。

【0003】

InN系FETあるいはHFETが、理論的にはGaN系FETあるいはHFETを凌ぐ高速動作が期待されながら(参考文献2)、その作製やトランジスタ動作がほとんど報告されていない理由のひとつは、InN結晶には一般に高濃度の残留背景電子(〜1018 cm-3)が存在するため(参考文献3)、トランジスタ動作に必須となるピンチオフ特性(ゲートに正電圧を印加することによってドレイン電流をゼロにする(ピンチオフ)ことができる特性)が得られないことである。この問題を解決するためには、残留背景電子濃度を低減することが直接的な方法であり、実際、このような目的で多くの研究がなされているが、今現在、問題が解決されるには至っていない。

【0004】

そこでこのような状況のもと、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、新しいトランジスタ構造を開発することによって、高性能のInN系FETあるいはHFETを実現することが強く望まれていた。

【0005】

なお、下記非特許文献1は、AlGaN/GaN HFETの実用化研究の報告(文献表題のHeterojunction FETはHFETに同じ)であり、非特許文献2は、InNの電子輸送特性に関する理論的検討の報告で、電子デバイス材料として、InNが、GaNを凌駕する、優れた電子輸送特性を有することを報告しており、非特許文献3は、InN結晶に高濃度の残留電子(〜1018 cm-3)が存在することを報告する文献である。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】Y. Okamoto et. al., Trans. on Microwave Theory and Tech. 52, 2536 (2004).

【非特許文献2】S. K. O’Leary et al., J. of Appl. Phys. 83, 826 (1998).

【非特許文献3】L. F. J. Piper et. al., Appl. Phys. Lett. 88, 252109 (2006).

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、上記の要望に鑑みてなされたものであり、本発明が解決しようとする課題は、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる半導体装置およびその作製法を提供することにある。

【課題を解決するための手段】

【0008】

本発明においては、上記課題を解決するために、請求項1に記載のように、

窒化物半導体を用いた電界効果トランジスタであり、ゲート電極の下方に存在するチャネル層半導体として、InN系半導体であるInN、InGaN、InAlNあるいはInAlGaNが用いられている半導体装置において、ソース電極にオーミック接触するオーミック領域障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側窒化物半導体へテロ接合構造、および、ドレイン電極にオーミック接触するオーミック領域障壁層半導体と前記オーミック領域チャネル層半導体とから形成されるドレイン側窒化物半導体へテロ接合構造が形成され、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とにおいて、それぞれ、ヘテロ接合界面近傍のみに伝導電子が局在し、前記ソース側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置と前記ドレイン側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置とが、前記チャネル層半導体の層内位置に存在することを特徴とする半導体装置を構成する。

【0009】

また、本発明においては、請求項2に記載のように、

請求項1に記載の半導体装置において、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、組成傾斜を設けた窒化物半導体層を介して前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記チャネル層半導体との間、および、前記ドレイン側窒化物半導体へテロ接合構造と前記チャネル層半導体との間に伝導帯不連続が生じていないことを特徴とする半導体装置を構成する。

【0010】

また、本発明においては、請求項3に記載のように、

請求項1に記載の半導体装置を作製する半導体装置の作製法であって、基板上に、ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造とを部分として含む積層構造をエピタキシャル結晶成長法により形成する成長工程と、該成長工程後に、チャネル層半導体を形成する位置にある前記積層構造の部分を、ドライ・エッチング法により削除するエッチング工程と、該エッチング工程後に、チャネル層半導体を、エピタキシャル結晶成長法により形成する再成長工程とを有することを特徴とする半導体装置の作製法を構成する。

【0011】

また、本発明においては、請求項4に記載のように、

請求項2に記載の半導体装置を作製する半導体装置の作製法であって、基板上に、ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造とを部分として含む積層構造をエピタキシャル結晶成長法により形成する成長工程と、該成長工程後に、チャネル層半導体および組成傾斜を設けた窒化物半導体層を形成する位置にある前記積層構造の部分を、ドライ・エッチング法により削除するエッチング工程と、該エッチング工程後に、組成傾斜を設けた窒化物半導体層およびチャネル層半導体を、エピタキシャル結晶成長法により形成する再成長工程とを有することを特徴とする半導体装置の作製法を構成する。

【発明の効果】

【0012】

本発明に係る半導体装置、その作製法においては、ソース側窒化物半導体へテロ接合構造と、ドレイン側窒化物半導体へテロ接合構造とによってInN系チャネル層半導体を挟み、両へテロ接合構造において、それぞれ、ヘテロ接合界面近傍のみに伝導電子が局在し、テロ接合界面の垂直方向位置が、前記チャネル層半導体の層内位置に存在するようにし、それによって、InN系FETあるいはHFETにおいて、InN系半導体チャネル層において高濃度の残留背景電子が存在する場合にも、ピンチオフ特性が得られる、高性能のInN系FETあるいはHFETを実現することが可能となる。

【0013】

また、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、組成傾斜を設けた窒化物半導体層を介して前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記チャネル層半導体との間、および、前記ドレイン側窒化物半導体へテロ接合構造と前記チャネル層半導体との間に伝導帯不連続が生じていないようにすることによって、FET動作時の電気抵抗が低減され、素子特性が高性能化される。

【図面の簡単な説明】

【0014】

【図1】窒化物半導体を用いたFETの模式図である。

【図2】図1に示される窒化物半導体を用いたFETにおいて、ゲート電極とチャネル半導体との間に絶縁膜(絶縁ゲート膜)の挿入されているMIS構造FETの模式図である。

【図3】図2に示されるMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図4】残留背景電子濃度の高いInN系窒化物半導体をチャネル層半導体として用いた、MIS構造FETの基本的な構造を模式的に示す図である。

【図5】図4に示されるInN系チャネル層半導体を用いたMIS構造FETにおいて、ピンチオフ動作を得るために、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図6】本発明による、InN系チャネル層半導体を用いたMIS構造FETの層構造を模式的に示す図である。

【図7】図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図8】図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETを改良した、本発明による改良型のMIS構造FETを模式的に示す図である。

【図9】図8に示される、本発明による改良型の、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図10】実施例3における、InN系チャネル層半導体を用いたFETを示す図である。

【図11】実施例4における、InN系チャネル層半導体を用いたFETを示す図である。

【図12】実施例5における、InN系チャネル層半導体を用いたFETを示す図である。

【図13】本実施例5のInN系MIS構造HFETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示す図である。

【図14】実施例6における、InN系チャネル層半導体を用いたFETを示す図である。

【図15】実施例7における、InN系チャネル層半導体を用いたFETを示す図である。

【図16】実施例8における、InN系チャネル層半導体を用いたFETを示す図である。

【発明を実施するための形態】

【0015】

本発明によれば、チャネル層半導体として用いられるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、本発明によるトランジスタ構造の作用を、図1から図9を用いて説明する。また、本発明によるトランジスタ構造の作製法を説明する。

【0016】

本発明による作用を説明するためのトランジスタ構造として、ここでは、窒化物半導体を用いた電界効果トランジスタ(Field Effect Transistor: FET)において、ゲート電極とチャネル半導体との間に絶縁膜が挿入されている、いわゆる絶縁ゲート構造(すなわちMIS構造(MIS: Metal-Insulator-Semiconductor))のFET(MIS構造FET)を用いる。その理由は、(i) MIS構造が一般にゲート耐圧が高く、高いゲート電圧の印加が可能であり、したがって、ピンチオフ動作を得るのに有利であること、また、(ii) ヘテロ構造を有するヘテロ構造電界効果トランジスタ(Heterostructure Field Effect Transistor: HFET)に比べて、窒化物半導体のヘテロ構造を有しないFETは、より単純な構造ゆえに一般性があること、であるが、本発明によるトランジスタ構造の作用は、MIS構造でないFET、MIS構造でないHFET、およびMIS構造のHFET、においても全く同様である。詳細は実施例で示す。

【0017】

図1は、窒化物半導体を用いたFETの模式図で、窒化物チャネル層半導体、ソース電極1、ゲート電極2、ドレイン電極3の構成が示されており、同時に、チャネル層半導体の表面近傍の、典型的には層厚10-200 nmの領域(1)に、不純物ドーピングやイオン注入が施され、当該の層領域にチャネル電子が分布している様子が示されている。ここで、チャネル電子が分布している当該の層領域以外の領域は、背景残留電子の存在しない高抵抗の半導体層である。また、チャネル層半導体としては、典型的にはGaNが想定される。

【0018】

図2は、図1に示される窒化物半導体を用いたFETにおいて、ゲート電極2とチャネル半導体との間に絶縁膜(絶縁ゲート膜)の挿入されているMIS構造FETの模式図で、図1と同様のチャネル電子の分布の様子が示されている。図2の構造は、図1の構造に比べて、ゲートリーク電流が低減され、また、ゲート耐圧が増大された構造である。

【0019】

図2に示されるMIS構造FETにおいて、トランジスタ動作において必須のピンチオフ動作(正のゲート電圧を印加することによってドレイン電流をゼロにする(ピンチオフ)動作)について説明する。

【0020】

図3は、図2に示されるMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したもので、ゲート電極2下においては、ゲート電極2の負電位によって形成される電界によってチャネル電子が排除され、チャネル電子が存在しなくなる(すなわち電子濃度がゼロとなる)様子が示されている。したがって、図3の状況においては、ドレイン電圧を印加してもドレイン電流は流れない。これが、ピンチオフ動作が実現される状況である。

【0021】

このようにピンチオフ動作が実現されるのは、チャネル電子の分布幅(垂直方向のチャネル電子の分布厚)が小さく、チャネル電子の分布が、ゲートの電位によって形成される電界の作用が及ぶ、十分小さい領域に限られていることによるものである。

【0022】

次に、InN系半導体の代表であるInNの残留背景電子について述べる。InNが、現状の結晶成長技術において、他の窒化物半導体と大きく異なる点は、残留背景電子濃度が高く、不純物ドーピングを施さない場合においても、高抵抗のInN結晶が得られていない点である。すなわち、InNを、MBE法(MBE: Molecular Beam Epitaxy)あるいはMOVPE法(MOVPE: Metal Organic Vapor Phase Epitaxy)等の結晶成長法によって成長する場合、成長初期の残留背景電子濃度は〜1019 cm-3以上と極めて高く、成長を続行してInN膜厚を増大するにしたがって残留背景電子濃度が徐々に低下するものの、膜厚0.2-0.3 μm程度のInNにおいては残留背景電子濃度は5×1018 cm-3以上、膜厚1 μm程度のInNにおいても1×1018 cm-3以上と残留背景電子濃度が高く、さらに、成長時間の観点からは実用性の乏しい10 μm程度以上の厚膜InNにおいても、電子デバイス応用には不適合な5×1017 cm-3以上の高濃度の残留背景電子が存在する(非特許文献3)。

【0023】

このように、InNは、100 nm以下の膜厚では〜1019 cm-3程度の極めて高濃度の残留背景電子が存在し、5×1018 cm-3程度の残留背景電子濃度を得るためにも、0.2-0.3 μm以上の膜厚の成長が必要であり、また、10 μm程度以上の厚膜InNにおいても、電子デバイス応用に適合する低い残留背景電子濃度が得られない、という、デバイス応用上不利な特徴を有する。一般に、InN系窒化物半導体、すなわち、InNにGa、Al、あるいはその両方が加わった、InGaN、InAlN、あるいはInAlGaNも、同様の特徴を持ち得る。

【0024】

図4は、上述の特徴を有する、すなわち、残留背景電子濃度の高いInN系窒化物半導体をチャネル層半導体として用いた、MIS構造FETの基本的な構造を模式的に示したもので、InN系チャネル層半導体、絶縁膜(絶縁ゲート膜)、ソース電極1、ゲート電極2、ドレイン電極3とともに、電極に電圧印加を行わない状態での電子分布が模式的に示されており、InN層全体に残留電子が存在する様子が示されている。(ただし、残留背景電子濃度の層厚方向の分布は、簡単のため図1においては表現されていない。)

図4に示されるInN系チャネル層半導体を用いたMIS構造FETにおいては、ピンチオフ動作が得られないことを説明する。

【0025】

図5は、図4に示されるInN系チャネル層半導体を用いたMIS構造FETにおいて、ピンチオフ動作を得るために、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したもので、ゲート電極2近傍において、ゲート電極2の負電位によって形成される電界によってチャネル電子が排除されて電子が空乏する領域は存在するものの、大きな負のゲート電圧の印加によって、その電子空乏領域がソース電極1あるいはドレイン電極3にまで達するような状況であっても、電子空乏領域の下には、残留背景電子がチャネル電子として存在している様子が示されている。したがって、図5の状況においては、ドレイン電圧を印加すればドレイン電流が流れ、ピンチオフ動作は得られない。これが、従来技術によるInN系チャネル層半導体を用いたMIS構造FETの動作である。

【0026】

図6は、本発明による、InN系チャネル層半導体を用いたMIS構造FETの層構造を模式的に示したもので、ゲート電極2の下方に存在するチャネル層半導体として、InN系半導体が用いられていると同時に、ソース電極1およびドレイン電極3が形成されているオーミック領域において、窒化物障壁層半導体(オーミック領域障壁層半導体)と窒化物チャネル層半導体(オーミック領域チャネル層半導体)とから構成される窒化物半導体へテロ構造(オーミック領域へテロ構造)が形成されており、当該のオーミック領域へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する様子が示されている。ここで、前記のオーミック領域へテロ構造は、オーミック領域チャネル層半導体として、オーミック領域障壁層半導体よりもバンドギャップの小さい窒化物半導体を用いることにより、形成することが可能である。典型的には、オーミック領域障壁層半導体としてAlGaN、オーミック領域チャネル層半導体としてGaNを用いることが可能である。また、図6においては、InN系チャネル層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、本発明において、前記の両半導体層の表面位置が一致している必要は全くない。また、図6においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。

【0027】

図7は、図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したものである。InN系チャネル層半導体の領域においては、ゲート電極2の負電位によって形成される電界によってチャネル電子が排除される結果、電子が空乏する領域が存在し、その下方には、残留背景電子がチャネル電子として存在するが、一方、オーミック領域へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する様子が示されている。ここで、前記の当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在するため、InN系チャネル層半導体の領域に存在するチャネル電子(残留背景電子)と、オーミック領域チャネル電子(高濃度2次元電子)とは、電気的に接触していない。したがって、図7の状況においては、ドレイン電圧を印加してもドレイン電流は流れない。すなわち、図6に示される本発明により、ピンチオフ動作が実現される。このようにして、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる。

【0028】

図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETは、下記の方法により作製することが可能である。すなわち、(i)オーミック領域へテロ構造の層構造を、MBE法あるいはMOVPE法などの結晶成長法によって、結晶成長基板の全領域に成長し、その後、(ii) InN系チャネル層半導体を形成する領域に存在する、オーミック領域障壁層半導体、およびオーミック領域チャネル層半導体の一部を、ドライエッチング法等の通常のエッチング法によって所定の深さまで削除し、その後、(iii) InN系チャネル層半導体を形成する領域に、MBE法あるいはMOVPE法などの結晶成長法によって、選択的に、InN系チャネル層半導体を再成長し、その後、(iv) MIS構造FETの通常の作製プロセスによって、図6に示されるMIS構造FETを作製することが可能である。

【0029】

図8は、図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETを改良した、本発明による改良型のMIS構造FETを模式的に示したもので、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)が挿入されている様子が示されている。

【0030】

図8には、当該の窒化物組成傾斜半導体層の、InN系チャネル層半導体近傍の領域においても、残留背景電子が存在している様子も示されている。今、典型的な構造として、InN系チャネル層半導体としてInN、オーミック領域障壁層半導体としてAlGaN、オーミック領域チャネル層半導体としてGaNを用いた場合に、窒化物組成傾斜半導体層としてInxGa1-xN(0≦x≦1)を用いて、In組成xを、オーミック領域チャネル層半導体であるGaN側のx=0からInN系チャネル層半導体であるInN側のx=1まで連続的に変化させることにより、図8の構造が得られる。

【0031】

図8においては、InN系チャネル層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、本発明において、前記の両半導体層の表面位置が一致している必要は全くない。また、図8においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。

【0032】

図8に示される、本発明による改良型の、InN系チャネル層半導体を用いたMIS構造FETの改良点を以下に記す。図6に示される構造においては、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に一般に存在する、伝導帯不連続が、FETの動作時、すなわち、ドレイン電流が流れる際に、前記の両半導体層間でのチャネル電子輸送においてエネルギー障壁となり、これが、FET動作にとって不利な、電気抵抗の要因になる。しかし、図8に示される、本発明による改良型の構造においては、窒化物組成傾斜半導体層によって当該の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。

【0033】

図9は、図8に示される、本発明による改良型の、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したものである。図9に示されている状況は、図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示した、図7に示されている状況と全く同様であり、したがって、図9の状況においても、ドレイン電圧を印加してもドレイン電流は流れない。すなわち、図8に示される本発明においても、ピンチオフ動作が実現される。また同時に、図8に示される、本発明による改良型の構造においては、前述の説明のように、窒化物組成傾斜半導体層によって当該の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。

【0034】

図8に示される、本発明による改良型の、InN系チャネル層半導体を用いたMIS構造FETの作製は、図6に示される、本発明による、InN系チャネル層半導体を用いたMIS構造FETの作製方法に準じた、下記の方法により行うことが可能である。すなわち、(i)オーミック領域へテロ構造の層構造を、MBE法あるいはMOVPE法などの結晶成長法によって、結晶成長基板の全領域に成長し、その後、(ii) 窒化物組成傾斜半導体層およびInN系チャネル層半導体を形成する領域に存在する、オーミック領域障壁層半導体、およびオーミック領域チャネル層半導体の一部を、ドライエッチング法等の通常のエッチング法によって所定の深さまで削除し、その後、(iii) 窒化物組成傾斜半導体層およびInN系チャネル層半導体を形成する領域に、MBE法あるいはMOVPE法などの結晶成長法によって、選択的に、窒化物組成傾斜半導体層およびInN系チャネル層半導体を再成長し、その後、(iv) MIS構造FETの通常の作製プロセスによって、図8に示されるMIS構造FETを作製することが可能である。ここで、上記(iii)の窒化物組成傾斜半導体層の再成長においては、結晶成長条件の制御によって、通常の縦方向成長と同時に、横方向成長も実現することが可能であり、したがって、図8に示されている、横方向の層構造を有する、窒化物組成傾斜半導体層の層構造を形成することが可能である。

【0035】

以上で、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、本発明によるトランジスタ構造の作用が、その作製法とともに、すべて示された。

【0036】

窒化物半導体を用いた電界効果トランジスタ(Field Effect Transistor: FET)あるいはヘテロ構造電界効果トランジスタ(Heterostructure Field Effect Transistor: HFET)において、ゲート電極の下方に存在するチャネル層半導体として、InN系半導体であるInN、InGaN、InAlN、あるいはInAlGaNが用いられているInN系FETあるいはHFETにおいて、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、InN系FETあるいはHFETが実現される。

【実施例1】

【0037】

図6に示される、InN系チャネル層半導体を用いたMIS構造FET。すわなち、ゲート電極2の下方に存在するチャネル層半導体として、InN系半導体(図中、(#)で示す)が用いられていると同時に、ソース電極1およびドレイン電極3が形成されているオーミック領域において、オーミック領域障壁層半導体と窒化物オーミック領域チャネル層半導体とから構成される窒化物半導体へテロ構造(ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造)が形成されており、当該の窒化物半導体へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する構造。

【0038】

すなわち、この構造において、ソース電極1にオーミック接触するオーミック領域障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側窒化物半導体へテロ接合構造、および、ドレイン電極3にオーミック接触するオーミック領域障壁層半導体と前記オーミック領域チャネル層半導体とから形成されるドレイン側窒化物半導体へテロ接合構造が形成され、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とにおいて、それぞれ、ヘテロ接合界面近傍のみに伝導電子が局在し、前記ソース側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置と前記ドレイン側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置とが、前記チャネル層半導体の層内位置に存在している。

【0039】

図6においては、InN系チャネル層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、前記の両半導体層の表面位置が一致している必要は全くない。また、図6においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。

【0040】

本実施例1の具体的な構造は、上記の特徴を有する図6において、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-x22N(0≦xM2<xM1≦1.0)が用いられている構造である。図6における絶縁膜(絶縁ゲート)としては、SiO2、Si3N4、AlN、Al2O3、ZrO2、HfO2、その他、いかなる絶縁膜を用いることも可能である。

【0041】

本実施例として、下記の構造を有するMIS構造FETを、下記の製造方法によって作製した。

【0042】

まず、オーミック領域チャネル層半導体としてGaN、オーミック領域障壁層半導体として層厚15 nmのAl0.3Ga0.7Nを用いたAl0.3Ga0.7N/GaNヘテロ構造を、MBE法あるいはMOVPE法等の結晶成長法によってサファイア基板上の全領域に成長した(成長工程)。

【0043】

次に、図6におけるInN系チャネル層半導体の領域において、すなわち、オーミック領域以外の全領域において、オーミック領域障壁層半導体である層厚15 nmのAl0.3Ga0.7N、およびその下方の層厚200 nmのGaNをドライエッチング法等の通常の半導体エッチング法により削除した(エッチング工程)。

【0044】

その後、この領域に、MBE法あるいはMOVPE法などの結晶成長法によって、選択的に、InN系チャネル層半導体として層厚215 nmのInNを再成長した(再成長工程)。ここで、選択的な再成長は、SiO2等の絶縁膜を選択成長マスクとして用いる等の方法により可能である。その後、絶縁ゲート膜として層厚10 nmのSi3N4を用いたMIS構造FETを、通常のMIS構造FETの作製プロセスにより作製した。このようにして作製した、InN系チャネル層半導体を用いたMIS構造FETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。

【0045】

ここで、本実施例のMIS構造FETが、サファイア基板上の他、SiC(シリコンカーバイド)基板上あるいはSi(シリコン)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、図6に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0046】

また、本実施例においては、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)が用いられているが、InN系チャネル層半導体としてInNやInGaNの他、InxAl1-xN(0<x≦1.0)、あるいはInxAlYGa1-x-YN(0<x≦1、0≦Y≦1)が用いられている場合も、図6に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0047】

また、本実施例においては、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-xM2N(0≦Mx2<xM1≦1.0)が用いられているが、オーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、InxAl1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、オーミック領域障壁層半導体のバンドギャップがオーミック領域チャネル層半導体のそれよりも大きい、という条件のもとで、AlN/AlGaN、AlGaN/AlGaN、AlGaN/GaNの他、AlGaN/InN、AlGaN/InGaN、InAlN/InN、InAlN/InGaN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなオーミック領域へテロ構造を構成することが可能であり、当該へテロ構造のオーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてこれらの半導体が用いられている場合も、図6に示される本発明による特徴を有する限り、すべて本発明の範囲内である。

【実施例2】

【0048】

図8に示される、InN系チャネル層半導体を用いたMIS構造FET。本実施例2は、実施例1の改良型である。すわなち、ゲート電極2の下方に存在するチャネル層半導体として、InN系半導体が用いられていると同時に、ソース電極1およびドレイン電極3が形成されているオーミック領域において、オーミック領域障壁層半導体とオーミック領域チャネル層半導体とから構成される窒化物半導体へテロ構造(ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造)が形成されており、当該の窒化物半導体へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する構造において、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)が挿入されている構造である。すなわち、前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、組成傾斜を設けた窒化物半導体層を介して前記チャネル層半導体と接している構造である。

【0049】

図8においては、InN系チャネル層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、本発明において、前記の両半導体層の表面位置が一致している必要は全くない。また、図8においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。図8には、当該の窒化物組成傾斜半導体層の、InN系チャネル層半導体近傍の領域においても、残留背景電子が存在している様子も示されている。

【0050】

本実施例2の、実施例1と比較した場合の改良点を以下に記す。図6に示される実施例1の構造においては、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に一般に存在する、伝導帯不連続が、FETの動作時、すなわち、ドレイン電流が流れる際に、前記の両半導体層間でのチャネル電子輸送においてエネルギー障壁となり、これが、FET動作にとって不利な、電気抵抗の要因になる。しかし、図8に示される本実施例2の構造においては、窒化物組成傾斜半導体層によって当該の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。本実施例2を実施例1と比較すると、本実施例2は層構造がより複雑になるために、実施例1に比べてより高度な結晶成長技術が必要とされるという、不利な点が存在するものの、実施例1に比べて素子特性が高性能化されるという、有利な点を有する。

【0051】

本実施例2の具体的な構造は、上記の特徴を有する図8において、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-x22N(0≦xM2<xM1≦1.0)が用いられており、かつ、InN系チャネル層半導体InxCGa1-xCN(0<xC≦1.0)と、オーミック領域チャネル層半導体AlxM1Ga1-xM1N(0<xM1≦1.0)との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)InxAlYGa1-x-YN(xおよびYは層内で連続的に変化、0≦x≦1、0≦Y≦1)が挿入されている構造である。図8における絶縁膜(絶縁ゲート)としては、SiO2、Si3N4、AlN、Al2O3、ZrO2、HfO2、その他、いかなる絶縁膜を用いることも可能である。

【0052】

本実施例として、下記の構造を有するMIS構造FETを、下記の製造方法によって作製した。

【0053】

まず、オーミック領域チャネル層半導体としてGaN、オーミック領域障壁層半導体として層厚15 nmのAl0.3Ga0.7Nを用いたAl0.3Ga0.7N/GaNヘテロ構造を、MBE法あるいはMOVPE法等の結晶成長法によってサファイア基板上の全領域に成長した(成長工程)。

【0054】

次に、図8における窒化物組成傾斜半導体層およびInN系チャネル層半導体の領域において、すなわち、オーミック領域以外の全領域において、オーミック領域障壁層半導体である層厚15 nmのAl0.3Ga0.7N、およびその下方の層厚200 nmのGaNをドライエッチング法等の通常の半導体エッチング法により削除した(エッチング工程)。

【0055】

その後、この領域に、縦方向層厚10 nmの組成傾斜InGaNを、初期In組成0、最終In組成1.0なる線形変化の組成傾斜InGaN層として、MBE法あるいはMOVPE法等の結晶成長法により再成長を行った。この際の結晶成長条件においては、当該の組成傾斜InGaN層の横方向層厚は5 nmであった。前記の組成傾斜InGaN層の再成長に引き続き、InN系チャネル層半導体として層厚205 nmのInNを再成長した(再成長工程)。ここで、選択的な再成長は、SiO2等の絶縁膜を選択成長マスクとして用いる等の方法により可能である。その後、絶縁ゲート膜として層厚10 nmのSi3N4を用いたMIS構造FETを、通常のMIS構造FETの作製プロセスにより作製した。このようにして作製した、InN系チャネル層半導体を用いたMIS構造FETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、本実施例2のドレイン電流が、実施例1のドレイン電流の約1.5倍になることが確認された。

【0056】

ここで、本実施例のMIS構造FETが、サファイア基板上の他、SiC(シリコンカーバイド)基板上あるいはSi(シリコン)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、図8に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0057】

また、本実施例においては、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)が用いられているが、InN系チャネル層半導体としてInNやInGaNの他、InxAl1-xN(0<x≦1.0)、あるいはInxAlYGa1-x-YN(0<x≦1、0≦Y≦1)が用いられている場合も、図8に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0058】

また、本実施例においては、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-xM2N(0≦Mx2<xM1≦1.0)が用いられているが、オーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、InxAl1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、オーミック領域障壁層半導体のバンドギャップがオーミック領域チャネル層半導体のそれよりも大きい、という条件のもとで、AlN/AlGaN、AlGaN/AlGaN、AlGaN/GaNの他、AlGaN/InN、AlGaN/InGaN、InAlN/InN、InAlN/InGaN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなオーミック領域へテロ構造を構成することが可能であり、当該へテロ構造のオーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてこれらの半導体が用いられている場合も、図8に示される本発明による特徴を有する限り、すべて本発明の範囲内である。この際には、図8における組成傾斜半導体層としてInxAlYGa1-x-YN(xおよびYは層内で連続的に変化、0≦x≦1、0≦Y≦1)を用いることにより、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、伝導帯不連続が生じないように、組成傾斜を設けることが可能である。

【実施例3】

【0059】

図10に示される、InN系チャネル層半導体を用いたFET。本実施例3は、図6に示される実施例1において、ゲート絶縁膜が用いられていない、すなわち、MIS構造ではない、通常のFETである。図10には、図6と同様に、チャネル電子の分布の様子が示されている。本実施例3のFETは、実施例1のMIS構造FETに比べて、ゲートリーク電流が大きく、また、ゲート耐圧が小さい、という不利な点を有するが、一方、ゲート絶縁膜を用いていないため、素子作製プロセスがより簡便であるという、有利な点を有する。

【0060】

本実施例3として、実施例1において絶縁ゲート膜を堆積せずに、ゲート電極2を形成したFETを、すわなち、ゲート絶縁膜が用いられていないという点以外は実施例1と全く同じ構造のFETを、実施例1と全く同様の作製方法によって作製した。このようにして作製した、InN系チャネル層半導体を用いたFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、実施例1と比べると、ゲートリーク電流が増大し、ゲート耐圧も低減したものの、より簡便な素子作製プロセスにより、高性能のInN系FETが実現されることが確認された。

【0061】

本実施例3は、ゲート絶縁膜が用いられていないという点以外は、実施例1と全く同様であるため、本実施例3における、結晶成長基板、構成される半導体層、および、その他に関する請求範囲は、実施例1に準ずるものとする。

【実施例4】

【0062】

図11に示される、InN系チャネル層半導体を用いたFET。本実施例4は、図8に示される実施例2において、ゲート絶縁膜が用いられていない、すなわち、MIS構造ではない、通常のFETである。図11には、図8と同様に、チャネル電子の分布の様子が示されている。本実施例4のFETは、実施例2のMIS構造FETに比べて、ゲートリーク電流が大きく、また、ゲート耐圧が小さい、という不利な点を有するが、一方、ゲート絶縁膜を用いていないため、素子作製プロセスがより簡便であるという、有利な点を有する。また、本実施例4のFETを、実施例3のFETと比較すると、実施例2の実施例1に対する比較と全く同様に、窒化物組成傾斜半導体層の設置によって、InN系チャネル層半導体とオーミック領域チャネル層半導体との間の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。このように、本実施例4は層構造がより複雑になるために、実施例3に比べて作製により手間がかかるという不利な点が存在するものの、実施例1に比べて素子特性が高性能化されるという、有利な点を有する。

【0063】

本実施例4として、実施例2において絶縁ゲート膜を堆積せずに、ゲート電極2を形成したFETを、すわなち、ゲート絶縁膜が用いられていないという点以外は実施例2と全く同じ構造のFETを、実施例2と全く同様の作製方法によって作製した。このようにして作製した、InN系チャネル層半導体を用いたFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、実施例2と比べると、ゲートリーク電流が増大し、ゲート耐圧も低減したものの、より簡便な素子作製プロセスにより、高性能のInN系FETが実現されることが確認された。

【0064】

本実施例4は、ゲート絶縁膜が用いられていないという点以外は、実施例2と全く同様であるため、本実施例2における、結晶成長基板、組成傾斜層その他の構成される半導体層、および、その他に関する請求範囲は、実施例2に準ずるものとする。

【実施例5】

【0065】

図12に示される、ゲート電極2の形成されるチャネル領域において、窒化物障壁層半導体(チャネル領域障壁層半導体(#1))およびInN系チャネル層半導体とから構成される、InN系チャネル層半導体へテロ構造を用いた、InN系MIS構造へテロ構造FET(HFET)において、チャネル領域障壁層半導体およびInN系チャネル層半導体とから構成される、InN系チャネル層半導体へテロ構造を用いた、InN系MIS構造へテロ構造FET(HFET)において、ソース電極1およびドレイン電極3が形成されているオーミック領域において、窒化物障壁層半導体(オーミック領域障壁層半導体)と窒化物チャネル層半導体(オーミック領域チャネル層半導体)とから構成される窒化物半導体へテロ構造(オーミック領域へテロ構造)が形成されており、当該のオーミック領域へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、オーミック領域ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する、すわなち、チャネル領域へテロ界面の垂直位置よりも下方(同位置を含む)に存在する構造。図12に示される本実施例5の構造は、図6に示される実施例1の構造において、チャネル領域において、単層のInN系チャネル層半導体が用いられている、InN系FETではなく、チャネル領域障壁層半導体とInN系チャネル層半導体とから構成される、InN系チャネル層半導体へテロ構造が用いられている、InN系MIS構造へテロ構造FET(HFET)である。チャネル領域へテロ構造のInN系チャネル層半導体においては、図12に模式的に示されているように、InNの背景残留電子に加えて、当該へテロ界面の近傍には、高濃度の伝導電子(チャネル領域チャネル電子(高濃度2次元電子))が存在する。

【0066】

図13は、図12に示される本実施例5のInN系MIS構造HFETにおいて、十分に大きな負のゲート電圧を印加した際のチャネル電子の分布の様子を示したもので、図7に示される実施例1のInN系MIS構造FETにおける、対応する状況におけるチャネル電子の分布の様子と全く同様の状況が実現される様子が示されており、したがって、図12に示される本実施例5のInN系MIS構造HFETにおいて、チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となることが模式的に示されている。

【0067】

本実施例が示されている図12においては、チャネル領域障壁層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、前記の両半導体層の表面位置が一致している必要は全くない。また、図12においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。

【0068】

本実施例5を、実施例1と比較した場合、本実施例5においては、チャネル領域においてヘテロ構造を形成する必要があり、したがって、より高度な結晶成長技術が必要とされるという、不利な点が存在するものの、チャネル領域へテロ構造におけるチャネル領域チャネル電子(高濃度2次元電子)の存在によって、チャネル抵抗が低減し、その結果、実施例1に比べて素子特性が高性能化される、という有利な点を有する。

【0069】

本実施例5の具体的な構造は、上記の特徴を有する図12において、チャネル領域障壁層半導体としてInxAl1-xN(0≦x<1.0)、InN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)(バンドギャップはInxAl1-xN(0≦x<1.0)のそれよりも小さいとする)、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-x22N(0≦xM2<xM1≦1.0)が用いられている構造である。図12における絶縁膜(絶縁ゲート)としては、SiO2、Si3N4、AlN、Al2O3、ZrO2、HfO2、その他、いかなる絶縁膜を用いることも可能である。

【0070】

本実施例として、下記の構造を有するMIS構造HFETを、下記の製造方法によって作製した。まず、オーミック領域チャネル層半導体としてGaN、オーミック領域障壁層半導体として層厚15 nmのAl0.3Ga0.7Nを用いたAl0.3Ga0.7N/GaNヘテロ構造を、MBE法あるいはMOVPE法等の結晶成長法によってサファイア基板上の全領域に成長した。次に、図12におけるInN系チャネル層半導体の領域において、すなわち、オーミック領域以外の全領域において、オーミック領域障壁層半導体である層厚15 nmのAl0.3Ga0.7N、およびその下方の層厚200 nmのGaNをドライエッチング法等の通常の半導体エッチング法により削除し、その後、この領域に、MBE法あるいはMOVPE法などの結晶成長法によって、選択的に、InN系チャネル層半導体として層厚205 nmのInN、および、チャネル領域障壁層半導体として層厚10 nmのInl0.2Al0.8Nを、再成長した。ここで、選択的な再成長は、SiO2等の絶縁膜を選択成長マスクとして用いる等の方法により可能である。その後、絶縁ゲート膜として層厚10 nmのSi3N4を用いたMIS構造FETを、通常のMIS構造FETの作製プロセスにより作製した。このようにして作製した、InN系チャネル層半導体を用いたMIS構造FETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、本実施例5のドレイン電流が、実施例1のドレイン電流の約2倍になることが確認された。

【0071】

ここで、本実施例のMIS構造FETが、サファイア基板上の他、SiC(シリコンカーバイド)基板上あるいはSi(シリコン)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、図12に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0072】

また、本実施例においては、チャネル領域障壁層半導体としてInxAl1-xN(0≦x<1.0)、InN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)(バンドギャップはInxAl1-xN(0≦x<1.0)のそれよりも小さいとする)が用いられているが、チャネル領域障壁層半導体およびチャネル領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、チャネル領域障壁層半導体のバンドギャップがチャネル領域チャネル層半導体のそれよりも大きい、という条件のもとで、InAlN/InGaN、InAlN/InN、AlN/InGaNの他、AlGaN/InN、AlGaN/InGaN、InGaN/InN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなチャネル領域へテロ構造を構成することが可能であり、当該へテロ構造のチャネル領域障壁層半導体およびチャネル領域チャネル層半導体としてこれらの半導体が用いられている場合も、図12に示される本発明による特徴を有する限り、すべて本発明の範囲内である。

【実施例6】

【0073】

図14に示される、InN系チャネル層半導体を用いたMIS構造HFET。本実施例6は、実施例5の改良型である。すわなち、ゲート電極2の形成されているチャネル領域において、窒化物障壁層半導体(チャネル領域障壁層半導体)およびInN系チャネル層半導体とから構成される、InN系チャネル層半導体へテロ構造が形成されていると同時に、ソース電極1およびドレイン電極3が形成されているオーミック領域において、窒化物障壁層半導体(オーミック領域障壁層半導体)と窒化物チャネル層半導体(オーミック領域チャネル層半導体)とから構成される窒化物半導体へテロ構造(オーミック領域へテロ構造)が形成されており、当該のオーミック領域へテロ構造においては、ヘテロ界面近傍のみに伝導電子(オーミック領域チャネル電子(高濃度2次元電子))が局在する構造において、当該ヘテロ界面の垂直方向位置が、InN系チャネル層半導体の層内位置に存在する構造において、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)が挿入されている構造である。

【0074】

図12においては、チャネル領域障壁層半導体の表面位置と、オーミック領域障壁層半導体の表面位置とが、一致しているように描かれているが、これは、図を簡単にするためにであって、本発明において、前記の両半導体層の表面位置が一致している必要は全くない。また、図12においては、ゲート電極2の領域が、チャネル層半導体の領域に含まれているように描かれているが、前記の両領域の大小関係は任意である。図12には、当該の窒化物組成傾斜半導体層の、InN系チャネル層半導体近傍の領域においても、残留背景電子が存在している様子も示されている。

【0075】

本実施例6の、実施例5と比較した場合の改良点は、実施例2の、実施例1と比較した場合の改良点と全く同じである。すわなち、図12に示される実施例5の構造においては、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に一般に存在する、伝導帯不連続が、FETの動作時、すなわち、ドレイン電流が流れる際に、前記の両半導体層間でのチャネル電子輸送においてエネルギー障壁となり、これが、FET動作にとって不利な、電気抵抗の要因になる。しかし、図14に示される本実施例6の構造においては、窒化物組成傾斜半導体層によって当該の伝導帯不連続が解消されるため、FET動作時の電気抵抗が低減され、素子特性が高性能化される。本実施例6を実施例5と比較すると、本実施例6は層構造がより複雑になるために、実施例5に比べてより高度な結晶成長技術が必要とされるという、不利な点が存在するものの、実施例5に比べて素子特性が高性能化されるという、有利な点を有する。

【0076】

本実施例6の具体的な構造は、上記の特徴を有する図14において、チャネル領域障壁層半導体としてInxAl1-xN(0≦x<1.0)、InN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)(バンドギャップはInxAl1-xN(0≦x<1.0)のそれよりも小さいとする)、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-x22N(0≦xM2<xM1≦1.0)が用いられており、かつ、InN系チャネル層半導体InxCGa1-xCN(0<xC≦1.0)と、オーミック領域チャネル層半導体AlxM1Ga1-xM1N(0<xM1≦1.0)との間に、前記の両半導体層の間に伝導帯不連続が生じないように、組成傾斜を設けた窒化物半導体層(窒化物組成傾斜半導体層)InxAlYGa1-x-YN(xおよびYは層内で連続的に変化、0≦x≦1、0≦Y≦1)が挿入されている構造である。図8における絶縁膜(絶縁ゲート)としては、SiO2、Si3N4、AlN、Al2O3、ZrO2、HfO2、その他、いかなる絶縁膜を用いることも可能である。

【0077】

本実施例として、下記の構造を有するMIS構造HFETを、下記の製造方法によって作製した。まず、オーミック領域チャネル層半導体としてGaN、オーミック領域障壁層半導体として層厚15 nmのAl0.3Ga0.7Nを用いたAl0.3Ga0.7N/GaNヘテロ構造を、MBE法あるいはMOVPE法等の結晶成長法によってサファイア基板上の全領域に成長した。次に、図8における窒化物組成傾斜半導体層およびInN系チャネル層半導体の領域において、すなわち、オーミック領域以外の全領域において、オーミック領域障壁層半導体である層厚15 nmのAl0.3Ga0.7N、およびその下方の層厚200 nmのGaNをドライエッチング法等の通常の半導体エッチング法により削除した。その後、この領域に、縦方向層厚10 nmの組成傾斜InGaNを、初期In組成0、最終In組成1.0なる線形変化の組成傾斜InGaN層として、MBE法あるいはMOVPE法等の結晶成長法により再成長を行った。この際の結晶成長条件においては、当該の組成傾斜InGaN層の横方向層厚は5 nmであった。前記の組成傾斜InGaN層の再成長に引き続き、InN系チャネル層半導体として層厚205 nmのInN、および、チャネル領域障壁層半導体として層厚10 nmのInl0.2Al0.8Nを、再成長した。ここで、選択的な再成長は、SiO2等の絶縁膜を選択成長マスクとして用いる等の方法により可能である。その後、絶縁ゲート膜として層厚10 nmのSi3N4を用いたMIS構造HFETを、通常のMIS構造HFETの作製プロセスにより作製した。このようにして作製した、InN系チャネル層半導体を用いたMIS構造HFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、本実施例6のドレイン電流が、実施例5のドレイン電流の約1.5倍になることが確認された。

【0078】

ここで、本実施例のMIS構造HFETが、サファイア基板上の他、SiC(シリコンカーバイド)基板上あるいはSi(シリコン)基板上、あるいは、これらの基板上に形成されたGaN、AlN、AlGaN、InGaN等のテンプレート基板上、もしくはGaN、AlN、InN、AlGaN、InGaN等の自立基板上等、いかなる基板上に形成されている場合も、図8に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0079】

また、本実施例においては、ゲート電極2の下方に存在するInN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)が用いられているが、InN系チャネル層半導体としてInNやInGaNの他、InxAl1-xN(0<x≦1.0)、あるいはInxAlYGa1-x-YN(0<x≦1、0≦Y≦1)が用いられている場合も、図8に示される本発明による構造の特徴を有する限り、すべて本発明の範囲内である。

【0080】

また、本実施例においては、チャネル領域障壁層半導体としてInxAl1-xN(0≦x<1.0)、InN系チャネル層半導体としてInxCGa1-xCN(0<xC≦1.0)(バンドギャップはInxAl1-xN(0≦x<1.0)のそれよりも小さいとする)が用いられているが、チャネル領域障壁層半導体およびチャネル領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、チャネル領域障壁層半導体のバンドギャップがチャネル領域チャネル層半導体のそれよりも大きい、という条件のもとで、InAlN/InGaN、InAlN/InN、AlN/InGaNの他、AlGaN/InN、AlGaN/InGaN、InGaN/InN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなチャネル領域へテロ構造を構成することが可能であり、当該へテロ構造のチャネル領域障壁層半導体およびチャネル領域チャネル層半導体としてこれらの半導体が用いられている場合も、図14に示される本発明による特徴を有する限り、すべて本発明の範囲内である。

【0081】

また、本実施例においては、オーミック領域壁層半導体としてAlxM1Ga1-xM1N(0<xM1≦1.0)、オーミック領域チャネル層半導体としてAlxM2Ga1-xM2N(0≦Mx2<xM1≦1.0)が用いられているが、オーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてAlxGa1-xN(0≦x≦1.0)、InxGa1-xN(0≦x≦1.0)、InxAl1-xN(0≦x≦1.0)、あるいはInxAlYGa1-x-YN(0≦x≦1、0≦Y≦1)を用いて、オーミック領域障壁層半導体のバンドギャップがオーミック領域チャネル層半導体のそれよりも大きい、という条件のもとで、AlN/AlGaN、AlGaN/AlGaN、AlGaN/GaNの他、AlGaN/InN、AlGaN/InGaN、InAlN/InN、InAlN/InGaN、InAlN/InAlN、InAlGaN/InN、InAlGaN/InGaN等の、さまざまなオーミック領域へテロ構造を構成することが可能であり、当該へテロ構造のオーミック領域障壁層半導体およびオーミック領域チャネル層半導体としてこれらの半導体が用いられている場合も、図14に示される本発明による特徴を有する限り、すべて本発明の範囲内である。この際には、図14における組成傾斜半導体層としてInxAlYGa1-x-YN(xおよびYは層内で連続的に変化、0≦x≦1、0≦Y≦1)を用いることにより、InN系チャネル層半導体と、オーミック領域チャネル層半導体との間に、伝導帯不連続が生じないように、組成傾斜を設けることが可能である。

【実施例7】

【0082】

図15に示される、InN系チャネル層半導体を用いたHFET。本実施例7は、図12に示される実施例5において、ゲート絶縁膜が用いられていない、すなわち、MIS構造ではない、通常のHFETである。図15には、図12と同様に、チャネル電子の分布の様子が示されている。本実施例7のHFETは、実施例5のMIS構造HFETに比べて、ゲートリーク電流が大きく、また、ゲート耐圧が小さい、という不利な点を有するが、一方、ゲート絶縁膜を用いていないため、素子作製プロセスがより簡便であるという、有利な点を有する。

【0083】

本実施例7として、実施例5において絶縁ゲート膜を堆積せずに、ゲート電極2を形成したFETを、すわなち、ゲート絶縁膜が用いられていないという点以外は実施例5と全く同じ構造のHFETを、実施例5と全く同様の作製方法によって作製した。このようにして作製した、InN系チャネル層半導体を用いたHFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系HFETが実現された。また、実施例5と比べると、ゲートリーク電流が増大し、ゲート耐圧も低減したものの、より簡便な素子作製プロセスにより、高性能のInN系HFETが実現されることが確認された。

【0084】

本実施例7は、ゲート絶縁膜が用いられていないという点以外は、実施例5と全く同様であるため、本実施例5における、結晶成長基板、構成される半導体層、および、その他に関する請求範囲は、実施例5に準ずるものとする。

【実施例8】

【0085】

図16に示される、InN系チャネル層半導体を用いたHFET。本実施例8は、図14に示される実施例6において、ゲート絶縁膜が用いられていない、すなわち、MIS構造ではない、通常のHFETである。図11には、図8と同様に、チャネル電子の分布の様子が示されている。本実施例8のFETは、実施例6のMIS構造HFETに比べて、ゲートリーク電流が大きく、また、ゲート耐圧が小さい、という不利な点を有するが、一方、ゲート絶縁膜を用いていないため、素子作製プロセスがより簡便であるという、有利な点を有する。また、本実施例8のHFETを、実施例7のHFETと比較すると、実施例6の実施例5に対する比較と全く同様に、窒化物組成傾斜半導体層の設置によって、InN系チャネル層半導体とオーミック領域チャネル層半導体との間の伝導帯不連続が解消されるため、HFET動作時の電気抵抗が低減され、素子特性が高性能化される。このように、本実施例8は層構造がより複雑になるために、実施例7に比べて作製により手間がかかるという不利な点が存在するものの、実施例7に比べて素子特性が高性能化されるという、有利な点を有する。

【0086】

本実施例8として、実施例6において絶縁ゲート膜を堆積せずに、ゲート電極2を形成したHFETを、すわなち、ゲート絶縁膜が用いられていないという点以外は実施例6と全く同じ構造のHFETを、実施例6と全く同様の作製方法によって作製した。このようにして作製した、InN系チャネル層半導体を用いたHFETのデバイス特性の評価を行ったところ、InN系半導体チャネル層において高濃度の残留背景電子が存在するにもかかわらず、ピンチオフ特性が得られることが確認され、高性能のInN系FETが実現された。また、実施例6と比べると、ゲートリーク電流が増大し、ゲート耐圧も低減したものの、より簡便な素子作製プロセスにより、高性能のInN系FETが実現されることが確認された。

【0087】

本実施例8は、ゲート絶縁膜が用いられていないという点以外は、実施例6と全く同様であるため、本実施例6における、結晶成長基板、組成傾斜層その他の構成される半導体層、および、その他に関する請求範囲は、実施例6に準ずるものとする。

【符号の説明】

【0088】

1:ソース電極、2:ゲート電極、3:ドレイン電極。

【特許請求の範囲】

【請求項1】

窒化物半導体を用いた電界効果トランジスタであり、ゲート電極の下方に存在するチャネル層半導体として、InN系半導体であるInN、InGaN、InAlNあるいはInAlGaNが用いられている半導体装置において、

ソース電極にオーミック接触するオーミック領域障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側窒化物半導体へテロ接合構造、および、ドレイン電極にオーミック接触するオーミック領域障壁層半導体と前記オーミック領域チャネル層半導体とから形成されるドレイン側窒化物半導体へテロ接合構造が形成され、

前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、前記チャネル層半導体と接し、

前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とにおいて、それぞれ、ヘテロ接合界面近傍のみに伝導電子が局在し、

前記ソース側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置と前記ドレイン側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置とが、前記チャネル層半導体の層内位置に存在することを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、組成傾斜を設けた窒化物半導体層を介して前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記チャネル層半導体との間、および、前記ドレイン側窒化物半導体へテロ接合構造と前記チャネル層半導体との間に伝導帯不連続が生じていないことを特徴とする半導体装置。

【請求項3】

請求項1に記載の半導体装置を作製する半導体装置の作製法であって、

基板上に、ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造とを部分として含む積層構造をエピタキシャル結晶成長法により形成する成長工程と、

該成長工程後に、チャネル層半導体を形成する位置にある前記積層構造の部分を、ドライ・エッチング法により削除するエッチング工程と、

該エッチング工程後に、チャネル層半導体を、エピタキシャル結晶成長法により形成する再成長工程とを有することを特徴とする半導体装置の作製法。

【請求項4】

請求項2に記載の半導体装置を作製する半導体装置の作製法であって、

基板上に、ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造とを部分として含む積層構造をエピタキシャル結晶成長法により形成する成長工程と、

該成長工程後に、チャネル層半導体および組成傾斜を設けた窒化物半導体層を形成する位置にある前記積層構造の部分を、ドライ・エッチング法により削除するエッチング工程と、

該エッチング工程後に、組成傾斜を設けた窒化物半導体層およびチャネル層半導体を、エピタキシャル結晶成長法により形成する再成長工程とを有することを特徴とする半導体装置の作製法。

【請求項1】

窒化物半導体を用いた電界効果トランジスタであり、ゲート電極の下方に存在するチャネル層半導体として、InN系半導体であるInN、InGaN、InAlNあるいはInAlGaNが用いられている半導体装置において、

ソース電極にオーミック接触するオーミック領域障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側窒化物半導体へテロ接合構造、および、ドレイン電極にオーミック接触するオーミック領域障壁層半導体と前記オーミック領域チャネル層半導体とから形成されるドレイン側窒化物半導体へテロ接合構造が形成され、

前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、前記チャネル層半導体と接し、

前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とにおいて、それぞれ、ヘテロ接合界面近傍のみに伝導電子が局在し、

前記ソース側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置と前記ドレイン側窒化物半導体へテロ接合構造のヘテロ接合界面の垂直方向位置とが、前記チャネル層半導体の層内位置に存在することを特徴とする半導体装置。

【請求項2】

請求項1に記載の半導体装置において、

前記ソース側窒化物半導体へテロ接合構造と前記ドレイン側窒化物半導体へテロ接合構造とが、それぞれ、接合部分を含めて、組成傾斜を設けた窒化物半導体層を介して前記チャネル層半導体と接し、前記ソース側窒化物半導体へテロ接合構造と前記チャネル層半導体との間、および、前記ドレイン側窒化物半導体へテロ接合構造と前記チャネル層半導体との間に伝導帯不連続が生じていないことを特徴とする半導体装置。

【請求項3】

請求項1に記載の半導体装置を作製する半導体装置の作製法であって、

基板上に、ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造とを部分として含む積層構造をエピタキシャル結晶成長法により形成する成長工程と、

該成長工程後に、チャネル層半導体を形成する位置にある前記積層構造の部分を、ドライ・エッチング法により削除するエッチング工程と、

該エッチング工程後に、チャネル層半導体を、エピタキシャル結晶成長法により形成する再成長工程とを有することを特徴とする半導体装置の作製法。

【請求項4】

請求項2に記載の半導体装置を作製する半導体装置の作製法であって、

基板上に、ソース側窒化物半導体へテロ接合構造とドレイン側窒化物半導体へテロ接合構造とを部分として含む積層構造をエピタキシャル結晶成長法により形成する成長工程と、

該成長工程後に、チャネル層半導体および組成傾斜を設けた窒化物半導体層を形成する位置にある前記積層構造の部分を、ドライ・エッチング法により削除するエッチング工程と、

該エッチング工程後に、組成傾斜を設けた窒化物半導体層およびチャネル層半導体を、エピタキシャル結晶成長法により形成する再成長工程とを有することを特徴とする半導体装置の作製法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2011−159794(P2011−159794A)

【公開日】平成23年8月18日(2011.8.18)

【国際特許分類】

【出願番号】特願2010−20133(P2010−20133)

【出願日】平成22年2月1日(2010.2.1)

【出願人】(000004226)日本電信電話株式会社 (13,992)

【出願人】(593006630)学校法人立命館 (359)

【Fターム(参考)】

【公開日】平成23年8月18日(2011.8.18)

【国際特許分類】

【出願日】平成22年2月1日(2010.2.1)

【出願人】(000004226)日本電信電話株式会社 (13,992)

【出願人】(593006630)学校法人立命館 (359)

【Fターム(参考)】

[ Back to top ]