半導体装置およびその製造方法、電子部品

【課題】貫通電極の微細化と表面電極の縮小化とを両立することができる半導体装置、および表面電極の大きさに関わらず、表面電極に対して貫通電極を確実にコンタクトさせることができる半導体装置の製造方法を提供すること。

【解決手段】Si基板29の表面13に複数の絶縁膜リング32を選択的に形成し、絶縁膜リング32の開口42に対向するように表面パッド33を形成する。次に、Si基板29を裏面14からエッチングすることにより、絶縁膜リング32の開口42を通過して表面パッド33に達する貫通孔56を形成し、貫通孔56の側面にビア絶縁膜35を形成した後、貫通孔56に電極材料を充填することにより、表面パッド33に電気的に接続されるように貫通電極17を形成する。

【解決手段】Si基板29の表面13に複数の絶縁膜リング32を選択的に形成し、絶縁膜リング32の開口42に対向するように表面パッド33を形成する。次に、Si基板29を裏面14からエッチングすることにより、絶縁膜リング32の開口42を通過して表面パッド33に達する貫通孔56を形成し、貫通孔56の側面にビア絶縁膜35を形成した後、貫通孔56に電極材料を充填することにより、表面パッド33に電気的に接続されるように貫通電極17を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、貫通電極を有する半導体装置およびその製造方法、ならびに当該半導体装置を備える電子部品(パッケージ)に関する。

【背景技術】

【0002】

近年、貫通電極を有する半導体装置を複数積層して、小型、大容量、高機能の電子部品を形成する技術が開発されている。

貫通電極を有する半導体装置は、たとえば、特許文献1および2に開示されている。

特許文献1および2の半導体装置は、Si基板と、Si基板に設けられた貫通電極と、Si基板の表面に形成された電極パッドと、電極パッド上に形成された再配置配線層とを含む。

【0003】

係る半導体装置は、たとえば、以下の方法により製造される。まず、Si基板の表面に絶縁膜を介して電極パッドを形成し、再配置配線層を形成する。次に、第1のエッチングガス(SF6)を用いて、Si基板の裏面からSi基板の途中までドライエッチングする。その後、第2のエッチングガス(C4F8)を用いてSi基板の残りの部分をドライエッチングすることにより、電極パッドに達する貫通孔を形成する。そして、貫通孔の側面に絶縁膜を形成し、絶縁膜の内側に貫通電極を形成する。以上の工程を経て、貫通電極を有する半導体装置が得られる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011−86773号公報

【特許文献2】特開2011−86850号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、貫通電極の微細化と表面電極の縮小化とを両立することができる半導体装置を提供することである。

本発明の他の目的は、表面電極の大きさに関わらず、表面電極に対して貫通電極を確実にコンタクトさせることができる半導体装置の製造方法を提供することである。

本発明のさらに他の目的は、半導体装置に貫通電極を高密度に設けることにより、小型化、大容量化および高機能化を実現することができる電子部品を提供することである。

【課題を解決するための手段】

【0006】

本発明の半導体装置は、半導体基板と、前記半導体基板の表面に選択的に形成された複数の絶縁膜リングと、前記絶縁膜リングの開口を通過して、前記半導体基板の前記表面と裏面との間を貫通する貫通電極と、前記貫通電極と前記半導体基板との間に設けられたビア絶縁膜と、前記半導体基板の前記表面の前記絶縁膜リングに対して前記表面側に離間して、前記開口に対向して形成され、前記貫通電極に電気的に接続された表面電極とを含む(請求項1)。

【0007】

この半導体装置は、半導体基板の表面に、複数の絶縁膜リングを選択的に形成する工程と、前記絶縁膜リングに対して前記半導体基板の反対側に、前記開口に対向するように表面電極を形成する工程と、前記半導体基板を裏面からエッチングすることにより、前記絶縁膜リングの前記開口を通過して前記表面電極に達する貫通孔を形成する工程と、前記貫通孔の側面にビア絶縁膜を形成する工程と、前記ビア絶縁膜が形成された前記貫通孔に電極材料を充填することにより、前記表面電極に電気的に接続されるように貫通電極を形成する工程とを含む、本発明の半導体装置の製造方法(請求項14)により製造することができる。

【0008】

この方法によれば、半導体基板の上部に表面電極を形成する位置に対向して、半導体基板の表面に開口を有する絶縁膜リングを予め形成する。そのため、当該絶縁膜リング上に表面電極を形成した後、半導体基板を裏面から表面電極へ向かってエッチングする工程において、理想のエッチング位置(絶縁膜リングの開口位置)と実際のエッチング位置との間にギャップが生じていても、エッチングが絶縁膜リングに到達した後は、絶縁膜リングと半導体基板とのエッチングレートの差を利用して(絶縁膜リングをマスクとして利用して)、当該エッチングを開口へガイドすることができる。

【0009】

そのため、当該エッチングにより形成される貫通孔のボトム部を、絶縁膜リングの開口位置に固定することができる。すなわち、半導体基板の表面の絶縁膜リングの開口に対向するように半導体基板の上部に配置された表面電極に対して、貫通孔を自己整合的に到達させることができる。その結果、貫通孔に電極材料を充填することにより、表面電極に対して貫通電極を確実にコンタクトさせることができる。

【0010】

従って、貫通孔を形成するときのパターニングの合わせ精度を考慮して、貫通孔の径よりも表面電極を常に大きく設計していた従来とは異なり、本発明によれば、表面電極の大きさに関わらず、表面電極に到達する貫通孔を正確に形成することができるので、表面電極の大きさの自由度を広げることができる。

これにより、本発明の半導体装置では、貫通電極の微細化を行なう場合に、従来に比べて表面電極を縮小化できる。その結果、貫通電極を高密度に設けることができるので、小型、大容量および高機能の半導体装置を実現することができる。

【0011】

また、表面電極の縮小化により、互いに隣り合う表面電極の間のスペースを広げることができるので、そのスペースを有効利用することができる。たとえば、配線等を当該スペースに敷設することができる。

本発明の半導体装置では、前記貫通電極は、前記開口内のボトム部と、前記開口外の本体部とを含み、前記本体部は、前記開口を区画する前記絶縁膜リングの内縁部に重なるように、前記開口に対して横方向へ張り出していることが好ましい(請求項2)。

【0012】

この構成によれば、貫通電極(本体部)の裏面側の端部に力が加わっても、本体部に重なっている絶縁膜リングが緩衝材として働くので、表面電極に伝わる力を低減することができる。その結果、たとえば、半導体装置の実装時に、表面電極がダメージを受けることを防止することができる。

この構成を有する半導体装置は、たとえば、前記半導体装置の製造方法において、前記開口を区画する前記絶縁膜リングの内縁部が前記貫通孔内に露出するように、前記開口の径よりも大きいパターン径で前記半導体基板をエッチングする工程を含む、前記貫通孔を形成する工程を実行することにより製造することができる(請求項15)。

【0013】

また、本発明の半導体装置では、表面電極の大きさの自由度を広げることができることから、前記貫通電極の前記本体部は、前記表面電極の径と同じかそれ以上の径を有していてもよい(請求項3)。言い換えれば、前記表面電極は、前記貫通電極の前記本体部の径と同じかそれ以下の径を有していてもよい。

この構成を有する半導体装置は、たとえば、前記半導体装置の製造方法において、前記表面電極の径と同じかそれ以上のパターン径で前記半導体基板をエッチングする工程を含む、前記貫通孔を形成する工程を実行することにより製造することができる(請求項16)。

【0014】

また、本発明の半導体装置では、前記絶縁膜リングの前記内縁部は、前記絶縁膜リングの外形を画成する外縁部よりも薄く形成されていてもよい(請求項4)。

また、本発明の半導体装置では、前記絶縁膜リングは、前記半導体基板の前記表面に対して前記裏面側へ埋め込まれていることが好ましい(請求項5)。

この構成によれば、絶縁膜リングの厚さ分、貫通電極の表面側の端部が裏面側に後退するので、貫通電極のアスクペクト比(貫通電極の高さ/貫通電極の径)を小さくすることができる。そのため、貫通孔に電極材料を充填するときのステップカバレッジ(段差被膜性)を向上させることができる。また、半導体基板の表面と絶縁膜リングの上面との間の段差をなくすことができるので、半導体基板の表面の平坦性を維持することもできる。

【0015】

この構成を有する半導体装置は、たとえば、前記半導体装置の製造方法において、前記半導体基板を前記表面からエッチングすることによりシャロートレンチを形成する工程と、前記シャロートレンチに絶縁材料を充填することにより、前記絶縁膜リングを前記半導体基板の前記表面に対して前記裏面側へ埋め込むように形成する工程とを含む、前記絶縁膜リングを形成する工程を実行することにより製造することができる(請求項17)。

【0016】

この方法によれば、たとえば、STI(Shallow Trench Isolation:シャロートレンチアイソレーション)工程により半導体基板に複数の素子分離領域を形成する場合に、当該STI工程と同一工程で絶縁膜リングを形成することができるので、効率よく絶縁膜リングを形成することができる。

また、本発明の半導体装置は、互いに隣り合う複数の前記表面電極の間に敷設された配線を含んでいてもよい(請求項6)。

【0017】

また、前記表面電極は、層間絶縁膜を介して積層された多層電極を含んでいてもよい(請求項7)。

また、本発明の半導体装置は、前記貫通電極との間に前記表面電極が置かれるように前記貫通電極の直上位置に配置された、外部接続用の表面バンプを含んでいてもよいし(請求項8)、前記貫通電極の前記裏面側の端部に配置された、外部接続用の裏面バンプを含んでいてもよい(請求項9)。

【0018】

また、前記絶縁膜リングは、円環状に形成されていてもよい(請求項10)。さらに、前記貫通電極は、円柱状に形成されていてもよい(請求項11)。

また、前記半導体基板の前記表面は、複数の半導体素子が形成された素子形成面を含んでいてもよい(請求項12)。

また、本発明の電子部品は、裏面に複数の外部端子を有するインタポーザと、前記インタポーザの表面に、前記表面が上方に向く姿勢で積層された請求項1〜12のいずれか一項に記載の半導体装置と、複数の裏面バンプを有し、当該裏面バンプが前記貫通電極に電気的に接続されるように前記半導体装置の前記表面に積層された第2半導体装置と、前記半導体装置および前記第2半導体装置を封止する樹脂パッケージとを含む(請求項13)。

【0019】

この構成によれば、本発明の半導体装置が搭載されているので、当該半導体装置に貫通電極を高密度に設けることにより、小型化、大容量化および高機能化を実現することができる。

【図面の簡単な説明】

【0020】

【図1】図1は、本発明の一実施形態に係る電子部品の模式的な断面図である。

【図2】図2は、図1の電子部品のシステム構成を模式的に示すブロック図である。

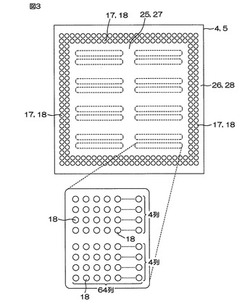

【図3】図3は、図1のSiインタポーザおよび演算チップにおける貫通電極のレイアウト図である。

【図4】図4は、図1の演算チップの構造を説明するための模式的な断面図であって、貫通電極が設けられた部分を拡大して示している。

【図5A】図5Aは、図4の演算チップの製造工程の一部を示す図である。

【図5B】図5Bは、図5Aの次の工程を示す図である。

【図5C】図5Cは、図5Bの次の工程を示す図である。

【図5D】図5Dは、図5Cの次の工程を示す図である。

【図5E】図5Eは、図5Dの次の工程を示す図である。

【図5F】図5Fは、図5Eの次の工程を示す図である。

【図5G】図5Gは、図5Fの次の工程を示す図である。

【図5H】図5Hは、図5Gの次の工程を示す図である。

【図5I】図5Iは、図5Hの次の工程を示す図である。

【図5J】図5Jは、図5Iの次の工程を示す図である。

【図5K】図5Kは、図5Jの次の工程を示す図である。

【図5L】図5Lは、図5Kの次の工程を示す図である。

【図5M】図5Mは、図5Lの次の工程を示す図である。

【発明を実施するための形態】

【0021】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の一実施形態に係る電子部品1の模式的な断面図である。図2は、図1の電子部品1のシステム構成を模式的に示すブロック図である。

電子部品1は、樹脂インタポーザ2と、樹脂インタポーザ2の表面3から順に積層された演算チップ4、Siインタポーザ5およびメモリチップ6と、樹脂パッケージ7とを含み、内部に電源系配線8および信号系配線9が組み込まれている。なお、演算チップ4、Siインタポーザ5およびメモリチップ6は、樹脂インタポーザ2の表面3に積層された複数の半導体装置の一例であり、これに限るものではない。

【0022】

樹脂インタポーザ2は、樹脂製(たとえば、エポキシ樹脂)基板からなり、その表面3に演算チップ4等が積層され、その裏面10に複数の外部端子11が形成されている。樹脂インタポーザ2のサイズは、14mm角であり、たとえば、10mm角〜15mm角であってもよい。樹脂インタポーザ2の厚さは、0.7mmであり、たとえば、0.6mm〜0.7mmであってもよい。

【0023】

外部端子11は、実装基板(プリント配線板)上のランド(電極)との電気接続用の端子である。外部端子11は、たとえば、半田などの金属材料を用いてボール状に形成されており、たとえば、互いに間隔を空けて行列状に配置されている。各外部端子11は、樹脂インタポーザ2の表面3と裏面10との間を貫通する導電性のビア(図示せず)を介して、演算チップ4の裏面バンプ19(後述)に電気的に接続されている。

【0024】

演算チップ4、Siインタポーザ5およびメモリチップ6は、この実施形態では、互いに同じ大きさで形成されており、互いに側面が揃うように整って積層されている。これらのチップのサイズは、10mm角であり、たとえば、6mm角〜10mm角であってもよい。樹脂インタポーザ2よりも小さく、チップの厚さは、0.05mmであり、たとえば、0.04mm〜0.06mmであってもよい。

【0025】

これら複数の半導体チップ4〜6のうち、最上層の第2半導体装置としてのメモリチップ6と樹脂インタポーザ2との間にある半導体装置としての演算チップ4には、図2に示すように、論理(Logic)・制御回路12が組み込まれている。論理・制御回路12には、電子部品1の電源系配線8および信号系配線9が接続されている。また、演算チップ4には、その表面13に当該論理・制御回路12を構成するトランジスタ(たとえばCMOSトランジスタ)、ダイオード、抵抗、キャパシタなどの複数の半導体素子が形成されている。つまり、演算チップ4では、メモリチップ6に対向する表面13が素子形成面であり、この素子形成面13が上方に向く姿勢で演算チップ4が樹脂インタポーザ2に積層されている。

【0026】

また、演算チップ4および半導体装置としてのSiインタポーザ5には、それぞれ表面13,15と裏面14,16との間を貫通する複数の貫通電極17,18が形成されており、各貫通電極17,18の裏面14,16側の端部に1つずつ裏面バンプ19,20が設けられている。裏面バンプ19,20は、たとえば、半田などの金属材料を用いてボール状に形成されている。また、演算チップ4の裏面バンプ19は、表面13上の半導体素子に電気的に接続されている。

【0027】

一方、最上層のメモリチップ6には、メモリセルアレイ21(この実施形態では、SRAM:Static Random Access Memoryのセルアレイ)および制御回路22が組み込まれており、これらの回路21,22には、電子部品1の電源系配線8および信号系配線9が接続されている。具体的には、制御回路22は電源系配線8によりメモリセルアレイ21に接続されており、メモリセルアレイ21は信号系配線9により演算チップ4の論理・制御回路12に接続されている。また、メモリチップ6には、その裏面23に当該メモリセルアレイ21および制御回路22を構成するトランジスタ、ダイオード、抵抗、キャパシタなどの複数の半導体素子が形成されている。つまり、メモリチップ6では、演算チップ4に対向する裏面23が素子形成面であり、この素子形成面23が下方に向く姿勢でメモリチップ6が樹脂インタポーザ2に積層されている。また、メモリチップ6には、その裏面23に複数の裏面バンプ24が設けられている。裏面バンプ24は、たとえば、半田などの金属材料を用いてボール状に形成されている。この裏面バンプ24は、裏面23上の半導体素子に電気的に接続されている。

【0028】

そして、メモリチップ6の裏面バンプ24は、Siインタポーザ5の貫通電極18および裏面バンプ20により中継されて、ピッチの異なる演算チップ4の貫通電極17および裏面バンプ19に電気的に接続されている。これにより、積層配置された複数の半導体チップが互いに電気的に接続され、樹脂インタポーザ2の外部端子11に電気的に接続されることとなる。

【0029】

なお、この実施形態では、演算チップ4とメモリチップ6との端子ピッチが互いに異なるので、これらの間に電気的な中継を担うSiインタポーザ5を配置しているが、当該端子ピッチが全く同じである場合には、Siインタポーザ5は省略されていてもよい。

樹脂パッケージ7(たとえば、エポキシ樹脂)は、樹脂インタポーザ2の裏面10を露出させるように、樹脂インタポーザ2の表面3側のみを封止しており、演算チップ4、Siインタポーザ5およびメモリチップ6が露出しないようにこれらのチップの全体を覆っている。また、樹脂パッケージ7は、その側面が樹脂インタポーザ2の側面と面一に揃うように形成されている。

【0030】

図3は、図1のSiインタポーザ5および演算チップ4における貫通電極17,18のレイアウト図である。

図1で示したように、この実施形態では、積層配置された複数の半導体チップ4〜6のうち、演算チップ4およびSiインタポーザ5それぞれに貫通電極17,18が設けられている。

【0031】

演算チップ4では、たとえば、複数列(この実施形態では、2列)に整列した貫通電極17が、演算チップ4の中央部25を取り囲む周縁部26に沿って環状に設けられている。なお、演算チップ4の貫通電極17は、たとえば、それぞれが不規則にランダムに配置され、全体として演算チップ4の周縁部26に沿った環状に設けられていてもよい。

これにより、演算チップ4は、貫通電極17を利用して、メモリチップ6に電力および電気信号を送ることができる。つまり、演算チップ4の貫通電極17が電子部品1の電源系配線8および信号系配線9を形成し、当該配線8,9により電力および信号が送られる。

【0032】

一方、Siインタポーザ5では、たとえば、単列の貫通電極18が、Siインタポーザ5の中央部27を取り囲む周縁部28に沿って環状に設けられているとともに(以下、これらの貫通電極18を周縁部28の貫通電極18ということがある。)、当該周縁部28に取り囲まれた中央部27に、複数の貫通電極18を1つの群として、複数の群が行列状に配置されている(以下、これらの貫通電極18を中央部27の貫通電極18ということがある。)。

【0033】

周縁部28の各貫通電極18は、この実施形態では、それぞれ演算チップ4の各貫通電極17と同一直線上に配置されるように、演算チップ4の各貫通電極17の直上に配置されている。

中央部27の貫通電極18の各群では、行列状に配置された複数の貫通電極18を1つのブロックとして、複数のブロックが設けられている。具体的には、この実施形態では、8つの群が2行4列(2×4)の行列状に配置されており、各群では、4行64列(4×64)の貫通電極18を1ブロックとして2ブロック、つまり1つの群当たり合計512個の貫通電極18が設けられている。この群が8群あるので、Siインタポーザ5全体では、4096個(512個×8群)の貫通電極18が設けられている。

【0034】

これにより、Siインタポーザ5は、たとえば、中央部27の貫通電極18を利用して、演算チップ4(たとえば、論理・制御回路12)とメモリチップ6(たとえば、メモリセルアレイ21)との間に中央部27の貫通電極18の数のビット数(この実施形態では、4096ビット)の電気信号を中継することができる。つまり、Siインタポーザ5の中央部27の貫通電極18が電子部品1の信号系配線9を形成し、当該配線9により電気信号が双方向に送受信される。なお、貫通電極18の配置や数は、本発明の一例に過ぎず、それぞれの電子部品1の設計に合わせて適宜変更することができる。たとえば、1ブロック256個の貫通電極18は、8行32列(8×32)の行列状に配置されていてもよい。

【0035】

また、Siインタポーザ5は、たとえば、周縁部28の貫通電極18を利用して、演算チップ4からメモリチップ6(たとえば、制御回路22)へと送られる電力および電気信号を中継することができる。つまり、Siインタポーザ5の周縁部28の貫通電極18が電子部品1の電源系配線8および信号系配線9を形成し、当該配線8,9により電力および電気信号が送られる。

【0036】

図4は、図1の演算チップ4の構造を説明するための模式的な断面図であって、貫通電極17が設けられた部分を拡大して示している。

演算チップ4は、演算チップ4の本体をなす半導体基板としてのSi基板29と、ゲート絶縁膜30と、層間絶縁膜31と、絶縁膜リング32と、表面電極としての表面パッド33と、パッド間配線34と、貫通電極17と、ビア絶縁膜35と、表面バンプ36と、裏面バンプ19とを含む。

【0037】

Si基板29は、たとえば、厚さ30μm〜50μmの基板であり、その表面13(素子形成面)に、ゲート絶縁膜30および複数(この実施形態では、2層)の層間絶縁膜31がこの順に積層されている。ゲート絶縁膜30は、当該表面13に形成されたトランジスタ(図示せず)が有するゲート絶縁膜30と一体な膜であり、当該トランジスタとの間で共有されている。

【0038】

また、Si基板29の表面13には、当該表面13に対して裏面14側に複数の絶縁膜リング32が選択的に埋め込まれており、当該表面13の一部が、表面13と面一に揃った絶縁膜リング32の上面により形成されている。これにより、Si基板29の表面13と絶縁膜リング32の上面との間の段差がないので、Si基板29の表面13の平坦性を維持することができる。絶縁膜リング32は、この実施形態は、酸化シリコン(SiO2)からなり、外径R1が12μm程度、内径(絶縁膜リング32の開口42の径)R2が8μm程度の円環状に形成されている。

【0039】

表面パッド33は、アルミニウム(Al)からなり、ゲート絶縁膜30、およびゲート絶縁膜30と最上層の層間絶縁膜(第2層間絶縁膜38)の間の層間絶縁膜(第1層間絶縁膜37)それぞれの上に積層された多層パッド構造を有している。

この実施形態では、表面パッド33は、2層パッド構造を有しており、ゲート絶縁膜30上に形成された下側パッド39と、第1層間絶縁膜37上に形成された上側パッド40とを含み、互いに上下に重なり合う下側パッド39と上側パッド40との間は、第1層間絶縁膜37を貫通する複数の導電性のビア41を介して電気的に接続されている。表面パッド33の層構造は、2層構造に限らず、たとえば、3層構造、4層構造、5層構造、それ以上の層構造であってもよい。また、表面パッド33の材料は、銅(Cu)などの他の金属材料であってもよい。

【0040】

表面パッド33は、各絶縁膜30,37上において、絶縁膜リング32の開口42を塞ぐように当該開口42に対向して形成されている。各表面パッド33は、絶縁膜リング32の外径R1よりも小さく、内径R2よりも大きい幅W1(たとえば、W1=10μm程度)を有する四角状に形成されており、Si基板29を裏面14側から見た底面視において絶縁膜リング32の外周よりも内側に収まっている。

【0041】

また、第1層間絶縁膜37上において、互いに隣り合う上側パッド40の間には、複数のパッド間配線34が選択的に敷設されている。パッド間配線34は、ゲート絶縁膜30上の下側パッド39の間に敷設されていてもよい。

貫通電極17は、銅(Cu)からなり、Si基板29の裏面14から当該裏面14に対して垂直に絶縁膜リング32の開口42を通過して表面パッド33(下側パッド39)に達する円柱状に形成されている。これにより、貫通電極17および表面パッド33は、Si基板29の厚さ方向に同一直線上に並んでいる。なお、貫通電極17および表面パッド33は、必ずしも同一直線上に並んでいる必要はなく、たとえば、表面パッド33は、貫通電極17のSi基板29の表面13側端部から再配線等を引き回すことにより、平面視において貫通電極17から離れた位置に配置されていてもよい。

【0042】

貫通電極17は、絶縁膜リング32の開口42内のボトム部43と、当該開口42外の本体部44とを含み、本体部44は、開口42を区画する絶縁膜リング32の内縁部45全周に重なるように、開口42に対して横方向(Si基板29の表面13に沿う方向)へ均等に張り出している。これにより、貫通電極17の本体部44は、表面パッド33の幅W1と同じかそれ以上の径R3を有している。この実施形態では、たとえば、R3=10μm程度である。

【0043】

また、絶縁膜リング32において、貫通電極17の本体部44に重なる内縁部45は、絶縁膜リング32の外形を画成する外縁部46よりも薄く形成されている。たとえば、絶縁膜リング32の内縁部45の厚さT1が0.2μm程度であり、外縁部46の厚さT2が0.4μm程度である。

ビア絶縁膜35は、酸化シリコン(SiO2)からなり、貫通電極17とSi基板29との間およびSi基板29の裏面14全域に設けられている。

【0044】

この実施形態では、ビア絶縁膜35は、貫通電極17のボトム部43の側面(周面)を覆うボトム部47、貫通電極17の本体部44の側面(周面)を覆う本体部48およびSi基板29の裏面14を覆う裏面部49を含む。ビア絶縁膜35の本体部48およびビア絶縁膜35の裏面部49は、互いに一体的に形成されている。一方、ビア絶縁膜35の本体部48とビア絶縁膜35のボトム部47との間には、絶縁膜リング32の内縁部45に沿って所定の間隔が設けられていて、これらの部分は絶縁膜リング32の内縁部45で互いに分断されている。

【0045】

また、ビア絶縁膜35は、本体部48およびボトム部47が、裏面部49に比べて薄く形成されている。たとえば、本体部48およびボトム部47の厚さが、0.5μm程度であり、裏面部49の厚さが1μm程度である。

表面バンプ36は、第2層間絶縁膜38上において、貫通電極17との間に表面パッド33が置かれるように、貫通電極17の直上位置に1つずつ配置されている。各表面バンプ36は、互いに上下に重なり合う上側パッド40に対して、第2層間絶縁膜38を貫通する導電性のビア50を介して電気的に接続されている。また、各表面バンプ36は、演算チップ4上にSiインタポーザ5を積層した状態において、たとえば、Siインタポーザ5の裏面バンプ20(図1参照)と接続される。

【0046】

裏面バンプ19は、前述のように、各貫通電極17の裏面14側の端部に1つずつ設けられている。

以上説明した絶縁膜リング32を有する演算チップ4の構成は、この実施形態では、貫通電極18が形成された半導体基板(Si基板)であるSiインタポーザ5にも採用されている。また、絶縁膜リング32を形成することにより本体部44に比べて細く形成されたボトム部43を有する貫通電極17は、電子部品1の電源系配線8および信号系配線9のいずれにも使用する必要はなく、好ましくは、配線の低抵抗化が特に必要とされない信号系配線9を形成する貫通電極17に用いる。

【0047】

図5A〜図5Mは、図4の演算チップ4の製造工程の一部を工程順に示す図である。

演算チップ4を製造するには、まず、図5Aに示すように、700μm以上の厚さを有するSi基板29を表面13からエッチングすることにより、円環状のシャロートレンチ51を選択的に形成し、当該シャロートレンチ51にCVD法によりSiO2(絶縁材料)を充填する。これにより、Si基板29に埋め込まれた絶縁膜リング32(外径R1=12μm、内径R2=8μm)が形成される。この絶縁膜リング32を形成する工程は、たとえば、STI(Shallow Trench Isolation:シャロートレンチアイソレーション)工程によりSi基板29に複数の素子分離領域を形成する工程と同一工程で行うことができるので、効率よく絶縁膜リング32を形成することができる。

【0048】

その後、図示は省略するが、公知の方法により、Si基板29の表面13に対してイオン注入(たとえば、n型イオン、p型イオン)することにより、半導体素子を構成する不純物領域が形成される。

次に、図5Bに示すように、熱酸化法によりゲート絶縁膜30を形成する。その後、スパッタ、フォトリソグラフィ、CVD等の公知の半導体装置の製造技術により、ゲート絶縁膜30上に、下側パッド39、第1層間絶縁膜37、ビア41、上側パッド40およびパッド間配線34、第2層間絶縁膜38、ビア50および表面バンプ36を順に形成する。

【0049】

次に、図5Cに示すように、Si基板29の表面13側に、接着剤52を介してガラス基板53(支持体)を貼り付ける。

次に、図5Dに示すように、たとえば、グラインダなどを用いて、Si基板29を裏面14側から研削して(バックグラインド)、Si基板29を薄化する。この実施形態では、700μm以上のSi基板29が30μm〜50μmになるまで研削する。

【0050】

次に、図5Eに示すように、絶縁膜リング32の開口42を基準に位置合わせをして、Si基板29の裏面14に、貫通電極17を形成すべき領域に本体部44と同じ径R3(R3≧表面パッド33の幅W1、絶縁膜リング32の内径R2)の開口55を有するフォトレジスト54(たとえば、ポリイミド等の有機レジスト)を形成する。

次に、図5Fに示すように、フォトレジスト54を介してSi基板29にエッチングガス(たとえば、SF6/O2など)を供給して、Si基板29を裏面14側からドライエッチングする。このエッチングは、絶縁膜リング32に到達した後、絶縁膜リング32(SiO2)とSi基板29とのエッチングレートの差を利用して(絶縁膜リング32をマスクとして利用して)絶縁膜リング32の開口42へガイドされる。そして、絶縁膜リング32の開口42を通過してゲート絶縁膜30が露出するまで、エッチングガスの種類を代えずに同一のガス種でエッチングを続ける。これにより、Si基板29に貫通孔56が形成され、各貫通孔56内には、絶縁膜リング32の内縁部45が露出することとなる。

【0051】

次に、図5Gに示すように、貫通孔56を形成したときのフォトレジスト54を残した状態で、貫通孔56の底面を形成するゲート絶縁膜30をエッチングすることにより、貫通孔56内に表面パッド33(下側パッド39)を露出させる。この際、ゲート絶縁膜30と同一材料(SiO2)からなる絶縁膜リング32のうち、貫通孔56の側面よりも内側の内縁部45もエッチングガスに晒されるので、ゲート絶縁膜30と同時にエッチングされる。これにより、絶縁膜リング32の内縁部45と外縁部46との間に段差(厚さの差)が生じる。

【0052】

次に、図5Hに示すように、フォトレジスト54を除去した後、CVD法により、貫通孔56内に露出している表面パッド33が覆われるように、貫通孔56の内面およびSi基板29の裏面14にビア絶縁膜35を形成する。

次に、図5Iに示すように、エッチバックにより、ビア絶縁膜35における貫通孔56の開口端に臨む部分、具体的には、表面パッド33上の部分(底面部分)および絶縁膜リング32の内縁部45上の部分を選択的に除去する。これにより、貫通孔56内に表面パッド33(下側パッド39)が再度露出する。

【0053】

次に、図5Jに示すように、ビア絶縁膜35の表面にシード膜(たとえば、Ti/Cuの積層膜)をスパッタした後、電解めっきにより、当該シード膜からCuをめっき成長させる。これにより、貫通孔56におけるビア絶縁膜35の内側にCu(電極材料)が充填され、表面パッド33に電気的に接続された貫通電極17が形成される。

次に、図5Kに示すように、研磨面がビア絶縁膜35の裏面部49と面一に揃うまで、貫通電極17の余分な部分(貫通孔56外の部分)をCMP(Chemical Mechanical Polishing)法により研磨して除去する。

【0054】

その後、図5Lに示すように、各貫通電極17に1つずつ裏面バンプ19を形成し、図5Mに示すように、Si基板29をガラス基板53から取り外すことにより、図4の演算チップ4が得られる。

以上、この実施形態の方法によれば、図5Aに示すように、表面パッド33の位置に対向する開口42を有する絶縁膜リング32を予め形成する。そのため、当該絶縁膜リング32上に表面パッド33を形成した後、Si基板29を裏面14から表面パッド33へ向かってエッチングする図5Fの工程において、理想のエッチング位置(絶縁膜リング32の開口42の位置)と実際のエッチング位置との間にギャップが生じていても、ドライエッチングが絶縁膜リング32に到達した後は、絶縁膜リング32(SiO2)とSi基板29とのエッチングレートの差を利用して(絶縁膜リング32をマスクとして利用して)、当該エッチングを開口42へガイドすることができる。

【0055】

そのため、当該エッチングにより形成される貫通孔56のボトム部を、絶縁膜リング32の開口42位置に固定するとともに、表面パッド33の幅W1よりも細くすることができる。すなわち、絶縁膜リング32の開口42に対向するように配置された表面パッド33に対して、貫通孔56を自己整合的に到達させることができる。その結果、貫通孔56にCuをめっき成長させることにより、表面パッド33に対して貫通電極17を確実にコンタクトさせることができる。

【0056】

従って、貫通孔56を形成するときのパターニングの合わせ精度を考慮して、貫通孔56の径R3よりも表面パッド33を常に大きく設計していた従来とは異なり、この実施形態によれば、表面パッド33の大きさ(幅W1)に関わらず、表面パッド33に到達する貫通孔56を正確に形成することができる。よって、表面パッド33の大きさの自由度を広げることができる。

【0057】

これにより、演算チップ4では、貫通電極17の微細化を行なう場合に、従来に比べて表面パッド33を縮小化できる。その結果、貫通電極17を高密度に設けることができるので、小型、大容量および高機能の半導体チップを実現することができる。

また、表面パッド33の縮小化により、互いに隣り合う表面パッド33の間のスペースを広げることができるので、そのスペースを有効利用して、パッド間配線34を敷設することができる。

【0058】

なお、この実施形態の方法では、貫通電極17のボトム部43を固定する絶縁膜リング32を表面パッド33に対して精密に位置合わせする必要があるが、絶縁膜リング32と表面パッド33とはゲート絶縁膜30の厚さ程度しか離れていないので、公知の方法でも精密に位置合わせすることができる。

また、演算チップ4によれば、裏面バンプ19を介して貫通電極17(本体部44)の裏面14側の端部に力が加わっても、本体部44に重なっている絶縁膜リング32(内縁部45)が緩衝材として働くので、表面パッド33に伝わる力を低減することができる。その結果、たとえば、演算チップ4を樹脂インタポーザ2に実装する時に、表面パッド33がダメージを受けることを防止することができる。

【0059】

また、演算チップ4によれば、絶縁膜リング32の内縁部45の厚さT1分、貫通電極17(本体部44)の表面13側の端部が裏面14側に後退しているので、貫通電極17のアスクペクト比(貫通電極17の高さ/貫通電極17の径R3)を小さくすることができる。そのため、貫通孔56に電極材料を充填するときのステップカバレッジ(段差被膜性)を向上させることができる。

【0060】

また、演算チップ4によれば、貫通電極17とSi基板29との間のリーク電流も防止することができる。

すなわち、図5Iの工程において、表面パッド33を露出させるためにビア絶縁膜35の底面部分をエッチバックにより除去することになるが、貫通孔56の内面のビア絶縁膜35(本体部48およびボトム部47)をそれほど厚いものではない。そのため、エッチバックの際、貫通孔56のボトム部の側面に形成されたビア絶縁膜35も一緒に除去されてしまうおそれがある。

【0061】

そこで、この実施形態では、たとえ貫通孔56のボトム部側面のビア絶縁膜35が除去されてしまっても、その周りに絶縁膜リング32が存在しているので、貫通電極17とSi基板29との絶縁状態を保持することができる。その結果、貫通電極17とSi基板29との間のリーク電流を防止することができる。

そして、図1の電子部品1によれば、上記した演算チップ4およびSiインタポーザ5が搭載されているので、演算チップ4およびSiインタポーザ5に貫通電極17を高密度に設けることにより、小型化、大容量化および高機能化を実現することができる。

【0062】

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

たとえば、貫通電極17は、楕円柱状、四角柱状、六角柱状、八角柱状であってもよく、絶縁膜リング32も、楕円環状、四角環状、六角環状、八角環状であってもよい。

また、図5Jの工程において、貫通電極17は、CVD法を用いてポリシリコンを貫通孔56に充填することにより形成することができる。ただし、その場合にはSi基板29およびガラス基板53が高温に晒されるので、接着剤52が溶けないように対策を施す必要がある。つまり、接着剤52の耐熱温度が比較的低温(200℃程度)である場合には、前述の実施形態のように、電解めっき法を採用することが好ましい。

【0063】

また、図5Aの工程において、絶縁膜リング32を形成する工程は、Si基板29に素子分離領域を形成するSTI工程と同一工程で行ったが、独立して行ってもよい。また、絶縁膜リング32を形成する工程は、Si基板29の表面13に熱酸化により絶縁膜を形成する工程と、当該絶縁膜をパターニングすることにより、Si基板29の表面13に対して突出するように絶縁膜リング32を形成する工程とを含んでいてもよい。

【0064】

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0065】

1 電子部品

2 樹脂インタポーザ

3 (樹脂インタポーザの)表面

4 演算チップ

5 Siインタポーザ

6 メモリチップ

7 樹脂パッケージ

8 電源系配線

9 信号系配線

10 (樹脂インタポーザの)裏面

11 外部端子

12 論理・制御回路

13 (演算チップの)表面

14 (演算チップの)裏面

15 (Siインタポーザの)表面

16 (Siインタポーザの)裏面

17 (演算チップの)貫通電極

18 (Siインタポーザの)貫通電極

19 (演算チップの)裏面バンプ

20 (Siインタポーザの)裏面バンプ

21 メモリセルアレイ

22 制御回路

23 (メモリチップの)裏面

24 (メモリチップの)裏面バンプ

25 (演算チップの)中央部

26 (演算チップの)周縁部

27 (Siインタポーザの)中央部

28 (Siインタポーザの)周縁部

29 Si基板

30 ゲート絶縁膜

31 層間絶縁膜

32 絶縁膜リング

33 表面パッド

34 パッド間配線

35 ビア絶縁膜

36 表面バンプ

37 第1層間絶縁膜

38 第2層間絶縁膜

39 下側パッド

40 上側パッド

41 ビア

42 (絶縁膜リングの)開口

43 (貫通電極の)ボトム部

44 (貫通電極の)本体部

45 (絶縁膜リングの)内縁部

46 (絶縁膜リングの)外縁部

47 (ビア絶縁膜の)ボトム部

48 (ビア絶縁膜の)本体部

49 (ビア絶縁膜の)裏面部

50 ビア

51 シャロートレンチ

52 接着剤

53 ガラス基板

54 フォトレジスト

55 (フォトレジストの)開口

56 貫通孔

【技術分野】

【0001】

本発明は、貫通電極を有する半導体装置およびその製造方法、ならびに当該半導体装置を備える電子部品(パッケージ)に関する。

【背景技術】

【0002】

近年、貫通電極を有する半導体装置を複数積層して、小型、大容量、高機能の電子部品を形成する技術が開発されている。

貫通電極を有する半導体装置は、たとえば、特許文献1および2に開示されている。

特許文献1および2の半導体装置は、Si基板と、Si基板に設けられた貫通電極と、Si基板の表面に形成された電極パッドと、電極パッド上に形成された再配置配線層とを含む。

【0003】

係る半導体装置は、たとえば、以下の方法により製造される。まず、Si基板の表面に絶縁膜を介して電極パッドを形成し、再配置配線層を形成する。次に、第1のエッチングガス(SF6)を用いて、Si基板の裏面からSi基板の途中までドライエッチングする。その後、第2のエッチングガス(C4F8)を用いてSi基板の残りの部分をドライエッチングすることにより、電極パッドに達する貫通孔を形成する。そして、貫通孔の側面に絶縁膜を形成し、絶縁膜の内側に貫通電極を形成する。以上の工程を経て、貫通電極を有する半導体装置が得られる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011−86773号公報

【特許文献2】特開2011−86850号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、貫通電極の微細化と表面電極の縮小化とを両立することができる半導体装置を提供することである。

本発明の他の目的は、表面電極の大きさに関わらず、表面電極に対して貫通電極を確実にコンタクトさせることができる半導体装置の製造方法を提供することである。

本発明のさらに他の目的は、半導体装置に貫通電極を高密度に設けることにより、小型化、大容量化および高機能化を実現することができる電子部品を提供することである。

【課題を解決するための手段】

【0006】

本発明の半導体装置は、半導体基板と、前記半導体基板の表面に選択的に形成された複数の絶縁膜リングと、前記絶縁膜リングの開口を通過して、前記半導体基板の前記表面と裏面との間を貫通する貫通電極と、前記貫通電極と前記半導体基板との間に設けられたビア絶縁膜と、前記半導体基板の前記表面の前記絶縁膜リングに対して前記表面側に離間して、前記開口に対向して形成され、前記貫通電極に電気的に接続された表面電極とを含む(請求項1)。

【0007】

この半導体装置は、半導体基板の表面に、複数の絶縁膜リングを選択的に形成する工程と、前記絶縁膜リングに対して前記半導体基板の反対側に、前記開口に対向するように表面電極を形成する工程と、前記半導体基板を裏面からエッチングすることにより、前記絶縁膜リングの前記開口を通過して前記表面電極に達する貫通孔を形成する工程と、前記貫通孔の側面にビア絶縁膜を形成する工程と、前記ビア絶縁膜が形成された前記貫通孔に電極材料を充填することにより、前記表面電極に電気的に接続されるように貫通電極を形成する工程とを含む、本発明の半導体装置の製造方法(請求項14)により製造することができる。

【0008】

この方法によれば、半導体基板の上部に表面電極を形成する位置に対向して、半導体基板の表面に開口を有する絶縁膜リングを予め形成する。そのため、当該絶縁膜リング上に表面電極を形成した後、半導体基板を裏面から表面電極へ向かってエッチングする工程において、理想のエッチング位置(絶縁膜リングの開口位置)と実際のエッチング位置との間にギャップが生じていても、エッチングが絶縁膜リングに到達した後は、絶縁膜リングと半導体基板とのエッチングレートの差を利用して(絶縁膜リングをマスクとして利用して)、当該エッチングを開口へガイドすることができる。

【0009】

そのため、当該エッチングにより形成される貫通孔のボトム部を、絶縁膜リングの開口位置に固定することができる。すなわち、半導体基板の表面の絶縁膜リングの開口に対向するように半導体基板の上部に配置された表面電極に対して、貫通孔を自己整合的に到達させることができる。その結果、貫通孔に電極材料を充填することにより、表面電極に対して貫通電極を確実にコンタクトさせることができる。

【0010】

従って、貫通孔を形成するときのパターニングの合わせ精度を考慮して、貫通孔の径よりも表面電極を常に大きく設計していた従来とは異なり、本発明によれば、表面電極の大きさに関わらず、表面電極に到達する貫通孔を正確に形成することができるので、表面電極の大きさの自由度を広げることができる。

これにより、本発明の半導体装置では、貫通電極の微細化を行なう場合に、従来に比べて表面電極を縮小化できる。その結果、貫通電極を高密度に設けることができるので、小型、大容量および高機能の半導体装置を実現することができる。

【0011】

また、表面電極の縮小化により、互いに隣り合う表面電極の間のスペースを広げることができるので、そのスペースを有効利用することができる。たとえば、配線等を当該スペースに敷設することができる。

本発明の半導体装置では、前記貫通電極は、前記開口内のボトム部と、前記開口外の本体部とを含み、前記本体部は、前記開口を区画する前記絶縁膜リングの内縁部に重なるように、前記開口に対して横方向へ張り出していることが好ましい(請求項2)。

【0012】

この構成によれば、貫通電極(本体部)の裏面側の端部に力が加わっても、本体部に重なっている絶縁膜リングが緩衝材として働くので、表面電極に伝わる力を低減することができる。その結果、たとえば、半導体装置の実装時に、表面電極がダメージを受けることを防止することができる。

この構成を有する半導体装置は、たとえば、前記半導体装置の製造方法において、前記開口を区画する前記絶縁膜リングの内縁部が前記貫通孔内に露出するように、前記開口の径よりも大きいパターン径で前記半導体基板をエッチングする工程を含む、前記貫通孔を形成する工程を実行することにより製造することができる(請求項15)。

【0013】

また、本発明の半導体装置では、表面電極の大きさの自由度を広げることができることから、前記貫通電極の前記本体部は、前記表面電極の径と同じかそれ以上の径を有していてもよい(請求項3)。言い換えれば、前記表面電極は、前記貫通電極の前記本体部の径と同じかそれ以下の径を有していてもよい。

この構成を有する半導体装置は、たとえば、前記半導体装置の製造方法において、前記表面電極の径と同じかそれ以上のパターン径で前記半導体基板をエッチングする工程を含む、前記貫通孔を形成する工程を実行することにより製造することができる(請求項16)。

【0014】

また、本発明の半導体装置では、前記絶縁膜リングの前記内縁部は、前記絶縁膜リングの外形を画成する外縁部よりも薄く形成されていてもよい(請求項4)。

また、本発明の半導体装置では、前記絶縁膜リングは、前記半導体基板の前記表面に対して前記裏面側へ埋め込まれていることが好ましい(請求項5)。

この構成によれば、絶縁膜リングの厚さ分、貫通電極の表面側の端部が裏面側に後退するので、貫通電極のアスクペクト比(貫通電極の高さ/貫通電極の径)を小さくすることができる。そのため、貫通孔に電極材料を充填するときのステップカバレッジ(段差被膜性)を向上させることができる。また、半導体基板の表面と絶縁膜リングの上面との間の段差をなくすことができるので、半導体基板の表面の平坦性を維持することもできる。

【0015】

この構成を有する半導体装置は、たとえば、前記半導体装置の製造方法において、前記半導体基板を前記表面からエッチングすることによりシャロートレンチを形成する工程と、前記シャロートレンチに絶縁材料を充填することにより、前記絶縁膜リングを前記半導体基板の前記表面に対して前記裏面側へ埋め込むように形成する工程とを含む、前記絶縁膜リングを形成する工程を実行することにより製造することができる(請求項17)。

【0016】

この方法によれば、たとえば、STI(Shallow Trench Isolation:シャロートレンチアイソレーション)工程により半導体基板に複数の素子分離領域を形成する場合に、当該STI工程と同一工程で絶縁膜リングを形成することができるので、効率よく絶縁膜リングを形成することができる。

また、本発明の半導体装置は、互いに隣り合う複数の前記表面電極の間に敷設された配線を含んでいてもよい(請求項6)。

【0017】

また、前記表面電極は、層間絶縁膜を介して積層された多層電極を含んでいてもよい(請求項7)。

また、本発明の半導体装置は、前記貫通電極との間に前記表面電極が置かれるように前記貫通電極の直上位置に配置された、外部接続用の表面バンプを含んでいてもよいし(請求項8)、前記貫通電極の前記裏面側の端部に配置された、外部接続用の裏面バンプを含んでいてもよい(請求項9)。

【0018】

また、前記絶縁膜リングは、円環状に形成されていてもよい(請求項10)。さらに、前記貫通電極は、円柱状に形成されていてもよい(請求項11)。

また、前記半導体基板の前記表面は、複数の半導体素子が形成された素子形成面を含んでいてもよい(請求項12)。

また、本発明の電子部品は、裏面に複数の外部端子を有するインタポーザと、前記インタポーザの表面に、前記表面が上方に向く姿勢で積層された請求項1〜12のいずれか一項に記載の半導体装置と、複数の裏面バンプを有し、当該裏面バンプが前記貫通電極に電気的に接続されるように前記半導体装置の前記表面に積層された第2半導体装置と、前記半導体装置および前記第2半導体装置を封止する樹脂パッケージとを含む(請求項13)。

【0019】

この構成によれば、本発明の半導体装置が搭載されているので、当該半導体装置に貫通電極を高密度に設けることにより、小型化、大容量化および高機能化を実現することができる。

【図面の簡単な説明】

【0020】

【図1】図1は、本発明の一実施形態に係る電子部品の模式的な断面図である。

【図2】図2は、図1の電子部品のシステム構成を模式的に示すブロック図である。

【図3】図3は、図1のSiインタポーザおよび演算チップにおける貫通電極のレイアウト図である。

【図4】図4は、図1の演算チップの構造を説明するための模式的な断面図であって、貫通電極が設けられた部分を拡大して示している。

【図5A】図5Aは、図4の演算チップの製造工程の一部を示す図である。

【図5B】図5Bは、図5Aの次の工程を示す図である。

【図5C】図5Cは、図5Bの次の工程を示す図である。

【図5D】図5Dは、図5Cの次の工程を示す図である。

【図5E】図5Eは、図5Dの次の工程を示す図である。

【図5F】図5Fは、図5Eの次の工程を示す図である。

【図5G】図5Gは、図5Fの次の工程を示す図である。

【図5H】図5Hは、図5Gの次の工程を示す図である。

【図5I】図5Iは、図5Hの次の工程を示す図である。

【図5J】図5Jは、図5Iの次の工程を示す図である。

【図5K】図5Kは、図5Jの次の工程を示す図である。

【図5L】図5Lは、図5Kの次の工程を示す図である。

【図5M】図5Mは、図5Lの次の工程を示す図である。

【発明を実施するための形態】

【0021】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の一実施形態に係る電子部品1の模式的な断面図である。図2は、図1の電子部品1のシステム構成を模式的に示すブロック図である。

電子部品1は、樹脂インタポーザ2と、樹脂インタポーザ2の表面3から順に積層された演算チップ4、Siインタポーザ5およびメモリチップ6と、樹脂パッケージ7とを含み、内部に電源系配線8および信号系配線9が組み込まれている。なお、演算チップ4、Siインタポーザ5およびメモリチップ6は、樹脂インタポーザ2の表面3に積層された複数の半導体装置の一例であり、これに限るものではない。

【0022】

樹脂インタポーザ2は、樹脂製(たとえば、エポキシ樹脂)基板からなり、その表面3に演算チップ4等が積層され、その裏面10に複数の外部端子11が形成されている。樹脂インタポーザ2のサイズは、14mm角であり、たとえば、10mm角〜15mm角であってもよい。樹脂インタポーザ2の厚さは、0.7mmであり、たとえば、0.6mm〜0.7mmであってもよい。

【0023】

外部端子11は、実装基板(プリント配線板)上のランド(電極)との電気接続用の端子である。外部端子11は、たとえば、半田などの金属材料を用いてボール状に形成されており、たとえば、互いに間隔を空けて行列状に配置されている。各外部端子11は、樹脂インタポーザ2の表面3と裏面10との間を貫通する導電性のビア(図示せず)を介して、演算チップ4の裏面バンプ19(後述)に電気的に接続されている。

【0024】

演算チップ4、Siインタポーザ5およびメモリチップ6は、この実施形態では、互いに同じ大きさで形成されており、互いに側面が揃うように整って積層されている。これらのチップのサイズは、10mm角であり、たとえば、6mm角〜10mm角であってもよい。樹脂インタポーザ2よりも小さく、チップの厚さは、0.05mmであり、たとえば、0.04mm〜0.06mmであってもよい。

【0025】

これら複数の半導体チップ4〜6のうち、最上層の第2半導体装置としてのメモリチップ6と樹脂インタポーザ2との間にある半導体装置としての演算チップ4には、図2に示すように、論理(Logic)・制御回路12が組み込まれている。論理・制御回路12には、電子部品1の電源系配線8および信号系配線9が接続されている。また、演算チップ4には、その表面13に当該論理・制御回路12を構成するトランジスタ(たとえばCMOSトランジスタ)、ダイオード、抵抗、キャパシタなどの複数の半導体素子が形成されている。つまり、演算チップ4では、メモリチップ6に対向する表面13が素子形成面であり、この素子形成面13が上方に向く姿勢で演算チップ4が樹脂インタポーザ2に積層されている。

【0026】

また、演算チップ4および半導体装置としてのSiインタポーザ5には、それぞれ表面13,15と裏面14,16との間を貫通する複数の貫通電極17,18が形成されており、各貫通電極17,18の裏面14,16側の端部に1つずつ裏面バンプ19,20が設けられている。裏面バンプ19,20は、たとえば、半田などの金属材料を用いてボール状に形成されている。また、演算チップ4の裏面バンプ19は、表面13上の半導体素子に電気的に接続されている。

【0027】

一方、最上層のメモリチップ6には、メモリセルアレイ21(この実施形態では、SRAM:Static Random Access Memoryのセルアレイ)および制御回路22が組み込まれており、これらの回路21,22には、電子部品1の電源系配線8および信号系配線9が接続されている。具体的には、制御回路22は電源系配線8によりメモリセルアレイ21に接続されており、メモリセルアレイ21は信号系配線9により演算チップ4の論理・制御回路12に接続されている。また、メモリチップ6には、その裏面23に当該メモリセルアレイ21および制御回路22を構成するトランジスタ、ダイオード、抵抗、キャパシタなどの複数の半導体素子が形成されている。つまり、メモリチップ6では、演算チップ4に対向する裏面23が素子形成面であり、この素子形成面23が下方に向く姿勢でメモリチップ6が樹脂インタポーザ2に積層されている。また、メモリチップ6には、その裏面23に複数の裏面バンプ24が設けられている。裏面バンプ24は、たとえば、半田などの金属材料を用いてボール状に形成されている。この裏面バンプ24は、裏面23上の半導体素子に電気的に接続されている。

【0028】

そして、メモリチップ6の裏面バンプ24は、Siインタポーザ5の貫通電極18および裏面バンプ20により中継されて、ピッチの異なる演算チップ4の貫通電極17および裏面バンプ19に電気的に接続されている。これにより、積層配置された複数の半導体チップが互いに電気的に接続され、樹脂インタポーザ2の外部端子11に電気的に接続されることとなる。

【0029】

なお、この実施形態では、演算チップ4とメモリチップ6との端子ピッチが互いに異なるので、これらの間に電気的な中継を担うSiインタポーザ5を配置しているが、当該端子ピッチが全く同じである場合には、Siインタポーザ5は省略されていてもよい。

樹脂パッケージ7(たとえば、エポキシ樹脂)は、樹脂インタポーザ2の裏面10を露出させるように、樹脂インタポーザ2の表面3側のみを封止しており、演算チップ4、Siインタポーザ5およびメモリチップ6が露出しないようにこれらのチップの全体を覆っている。また、樹脂パッケージ7は、その側面が樹脂インタポーザ2の側面と面一に揃うように形成されている。

【0030】

図3は、図1のSiインタポーザ5および演算チップ4における貫通電極17,18のレイアウト図である。

図1で示したように、この実施形態では、積層配置された複数の半導体チップ4〜6のうち、演算チップ4およびSiインタポーザ5それぞれに貫通電極17,18が設けられている。

【0031】

演算チップ4では、たとえば、複数列(この実施形態では、2列)に整列した貫通電極17が、演算チップ4の中央部25を取り囲む周縁部26に沿って環状に設けられている。なお、演算チップ4の貫通電極17は、たとえば、それぞれが不規則にランダムに配置され、全体として演算チップ4の周縁部26に沿った環状に設けられていてもよい。

これにより、演算チップ4は、貫通電極17を利用して、メモリチップ6に電力および電気信号を送ることができる。つまり、演算チップ4の貫通電極17が電子部品1の電源系配線8および信号系配線9を形成し、当該配線8,9により電力および信号が送られる。

【0032】

一方、Siインタポーザ5では、たとえば、単列の貫通電極18が、Siインタポーザ5の中央部27を取り囲む周縁部28に沿って環状に設けられているとともに(以下、これらの貫通電極18を周縁部28の貫通電極18ということがある。)、当該周縁部28に取り囲まれた中央部27に、複数の貫通電極18を1つの群として、複数の群が行列状に配置されている(以下、これらの貫通電極18を中央部27の貫通電極18ということがある。)。

【0033】

周縁部28の各貫通電極18は、この実施形態では、それぞれ演算チップ4の各貫通電極17と同一直線上に配置されるように、演算チップ4の各貫通電極17の直上に配置されている。

中央部27の貫通電極18の各群では、行列状に配置された複数の貫通電極18を1つのブロックとして、複数のブロックが設けられている。具体的には、この実施形態では、8つの群が2行4列(2×4)の行列状に配置されており、各群では、4行64列(4×64)の貫通電極18を1ブロックとして2ブロック、つまり1つの群当たり合計512個の貫通電極18が設けられている。この群が8群あるので、Siインタポーザ5全体では、4096個(512個×8群)の貫通電極18が設けられている。

【0034】

これにより、Siインタポーザ5は、たとえば、中央部27の貫通電極18を利用して、演算チップ4(たとえば、論理・制御回路12)とメモリチップ6(たとえば、メモリセルアレイ21)との間に中央部27の貫通電極18の数のビット数(この実施形態では、4096ビット)の電気信号を中継することができる。つまり、Siインタポーザ5の中央部27の貫通電極18が電子部品1の信号系配線9を形成し、当該配線9により電気信号が双方向に送受信される。なお、貫通電極18の配置や数は、本発明の一例に過ぎず、それぞれの電子部品1の設計に合わせて適宜変更することができる。たとえば、1ブロック256個の貫通電極18は、8行32列(8×32)の行列状に配置されていてもよい。

【0035】

また、Siインタポーザ5は、たとえば、周縁部28の貫通電極18を利用して、演算チップ4からメモリチップ6(たとえば、制御回路22)へと送られる電力および電気信号を中継することができる。つまり、Siインタポーザ5の周縁部28の貫通電極18が電子部品1の電源系配線8および信号系配線9を形成し、当該配線8,9により電力および電気信号が送られる。

【0036】

図4は、図1の演算チップ4の構造を説明するための模式的な断面図であって、貫通電極17が設けられた部分を拡大して示している。

演算チップ4は、演算チップ4の本体をなす半導体基板としてのSi基板29と、ゲート絶縁膜30と、層間絶縁膜31と、絶縁膜リング32と、表面電極としての表面パッド33と、パッド間配線34と、貫通電極17と、ビア絶縁膜35と、表面バンプ36と、裏面バンプ19とを含む。

【0037】

Si基板29は、たとえば、厚さ30μm〜50μmの基板であり、その表面13(素子形成面)に、ゲート絶縁膜30および複数(この実施形態では、2層)の層間絶縁膜31がこの順に積層されている。ゲート絶縁膜30は、当該表面13に形成されたトランジスタ(図示せず)が有するゲート絶縁膜30と一体な膜であり、当該トランジスタとの間で共有されている。

【0038】

また、Si基板29の表面13には、当該表面13に対して裏面14側に複数の絶縁膜リング32が選択的に埋め込まれており、当該表面13の一部が、表面13と面一に揃った絶縁膜リング32の上面により形成されている。これにより、Si基板29の表面13と絶縁膜リング32の上面との間の段差がないので、Si基板29の表面13の平坦性を維持することができる。絶縁膜リング32は、この実施形態は、酸化シリコン(SiO2)からなり、外径R1が12μm程度、内径(絶縁膜リング32の開口42の径)R2が8μm程度の円環状に形成されている。

【0039】

表面パッド33は、アルミニウム(Al)からなり、ゲート絶縁膜30、およびゲート絶縁膜30と最上層の層間絶縁膜(第2層間絶縁膜38)の間の層間絶縁膜(第1層間絶縁膜37)それぞれの上に積層された多層パッド構造を有している。

この実施形態では、表面パッド33は、2層パッド構造を有しており、ゲート絶縁膜30上に形成された下側パッド39と、第1層間絶縁膜37上に形成された上側パッド40とを含み、互いに上下に重なり合う下側パッド39と上側パッド40との間は、第1層間絶縁膜37を貫通する複数の導電性のビア41を介して電気的に接続されている。表面パッド33の層構造は、2層構造に限らず、たとえば、3層構造、4層構造、5層構造、それ以上の層構造であってもよい。また、表面パッド33の材料は、銅(Cu)などの他の金属材料であってもよい。

【0040】

表面パッド33は、各絶縁膜30,37上において、絶縁膜リング32の開口42を塞ぐように当該開口42に対向して形成されている。各表面パッド33は、絶縁膜リング32の外径R1よりも小さく、内径R2よりも大きい幅W1(たとえば、W1=10μm程度)を有する四角状に形成されており、Si基板29を裏面14側から見た底面視において絶縁膜リング32の外周よりも内側に収まっている。

【0041】

また、第1層間絶縁膜37上において、互いに隣り合う上側パッド40の間には、複数のパッド間配線34が選択的に敷設されている。パッド間配線34は、ゲート絶縁膜30上の下側パッド39の間に敷設されていてもよい。

貫通電極17は、銅(Cu)からなり、Si基板29の裏面14から当該裏面14に対して垂直に絶縁膜リング32の開口42を通過して表面パッド33(下側パッド39)に達する円柱状に形成されている。これにより、貫通電極17および表面パッド33は、Si基板29の厚さ方向に同一直線上に並んでいる。なお、貫通電極17および表面パッド33は、必ずしも同一直線上に並んでいる必要はなく、たとえば、表面パッド33は、貫通電極17のSi基板29の表面13側端部から再配線等を引き回すことにより、平面視において貫通電極17から離れた位置に配置されていてもよい。

【0042】

貫通電極17は、絶縁膜リング32の開口42内のボトム部43と、当該開口42外の本体部44とを含み、本体部44は、開口42を区画する絶縁膜リング32の内縁部45全周に重なるように、開口42に対して横方向(Si基板29の表面13に沿う方向)へ均等に張り出している。これにより、貫通電極17の本体部44は、表面パッド33の幅W1と同じかそれ以上の径R3を有している。この実施形態では、たとえば、R3=10μm程度である。

【0043】

また、絶縁膜リング32において、貫通電極17の本体部44に重なる内縁部45は、絶縁膜リング32の外形を画成する外縁部46よりも薄く形成されている。たとえば、絶縁膜リング32の内縁部45の厚さT1が0.2μm程度であり、外縁部46の厚さT2が0.4μm程度である。

ビア絶縁膜35は、酸化シリコン(SiO2)からなり、貫通電極17とSi基板29との間およびSi基板29の裏面14全域に設けられている。

【0044】

この実施形態では、ビア絶縁膜35は、貫通電極17のボトム部43の側面(周面)を覆うボトム部47、貫通電極17の本体部44の側面(周面)を覆う本体部48およびSi基板29の裏面14を覆う裏面部49を含む。ビア絶縁膜35の本体部48およびビア絶縁膜35の裏面部49は、互いに一体的に形成されている。一方、ビア絶縁膜35の本体部48とビア絶縁膜35のボトム部47との間には、絶縁膜リング32の内縁部45に沿って所定の間隔が設けられていて、これらの部分は絶縁膜リング32の内縁部45で互いに分断されている。

【0045】

また、ビア絶縁膜35は、本体部48およびボトム部47が、裏面部49に比べて薄く形成されている。たとえば、本体部48およびボトム部47の厚さが、0.5μm程度であり、裏面部49の厚さが1μm程度である。

表面バンプ36は、第2層間絶縁膜38上において、貫通電極17との間に表面パッド33が置かれるように、貫通電極17の直上位置に1つずつ配置されている。各表面バンプ36は、互いに上下に重なり合う上側パッド40に対して、第2層間絶縁膜38を貫通する導電性のビア50を介して電気的に接続されている。また、各表面バンプ36は、演算チップ4上にSiインタポーザ5を積層した状態において、たとえば、Siインタポーザ5の裏面バンプ20(図1参照)と接続される。

【0046】

裏面バンプ19は、前述のように、各貫通電極17の裏面14側の端部に1つずつ設けられている。

以上説明した絶縁膜リング32を有する演算チップ4の構成は、この実施形態では、貫通電極18が形成された半導体基板(Si基板)であるSiインタポーザ5にも採用されている。また、絶縁膜リング32を形成することにより本体部44に比べて細く形成されたボトム部43を有する貫通電極17は、電子部品1の電源系配線8および信号系配線9のいずれにも使用する必要はなく、好ましくは、配線の低抵抗化が特に必要とされない信号系配線9を形成する貫通電極17に用いる。

【0047】

図5A〜図5Mは、図4の演算チップ4の製造工程の一部を工程順に示す図である。

演算チップ4を製造するには、まず、図5Aに示すように、700μm以上の厚さを有するSi基板29を表面13からエッチングすることにより、円環状のシャロートレンチ51を選択的に形成し、当該シャロートレンチ51にCVD法によりSiO2(絶縁材料)を充填する。これにより、Si基板29に埋め込まれた絶縁膜リング32(外径R1=12μm、内径R2=8μm)が形成される。この絶縁膜リング32を形成する工程は、たとえば、STI(Shallow Trench Isolation:シャロートレンチアイソレーション)工程によりSi基板29に複数の素子分離領域を形成する工程と同一工程で行うことができるので、効率よく絶縁膜リング32を形成することができる。

【0048】

その後、図示は省略するが、公知の方法により、Si基板29の表面13に対してイオン注入(たとえば、n型イオン、p型イオン)することにより、半導体素子を構成する不純物領域が形成される。

次に、図5Bに示すように、熱酸化法によりゲート絶縁膜30を形成する。その後、スパッタ、フォトリソグラフィ、CVD等の公知の半導体装置の製造技術により、ゲート絶縁膜30上に、下側パッド39、第1層間絶縁膜37、ビア41、上側パッド40およびパッド間配線34、第2層間絶縁膜38、ビア50および表面バンプ36を順に形成する。

【0049】

次に、図5Cに示すように、Si基板29の表面13側に、接着剤52を介してガラス基板53(支持体)を貼り付ける。

次に、図5Dに示すように、たとえば、グラインダなどを用いて、Si基板29を裏面14側から研削して(バックグラインド)、Si基板29を薄化する。この実施形態では、700μm以上のSi基板29が30μm〜50μmになるまで研削する。

【0050】

次に、図5Eに示すように、絶縁膜リング32の開口42を基準に位置合わせをして、Si基板29の裏面14に、貫通電極17を形成すべき領域に本体部44と同じ径R3(R3≧表面パッド33の幅W1、絶縁膜リング32の内径R2)の開口55を有するフォトレジスト54(たとえば、ポリイミド等の有機レジスト)を形成する。

次に、図5Fに示すように、フォトレジスト54を介してSi基板29にエッチングガス(たとえば、SF6/O2など)を供給して、Si基板29を裏面14側からドライエッチングする。このエッチングは、絶縁膜リング32に到達した後、絶縁膜リング32(SiO2)とSi基板29とのエッチングレートの差を利用して(絶縁膜リング32をマスクとして利用して)絶縁膜リング32の開口42へガイドされる。そして、絶縁膜リング32の開口42を通過してゲート絶縁膜30が露出するまで、エッチングガスの種類を代えずに同一のガス種でエッチングを続ける。これにより、Si基板29に貫通孔56が形成され、各貫通孔56内には、絶縁膜リング32の内縁部45が露出することとなる。

【0051】

次に、図5Gに示すように、貫通孔56を形成したときのフォトレジスト54を残した状態で、貫通孔56の底面を形成するゲート絶縁膜30をエッチングすることにより、貫通孔56内に表面パッド33(下側パッド39)を露出させる。この際、ゲート絶縁膜30と同一材料(SiO2)からなる絶縁膜リング32のうち、貫通孔56の側面よりも内側の内縁部45もエッチングガスに晒されるので、ゲート絶縁膜30と同時にエッチングされる。これにより、絶縁膜リング32の内縁部45と外縁部46との間に段差(厚さの差)が生じる。

【0052】

次に、図5Hに示すように、フォトレジスト54を除去した後、CVD法により、貫通孔56内に露出している表面パッド33が覆われるように、貫通孔56の内面およびSi基板29の裏面14にビア絶縁膜35を形成する。

次に、図5Iに示すように、エッチバックにより、ビア絶縁膜35における貫通孔56の開口端に臨む部分、具体的には、表面パッド33上の部分(底面部分)および絶縁膜リング32の内縁部45上の部分を選択的に除去する。これにより、貫通孔56内に表面パッド33(下側パッド39)が再度露出する。

【0053】

次に、図5Jに示すように、ビア絶縁膜35の表面にシード膜(たとえば、Ti/Cuの積層膜)をスパッタした後、電解めっきにより、当該シード膜からCuをめっき成長させる。これにより、貫通孔56におけるビア絶縁膜35の内側にCu(電極材料)が充填され、表面パッド33に電気的に接続された貫通電極17が形成される。

次に、図5Kに示すように、研磨面がビア絶縁膜35の裏面部49と面一に揃うまで、貫通電極17の余分な部分(貫通孔56外の部分)をCMP(Chemical Mechanical Polishing)法により研磨して除去する。

【0054】

その後、図5Lに示すように、各貫通電極17に1つずつ裏面バンプ19を形成し、図5Mに示すように、Si基板29をガラス基板53から取り外すことにより、図4の演算チップ4が得られる。

以上、この実施形態の方法によれば、図5Aに示すように、表面パッド33の位置に対向する開口42を有する絶縁膜リング32を予め形成する。そのため、当該絶縁膜リング32上に表面パッド33を形成した後、Si基板29を裏面14から表面パッド33へ向かってエッチングする図5Fの工程において、理想のエッチング位置(絶縁膜リング32の開口42の位置)と実際のエッチング位置との間にギャップが生じていても、ドライエッチングが絶縁膜リング32に到達した後は、絶縁膜リング32(SiO2)とSi基板29とのエッチングレートの差を利用して(絶縁膜リング32をマスクとして利用して)、当該エッチングを開口42へガイドすることができる。

【0055】

そのため、当該エッチングにより形成される貫通孔56のボトム部を、絶縁膜リング32の開口42位置に固定するとともに、表面パッド33の幅W1よりも細くすることができる。すなわち、絶縁膜リング32の開口42に対向するように配置された表面パッド33に対して、貫通孔56を自己整合的に到達させることができる。その結果、貫通孔56にCuをめっき成長させることにより、表面パッド33に対して貫通電極17を確実にコンタクトさせることができる。

【0056】

従って、貫通孔56を形成するときのパターニングの合わせ精度を考慮して、貫通孔56の径R3よりも表面パッド33を常に大きく設計していた従来とは異なり、この実施形態によれば、表面パッド33の大きさ(幅W1)に関わらず、表面パッド33に到達する貫通孔56を正確に形成することができる。よって、表面パッド33の大きさの自由度を広げることができる。

【0057】

これにより、演算チップ4では、貫通電極17の微細化を行なう場合に、従来に比べて表面パッド33を縮小化できる。その結果、貫通電極17を高密度に設けることができるので、小型、大容量および高機能の半導体チップを実現することができる。

また、表面パッド33の縮小化により、互いに隣り合う表面パッド33の間のスペースを広げることができるので、そのスペースを有効利用して、パッド間配線34を敷設することができる。

【0058】

なお、この実施形態の方法では、貫通電極17のボトム部43を固定する絶縁膜リング32を表面パッド33に対して精密に位置合わせする必要があるが、絶縁膜リング32と表面パッド33とはゲート絶縁膜30の厚さ程度しか離れていないので、公知の方法でも精密に位置合わせすることができる。

また、演算チップ4によれば、裏面バンプ19を介して貫通電極17(本体部44)の裏面14側の端部に力が加わっても、本体部44に重なっている絶縁膜リング32(内縁部45)が緩衝材として働くので、表面パッド33に伝わる力を低減することができる。その結果、たとえば、演算チップ4を樹脂インタポーザ2に実装する時に、表面パッド33がダメージを受けることを防止することができる。

【0059】

また、演算チップ4によれば、絶縁膜リング32の内縁部45の厚さT1分、貫通電極17(本体部44)の表面13側の端部が裏面14側に後退しているので、貫通電極17のアスクペクト比(貫通電極17の高さ/貫通電極17の径R3)を小さくすることができる。そのため、貫通孔56に電極材料を充填するときのステップカバレッジ(段差被膜性)を向上させることができる。

【0060】

また、演算チップ4によれば、貫通電極17とSi基板29との間のリーク電流も防止することができる。

すなわち、図5Iの工程において、表面パッド33を露出させるためにビア絶縁膜35の底面部分をエッチバックにより除去することになるが、貫通孔56の内面のビア絶縁膜35(本体部48およびボトム部47)をそれほど厚いものではない。そのため、エッチバックの際、貫通孔56のボトム部の側面に形成されたビア絶縁膜35も一緒に除去されてしまうおそれがある。

【0061】

そこで、この実施形態では、たとえ貫通孔56のボトム部側面のビア絶縁膜35が除去されてしまっても、その周りに絶縁膜リング32が存在しているので、貫通電極17とSi基板29との絶縁状態を保持することができる。その結果、貫通電極17とSi基板29との間のリーク電流を防止することができる。

そして、図1の電子部品1によれば、上記した演算チップ4およびSiインタポーザ5が搭載されているので、演算チップ4およびSiインタポーザ5に貫通電極17を高密度に設けることにより、小型化、大容量化および高機能化を実現することができる。

【0062】

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

たとえば、貫通電極17は、楕円柱状、四角柱状、六角柱状、八角柱状であってもよく、絶縁膜リング32も、楕円環状、四角環状、六角環状、八角環状であってもよい。

また、図5Jの工程において、貫通電極17は、CVD法を用いてポリシリコンを貫通孔56に充填することにより形成することができる。ただし、その場合にはSi基板29およびガラス基板53が高温に晒されるので、接着剤52が溶けないように対策を施す必要がある。つまり、接着剤52の耐熱温度が比較的低温(200℃程度)である場合には、前述の実施形態のように、電解めっき法を採用することが好ましい。

【0063】

また、図5Aの工程において、絶縁膜リング32を形成する工程は、Si基板29に素子分離領域を形成するSTI工程と同一工程で行ったが、独立して行ってもよい。また、絶縁膜リング32を形成する工程は、Si基板29の表面13に熱酸化により絶縁膜を形成する工程と、当該絶縁膜をパターニングすることにより、Si基板29の表面13に対して突出するように絶縁膜リング32を形成する工程とを含んでいてもよい。

【0064】

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0065】

1 電子部品

2 樹脂インタポーザ

3 (樹脂インタポーザの)表面

4 演算チップ

5 Siインタポーザ

6 メモリチップ

7 樹脂パッケージ

8 電源系配線

9 信号系配線

10 (樹脂インタポーザの)裏面

11 外部端子

12 論理・制御回路

13 (演算チップの)表面

14 (演算チップの)裏面

15 (Siインタポーザの)表面

16 (Siインタポーザの)裏面

17 (演算チップの)貫通電極

18 (Siインタポーザの)貫通電極

19 (演算チップの)裏面バンプ

20 (Siインタポーザの)裏面バンプ

21 メモリセルアレイ

22 制御回路

23 (メモリチップの)裏面

24 (メモリチップの)裏面バンプ

25 (演算チップの)中央部

26 (演算チップの)周縁部

27 (Siインタポーザの)中央部

28 (Siインタポーザの)周縁部

29 Si基板

30 ゲート絶縁膜

31 層間絶縁膜

32 絶縁膜リング

33 表面パッド

34 パッド間配線

35 ビア絶縁膜

36 表面バンプ

37 第1層間絶縁膜

38 第2層間絶縁膜

39 下側パッド

40 上側パッド

41 ビア

42 (絶縁膜リングの)開口

43 (貫通電極の)ボトム部

44 (貫通電極の)本体部

45 (絶縁膜リングの)内縁部

46 (絶縁膜リングの)外縁部

47 (ビア絶縁膜の)ボトム部

48 (ビア絶縁膜の)本体部

49 (ビア絶縁膜の)裏面部

50 ビア

51 シャロートレンチ

52 接着剤

53 ガラス基板

54 フォトレジスト

55 (フォトレジストの)開口

56 貫通孔

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板の表面に選択的に形成された複数の絶縁膜リングと、

前記絶縁膜リングの開口を通過して、前記半導体基板の前記表面と裏面との間を貫通する貫通電極と、

前記貫通電極と前記半導体基板との間に設けられたビア絶縁膜と、

前記半導体基板の前記表面の前記絶縁膜リングに対して前記表面側に離間して、前記開口に対向して形成され、前記貫通電極に電気的に接続された表面電極とを含む、半導体装置。

【請求項2】

前記貫通電極は、前記開口内のボトム部と、前記開口外の本体部とを含み、

前記本体部は、前記開口を区画する前記絶縁膜リングの内縁部に重なるように、前記開口に対して横方向へ張り出している、請求項1または2に記載の半導体装置。

【請求項3】

前記貫通電極の前記本体部は、前記表面電極の径と同じかそれ以上の径を有している、請求項2に記載の半導体装置。

【請求項4】

前記絶縁膜リングの前記内縁部は、前記絶縁膜リングの外形を画成する外縁部よりも薄く形成されている、請求項2または3に記載の半導体装置。

【請求項5】

前記絶縁膜リングは、前記半導体基板の前記表面に対して前記裏面側へ埋め込まれている、請求項1〜4のいずれか一項に記載の半導体装置。

【請求項6】

前記半導体装置は、互いに隣り合う複数の前記表面電極の間に敷設された配線を含む、請求項1〜5のいずれか一項に記載の半導体装置。

【請求項7】

前記表面電極は、層間絶縁膜を介して積層された多層電極を含む、請求項1〜6のいずれか一項に記載の半導体装置。

【請求項8】

前記半導体装置は、前記貫通電極との間に前記表面電極が置かれるように前記貫通電極の直上位置に配置された、外部接続用の表面バンプを含む、請求項1〜7のいずれか一項に記載の半導体装置。

【請求項9】

前記半導体装置は、前記貫通電極の前記裏面側の端部に配置された、外部接続用の裏面バンプを含む、請求項1〜8のいずれか一項に記載の半導体装置。

【請求項10】

前記絶縁膜リングは、円環状に形成されている、請求項1〜9のいずれか一項に記載の半導体装置。

【請求項11】

前記貫通電極は、円柱状に形成されている、請求項1〜10のいずれか一項に記載の半導体装置。

【請求項12】

前記半導体基板の前記表面は、複数の半導体素子が形成された素子形成面を含む、請求項1〜11のいずれか一項に記載の半導体装置。

【請求項13】

裏面に複数の外部端子を有するインタポーザと、

前記インタポーザの表面に、前記表面が上方に向く姿勢で積層された請求項1〜12のいずれか一項に記載の半導体装置と、

複数の裏面バンプを有し、当該裏面バンプが前記貫通電極に電気的に接続されるように前記半導体装置の前記表面に積層された第2半導体装置と、

前記半導体装置および前記第2半導体装置を封止する樹脂パッケージとを含む、電子部品。

【請求項14】

半導体基板の表面に、複数の絶縁膜リングを選択的に形成する工程と、

前記絶縁膜リングに対して前記半導体基板の反対側に、前記開口に対向するように表面電極を形成する工程と、

前記半導体基板を裏面からエッチングすることにより、前記絶縁膜リングの前記開口を通過して前記表面電極に達する貫通孔を形成する工程と、

前記貫通孔の側面にビア絶縁膜を形成する工程と、

前記ビア絶縁膜が形成された前記貫通孔に電極材料を充填することにより、前記表面電極に電気的に接続されるように貫通電極を形成する工程とを含む、半導体装置の製造方法。

【請求項15】

前記貫通孔を形成する工程は、前記開口を区画する前記絶縁膜リングの内縁部が前記貫通孔内に露出するように、前記開口の径よりも大きいパターン径で前記半導体基板をエッチングする工程を含む、請求項14に記載の半導体装置の製造方法。

【請求項16】

前記貫通孔を形成する工程は、前記表面電極の径と同じかそれ以上のパターン径で前記半導体基板をエッチングする工程を含む、請求項14または15に記載の半導体装置の製造方法。

【請求項17】

前記絶縁膜リングを形成する工程は、前記半導体基板を前記表面からエッチングすることによりシャロートレンチを形成する工程と、前記シャロートレンチに絶縁材料を充填することにより、前記絶縁膜リングを前記半導体基板の前記表面に対して前記裏面側へ埋め込むように形成する工程とを含む、請求項14〜16のいずれか一項に記載の半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板の表面に選択的に形成された複数の絶縁膜リングと、

前記絶縁膜リングの開口を通過して、前記半導体基板の前記表面と裏面との間を貫通する貫通電極と、

前記貫通電極と前記半導体基板との間に設けられたビア絶縁膜と、

前記半導体基板の前記表面の前記絶縁膜リングに対して前記表面側に離間して、前記開口に対向して形成され、前記貫通電極に電気的に接続された表面電極とを含む、半導体装置。

【請求項2】

前記貫通電極は、前記開口内のボトム部と、前記開口外の本体部とを含み、

前記本体部は、前記開口を区画する前記絶縁膜リングの内縁部に重なるように、前記開口に対して横方向へ張り出している、請求項1または2に記載の半導体装置。

【請求項3】

前記貫通電極の前記本体部は、前記表面電極の径と同じかそれ以上の径を有している、請求項2に記載の半導体装置。

【請求項4】

前記絶縁膜リングの前記内縁部は、前記絶縁膜リングの外形を画成する外縁部よりも薄く形成されている、請求項2または3に記載の半導体装置。

【請求項5】

前記絶縁膜リングは、前記半導体基板の前記表面に対して前記裏面側へ埋め込まれている、請求項1〜4のいずれか一項に記載の半導体装置。

【請求項6】

前記半導体装置は、互いに隣り合う複数の前記表面電極の間に敷設された配線を含む、請求項1〜5のいずれか一項に記載の半導体装置。

【請求項7】

前記表面電極は、層間絶縁膜を介して積層された多層電極を含む、請求項1〜6のいずれか一項に記載の半導体装置。

【請求項8】

前記半導体装置は、前記貫通電極との間に前記表面電極が置かれるように前記貫通電極の直上位置に配置された、外部接続用の表面バンプを含む、請求項1〜7のいずれか一項に記載の半導体装置。

【請求項9】

前記半導体装置は、前記貫通電極の前記裏面側の端部に配置された、外部接続用の裏面バンプを含む、請求項1〜8のいずれか一項に記載の半導体装置。

【請求項10】

前記絶縁膜リングは、円環状に形成されている、請求項1〜9のいずれか一項に記載の半導体装置。

【請求項11】

前記貫通電極は、円柱状に形成されている、請求項1〜10のいずれか一項に記載の半導体装置。

【請求項12】

前記半導体基板の前記表面は、複数の半導体素子が形成された素子形成面を含む、請求項1〜11のいずれか一項に記載の半導体装置。

【請求項13】

裏面に複数の外部端子を有するインタポーザと、

前記インタポーザの表面に、前記表面が上方に向く姿勢で積層された請求項1〜12のいずれか一項に記載の半導体装置と、

複数の裏面バンプを有し、当該裏面バンプが前記貫通電極に電気的に接続されるように前記半導体装置の前記表面に積層された第2半導体装置と、

前記半導体装置および前記第2半導体装置を封止する樹脂パッケージとを含む、電子部品。

【請求項14】

半導体基板の表面に、複数の絶縁膜リングを選択的に形成する工程と、

前記絶縁膜リングに対して前記半導体基板の反対側に、前記開口に対向するように表面電極を形成する工程と、

前記半導体基板を裏面からエッチングすることにより、前記絶縁膜リングの前記開口を通過して前記表面電極に達する貫通孔を形成する工程と、

前記貫通孔の側面にビア絶縁膜を形成する工程と、

前記ビア絶縁膜が形成された前記貫通孔に電極材料を充填することにより、前記表面電極に電気的に接続されるように貫通電極を形成する工程とを含む、半導体装置の製造方法。

【請求項15】

前記貫通孔を形成する工程は、前記開口を区画する前記絶縁膜リングの内縁部が前記貫通孔内に露出するように、前記開口の径よりも大きいパターン径で前記半導体基板をエッチングする工程を含む、請求項14に記載の半導体装置の製造方法。

【請求項16】

前記貫通孔を形成する工程は、前記表面電極の径と同じかそれ以上のパターン径で前記半導体基板をエッチングする工程を含む、請求項14または15に記載の半導体装置の製造方法。

【請求項17】

前記絶縁膜リングを形成する工程は、前記半導体基板を前記表面からエッチングすることによりシャロートレンチを形成する工程と、前記シャロートレンチに絶縁材料を充填することにより、前記絶縁膜リングを前記半導体基板の前記表面に対して前記裏面側へ埋め込むように形成する工程とを含む、請求項14〜16のいずれか一項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図5G】

【図5H】

【図5I】

【図5J】

【図5K】

【図5L】

【図5M】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図5G】

【図5H】

【図5I】

【図5J】

【図5K】

【図5L】

【図5M】

【公開番号】特開2013−105956(P2013−105956A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−249938(P2011−249938)

【出願日】平成23年11月15日(2011.11.15)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構、立体構造新機能集積回路(ドリームチップ)技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月15日(2011.11.15)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構、立体構造新機能集積回路(ドリームチップ)技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]