半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、半導体装置およびその製造方法ならびにこれを用いた表示装置および電子機器に関する。

【背景技術】

【0002】

近年、さまざまな薄膜トランジスタを集積形成した表示装置等の半導体装置が製造されている。このような半導体装置の例としては、例えば特許文献1では、以下の構成を有するボトムゲート型の薄膜トランジスタを備えた半導体装置が開示されている。その構成は、基板上にゲート配線や補助容量配線等の下側配線と、この下側配線と同電位で且つ同時にパターニングされたゲート電極とが形成され、この上にゲート絶縁膜、薄膜トランジスタの素子領域を構成する半導体層、層間絶縁膜および層間絶縁膜に形成されたコンタクトホールを介して薄膜トランジスタに接続する信号配線等の上側配線が順に積層されている。

【0003】

このように、ゲート電極上にゲート絶縁膜を介して半導体層が形成された薄膜トランジスタでは、半導体層はその多結晶化工程においてレーザ照射を用いることからゲート電極およびゲート配線には高融点金属が用いられる。また、半導体層は効率的に加熱することによって良好な多結晶構造が得られるため、ゲート電極は排熱効果を制御するために膜厚を薄く形成する必要がある。一方、ゲート配線はゲートパルスの伝達遅延を緩和するために膜厚を厚く形成する必要がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開20010177103号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、基板上に膜厚の大きな金属膜を形成すると、その膜応力によって基板の反り量が大きくなる。このため、例えばフォトリソグラフィ工程では合わせずれ、基板運搬時には基板吸着異常等の問題が生じていた。この問題は、例えば表示装置のパネルの大型化や高精細化によって配線密度が高くなることで更に顕著となり、基板の薄板化および大型化に対して問題となっていた。

【0006】

本技術はかかる問題点に鑑みてなされたもので、その目的は、配線層の膜応力を低減し、製造歩留まりを向上させることが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供することにある。

【課題を解決するための手段】

【0007】

本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えたものである。

【0008】

本技術の半導体装置の製造方法は、以下の(A)〜(H)の工程を含むものである。

(A)一方向に延在する金属膜を成膜する工程

(B)金属膜をエッチングすることによって複数の第1配線層を形成する工程

(C)第1配線層の間に前記第1配線層より膜厚の薄いゲート電極を形成する工程

(D)第1配線層およびゲート電極上に絶縁膜を形成する工程

(E)絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層を形成する工程

(F)半導体層上に層間膜を形成する工程

(G)層間膜に貫通孔を形成する工程

(H)層間膜上に、貫通孔を介して半導体層と接続される第2配線層を形成する工程

【0009】

本技術の表示装置および電子機器は、表示素子と、上記半導体装置とを備えたものである。

【0010】

本技術の半導体装置およびその製造方法ならびに表示装置および電子機器では、一方向に延在する金属膜を形成したのちエッチングすることで複数の第1配線層を設け、この第1配線層間に第1配線層よりも膜厚の薄いゲート電極を形成するようにした。これにより、第1配線層による基板への膜応力を緩和することが可能となる。

【発明の効果】

【0011】

本技術の半導体装置およびその製造方法ならびに表示装置および電子機器によれば、一方向に延在する複数の第1配線層を設け、その第1配線層間に、第1配線層よりも膜厚の薄いゲート電極を設けるようにした。よって、第1配線層による基板への膜応力が緩和され、製造歩留まりを向上することが可能となる。

【図面の簡単な説明】

【0012】

【図1】本開示の第1の実施の形態に係る表示装置の一例を表す断面図である。

【図2】図1に示した表示装置を構成する半導体装置の平面図である。

【図3】本開示の第1の実施の形態に係る表示装置の他の例を表す断面図である。

【図4A】図1に示した表示装置の製造方法を工程順に表す図である。

【図4B】図4Aに続く工程を表す図である。

【図4C】図4Bに続く工程を表す図である。

【図4D】図4Cに続く工程を表す図である。

【図4E】図4Dに続く工程を表す図である。

【図4F】図4Eに続く工程を表す図である。

【図4G】図4Fに続く工程を表す図である。

【図4H】図4Gに続く工程を表す図である。

【図4I】図4Hに続く工程を表す図である。

【図4J】図4Iに続く工程を表す図である。

【図5】本開示の比較例に係る表示装置の断面図である。

【図6】図5に示した表示装置を構成する半導体装置の平面図である。

【図7】本開示の第2の実施の形態に係る表示装置の断面図である。

【図8】図7に示した表示装置を構成する半導体装置の平面図である。

【図9A】図1に示した表示装置の製造方法を工程順に表す図である。

【図9B】図9Aに続く工程を表す図である。

【図9C】図9Bに続く工程を表す図である。

【図9D】図9Cに続く工程を表す図である。

【図9E】図9Dに続く工程を表す図である。

【図9F】図9Eに続く工程を表す図である。

【図9G】図9Fに続く工程を表す図である。

【図9H】図9Gに続く工程を表す図である。

【図9I】図9Hに続く工程を表す図である。

【図10】図1に示した表示装置を含むモジュールの概略構成を表す平面図である。

【図11】図10に示した表示装置の適用例1の外観を表す斜視図である。

【図12】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図13】適用例3の外観を表す斜視図である。

【図14】適用例4の外観を表す斜視図である。

【図15】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【発明を実施するための形態】

【0013】

以下、本開示の実施の形態について図面を参照して詳細に説明する。尚、説明は以下の順序で行う。

1.第1の実施の形態(FSSモードの表示装置)

2.第2の実施の形態(VAモードの表示装置)

3.適用例(表示装置および電子機器の例)

【0014】

<第1の実施の形態>

[半導体装置1の構成]

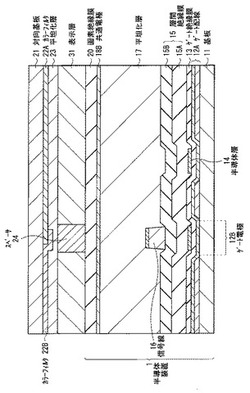

図1は、本開示の第1の実施の形態に係る表示装置の断面構成を表したものであり、図2はこの表示装置を構成する半導体装置1の平面構成を表したものである。なお、図1は図2のI−I’一点鎖線における断面図である。半導体装置1は、スイッチング素子として、いわゆるボトムゲート型(逆スタガー構造)の薄膜トランジスタ(Thin Film Transistor;TFT)を有する。この半導体装置1では、ガラス等の基板11上にゲート電極12Bおよびゲート配線(第1配線)12Aが形成されている。ゲート電極12B上には、ゲート絶縁膜(絶縁膜)13、半導体層14、層間絶縁膜(層間膜)15(15A,15B)、信号線16が順に設けられた薄膜トランジスタが形成されている。薄膜トランジスタ上には平坦化層17が順に設けられており、この平坦化層17上に画素電極(第2配線層)18Aおよび共通電極18Bが形成されている。本実施の形態では、ゲート配線12Aと、ゲート配線12Aよりも膜厚の薄いゲート電極12Bとが一方向に交互に形成されている。

【0015】

ゲート電極12Bは、薄膜トランジスタに印加されるゲート電圧によって半導体層14中のキャリア密度(ここでは、電子密度)を制御する役割を果たすものである。ゲート配線12Aは基板11上に複数設けられたゲート電極12Bを電気的に接続するためのものである。ゲート配線12Aおよびゲート電極12Bは、例えばクロム(Cr),モリブデン(Mo),タンタル(Ta),タングステン(W),チタン(Ti)等の高融点金属(例えば、融点1500℃〜3500℃)によって形成されている。

【0016】

ゲート電極12Bはゲート配線12Aの膜厚と比較して薄く、ゲート配線12Aとゲート電極12Bとの膜厚比は、例えば2:1以上6:1以下の範囲で形成されることが好ましい。具体的には、ゲート配線12Aは例えば、60〜540nm、ゲート電極12Bは例えば30〜90nmの膜厚で形成されている。このようにゲート配線12Aはゲート電極12Bよりも膜厚が厚く、特に上記高融点金属を用いた場合にはその膜応力は高くなり、基板11の反り量が大きくなるという問題があった。これに対して、本実施の形態では、詳細は後述するが、基板上11にゲート配線12Aとなる金属膜を成膜したのち、少なくとも一部をエッチング等により除去して金属膜を分割、即ちアイランド上に形成し、これによって形成された金属層(ゲート配線12A)の間にゲート電極12Bを形成する。即ち、ゲート配線12Aとゲート電極12Bとが交互に延在するように配置される。これにより、ゲート配線12Aの応力が緩和され、基板11の反り量が低減される。なお、図1ではゲート配線12Aは、基板11上に直接成膜された金属膜と、ゲート電極12Bのゲート配線12A上に形成された2層構造としたが、これに限らず、図3のようにゲート配線12Aおよびゲート電極12を1層からなる金属膜で形成し、この金属膜の適当な位置で膜厚の一部をエッチングしてこの薄膜部分をゲート電極12Bとするようにしてもよい。

【0017】

ゲート絶縁膜13は、シリコン酸化膜,シリコン窒化膜,シリコン窒化酸化膜および酸化アルミニウム膜等のうちの1種よりなる単層膜、またはこれらのうちの2種以上よりなる積層膜である。ゲート絶縁膜13の厚みは、例えば100nm〜300nmである。

【0018】

半導体層14は、アモルファスシリコンによって構成されている。この半導体層14は、ゲート電圧の印加によりソース・ドレイン電極19A,19B(図2参照)間にチャネルを形成するものであり、半導体層14の厚みは、例えば5nm〜100nmである。なお、半導体層14の材料としては、アモルファスシリコンの他に、例えばインジウム(In),ガリウム(Ga),亜鉛(Zn),スズ(Sn),Al,チタン(Ti)のうち少なくとも1種の元素の酸化物を用いてもよい。

【0019】

層間絶縁膜15(15A,15B)は、半導体層14上に形成され、ソース・ドレイン電極19A,19B形成時におけるチャネルの損傷を防止するためのものである。層間絶縁膜15の厚みは、例えば10〜300nmである。この層間絶縁膜15は半導体層層14への水分等の供給が少ないことが望ましい。層間絶縁膜15は、例えば、シリコン酸化膜,シリコン窒化膜,シリコン酸窒化膜あるいは酸化アルミニウム膜、またはこれらの積層膜により構成されている。

【0020】

ソース・ドレイン電極19A,19Bは、図2に示したように、層間絶縁膜15を介して半導体層14上に形成されている。ソース・ドレイン電極19A,19Bの材料としては、例えばCr,Mo,Al,銅(Cu),Ti,Ta,W,ITO(インジウム錫酸化物)および酸化チタン等のうち1種よりなる単層膜またはこれらのうちの2種以上よりなる積層膜である。例えば、Mo/Al/Moの順に、例えば50nm、500nm、50nmの膜厚で積層した3層膜や、ITOおよび酸化チタン等の酸素を含む金属化合物のような酸素との結びつきの弱い金属または金属化合物を用いることが望ましい。これにより、半導体層14を酸化物半導体で形成した際の電気特性を安定して保持することができる。逆に、ソース・ドレイン電極19A,19Bを酸素との結びつきが強い金属で構成した場合には、ソース・ドレイン電極19A,19Bは、酸化物半導体に接触して形成されるため、酸化物半導体中の酸素が引き抜かれて酸素欠陥を生じ、電気特性が悪化してしまう。なお、信号線16,共通電極18Bについても、ソース・ドレイン電極19A,19Bと同様の材料を用いることができる。

【0021】

平坦化層17は、例えば酸化アルミニウム膜またはシリコン酸化膜等の単層膜、もしくは酸化アルミニウム膜とシリコン酸化膜との積層膜により構成されている。この平坦化層17の厚みは、例えば10nm〜100nmであり、好ましくは50nm以下である。

【0022】

[半導体装置1の製造方法]

図4A〜図4Jは、半導体装置1の製造方法を説明するための図である。半導体装置1は、例えば次のようにして製造することができる。

【0023】

まず、図4Aに示したように、基板11上の全面にスパッタリング法や蒸着法により金属膜を例えば200nmの厚さで形成したのち、この金属膜を、例えばフォトリソグラフィ法を用いてパターニングすることにより、アイランド上の配線パターン(複数のゲート配線12A)を形成する。続いて、図4Bに示したように、基板11およびゲート配線12A上の全面に金属膜を例えば50nmの厚さで成膜したのち、例えばフォトリソグラフィ法を用いてパターニングすることによりゲート配線12Aの間およびゲート配線12A上に延在するゲート電極12Bを形成する。次に、図4Cに示したように、基板11,ゲート配線12Aおよびゲート電極12B上を覆うように、ゲート絶縁膜13をプラズマCVD法を用いて例えば50nmの厚さで形成する。具体的には、例えば原料ガスとしてシラン(SiH4)、アンモニア(NH3)、窒素を含む混合ガスを用いたプラズマCVD法により、シリコン窒化膜よりなるゲート絶縁膜13を成膜する。

【0024】

続いて、図4Dに示したように、半導体層14となるアモルファスシリコン層を、例えばプラズマCVD法を用いて50nmの膜厚で形成する。そののち、アモルファスシリコン層をエキシマレーザやランプアニール、半導体レーザアニールなどにより結晶化する。このとき、薄膜トランジスタのゲート電極12Bは、50nmと薄く形成されているため、必要な結晶化エネルギーが極端に高くなることはない。結晶化エネルギーに影響を与えず、且つ、ゲート配線の低抵抗化が実現できる。次に、不純物領域を形成するが、LDD領域については形成してもしなくても構わない。続いて、ソース・ドレイン領域を形成するために、N型もしくはP型となる不純物をイオンドーピングまたはイオンインプランテーションにより半導体層14のソース・ドレイン領域にドープする。

【0025】

次いで、図4Eに示したように、アモルファスシリコン層を例えばフォトリソグラフィによってトランジスタの形状に形成する。続いて、図4Fに示したように、薄膜トランジスタと信号線16とを分離するための層間絶縁膜15A,15Bを形成する。具体的には、プラズマCVD法によって、例えば窒化シリコン膜を300nm(15A)、酸化シリコン膜(15B)をそれぞれ300nmの膜厚で成膜する。次いで、後に形成する信号線16の信号を、例えばフォトリソグラフィを用いて半導体層14へ伝達するためのコンタクトホールPC,DCを形成する。

【0026】

続いて、図4Gに示したように、各画素に信号電位を入力するための金属膜を、例えばスパッタ法を用いて成膜したのち、フォトリソグラフィにより配線状(信号線16)に形成する。次に、図4Hに示したように、後に形成する共通電極18Bと信号線16とが短絡しないように、且つ、表面を平坦化するための層間絶縁膜15A,15Bを形成する。具体的には、例えば感光性のアクリル樹脂を基板11上の全面に塗布したのち、フォトリソグラフィにて露光する。この露光された部分のアクリル樹脂を現像にて除去することにより、画素電極18Aと薄膜トランジスタとを接続するためのコンタクトホール(PLNC)を形成する。

【0027】

続いて、図4Iに示したように、共通電極18Bを例えば酸化インジウムスズにて形成する。このとき、薄膜トランジスタの後述する画素電極18Aと共通電極18Bとが短絡しないように、先に開けたコンタクトホールPLNCよりも大きく共通電極コンタクトホールCMCを開ける。次いで、画素電極18Aから共通電極18Bへ電界をかけるための誘電膜となる画素絶縁膜20を、例えば窒化シリコン膜や酸化シリコン膜などを用い、プラズマCVDにより成膜する。続いて、フォトリソグラフィにて、薄膜トランジスタと画素電極18Aとを導通するためのコンタクトホールPILCを、コンタクトホールPLNC上で且つコンタクトホールCMCの内側にくるように形成することで画素電極18Aと共通電極18Bとの短絡を紡糸する。次に、画素電極18Aをスパッタ法およびフォトリソグラフィ法により任意の形状に形成する。画素電極18Aは、共通電極18Bとの間で電界を形成するため、例えば図2に示したように短冊状の隙間を複数形成する。

【0028】

続いて、対向基板21側に例えば赤色または緑色等のカラーフィルタ24A,24B等を形成する。まず、対向基板21上に、例えばネガ型レジストを使用して赤のカラーレジストを塗布したのち、フォトリソグラフィにて露光、現像する。以下、緑、青と同様に任意の画素を形成していく。そして、各カラーレジストの重なり部分にできる凹凸を平坦化するため、平坦化材を対向基板21全面に塗布し平坦化層23を形成する。続いて、例えばポジ形レジストを対向基板21の全面に塗布したのち、フォトリソグラフィにて露光、現像することによって基板11および対向基板21との間を支え、距離を一定にするためのスペーサ24を形成する。

【0029】

最後に、図4Iに示したように、基板11と対向基板21とを張り合わせ、スペーサ24によって形成された隙間に、例えば液晶を注入して表示層30を形成する。これにより、表示装置が完成する。この表示装置は、表示層(液晶層)30にフリンジ電界(横電界と縦電界の量成分を含む斜め電界)を印加して表示を行うFFSモードと呼ばれるものである。

【0030】

従来の半導体装置では、前述したようにゲート電極およびゲート配線は高融点金属が用いられており、ゲート電極はシリコンからなる半導体層を効率的に多結晶化させるために薄く、ゲート配線はゲートパルスの伝達遅延を緩和するために厚く形成する必要があった。そこで、例えば図5(断面構成)および図6(平面構成)に示したように、直線状に形成されたゲート配線112Aの一部にゲート配線よりも膜厚の薄い張り出し部Xを設け、この張り出し部Xをゲート電極112Bとした半導体装置100が開示されている(特許文献1)。

【0031】

しかしながら、このような半導体装置100ではゲート配線112Aの膜応力によって基板111の反り量が大きくなり、フォトリソグラフィ工程等では位置合わせずれ、基板搬送時では基板111の吸着異常等の問題があり、信頼性および歩留まりの低下の要因となっていた。

【0032】

これに対して、本実施の形態の半導体装置1では、ゲート配線12Aとして一方向に延在する厚膜の金属膜を形成したのち、この金属膜をエッチングして一部を除去し、この除去部分にゲート配線12Aよりも膜厚の薄いゲート電極12Bを形成するようにした。これにより、ゲート配線12Aによる基板11への膜応力を緩和することが可能となる。

【0033】

以上のように本実施の形態では、ゲート配線12Aとして一方向に形成した金属膜の一部をエッチングし、その間にゲート配線12Aよりも膜厚の薄いゲート電極12Bを設けるようにしたので、ゲート配線12Aの応力が低減される。これにより、基板11の反り量が抑えられ、位置合わせ等が容易になり製造歩留まりが向上する。よって信頼性が向上した表示装置および電子機器を提供することが可能となる。

【0034】

また、本実施の形態の半導体装置では、ゲート配線12Aおよびゲート電極12Bを直線状に形成するようにしたので、上記半導体装置100と比較して、画素の開口率を向上させることが可能となる。

【0035】

<第2の実施の形態>

図7は、本開示の第2の実施の形態に係る表示装置の断面構成を表したものであり、図8はこの表示装置を構成する半導体装置2の平面構成を表したものである。なお、図8は図8のII−II’一点鎖線における断面図である。この半導体装置2は、ゲート電極12Bと同時に保持容量配線32を形成した点が上記第1の実施の形態とは異なる。この保持容量配線32は、上記ゲート配線12Aおよびゲート電極12B等と同様に、例えばCr,Mo,Ta,W,Tiなどの高融点金属によって構成されている。以下に、半導体装置2の製造方法を説明する。なお、第1の実施の形態と同一の構成要素については同一符号を付してその説明は省略する。

【0036】

[半導体装置2の製造方法]

図9A〜図9Iは、半導体装置1の製造方法を説明するための図である。半導体装置2は、例えば次のようにして製造することができる。

【0037】

[半導体装置2の製造方法]

まず、図9Aに示したように、基板11上の全面にスパッタリング法や蒸着法により金属膜を例えば200nmの厚さで形成したのち、この金属膜を、例えばフォトリソグラフィ法を用いてパターニングすることにより、アイランド上の配線パターン(複数のゲート配線12A)を形成する。続いて、図9Bに示したように、基板11およびゲート配線12A上の全面に金属膜を例えば50nmの厚さで成膜したのち、例えばフォトリソグラフィ法を用いてパターニングすることによりゲート配線12Aの間およびゲート配線12A上に延在するゲート電極12Bを形成する。また、これらゲート配線12Aおよびゲート電極12Bによって形成された配線ラインと並走するようにゲート電極12Bと同じ膜厚の保持容量配線32を形成する。次に、図9Cに示したように、基板11,ゲート配線12Aおよびゲート電極12B上を覆うように、ゲート絶縁膜13をプラズマCVD法を用いて例えば50nmの厚さで形成する。具体的には、例えば原料ガスとしてシラン(SiH4)、アンモニア(NH3)、窒素を含む混合ガスを用いたプラズマCVD法により、シリコン窒化膜よりなるゲート絶縁膜13を成膜する。

【0038】

続いて、図9Dに示したように、半導体層14となるアモルファスシリコン層を、例えばプラズマCVD法を用いて50nmの膜厚で形成する。そののち、アモルファスシリコン層をエキシマレーザやランプアニール、半導体レーザアニールなどにより結晶化する。このとき、薄膜トランジスタのゲート電極12Bは、50nmと薄く形成されているため、必要な結晶化エネルギーが極端に高くなることはない。結晶化エネルギーに影響を与えず、且つ、ゲート配線の低抵抗化が実現できる。次に、不純物領域を形成するが、LDD量位に器浮いては形成してもしなくても構わない。続いて、ソース・ドレイン領域を形成するために、N型もしくはP型となる不純物をイオンドーピングまたはイオンインプランテーションにより半導体層14のソース・ドレイン領域にドープする。

【0039】

次いで、図9Eに示したように、アモルファスシリコン層を例えばフォトリソグラフィによってトランジスタおよび保持容量(CS)の形状に形成する。続いて、図9Fに示したように、薄膜トランジスタと信号線16とを分離するための層間絶縁膜15A,15Bを形成する。具体的には、プラズマCVD法によって、例えば窒化シリコン膜を300nm(15A)、酸化シリコン膜(15B)をそれぞれ300nmの膜厚で成膜する。次いで、後に形成する信号線16の信号を、例えばフォトリソグラフィを用いて半導体層14へ伝達するためのコンタクトホールPC,DCを形成する。

【0040】

続いて、図9Gに示したように、各画素に信号電位を入力するための金属膜を、例えばスパッタ法を用いて成膜したのち、フォトリソグラフィにより配線状(信号線16)に形成する。次に、図9Hに示したように、画素電極18Aと信号線16とが短絡しないように、且つ、表面を平坦化するための層間絶縁膜15A,15Bを形成する。具体的には、例えば感光性のアクリル樹脂を基板11上の全面に塗布したのち、フォトリソグラフィにて露光する。この露光された部分のアクリル樹脂を現像にて除去することにより、画素電極18Aと薄膜トランジスタとを接続するためのコンタクトホール(PLNC)を形成する。

【0041】

次に、画素電極18Aとして、例えば酸化インジウムスズスをパッタ法およびフォトリソグラフィ法により任意の形状に形成する。この画素電極18Aは、共通電極25との間で電界を形成する。

【0042】

続いて、対向基板21側にカラーフィルタ22、遮光膜22B、平坦化層23、対向共通電極45およびスペーサ24を形成する。まず、対向基板21上に、例えばネガ型レジストを使用して赤のカラーレジストを塗布したのち、フォトリソグラフィにて露光、現像する。以下、緑、青と同様に任意の画素を形成していく。そして、各カラーレジストの重なり部分にできる凹凸を平坦化するため、平坦化材を対向基板21全面に塗布し平坦化層23を形成する。次に、対向共通電極25として、例えば酸化インジウムスズをスパッタにて成膜したのちフォトリソグラフィにより、例えばホール状に形成する。続いて、例えばポジ形レジストを対向基板21の全面に塗布したのち、フォトリソグラフィにて露光、現像することによって基板11および対向基板21との間を支え、距離を一定にするためのスペーサ24を形成する。

【0043】

最後に、図9Iに示したように、基板11と対向基板21とを張り合わせ、スペーサ24によって形成された隙間に、例えば液晶を注入して表示層30を形成する。これにより、表示装置が完成する。この表示装置は、画素電極18Aと共通電極25との間に電界を発生させることで液晶を駆動し、画素に印加された画素電位を保持する保持容量を保持容量配線32と、半導体層14との間で形成するVAモード(垂直方向)と呼ばれるものである。

【0044】

以上のような構成を有する本実施の形態においても、上記第1の実施の形態と同様の効果が得られる。

【0045】

<適用例>

次に、上記第1の実施の形態および第2の実施の形態に係る半導体装置1,2を備えた表示装置の電子機器への適用例について説明する。

【0046】

[電子機器]

以下、上記半導体装置の電子機器への適用例について説明する。上記半導体装置は、テレビジョン装置,デジタルカメラ,ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなどのあらゆる分野の電子機器に適用することが可能である。言い換えると、上記半導体装置は、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器に適用することが可能である。

【0047】

(モジュール)

上記半導体装置は、例えば図10に示したようなモジュールとして、後述の適用例1〜5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板11の一辺に、封止用基板50から露出した領域210を設け、この露出した領域210に、水平セレクタ31、ライトスキャナ32および電源スキャナ33の配線を延長して外部接続端子(図示せず)を形成したものである。この外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

【0048】

(適用例1)

図11は、テレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300が上記半導体装置に相当する。

【0049】

(適用例2)

図12は、デジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、この表示部420が上記半導体装置に相当する。

【0050】

(適用例3)

図13は、ノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、この表示部530が上記半導体装置に相当する。

【0051】

(適用例4)

図14は、ビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有している。この表示部640が上記半導体装置に相当する。

【0052】

(適用例5)

図15は、携帯電話機の外観を表したものである。この携帯電話機は、例えば上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そして、これらのうちのディスプレイ740またはサブディスプレイ750が、上記半導体装置に相当する。

【0053】

以上、第1および第2の実施の形態を挙げて本技術を説明したが、本技術は上記実施の形態に限定されず、種々の変形が可能である。例えば、上記実施の形態では、ゲート絶縁膜13を単層膜として説明したが、シリコン酸化膜とシリコン窒化膜との2層膜や低密度の酸化アルミニウムをシリコン酸化膜またはシリコン窒化膜で挟持した3層膜、あるいは4層以上を積層した構造であってもよい。

【0054】

なお、本技術は以下のような構成もとることができる。

(1)一方向に延在する複数の第1配線層と、前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、前記第1配線層およびゲート電極上に形成された絶縁膜と、前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、前記半導体層上に設けられた層間膜と、前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層とを備えた半導体装置。

(2)前記第1配線層と前記ゲート電極とは電気的に接続されている、前記(1)に記載の半導体装置。

(3)第1配線層は積層構造を有し、その最上層には前記ゲート電極と同一の膜厚の層を有する、前記(1)または(2)に記載の薄膜トランジスタ。

(4)前記第1配線層およびゲート電極からなる層が複数積層した構造を有する、前記(1)乃至(3)のいずれか1つに記載の薄膜トランジスタ。

(5)前記ゲート電極の膜厚は30nm以上90nm以下である、前記(1)乃至(4)のいずれか1つに記載の薄膜トランジスタ。

(6)前記第1配線層とゲート電極との膜厚比は2:1以上6:1以下である、前記(1)乃至(5)のいずれか1つに記載の薄膜トランジスタ。

(7)一方向に延在する金属膜を成膜する工程と、前記金属膜をエッチングすることによって複数の第1配線層を形成する工程と、前記第1配線層の間に前記第1配線層より膜厚の薄いゲート電極を形成する工程と、前記第1配線層およびゲート電極上に絶縁膜を形成する工程と、前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層を形成する工程と、前記半導体層上に層間膜を形成する工程と、前記層間膜に貫通孔を形成する工程と、前記層間膜上に、前記貫通孔を介して前記半導体層と接続される第2配線層を形成する工程とを含む半導体装置の製造方法。

(8)前記ゲート電極を前記第1配線層の間および前記第1配線層上に連続して形成する、前記(7)に記載の半導体装置の製造方法。

(9)表示素子と、前記表示素子を駆動するための半導体装置を備え、前記半導体装置は、一方向に延在する複数の第1配線層と、前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、前記第1配線層およびゲート電極上に形成された絶縁膜と、前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、前記半導体層上に設けられた層間膜と、前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層とを備えた表示装置。

(10)表示素子と、前記表示素子を駆動するための半導体装置とを有する表示装置を備え、前記半導体装置は、一方向に延在する複数の第1配線層と、前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、前記第1配線層およびゲート電極上に形成された絶縁膜と、前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、前記半導体層上に設けられた層間膜と、前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層とを有する電子機器。

【符号の説明】

【0055】

1,2…半導体装置、11…基板、12A…ゲート配線、12B…ゲート電極、13,…ゲート絶縁膜、14…酸化物半導体層、15A,15B…チャネル保護膜、16…信号線、17…平坦化層、18…画素電極、19A…ソース電極、19B…ドレイン電極、21…基板、22A,22B…カラーフィルタ、23…平坦化層、24…スペーサ。

【技術分野】

【0001】

本技術は、半導体装置およびその製造方法ならびにこれを用いた表示装置および電子機器に関する。

【背景技術】

【0002】

近年、さまざまな薄膜トランジスタを集積形成した表示装置等の半導体装置が製造されている。このような半導体装置の例としては、例えば特許文献1では、以下の構成を有するボトムゲート型の薄膜トランジスタを備えた半導体装置が開示されている。その構成は、基板上にゲート配線や補助容量配線等の下側配線と、この下側配線と同電位で且つ同時にパターニングされたゲート電極とが形成され、この上にゲート絶縁膜、薄膜トランジスタの素子領域を構成する半導体層、層間絶縁膜および層間絶縁膜に形成されたコンタクトホールを介して薄膜トランジスタに接続する信号配線等の上側配線が順に積層されている。

【0003】

このように、ゲート電極上にゲート絶縁膜を介して半導体層が形成された薄膜トランジスタでは、半導体層はその多結晶化工程においてレーザ照射を用いることからゲート電極およびゲート配線には高融点金属が用いられる。また、半導体層は効率的に加熱することによって良好な多結晶構造が得られるため、ゲート電極は排熱効果を制御するために膜厚を薄く形成する必要がある。一方、ゲート配線はゲートパルスの伝達遅延を緩和するために膜厚を厚く形成する必要がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開20010177103号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、基板上に膜厚の大きな金属膜を形成すると、その膜応力によって基板の反り量が大きくなる。このため、例えばフォトリソグラフィ工程では合わせずれ、基板運搬時には基板吸着異常等の問題が生じていた。この問題は、例えば表示装置のパネルの大型化や高精細化によって配線密度が高くなることで更に顕著となり、基板の薄板化および大型化に対して問題となっていた。

【0006】

本技術はかかる問題点に鑑みてなされたもので、その目的は、配線層の膜応力を低減し、製造歩留まりを向上させることが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供することにある。

【課題を解決するための手段】

【0007】

本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えたものである。

【0008】

本技術の半導体装置の製造方法は、以下の(A)〜(H)の工程を含むものである。

(A)一方向に延在する金属膜を成膜する工程

(B)金属膜をエッチングすることによって複数の第1配線層を形成する工程

(C)第1配線層の間に前記第1配線層より膜厚の薄いゲート電極を形成する工程

(D)第1配線層およびゲート電極上に絶縁膜を形成する工程

(E)絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層を形成する工程

(F)半導体層上に層間膜を形成する工程

(G)層間膜に貫通孔を形成する工程

(H)層間膜上に、貫通孔を介して半導体層と接続される第2配線層を形成する工程

【0009】

本技術の表示装置および電子機器は、表示素子と、上記半導体装置とを備えたものである。

【0010】

本技術の半導体装置およびその製造方法ならびに表示装置および電子機器では、一方向に延在する金属膜を形成したのちエッチングすることで複数の第1配線層を設け、この第1配線層間に第1配線層よりも膜厚の薄いゲート電極を形成するようにした。これにより、第1配線層による基板への膜応力を緩和することが可能となる。

【発明の効果】

【0011】

本技術の半導体装置およびその製造方法ならびに表示装置および電子機器によれば、一方向に延在する複数の第1配線層を設け、その第1配線層間に、第1配線層よりも膜厚の薄いゲート電極を設けるようにした。よって、第1配線層による基板への膜応力が緩和され、製造歩留まりを向上することが可能となる。

【図面の簡単な説明】

【0012】

【図1】本開示の第1の実施の形態に係る表示装置の一例を表す断面図である。

【図2】図1に示した表示装置を構成する半導体装置の平面図である。

【図3】本開示の第1の実施の形態に係る表示装置の他の例を表す断面図である。

【図4A】図1に示した表示装置の製造方法を工程順に表す図である。

【図4B】図4Aに続く工程を表す図である。

【図4C】図4Bに続く工程を表す図である。

【図4D】図4Cに続く工程を表す図である。

【図4E】図4Dに続く工程を表す図である。

【図4F】図4Eに続く工程を表す図である。

【図4G】図4Fに続く工程を表す図である。

【図4H】図4Gに続く工程を表す図である。

【図4I】図4Hに続く工程を表す図である。

【図4J】図4Iに続く工程を表す図である。

【図5】本開示の比較例に係る表示装置の断面図である。

【図6】図5に示した表示装置を構成する半導体装置の平面図である。

【図7】本開示の第2の実施の形態に係る表示装置の断面図である。

【図8】図7に示した表示装置を構成する半導体装置の平面図である。

【図9A】図1に示した表示装置の製造方法を工程順に表す図である。

【図9B】図9Aに続く工程を表す図である。

【図9C】図9Bに続く工程を表す図である。

【図9D】図9Cに続く工程を表す図である。

【図9E】図9Dに続く工程を表す図である。

【図9F】図9Eに続く工程を表す図である。

【図9G】図9Fに続く工程を表す図である。

【図9H】図9Gに続く工程を表す図である。

【図9I】図9Hに続く工程を表す図である。

【図10】図1に示した表示装置を含むモジュールの概略構成を表す平面図である。

【図11】図10に示した表示装置の適用例1の外観を表す斜視図である。

【図12】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図13】適用例3の外観を表す斜視図である。

【図14】適用例4の外観を表す斜視図である。

【図15】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。

【発明を実施するための形態】

【0013】

以下、本開示の実施の形態について図面を参照して詳細に説明する。尚、説明は以下の順序で行う。

1.第1の実施の形態(FSSモードの表示装置)

2.第2の実施の形態(VAモードの表示装置)

3.適用例(表示装置および電子機器の例)

【0014】

<第1の実施の形態>

[半導体装置1の構成]

図1は、本開示の第1の実施の形態に係る表示装置の断面構成を表したものであり、図2はこの表示装置を構成する半導体装置1の平面構成を表したものである。なお、図1は図2のI−I’一点鎖線における断面図である。半導体装置1は、スイッチング素子として、いわゆるボトムゲート型(逆スタガー構造)の薄膜トランジスタ(Thin Film Transistor;TFT)を有する。この半導体装置1では、ガラス等の基板11上にゲート電極12Bおよびゲート配線(第1配線)12Aが形成されている。ゲート電極12B上には、ゲート絶縁膜(絶縁膜)13、半導体層14、層間絶縁膜(層間膜)15(15A,15B)、信号線16が順に設けられた薄膜トランジスタが形成されている。薄膜トランジスタ上には平坦化層17が順に設けられており、この平坦化層17上に画素電極(第2配線層)18Aおよび共通電極18Bが形成されている。本実施の形態では、ゲート配線12Aと、ゲート配線12Aよりも膜厚の薄いゲート電極12Bとが一方向に交互に形成されている。

【0015】

ゲート電極12Bは、薄膜トランジスタに印加されるゲート電圧によって半導体層14中のキャリア密度(ここでは、電子密度)を制御する役割を果たすものである。ゲート配線12Aは基板11上に複数設けられたゲート電極12Bを電気的に接続するためのものである。ゲート配線12Aおよびゲート電極12Bは、例えばクロム(Cr),モリブデン(Mo),タンタル(Ta),タングステン(W),チタン(Ti)等の高融点金属(例えば、融点1500℃〜3500℃)によって形成されている。

【0016】

ゲート電極12Bはゲート配線12Aの膜厚と比較して薄く、ゲート配線12Aとゲート電極12Bとの膜厚比は、例えば2:1以上6:1以下の範囲で形成されることが好ましい。具体的には、ゲート配線12Aは例えば、60〜540nm、ゲート電極12Bは例えば30〜90nmの膜厚で形成されている。このようにゲート配線12Aはゲート電極12Bよりも膜厚が厚く、特に上記高融点金属を用いた場合にはその膜応力は高くなり、基板11の反り量が大きくなるという問題があった。これに対して、本実施の形態では、詳細は後述するが、基板上11にゲート配線12Aとなる金属膜を成膜したのち、少なくとも一部をエッチング等により除去して金属膜を分割、即ちアイランド上に形成し、これによって形成された金属層(ゲート配線12A)の間にゲート電極12Bを形成する。即ち、ゲート配線12Aとゲート電極12Bとが交互に延在するように配置される。これにより、ゲート配線12Aの応力が緩和され、基板11の反り量が低減される。なお、図1ではゲート配線12Aは、基板11上に直接成膜された金属膜と、ゲート電極12Bのゲート配線12A上に形成された2層構造としたが、これに限らず、図3のようにゲート配線12Aおよびゲート電極12を1層からなる金属膜で形成し、この金属膜の適当な位置で膜厚の一部をエッチングしてこの薄膜部分をゲート電極12Bとするようにしてもよい。

【0017】

ゲート絶縁膜13は、シリコン酸化膜,シリコン窒化膜,シリコン窒化酸化膜および酸化アルミニウム膜等のうちの1種よりなる単層膜、またはこれらのうちの2種以上よりなる積層膜である。ゲート絶縁膜13の厚みは、例えば100nm〜300nmである。

【0018】

半導体層14は、アモルファスシリコンによって構成されている。この半導体層14は、ゲート電圧の印加によりソース・ドレイン電極19A,19B(図2参照)間にチャネルを形成するものであり、半導体層14の厚みは、例えば5nm〜100nmである。なお、半導体層14の材料としては、アモルファスシリコンの他に、例えばインジウム(In),ガリウム(Ga),亜鉛(Zn),スズ(Sn),Al,チタン(Ti)のうち少なくとも1種の元素の酸化物を用いてもよい。

【0019】

層間絶縁膜15(15A,15B)は、半導体層14上に形成され、ソース・ドレイン電極19A,19B形成時におけるチャネルの損傷を防止するためのものである。層間絶縁膜15の厚みは、例えば10〜300nmである。この層間絶縁膜15は半導体層層14への水分等の供給が少ないことが望ましい。層間絶縁膜15は、例えば、シリコン酸化膜,シリコン窒化膜,シリコン酸窒化膜あるいは酸化アルミニウム膜、またはこれらの積層膜により構成されている。

【0020】

ソース・ドレイン電極19A,19Bは、図2に示したように、層間絶縁膜15を介して半導体層14上に形成されている。ソース・ドレイン電極19A,19Bの材料としては、例えばCr,Mo,Al,銅(Cu),Ti,Ta,W,ITO(インジウム錫酸化物)および酸化チタン等のうち1種よりなる単層膜またはこれらのうちの2種以上よりなる積層膜である。例えば、Mo/Al/Moの順に、例えば50nm、500nm、50nmの膜厚で積層した3層膜や、ITOおよび酸化チタン等の酸素を含む金属化合物のような酸素との結びつきの弱い金属または金属化合物を用いることが望ましい。これにより、半導体層14を酸化物半導体で形成した際の電気特性を安定して保持することができる。逆に、ソース・ドレイン電極19A,19Bを酸素との結びつきが強い金属で構成した場合には、ソース・ドレイン電極19A,19Bは、酸化物半導体に接触して形成されるため、酸化物半導体中の酸素が引き抜かれて酸素欠陥を生じ、電気特性が悪化してしまう。なお、信号線16,共通電極18Bについても、ソース・ドレイン電極19A,19Bと同様の材料を用いることができる。

【0021】

平坦化層17は、例えば酸化アルミニウム膜またはシリコン酸化膜等の単層膜、もしくは酸化アルミニウム膜とシリコン酸化膜との積層膜により構成されている。この平坦化層17の厚みは、例えば10nm〜100nmであり、好ましくは50nm以下である。

【0022】

[半導体装置1の製造方法]

図4A〜図4Jは、半導体装置1の製造方法を説明するための図である。半導体装置1は、例えば次のようにして製造することができる。

【0023】

まず、図4Aに示したように、基板11上の全面にスパッタリング法や蒸着法により金属膜を例えば200nmの厚さで形成したのち、この金属膜を、例えばフォトリソグラフィ法を用いてパターニングすることにより、アイランド上の配線パターン(複数のゲート配線12A)を形成する。続いて、図4Bに示したように、基板11およびゲート配線12A上の全面に金属膜を例えば50nmの厚さで成膜したのち、例えばフォトリソグラフィ法を用いてパターニングすることによりゲート配線12Aの間およびゲート配線12A上に延在するゲート電極12Bを形成する。次に、図4Cに示したように、基板11,ゲート配線12Aおよびゲート電極12B上を覆うように、ゲート絶縁膜13をプラズマCVD法を用いて例えば50nmの厚さで形成する。具体的には、例えば原料ガスとしてシラン(SiH4)、アンモニア(NH3)、窒素を含む混合ガスを用いたプラズマCVD法により、シリコン窒化膜よりなるゲート絶縁膜13を成膜する。

【0024】

続いて、図4Dに示したように、半導体層14となるアモルファスシリコン層を、例えばプラズマCVD法を用いて50nmの膜厚で形成する。そののち、アモルファスシリコン層をエキシマレーザやランプアニール、半導体レーザアニールなどにより結晶化する。このとき、薄膜トランジスタのゲート電極12Bは、50nmと薄く形成されているため、必要な結晶化エネルギーが極端に高くなることはない。結晶化エネルギーに影響を与えず、且つ、ゲート配線の低抵抗化が実現できる。次に、不純物領域を形成するが、LDD領域については形成してもしなくても構わない。続いて、ソース・ドレイン領域を形成するために、N型もしくはP型となる不純物をイオンドーピングまたはイオンインプランテーションにより半導体層14のソース・ドレイン領域にドープする。

【0025】

次いで、図4Eに示したように、アモルファスシリコン層を例えばフォトリソグラフィによってトランジスタの形状に形成する。続いて、図4Fに示したように、薄膜トランジスタと信号線16とを分離するための層間絶縁膜15A,15Bを形成する。具体的には、プラズマCVD法によって、例えば窒化シリコン膜を300nm(15A)、酸化シリコン膜(15B)をそれぞれ300nmの膜厚で成膜する。次いで、後に形成する信号線16の信号を、例えばフォトリソグラフィを用いて半導体層14へ伝達するためのコンタクトホールPC,DCを形成する。

【0026】

続いて、図4Gに示したように、各画素に信号電位を入力するための金属膜を、例えばスパッタ法を用いて成膜したのち、フォトリソグラフィにより配線状(信号線16)に形成する。次に、図4Hに示したように、後に形成する共通電極18Bと信号線16とが短絡しないように、且つ、表面を平坦化するための層間絶縁膜15A,15Bを形成する。具体的には、例えば感光性のアクリル樹脂を基板11上の全面に塗布したのち、フォトリソグラフィにて露光する。この露光された部分のアクリル樹脂を現像にて除去することにより、画素電極18Aと薄膜トランジスタとを接続するためのコンタクトホール(PLNC)を形成する。

【0027】

続いて、図4Iに示したように、共通電極18Bを例えば酸化インジウムスズにて形成する。このとき、薄膜トランジスタの後述する画素電極18Aと共通電極18Bとが短絡しないように、先に開けたコンタクトホールPLNCよりも大きく共通電極コンタクトホールCMCを開ける。次いで、画素電極18Aから共通電極18Bへ電界をかけるための誘電膜となる画素絶縁膜20を、例えば窒化シリコン膜や酸化シリコン膜などを用い、プラズマCVDにより成膜する。続いて、フォトリソグラフィにて、薄膜トランジスタと画素電極18Aとを導通するためのコンタクトホールPILCを、コンタクトホールPLNC上で且つコンタクトホールCMCの内側にくるように形成することで画素電極18Aと共通電極18Bとの短絡を紡糸する。次に、画素電極18Aをスパッタ法およびフォトリソグラフィ法により任意の形状に形成する。画素電極18Aは、共通電極18Bとの間で電界を形成するため、例えば図2に示したように短冊状の隙間を複数形成する。

【0028】

続いて、対向基板21側に例えば赤色または緑色等のカラーフィルタ24A,24B等を形成する。まず、対向基板21上に、例えばネガ型レジストを使用して赤のカラーレジストを塗布したのち、フォトリソグラフィにて露光、現像する。以下、緑、青と同様に任意の画素を形成していく。そして、各カラーレジストの重なり部分にできる凹凸を平坦化するため、平坦化材を対向基板21全面に塗布し平坦化層23を形成する。続いて、例えばポジ形レジストを対向基板21の全面に塗布したのち、フォトリソグラフィにて露光、現像することによって基板11および対向基板21との間を支え、距離を一定にするためのスペーサ24を形成する。

【0029】

最後に、図4Iに示したように、基板11と対向基板21とを張り合わせ、スペーサ24によって形成された隙間に、例えば液晶を注入して表示層30を形成する。これにより、表示装置が完成する。この表示装置は、表示層(液晶層)30にフリンジ電界(横電界と縦電界の量成分を含む斜め電界)を印加して表示を行うFFSモードと呼ばれるものである。

【0030】

従来の半導体装置では、前述したようにゲート電極およびゲート配線は高融点金属が用いられており、ゲート電極はシリコンからなる半導体層を効率的に多結晶化させるために薄く、ゲート配線はゲートパルスの伝達遅延を緩和するために厚く形成する必要があった。そこで、例えば図5(断面構成)および図6(平面構成)に示したように、直線状に形成されたゲート配線112Aの一部にゲート配線よりも膜厚の薄い張り出し部Xを設け、この張り出し部Xをゲート電極112Bとした半導体装置100が開示されている(特許文献1)。

【0031】

しかしながら、このような半導体装置100ではゲート配線112Aの膜応力によって基板111の反り量が大きくなり、フォトリソグラフィ工程等では位置合わせずれ、基板搬送時では基板111の吸着異常等の問題があり、信頼性および歩留まりの低下の要因となっていた。

【0032】

これに対して、本実施の形態の半導体装置1では、ゲート配線12Aとして一方向に延在する厚膜の金属膜を形成したのち、この金属膜をエッチングして一部を除去し、この除去部分にゲート配線12Aよりも膜厚の薄いゲート電極12Bを形成するようにした。これにより、ゲート配線12Aによる基板11への膜応力を緩和することが可能となる。

【0033】

以上のように本実施の形態では、ゲート配線12Aとして一方向に形成した金属膜の一部をエッチングし、その間にゲート配線12Aよりも膜厚の薄いゲート電極12Bを設けるようにしたので、ゲート配線12Aの応力が低減される。これにより、基板11の反り量が抑えられ、位置合わせ等が容易になり製造歩留まりが向上する。よって信頼性が向上した表示装置および電子機器を提供することが可能となる。

【0034】

また、本実施の形態の半導体装置では、ゲート配線12Aおよびゲート電極12Bを直線状に形成するようにしたので、上記半導体装置100と比較して、画素の開口率を向上させることが可能となる。

【0035】

<第2の実施の形態>

図7は、本開示の第2の実施の形態に係る表示装置の断面構成を表したものであり、図8はこの表示装置を構成する半導体装置2の平面構成を表したものである。なお、図8は図8のII−II’一点鎖線における断面図である。この半導体装置2は、ゲート電極12Bと同時に保持容量配線32を形成した点が上記第1の実施の形態とは異なる。この保持容量配線32は、上記ゲート配線12Aおよびゲート電極12B等と同様に、例えばCr,Mo,Ta,W,Tiなどの高融点金属によって構成されている。以下に、半導体装置2の製造方法を説明する。なお、第1の実施の形態と同一の構成要素については同一符号を付してその説明は省略する。

【0036】

[半導体装置2の製造方法]

図9A〜図9Iは、半導体装置1の製造方法を説明するための図である。半導体装置2は、例えば次のようにして製造することができる。

【0037】

[半導体装置2の製造方法]

まず、図9Aに示したように、基板11上の全面にスパッタリング法や蒸着法により金属膜を例えば200nmの厚さで形成したのち、この金属膜を、例えばフォトリソグラフィ法を用いてパターニングすることにより、アイランド上の配線パターン(複数のゲート配線12A)を形成する。続いて、図9Bに示したように、基板11およびゲート配線12A上の全面に金属膜を例えば50nmの厚さで成膜したのち、例えばフォトリソグラフィ法を用いてパターニングすることによりゲート配線12Aの間およびゲート配線12A上に延在するゲート電極12Bを形成する。また、これらゲート配線12Aおよびゲート電極12Bによって形成された配線ラインと並走するようにゲート電極12Bと同じ膜厚の保持容量配線32を形成する。次に、図9Cに示したように、基板11,ゲート配線12Aおよびゲート電極12B上を覆うように、ゲート絶縁膜13をプラズマCVD法を用いて例えば50nmの厚さで形成する。具体的には、例えば原料ガスとしてシラン(SiH4)、アンモニア(NH3)、窒素を含む混合ガスを用いたプラズマCVD法により、シリコン窒化膜よりなるゲート絶縁膜13を成膜する。

【0038】

続いて、図9Dに示したように、半導体層14となるアモルファスシリコン層を、例えばプラズマCVD法を用いて50nmの膜厚で形成する。そののち、アモルファスシリコン層をエキシマレーザやランプアニール、半導体レーザアニールなどにより結晶化する。このとき、薄膜トランジスタのゲート電極12Bは、50nmと薄く形成されているため、必要な結晶化エネルギーが極端に高くなることはない。結晶化エネルギーに影響を与えず、且つ、ゲート配線の低抵抗化が実現できる。次に、不純物領域を形成するが、LDD量位に器浮いては形成してもしなくても構わない。続いて、ソース・ドレイン領域を形成するために、N型もしくはP型となる不純物をイオンドーピングまたはイオンインプランテーションにより半導体層14のソース・ドレイン領域にドープする。

【0039】

次いで、図9Eに示したように、アモルファスシリコン層を例えばフォトリソグラフィによってトランジスタおよび保持容量(CS)の形状に形成する。続いて、図9Fに示したように、薄膜トランジスタと信号線16とを分離するための層間絶縁膜15A,15Bを形成する。具体的には、プラズマCVD法によって、例えば窒化シリコン膜を300nm(15A)、酸化シリコン膜(15B)をそれぞれ300nmの膜厚で成膜する。次いで、後に形成する信号線16の信号を、例えばフォトリソグラフィを用いて半導体層14へ伝達するためのコンタクトホールPC,DCを形成する。

【0040】

続いて、図9Gに示したように、各画素に信号電位を入力するための金属膜を、例えばスパッタ法を用いて成膜したのち、フォトリソグラフィにより配線状(信号線16)に形成する。次に、図9Hに示したように、画素電極18Aと信号線16とが短絡しないように、且つ、表面を平坦化するための層間絶縁膜15A,15Bを形成する。具体的には、例えば感光性のアクリル樹脂を基板11上の全面に塗布したのち、フォトリソグラフィにて露光する。この露光された部分のアクリル樹脂を現像にて除去することにより、画素電極18Aと薄膜トランジスタとを接続するためのコンタクトホール(PLNC)を形成する。

【0041】

次に、画素電極18Aとして、例えば酸化インジウムスズスをパッタ法およびフォトリソグラフィ法により任意の形状に形成する。この画素電極18Aは、共通電極25との間で電界を形成する。

【0042】

続いて、対向基板21側にカラーフィルタ22、遮光膜22B、平坦化層23、対向共通電極45およびスペーサ24を形成する。まず、対向基板21上に、例えばネガ型レジストを使用して赤のカラーレジストを塗布したのち、フォトリソグラフィにて露光、現像する。以下、緑、青と同様に任意の画素を形成していく。そして、各カラーレジストの重なり部分にできる凹凸を平坦化するため、平坦化材を対向基板21全面に塗布し平坦化層23を形成する。次に、対向共通電極25として、例えば酸化インジウムスズをスパッタにて成膜したのちフォトリソグラフィにより、例えばホール状に形成する。続いて、例えばポジ形レジストを対向基板21の全面に塗布したのち、フォトリソグラフィにて露光、現像することによって基板11および対向基板21との間を支え、距離を一定にするためのスペーサ24を形成する。

【0043】

最後に、図9Iに示したように、基板11と対向基板21とを張り合わせ、スペーサ24によって形成された隙間に、例えば液晶を注入して表示層30を形成する。これにより、表示装置が完成する。この表示装置は、画素電極18Aと共通電極25との間に電界を発生させることで液晶を駆動し、画素に印加された画素電位を保持する保持容量を保持容量配線32と、半導体層14との間で形成するVAモード(垂直方向)と呼ばれるものである。

【0044】

以上のような構成を有する本実施の形態においても、上記第1の実施の形態と同様の効果が得られる。

【0045】

<適用例>

次に、上記第1の実施の形態および第2の実施の形態に係る半導体装置1,2を備えた表示装置の電子機器への適用例について説明する。

【0046】

[電子機器]

以下、上記半導体装置の電子機器への適用例について説明する。上記半導体装置は、テレビジョン装置,デジタルカメラ,ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラなどのあらゆる分野の電子機器に適用することが可能である。言い換えると、上記半導体装置は、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器に適用することが可能である。

【0047】

(モジュール)

上記半導体装置は、例えば図10に示したようなモジュールとして、後述の適用例1〜5などの種々の電子機器に組み込まれる。このモジュールは、例えば、基板11の一辺に、封止用基板50から露出した領域210を設け、この露出した領域210に、水平セレクタ31、ライトスキャナ32および電源スキャナ33の配線を延長して外部接続端子(図示せず)を形成したものである。この外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(FPC;Flexible Printed Circuit)220が設けられていてもよい。

【0048】

(適用例1)

図11は、テレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300が上記半導体装置に相当する。

【0049】

(適用例2)

図12は、デジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュースイッチ430およびシャッターボタン440を有しており、この表示部420が上記半導体装置に相当する。

【0050】

(適用例3)

図13は、ノート型パーソナルコンピュータの外観を表したものである。このノート型パーソナルコンピュータは、例えば、本体510,文字等の入力操作のためのキーボード520および画像を表示する表示部530を有しており、この表示部530が上記半導体装置に相当する。

【0051】

(適用例4)

図14は、ビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部610,この本体部610の前方側面に設けられた被写体撮影用のレンズ620,撮影時のスタート/ストップスイッチ630および表示部640を有している。この表示部640が上記半導体装置に相当する。

【0052】

(適用例5)

図15は、携帯電話機の外観を表したものである。この携帯電話機は、例えば上側筐体710と下側筐体720とを連結部(ヒンジ部)730で連結したものであり、ディスプレイ740,サブディスプレイ750,ピクチャーライト760およびカメラ770を有している。そして、これらのうちのディスプレイ740またはサブディスプレイ750が、上記半導体装置に相当する。

【0053】

以上、第1および第2の実施の形態を挙げて本技術を説明したが、本技術は上記実施の形態に限定されず、種々の変形が可能である。例えば、上記実施の形態では、ゲート絶縁膜13を単層膜として説明したが、シリコン酸化膜とシリコン窒化膜との2層膜や低密度の酸化アルミニウムをシリコン酸化膜またはシリコン窒化膜で挟持した3層膜、あるいは4層以上を積層した構造であってもよい。

【0054】

なお、本技術は以下のような構成もとることができる。

(1)一方向に延在する複数の第1配線層と、前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、前記第1配線層およびゲート電極上に形成された絶縁膜と、前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、前記半導体層上に設けられた層間膜と、前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層とを備えた半導体装置。

(2)前記第1配線層と前記ゲート電極とは電気的に接続されている、前記(1)に記載の半導体装置。

(3)第1配線層は積層構造を有し、その最上層には前記ゲート電極と同一の膜厚の層を有する、前記(1)または(2)に記載の薄膜トランジスタ。

(4)前記第1配線層およびゲート電極からなる層が複数積層した構造を有する、前記(1)乃至(3)のいずれか1つに記載の薄膜トランジスタ。

(5)前記ゲート電極の膜厚は30nm以上90nm以下である、前記(1)乃至(4)のいずれか1つに記載の薄膜トランジスタ。

(6)前記第1配線層とゲート電極との膜厚比は2:1以上6:1以下である、前記(1)乃至(5)のいずれか1つに記載の薄膜トランジスタ。

(7)一方向に延在する金属膜を成膜する工程と、前記金属膜をエッチングすることによって複数の第1配線層を形成する工程と、前記第1配線層の間に前記第1配線層より膜厚の薄いゲート電極を形成する工程と、前記第1配線層およびゲート電極上に絶縁膜を形成する工程と、前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層を形成する工程と、前記半導体層上に層間膜を形成する工程と、前記層間膜に貫通孔を形成する工程と、前記層間膜上に、前記貫通孔を介して前記半導体層と接続される第2配線層を形成する工程とを含む半導体装置の製造方法。

(8)前記ゲート電極を前記第1配線層の間および前記第1配線層上に連続して形成する、前記(7)に記載の半導体装置の製造方法。

(9)表示素子と、前記表示素子を駆動するための半導体装置を備え、前記半導体装置は、一方向に延在する複数の第1配線層と、前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、前記第1配線層およびゲート電極上に形成された絶縁膜と、前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、前記半導体層上に設けられた層間膜と、前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層とを備えた表示装置。

(10)表示素子と、前記表示素子を駆動するための半導体装置とを有する表示装置を備え、前記半導体装置は、一方向に延在する複数の第1配線層と、前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、前記第1配線層およびゲート電極上に形成された絶縁膜と、前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、前記半導体層上に設けられた層間膜と、前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層とを有する電子機器。

【符号の説明】

【0055】

1,2…半導体装置、11…基板、12A…ゲート配線、12B…ゲート電極、13,…ゲート絶縁膜、14…酸化物半導体層、15A,15B…チャネル保護膜、16…信号線、17…平坦化層、18…画素電極、19A…ソース電極、19B…ドレイン電極、21…基板、22A,22B…カラーフィルタ、23…平坦化層、24…スペーサ。

【特許請求の範囲】

【請求項1】

一方向に延在する複数の第1配線層と、

前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、

前記第1配線層およびゲート電極上に形成された絶縁膜と、

前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、

前記半導体層上に設けられた層間膜と、

前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層と

を備えた半導体装置。

【請求項2】

前記第1配線層と前記ゲート電極とは電気的に接続されている、請求項1に記載の半導体装置。

【請求項3】

第1配線層は積層構造を有し、その最上層には前記ゲート電極と同一の膜厚の層を有する、請求項1に記載の半導体装置。

【請求項4】

前記第1配線層およびゲート電極からなる層が複数積層した構造を有する、請求項1に記載の半導体装置。

【請求項5】

前記ゲート電極の膜厚は30nm以上90nm以下である、請求項1に記載の半導体装置。

【請求項6】

前記第1配線層とゲート電極との膜厚比は2:1以上6:1以下である、請求項1に記載の半導体装置。

【請求項7】

一方向に延在する金属膜を成膜する工程と、

前記金属膜をエッチングすることによって複数の第1配線層を形成する工程と、

前記第1配線層の間に前記第1配線層より膜厚の薄いゲート電極を形成する工程と、

前記第1配線層およびゲート電極上に絶縁膜を形成する工程と、

前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層を形成する工程と、

前記半導体層上に層間膜を形成する工程と、

前記層間膜に貫通孔を形成する工程と、

前記層間膜上に、前記貫通孔を介して前記半導体層と接続される第2配線層を形成する工程と

を含む半導体装置の製造方法。

【請求項8】

前記ゲート電極を前記第1配線層の間および前記第1配線層上に連続して形成する、請求項7に記載の半導体装置の製造方法。

【請求項9】

表示素子と、前記表示素子を駆動するための半導体装置を備え、

前記半導体装置は、

一方向に延在する複数の第1配線層と、

前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、

前記第1配線層およびゲート電極上に形成された絶縁膜と、

前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、

前記半導体層上に設けられた層間膜と、

前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層と

を備えた表示装置。

【請求項10】

表示素子と、前記表示素子を駆動するための半導体装置とを有する表示装置を備え、

前記半導体装置は、

一方向に延在する複数の第1配線層と、

前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、

前記第1配線層およびゲート電極上に形成された絶縁膜と、

前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、

前記半導体層上に設けられた層間膜と、

前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層と

を有する電子機器。

【請求項1】

一方向に延在する複数の第1配線層と、

前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、

前記第1配線層およびゲート電極上に形成された絶縁膜と、

前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、

前記半導体層上に設けられた層間膜と、

前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層と

を備えた半導体装置。

【請求項2】

前記第1配線層と前記ゲート電極とは電気的に接続されている、請求項1に記載の半導体装置。

【請求項3】

第1配線層は積層構造を有し、その最上層には前記ゲート電極と同一の膜厚の層を有する、請求項1に記載の半導体装置。

【請求項4】

前記第1配線層およびゲート電極からなる層が複数積層した構造を有する、請求項1に記載の半導体装置。

【請求項5】

前記ゲート電極の膜厚は30nm以上90nm以下である、請求項1に記載の半導体装置。

【請求項6】

前記第1配線層とゲート電極との膜厚比は2:1以上6:1以下である、請求項1に記載の半導体装置。

【請求項7】

一方向に延在する金属膜を成膜する工程と、

前記金属膜をエッチングすることによって複数の第1配線層を形成する工程と、

前記第1配線層の間に前記第1配線層より膜厚の薄いゲート電極を形成する工程と、

前記第1配線層およびゲート電極上に絶縁膜を形成する工程と、

前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層を形成する工程と、

前記半導体層上に層間膜を形成する工程と、

前記層間膜に貫通孔を形成する工程と、

前記層間膜上に、前記貫通孔を介して前記半導体層と接続される第2配線層を形成する工程と

を含む半導体装置の製造方法。

【請求項8】

前記ゲート電極を前記第1配線層の間および前記第1配線層上に連続して形成する、請求項7に記載の半導体装置の製造方法。

【請求項9】

表示素子と、前記表示素子を駆動するための半導体装置を備え、

前記半導体装置は、

一方向に延在する複数の第1配線層と、

前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、

前記第1配線層およびゲート電極上に形成された絶縁膜と、

前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、

前記半導体層上に設けられた層間膜と、

前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層と

を備えた表示装置。

【請求項10】

表示素子と、前記表示素子を駆動するための半導体装置とを有する表示装置を備え、

前記半導体装置は、

一方向に延在する複数の第1配線層と、

前記第1配線層の間に設けられた前記第1配線層よりも膜厚が薄いゲート電極と、

前記第1配線層およびゲート電極上に形成された絶縁膜と、

前記絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、

前記半導体層上に設けられた層間膜と、

前記層間膜上に形成されると共に、前記層間膜に設けられた貫通孔を介して前記半導体層と接続された第2配線層と

を有する電子機器。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図4H】

【図4I】

【図4J】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図9C】

【図9D】

【図9E】

【図9F】

【図9G】

【図9H】

【図9I】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図4G】

【図4H】

【図4I】

【図4J】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図9C】

【図9D】

【図9E】

【図9F】

【図9G】

【図9H】

【図9I】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−115097(P2013−115097A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−257435(P2011−257435)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(598172398)株式会社ジャパンディスプレイウェスト (90)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(598172398)株式会社ジャパンディスプレイウェスト (90)

【Fターム(参考)】

[ Back to top ]